## **MP5515**

The Future of Analog IC Technology

Wide Input 2.7 - 18V, 5A, High-Efficiency Bidirectional, Power Back-Up Manager with Integrated Hot-Swap, I<sup>2</sup>C, ADC, and Cap Health Test

#### DESCRIPTION

The MP5515 is an input power conditioning PMIC targeting enterprise solid-state drives, NVDIMM, and other applications with back-up system requirements. The MP5515 consists of input current limiting, input reverse current blocking, and an MPS-patented, high-efficiency, bidirectional, boost-buck converter with only one inductor for energy storage and system back-up power when there is an input power failure. The MP5515 also provides I<sup>2</sup>C interface and ADC. By using the I2C, users can set the input current limit, slew rate, and perform cap health tests. The MP5515 can also monitor system status, such as input voltage, input current, storage voltage, temperature, and provide interrupt options for these features.

The internal input current-limit block prevents inrush current during system start-up while the reverse-current block prevents backup energy from flowing to the failing VIN port. MPS's patented energy storage and release management control circuit minimizes the storage capacitor requirement. It pumps the input voltage to a higher backup voltage and releases the energy over a hold-up time to the system bus voltage in case of an input outage.

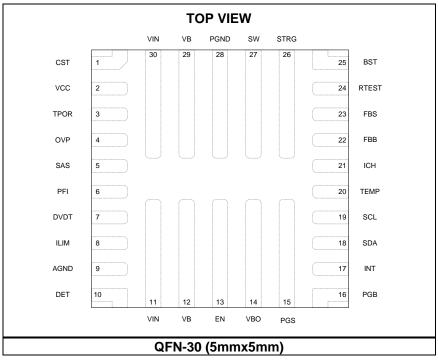

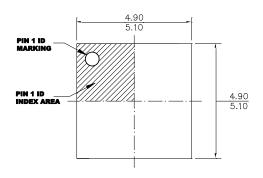

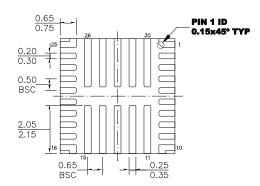

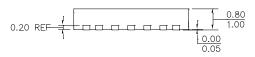

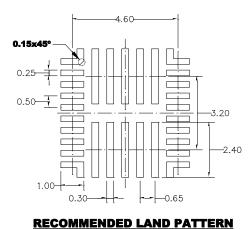

The MP5515 requires a minimal number of standard, external components and is available in a 30-pin QFN (5mmx5mm) package.

### **FEATURES**

- Wide 2.7V-to-18V Operating Input Range

- Up to 32V Programmable Storage Voltage

- Up to 6A Programmable Input Current Limit

- 5A Buck Load Capability

- Adjustable Slew Rate for VB Voltage Rising

- Input Current Limiter with Integrated 14mΩ MOSFET

- Input Over-Voltage Protection (OVP)

- Reverse-Current Protection (RCP)

- Input Power Failure Indicator

- Backup Capacitor Health Test

- Comprehensive Voltage, Current,

Temperature Sensor ADC Conversion

- Thermal Protection

- Available in a QFN-30 (5mmx5mm) Package

#### **APPLICATIONS**

- Solid-State Drives (SSD)

- NVDIMMs

- Hard-Disk Drives

- Power Back-Up Systems

All MPS parts are lead-free, halogen-free, and adhere to the RoHS directive. For MPS green status, please visit the MPS website under Quality Assurance. "MPS" and "The Future of Analog IC Technology" are registered trademarks of Monolithic Power Systems, Inc.

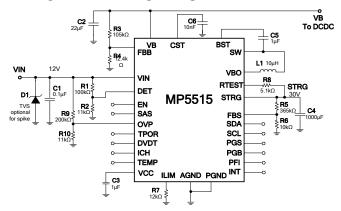

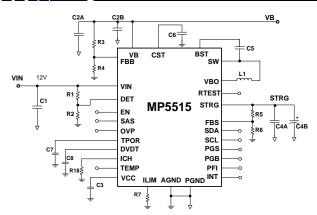

#### TYPICAL APPLICATION

CH1: V<sub>B</sub>

5V/div.

CH2: V<sub>STRG</sub>

10V/div.

CH3: V<sub>PFI</sub>

5V/div.

CH4: I<sub>L</sub>

5A/div.

#### ORDERING INFORMATION

| Part Number | Package          | Top Marking |

|-------------|------------------|-------------|

| MP5515GU*   | QFN-30 (5mmx5mm) | See Below   |

| EVKT-5515   | Evaluation Kit   |             |

<sup>\*</sup> For Tape & Reel, add suffix –Z (e.g. MP5515GU–Z)

### **TOP MARKING**

MPSYYWW

MP5515

LLLLLLL

MPS: MPS prefix YY: Year code WW: Week code

MP5515: Product code of MP5515GU

LLLLLL: Lot number

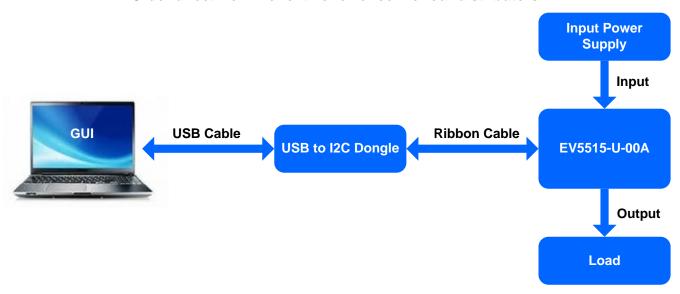

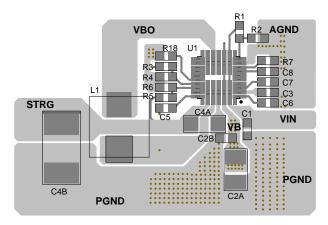

#### **EVALUATION KIT EVKT-5515**

EVKT-5515 Kit contents: (Items can be ordered separately).

| # | Part Number    | Item                                                                           | Quantity |

|---|----------------|--------------------------------------------------------------------------------|----------|

| 1 | EV5515-U-00A   | MP5515GU evaluation board                                                      | 1        |

| 2 | EVKT-USBI2C-02 | Includes one USB to I2C dongle, one USB cable, and one ribbon cable            | 1        |

| 3 | Tdrive-5515    | USB flash drive that stores the GUI installation file and supplement documents | 1        |

#### Order direct from MonolithicPower.com or our distributors.

Figure 1: EVKT-5515 Evaluation Kit Set-Up

#### PACKAGE REFERENCE

| ARSOL | HTE    | MAXIMU     | MPAT   | INGS (1) |

|-------|--------|------------|--------|----------|

| ADOUL | .U I C | IVIAAIIVIU | IVIKAI | INGS ''  |

| $\begin{array}{llllllllllllllllllllllllllllllllllll$ | V V V V V V V V V V V V V V V V V V V |

|------------------------------------------------------|---------------------------------------|

| Junction temperature                                 | C                                     |

| /                                                    |                                       |

## Recommended Operating Conditions (5)

| Necommenueu Operati                  | ing Conditions                  |

|--------------------------------------|---------------------------------|

| Supply voltage (V <sub>IN</sub> )    | 2.7V <sup>(6)</sup> to 18V      |

| Bus voltage (V <sub>B</sub> )        |                                 |

| Storage voltage (V <sub>STRG</sub> ) | V <sub>IN_MAX</sub> + 3V to 32V |

| Max input current                    | 6A                              |

| Max buck-release current.            | 5A                              |

| EN current                           | 0.5mA <sup>(2)</sup>            |

| Operating junction temp. (7          | Γ <sub>1</sub> )40°C to +125°C  |

| Thermal Resistance          | $\boldsymbol{\theta}_{JA}$ | $\boldsymbol{\theta}$ JC |      |

|-----------------------------|----------------------------|--------------------------|------|

| QFN-30 (5mmx5mm)            |                            |                          |      |

| EV5515-U-00A <sup>(7)</sup> | . 35                       | . 6.5                    | °C/W |

| JESD51-7 <sup>(8)</sup>     | . 36                       | 8                        | °C/W |

#### NOTES:

- 1) Exceeding these ratings may damage the device.

- For more detail, refer to the Enable Control section on page 22.

- 3) When these pins are pulled up to the power source, the current should be limited below the maximum value.

- 4) The maximum allowable power dissipation is a function of the maximum junction temperature  $T_J$  (MAX), the junction-to-ambient thermal resistance  $\theta_{JA}$ , and the ambient temperature  $T_A$ . The maximum allowable continuous power dissipation at any ambient temperature is calculated by  $P_D$  (MAX) =  $(T_J$  (MAX)- $T_A$ )/ $\theta_{JA}$ . Exceeding the maximum allowable power dissipation produces an excessive die temperature, causing the regulator to go into thermal shutdown. Internal thermal shutdown circuitry protects the device from permanent damage.

- The device is not guaranteed to function outside of its operating conditions.

- 6) Guaranteed for temperature conditions 25°C or higher. If the temperature is lower than 25°C, one Schottky diode from VIN to VCC is recommended to help start-up from a 2.7V input.

- 7) Measured on EV5515-U-00A, 2-layer 63mmx63mm PCB.

- 8) Measured on JESD51-7, 4-layer PCB.

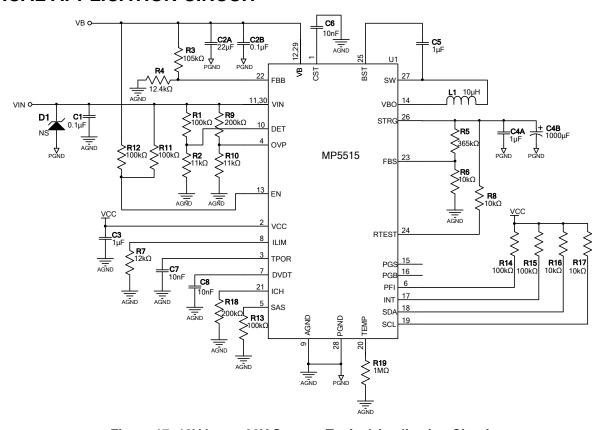

## **ELECTRICAL CHARACTERISTICS**

$V_{IN}$  = 12V,  $V_{EN}$  = 2V,  $T_J$  = -40°C to 125°C <sup>(9)</sup>, typical value is tested at  $T_J$  = 25°C, unless otherwise noted.

| Parameter                                       | Symbol                                                  | Condition                                                                               | Min   | Тур  | Max      | Units    |

|-------------------------------------------------|---------------------------------------------------------|-----------------------------------------------------------------------------------------|-------|------|----------|----------|

| Power Supply                                    |                                                         | -                                                                                       | I.    |      | <u> </u> | <u>I</u> |

| Supply current (shutdown)                       | Is                                                      | EN = 0V, then power on VIN,<br>$T_J = 25^{\circ}C$                                      |       | 2.5  | 5        | μΑ       |

| Supply current (quiescent)                      | ΙQ                                                      | SAS = 2V, EN = 2V, V <sub>FBB/FBS/DET</sub> = 1.1V                                      |       | 1.5  |          | mA       |

| Supply current (quiescent)                      | g                                                       | SAS = 0V, EN = 2V, V <sub>FBB/FBS/DET</sub> = 1.1V                                      |       | 2.5  | 3        | mA       |

| VCC regulator                                   | Vcc                                                     | VIN or VB = 6V, Ivcc = 1mA                                                              | 4.75  | 5    | 5.25     | V        |

| VIN under-voltage lockout threshold rising (10) | $INUV_R$                                                | VCC floating, T <sub>J</sub> = 25°C                                                     |       | 2.5  | 2.68     | V        |

| VIN under-voltage lockout threshold hysteresis  | INUV <sub>HYS</sub>                                     |                                                                                         |       | 0.1  |          | V        |

| VIN to VB current limit MOSFET on resistance    | Rdson                                                   |                                                                                         |       | 14   |          | mΩ       |

| VIN to VB continuous current                    |                                                         | $R_{ILIM} = 36.5 k\Omega$ , $T_J = 25$ °C                                               | 1.92  | 2    | 2.08     | Α        |

| limit                                           | ILIM                                                    | $R_{\text{ILIM}} = 36.5 \text{k}\Omega$ , $T_{\text{J}} = -40^{\circ}\text{C}$ to 125°C | 1.88  | 2    | 2.12     | А        |

| Off state leakage current                       | I <sub>LEAK</sub>                                       | $V_{IN} = 12V$ , $V_B = 0V$ or $V_B = 12V$ , $V_{IN} = 0V$ , $T_J = 25$ °C              |       | 2    | 3        | μA       |

| VB clamping voltage                             | $V_{CLAMP}$                                             | $V_{IN} = 18V$                                                                          | 15.2  | 16   | 16.8     | V        |

| VB rise time (DVDT) control                     | $T_DVDT$                                                | DVDT floating, VIN = 12V, DVDT bits = 00, test VB rise time                             |       | 1.6  |          | ms       |

| (11)                                            | I <sub>DVDT</sub>                                       | Connect capacitor to DVDT, test DVDT charge current                                     |       | 3    |          | μA       |

| Internal reset delay-time                       | $T_DLY$                                                 | TPOR floating, test reset delay time                                                    |       | 1.5  |          | ms       |

| control                                         | I <sub>TPOR</sub>                                       | Connect capacitor to TPOR, test TPOR charge current                                     |       | 1    |          | μA       |

| <b>Energy Storage and Release</b>               |                                                         |                                                                                         |       |      |          |          |

| Storage pre-charge current                      | I <sub>CH-PRE</sub>                                     |                                                                                         | 250   | 350  | 450      | mA       |

| Boost disconnect switch RoN                     | R <sub>dison</sub>                                      |                                                                                         |       | 30   |          | mΩ       |

| Switching peak current @                        | Існ                                                     | ICH floating, L = 10μH                                                                  |       | 2    |          | Α        |

| boost mode                                      |                                                         | $R_{ICH} = 200k\Omega$ , $L = 10\mu H$                                                  |       | 0.65 |          | Α        |

| Energy management HS R <sub>ON</sub>            | R <sub>Hon</sub>                                        |                                                                                         |       | 80   |          | mΩ       |

| Energy management LS Ron                        | R <sub>Lon</sub>                                        |                                                                                         |       | 40   |          | mΩ       |

| Feedback voltage                                | V <sub>FBB-REF</sub> ,                                  | $T_J = 25$ °C                                                                           | 0.792 | 0.8  | 0.808    | V        |

| i eeuback voitage                               | V <sub>FBS-REF</sub> ,<br>V <sub>DET-REF</sub>          | $T_J = -40^{\circ}\text{C} \text{ to } 125^{\circ}\text{C}$                             | 0.786 | 0.0  | 0.812    | v        |

| Feedback current                                | I <sub>FBB,</sub> I <sub>FBS,</sub><br>I <sub>DET</sub> | $V_{\text{FBB}} = V_{\text{FBS}} = V_{\text{DET}} = 0.85V$                              |       | 10   | 50       | nA       |

ELECTRICAL CHARACTERISTICS (continued)  $V_{IN} = 12V$ ,  $V_{EN} = 2V$ ,  $T_{J} = -40$ °C to 125°C (9), typical value is tested at  $T_{J} = 25$ °C, unless otherwise noted.

| Parameter                                          | Symbol                 | Condition                                                 | Min | Тур  | Max  | Units              |

|----------------------------------------------------|------------------------|-----------------------------------------------------------|-----|------|------|--------------------|

| VIN over-voltage threshold                         | Vovp                   | OVP pin voltage rising                                    |     | 0.81 |      | V                  |

| VIN over-voltage hysteresis                        | Vovp-HYS               | OVP pin voltage hysteresis                                |     | 45   |      | mV                 |

| Vs over-voltage threshold                          | V <sub>S-OVP</sub>     |                                                           |     | 1.1  |      | V <sub>FBS</sub> - |

| VIN to VB ISOFET turn-on voltage                   |                        | VIN - VB, VB = 5V, then start VIN                         |     | 0.2  |      | V                  |

| VIN to VB ISOFET shut-down current                 | I <sub>IN-VB-OFF</sub> | PFI = low                                                 |     | -250 | 0    | mA                 |

| PFI high threshold                                 | PFI <sub>H</sub>       |                                                           |     | 1.02 |      | V <sub>DET</sub> - |

| PFI low threshold                                  | PFIL                   |                                                           |     | 0.99 |      | V <sub>DET</sub> - |

| PFI falling delay                                  | PFI <sub>D-L</sub>     |                                                           |     | 0.5  |      | μs                 |

| PFI rising delay                                   | PFI <sub>D-H</sub>     |                                                           |     | 200  |      | μs                 |

| PFI sink current capability                        | V <sub>PFI</sub>       | Sink 4mA                                                  |     |      | 0.3  | V                  |

| PGB high threshold                                 | PG <sub>H-VB</sub>     |                                                           |     | 0.95 |      | V <sub>FBB</sub> - |

| PGB low threshold                                  | PG <sub>L-VB</sub>     |                                                           |     | 0.9  |      | V <sub>FBB</sub> - |

| PGB delay                                          | PG <sub>D-VB</sub>     | Rising and falling edge                                   |     | 5    |      | μs                 |

| PGB sink-current capability                        | $V_{PG-VB}$            | Sink 4mA                                                  |     |      | 0.3  | V                  |

| PGS high threshold                                 | PG <sub>H-S</sub>      | PGS threshold bits = 1111                                 |     | 0.97 |      | V <sub>FBS</sub> - |

| PGS low threshold                                  | PG <sub>L-S</sub>      | PGS threshold bits = 1111                                 |     | 0.95 |      | V <sub>FBS</sub> - |

| PGS delay                                          | PGS <sub>D-S</sub>     | Rising and falling edge                                   |     | 25   |      | μs                 |

| PGS sink-current capability                        | $V_{PG-S}$             | Sink 4mA                                                  |     |      | 0.3  | V                  |

| Buck-mode dumping valley current limit             | IDUMP-VALLEY           |                                                           | 5   | 6.5  |      | А                  |

| Release-buck switching frequency                   | f <sub>s-RLS</sub>     | V <sub>STRG</sub> from 32V to 10V,<br>buck_Fsw bits = 100 | 380 | 480  | 580  | kHz                |

| VB under-voltage lockout threshold rising (10)     | INUVB <sub>R</sub>     |                                                           | 2.2 | 2.35 | 2.5  | V                  |

| VB under-voltage lockout threshold hysteresis (10) | INUVB <sub>HYS</sub>   |                                                           |     | 0.1  |      | V                  |

| ADC                                                |                        |                                                           |     |      |      |                    |

| Voltage range                                      |                        |                                                           | 0   |      | 1.28 | V                  |

| ADC resolution (12)                                |                        |                                                           |     | 10   |      | bits               |

| ADC conversion time (12)                           |                        | ADC conversion for one data                               |     | 45   |      | μs                 |

## **ELECTRICAL CHARACTERISTICS** (continued)

$V_{IN} = 12V$ ,  $V_{EN} = 2V$ ,  $T_J = -40$ °C to 125°C <sup>(9)</sup>, typical value is tested at  $T_J = 25$ °C, unless otherwise noted.

| Parameter                                       | Symbol           | Condition                        | Min | Тур | Max | Units |

|-------------------------------------------------|------------------|----------------------------------|-----|-----|-----|-------|

| Logic Interface (SDA, SCL, IN                   | NT, SAS, EN      | )                                | •   | •   |     | •     |

| High-level input voltage                        | ViH              | SDA, SCL, SAS, EN                | 1.2 |     |     | V     |

| Low-level input voltage                         | VIL              | SDA, SCL, SAS, EN                |     |     | 0.4 | V     |

| Low-level output voltage                        | Vol              | Sink 4mA, SDA, INT               |     |     | 0.3 | V     |

| Input leakage current                           | I <sub>LKG</sub> | Connected to 6V, SCL             |     | 10  |     | nA    |

| High level output leakage                       |                  | Open drain, connected to 6V, SDA |     | 10  |     | nA    |

| Protection                                      |                  |                                  |     |     |     | -     |

| Thermal shutdown, forced backup (12)            | T <sub>SD</sub>  |                                  |     | 150 |     | °C    |

| Thermal shutdown, forced backup hysteresis (12) | T <sub>HYS</sub> |                                  |     | 25  |     | °C    |

| Thermal warning (12)                            | T <sub>WRN</sub> |                                  |     | 120 |     | °C    |

#### NOTES:

- 9) Guaranteed by over-temperature correlation, not tested in production.

- 10) VIN UVLO controls the IC start-up voltage threshold. VB UVLO controls energy storage and release circuitry. The internal VCC is powered from both VIN and VB. If either VIN or VB is higher than UVLO, the IC will not shut down.

- 11) Refer to the "Power-On Reset Delay and VB Rising Control" section on page 19 for detailed calculations.

- 12) Guaranteed by characterization, not tested in production.

## I<sup>2</sup>C PORT SIGNAL CHARACTERISTICS

| Danamatan                                                                              | Council of          | Condition                              | Cb = | 100pF | Cb = 4   | 00pF | l lucit a |

|----------------------------------------------------------------------------------------|---------------------|----------------------------------------|------|-------|----------|------|-----------|

| Parameter                                                                              | Symbol              | Condition                              | Min  | Max   | Min      | Max  | Units     |

| SCLH and SCL clock frequency                                                           | fschl               |                                        | 0    | 3.4   | 0        | 0.4  | MHz       |

| Set-up time for a repeated start condition                                             | Tsu;sta             |                                        | 160  | -     | 600      | -    | ns        |

| Hold-time (repeated) start condition                                                   | THD;STA             |                                        | 160  | -     | 600      | -    | ns        |

| Low period of the SCL clock                                                            | TLOW                |                                        | 160  | -     | 1300     | -    | ns        |

| High period of the SCL clock                                                           | <b>t</b> HIGH       |                                        | 60   | -     | 600      | -    | ns        |

| Data set-up time                                                                       | TSU:DAT             |                                        | 10   | -     | 100      | -    | ns        |

| Data hold time                                                                         | T <sub>HD;DAT</sub> |                                        | 0    | 70    | 0        | -    | ns        |

| Rise time of SCLH signal                                                               | TrCL                |                                        | 10   | 40    | 20*0.1Cb | 300  | ns        |

| Rise time of SCLH signal after a repeated start condition and after an acknowledge bit | T <sub>fCL1</sub>   |                                        | 10   | 80    | 20*0.1Cb | 300  | ns        |

| Fall time of SCLH signal                                                               | T <sub>fCL</sub>    |                                        | 10   | 40    | 20*0.1Cb | 300  | ns        |

| Rise time of SDAH signal                                                               | $T_{rDA}$           |                                        | 10   | 80    | 20*0.1Cb | 300  | ns        |

| Fall time of SDAH signal                                                               | T <sub>fDA</sub>    |                                        | 10   | 80    | 20*0.1Cb | 300  | ns        |

| Set-up time for stop condition                                                         | Tsu;sto             |                                        | 160  | -     | 600      | -    | ns        |

| Bus free time between a stop and start condition                                       | T <sub>BUF</sub>    |                                        | 160  | -     | 1300     | -    | ns        |

| Data valid time                                                                        | TVD;DAT             |                                        | -    | 16    | -        | 90   | ns        |

| Data valid acknowledge time                                                            | T <sub>VD;ACK</sub> |                                        | -    | 160   | -        | 900  | ns        |

| Pulse width of spikes that must be suppressed by the input filter                      | t <sub>SP</sub>     |                                        | 0    | 10    | 0        | 50   | ns        |

| Capacitive load for each                                                               |                     | SDAH and SCLH line                     | -    | 100   | -        | 400  | pF        |

| bus line                                                                               | Сь                  | SDAH + SDA line and<br>SCLH + SCL line | -    | 400   | -        | 400  | pF        |

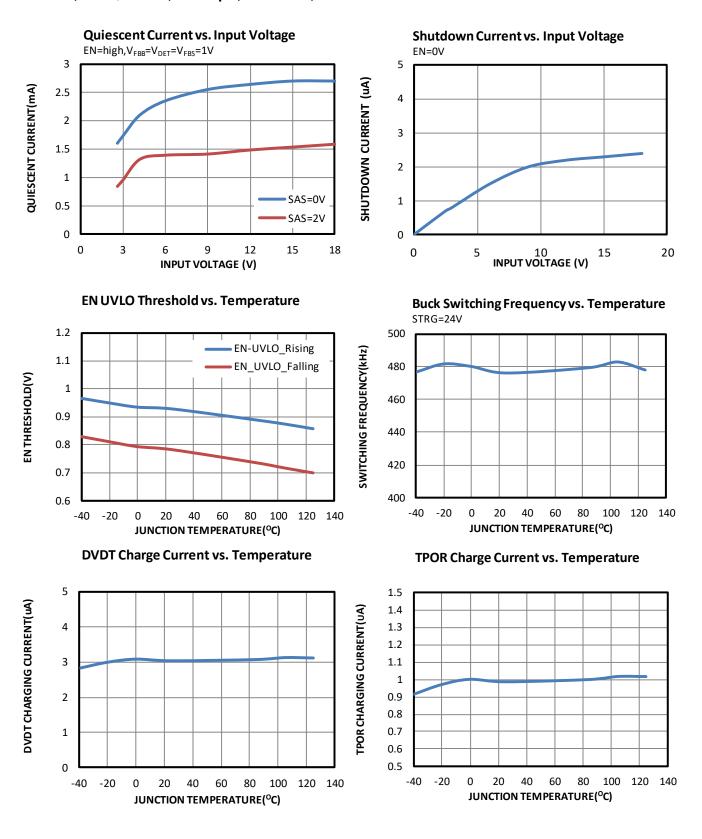

## TYPICAL CHARACTERISTICS

$V_{IN} = 12V$ ,  $VB_{RLS} = 7.5V$ ,  $L = 10\mu H$ ,  $T_A = 25$ °C, unless otherwise noted.

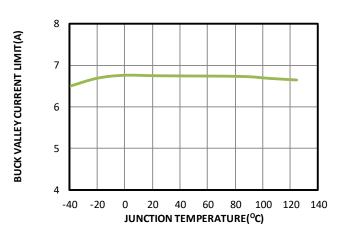

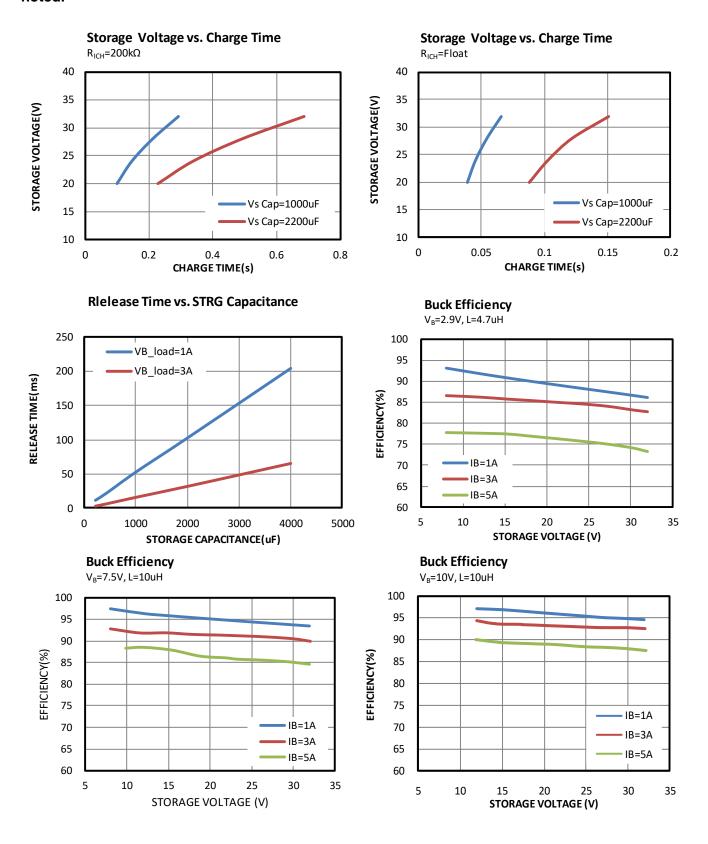

## TYPICAL CHARACTERISTICS (continued)

$V_{IN}$  = 12V,  $VB_{RLS}$  = 7.5V, L = 10 $\mu$ H,  $T_A$  = 25°C, unless otherwise noted.

#### **Buck Valley Current Limit vs. Temperature**

#### **VB Rising Time vs. DVDT Capacitance**

#### Hot-swap Current Limit vs. ILIM Resistor

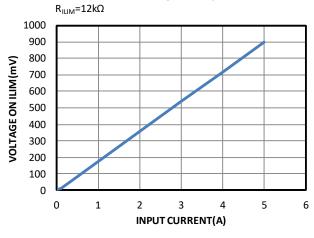

#### **ILIM Monitor Voltage vs. Input Current**

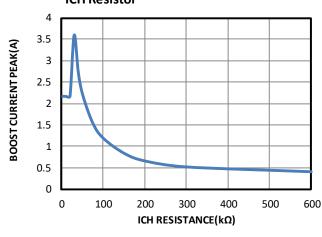

# Boost switching Peak Current vs. ICH Resistor

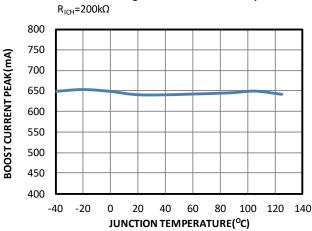

Boost switching Peak Current vs. Temperature

## TYPICAL CHARACTERISTICS (continued)

$V_{IN}$  = 12V,  $VB_{RLS}$  = 7.5V, L = 10 $\mu$ H,  $T_A$  = 25°C, unless otherwise noted.

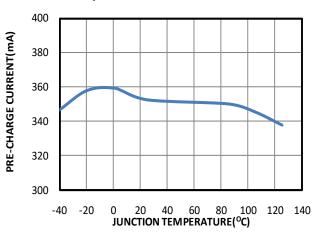

# **Boost Pre-Charge Current vs. Temperature**

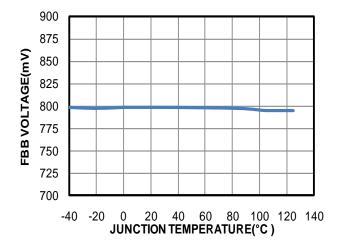

FBB vs. Temperature

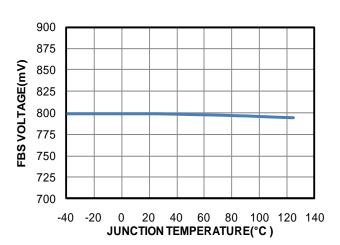

FBS vs. Temperature

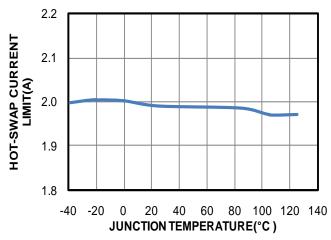

Hot-Swap Current Limit vs. Temperature

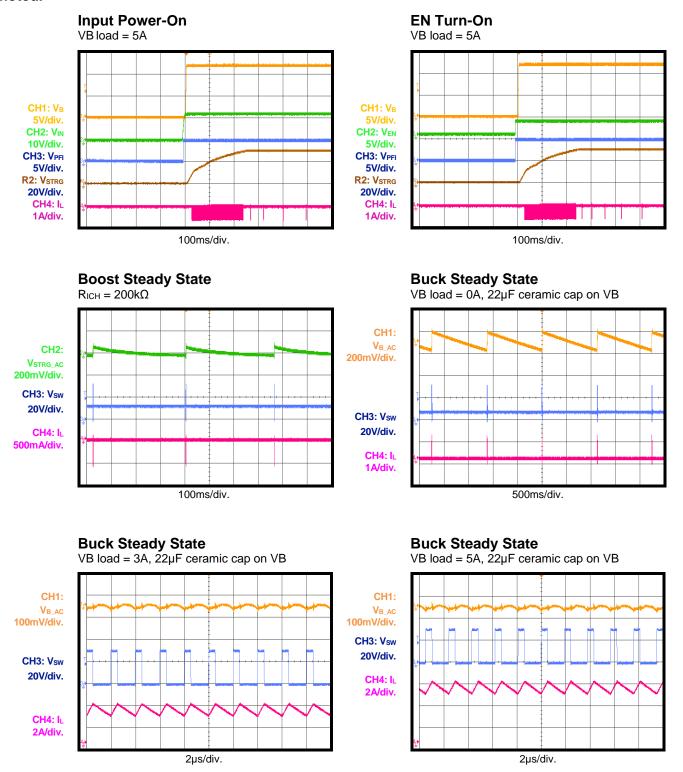

#### TYPICAL PERFORMANCE CHARACTERISTICS

$V_{IN}$  = 12V,  $V_{STRG}$  = 30V,  $V_{PFI}$  = 8V,  $V_{BRLS}$  = 7.5V, L = 10 $\mu$ H,  $I_{LOAD}$  = 5A,  $T_A$  = 25°C, unless otherwise noted.

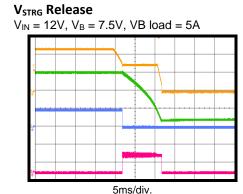

## TYPICAL PERFORMANCE CHARACTERISTICS (continued)

$V_{IN} = 12V$ ,  $V_{STRG} = 30V$ ,  $V_{PFI} = 8V$ ,  $V_{RLS} = 7.5V$ ,  $L = 10\mu H$ ,  $I_{LOAD} = 5A$ ,  $T_A = 25^{\circ}C$ , unless otherwise noted.

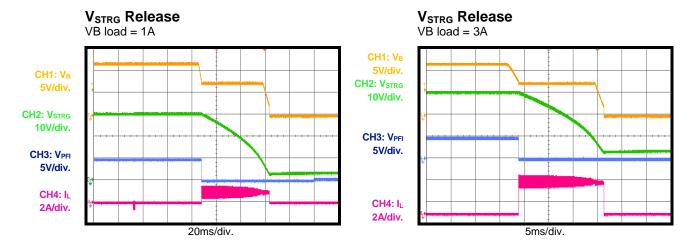

## TYPICAL PERFORMANCE CHARACTERISTICS (continued)

$V_{\text{IN}}$  = 12V,  $V_{\text{STRG}}$  = 30V,  $V_{\text{PFI}}$  = 8V,  $V_{\text{BRLS}}$  = 7.5V, L = 10 $\mu$ H,  $I_{\text{LOAD}}$  = 5A,  $T_{\text{A}}$  = 25°C, unless otherwise noted.

VB load = 5A

## **PIN FUNCTIONS**

| QFN-30<br>Pin# | Name | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|----------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1              | CST  | Storage capacitor for the internal charge pump. A 10nF capacitor is required between CST and AGND to drive the input current-limit MOSFET and disconnection MOSFET. Do not connect CST to a capacitor over 47nF.                                                                                                                                                                                                                                                                                                                                                              |

| 2              | VCC  | Internal LDO output. VCC provides power for the internal circuits. Decouple VCC with a minimum 1µF ceramic capacitor placed as close to VCC as possible. Do not add an external load to VCC.                                                                                                                                                                                                                                                                                                                                                                                  |

| 3              | TPOR | <b>Power-on reset delay.</b> Connect a capacitor 1nF or higher between TPOR and AGND to determine the power-on reset delay time. Leave TPOR floating for the 1.5ms default power-on reset delay time                                                                                                                                                                                                                                                                                                                                                                          |

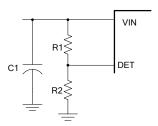

| 4              | OVP  | <b>Over-voltage detection.</b> A resistor divider from VIN to OVP can program the input over-voltage threshold. If the OVP voltage is higher than 0.81V, the MP5515 is forced into buck mode and recovers when the OVP voltage drops to 0.765V and VB triggers VB_UVLO with a new TPOR time as the first power-on in default. Connect OVP to AGND if the OVP function is not needed.                                                                                                                                                                                          |

| 5              | SAS  | Configured as SAS function. When applying a high-level voltage on SAS, the input current limit switch turns off, and backup mode begins operating. When VB and VSTRG are discharged to UVLO, buck_release shuts down, but VCC continues working. SAS is pulled down internally through a $4M\Omega$ resistor.                                                                                                                                                                                                                                                                 |

| 6              | PFI  | Power failure indicator. PFI is an open-drain output. To indicate a signal, PFI should be pulled up to a power source through a resistor. PFI goes high if the DET voltage exceeds 1.02 x V <sub>DET-REF</sub> . PFI goes low if the DET voltage drops below 0.99 x V <sub>DET-REF</sub> . Once PFI is pulled low, a 200µs blanking time keeps PFI low. PFI is pulled down if SAS, OTP, or EN is off. If PFI is pulled up to another external DC source, PFI can still be pulled low when EN is low. If both VIN and VCC are not available, PFI is pulled low to about 0.85V. |

| 7              | DVDT | <b>Bus voltage start-up slew rate control.</b> Connect a capacitor 1nF or higher from DVDT to AGND to program different VB charge-up slew rates. The DVDT time can be controlled by the I <sup>2</sup> C if DVDT is floating.                                                                                                                                                                                                                                                                                                                                                 |

| 8              | ILIM | <b>DC input current limit.</b> Connect a resistor between ILIM and AGND to adjust the DC current limit from VIN to VB. Apply a voltage higher than 1.5V on ILIM to trigger OCP and disable the ISOFET from VIN to VB.                                                                                                                                                                                                                                                                                                                                                         |

| 9              | AGND | IC signal ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 10             | DET  | <b>Input voltage detection sense.</b> DET sets the buck release start voltage when VIN drops.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 11, 30         | VIN  | Input supply voltage. Place a $0.1\mu F$ ceramic capacitor as close to VIN as possible. A TVS diode at the input is necessary if the VIN power line is long and the VIN voltage spike is high in the system. Otherwise, the TVS can be ignored. Refer to the Selecting the Input Capacitor and TVS section on page 37 for more detail.                                                                                                                                                                                                                                        |

| 12, 29         | VB   | Bus voltage. A $22\mu F$ to $47\mu F$ ceramic capacitor is required as close to VB as possible.                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 13             | EN   | <b>On/off control.</b> EN enables or disables the internal circuits. When EN is low, the MP5515 is forced to buck mode until $V_{STRG}$ is discharged. The IC shuts down after VB drops, and EN is pulled down internally through a 4M $\Omega$ resistor. There is more sink current on EN if a voltage 2V or higher is forced on EN.                                                                                                                                                                                                                                         |

| 14             | VBO  | Source of the internal disconnect MOSFET. Connect an inductor between SW and VBO for backup boost charge and buck release operation.                                                                                                                                                                                                                                                                                                                                                                                                                                          |

## PIN FUNCTIONS (continued)

| QFN-30<br>Pin # | Name  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-----------------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15              | PGS   | Storage voltage power good indicator. By default with the PGS threshold bits = 1111, PGS goes high if the FBS voltage exceeds 0.97 x V <sub>FBS-REF</sub> . PGS goes low if the FBS voltage drops below 0.95 x V <sub>FBS-REF</sub> . PGS can be programmed by the PGS threshold bits. PGS is driven by an internal circuit, which does not require an external pull-up. PGS is low even if the IC is disabled, but if both VIN and VCC power are not available, PGS is pulled low to about 1.3V. |

| 16              | PGB   | Bus voltage power-good indicator. PGB goes high if the FBB voltage exceeds 0.95 x V <sub>FBB-REF</sub> . PGB goes low if the FBB voltage drops below 0.9 x V <sub>FBB-REF</sub> . PGB is driven by an internal circuit, which does not require an external pull-up. PGB is low even if the IC is disabled, but if both VIN and VCC power are not available, PGB is pulled low to about 1.3V.                                                                                                      |

| 17              | INT   | Interrupt output from the MP5515. INT is an open-drain output. Even if INT is pulled up to external DC source, INT is pulled low when EN is low and the IC is not in buck switching mode. If both VIN and VCC are not available, INT is pulled low only to about 0.85V.                                                                                                                                                                                                                           |

| 18              | SDA   | I <sup>2</sup> C serial data.                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 19              | SCL   | I <sup>2</sup> C serial clock.                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 20              | TEMP  | Temperature sensor input from thermistor to ADC.                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 21              | ICH   | <b>Boost-mode charge switching peak current programmable.</b> Float ICH to set the boost switching peak current at 2A.                                                                                                                                                                                                                                                                                                                                                                            |

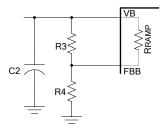

| 22              | FBB   | Bus voltage feedback sense. FBB regulates the bus voltage in buck mode.                                                                                                                                                                                                                                                                                                                                                                                                                           |

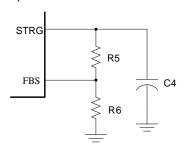

| 23              | FBS   | Storage voltage feedback sense. FBS sets the storage voltage in boost mode.                                                                                                                                                                                                                                                                                                                                                                                                                       |

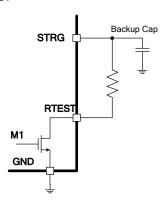

| 24              | RTEST | Resistor connect for capacitor health test. In backup capacitor health test mode, RTEST is pulled to GND internally. One resistor from STRG to RTEST can discharge the backup capacitor. The discharge current through RTEST must be limited below 500mA.                                                                                                                                                                                                                                         |

| 25              | BST   | <b>Bootstrap.</b> A bootstrap capacitor is required from BST to SW to supply the high-side switch driver.                                                                                                                                                                                                                                                                                                                                                                                         |

| 26              | STRG  | <b>Backup energy storage.</b> Connect a backup capacitor to STRG for energy storage and release operation.                                                                                                                                                                                                                                                                                                                                                                                        |

| 27              | SW    | <b>Switch output.</b> SW is used for the energy storage and release circuitry. Connect an inductor between SW and VBO.                                                                                                                                                                                                                                                                                                                                                                            |

| 28              | PGND  | Power ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

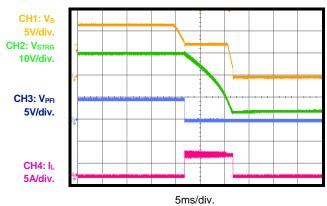

## **BLOCK DIAGRAM**

Figure 2: Functional Block Diagram

#### **OPERATION**

The MP5515 is an energy backup and management unit in a QFN-30 (5mmx5mm) package. The MP5515 provides a very compact and efficient energy management solution for typical solid-state drive or hard disk drive applications. MPS's patented lossless energy storage and release management circuits use a bidirectional buck-boost converter to achieve optimal energy transfer and provide the most cost-effective energy storage solution.

The integrated boost converter raises the energy backup voltage level. The backup feedback resistor divider sets the backup voltage. If the input shuts down suddenly, the internal buck converter transfers the energy from the backup capacitor to the bus and holds the bus voltage when the system consumes the energy from the backup capacitor.

The MP5515 also features an I<sup>2</sup>C interface. This interface can be used to write the control command and the monitor system status. One integrated ADC converter converts the voltage, current, and temperature sensor signals.

#### Start-Up

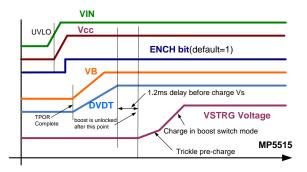

When the VIN power is higher than its undervoltage lockout (UVLO) threshold, the VCC and I<sup>2</sup>C interface is enabled. After the power-on reset delay time, if VCC is ready and VIN is 0.2V higher than VB, the isolation MOSFET (ISOFET) from VIN to VB is turned on, and the bus capacitor is charged from 0V to VIN controlled by the DVDT slew rate.

When the DVDT voltage is saturated, the backup boost converter is unlocked and can be enabled by the register bits. There is a timer for ~1.2ms of delay time before starting the boost converter to ensure that the ISOFET is fully turned on.

The backup boost converter is enabled by default. The storage voltage is charged up with about 350mA of trickle current during the precharge period. Once the storage voltage is close to VB, the boost switching circuit initiates, and the storage voltage is boosted and regulated to the target voltage (see Figure 3).

Figure 3: System Power-Up Sequence

#### **Back-Up Voltage**

After the start-up period, the internal boost converter regulates the backup voltage to the set value automatically. The MP5515 uses burst mode to minimize the converter's power loss. When the storage voltage drops below the set voltage, burst mode initiates and charges the storage capacitor.

During the boost period, the boost switching current limit and the low-side MOSFET (LS-FET) control the boost. When the LS-FET turns on, the inductor current increases until it reaches its peak current level set by ICH. After reaching the peak current level, the LS-FET turns off for the set minimum off time. At the end of this minimum off time, if the feedback voltage remains below the 0.8V internal reference, the LS-FET turns on again. Otherwise, the MP5515 waits until the voltage drops below the reference before turning on the LS-FET. In boost mode, the high-side MOSFET (HS-FET) does not turn on, and the inductor current conducts through the body diode of the HS-FET.

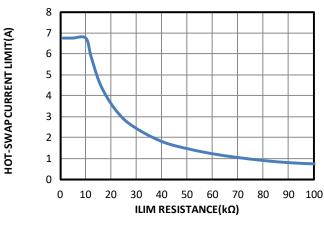

The boost-current limit is programmed by the ICH resistor. The programmed boost-switching current limit can be estimated with Equation (1):

$$I_{CH}(A) = \frac{88}{R_{ICH}(k\Omega)} + \frac{V_{IN}}{L(H) \times 10^7} + 0.1$$

(1)

Where  $R_{\text{ICH}}$  is the resistor connected to ICH, and L is the boost inductor.

The boost switching current limit is programmed by the ICH resistor (0.5A to 2A recommended for normal application). By floating ICH, the boost switching peak current is set at 2A by default with ICH bits = 11 (for typical 12V input and 10µH inductor application conditions).

Refer to the ICH bits register description on page 31 for other boost peak settings with ICH floating.

The MP5515 applies an over-voltage protection (OVP) function for  $V_{STRG}$ . If the feedback voltage of  $V_{STRG}$  on FBS is over 1.1 x  $V_{FBS-REF}$ , the MP5515 shuts down the LS-FET of the boost converter until  $V_{STRG}$  drops to the regulating voltage. It is not necessary to add an external power to STRG with a voltage higher than the  $V_{STRG}$  regulation voltage.

#### **Power-Down Release**

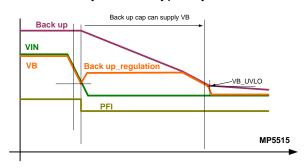

After the first start-up period and the boost starts switching, the MP5515 registers and enables the release function. Once the input power drops and DET drops to  $0.99 \times V_{DET-REF}$ , the storage boost converter stops charging and works in buck-release mode. At the same time, the ISOFET shuts down to prevent a negative current from VB to VIN.

In buck mode, the MP5515 transfers energy from the high-voltage storage capacitor to the low-voltage bus capacitor. The regulated bus voltage is determined by  $V_{\text{FBB-REF}}$  and the resistor divider from VB to FBB.

Figure 4 shows the detailed system shutdown process. Buck mode has a max current limit function to limit the release current. In each buck mode switching cycle, the high-side switch does not turn on until the inductor current drops to a 6.5A valley current, typically.

Figure 4: VIN Shutdown Sequence

#### **Input Recovery Start-Up**

If the input power fails and is restored, the MP5515 remains in buck release mode. When STRG is discharged and VB drops to VB\_UVLO, the MP5515 restarts from the recovered VIN power, which is a new input power start-up cycle with TPOR delay.

#### **Input Current Limit**

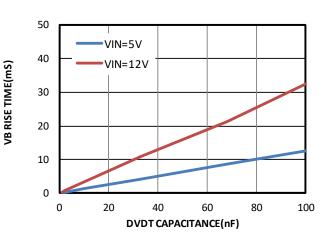

The input current limit controls the input inrush current of the ISOFET carefully to prevent an inrush current from VIN to VB. The internal DVDT bits or external DVDT cap can set the soft-start time. In addition to the soft-start process, ILIM can limit the steady-state current by connecting a resistor between ILIM and AGND to set the current limit. The current limit can be estimated with Equation (2):

$$I_{LIM} = \frac{70.04}{R_{ILM}(k\Omega)} + 0.08 \tag{2}$$

Where  $R_{\text{ILIM}}$  is the current-limit setting resistor from ILIM to AGND.

The voltage on ILIM can also monitor and indicate the current in the ISOFET. The relationship between the input current and ILIM voltage can be estimated with Equation (3):

$$I_{IN} = \frac{V_{ILIM} * 64.26}{R_{ILIM} (k\Omega)} + 0.08$$

(3)

Where  $V_{\text{ILIM}}$  is the ILIM voltage.  $V_{\text{ILIM}}$  can be read through an ADC converter.

The voltage on ILIM is lower than 1.09V in normal applications. If a voltage greater than 1.5V is applied on ILIM externally, the ISOFET is shut down, and the MP5515 enters a buck-up process.

When the VB load is close to the ILIM threshold, during every boost refresh cycle, the input current may easily trigger the current limit as well as the system interrupt. To avoid continuously triggering ILIM interrupt in this condition, during every boost-up refresh cycle, the input over current-interrupt is masked automatically. The mask time depends on the boost-up switching time.

Once the input over-current threshold is triggered and FBB drops to  $V_{\text{FBB-REF}}$ , the backup buck converter starts working to maintain VB. Once FBB is charged back to 105% of  $V_{\text{FBB-REF}}$ , the buck is disabled again in this condition. During the boost refresh cycle, the buck converter is not enabled, even if the over-current threshold is triggered.

# Power-On Reset Delay and VB Rising Control

TPOR controls the power-on reset function for hot swapping. By floating TPOR, the TPOR time is about 1.5ms by default. If an external capacitor is connected to TPOR, an internal 1µA current charges the capacitor and determines the TPOR time (charge TOPR cap from 0V to 1V). The power-reset-delay time can be estimated with Equation (4):

$$T_{D} = \frac{C_{TPOR} \times 1V}{1\mu A}$$

(4)

After the TPOR time, one capacitor across DVDT programs the VB soft-start (SS) time. During the SS period, the relationship between VB and DVDT can be estimated with Equation (5):

$$VB = 13 \times V_{DVDT} \tag{5}$$

Where  $V_{DVDT}$  is the DVDT capacitor voltage charged by a  $3\mu A$  current. The  $V_{DVDT}$  charge is saturated to about 1.23V.

The VB soft-start time from 0V to VIN can be estimated with Equation (6):

$$T_R = \frac{VB \times C_{DVDT}}{13 \times 3 \,\mu\text{A}} \tag{6}$$

By floating DVDT, the VB rising time can be programmed by the internal DVDT register bits. By default, the DVDT bit is set to 00, and the VB slew rate is about 7.5V/ms. VB from 0V to 12V is 1.6ms by default, typically, if DVDT is floating. Refer to the DVDT register description on page 33 for other DVDT bit settings.

#### **Reverse-Current Protection (RCP)**

The VIN to VB MOSFET turns on when the input voltage exceeds the VIN UVLO threshold and VIN becomes greater than VB + 0.2V. This MOSFET turns off when the DET voltage falls, causing the MP5515 to enter buck-release mode and does not turn on again until buck mode finishes.

The ISOFET circuit applies reverse-current protection (RCP) when energy is released from the storage capacitors to VB. Typically, a 250mA reverse current from VB to VIN shuts down the ISOFET.

#### **Start-Up Sequence**

After the IC is enabled, MP5515 starts to work with the TPOR reset time and DVDT soft-start time. During the VB rising time, an internal charge pump charges the CST capacitor. This provides a driver source for the hot-swap MOSFET. Too short of a DVDT time may trigger the input current-limit threshold. Too large of a CST capacitor may affect the charge-pump slew rate. A 10nF CST capacitor is recommended. During the DVDT soft start, the VB capacitor is charged, and the STRG capacitor is not charged.

Once VB is charged, the DVDT voltage charges to about 1.23V and is held at this saturated voltage. If PFI is high and DVDT saturates, the charge function is enabled and the storage capacitor charges to the target voltage.

## **Backup Capacitance Test**

The MP5515 features a back-up capacitor test by discharging the backup capacitor through one external resistor from STRG to RTEST. Figure 5 shows the discharge block. The MOSFET is about  $4.5\Omega$ , and the peak discharge current must be limited below 500mA by an external resistor, even it is discharged in a short time.

Figure 5: Backup Capacitance Test Circuit

When the Start Cap Test register bit is set, the MP5515 disables the boost charge switching, and RTEST is connected to GND through the internal MOSFET (M1) for energy discharging. The MP5515 enables the  $V_{\rm STRG}$  ADC conversion when FBS drops to the  $V_{\rm FBS-REF}$  threshold (SOC can read the STRG voltage

through the I²C). Simultaneously, an internal counter is enabled to measure the discharge time. The counter continues until the cap voltage drops below the PGS threshold voltage. When V<sub>STRG</sub> drops to the PGS threshold, the ADC reads V<sub>STRG</sub> again, and the Cap Test Done register is set to indicate that cap test is complete. Cap Test Done produces one interrupt to inform the SOC that the test has been completed. The SOC can read the backup voltage and the counter timer registers. With the initial voltage and end voltage reading, the discharge time can be determined as acceptable or not.

At the first ADC conversion, the MP5515 reads  $V_{STRG}$  and stores this in the register ADC Backup Voltage Data2. At the end of the capacitor discharge ADC records the end voltage in the register 'ADC Backup Voltage Data1. The counter result is stored in the register Cap Test Timer.

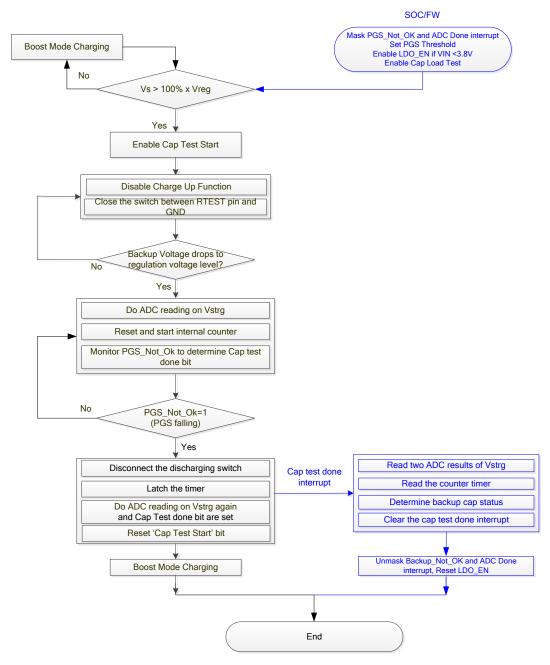

After the cap test is done, the Cap Test Start bit is reset automatically, and the recharge function is enabled automatically. Figure 6 shows the work flow of performing the capacitance test.

SOC capacitance test function follows the following operations:

- Write register 04h bit[2] and bit[6] to code 1 (mask PGS Not Ok and ADC Done interrupt).

- 2. Write register 06h to code 00h or another value (set PGS Threshold at 80% or another ratio of regulation).

- If VIN is lower than 3.8V, write register 1Bh bit[1] to code 1. This turns on the internal V<sub>STRG</sub> to the VCC LDO. If VIN is higher than 3.8V, ignore this step.

- 4. Write register 01h bit[3] to code 1 (request Start Cap Test).

The MP5515 disables the  $V_{STRG}$  charge function automatically after  $V_{STRG}$  is charged higher than the FBS-set voltage. Register 01h bit[0] does not change.

The MP5515 starts discharging the STRG cap through an external resistor after V<sub>STRG</sub> is fully charged.

The MP5515 starts the ADC only when  $V_{\text{FBS}}$  drops to the  $V_{\text{REF-FBS}}$  threshold. ADC reads

$V_{\text{STRG}}$  and stores data in ADC Backup Voltage Data2.

The internal timer starts when  $V_{\text{FBS}}$  drops to the  $V_{\text{REF-FBS}}$  threshold.

5. Wait for the interrupt from the MP5515 (afterward, if register 02h bit[7] is 1, the cap test is complete).

When  $V_{\text{STRG}}$  discharges to the PGS threshold, the discharge stops, and the timer value is written to register Cap Test Timer.

When PGS Threshold falling is triggered, the MP5515 starts ADC a second time and stores data in ADC Backup Voltage Data1.

After ADC conversion, the MP5515 sets the Cap Test Done interrupt.

The MP5515 resets register 01h bit[3] to code 0 automatically to clear Cap Test Start.

The MP5515 re-enables the boost charge function automatically.

Read registers 12h bit[7:0], 13h bit[1:0] and store as V<sub>FINAL</sub>, total 10 bits (12h is the high byte, 13h is the low byte).

Read registers 14h bit[7:0], 15h bit[1:0] and store as V<sub>INITIAL</sub>, total 10 bits (14h is the high byte, 15h is the low byte)

Read registers 16h bit[7:0], 17h bit[7:0] and store as Time, total 16 bits (16h is the low byte, 17h is the high byte).

- 7. Write register 02h bit[7] to code 1 to reset the cap test interrupt event. Write both register 04h bit[2] and bit[6] to code 1 to reenable PGS Not OK and ADC Done interrupt. Write register 1Bh bit[1] to code 0 if it was set to 1 in step 3.

- 8. Calculate ADC results with Equation (7):

$$C_{STRG} = \frac{Time}{R_{DISCH} \times \ln(\frac{V_{INITIAL} + R_{DISCH} \times I_{LDO}}{V_{FINAL} + R_{DISCH} \times I_{LDO}})}$$

(7)

Where V<sub>INITIAL</sub> is V<sub>STRG</sub> before the discharge timer starts stored in ADC Backup Voltage Data2 (in V), V<sub>FINAL</sub> is V<sub>STRG</sub> after discharge completes and stored in ADC Backup Voltage

Data1 register (in V), and  $R_{DISCH}$  is the resistor between STRG and RTEST (in  $k\Omega$ ).

When VIN is less than 5V and register 1Bh bit[1] = 1,  $I_{LDO}$  is typically 2mA, which is the VCC LDO current from  $V_{STRG}$ . Otherwise,  $I_{LDO}$  is 0mA. It is recommended to reset the LDO\_EN bit after the capacitance test finishes

to save operation current (use the mA unit for the LDO in the cap test).

Time is recorded in the counter register Cap Test Timer (unit in 1ms).

Refer to the ADC Results register on page 32 for cap test time and voltage calculation.

Figure 6: Backup Capacitance Test Work Flow

The MP5515 enters buck mode if VIN fails during the cap test. The cap test cannot be done in buck mode. For more information on the cap health test, refer to the application note AN125, "MP5515 Capacitor Health Measurement Accuracy and Recommended Method."

#### **VCC Power Management**

The MP5515 internal circuits are powered by the VCC capacitor. VCC is supplied by VIN, VB, or  $V_{\text{STRG}}$  under different conditions (see Table 1).

**Table 1: VCC Power Sources**

| Operation Mode    | LDO_EN<br>Bit  | Power Sources                                                                                                             |

|-------------------|----------------|---------------------------------------------------------------------------------------------------------------------------|

| Boost<br>charge   | 0<br>(default) | VCC is supplied by the higher value of either VIN or VB.                                                                  |

| Buck<br>discharge |                | VCC is supplied by the higher value of either VIN                                                                         |

| Boost charge      | 1              | or VB when it is above 4.5V (typical value). If                                                                           |

| Buck<br>discharge |                | VCC is lower than 4.5V,<br>the LDO from V <sub>STRG</sub> to<br>VCC is enabled and<br>regulates the VCC at<br>about 4.5V. |

The LDO\_EN (0x1Bh bit[1]) is useful for ADC conversion, including the cap test when VIN and VB are low. It is recommended to enable the LDO\_EN bit before ADC operation when VIN and VB are low. Refer to the 10-Bit ADC section on page 23 for more details.

A capacitor no less than 1 $\mu$ F is required on VCC. When starting up from 3V or a lower VIN, VCC is low due to the VIN-to-VCC voltage drop. Any external current on VCC (i.e.: a PFI pull-up resistor) pulls VCC lower and makes the MP5515 difficult to start up. Typically, a 100k $\Omega$  pull-up resistor for PFI and INT is suggested, but these pins can also be pulled up to VB if the VB voltage is lower than 5V.

The MP5515 can start up from a 2.7V low input power at 25°C or a higher temperature. If the temperature is lower than 25°C, the UVLO rises slightly. One external Schottky diode from VIN to VCC is suggested if the IC needs to start up with 2.7V under low-temperature conditions. This diode is recommended even if VIN is 3V under -40°C.

#### **Enable Control (EN)**

The EN pin of the MP5515 works together with the EN bit to enable the internal circuit. The MP5515 is enabled after both the EN pin and EN bit are high. During application, the EN pin cannot be connected to a voltage higher than 6.5V. For resistor pull-up condition, an internal Zener diode clamps the voltage at the EN pin. The maximum pull-up current (assuming the worst case, 6V) for the internal Zener clamp should be less than 1mA. When pulled up to VIN and VB,  $100k\Omega$  pull-up resistors to both VIN and VB are recommended.

#### **SAS Function**

The MP5515 provides a forced backup mode for energy discharge. When SAS or the Force Buck Release bit is high, the ISOFET turns off, operates in buck release mode, and PFI drops low to indicate the power status. If VB drops to UVLO before SAS resets, the buck shuts down, and the VCC power continues working. The MP5515 works with a new start cycle when SAS resets. If VB is still higher than UVLO after SAS resets to 0, PFI is pulled high, and the ISOFET works as the VIN power recovery after VB triggers VB\_UVLO.

#### Input Power Failure Indicator (PFI)

If DET drops below 0.99 x  $V_{DET-REF}$ , the MP5515 pulls PFI low internally to indicate a power failure. Simultaneously, the MP5515 exits boost mode. If the DET voltage rises to 1.02 x  $V_{DET-REF}$ , PFI is set to high again (if pulled up by a resistor externally), but the MP5515 does not exit buck mode, even if PFI is high, until the  $V_{STRG}$  energy is discharged to UVLO or the IC resets.

#### **Bus Voltage Power Good Indicator (PGB)**

When the voltage on the FBB (VB feedback) drops below 0.9 x  $V_{FBB-REF}$ , the MP5515 pulls PGB low internally. When the FBB voltage is above 0.95 x  $V_{FBB-REF}$ , PGB goes high.

#### STRG Voltage Power Good Indicator (PGS)

The storage power good threshold can be programmed by the PGS Threshold bits. By default, the PGS falling threshold is 95% of the reference voltage. When the voltage on FBS ( $V_{\rm STRG}$  feedback) drops below 0.95 x  $V_{\rm FBS-REF}$ , the MP5515 pulls PGS low internally.

When the FBB voltage is above 0.97 x  $V_{\text{FBS-REF}}$ , PGS goes high.

### Input Over-Voltage Protection (OVP)

A resistor divider from the VIN power to OVP can set input over-voltage protection (OVP). Once the OVP pin voltage rises to 0.81V, the MP5515 is forced into buck backup mode. After the OVP pin voltage drops to 0.765V and the buck stops (VB triggers VB\_UVLO), the MP5515 restarts automatically as a new power-on cycle with a TPOR process. One Input Over-Voltage register bit records the OVP event and generates an interrupt signal on INT if it is unmasked.

#### 10-Bit ADC

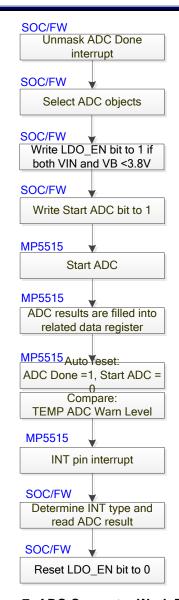

The MP5515 integrates a 10-bit A/D converter to measure the input voltage, input current, backup voltage, and TEMP pin temperature sensor voltage. The register Start ADC can enable A/D conversion. ADC Done is set if one ADC conversion completes. An interrupt request to the controller can be set if the ADC Done bit is set. Figure 7 shows the ADC setting work flow. Refer to the ADC Results register on page 32 for details on ADC converting results calculation.

When VIN is lower than 3.8V, set register 0x1Bh bit[1] to 1 by the host chip before enabling the ADC or capacitance test functions. Setting this bit enables the LDO from  $V_{STRG}$  to VCC, provides more margins for the internal ADC reference, and insures ADC accuracy. The LDO from  $V_{STRG}$  to VCC draws about 2mA of current from STRG. It is recommended to disable the LDO after ADC or the capacitance test completes. By default, the LDO\_EN bit is 0.

#### **Interrupt Control**

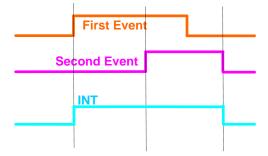

The MP5515 pulls INT high if any fault condition in the interrupt register occurs when the fault bits are not masked. This interrupt signal is asserted to inform the SOC that certain fault conditions have occurred. When there is an existing interrupt event, and a second interrupt event occurs before SOC resets INT where the INT voltage is still high, the MP5515 keeps INT high until SOC resets all interrupt event sources (see Figure 8).

Figure 7: ADC Converter Work Flow

Figure 8: Interrupt Sequence

After the fault event occurs, the MP5515 generates an interrupt and other actions (see Table 2).

#### Thermal Shutdown

Thermal shutdown is implemented to prevent the chip from running away thermally. When the silicon die temperature is higher than 120°C, the T<sub>J</sub> warn bit is set to 1 and sends an interrupt to SOC. Write 1 to the TJ Warn bit to reset the interrupt after T<sub>J</sub> drops below 100°C.

If the silicon die temperature is higher than  $150^{\circ}\text{C}$ , the MP5515 is forced into backup mode and discharges energy from  $V_{\text{STRG}}$  to VB. In this condition, the ISOFET is off and PFI is low. The buck is released until the energy is fully discharged. When the junction temperature is lower than  $125^{\circ}\text{C}$ , the MP5515 is re-powered from VIN and works as the VIN power recovery. There is an interrupt for  $150^{\circ}\text{C}$  overtemperature. It can be reset by writing 1 to the TJ Warn bit.

If the silicon die temperature rises to 165°C, the MP5515 turns off all circuits.

#### Register Default Value Program

The MP5515 has many control register bits, and all have a fixed default value after a power reset. After power-up, all bits can be programmed by writing the I<sup>2</sup>C. Registers 0x06h, 0x07h, 0x21h, and the device I<sup>2</sup>C address default value can be programmed, so providing different default values can match different system requirements after power-on.

**Table 2: Fault Event Response Table**

| Event                                                                    | Status Bit             | Status/INT Reset Condition | PFI          | INT           | MP5515 Power Action                                                                         |

|--------------------------------------------------------------------------|------------------------|----------------------------|--------------|---------------|---------------------------------------------------------------------------------------------|

| Input over-current                                                       | Input Over-<br>Current | POR, write 1 to the bit    | No<br>action | Yes<br>(high) | Limit input current. Enter buck if VB drops to FBB regulation.                              |

| Input power fail                                                         | N/A                    | N/A                        | Yes<br>(low) | No<br>action  | ISOFET off, IC switches to buck release mode.                                               |

| OVP pin over-voltage                                                     | Input Over-<br>Voltage | POR, write 1 to the bit    | Yes<br>(low) | Yes<br>(high) | ISOFET off, IC switches to buck release mode.                                               |

| VSTRG triggers PGS falling                                               | PGS Not Ok             | POR, write 1 to the bit    | No<br>action | Yes<br>(high) | No action.                                                                                  |

| TEMP pin warn TEMP Warn                                                  |                        | POR, write 1 to the bit    | No<br>action | Yes<br>(high) | No action.                                                                                  |

| Die temp high warning                                                    | IC T <sub>J</sub> Warn | POR, write 1 to the bit    | No<br>action | Yes<br>(high) | No action.                                                                                  |

| Die over-temp to forced buck  SAS disable supply  ADC complete  ADC Done |                        | POR, write 1 to the bit    | Yes<br>(low) | Yes<br>(high) | ISOFET is off, IC switches to buck release mode, then shuts down after power is discharged. |

|                                                                          |                        | POR, write 1 to the bit    | Yes<br>(low) | Yes<br>(high) | ISOFET off, IC switches to buck release mode.                                               |

|                                                                          |                        | POR, write 1 to the bit    | No<br>action | Yes<br>(high) | No action.                                                                                  |

| Cap test complete Cap Test Done                                          |                        | POR, write 1 to the bit    | No<br>action | Yes<br>(high) | Refer to cap test state diagram.                                                            |

It is suggested to use the default register value of registers 0x06h, 0x07h, 0x21h, and device I<sup>2</sup>C address for application. If different default values are needed for these registers, please contact MPS for a program solution.

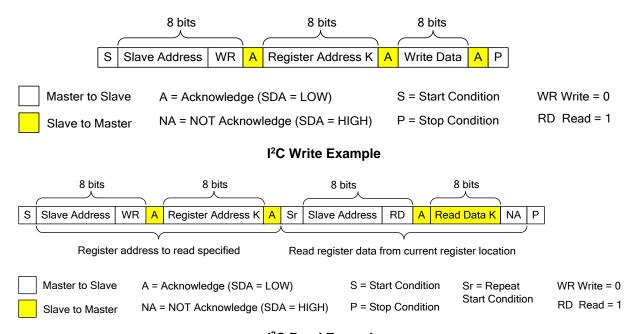

#### I<sup>2</sup>C Interface

The I<sup>2</sup>C is a two-wire, bidirectional, serial interface consisting of a data line (SDA) and a clock line (SCL). The lines are pulled to a bus voltage externally when they are idle. When connecting to the line, a master device generates the SCL signal and device address and arranges the communication sequence. The MP5515 interface is an I<sup>2</sup>C slave. The I<sup>2</sup>C interface adds flexibility to the SSD power system control by different register configurations.

The MP5515 7-bit device address is defined as 33h (011 0011). When the master sends an 8-bit address value, the 7-bit I<sup>2</sup>C address should be followed by a 0 or 1 to indicate a write or read operation, respectively.

#### I<sup>2</sup>C Data Validity

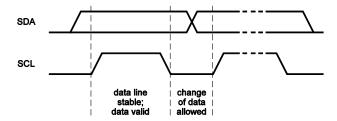

One clock pulse is generated for each data bit transferred. The data on the SDA line must be stable during the high period of the clock. A high or low state of the data line can change only when the clock signal on the SCL line is low as shown in Figure 9.

Figure 9: Bit Transfer on the I<sup>2</sup>C Bus

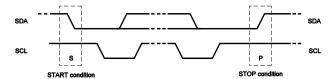

The start and stop are signaled by the master device, which signifies the beginning and the end of the I<sup>2</sup>C transfer. The start condition is defined as the SDA signal transitioning from high to low while the SCL is high. The stop condition is defined as the SDA signal transitioning from low to high while the SCL is high (see Figure 10).

Figure 10: Start and Stop Conditions

Start and stop conditions are always generated by the master. The bus is considered to be busy after the start condition. The bus is considered to be free again after a minimum of 4.7µs after the stop condition. The bus stays busy if a repeated start (Sr) is generated instead of a stop condition. The start (S) and repeated start (Sr) conditions are identical functionally.

#### I<sup>2</sup>C Transfer Data

Every byte put on the SDA line must be eight bits long. Each byte must be followed by an acknowledge bit. The acknowledge-related clock pulse is generated by the master. The transmitter releases the SDA line (high) during the acknowledge clock pulse. The receiver must pull down the SDA line during the acknowledge clock pulse so it remains stable low during the high period of this clock pulse.

Data transfers follow the format shown in Figure 11. After the start condition (S), a slave address is sent. This address is seven bits long followed by an eighth bit, which is a data direction bit (r/w). A zero (0) indicates a transmission (write), and a one (1) indicates a request for data (read). A data transfer is always terminated by a stop condition (P) generated by the master. However, if a master still wishes to communicate on the bus, it can generate a repeated start condition (Sr) and address another slave without first generating a stop condition.

Figure 11: Complete Data Transfer

The MP5515 includes a full I<sup>2</sup>C slave controller. The I<sup>2</sup>C slave fully complies with the I<sup>2</sup>C specification requirements and requires a start condition, a valid I<sup>2</sup>C address, a register address byte, and a data byte for a single data update. After receiving each byte, the MP5515 acknowledges by pulling the SDA line low

during the high period of a single clock pulse. A valid I<sup>2</sup>C address selects the MP5515. The MP5515 performs an update on the falling edge of the LSB byte.

Figure 12 shows an example of an I<sup>2</sup>C read and write command.

I<sup>2</sup>C Read Example Figure 12: I<sup>2</sup>C Read and Write

## **REGISTER DESCRIPTION**

## **Register Map**

| Addr  | Register                      | Туре | D7                          | D6                  | D5                 | D4                                | D3                                | D2                 | D1               | D0                     | Reset                |

|-------|-------------------------------|------|-----------------------------|---------------------|--------------------|-----------------------------------|-----------------------------------|--------------------|------------------|------------------------|----------------------|

| 0x00h | Vendor ID                     | r    | F                           | <u> </u><br>ab      | Majo               | r Rev                             | Mino                              | r Rev              | Vend             | dor ID                 | State<br>0000        |

| 0x01h | Sys<br>Control 1              | r/w  | -                           | -                   | -                  | -                                 | Start<br>Cap<br>Test              | Start<br>ADC       | -                | ENCH                   | 0000<br>0000<br>0001 |

| 0x02h | Interrupt1<br>Status          | r/w  | Cap<br>Test<br>Done         | ADC<br>Done         | -                  | Input<br>Over-<br>Current         | Input<br>Over-<br>Voltage         | PGS Not<br>Ok      | -                | TEMP<br>Warn           | 0000<br>0100         |

| 0x03h | Interrupt2<br>Status          | r/w  | -                           | SAS DIS             | ISOFET<br>Off      | IC TJ<br>Shut-<br>down            | IC TJ<br>Warn                     | -                  | -                | -                      | 0010<br>0000         |

| 0x04h | Interrupt1<br>Mask<br>Control | r/w  | Cap<br>Test<br>Done<br>Mask | ADC<br>Done<br>Mask | -                  | Input<br>Over-<br>Current<br>Mask | Input<br>Over-<br>Voltage<br>Mask | PGS Not<br>Ok Mask | -                | TEMP<br>Warn<br>Mask   | 0010<br>0100         |

| 0x05h | Interrupt2<br>Mask<br>Control | r/w  | -                           | SAS DIS<br>Mask     | ISOFET<br>Off Mask | IC TJ<br>Shut-<br>down<br>Mask    | IC TJ<br>Warn<br>Mask             | -                  | -                | -                      | 0010<br>0101         |

| 0x06h | Backup<br>Cap<br>Threshold    | r/w  | -                           | -                   | IC                 | СН                                |                                   | PGS Th             | reshold          |                        | 0011<br>1111         |

| 0x07h | TEMP<br>Warn<br>Threshold     | r/w  | -                           | -                   | -                  |                                   | Temp ADC Warn Level               |                    |                  |                        | 0001<br>1111         |

| 0x08h | -                             | -    | -                           | -                   | -                  | -                                 | -                                 | -                  | -                | -                      | 0001<br>1111         |