MP6532

The Future of Analog IC Technology

# DESCRIPTION

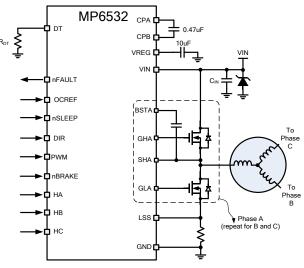

The MP6532 is a gate driver IC designed for brushless DC motor three-phase driver applications. It is capable of driving three half bridges consisting of six N-channel power MOSFETs up to 60V.

The MP6532 integrates a regulated charge pump to generate gate drive power, and uses a bootstrap capacitor to generate a supply voltage for the high-side MOSFET driver. An internal trickle-charge circuit maintains sufficient highside gate driver voltage even when an output is operated at 100% duty cycle

Internal protection features include programmable short-circuit protection, overcurrent protection, adjustable dead-time control, undervoltage lockout, and thermal shutdown.

The device integrates 120° commutation using three Hall sensor inputs. The PWM, DIR, and nBRAKE inputs are used to control motor speed, direction, and braking.

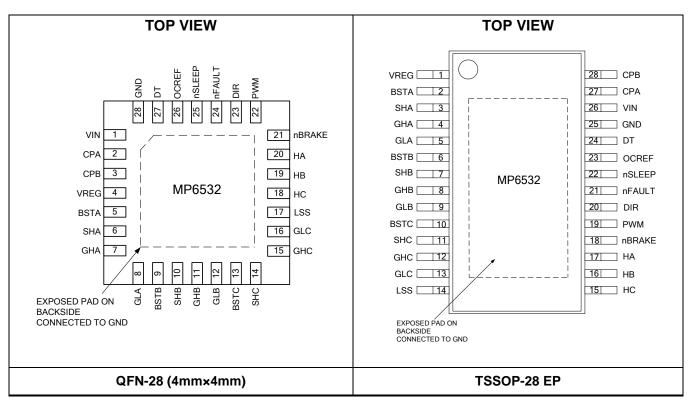

The MP6532 is available in 28-pin, 9.7mm × 6.4mm TSSOP and 4mm x 4mm QFN packages with an exposed thermal pad.

# FEATURES

- Wide 5V to 60V Input Voltage Range

- Built-in Hall Sensor Inputs 120° • and **Commutation Logic**

- Charge Pump Gate Drive Supply

- Bootstrap High-Side Driver with Trickle-Charge Circuit Supports 100% Duty Cycle Operation

- Low-Power Sleep Mode ٠

- **Programmable Short-Circuit Protection** •

- **Over-Current Protection** •

- Adjustable Dead-Time Control to Prevent • Shoot-Through

- Thermal Shutdown and UVLO Protection

- Fault Indication Output

- Thermally Enhanced Surface-Mount Package ٠

# APPLICATIONS

- Three-Phase Brushless DC Motors and Permanent Magnet Synchronous Motors

- Power Drills •

- Impact Drivers

- E-Bike

All MPS parts are lead-free, halogen-free and adhere to the RoHS directive. For MPS green status, please visit MPS website under Quality Assurance. "MPS" and "The Future of Analog IC Technology" are registered trademarks of Monolithic Power Systems, Inc.

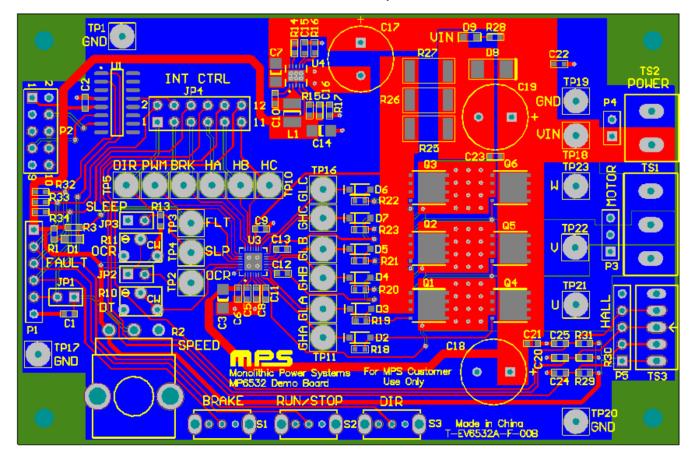

# **TYPICAL APPLICATION**

www.MonolithicPower.com MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited. © 2018 MPS. All Rights Reserved.

# Part NumberPackageTop MarkingMP6532GR\*QFN-28 (4mm x 4mm)See BelowMP6532GF\*\*TSSOP-28 EPSee Below

#### **ORDERING INFORMATION**

\* For Tape & Reel, add suffix -Z (e.g. MP6532GR-Z)

\*\* For Tape & Reel, add suffix -Z (e.g. MP6532GF-Z)

# **TOP MARKING (MP6532GR)**

<u>MPSYWW</u>

MP6532

LLLLLL

MPS: MPS prefix: Y: year code; WW: week code: MP6532: part number; LLLLLL: lot number;

# **TOP MARKING (MP6532GF)**

M<u>PSYYWW</u> MP6532 LLLLLLLL

MPS: MPS prefix: YY: year code; WW: week code: MP6532: part number; LLLLLLLL: lot number;

# PACKAGE REFERENCE

# ABSOLUTE MAXIMUM RATINGS (1)

| Input Voltage V <sub>IN</sub><br>CPA<br>CPB<br>VREG<br>BSTA/B/C<br>GHA/B/C  | 0.3V to 60V<br>0.3V to 12.5V<br>0.3V to 13V<br>0.3V to 70V |

|-----------------------------------------------------------------------------|------------------------------------------------------------|

| GHA/B/C (Transient, 2µS)<br>SHA/B/C                                         | 8V to 70V<br>0.3V to 65V                                   |

| SHA/B/C (Transient, 2µS)<br>GLA/B/C<br>LSS                                  | 0.3V to 13V                                                |

| All Other Pins to AGND<br>Continuous Power Dissipation                      | (T <sub>A</sub> = +25°C) <sup>(2)</sup>                    |

| QFN-28 (4mm x 4mm)<br>TSSOP-28 EP<br>Storage Temperature                    | 3.9W                                                       |

| Junction Temperature<br>Lead Temperature (Solder)<br>ESD (Human Body Model) | +150°C<br>+260°C                                           |

# Recommended Operating Conditions <sup>(3)</sup>

| , ,                                     |            |

|-----------------------------------------|------------|

| Input Voltage V <sub>IN</sub>           | 5V to 60V  |

| OCREF Voltage Voc                       |            |

| Operating Junct. Temp (T <sub>J</sub> ) |            |

| Thormal Posistance (4)                  | <b>Ο Ο</b> |

| inerinal Resistance | σյΑ | ₽JC |       |

|---------------------|-----|-----|-------|

| QFN-28 (4mm×4mm)    | 42  | 9   | .°C/W |

| TSSOP-28 EP         | 32  | 6   | .°C/W |

#### Notes:

- 2) The maximum allowable power dissipation is a function of the maximum junction temperature T<sub>J</sub> (MAX), the junction-to-ambient thermal resistance θ<sub>JA</sub>, and the ambient temperature T<sub>A</sub>. The maximum allowable continuous power dissipation at any ambient temperature is calculated by P<sub>D</sub> (MAX) = (T<sub>J</sub> (MAX)-T<sub>A</sub>)/θ<sub>JA</sub>. Exceeding the maximum allowable power dissipation will cause excessive die temperature, and the regulator will go into thermal shutdown. Internal thermal shutdown circuitry protects the device from permanent damage.

- 3) The device is not guaranteed to function outside of its operating conditions.

- 4) Measured on JESD51-7, 4-layer PCB.

www.MonolithicPower.com MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited. © 2018 MPS. All Rights Reserved.

<sup>1)</sup> Exceeding these ratings may damage the device.

# **ELECTRICAL CHARACTERISTICS**

$V_{IN} = 24V$ ,  $T_A = 25^{\circ}C$ , unless otherwise noted.

| Parameter                                      | Symbol                | Condition                                   | Min  | Тур  | Max  | Units |

|------------------------------------------------|-----------------------|---------------------------------------------|------|------|------|-------|

| Power Supply                                   |                       |                                             |      |      |      |       |

| Input Supply Voltage                           | V <sub>IN</sub>       |                                             | 5    |      | 60   | V     |

| Quiescent Current                              | Ι <sub>Q</sub>        | nSLEEP=1, gate not switching                |      | 0.95 | 2    | mA    |

| Quiescent Current                              | I <sub>SLEEP</sub>    | nSLEEP=0                                    |      |      | 1    | μA    |

| Control Logic                                  | _                     | -                                           |      | -    |      |       |

| Input Logic 'Low' Threshold                    | V <sub>IL</sub>       |                                             |      |      | 0.8  | V     |

| Input Logic 'High' Threshold                   | V <sub>IH</sub>       |                                             | 2    |      |      | V     |

| Logic Input Current                            | I <sub>IN(H)</sub>    | V <sub>IH</sub> =5V                         | -20  |      | 20   | μA    |

|                                                | IN(L)                 | V <sub>IL</sub> =0.8V                       | -20  |      | 20   | μA    |

| nSLEEP Pull Down Current                       | I <sub>SLEEP-PD</sub> |                                             |      | 1    |      | μA    |

| Internal Pull Down<br>Resistance               | R <sub>PD</sub>       | All logic inputs except nSLEEP              |      | 880  |      | kΩ    |

| nFAULT Output (Open-Drain                      | Output)               | -                                           |      | -    |      |       |

| Output Low Voltage                             | V <sub>OL</sub>       | I <sub>O</sub> =5mA                         |      |      | 0.5  | V     |

| Output High Leakage Current I <sub>OH</sub>    |                       | V <sub>0</sub> =3.3V                        |      |      | 1    | μA    |

| Protection Circuits                            | _                     | -                                           |      | -    |      |       |

| UVLO Rising Threshold                          | V <sub>IN RISE</sub>  |                                             | 3.3  | 3.9  | 4.5  | V     |

| UVLO Hysteresis                                | V <sub>IN HYS</sub>   |                                             |      | 200  |      | mV    |

| VREG Rising Threshold                          | V <sub>REG RISE</sub> |                                             | 6.8  | 7.6  | 8.4  | V     |

| VREG Hysteresis                                | V <sub>REG_HYS</sub>  |                                             |      | 0.54 | 1    | V     |

| VREG Startup Delay                             | t <sub>REG</sub>      |                                             |      | 700  |      | μs    |

| Short-Circuit Threshold                        | V <sub>SC</sub>       | V <sub>OC</sub> =1V, T <sub>J</sub> =25°C   | 0.8  | 1    | 1.2  | V     |

| Accuracy (MOSFET V <sub>DS</sub> )             | V SC                  | V <sub>OC</sub> =2.4V, T <sub>J</sub> =25°C | 2.18 | 2.4  | 2.62 | V     |

| OCP Deglitch Time                              | t <sub>oc</sub>       |                                             |      | 3    |      | μs    |

| SLEEP Wakeup Time                              | t <sub>SLEEP</sub>    |                                             |      | 1    |      | ms    |

| LSS Current Limit Threshold                    | V <sub>LSS</sub>      |                                             | 0.4  | 0.5  | 0.6  | V     |

| LSS Current Limit Fixed Off<br>Time            | t <sub>OFF</sub>      |                                             | 53   | 66   | 80   | us    |

| LSS Current Limit High side<br>Minimum On Time | t <sub>ON</sub>       |                                             |      | 1    |      | us    |

| Thermal Shutdown                               | T <sub>TSD</sub>      |                                             |      | 150  |      | °C    |

# **ELECTRICAL CHARACTERISTICS** (continued) $V_{IN} = 24V$ , $T_A = 25^{\circ}C$ , unless otherwise noted.

| Parameter                             | Symbol                  | Condition                  | Min           | Тур  | Max  | Units |  |

|---------------------------------------|-------------------------|----------------------------|---------------|------|------|-------|--|

| Gate Drive                            |                         |                            |               |      |      |       |  |

| Bootstrap Diode Forward               | V                       | I <sub>D</sub> =10mA       |               |      | 0.9  | V     |  |

| Voltage                               | V <sub>FBOOT</sub>      | I <sub>D</sub> =100mA      |               |      | 1.3  | V     |  |

|                                       |                         | V <sub>IN</sub> =5.5V-60V, | 10            | 11.5 | 12.8 |       |  |

| VREG Output Voltage                   | $V_{REG}$               | T <sub>J</sub> =25°C       | 10            |      |      |       |  |

|                                       |                         | V <sub>IN</sub> =5V        | $2xV_{IN}$ -1 |      |      | V     |  |

| Maximum source current                | l <sub>oso</sub> (5)    |                            |               | 0.8  |      | А     |  |

| Maximum sink current                  | (5)<br>I <sub>OSI</sub> |                            |               | 1    |      | А     |  |

| Gate Drive Pull Up<br>Resistance      | R <sub>UP</sub>         | V <sub>DS</sub> =1V        |               | 8    |      | Ω     |  |

| HS Gate Drive Pull Down<br>Resistance | R <sub>HS-DN</sub>      | V <sub>DS</sub> =1V        | 1.2           |      | 4.3  | Ω     |  |

| LS Gate Drive Pull Down<br>Resistance | $R_{LS\text{-}DN}$      | V <sub>DS</sub> =1V        | 1             |      | 5    | Ω     |  |

| LS Passive Pull Down<br>Resistance    | $R_{LS-PDN}$            |                            |               | 590  |      | kΩ    |  |

| LS Automatic Turn On Time             | t <sub>LS</sub>         | At each commutation time   |               | 1.8  |      | μs    |  |

| Charge Pump Frequency                 | f <sub>CP</sub>         |                            |               | 110  |      | kHz   |  |

| · · · ·                               |                         | DT Open                    |               | 6    |      | μs    |  |

| Dead Time                             | t <sub>DEAD</sub>       | $R_{DT}=200k\Omega$        |               | 0.74 |      | μs    |  |

|                                       |                         | DT tied to GND             |               | 30   |      | ns    |  |

NOTE:

5) Guaranteed by design - not tested in production

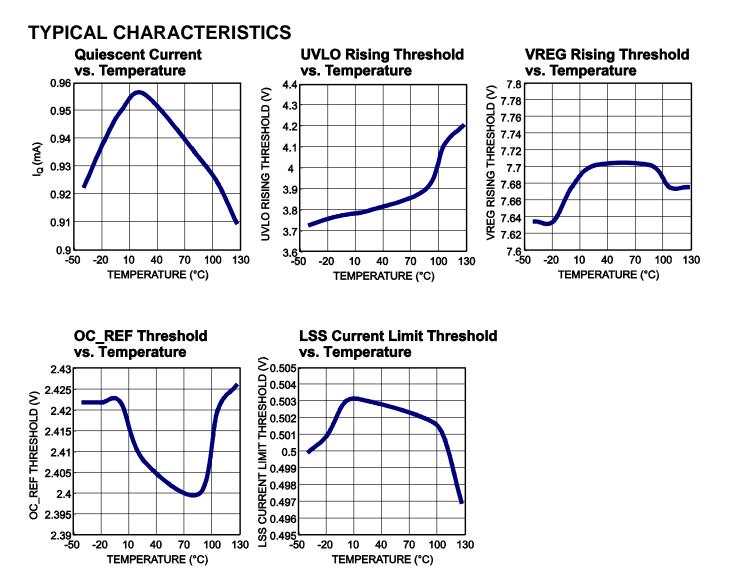

# **TYPICAL PERFORMANCE CHARACTERISTICS**

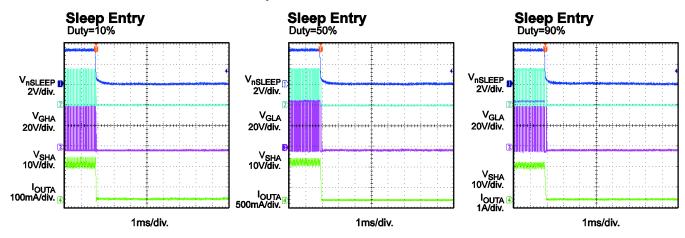

$V_{IN}$  = 24V, OCREF = 0.5V,  $R_{DT}$  = 200k, DIR = H, HA = HC = H, HB = L,  $f_{PWM}$  = 20kHz,  $T_A$  = 25°C, Resistor+Inductor Load: 50hm+1mH/phase with star connection, unless otherwise noted.

www.MonolithicPower.com MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited. © 2018 MPS. All Rights Reserved.

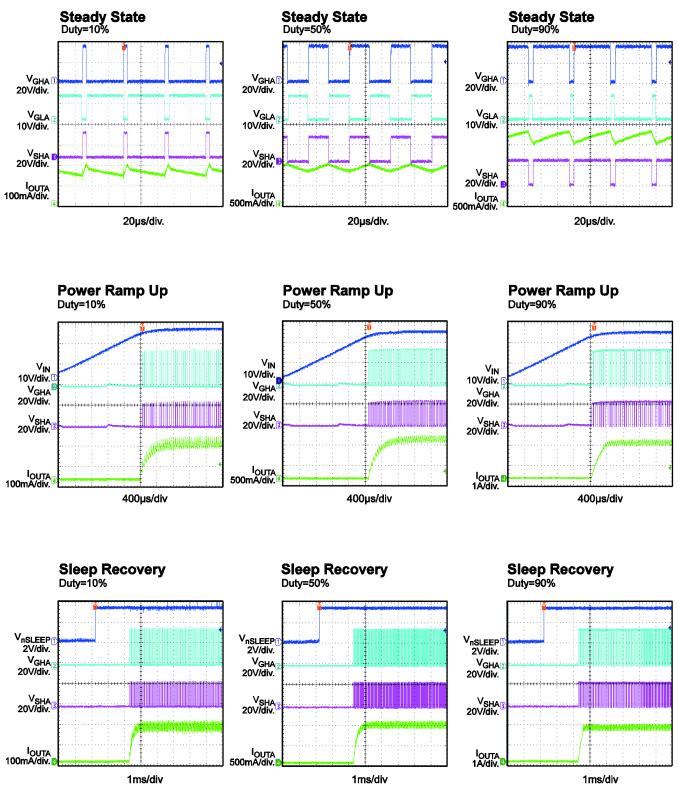

# **TYPICAL PERFORMANCE CHARACTERISTICS** (continued)

$V_{IN}$  = 24V, OCREF = 0.5V,  $R_{DT}$  = 200k, DIR = H, HA = HC = H, HB = L,  $f_{PWM}$  = 20kHz,  $T_A$  = 25°C, Resistor+Inductor Load: 50hm+1mH/phase with star connection, unless otherwise noted.

# **PIN FUNCTIONS**

| QFN<br>Pin # | TSSOP<br>Pin # | Name   | Description                                                                                                                                                |

|--------------|----------------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1            | 26             | VIN    | <b>Input supply voltage.</b> Bypass to ground with a ceramic capacitor. Additional bulk capacitance may be required. See Applications Information section. |

| 2            | 27             | CPA    | Charge pump capacitor. Connect a ceramic capacitor between these pins.                                                                                     |

| 3            | 28             | CPB    | See Applications Information section.                                                                                                                      |

| 4            | 1              | VREG   | Gate drive supply output. Connect a ceramic capacitor to ground.<br>See Applications Information section.                                                  |

| 5            | 2              | BSTA   | <b>Bootstrap phase A.</b> Connect a ceramic capacitor to SHA.<br>See Applications Information section.                                                     |

| 6            | 3              | SHA    | High-side source connection phase A.                                                                                                                       |

| 7            | 4              | GHA    | High-side gate drive phase A.                                                                                                                              |

| 8            | 5              | GLA    | Low-side gate drive phase A.                                                                                                                               |

| 9            | 6              | BSTB   | <b>Bootstrap phase B.</b> Connect a ceramic capacitor to SHB.<br>See Applications Information section.                                                     |

| 10           | 7              | SHB    | High-side source connection phase B.                                                                                                                       |

| 11           | 8              | GHB    | High-side gate drive phase B.                                                                                                                              |

| 12           | 9              | GLB    | Low-side gate drive phase B.                                                                                                                               |

| 13           | 10             | BSTC   | <b>Bootstrap phase C.</b> Connect a ceramic capacitor to SHC.<br>See Applications Information section.                                                     |

| 14           | 11             | SHC    | High-side source connection phase C.                                                                                                                       |

| 15           | 12             | GHC    | High-side gate drive phase C.                                                                                                                              |

| 16           | 13             | GLC    | Low-side gate drive phase C.                                                                                                                               |

| 17           | 14             | LSS    | Low-side source connection.                                                                                                                                |

| 18           | 15             | HC     | Hall-sensor input, phase C. Internal pulldown.                                                                                                             |

| 19           | 16             | HB     | Hall-sensor input, phase B. Internal pulldown.                                                                                                             |

| 20           | 17             | HA     | Hall-sensor input, phase A. Internal pulldown.                                                                                                             |

| 21           | 18             | nBRAKE | <b>Brake input.</b> Active low input turns on all low-side MOFSFETs to brake motor; high for normal operation. Internal pulldown.                          |

| 22           | 19             | PWM    | <b>External PWM input.</b> When active high, the phase selected by the commutation logic is driven high; when low, the phase is low. Internal pulldown.    |

| 23           | 20             | DIR    | <b>Direction input.</b> High or low sets the motor rotation direction. Refer to commutation table for details.                                             |

| 24           | 21             | nFAULT | Fault indication. Open-drain output. nFAULT is logic low when in a fault condition.                                                                        |

| 25           | 22             | nSLEEP | <b>Sleep mode input.</b> Logic low to enter low-power sleep mode; high to enable. Internal pulldown.                                                       |

| 26           | 23             | OCREF  | Over-current protection reference voltage input.                                                                                                           |

| 27           | 24             | DT     | <b>Dead time setting.</b> Connect a resistor to ground to set the dead time.<br>See Applications Information section.                                      |

| 28           | 25             | GND    | Ground.                                                                                                                                                    |

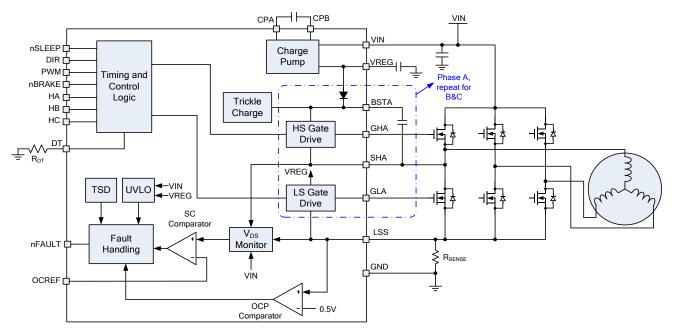

# **BLOCK DIAGRAM**

# OPERATION

The MP6532 is a three-phase BLDC motor predriver with built-in commutation logic that drives three external N-channel MOSFET half bridges, with 0.8A source and 1A sink current capability. It operates over a wide input voltage range of 5V to 60V, generating a boosted gate drive voltage when the input supply is below 12V. The MP6532 features a low-power sleep mode, which disables the device and draws a very low supply current.

The MP6532 provides several flexible functions, such as adjustable dead-time control and overcurrent protection, which allow the device to cover a wide range of applications.

#### **Power-Up Sequence**

The power-up sequence is initiated by the application of voltage to VIN pin. To initiate power-up, VIN must be above the undervoltage lockout threshold  $V_{UVLO}$ .

After power-up begins, the VREG supply starts operating. VREG must rise above  $V_{REG_RISE}$  before the device becomes functional.

The power-up process takes between 1mS and 2mS, after which the MP6532 will respond to logic inputs and drive the outputs.

#### **Gate Drive Power Supplies**

Gate drive voltages are generated from the input power, VIN. A regulated charge pump doubler circuit supplies a voltage of approximately 11.5V at the VREG pin. This voltage is used for the low-side gate drive supply. The charge pump requires external capacitors between the CPA and CPB pins, and from VREG to ground.

The high side gate drive is generated by a combination of a bootstrap capacitor and an internal "trickle" charge pump. Bootstrap capacitors are charged to the VREG voltage when the low side MOSFET is turned on. This charge is then used to drive the high side MOSFET gate when it is turned on.

To keep the bootstrap capacitors charged and allow operation at 100% duty cycle, an internal "trickle" charge pump supplies a small current (about  $5\mu$ A) to overcome leakages that would discharge the bootstrap capacitors.

Refer to the applications information section for details on the selection of external components.

#### Sleep Mode (nSLEEP Input)

Driving nSLEEP low will put the device into a low-power sleep state. In this state, all the internal circuits are disabled. All inputs are ignored when nSLEEP is active low. nSLEEP has an interval pulldown, so it must be driven high for the device to operate.

When exiting sleep mode, the power-up sequence described above is repeated.

#### Input Logic

The PWM input is typically connected to a PWM signal that controls the speed of the motor. DIR controls the direction of rotation. nBRAKE, when active low, turns on all low-side MOSFETs to stop the motor. This logic is shown in Table 1 below.

Table 1: Input Logic Truth Table

| PWM | nBRAKE | Operation                       |

|-----|--------|---------------------------------|

| Х   | L      | Brake – all low-side<br>FETs on |

| L   | н      | Selected phase driven<br>low    |

| н   | н      | Selected phase driven<br>high   |

#### **Commutation Logic and Hall Inputs**

The commutation logic is driven by three Hallsensor inputs. These inputs are connected to sensors in the motor that are spaced 120° from each other. Refer to Table 2 for the commutation logic.

At each Hall input transition, the phase that will be driven (high or low, depending on the PWM input pin) is first driven low for a short period of time ( $t_{LS}$ ). This ensures that the bootstrap capacitor is charged at the beginning of each commutation cycle. Because of this, even if the PWM input is held high, each phase will pulse low before being driven high.

|       | Logic                                                                          | : Inputs |     | Driver Outputs |      |      |     |     | Motor Terminals |     |     |     |

|-------|--------------------------------------------------------------------------------|----------|-----|----------------|------|------|-----|-----|-----------------|-----|-----|-----|

| HA    | HB                                                                             | HC       | DIR | GLA            | GLB  | GLC  | GHA | GHB | GHC             | SHA | SHB | SHC |

| 1     | 0                                                                              | 1        | 1   | /PWM           | 0    | 1    | PWM | 0   | 0               | Н   | Z   | L   |

| 1     | 0                                                                              | 0        | 1   | 0              | /PWM | 1    | 0   | PWM | 0               | Ζ   | Н   | L   |

| 1     | 1                                                                              | 0        | 1   | 1              | /PWM | 0    | 0   | PWM | 0               | L   | Н   | Z   |

| 0     | 1                                                                              | 0        | 1   | 1              | 0    | /PWM | 0   | 0   | PWM             | L   | Z   | Н   |

| 0     | 1                                                                              | 1        | 1   | 0              | 1    | /PWM | 0   | 0   | PWM             | Ζ   | L   | Н   |

| 0     | 0                                                                              | 1        | 1   | /PWM           | 1    | 0    | PWM | 0   | 0               | Н   | L   | Z   |

| 1     | 0                                                                              | 1        | 0   | 1              | 0    | /PWM | 0   | 0   | PWM             | L   | Z   | Н   |

| 1     | 0                                                                              | 0        | 0   | 0              | 1    | /PWM | 0   | 0   | PWM             | Z   | L   | Н   |

| 1     | 1                                                                              | 0        | 0   | /PWM           | 1    | 0    | PWM | 0   | 0               | Н   | L   | Z   |

| 0     | 1                                                                              | 0        | 0   | /PWM           | 0    | 1    | PWM | 0   | 0               | Н   | Z   | L   |

| 0     | 1                                                                              | 1        | 0   | 0              | /PWM | 1    | 0   | PWM | 0               | Z   | Н   | L   |

| 0     | 0                                                                              | 1        | 0   | 1              | /PWM | 0    | 0   | PWM | 0               | L   | Н   | Z   |

| Notor | Note: If pPPAKE_0, the broking function would be active, all low side actes on |          |     |                |      |      |     |     |                 |     |     |     |

#### Table 2. Commutation Table (nBRAKE=1)

Note: If nBRAKE=0, the braking function would be active, all low-side gates on.

#### nFAULT

The nFAULT output pin reports to the system when a fault condition (such as overcurrent or overtemperature) is detected. nFAULT is an open-drain output, and it is driven low when a fault condition occurs. If the fault condition is released, nFAULT is pulled high by an external pullup resistor.

#### Short Circuit Protection (V<sub>DS</sub> Sensing)

To protect the power stage from damage due to high currents, a VDS sensing circuitry is implemented in the MP6532. The voltage drop across each MOSFET is sensed. (This voltage is proportional to the R<sub>DS-ON</sub> of the MOSFET and the I<sub>DS</sub> current passing through it). If this voltage exceeds the voltage supplied to the OCREF terminal, a short circuit is recognized.

In the event of a short circuit, the MP6532 disables all of the gate drive outputs. nFAULT is driven active low. The device will stay latched off until it is reset by nSLEEP or VIN UVLO.

Short circuit protection can be disabled by connection a  $100k\Omega$  resistor from VREG to the OCREF pin.

#### **Over-current Protection (OCP)**

The MP6532 can implement output overcurrent protection (OCP) by monitoring the current through a low-side shunt resistor connected to MOSFETs. the low-side This resistor is connected to the LSS input pin and the low-side MOSFET source terminals. If the OCP function is not desired, the LSS pin and MOSFET source

terminals should all be connected directly to ground.

If the LSS voltage (the voltage across the shunt resistor) exceeds the LSS OCP threshold voltage V<sub>LSS-OCP</sub>, the high side will turn off and the corresponding low side turns on for a fixed off time  $(t_{OFF})$ . After the fixed off time, the high side will turn back on and the cycle repeats until LSS no longer exceeds the current limit threshold.

The OCP current limit level is selected by the value of the current sense resistor at LSS pin. Refer to the applications information section for more information.

OCP can be used to limit the stall current of a BLDC motor.

OCP protection can be disabled by connection a  $100k\Omega$  resistor from VREG to the OCREF pin.

#### Short-circuit and OCP Deglitch Time

There is often a current spike during switching transitions, due to body diode reverse-recovery current or the distributed capacitance of the load. This current spike requires filtering to prevent it from erroneously triggering OCP. An internal fixed deglitch time  $(t_{OC})$  blanks the output of the VDS monitor when the outputs are switched.

#### **Dead Time Adjustment**

To prevent shoot-through in any phase of the bridge, it is necessary to have a dead time (t<sub>DEAD</sub>) between a high- or low-side turn-off and the next complementary turn-on event. The dead time for all three phases is set by a single dead-time

12

resistor  $(R_{DT})$  between DT and ground with Equation (1):

$$t_{\text{DEAD}}(nS) = 3.7^* R(k\Omega)$$

(1)

If DT is tied directly to ground, an internal minimum dead time (30ns) will be applied. Leaving DT open generates approximately a 6µs dead time.

#### **UVLO Protection**

If at any time the voltage on VIN falls below the undervoltage lockout threshold  $V_{IN\_RISE}$ , all circuitry in the device is disabled and the internal logic will be reset.

Operation will resume with the power-up sequence when VIN rises above the UVLO thresholds.

After power-up, if the voltage on VREG drops below the  $V_{REG_{RISE}}$  threshold, the MP6530 will enter a latched fault state and disable all functions. The nFAULT pin will be driven active low. The device will stay latched off until it is reset by nSLEEP or VIN UVLO.

#### **Thermal Shutdown**

If the die temperature exceeds safe limits, the MP6532 will enter a latched fault state and disable all functions. The device will stay latched off until it is reset by nSLEEP or UVLO.

# **APPLICATIONS INFORMATION**

#### VIN Input Voltage

The VIN pin supplies all power to the device. It must be properly bypassed with a capacitor to ground – see below for specific recommendations.

The normal operating range of VIN is between 5V and 60V.

VIN should never be allowed to exceed the absolute maximum ratings, even in a short term transient condition, or damage to the device may result. In some cases – especially where mechanical energy can turn a motor into a generator – it may be necessary to use some form of overvoltage protection, such as a TVS diode, between VIN and ground.

#### **Component Selection**

#### **MOSFET** selection

Correctly selecting the power MOSFETs used to drive a motor is crucial to designing a successful motor drive.

The first requirement is that the MOSFET must have a VDS breakdown voltage that is higher than the supply voltage. It is recommended that considerable margin - 10-15 volts - be added to prevent MOSFET damage from transient voltages that can be caused by parasitic inductances in the PCB layout and wiring. For example, for 24V power supply applications, MOSFETs having a breakdown voltage of 40V-60V minimum are recommended. More margin is desirable in high current applications, as the transients caused by parasitic inductances may be larger. Also, there are conditions like regenerative braking that can inject current back into the power supply; care must be taken that this does not cause an increase in the power supply voltage large enough to damage components.

The MOSFETs must be able to safely pass the current needed to run the motor. The highest current condition, which is normally when the motor is first started or stalled, needs to be supported. This is typically called the "stall current" of the motor.

Related to the current capability of the MOSFET is the rds(on). This is the resistance of the MOSFET when it is in the fully "turned on" state. The MOSFET will dissipate power proportional to the rds(on) and the motor current:  $P=I^2R$ . The rds(on) needs to be selected so that for the desired motor current, the heat generated in this power can be safely dissipated. In some cases, require special PCB this may design considerations and/or external heatsinks to be used for the MOSFETs.

Some consideration should be made for the safe operating area (SOA) of the MOSFETs in fault conditions, such as a short circuit. The IC will act quickly in the event of a short, but there is still a very short time (on the order of  $3\mu$ S) where large currents can flow in the MOSFETs while the protection circuits recognize the fault and disable the outputs.

#### **External Capacitor Selection**

The MP6532 has a unique feature in that it can provide a gate drive voltage (VREG) of 10-12V even if the input supply voltage drops as low as 5V. This gate drive voltage is generated by a charge pump inside the part, which uses external capacitors.

The charge pump flying capacitor,  $C_{CP}$ , should have a capacitance of 470nF. It needs to be rated to withstand the maximum VIN power supply voltage. An X7R or X5R ceramic capacitor is recommended. With a 470nF capacitor, VREG can output approximately 10mA when VIN is 5V. If operation below 10V is not needed, a 220nF capacitor can be used

To provide the large peak currents needed to turn on the HS MOSFET, bootstrap capacitors are used. These capacitors are charged when the output is driven low, then the charge in the bootstrap capacitor is used to turn on the HS MOSFET when the output is driven high. (Note that an internal charge pump will keep the bootstrap capacitor changed when the output is held high for an extended period).

The bootstrap capacitors are selected depending on the MOSFET total gate charge. When the HS MOSFET is turned on, the charge stored in the

bootstrap capacitor is transferred to the HS MOSFET gate. As a simplified approximation, the minimum bootstrap capacitance can be estimated as  $C_{BOOT} > 8^*Q_G$ , where  $Q_G$  is the total gate charge of the MOSFET in nC, and  $C_{BOOT}$  is in nF. The bootstrap capacitors should not exceed 1µF, or they may cause improper operation at start-up.

For most applications, bootstrap capacitors between  $0.1\mu$ F and  $1\mu$ F, X5R or X7R ceramic, rated for 25V minimum, are recommended.

The VREG pin requires a bypass capacitor to ground of  $10\mu$ F. This should be an X7R or X5R ceramic capacitor rated for 16V minimum.

VIN requires a bypass capacitor to ground, placed as close as possible to the device. At a minimum, a  $0.1\mu$ F X5R or X7R ceramic capacitor, rated for the VIN voltage, is recommended.

Depending on the power supply impedance and the distance between the MOSFETs and the power supply, additional bulk capacitance is usually needed. Between  $47\mu$ F and  $470\mu$ F of low ESR electrolytic capacitors are typically used.

#### Dead Time Resistor Selection

During the transition between driving an output low and high, there is a short period when neither the HS nor LS MOSFET is turned on. This period, called "dead time", is needed to prevent any overlap in conduction between HS and LS MOSFETs, which would effectively provide a short-circuit directly between the power supply and ground. This condition, referred to as "shootthrough", causes large transient currents, and can destroy the MOSFETs.

Since motors are inductive by nature, once current is flowing in the motor, it cannot stop immediately, even if the MOSFETs are turned off. This "recirculation current" continues to flow in the original direction until the magnetic field has decayed.

When the MOSFETs are turned off, this current will flow through the "body diode" which is inherent in the MOSFET device.

MOSFET body diodes have a much higher voltage drop than the MOSFET has during conduction, so there more power dissipated in body diode conduction than during the on time.

Because of this, it is desirable to minimize the dead time. However, the dead time must be made large enough to guarantee under all conditions that the HS and LS MOSFETs are never turned on at the same time.

Dead time can be set over a large range, by selecting the value of the external resistor that is connected to the DT pin. Usually, a good starting point is a dead time of about  $1\mu$ S, which requires a 200k resistor on the DT pin. If faster switching and/or a high PWM frequency (over ~30kHz) is used, shorter dead time may be desirable; if switching is slowed using external gate resistors, longer dead time may be needed.

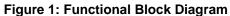

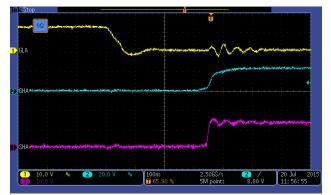

The waveform below shows about a 300nS dead time between the LS gate turn-off and the HS gate turn-on.

#### LSS Resistor Selection

If the voltage applied to the LSS pin ever exceeds 500mV, an overcurrent event will be recognized. The external sense resistor is sized to provide less than 500mV drop at the maximum expected motor current. For example, if a 50 m $\Omega$ resistor is used, a current of 10 amps would cause a 500mV drop, and activate the overcurrent protection.

If this function is not needed, connect LSS directly to ground.

#### **OCREF** Voltage Selection

An internal comparator compares the voltage drop across each MOSFET with a voltage that is externally provided on the OCREF input pin. This voltage is normally provided by an external resistor divider from a convenient power supply. If the drop across any MOSFET ever exceeds

the voltage on the OCREF pin, a short-circuit event is recognized.

If this function is not needed, connect OCREF to VREG through a 100k resistor.

#### **Gate Drive Considerations**

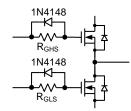

The gate characteristics of the selected MOSFETs will affect how fast they will be switched and off. The gate drive outputs of the device can be connected directly to the gates of the power MOSFETs, which results in the fastest possible turn-on and turn-off times. However, it may be advantageous to add external components (resistors and/or diodes) to modify the MOSFET turn-on and turn-off characteristics.

Adding external series resistance – typically between 10 and 100 ohms – will limit the current that charges and discharges the gate of the MOSFET, which will slow down the turn-on and turn-off times. Sometimes this is desirable to control EMI and noise. Slowing the transition down too much, however, results in large power dissipation in the MOSFET during switching.

In some cases, it is desirable to have a slow turnon, but a fast turn-off. This can be implemented by using a series resistor in parallel with a diode. At turn-on, the resistor limits the current flow into the gate; at turn-off, the gate is discharged quickly through the diode.

This waveform below shows the gates of the LS and HS MOSFETs, and the phase node (output) with no series resistance. You can see that the gates transition quickly. The resulting rise time on the phase node is quite fast. Note the scale of 100nS/div.

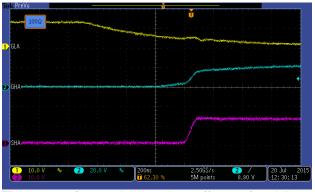

This waveform shows the effect of adding a  $100\Omega$  series resistor between the GLA and GLH pins and the MOSFET gates. Rise time on the phase node has been slowed significantly. The scale here is 200nS/div.

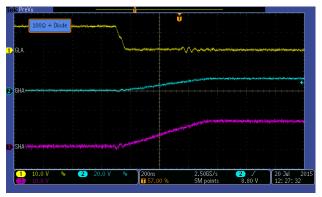

This waveform shows the effect of adding a 1N4148 diode in parallel with the  $100\Omega$  resistors (with the cathode connected to the IC). You can see that the fall time of the LS gate is quite fast compared to the HS gate rise time. The phase node moves even slower, because of a longer period of time between when the LS FET is turned off, and the HS FET is turned on.

#### **PCB** Layout

Proper PCB layout is critical to the performance of MOSFET gate drivers. In particular, the connection between the HS source and LS drain needs to be as direct as possible, to avoid negative undershoot on the phase node due to parasitic inductances. The pre-driver is designed to accommodate negative undershoot, but if it is excessive, unpredictable operation or damage to the IC can result.

An example PCB layout is shown below. It uses surface mount N-channel MOSFETs, which allows very short connection between the HS and LS MOSFETs. You can also see the use of wide copper areas for all of the high current paths.

The low-side sense resistor is composed of three resistors in parallel (R25, R26, and R27), and is connected to the input supply and LS MOSFET source terminals by wide copper areas.

Note the location of the charge pump and supply bypass capacitors, very close to the IC. The grounded side of these capacitors is connected to a ground plane, which is connected to the device ground pin and exposed pad. The highcurrent ground path between the input supply, input bulk capacitor C19, and MOSFETs is kept away from this area.

2.55

# **PACKAGE INFORMATION**

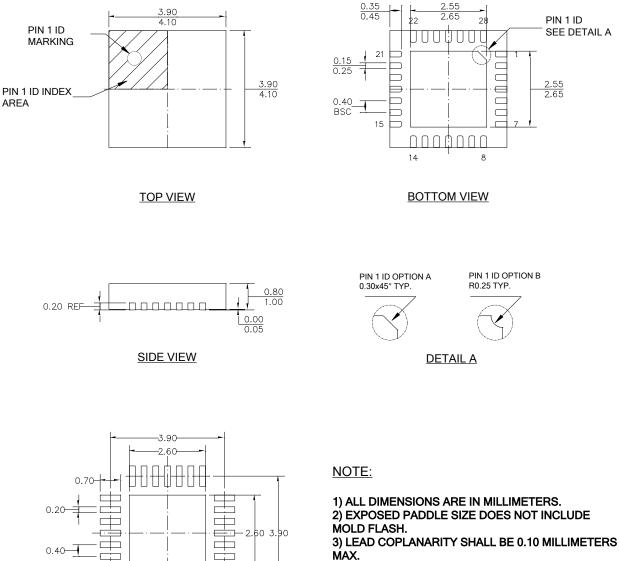

QFN-28 (4mm × 4mm)

4) DRAWING CONFORMS TO JEDEC MO-220. 5) DRAWING IS NOT TO SCALE.

RECOMMENDED LAND PATTERN

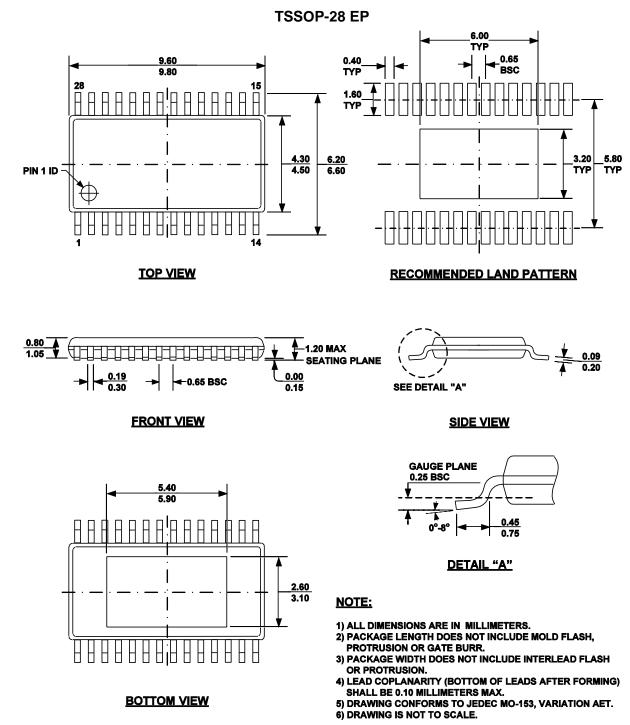

# **PACKAGE INFORMATION**

**NOTICE:** The information in this document is subject to change without notice. Users should warrant and guarantee that third party Intellectual Property rights are not infringed upon when integrating MPS products into any application. MPS will not assume any legal responsibility for any said applications.

# **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Motor/Motion/Ignition Controllers & Drivers category:

Click to view products by Monolithic Power Systems manufacturer:

Other Similar products are found below :

FSB50550TB2FSBF15CH60BTHMSVCPM2-63-12MSVGW45-14-2MSVGW54-14-3MSVGW54-14-5NTE7043LA6565VR-TLM-ELB11650-ELB1837M-TLM-ELB1845DAZ-XELC898300XA-MHSS30-TE-L-E26700LV8281VR-TLM-HBA5839FP-E2IRAM236-1067ALA6584JA-AHLB11847L-ENCV70501DW002R2GAH293-PL-BSTK672-630CN-ETND315S-TL-2HFNA23060FSB50250ABFNA41060MSVB54MSVBTC50EMSVCPM3-54-12MSVCPM3-63-12MSVCPM4-63-12MSVTA120FSB50550ABNCV70501DW002GLC898301XA-MHLV8413GP-TE-L-EMSVGW45-14-3MSVGW45-14-4MSVGW45-14-5MSVGW54-14-4STK984-091A-EMP6519GQ-ZLB11651-EIRSM515-025DA4LV8127T-TLM-HNCP81382MNTXGTDA21801LB11851FA-BHNCV70627DQ001R2GLB1938FAGEVB