# 100V, Three-Phase, BLDC Motor Pre-Driver with Hall Signal Interface

#### DESCRIPTION

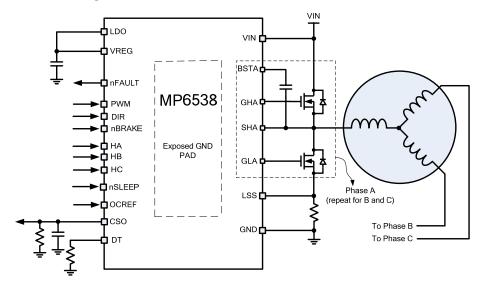

The MP6538 is a gate driver IC designed for three-phase, brushless DC motor driver applications. The MP6538 is capable of driving three half-bridges consisting of six N-channel power MOSFETs up to 100V.

The MP6538 uses bootstrap capacitor to generate a supply voltage for the high-side MOSFET driver. An internal charge pump maintains the high-side gate driver if the output is held high for an extended period of time.

Full protection features include programmable over-current protection (OCP), adjustable dead-time control, under-voltage lockout (UVLO), and thermal shutdown.

The MP6538 has three hall-sensor inputs. Commutation logic is determined by three Hall element inputs spaced at 120°. The PWM, DIR, and nBRAKE inputs are used to control motor speed, position, and torque.

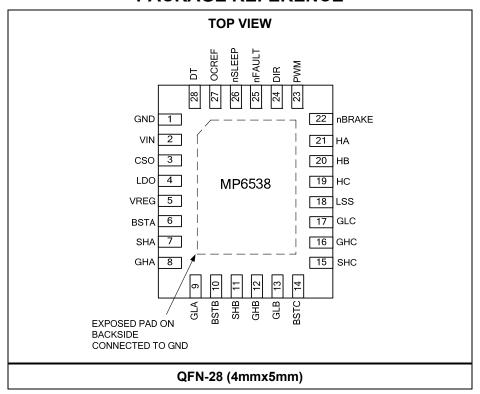

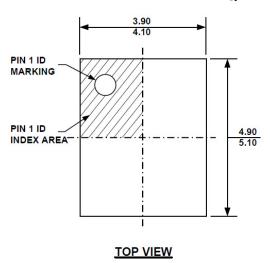

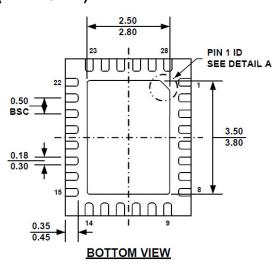

The MP6538 is available in a QFN-28 (4mmx5mm) package with an exposed thermal pad.

#### **FEATURES**

- Supports 100V Operation

- Hall Sensor Inputs

- 120V V<sub>BST</sub> Maximum Voltage

- Internal LDO Supports External NPN for High-Current Drive Requirements

- Integrated Current-Sense Amplifier

- Low-Power Sleep Mode

- Programmable Over-Current Protection (OCP) of External MOSFETs

- Adjustable Dead-Time Control to Prevent Shoot-Through

- Thermal Shutdown and Under-Voltage Lockout (UVLO) Protection

- Fault Indication Output

- Available in a Thermally Enhanced Surface-Mounted QFN-28 (4mmx5mm) Package

#### **APPLICATIONS**

- Three-Phase Brushless DC Motors and Permanent Magnet Synchronous Motors

- Power Drills

- E-Bikes

All MPS parts are lead-free, halogen-free, and adhere to the RoHS directive. For MPS green status, please visit the MPS website under Quality Assurance. "MPS" and "The Future of Analog IC Technology" are registered trademarks of Monolithic Power Systems, Inc.

#### TYPICAL APPLICATION

#### ORDERING INFORMATION

| Part Number | Package          | Top Marking |  |  |

|-------------|------------------|-------------|--|--|

| MP6538GV*   | QFN-28 (4mmx5mm) | See Below   |  |  |

<sup>\*</sup> For Tape & Reel, add suffix –Z (e.g.: MP6538GV–Z)

#### **TOP MARKING**

MPSYWW MP6538 LLLLLL

MPS: MPS prefix Y: Year code WW: Week code MP6538: Part number LLLLL: Lot number

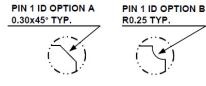

#### **PACKAGE REFERENCE**

#### ABSOLUTE MAXIMUM RATINGS (1) Input voltage (V<sub>IN</sub>) .....-0.3V to 110V Input voltage VREG, GLA/B/C.....-0.3V to 14.5V LDO .....-0.3V to 14.5V BSTA/B/C .....-0.3V to 120V GHA/B/C .....-0.3V to (BST-SH) + 0.3V GHA/B/C (transient, 2µs)..... .....-8V to (BST-SH) + 0.3V LSS.....-0.3V to 4V LSS (transient, 2µs).....-1V to 4V SHA/B/C .....-5V to 110V SHA/B/C (transient, 2µs) .....-8V to 110V All other pins to GND .....-0.3V to 6.5V Continuous power dissipation ( $T_A = +25^{\circ}C$ ) (2) QFN-28 (4mmx5mm)...... 3.1W Storage temperature .....-55°C to +150°C Junction temperature ......+150°C Lead temperature (solder) .....+260°C Recommended Operating Conditions (3) Input voltage (V<sub>IN</sub>) .....+8V to 100V Input voltage (V<sub>REG</sub>).....+8.5V to 14V OCREF voltage (Voc) ...... 0.125V to 2.4V Operating junction temp (T<sub>J</sub>).....-40°C to +125°C

| Thermal Resistance <sup>(4)</sup> | $oldsymbol{	heta}_{JA}$ | $oldsymbol{	heta}$ JC |       |

|-----------------------------------|-------------------------|-----------------------|-------|

| QFN-28 (4mmx5mm)                  | 40                      | 9                     | .°C/W |

#### NOTES:

- 1) Exceeding these ratings may damage the device.

- 2) The maximum allowable power dissipation is a function of the maximum junction temperature T<sub>J</sub> (MAX), the junction-to-ambient thermal resistance θ<sub>JA</sub>, and the ambient temperature T<sub>A</sub>. The maximum allowable continuous power dissipation at any ambient temperature is calculated by P<sub>D</sub> (MAX) = (T<sub>J</sub> (MAX)-T<sub>A</sub>)/θ<sub>JA</sub>. Exceeding the maximum allowable power dissipation produces an excessive die temperature, causing the regulator to go into thermal shutdown. Internal thermal shutdown circuitry protects the device from permanent damage.

- The device is not guaranteed to function outside of its operating conditions.

- 4) Measured on JESD51-7, 4-layer PCB.

#### **ELECTRICAL CHARACTERISTICS**

$V_{IN}$  = 48V, VREG = 12V,  $T_A$  = 25°C, unless otherwise noted.

| Parameter                          | Symbol                          | Condition                                     | Min      | Тур | Max   | Units |

|------------------------------------|---------------------------------|-----------------------------------------------|----------|-----|-------|-------|

| Power Supply                       | -                               |                                               |          |     |       |       |

| Input supply voltage               | VIN                             |                                               | 8        |     | 100   | V     |

| LDO output voltage                 | V <sub>LDO</sub>                | I <sub>LDO</sub> ≤ 5mA, V <sub>IN</sub> > 15V | 10.8     | 12  | 13.2  | V     |

| Gate driver supply voltage         | $V_{REG}$                       |                                               | 8.5      |     | 14    | V     |

|                                    | I <sub>Q</sub>                  | nSLEEP = 1, not switching                     |          | 0.7 |       | mA    |

| Quiescent current                  | I <sub>SLEEP</sub>              | nSLEEP = 0                                    |          |     | 1     | μA    |

| Control Logic                      | 0111                            |                                               |          | I   | I.    |       |

| Input logic low threshold          | VıL                             |                                               |          |     | 0.8   | V     |

| Input logic high threshold         | VIH                             |                                               | 2        |     |       | V     |

| Logic input current                | I <sub>IN(H)</sub>              | V <sub>IH</sub> = 0.8V                        | -2.4     |     | 2.4   | μA    |

| Logic input current                | I <sub>IN(L)</sub>              | V <sub>IL</sub> = 5V                          | -14      |     | 14    | μA    |

| nSLEEP pull-down resistance        | RSLEEP-PD                       |                                               |          | 450 |       | kΩ    |

| Internal pull-down resistance      | $R_{PD}$                        |                                               |          | 450 |       | kΩ    |

| Fault Output (Open-Drain Ou        |                                 |                                               |          | r   |       | 1     |

| Output low voltage                 | V <sub>OL</sub>                 | I <sub>O</sub> = 5mA                          |          |     | 0.1   | V     |

| Output high leakage current        | Іон                             | V <sub>0</sub> = 3.3V                         |          |     | 1     | μA    |

| Protection Circuit                 | 1                               |                                               | _        | r   |       | ,     |

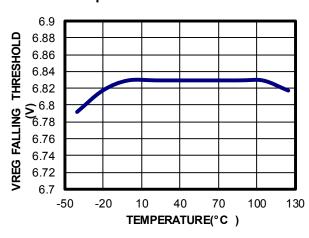

| VREG UVLO rising threshold         | V <sub>REG_RUVLO</sub>          |                                               | 6.5      | 7.5 | 8.5   | V     |

| VREG UVLO falling threshold        | V <sub>REG_FUVLO</sub>          |                                               | 6        | 6.8 | 7.6   | V     |

| VREG UVLO hysteresis               | V <sub>REG_HYS</sub>            |                                               |          | 610 |       | mV    |

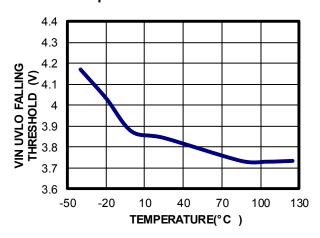

| VIN UVLO rising threshold          | $V_{VIN\_RUVLO}$                |                                               | 3.6      | 4   | 4.4   | V     |

| VIN UVLO falling threshold         | $V_{VIN\_FUVLO}$                |                                               | 3.4      | 3.8 | 4.3   | V     |

| VIN UVLO hysteresis                | $V_{VIN\_HYS}$                  |                                               |          | 100 |       | mV    |

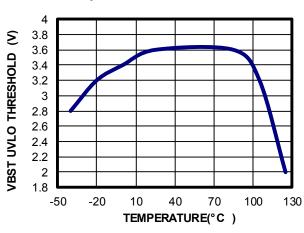

| VBST UVLO threshold                | V <sub>BST_UVLO</sub>           | Voltage between SHx and BSTx                  |          | 4   |       | V     |

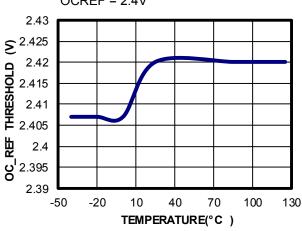

| OCREF threshold                    | V <sub>oc</sub>                 | V <sub>oc</sub> = 1V                          | 8.0      | 1   | 1.2   | V     |

|                                    |                                 | V <sub>OC</sub> = 2.4V                        | 2.18     | 2.4 | 2.62  | V     |

| OCP deglitch time                  | toc                             |                                               |          | 2.7 |       | μs    |

| Sleep wake-up time                 | tsleep                          |                                               |          | 2   |       | ms    |

| Thermal shutdown                   | T <sub>TSD</sub> <sup>(5)</sup> |                                               |          | 175 |       | °C    |

| Thermal shutdown hysteresis        | T <sub>TSD_HYS</sub> (5)        |                                               |          | 20  |       | °C    |

| Gate Drive                         | T                               |                                               |          | ı   | 1 4 0 | 1 1/  |

| Bootstrap diode forward            | V <sub>FBOOT</sub>              | I <sub>D</sub> = 10mA                         |          |     | 1.2   | V     |

| voltage                            |                                 | I <sub>D</sub> = 50mA                         |          | 0.0 | 2.3   | V     |

| Maximum source current             | DSo (5)                         |                                               |          | 0.8 |       | A     |

| Maximum sink current               | DS <sub>I</sub> (5)             | \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \         |          | 1 - |       | A     |

| Gate drive pull-up resistance      | R <sub>UP</sub>                 | V <sub>DS</sub> = 1V                          |          | 7   |       | Ω     |

| HS gate drive pull-down resistance | R <sub>HS-DN</sub>              | V <sub>DS</sub> = 1V                          | 0.6      |     | 4.5   | Ω     |

| LS gate drive pull-down resistance | R <sub>LS-DN</sub>              | V <sub>DS</sub> = 1V                          | 0.6      |     | 4.5   | Ω     |

| LS automatic turn-on time          | <b>t</b> LS                     |                                               |          | 4.6 |       | μs    |

|                                    |                                 | $R_{DT} = 10k\Omega$                          |          | 560 |       | ns    |

| Dead time                          | tDEAD                           | $R_{DT} = 100k\Omega$                         |          | 4.5 |       | μs    |

|                                    |                                 | DT tied to GND                                | <u> </u> | 77  |       | ns    |

#### NOTES:

5) Guaranteed by design.

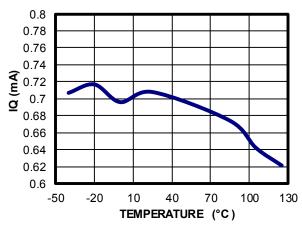

#### TYPICAL CHARACTERISTICS

$V_{IN}$  = 48V, unless otherwise noted.

#### **Quiescent Current vs. Temperature**

## VREG Falling Threshold vs. Temperature

### **OCREF Threshold vs. Temperature** OCREF = 2.4V

## VIN UVLO Falling Threshold vs. Temperature

## VBST UVLO Threshold vs. Temperature

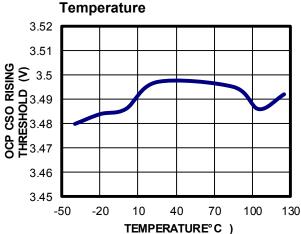

### OCP CSO Rising Threshold vs.

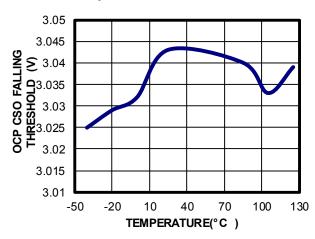

### TYPICAL CHARACTERISTICS (continued)

$V_{\text{IN}}$  = 48V, unless otherwise noted.

#### OCP CSO Falling Threshold vs. **Temperature**

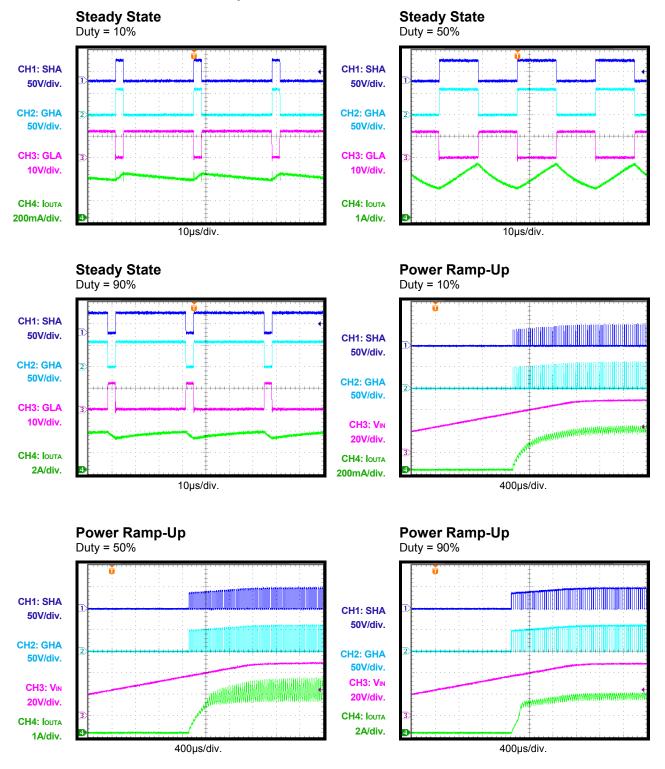

#### TYPICAL PERFORMANCE CHARACTERISTICS

$V_{IN}$  = 48V, OCREF = 0.5V,  $R_{DT}$  = 1k $\Omega$ , A phase switching, B phase LS on,  $f_{PWMA}$  = 30kHz,  $T_A$  = 25°C, resistor + inductor load:  $5\Omega$  + 1mH/phase with star connection, unless otherwise noted.

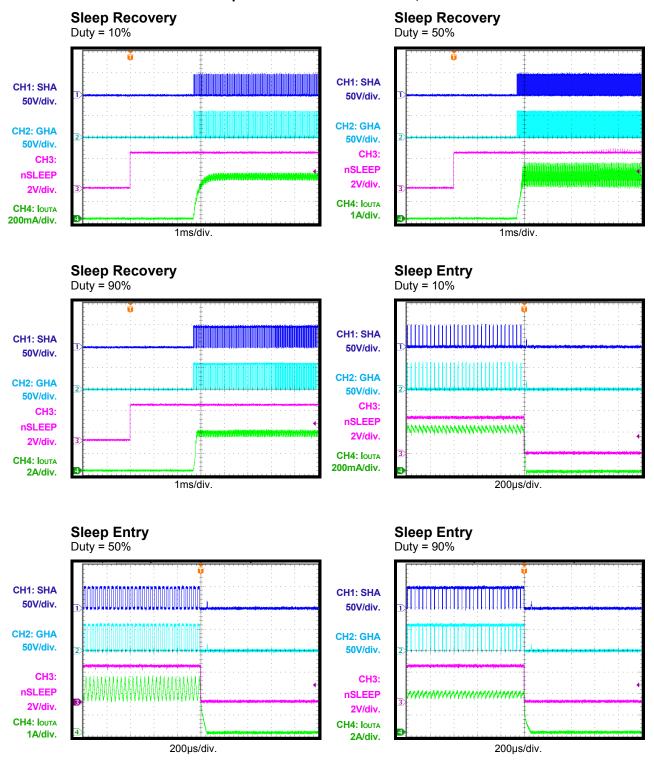

#### TYPICAL PERFORMANCE CHARACTERISTICS (continued)

$V_{IN}$  = 48V, OCREF = 0.5V,  $R_{DT}$  = 1k $\Omega$ , A phase switching, B phase LS on,  $f_{PWMA}$  = 30kHz,  $T_A$  = 25°C, resistor + inductor load:  $5\Omega$  + 1mH/phase with star connection, unless otherwise noted.

### **PIN FUNCTIONS**

| Pin# | Name   | Description                                                                                                  |

|------|--------|--------------------------------------------------------------------------------------------------------------|

| 1    | GND    | Ground.                                                                                                      |

| 2    | VIN    | Input supply voltage.                                                                                        |

| 3    | CSO    | Current sense output and OCP off time adjust.                                                                |

| 4    | LDO    | Gate drive LDO output/base drive for external NPN transistor.                                                |

| 5    | VREG   | Gate driver supply voltage.                                                                                  |

| 6    | BSTA   | Bootstrap output phase A.                                                                                    |

| 7    | SHA    | High-side source connection phase A.                                                                         |

| 8    | GHA    | High-side gate drive phase A.                                                                                |

| 9    | GLA    | Low-side gate drive phase A.                                                                                 |

| 10   | BSTB   | Bootstrap output phase B.                                                                                    |

| 11   | SHB    | High-side source connection phase B.                                                                         |

| 12   | GHB    | High-side gate drive phase B.                                                                                |

| 13   | GLB    | Low-side gate drive phase B.                                                                                 |

| 14   | BSTC   | Bootstrap output phase C.                                                                                    |

| 15   | SHC    | High-side source connection phase C.                                                                         |

| 16   | GHC    | High-side gate drive phase C.                                                                                |

| 17   | GLC    | Low-side gate drive phase C.                                                                                 |

| 18   | LSS    | Low-side source connection.                                                                                  |

| 19   | HC     | Phase C Hall-sensor input.                                                                                   |

| 20   | HB     | Phase B Hall-sensor input.                                                                                   |

| 21   | HA     | Phase A Hall-sensor input.                                                                                   |

| 22   | nBRAKE | Active-low logic input for the braking function.                                                             |

| 23   | PWM    | External PWM control for speed/torque.                                                                       |

| 24   | DIR    | Logic input to determine the direction of the motor torque output.                                           |

| 25   | nFAULT | <b>Fault indication.</b> nFAULT is an open-drain output type. nFAULT is logic low when in a fault condition. |

| 26   | nSLEEP | <b>Sleep mode input.</b> Logic low to enter low-power sleep mode; high to enable. Internal pulldown.         |

| 27   | OCREF  | Over-current protection reference input.                                                                     |

| 28   | DT     | Dead-time setting.                                                                                           |

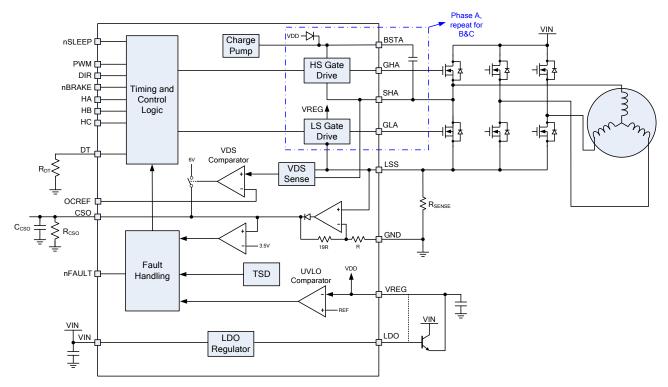

#### **BLOCK DIAGRAM**

Figure 1: Functional Block Diagram

#### **OPERATION**

The MP6538 is a three-phase, BLDC motor pre-driver that can drive three half-bridges with a 0.8A source and 1A sink current capability. The MP6538 supports operation up to 100V. The MP6538 features a low-power sleep mode, which disables the device and draws very low supply current.

The MP6538 provides several flexible functions, such as adjustable dead-time control and overcurrent protection (OCP), which allow the device to cover a wide range of applications.

#### **Power-Up Sequence**

The power-up sequence is initiated by the application of voltage to VIN and the voltage present on VREG. Usually, VREG is supplied by the internal LDO regulator connected to VIN, but it is also possible to drive VREG from another power source.

To initiate a power-up, VIN must be above ~4.5V, and VREG must be above the VREG under-voltage lockout (UVLO) threshold of 7.4V. If VREG is supplied by the internal LDO regulator, this means that VIN must be at about 8V before the part starts to power up. After VREG exceeds the VREG UVLO threshold, the MP6538 sequentially turns on each low-side MOSFET (LS-FET) in succession to charge the bootstrap capacitors.

The power-up process takes between 1ms and 2ms, after which the MP6538 responds to logic inputs and drives the outputs.

#### **Input Logic**

Driving nSLEEP low puts the device into a low-power sleep state. In this state, all internal circuits are disabled. All inputs are ignored when nSLEEP is active low. When waking up from sleep mode, approximately 1ms of time must pass before issuing a pulse-width modulation (PWM) command to allow the internal circuitry time to stabilize.

The commutation logic is determined by three Hall-element inputs spaced at 120°. The PWM, DIR, and nBRAKE inputs are used to control motor speed, position, and torque (see Table 1).

**Table 1: Input Logic Truth Table**

| PWM | nBRAKE | Mode of Operation                      |  |  |  |  |  |

|-----|--------|----------------------------------------|--|--|--|--|--|

| 0   | 1      | PWM chop mode, the load current decays |  |  |  |  |  |

| 0   | 0      | Brake mode – all low-side gates on     |  |  |  |  |  |

| 1   | 1      | Selected drivers on                    |  |  |  |  |  |

| 1   | 0      | Brake mode – all low-side gates on     |  |  |  |  |  |

Refer to Table 2 for the commutation table with nBRAKE = 1. If nBRAKE = 0, the braking function is active, and all low-side gates are on.

#### nFAULT

nFAULT reports to the system when a fault condition occurs, such as over-current protection (OCP) or over-temperature protection (OTP). nFAULT is an open-drain output type and is driven low when a fault condition occurs. If the fault condition is released, nFAULT is pulled up to a high level by an external pull-up resistor.

#### **Current-Sense Amplifier**

An integrated current-sense amplifier amplifies the voltage on LSS (relative to GND) by a factor of 20. This voltage is output to CSO.

The current-sense amplifier only sources current. An external capacitor of 1nF (minimum) must be connected from CSO to ground for stability.

During the PWM on time, current flowing through the output MOSFETs also flows through the shared low-side current sense resistor, generating a voltage that is amplified by the current sense amplifier, which charges the external capacitor on CSO. During the PWM off time, current recirculates through the LS-FETs, and does not pass through the sense resistor, so there is zero voltage across it. During this time, the capacitor discharges internal feedback through the (approximately  $450k\Omega$ ) and also through any external resistor to ground. Select an external resistor and capacitor to provide a filter to hold the value of the current through the PWM off time. Any external resistor used should be  $1k\Omega$ or larger.

| Logic Inputs |    |    |     | Driver Outputs |      |      |     |     |     | Motor Terminals |     |     |

|--------------|----|----|-----|----------------|------|------|-----|-----|-----|-----------------|-----|-----|

| HA           | HB | HC | DIR | GLA            | GLB  | GLC  | GHA | GHB | GHC | SHA             | SHB | SHC |

| 1            | 0  | 1  | 1   | /PWM           | 0    | 1    | PWM | 0   | 0   | Н               | Z   | L   |

| 1            | 0  | 0  | 1   | 0              | /PWM | 1    | 0   | PWM | 0   | Z               | Н   | L   |

| 1            | 1  | 0  | 1   | 1              | /PWM | 0    | 0   | PWM | 0   | L               | Н   | Z   |

| 0            | 1  | 0  | 1   | 1              | 0    | /PWM | 0   | 0   | PWM | L               | Z   | Н   |

| 0            | 1  | 1  | 1   | 0              | 1    | /PWM | 0   | 0   | PWM | Ζ               | L   | Н   |

| 0            | 0  | 1  | 1   | /PWM           | 1    | 0    | PWM | 0   | 0   | Н               | L   | Ζ   |

| 1            | 0  | 1  | 0   | 1              | 0    | /PWM | 0   | 0   | PWM | L               | Z   | Н   |

| 1            | 0  | 0  | 0   | 0              | 1    | /PWM | 0   | 0   | PWM | Z               | L   | Н   |

| 1            | 1  | 0  | 0   | /PWM           | 1    | 0    | PWM | 0   | 0   | Н               | Ш   | Z   |

| 0            | 1  | 0  | 0   | /PWM           | 0    | 1    | PWM | 0   | 0   | Н               | Z   | Ĺ   |

| 0            | 1  | 1  | 0   | 0              | /PWM | 1    | 0   | PWM | 0   | Ζ               | Н   | Ĺ   |

| 0            | 0  | 1  | 0   | 1              | /PWM | 0    | 0   | PWM | 0   | Ĺ               | Н   | Ζ   |

Table 2: Commutation Table (nBRAKE = 1)

### Over-Current Protection (OCP) / Current Regulation

The voltage across each LS-FET is monitored by a comparator in the MP6538 to turn the device off in the event of an over-current condition. The over-current shutdown voltage threshold level is programmable through OCREF by applying an external reference voltage with a DAC or resistor divider. When VDS of the MOSFET exceeds OCREF, CSO is pulled to ~6V internally. Whenever CSO exceeds 3.5V, an OCP event is detected, and all output MOSFETs are turned off. nFAULT is driven active low.

Once the current through the LS-FETs and the sense resistor stops, the CSO voltage is no longer driven and starts to fall at a rate determined by the external capacitor and resistor. When the voltage falls below 2.9V, the output MOSFETs are re-enabled, and nFAULT is inactive.

The resulting off time is set by the value of the external capacitor and the internal feedback resistor in parallel with the external resistor (if used).

The off time generated when CSO reaches 3.5V can be approximated with Equation (1):

$$t_{OFF}(\mu s) = 0.2*R(k\Omega)*C(nF)$$

(1)

The off time generated when VDS exceeds OCREF is longer since CSO is pulled to 6V and must decay to 2.9V for the outputs to be reenabled.

This off time can be approximated with Equation (2):

$$t_{OFF}(\mu s) = 0.6*R(k\Omega)*C(nF)$$

(2)

Where C is the capacitance from CSO to ground, and R is the total resistance from CSO to ground, comprised of the internal feedback resistor (~450k $\Omega$ ) in parallel with any external resistor to ground.

This feature can be used for current regulation to limit the stall/start-up current of a motor, either by using an external current sense resistor or (with lower accuracy) the  $R_{DS(ON)}$  of the LS-FET.

In addition to low-side current monitoring, a circuit monitors the output and triggers a fault condition of the output, driving it high, but it will not rise above ~4.5V. This provides protection against a short to ground, which would not be detected by low-side current sensing. If this occurs, the MP6538 enters a latched fault state and disables all outputs. The MP6538 remains latched off until it is reset by nSLEEP or UVLO.

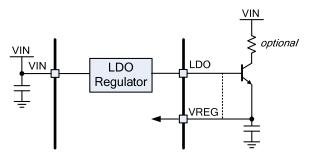

#### **Gate Drive Voltage Regulator**

To generate a voltage to drive the external MOSFET gates, a linear regulator is integrated into the MP6538.

If current over about 5mA is needed (to drive the high gate charge MOSFETs at a high switching frequency), an external NPN transistor (and optionally also a resistor) must be used to remove power dissipation from the IC. For low current applications, LDO is connected to VREG directly. For higher current requirements, an NPN transistor is used (see Figure 2).

Figure 2: High-Current Configuration of the LDO

If desired, an appropriate gate-drive supply voltage can be supplied directly to VREG from an external supply. In this case, connect only the capacitor to LDO. VIN must still be connected to the motor supply voltage.

#### **OCP Deglitch Time**

There is usually a current spike during the switching transition due to the body diode's reverse-recovery current or the distributed inductance or capacitance. This current spike requires filtering to prevent it from erroneously triggering OCP and shutting down the external MOSFET. An internal fixed deglitch time ( $t_{OC}$ ) (which is also the minimum on time for the MOSFET) blanks the output of the VDS monitor when the outputs are switched.

#### **Charge Pump and Bootstrap**

Normally, the high-side gate-drive voltage is generated from bootstrap capacitors connected between SHx and BSTx. The bootstrap capacitor is charged whenever the LS-FET is turned on.

If the output is held at a high state for a long period of time, the bootstrap capacitor discharges slowly. This eventually results in gate driver loss for the high-side MOSFET (HSFET).

To prevent this, an internal charge pump generates a voltage to maintain the bootstrap capacitor charge.

The bootstrap voltage is monitored by an under-voltage detection circuit. If any bootstrap voltage falls below the VBST UVLO voltage, the part initiates a new power-up sequence.

#### **Dead-Time Adjustment**

To prevent shoot-through in any phase of the bridge, it is necessary to insert a dead time  $(t_{DEAD})$  between a high- or low-side turn-off and the next complementary turn-on event. The dead time for all three phases is set by a single dead-time resistor  $(R_{DT})$  between DT and ground using Equation (3):

$$t_{DEAD}(\mu s) = 0.044*R(k\Omega) + 0.1$$

(3)

If DT is tied to GND directly, an internal minimum dead time of 30ns is applied. Leave DT open to generate a 6µs dead time.

#### **VREG and VIN UVLO Protection**

If at any time the voltage on VREG falls below the VREG UVLO threshold voltage, the outputs are disabled, and the nFAULT signal is asserted. Operation resumes with a bootstrap refresh when VREG rises above the UVLO threshold.

If the voltage on VIN falls below the VIN UVLO threshold voltage, all circuitry in the device is disabled, and the internal logic is reset. nFAULT is not be asserted. Operation resumes when VREG rises above the UVLO threshold.

#### **Thermal Shutdown**

If the die temperature exceeds safe limits, the MP6538 enters a latched fault state similar to an OCP event, and nFAULT is driven low. Only nSLEEP or UVLO can unlatch the device from an OTP fault lockout.

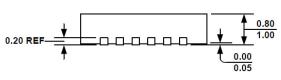

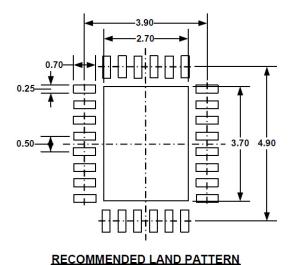

#### PACKAGE INFORMATION

#### QFN-28 (4mmx5mm)

SIDE VIEW

**DETAIL A**

#### NOTE:

- 1) ALL DIMENSIONS ARE IN MILLIMETERS.

- 2) EXPOSED PADDLE SIZE DOES NOT INCLUDE MOLD FLASH.

- 3) LEAD COPLANARITY SHALL BE 0.10 MILLIMETER MAX.

- 4) DRAWING CONFORMS TO JEDEC MO-220, VARIATION VHGD-3.

- 5) DRAWING IS NOT TO SCALE.

**NOTICE:** The information in this document is subject to change without notice. Users should warrant and guarantee that third party Intellectual Property rights are not infringed upon when integrating MPS products into any application. MPS will not assume any legal responsibility for any said applications.

### **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Motor/Motion/Ignition Controllers & Drivers category:

Click to view products by Monolithic Power Systems manufacturer:

Other Similar products are found below:

FSB50550TB2 FSBF15CH60BTH MSVCPM2-63-12 MSVGW45-14-2 MSVGW54-14-3 MSVGW54-14-5 NTE7043 LA6565VR-TLM-E LB11650-E LB1837M-TLM-E LB1845DAZ-XE LC898300XA-MH SS30-TE-L-E 26700 LV8281VR-TLM-H BA5839FP-E2 IRAM236-1067A LA6584JA-AH LB11847L-E NCV70501DW002R2G AH293-PL-B STK672-630CN-E TND315S-TL-2H FNA23060 FSB50250AB FNA41060 MSVB54 MSVBTC50E MSVCPM3-54-12 MSVCPM3-63-12 MSVCPM4-63-12 MSVTA120 FSB50550AB NCV70501DW002G LC898301XA-MH LV8413GP-TE-L-E MSVGW45-14-3 MSVGW45-14-4 MSVGW45-14-5 MSVGW54-14-4 STK984-091A-E MP6519GQ-Z LB11651-E IRSM515-025DA4 LV8127T-TLM-H NCP81382MNTXG TDA21801 LB11851FA-BH NCV70627DQ001R2G LB1938FAGEVB