**MP6650**

Single-Phase, BLDC Motor Driver with Integrated Hall Sensor in a TSOT23-6 Package

## DESCRIPTION

The MP6650 is a single-phase, brushless, DC motor driver with integrated power MOSFETs and a Hall-effect sensor. The device drives single-phase brushless DC fan motors with up to 2A of output current. The IC has a 3.3V to 18V input voltage range and input line reverse-voltage protection (RVP) to save the external diode on the supply line.

The device controls the rotational speed through the PWM signal on the PWM pin. It has a rotational speed detection feature and rotor lock fault indication on the FG/RD pin with an open-drain output. The output speed vs. the input duty curve can be configured easily for flexible use. To reduce audible fan driver noise and power loss, the MP6650 features a soft on/off phase transition and an automatic phaselock function of the motor winding BEMF and current.

Full protection features include input overvoltage protection (OVP), under-voltage lockout (UVLO), rotor deadlock (RD) protection, thermal shutdown, and input reverse protection.

The MP6650 requires a minimal number of external components to save solution cost. It is available in TSOT23-6-L, TSOT23-6-R, TSOT23-6-SL, and TSOT23-6-RSL packages.

## FEATURES

- Embedded Hall Sensor with High Sensitivity

- Wide 3.3V to 18V Operating Input Range

- Up to 2A Configurable Current Limit

- Integrated Power MOSFETs: Total 740mΩ (HS-FET and LS-FET)

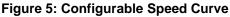

- Configurable Speed Curve

- Built-In Adjustable Speed Curve Corner Setting

- Automatic Phase-Lock Detection of Winding BEMF and Current Zero-Crossing

- Soft On/Off Phase Transition

- Rotational Speed Indicator (FG) Signal

- 2kHz to 100kHz PWM Input Frequency Range

- Fixed 26kHz Output Switching Frequency

- Input Line Reverse Voltage Protection (RVP)

- Rotor Deadlock (RD) Protection

- Thermal Protection and Automatic Recovery

- Built-In Input OVP, UVLO, and Automatic Recovery

- Available in TSOT23-6-L, TSOT23-6-R, TSOT23-6-SL, and TSOT23-6-RSL Packages

## APPLICATIONS

- CPU Fan for Personal Computers or Servers

- Brushless DC Motor

All MPS parts are lead-free, halogen-free, and adhere to the RoHS directive. For MPS green status, please visit the MPS website under Quality Assurance. "MPS", the MPS logo, and "Simple, Easy Solutions" are trademarks of Monolithic Power Systems, Inc. or its subsidiaries.

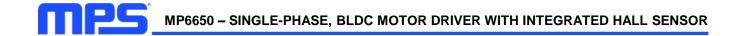

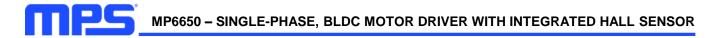

## **TYPICAL APPLICATION**

| Part Number*      | Package      | Tape & Reel | Top Marking | MSL Rating |

|-------------------|--------------|-------------|-------------|------------|

| MP6650GJL-xxxx**  | TSOT23-6-L   | Normal      |             |            |

| MP6650GJR-xxxx**  | TSOT23-6-R   | Reverse     |             |            |

| MP6650GJS-xxxx**  | TSOT23-6-SL  | Normal      | See Below   | Level 1    |

| MP6650GJSR-xxxx** | TSOT23-6-RSL | Reverse     |             |            |

## **ORDERING INFORMATION**

\* For Tape & Reel, add suffix –Z (e.g. MP6650GJS–Z).

\*\* "xxxx" is the configuration code identifier.

The four digits of the suffix (xxxx) can be a hexadecimal value between 0 and F. Work with an MPS FAE to create this unique number, even if ordering the "0000" code.

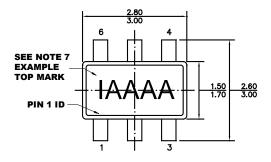

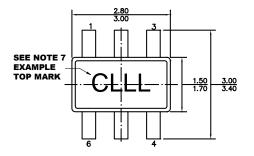

# TOP MARKING (MP6650GJL and MP6650GJR)

# | BGJY

BGJ: Product code of MP6650GJL and MP6650GJR Y: Year code

# TOP MARKING (MP6650GJS and MP6650GJSR) BGKY

## LLL

BGK: Product code of MP6650GJS and MP6650GJSR Y: Year code LLL: Lot number

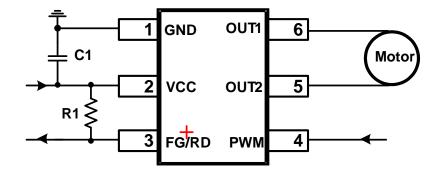

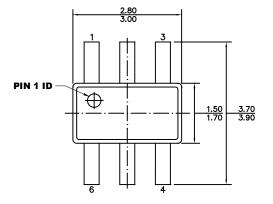

### PACKAGE REFERENCE

## **PIN FUNCTIONS**

| Pin # | Name  | Description                                                                                                                                                         |

|-------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1     | GND   | Ground.                                                                                                                                                             |

| 2     | VCC   | Input voltage supply.                                                                                                                                               |

| 3     | FG/RD | Speed indication or rotor lock fault indication output.                                                                                                             |

| 4     | PWM   | <b>Rotational speed control PWM input.</b> PWM 2kHz to 100kHz is recommended in normal operation. PWM is an internal pull-up with a resistance to the internal LDO. |

| 5     | OUT2  | <b>Motor driver output 2.</b> OUT2 is connected to the mid-point of the internal N-channel MOSFET half-bridge.                                                      |

| 6     | OUT1  | <b>Motor driver output 1.</b> OUT1 is connected to the mid-point of the internal N-channel MOSFET half-bridge.                                                      |

## ABSOLUTE MAXIMUM RATINGS (1)

| VCC                               | ±22V                   |

|-----------------------------------|------------------------|

| VCC (less than 1µs)               | 25V                    |

| PWM, FG/RD, V <sub>OUT1/2</sub> 0 |                        |

| Continuous power dissipation (TA  | = 25°C) <sup>(2)</sup> |

|                                   | 1.25W                  |

| Junction temperature              |                        |

| Lead temperature                  | 260°C                  |

| Storage temperature60             | 0°C to +150°C          |

|                                   |                        |

#### ESD Rating

| Human body model (HBM)     | 2000V |

|----------------------------|-------|

| Charged device model (CDM) | 1000V |

#### **Recommended Operating Conditions** <sup>(3)</sup>

## Thermal Resistance <sup>(4)</sup> θ<sub>JA</sub> θ<sub>JC</sub>

TSOT23-6 ..... 100..... 55 ... °C/W

#### Notes:

- 1) Exceeding these ratings may damage the device.

- 2) The maximum allowable power dissipation is a function of the maximum junction temperature T<sub>J</sub> (MAX), the junction-toambient thermal resistance  $\theta_{JA}$ , and the ambient temperature T<sub>A</sub>. The maximum allowable continuous power dissipation at any ambient temperature is calculated by P<sub>D</sub> (MAX) = (T<sub>J</sub> (MAX) - T<sub>A</sub>) /  $\theta_{JA}$ . Exceeding the maximum allowable power dissipation produces an excessive die temperature, causing the regulator to go into thermal shutdown. Internal thermal shutdown circuitry protects the device from permanent damage.

- The device is not guaranteed to function based on EC tables outside of its operating conditions.

- 4) Measured on JESD51-7, 4-layer PCB.

## **ELECTRICAL CHARACTERISTICS**

$V_{cc}$  = 12V,  $T_J$  = -40°C to +125°C, unless otherwise noted.

| Parameters                                     | Symbol                       | Condition                                                        | Min  | Тур  | Max  | Units |

|------------------------------------------------|------------------------------|------------------------------------------------------------------|------|------|------|-------|

| Input UVLO rising threshold                    | Vuvlo                        |                                                                  |      | 3    | 3.25 | V     |

| Input UVLO hysteresis                          |                              |                                                                  |      | 1    |      | V     |

| Operating supply current                       | Icc                          |                                                                  |      | 6.5  | 7.5  | mA    |

| Reverse supply current                         | ICCREV                       | VCC = -18V                                                       |      |      | 1    | mA    |

| PWM input high voltage                         | V <sub>PWMH</sub>            |                                                                  | 1.5  |      |      | V     |

| PWM input low voltage                          | V <sub>PWML</sub>            |                                                                  |      |      | 0.4  | V     |

| PWM input internal pull-up resistance          |                              |                                                                  |      | 41   | 50   | kΩ    |

| HS switch on resistance                        | Rhson                        | $I_{O}$ = 100mA, including<br>reversed MOSFET,<br>$T_{J}$ = 25°C |      | 480  | 550  | mΩ    |

| LS switch on resistance                        | RLSON                        | lo = 100mA<br>T <sub>J</sub> = 25°C                              |      | 260  | 320  | mΩ    |

| Over-current limit protection threshold        | I <sub>OCP</sub>             |                                                                  |      | 3    |      | А     |

| Output current limit                           | I <sub>LMT</sub>             | SUCL = 11                                                        | 1.7  | 2    | 2.3  | Α     |

| PWM output frequency                           | fs                           | $T_J = 25^{\circ}C$                                              | 22.1 | 26   | 29.9 | kHz   |

| FG output low-level voltage                    | $V_{FG_L}$                   | IFG/RD = 3mA, VPULL = 5V                                         |      |      | 0.35 | V     |

| FG leakage current                             |                              |                                                                  |      |      | 1    | μA    |

| OVP rising threshold                           | VOVP                         |                                                                  | 18.2 | 19.2 | 20.2 | V     |

| OVP hysteresis                                 | Vovp_hys                     |                                                                  |      | 0.9  |      | V     |

| Soft turn-on angle                             | θson_100                     | PWM duty = 100%                                                  |      | 22.5 |      | 0     |

| Soft turn-off angle                            | $\theta_{\text{SOFF}_{100}}$ | PWM duty = 100%                                                  |      | 45   |      | 0     |

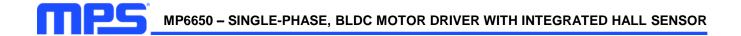

| Rotor lock detection time                      | t <sub>RD</sub>              |                                                                  | 0.45 | 0.6  | 0.75 | S     |

| Operate point                                  | BOP                          |                                                                  |      | 1    | 2    |       |

| Release point                                  | Brp                          |                                                                  | -2   | -1   |      |       |

| Hysteresis for operate point and release point | Внуз                         |                                                                  |      | 2    | 4    | mT    |

| Symmetry for operate points and release point  | B <sub>SYM</sub>             |                                                                  |      | 0    | 0.4  |       |

| Thermal shutdown threshold <sup>(5)</sup>      |                              |                                                                  |      | 150  |      | °C    |

| Thermal shutdown hysteresis (5)                |                              |                                                                  |      | 25   |      | °C    |

Note:

5) Guaranteed by design.

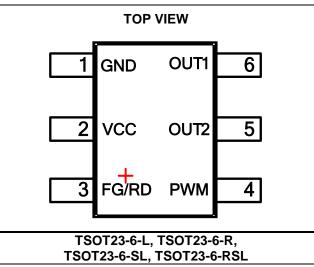

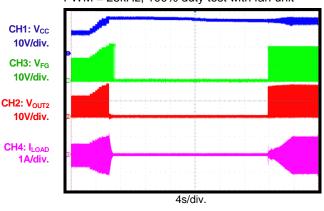

# **TYPICAL PERFORMANCE CHARACTERISTICS**

$V_{CC}$  = 12V,  $T_A$  = 25°C, tested with fan unit, unless otherwise noted.

www.MonolithicPower.com MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited. © 2019 MPS. All Rights Reserved.

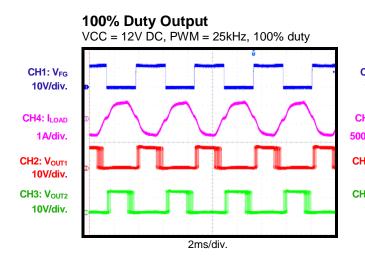

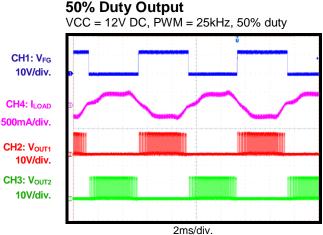

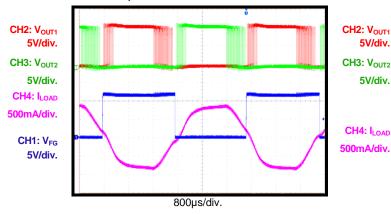

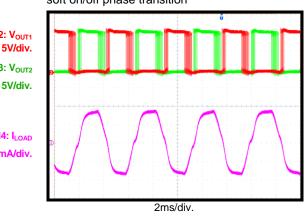

## **TYPICAL PERFORMANCE CHARACTERISTICS** (continued)

$V_{CC}$  = 12V,  $T_A$  = 25°C, tested with fan unit, unless otherwise noted.

Switching Soft On and Soft Off

VCC = 12V DC, PWM = 5V DC, soft on/off phase transition

Disable Soft On and Soft Off VCC = 12V DC, PWM = 5V DC, soft on/off phase transition CH2: V<sub>OUT1</sub> 5V/div. CH3: V<sub>OUT2</sub> 5V/div. CH4: I<sub>LOAD</sub> 1A/div.

2ms/div.

Enable Soft On and Soft Off VCC = 12V DC, PWM = 5V DC, soft on/off phase transition

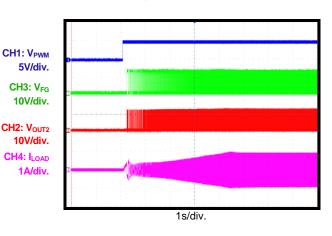

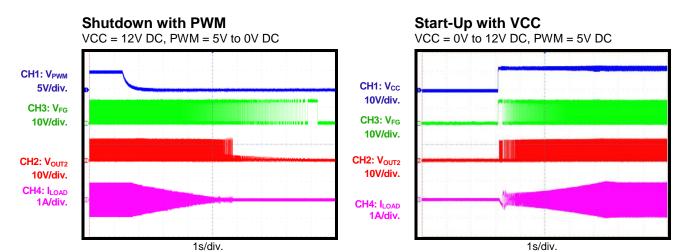

Start-Up with PWM VCC = 12V DC, PWM = 0V to 5V DC

MP6650 Rev. 1.0 11/14/2019 www.MonolithicPower.com MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited. © 2019 MPS. All Rights Reserved.

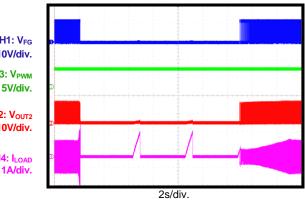

## **TYPICAL PERFORMANCE CHARACTERISTICS** (continued)

$V_{CC}$  = 12V,  $T_A$  = 25°C, tested with fan unit, unless otherwise noted.

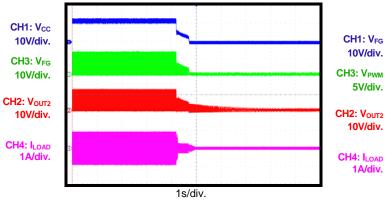

Shutdown with VCC

VCC = 12V to 0V DC, PWM = 5V DC

CH1: V<sub>RD</sub> 10V/div. CH3: V<sub>PWM</sub>

2s/div.

CH4: I<sub>LOAD</sub> 1A/div.

CH2: VOUT2

10V/div.

Over-Voltage Protection VCC = 12V DC, 19.1V to 18.3V, PWM = 25kHz, 100% duty test with fan unit

Rotor Lock and Release VCC = 12V DC, PWM = 5V DC,

lock rotor and release

www.MonolithicPower.com MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited. © 2019 MPS. All Rights Reserved.

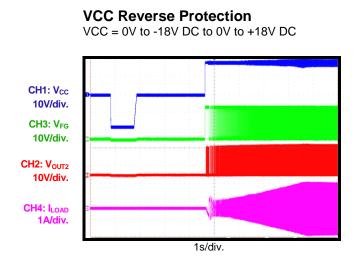

# TYPICAL PERFORMANCE CHARACTERISTICS (continued)

$V_{CC}$  = 12V,  $T_A$  = 25°C, tested with fan unit, unless otherwise noted.

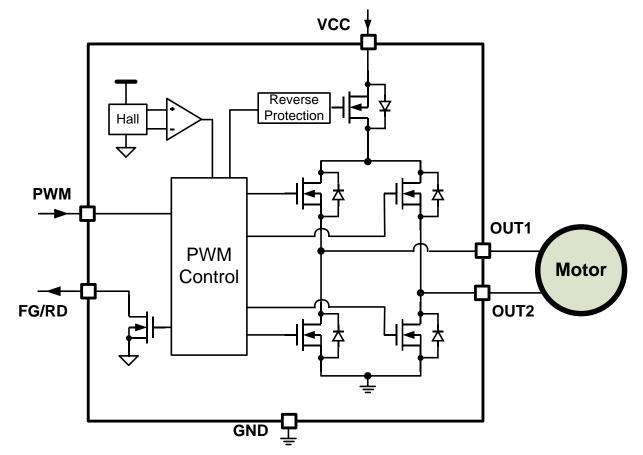

## FUNCTIONAL BLOCK DIAGRAM

Figure 1: Functional Block Diagram

## **OPERATION**

The MP6650 is a single-phase, brushless, DC motor driver with integrated power MOSFETs and a Hall-effect sensor.

#### **Speed Control**

The device is controlled using a pulse-width modulation (PWM) input interface that is compatible with industry-standard devices. The IC detects the PWM input signal duty cycle and linearly controls the H-bridge output duty cycle, so the fan speed increases as the input duty cycle increases.

The PWM input accepts a wide input frequency range of 2kHz to 100kHz, while the output frequency is maintained at 26kHz above the audible frequency range.

#### **PWM Output Drive**

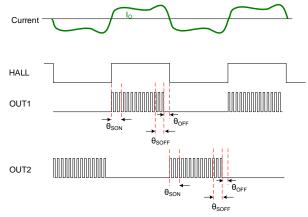

The IC controls the H-bridge MOSFET switching to reduce speed variation and increase system efficiency (see Figure 2).

When the rotor magnet pole S approaches, the internal Hall sensor outputs high. When the rotor magnet pole N approaches, the internal Hall sensor outputs low. With this Hall signal, the IC enables a soft-on transition or soft-off transition to maintain a smooth current and reduce fan vibration.

Figure 2: Timing Diagram

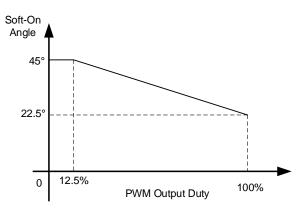

#### Soft Turn-On

During soft turn-on, OUT1 continues switching, and the duty cycle increases gradually from 0 to the target setting duty cycle in a maximum of 16 steps while OUT2 remains low. The soft-on angle lasts for 22.5 degrees when the output duty cycle is 100%, and the soft-on angle lasts for 45 degrees when the output duty cycle is 12.5%. Interpolation between the two output duties is linear (see Figure 3).

Figure 3: Soft-On Angle vs. Output Duty

#### Normal PWM Switching

While the PWM switches normally, OUT1 continues switching, and the duty cycle remains fixed at the target setting duty. OUT2 remains low.

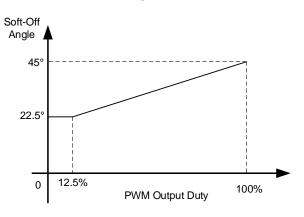

#### Soft Turn-Off

During soft turn-off, OUT1 continues switching, and the duty cycle decreases gradually from the target setting duty cycle to 0 in a maximum of 16 steps while OUT2 remains low. The soft-off angle lasts for 45 degrees when the output duty cycle is 100%, and the soft-off angle lasts for 22.5 degrees when the output duty cycle is 12.5%. Interpolation between the two output duties is linear (see Figure 4).

#### Off

During this time, OUT1 remains at high impedance, and OUT2 remains low. The time duration is adaptive from 0 degrees to 45 degrees. In steady state, this function block maintains the phase lock of the Hall output falling edge and winding current zero-crossing edge.

When the Hall output is at a low interval, the conducting phase changes, but the switching sequence remains the same.

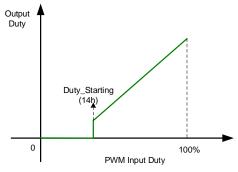

#### **PWM Input Starting Duty**

The start-up duty of the PWM input is determined by the 14H register value set by the register. An example is below:

#### SPD\_ZERO = 1, 14H = 0x20 (12.5%)

When the input duty is less than 12.5%, the fan maintains a zero speed. When the input duty is above 13.7% (hysteresis 1.2%), the fan starts rotating. The speed is based on the 00h to 08h duty cycle setting (see Figure 5).

#### SPD\_ZERO = 0, 14H = 0x20 (12.5%)

When the input duty is less than 12.5%, the fan keeps a minimum PWM output duty cycle set by the 00h to 08h register setting (see Figure 6).

Figure 6: Configurable Speed Curve

#### **Protection Circuits**

The MP6650 is fully protected against overvoltage, under-voltage, over-current, and overtemperature events. It also has input reverse protection.

#### **Over-Current Protection (OCP)**

The MP6650 protects against internal overload and short circuit by detecting the current flowing through each MOSFET. If the current flowing through any MOSFET exceeds the over-current protection (OCP) threshold after about 1.5µs of that turns off blanking time. MOSFET immediately. After the lock-retry time delay (default 3.6s), the bridge re-enables automatically.

#### **Overload Current Limit**

During normal switching, if the current flowing through the high-side MOSFET (HS-FET) of the H-bridge exceeds the threshold set by the SUCL register bits after about 1.5µs of blanking time, the HS-FET turns off immediately. The HS-FET resumes switching in the next switching cycle. The overload current limit is configurable with 0.7A, 1.1A, 1.6A, or 2A. The default limit it 1.6A.

#### Thermal Shutdown

Thermal monitoring is also integrated into the MP6650. If the die temperature exceeds 150°C, the MOSFETs of the switching half-bridge turn off. Once the die temperature drops to a safe temperature, operation resumes automatically.

#### **Under-Voltage Lockout (UVLO)**

If at any time  $V_{CC}$  falls below the under-voltage lockout (UVLO) threshold voltage, all circuitry in the device disables, and the internal logic resets. Operation resumes when  $V_{CC}$  rises above the UVLO threshold.

#### **Rotor Deadlock Protection (RD)**

The MP6650 detects the internal Hall signal and outputs a deadlock indication signal to the FG/RD pin if the FGRD bit is set to 11. If the IC cannot see the Hall signal edge change during the 0.6s detection time, the low-side MOSFETs of the H-bridge turn on. After 1.8s, 2.4s, 3s, or 3.6s of lock-retry time (depending on the RLOCK\_SEL bit's setting), the IC attempts to start up again automatically. FG/RD pin outputs again only after three Hall signal edges are

detected after the rotor lock condition is released (see Figure 7).

Figure 7: Rotor Deadlock Protection

#### **Rotor Speed Indication (FG)**

The device outputs a Hall detection signal to the FG/RD pin as speed indication. The output signal frequency can be optional for 100% or 50% of the internal Hall sensor output frequency. FG/RD pin is an open drain, and requires a pull-up resistor in the application.

#### **Over-Voltage Protection (OVP)**

If  $V_{CC}$  exceeds the over-voltage threshold (19.2V), the IC turns off the two HS-FETs and turns on the two low-side MOSFETs (LS-FET) until  $V_{CC}$  drops below 18.3V. Then the IC resumes normal operation.

#### **Input Reverse Connection Protection**

If the input line is reverse-connected to VCC and GND, the IC detects the fault condition automatically and shuts down to avoid damage.

#### Soft-Start Time

To reduce the input rush current when the duty changes, the MP6650 initiates a soft start to ramp up/down PWM input reference smoothly. This soft duty changing time is either 2.6s or the default 5.2s, and is selectable by the TSS bit.

#### **Test Mode and Factory Mode**

To program the internal register, the MP6650 has a test mode. In this test mode, all internal registers can be read/write. After completing the design, the register value can be programmed to the non-volatile memory. The non-volatile memory can be programmed twice. Refer to MPS Phase Fan Driver GUI Software for easy parameter changes and memory programming.

## **REGISTER MAP**

| Add     | Туре    | D7 | D6                   | D5                  | D4       | D3 | D2            | D1    | D0   |

|---------|---------|----|----------------------|---------------------|----------|----|---------------|-------|------|

| 00H-08H | OTP/REG |    | PWMO[7:0]            |                     |          |    |               |       |      |

| 09H     | OTP/REG | PR | PROG[1:0] Reserved   |                     |          |    |               |       |      |

| 0AH     | OTP/REG | FG | RD[1:0]              | RF                  | PMS[2:0] |    | TSS SUCL[1:0] |       | 1:0] |

| 0BH     | OTP/REG | FG | ТМ                   | SPD_ZERO            |          |    | Reserved      |       |      |

| 0DH     | OTP/REG |    | SOFTEN               | RD_HL               |          |    | Reserved      |       |      |

| 0FH     | OTP/REG |    | PLLEN                | LLEN RLOCK_SEL[1:0] |          |    | Rese          | erved |      |

| 10H     | REG     |    | Reserved FM Reserved |                     |          |    | ved           |       |      |

| 14H     | OTP/REG |    | DUTY_STARTING[7:0]   |                     |          |    |               |       |      |

#### **Register Table 1-9**

|     | Addr: 0x00 to 0x08 |             |      |         |                                 |  |  |  |  |  |

|-----|--------------------|-------------|------|---------|---------------------------------|--|--|--|--|--|

| Bit | Bit Name           | Access      | Addr | Default | Description                     |  |  |  |  |  |

|     |                    |             | 0x00 | 0x1F    |                                 |  |  |  |  |  |

|     |                    |             | 0x01 | 0x1F    |                                 |  |  |  |  |  |

|     | 7:0 PWMO OTP/REG   |             | 0x02 | 0x3F    |                                 |  |  |  |  |  |

|     |                    |             | 0x03 | 0x5F    | Output duty cycle lookup table. |  |  |  |  |  |

| 7:0 |                    | WMO OTP/REG | 0x04 | 0x7F    |                                 |  |  |  |  |  |

|     |                    |             | 0x05 | 0x9F    |                                 |  |  |  |  |  |

|     |                    |             | 0x06 | 0xBF    |                                 |  |  |  |  |  |

|     |                    |             | 0x07 | 0xDF    |                                 |  |  |  |  |  |

|     |                    |             | 0x08 | 0xFF    |                                 |  |  |  |  |  |

#### Register Table 10

|     | Addr: 0x09 |         |         |                                                                                               |  |  |  |

|-----|------------|---------|---------|-----------------------------------------------------------------------------------------------|--|--|--|

| Bit | Bit Name   | Access  | Default | Description                                                                                   |  |  |  |

| 7:6 | PROG       | OTP/REG | 00      | Indication of OTP flash.<br>00: Not programmed<br>01: Programmed once<br>10: Programmed twice |  |  |  |

| 5:0 | Reserved   |         |         |                                                                                               |  |  |  |

#### **Register Table 11**

|     | Addr: 0x0A |         |         |                                                                                                                                                                                                                                                           |  |  |  |

|-----|------------|---------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Bit | Bit Name   | Access  | Default | Description                                                                                                                                                                                                                                               |  |  |  |

| 7:6 | FGRD       | OTP/REG | 00      | FG or RD output selection.<br>00: FG<br>01: 1/2 x FG<br>11: RD                                                                                                                                                                                            |  |  |  |

| 5:3 | RPMS       | OTP/REG | 011     | Minimum speed supported. This setting influences the<br>internal clock's calculation. A higher value leads to higher<br>calculation resolution.<br>000: 50rpm<br>001: 100rpm<br>010: 200rpm<br>011: 400rpm<br>100: 800rpm<br>101: 1600rpm<br>110: 3200rpm |  |  |  |

| 2   | TSS        | OTP/REG | 1       | PWM input duty soft-start time.<br>1: 5.2s<br>0: 2.6                                                                                                                                                                                                      |  |  |  |

|     |      |         | Current limit. Default is 1.6A. |                                            |

|-----|------|---------|---------------------------------|--------------------------------------------|

| 1:0 | SUCL | OTP/REG | 10                              | 00: 0.7A<br>01: 1.1A<br>10: 1.6A<br>11: 2A |

#### **Register Table 12**

|     | Addr: 0x0B |         |         |                                                                                                                                              |  |  |  |

|-----|------------|---------|---------|----------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Bit | Bit Name   | Access  | Default | Description                                                                                                                                  |  |  |  |

| 7   | FG         | REG     | 0       | FG signal indication bit (read-only).                                                                                                        |  |  |  |

| 6   | ТМ         | REG     | 0       | Test mode indication (read-only). In test mode, turn on all functions except for the OTP flash block.<br>0: Normal operation<br>1: Test mode |  |  |  |

| 5   | SPD_ZERO   | OTP/REG | 1       | Zero speed enable bit<br>1: Enabled<br>0: Disabled                                                                                           |  |  |  |

| 4:0 | Reserve    |         |         |                                                                                                                                              |  |  |  |

#### **Register Table 13**

|     | Addr: 0x0D |         |         |                                                                                                        |  |  |  |  |

|-----|------------|---------|---------|--------------------------------------------------------------------------------------------------------|--|--|--|--|

| Bit | Bit Name   | Access  | Default | Description                                                                                            |  |  |  |  |

| 7   | Reserved   |         |         |                                                                                                        |  |  |  |  |

| 6   | SOFTEN     | OTP/REG | 1       | Soft switching function enable bit.<br>1: Soft function enable<br>0: Soft function disable             |  |  |  |  |

| 5   | RD_HL      | OTP/REG | 0       | RD polarity set when rotor is locked. Default is 0.<br>0: RD high when locked<br>1: RD low when locked |  |  |  |  |

| 4:0 | Reserved   |         |         |                                                                                                        |  |  |  |  |

#### **Register Table 14**

| Addr: 0x0F |           |         |         |                                                                                                                                                      |  |  |  |  |

|------------|-----------|---------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Bit        | Bit Name  | Access  | Default | Description                                                                                                                                          |  |  |  |  |

| 7          | Reserved  |         |         |                                                                                                                                                      |  |  |  |  |

| 6          | PLLEN     | OTP/REG | 1       | Load current zero-crossing PLL function enable bit.<br>1: Enabled<br>0: Disabled. Recommended for applications where input<br>current is below 100mA |  |  |  |  |

| 5:4        | RLOCK_SEL | OTP/REG | 11      | Rotor lock-retry time to detect time ratio selection.<br>00: 1:3 (0.6s/1.8s)<br>01: 1:4 (0.6s/2.4s)<br>10: 1:5 (0.6s/3.0s)<br>11: 1:6 (0.6s/3.6s)    |  |  |  |  |

| 3:0        | Reserved  |         |         |                                                                                                                                                      |  |  |  |  |

#### Register Table 15

| Addr: 0x14 |                   |         |         |                                                            |  |  |  |  |  |

|------------|-------------------|---------|---------|------------------------------------------------------------|--|--|--|--|--|

| Bit        | Bit Name          | Access  | Default | Description                                                |  |  |  |  |  |

| 7:0        | DUTY_<br>STARTING | OTP/REG | 20H     | PWM input starting duty cycle.<br>FFH: 100%<br><br>00H: 0% |  |  |  |  |  |

## **APPLICATION INFORMATION**

#### **Selecting the Input Capacitor**

Place an input capacitor (C1) near VCC to maintain a stable input voltage and reduce input switching voltage noise and ripple. The input capacitor impedance must be low at the switching frequency. Ceramic capacitors with X7R dielectrics are recommended due to their low ESR characteristics.

Ensure that the ceramic capacitance is based on the voltage rating. The DC bias voltage and value can lose as much as 50% of its capacitance at its rated voltage rating. Leave enough voltage rating margin when selecting the component. For applications requiring less than 500mA, a  $0.22\mu$ F to  $1\mu$ F ceramic capacitor is sufficient. If required, add an additional, large electrolytic capacitor to absorb inductor energy.

#### **Input Snubber**

Because the input capacitor charges and discharges energy during the phase transition soft switching, the input current has switching cycle ringing. If required, add a  $2\Omega$  resistor in series with the capacitor as an R-C.

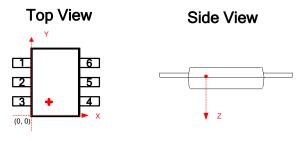

#### Hall Sensor Position

The Hall sensor cell is located in the lower-left corner of the package (see Figure 8).

(X, Y, Z) = (540μm, 508μm, 80μm) Figure 8: Hall Sensor Position

#### **Input Clamping Circuits**

High voltage spikes may be caused by back-EMF energy stored in the rotor, typically for high-current and inertia fans. It is recommended to add an input clamping TVS circuit. An SOD-323 package usually suffices. If an input clamping TVS circuit is needed, see the Typical Application Circuit section on page 19 for circuit details. For <300mA, <8cm fans, these circuits are usually not needed.

## **TYPICAL APPLICATION CIRCUIT**

Figure 9: Typical Application Circuit for 12V VCC Input

## **PACKAGE INFORMATION**

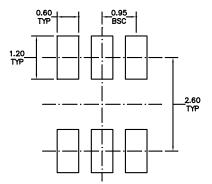

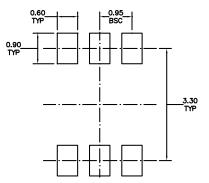

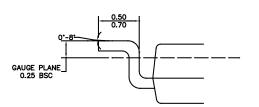

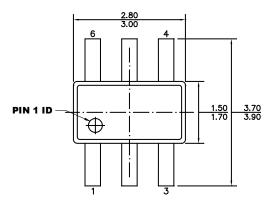

TSOT23-6-L

TOP VIEW

RECOMMENDED LAND PATTERN

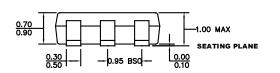

FRONT VIEW

SIDE VIEW

NOTE:

1) ALL DIMENSIONS ARE IN MILLIMETERS.

2) PACKAGE LENGTH DOES NOT INCLUDE MOLD FLASH,

PROTRUSION, OR GATE BURR.

3) PACKAGE WIDTH DOES NOT INCLUDE INTERLEAD FLASH OR PROTRUSION.

4) LEAD COPLANARITY (BOTTOM OF LEADS AFTER FORMING) SHALL BE 0.10 MILLIMETERS MAX.

5) DRAWING CONFORMS TO JEDEC MO-193, VARIATION AB. 6) DRAWING IS NOT TO SCALE.

7) PIN 1 IS LOWER-LEFT PIN WHEN READING TOP MARK FROM LEFT TO RIGHT (SEE EXAMPLE TOP MARK).

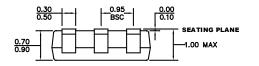

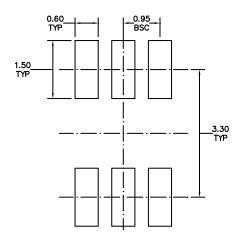

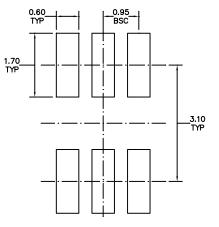

## **PACKAGE INFORMATION**

**RECOMMENDED LAND PATTERN**

TOP VIEW

FRONT VIEW

SIDE VIEW

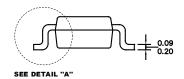

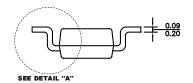

DETAIL "A"

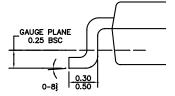

#### NOTE:

ALL DIMENSIONS ARE IN MILLIMETERS.

PACKAGE LENGTH DOES NOT INCLUDE MOLD FLASH, PROTRUSION, OR GATE BURR.

PACKAGE WIDTH DOES NOT INCLUDE INTERLEAD FLASH OR PROTRUSION.

LEAD COPLANARITY (BOTTOM OF LEADS AFTER FORMING) SHALL BE 0.10 MILLIMETERS MAX.

DRAWING REFERENCE TO JEDEC MO-193.

DRAWING IS NOT TO SCALE.

PIN 1 IS UPPER-LEFT PIN WHEN READING TOP MARK FROM LEFT TO RIGHT (SEE EXAMPLE TOP MARK).

TSOT23-6-SL

## **PACKAGE INFORMATION**

TOP VIEW

**RECOMMENDED LAND PATTERN**

FRONT VIEW

SIDE VIEW

#### NOTE:

ALL DIMENSIONS ARE IN MILLIMETERS.

PACKAGE LENGTH DOES NOT INCLUDE MOLD FLASH, PROTRUSION, OR GATE BURR.

PACKAGE WIDTH DOES NOT INCLUDE INTERLEAD FLASH OR PROTRUSION.

LEAD COPLANARITY (BOTTOM OF LEADS AFTER FORMING) SHALL BE 0.10 MILLIMETERS MAX.

DRAWING REFERENCE IS JEDEC MO-193.

DRAWING IS NOT TO SCALE.

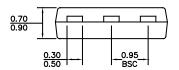

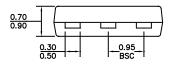

## **PACKAGE INFORMATION**

**TOP VIEW**

TSOT23-6-RSL

#### **RECOMMENDED LAND PATTERN**

#### FRONT VIEW

SIDE VIEW

#### NOTE:

1) ALL DIMENSIONS ARE IN MILLIMETERS.

2) PACKAGE LENGTH DOES NOT INCLUDE MOLD FLASH, PROTRUSION, OR GATE BURR.

3) PACKAGE WIDTH DOES NOT INCLUDE INTERLEAD FLASH OR PROTRUSION.

4) LEAD COPLANARITY (BOTTOM OF LEADS AFTER FORMING) SHALL BE 0.10

MILLIMETERS MAX.

5) DRAWING REFERENCE IS JEDEC MO-193.

6) DRAWING IS NOT TO SCALE.

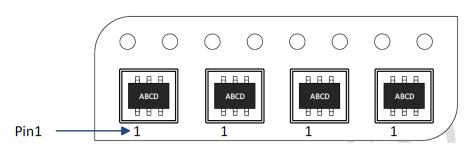

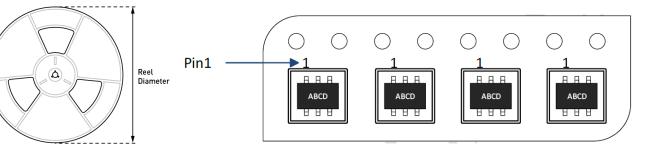

# **CARRIER INFORMATION**

TSOT23-6-L and TSOT23-6-SL

## TSOT23-6-R and TSOT23-6-RSL

| Part Number  | Package<br>Description | Quantity/Reel | Quantity/Tube | Reel<br>Diameter | Carrier<br>Tape Width | Carrier<br>Tape Pitch |

|--------------|------------------------|---------------|---------------|------------------|-----------------------|-----------------------|

| MP6650GJL-Z  | TSOT23-6-L             | 5000          | N/A           | 13in             | 12mm                  | 8mm                   |

| MP6650GJS-Z  | TSOT23-6-SL            | 5000          | N/A           | 13in             | 12mm                  | 8mm                   |

| MP6650GJR-Z  | TSOT23-6-R             | 5000          | N/A           | 13in             | 12mm                  | 8mm                   |

| MP6650GJSR-Z | TSOT23-6-<br>RSL       | 5000          | N/A           | 13in             | 12mm                  | 8mm                   |

**Notice:** The information in this document is subject to change without notice. Users should warrant and guarantee that thirdparty Intellectual Property rights are not infringed upon when integrating MPS products into any application. MPS will not assume any legal responsibility for any said applications.

# **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Motor/Motion/Ignition Controllers & Drivers category:

Click to view products by Monolithic Power Systems manufacturer:

Other Similar products are found below :

FSB50550TB2 FSBF15CH60BTH MSVCPM2-63-12 MSVGW45-14-2 MSVGW54-14-3 MSVGW54-14-5 NTE7043 LA6565VR-TLM-E LB11650-E LB1837M-TLM-E LB1845DAZ-XE LC898300XA-MH SS30-TE-L-E 26700 LV8281VR-TLM-H BA5839FP-E2 IRAM236-1067A LA6584JA-AH LB11847L-E NCV70501DW002R2G AH293-PL-B TND315S-TL-2H FNA23060 FSB50250AB FNA41060 MSVB54 MSVBTC50E MSVCPM3-54-12 MSVCPM3-63-12 MSVCPM4-63-12 MSVTA120 FSB50550AB NCV70501DW002G LC898301XA-MH LV8413GP-TE-L-E MSVGW45-14-3 MSVGW45-14-4 MSVGW45-14-5 MSVGW54-14-4 STK984-091A-E SLA7026M MP6519GQ-Z LB11651-E IRSM515-025DA4 LV8127T-TLM-H MC33812EKR2 NCP81382MNTXG TDA21801 LB11851FA-BH NCV70627DQ001R2G