# MP6905

Fast Turn-off, Intelligent Rectifier

DESCRIPTION

The MP6905 is a low-drop, diode-emulator IC with external switch; MP6905 replaces Schottky diodes in high-efficiency, flyback converters. The chip regulates the forward drop of the external switch (about 30mV) and switches it off when the voltage becomes negative. MP6905 has a light-load sleep mode that reduces the quiescent current to <300uA.

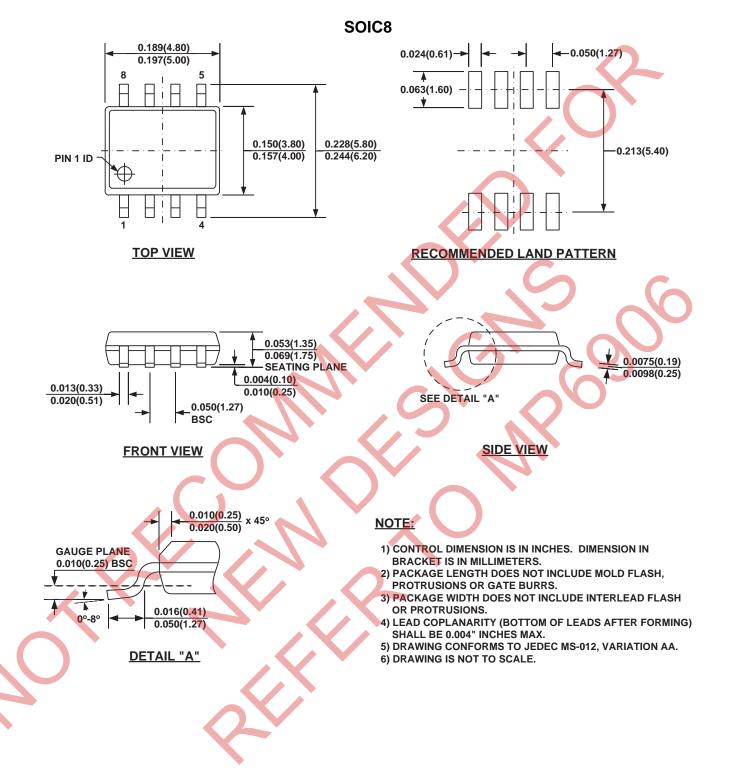

MP6905 is available in a compact SOIC-8 package.

## FEATURES

- Works with 12V Standard and 5V Logic Level FETS

- Compatible with Energy Star, 1W Standby Requirements

- Fast Turn-off, Total Delay 20ns

- <300uA Quiescent Current at Light-Load Mode

- Supports CCM, DCM and Quasi-Resonant Topologies

- Supports High-side and Low-side Rectification

- Saves Up to 1.5W in a Typical Notebook Adapter

- Available in a SOIC-8 Package

## APPLICATIONS

- Industrial Power Systems

- Distributed Power Systems

- Battery Powered Systems

- Flyback Converters

All MPS parts are lead-free and adhere to the RoHS directive. For MPS green status, please visit MPS website under Quality Assurance. "MPS" and "The Future of Analog IC Technology" are Registered Trademarks of Monolithic Power Systems, Inc.

www.MonolithicPower.com MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited. © 2015 MPS. All Rights Reserved.

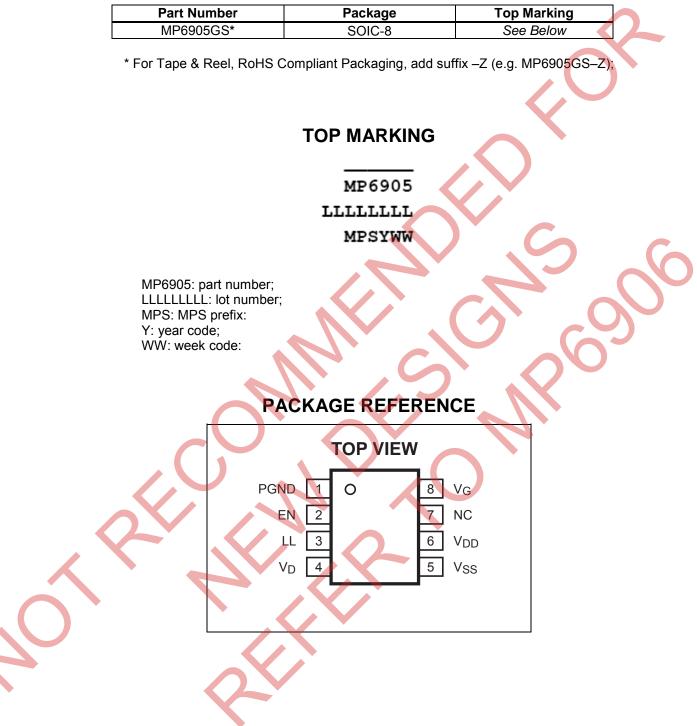

#### **ORDERING INFORMATION**

## ABSOLUTE MAXIMUM RATINGS (1)

| $V_{DD}$ to $V_{SS}$         | –0.3V to +27V                           |

|------------------------------|-----------------------------------------|

| PGND to V <sub>ss</sub>      | –0.3V to +0.3V                          |

| $V_G$ to $V_{SS}$            | –0.3V to V <sub>CC</sub>                |

| $V_D$ to $V_{SS}$            | –0.7V to +180V                          |

| LL, EN to V <sub>SS</sub>    |                                         |

| Continuous Power Dissipation | (T <sub>A</sub> = +25°C) <sup>(2)</sup> |

| SOIC8                        | 1.4W                                    |

| Junction Temperature         | 150°C                                   |

| Lead Temperature (Solder)    |                                         |

| Storage Temperature          | –55°C to +150°C                         |

## Recommended Operation Conditions <sup>(3)</sup>

| $V_{DD}$ to $V_{SS}$                     | <br>8 | V to 24V |

|------------------------------------------|-------|----------|

| Maximum Junction Temp. (T <sub>J</sub> ) | <br>  | +125°C   |

## Thermal Resistance <sup>(4)</sup> $\theta_{JA}$ $\theta_{JC}$

Notes:

- 1) Exceeding these ratings may damage the device.

- 2) The maximum allowable power dissipation is a function of the maximum junction temperature T<sub>J</sub>(MAX), the junction-to-ambient thermal resistance θ<sub>JA</sub>, and the ambient temperature T<sub>A</sub>. The maximum allowable continuous power dissipation at any ambient temperature is calculated by P<sub>D</sub>(MAX)=(T<sub>J</sub>(MAX)-T<sub>A</sub>)/θ<sub>JA</sub>. Exceeding the maximum allowable power dissipation will cause excessive die temperature, and the regulator will go into thermal shutdown. Internal thermal shutdown circuitry protects the device from permanent damage.

- The device is not guaranteed to function outside of its operating conditions.

Measured on JESD51-7, 4-layer PCB.

## **ELECTRICAL CHARACTERISTICS**

V<sub>DD</sub>=12V, T<sub>J</sub>=-40°C~125°C, Min & Max are guaranteed by characterization, typical is tested under 25°C, unless otherwise specified.

| 25 C, unless other wise spec                                 | incu:              |                                                    |                                                                           |      |                      |      |       |

|--------------------------------------------------------------|--------------------|----------------------------------------------------|---------------------------------------------------------------------------|------|----------------------|------|-------|

| Parameter                                                    | Symbol             | Conditions                                         |                                                                           | Min  | Тур                  | Max  | Units |

| V <sub>DD</sub> Voltage Range                                |                    |                                                    |                                                                           | 8    |                      | 24   | V     |

| V <sub>DD</sub> UVLO Rising                                  |                    |                                                    |                                                                           | 5.0  | 6.0                  | 7.0  | V     |

| V <sub>DD</sub> UVLO Hysteresis                              |                    |                                                    |                                                                           | 0.8  | 1                    | 1.25 | V     |

| Operating Current                                            | I <sub>CC</sub>    | C <sub>LOAD</sub> =5nF, F <sub>SW</sub> :          | =100kHz                                                                   |      | 8                    | 10   | mA    |

| Quiescent Current                                            | la                 | V <sub>SS</sub> -V <sub>D</sub> =0.5V              |                                                                           |      | 2                    | 3.6  | mA    |

| Shutdown Curront                                             |                    | V <sub>DD</sub> =4V                                |                                                                           |      |                      | 260  |       |

| Shutdown Current                                             |                    | V <sub>DD</sub> =20V, EN=0                         | V                                                                         |      |                      | 500  | μA    |

| Light-Load Mode Current                                      |                    |                                                    |                                                                           |      | 300                  | 400  | μA    |

| Thermal Shutdown <sup>(5)</sup>                              |                    |                                                    |                                                                           |      | 150                  |      | °C    |

| Thermal Shutdown                                             |                    |                                                    |                                                                           |      | 30                   |      | °C    |

| Hysteresis <sup>(5)</sup>                                    |                    |                                                    |                                                                           |      |                      |      | _     |

| Enable UVLO Rising                                           | $V_{EN-R}$         |                                                    |                                                                           | 1.1  | 1.5                  | 1.9  | V     |

| Enable UVLO Hysteresis                                       |                    |                                                    |                                                                           |      | 0.2                  | 0.4  | V     |

| Internal Pull-Up Current On                                  |                    |                                                    |                                                                           |      | 10                   | 15   | μA    |

|                                                              |                    |                                                    |                                                                           |      |                      |      | Pr. 1 |

| CONTROL CIRCUITRY SECT                                       |                    |                                                    |                                                                           | 00   | 00                   |      |       |

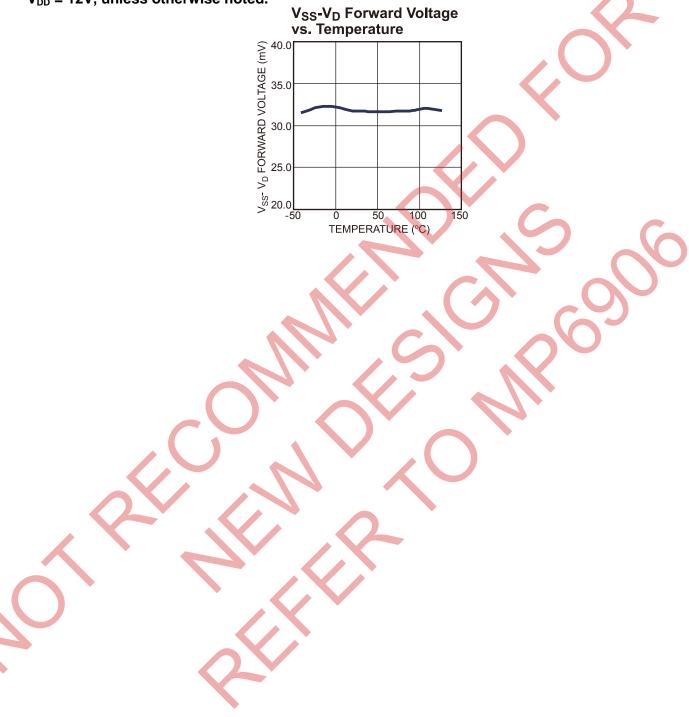

| V <sub>SS</sub> –V <sub>D</sub> Forward Voltage              | V <sub>fwd</sub>   |                                                    | 00°C <t <105°c<="" td=""><td>20</td><td>32</td><td>44</td><td>mV</td></t> | 20   | 32                   | 44   | mV    |

|                                                              | T <sub>Don</sub>   | $C_{LOAD} = 5nF$                                   | -20°C≤TJ≤125°C                                                            |      | 150                  | 250  | ns    |

| Turn-On Delay                                                |                    |                                                    | -40°C≤TJ<-20°C                                                            |      | 250                  | 050  |       |

|                                                              | T <sub>Don</sub>   | C <sub>LOAD</sub> = 10nF                           | -20°C≤TJ≤125°C                                                            |      | 250                  | 350  | ns    |

| Input Bias Current On V <sub>D</sub>                         |                    |                                                    | -40°C≤TJ<-20°C                                                            |      | 350                  | 1    |       |

| Minimum On Time                                              |                    | $V_{\rm D} = 180V$                                 |                                                                           | 0.6  | 1.0                  | 1    | μΑ    |

|                                                              |                    | $C_{LOAD} = 5nF$                                   |                                                                           | 0.6  | 1.2                  | 1.9  | μs    |

| Light-Load-Enter Delay                                       | LL-Delay           | R <sub>LL</sub> =100kΩ                             |                                                                           | 70   | 100                  | 130  | μs    |

| Light-Load-Enter Pulse Width<br>Light-Load-Enter Pulse Width | T <sub>LL</sub>    | $R_{LL}=100k\Omega$                                |                                                                           | 1.2  | 1.9                  | 2.6  | μs    |

| Hysteresis                                                   | T <sub>LL-H</sub>  | R <sub>LL</sub> =100kΩ                             |                                                                           |      | 0.2                  |      | μs    |

| Light-Load Resistor Value                                    | R <sub>LL</sub>    |                                                    |                                                                           | 30   |                      | 300  | kΩ    |

| Light-Load Mode Exit-Pulse                                   |                    |                                                    |                                                                           |      |                      |      |       |

| Width Threshold (V <sub>DS</sub> )                           | V <sub>LL-DS</sub> |                                                    |                                                                           | -380 | -250                 | -120 | mV    |

| GATE DRIVER SECTION                                          |                    |                                                    |                                                                           |      |                      |      |       |

| V <sub>G</sub> (Low)                                         | V <sub>G-L</sub>   | I <sub>LOAD</sub> =1mA                             |                                                                           |      | 0.05                 | 0.1  | V     |

|                                                              | V <sub>G-H</sub>   | V <sub>DD</sub> >17V                               |                                                                           | 13   | 14.8                 | 16.5 | V     |

| V <sub>G</sub> (High)                                        | 011                | V <sub>DD</sub> <17V                               |                                                                           |      | V <sub>DD</sub> -2.2 |      |       |

| Turn-Off Threshold (V <sub>SS</sub> -V <sub>D</sub> )        | V <sub>off</sub>   |                                                    |                                                                           | -23  | -5                   | 13   | mV    |

| Turn-Off Propagation Delay                                   |                    | V <sub>D</sub> =V <sub>SS</sub>                    |                                                                           | -    | 15                   | -    | ns    |

|                                                              | T <sub>Doff</sub>  | $V_{\rm D}$ =V <sub>SS</sub> , C <sub>LOAD</sub> = | 5nF, $R_{GATE}=0\Omega$                                                   |      | 35                   | 70   | ns    |

| Turn-Off Total Delay                                         | T <sub>Doff</sub>  |                                                    | 10nF, $R_{GATE}=0\Omega$                                                  | ĺ    | 45                   | 70   | ns    |

| Pull-Down Impedance                                          |                    | D - 33, -LOAD                                      |                                                                           |      | 1                    | 2    | Ω     |

| Pull-Down Current <sup>(5)</sup>                             |                    | 3V <v<sub>G&lt;10V</v<sub>                         |                                                                           |      | 2                    |      | A     |

| Notos:                                                       |                    |                                                    |                                                                           | 1    | -                    |      |       |

Notes:

5) Guaranteed by Characterization

## **PIN FUNCTIONS**

| Pin # | Name | Description                                                                 |

|-------|------|-----------------------------------------------------------------------------|

| 1     | PGND | Power Ground. The return for the driver switch.                             |

| 2     | EN   | Enable ( active high)                                                       |

| 3     | LL   | Light-load timing setting. Connect a resistor to set the light-load timing. |

| 4     | VD   | FET (drain-voltage sense)                                                   |

| 5     | VSS  | Ground, also used as reference for VD.                                      |

| 6     | VDD  | Supply Voltage                                                              |

| 7     | NC   | No connection                                                               |

| 8     | VG   | Gate drive output                                                           |

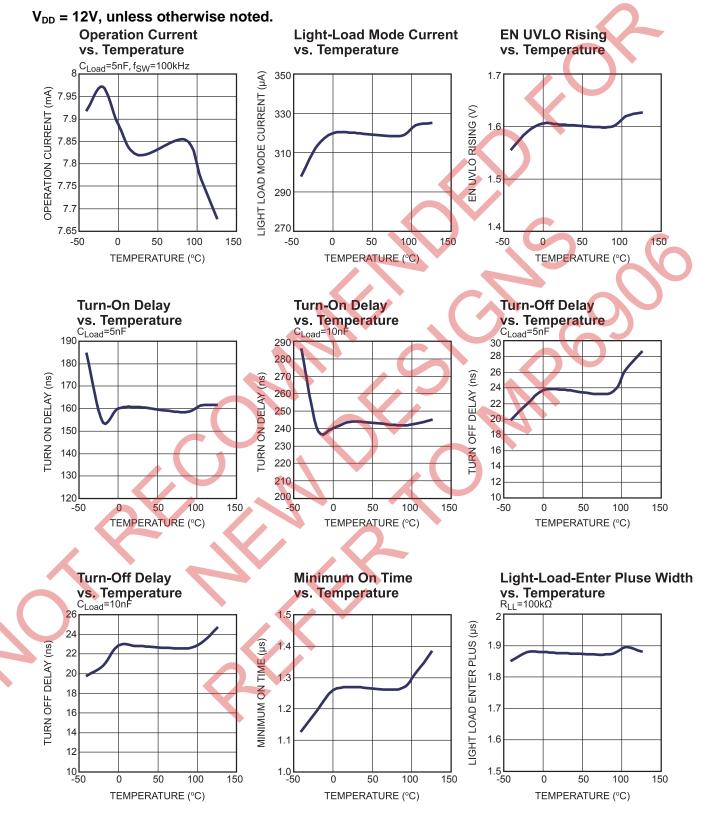

## **TYPICAL PERFORMANCE CHARACTERISTICS**

MP6905 Rev. 1.0 5/5/2015

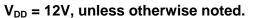

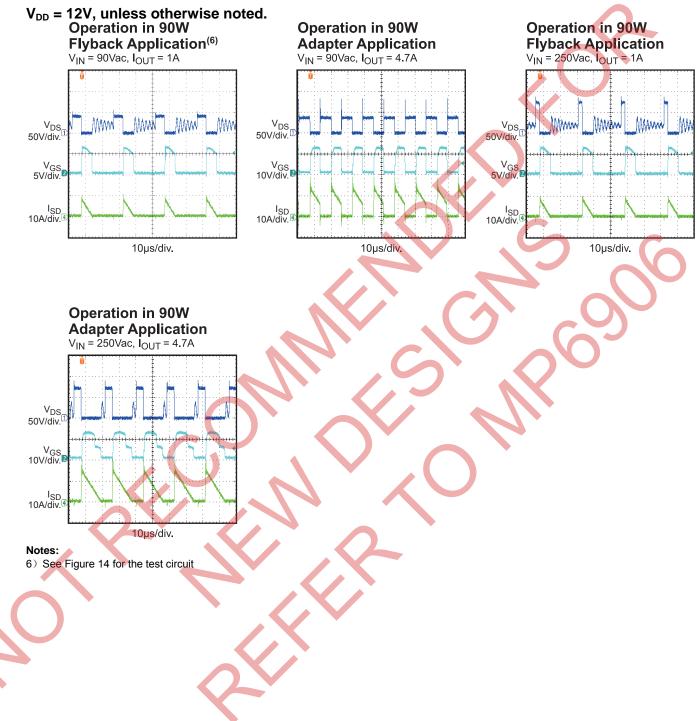

## **TYPICAL PERFORMANCE CHARACTERISTICS** (continued)

## **TYPICAL PERFORMANCE CHARACTERISTICS** (continued)

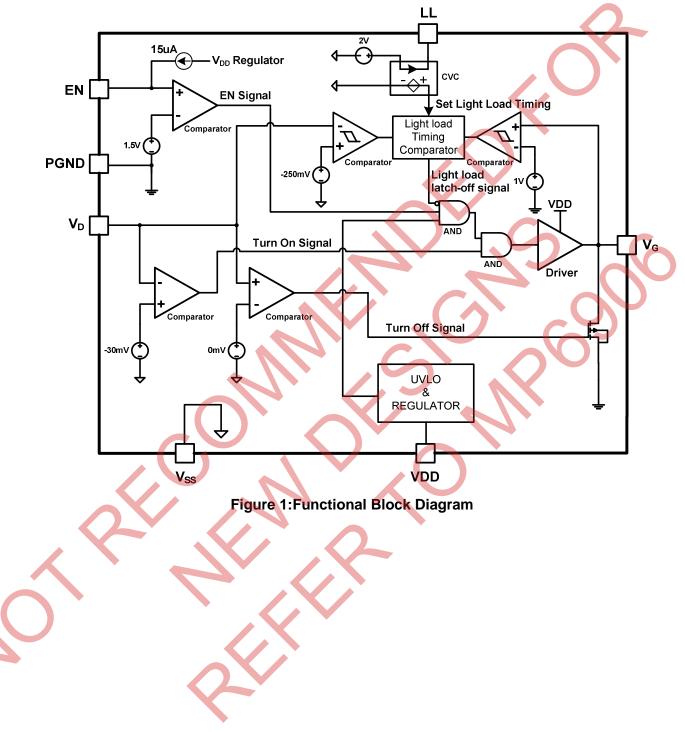

## **BLOCK DIAGRAM**

## **OPERATION**

The MP6905 operates in CCM, DCM and quasiresonant flyback converters. The control circuitry controls the gate in forward mode and turns the gate off when the MOSFET current is low.

#### Blanking

The control circuitry contains a blanking function. When it pulls the MOSFET on/off, it allows the on/off state to last for an extended period of time. The turn-on blanking time is ~1.6us, which determines the minimum on time. During the turn-on blanking period, the turn-off threshold is blanked.

#### **VD Clamp**

$V_D$  can reach up to 180V, which requires a highvoltage JFET at the input. To avoid excessive currents if  $V_G$  goes below -0.7V, a small resistor is recommended between  $V_D$  and the drain of the external MOSFET.

#### **Under-Voltage Lockout (UVLO)**

If  $V_{DD}$  is below the UVLO threshold, the part enters sleep mode, and  $V_G$  is pulled down by a  $10k\Omega$  resistor.

#### Enable

If EN is pulled low, the part enters shutdown mode, consuming <100uA shutdown current.

#### Thermal Shutdown (TSD)

If the junction temperature of the chip exceeds  $170^{\circ}$ C, the V<sub>G</sub> is pulled low and the part stops switching. The part returns to normal functioning after the junction temperature drops to  $120^{\circ}$ C.

#### Turn-On Phase

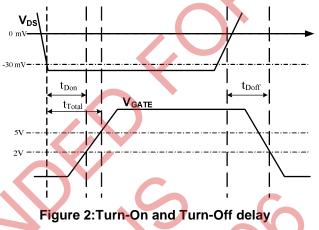

When the switch current flows through the body diode of the MOSFET, it carries a negative  $V_{DS}$  ( $V_D$ - $V_{SS}$ ) across (<-500mV). The  $V_{DS}$  is much lower than the turn-on threshold of the control circuitry (-30mV). This turns the MOSFET on after a 200ns turn-on delay (see Figure 2).

When the turn-on threshold (-30mV) is triggered, a blanking time (minimum on time) is added. This causes the turn-off threshold to be blanked. The blanking time helps avoid an error trigger on the turn-off threshold caused by turn-on ringing from the synchronous MOSFET.

#### **Conducting Phase**

When the synchronous MOSFET is turned on,  $V_{DS}$  rises (according to its on resistance). If  $V_{DS}$  rises above the turn-on threshold (-30mV), the control circuitry stops pulling the gate driver up. This pulls the gate driver down by internal pull-down resistance (10k $\Omega$ ) to increase the on resistance, easing the rise of  $V_{DS}$ .  $V_{DS}$  is adjusted to around -30mV even if the current through the MOSFET is small. This function lowers the driver voltage when the synchronous MOSFET is turned off to cause a fast turn-off speed (which is active during turn-on blanking time). Even with a small duty, the gate driver can be turned off.

#### Turn-off Phase

If  $V_{DS}$  rises and triggers the turn-off threshold (0mV), the gate voltage is pulled low by the control circuitry after about 20ns turn-off delay (see Figure 2). As with the turn-on phase, a 200ns blanking time is added when the synchronous MOSFET is turned off to avoid an error trigger.

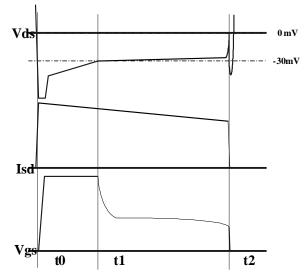

Figure 3 shows synchronous rectification operation in a heavy-load condition. Due to the high current, the gate driver initially is saturated. After  $V_{DS}$  rises above -30mV, the gate driver voltage decreases to adjust the  $V_{DS}$  (typically to - 30mV).

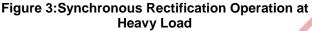

Figure 4 shows synchronous rectification operation in a light-load condition. Due to the low current, the gate-driver voltage never saturates but decreases when the synchronous MOSFET turns on, adjusting the  $V_{DS}$ .

www.MonolithicPower.com

MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited. © 2015 MPS. All Rights Reserved.

#### Light-Load Latch-Off Function

The MP6905 gate driver is latched. This reduces power loss in light-load conditions to improve efficiency. The light-load-enter pulse width  $T_{LL}$  is set by the resistor connected to LL. When the synchronous MOSFET conducting period is lower than  $T_{LL}$  for longer than the light-load-enter delay ( $T_{LL-Delay}$ ), MP6905 enters light-load mode and latches off the gate driver. The synchronous MOSFET conducting period begins when the gate driver turns on until V<sub>GS</sub> drops to the lightload mode, enter-pulse width threshold (V<sub>LL-GS</sub>). During light-load mode, MP6905 monitors the synchronous MOSFET conducting period by sensing V<sub>DS</sub> (when V<sub>DS</sub> exceeds the light-load mode exit-pulse width threshold  $V_{LL-DS}$ ). If it is longer than  $T_{LL}+T_{LL-H}$  ( $T_{LL-H}$  is light-load-enter pulse width hysteresis), the light-load mode finishes and the gate driver is unlatched to restart the synchronous rectification.

#### SR MOSFET Selection

To achieve higher efficiency, a MOSFET with a small  $R_{DS(ON)}$  is preferred. Although a Qg is larger with a smaller  $R_{DS(ON)}$ , it lowers the turn-on/off speed and leads to greater power loss, including driver power loss. The MP6904 adjusts the V<sub>DS</sub> to ~-30mV during the driving period when the switching current is low.

A MOSFET with low  $R_{DS(ON)}$  is not recommended as the gate driver is pulled low when  $V_{DS}$ =- $I_{SD}xR_{DS(ON)}$  exceeds -50mV. This means the MOSFET's  $R_{DS(ON)}$  doesn't contribute to conduction loss ( $P_{CON}$ =- $V_{DS}xI_{SD}$  $\approx I_{SD}x30mV$ ).

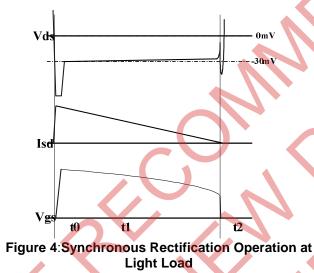

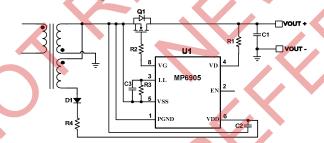

Figure 5 shows the typical waveform of a QR flyback: Assume a 50% duty cycle where  $I_{OUT}$  is the output current.

To efficiently utilize the MOSFET's  $R_{DS(ON)}$ , the MOSFET should be turned on at least 50% of the SR conduction period:

$Vds = -Ic \times Ron = -2 \cdot I_{OUT} \times Ron \le -Vfwd$

Where  $V_{DS}$  is the drain-source voltage, and  $V_{fwd}$  is the forward voltage threshold (~30mV).

The MOSFET's  $R_{DS(ON)}$  should be no lower than ~15/I<sub>OUT</sub> (m $\Omega$ ).

For example, for 5A applications, the MOSFET  $R_{DS(ON)}$  should be no lower than  $3m\Omega$ ).

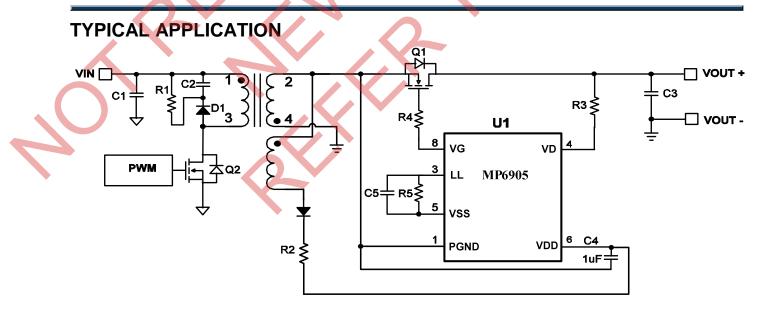

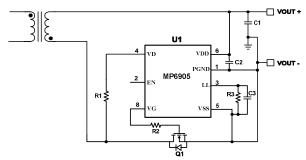

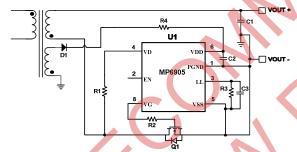

#### **Typical System Implementations**

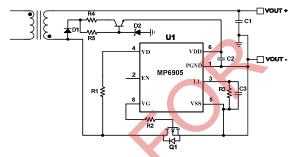

## Figure 6:IC Supply derived directly from Output Voltage

Typical system implementation for the IC supply (derived from output voltage) is available in lowside rectification (see Figure 6). The output voltage should be in the  $V_{DD}$  range of 8V to 24V.

If output voltage is out of the  $V_{DD}$  range (or highside rectification is used), use an auxiliary winding from the power transformer for the IC supply (see Figures7 and 8).

Figure 7: IC Supply Derived from Auxiliary Winding in Low-Side Rectification

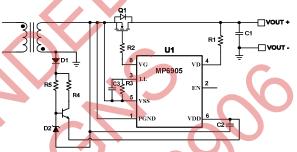

Figure 8: IC Supply Derived from Auxiliary Winding in High-Side Rectification

An additional non-auxiliary winding solution for the IC supply uses an external LDO circuit from the secondary transformer winding (see Figures 9 and 10). However, slightly higher power loss will occur, which dissipates on the LDO circuit, particularly when secondary-winding voltage is high.

Figure 9: IC Supply Derived from Secondary Winding through External LDO in Low-Side Rectification

Figure 10: IC Supply Derived from Secondary Winding through External LDO in High-Side Rectification

#### LAYOUT GUIDELINES

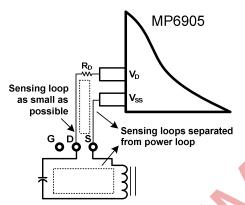

#### Sensing for V<sub>D</sub>/V<sub>SS</sub>

The sensing connection  $(V_D/V_{SS})$  should be closed off to the MOSFET (drain/source). Make the sensing loop as small as possible and place the VD resistor close to the VD. Keep the IC out of the power loop to make sure the sensing loop and power loop won't interrupt each other (see Figure 11).

Figure 11:Voltage Sensing for V<sub>D</sub>/V<sub>ss</sub> on MP6905

#### Sensing for $V_D/V_{SS}$

A decoupling ceramic capacitor (no smaller than  $1 \mu$ ) from  $V_{DD}$  to PGND should be close to the IC for adequate filtering.

#### **Gate-Driver Loop**

To minimize the parasitic inductance, the gatedriver loop should be as small as possible. Keep the driver signal far away from the VD sensing trace on the layout.

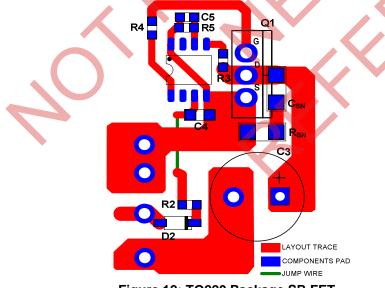

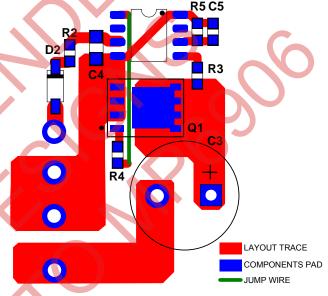

Figure 12: TO220 Package SR FET

Figure12 shows a layout example of a single layer with a through-hole transformer and TO220 package SR FET (see the application circuit on page 1).  $R_{SN}$  and  $C_{SN}$  provide the RC snubber network for the SR FET.

The sensing loop ( $V_D/V_{SS}$  to the SR FET) is minimized and separates from the power loop. The  $V_{DD}$  decoupling capacitor (C4) is placed beside the  $V_{DD}$ .

Figure 13 shows a layout example of a single layer with a PowerPAK/SO8 package SR FET, which also has a minimized sensing loop and power loop that won't interrupt each other.

Figure 13: PowerPAK/SO8 Package SR FET

www.MonolithicPower.com MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited. © 2015 MPS. All Rights Reserved.

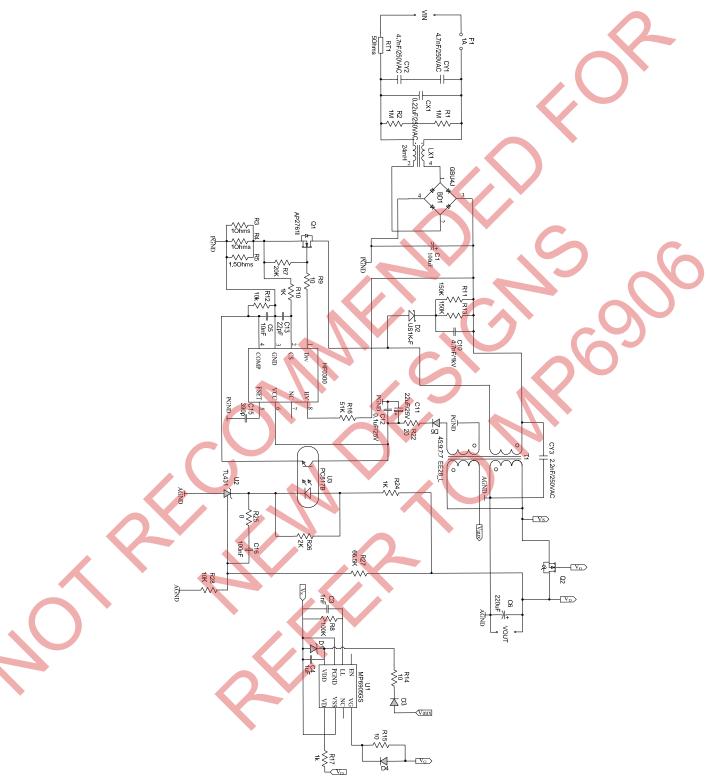

## **TYPICAL APPLICATION CIRCUIT**

Figure 14:MP6905 for Secondary Synchronous Controller in 90W Flyback Application

**NOTICE:** The information in this document is subject to change without notice. Users should warrant and guarantee that third party Intellectual Property rights are not infringed upon when integrating MPS products into any application. MPS will not assume any legal responsibility for any said applications.

## **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Switching Controllers category:

Click to view products by Monolithic Power Systems manufacturer:

Other Similar products are found below :

AZ7500EP-E1 NCP1218AD65R2G NCP1234AD100R2G NCP1244BD065R2G NCP1336ADR2G NCP6153MNTWG NCP81101BMNTXG NCP81205MNTXG SJE6600 SMBV1061LT1G SG3845DM NCP4204MNTXG NCP6132AMNR2G NCP81102MNTXG NCP81203MNTXG NCP81206MNTXG NX2155HCUPTR UBA2051C FSL4110LRLX MAX8778ETJ+ NTBV30N20T4G NCP1240AD065R2G NCP1240FD065R2G NCP1361BABAYSNT1G NTC6600NF NCP1230P100G NCP1612BDR2G NX2124CSTR SG2845M NCP81101MNTXG IFX81481ELV NCP81174NMNTXG NCP4308DMTTWG NCP4308DMNTWG NCP4308AMTTWG NCP1251FSN65T1G NCP1246BLD065R2G NTE7154 NTE7242 LTC7852IUFD-1#PBF LTC7852EUFD-1#PBF MB39A136PFT-G-BND-ERE1 NCP1256BSN100T1G LV5768V-A-TLM-E NCP1365BABCYDR2G NCP1365AABCYDR2G MCP1633T-E/MG NCV1397ADR2G AZ494AP-E1 UTC3843D