## IEEE 802.3af/at/bt-Compliant, PoE, Powered Device Interface

## DESCRIPTION

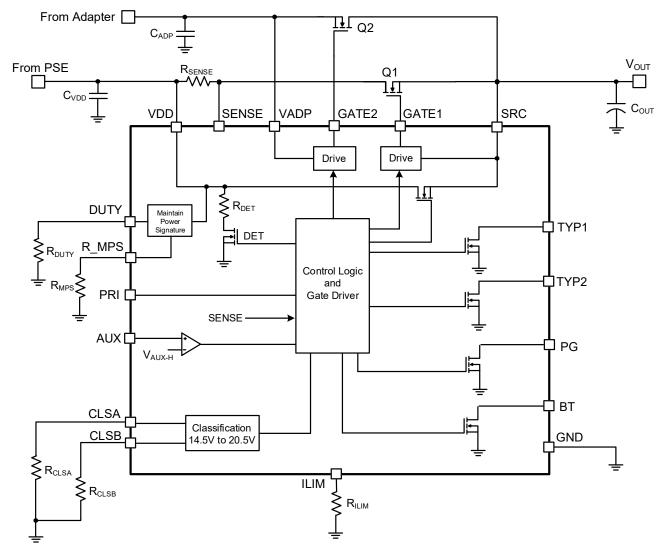

The MP8020 is an IEEE 802.3af/at/btcompliant, Power over Ethernet (PoE), powered device (PD). The device supports all the functions of IEEE 802.3af/at/bt, including detection, 5-event classification, input current ( $I_{IN}$ ) control, and an internal 100V hot-swap MOSFET.

The MP8020 provides configurable inrush current limiting during start-up and operation current limiting when the internal MOSFET is fully turned on. The GATE1 driver supports the use of an external low on resistance ( $R_{DS(ON)}$ ) MOSFET for high-power design. A high power good (PG) signal enables the use of a downstream DC/DC converter. The MP8020 also provides automatic maintain power signature functionality under light loads.

An auxiliary power input detector (AUX) and GATE2 driver provide a smooth power switch from the power-sourcing equipment (PSE) to an auxiliary wall adapter with low power loss. The MP8020 also features a built-in detection resistor, thermal protection, and a wide input under-voltage lockout (UVLO) hysteresis.

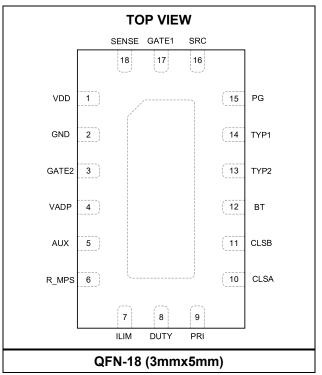

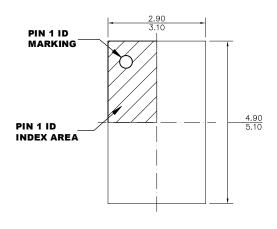

The MP8020 is available in a QFN-18 (3mmx5mm) package.

## FEATURES

- Compliant with 802.3af/at/bt Specifications

- Internal Detection Resistor

- Supports Up to 71.3W Powered Device (PD) Operation

- Internal Hot-Swap MOSFET for ≤51W Design

- External MOSFET with GATE1 for >51W Design

- Auxiliary Power Supply from >8.8V Adapter

- GATE2 N-Channel MOSFET Driver for Adapter Supply

- Configurable Current Limit

- Automatic Maintain Power Signature

- PG and Allocated Power Type Indicators

- 150°C Over-Temperature Protection (OTP)

- Available in a QFN-18 (3mmx5mm) Package

## **APPLICATIONS**

- IEEE 802.3 af/at/bt-Compliant Devices

- Security Cameras

- Video and VoIP Phones

- WLAN Access Points

- Internet of Things (IoT) Devices

- Pico Base Stations

CH4:

20V/div.

BT/TYP1/TYP2

All MPS parts are lead-free, halogen-free, and adhere to the RoHS directive. For MPS green status, please visit the MPS website under Quality Assurance. "MPS", the MPS logo, and "Simple, Easy Solutions" are trademarks of Monolithic Power Systems, Inc. or its subsidiaries.

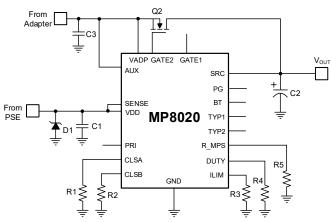

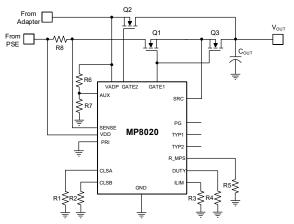

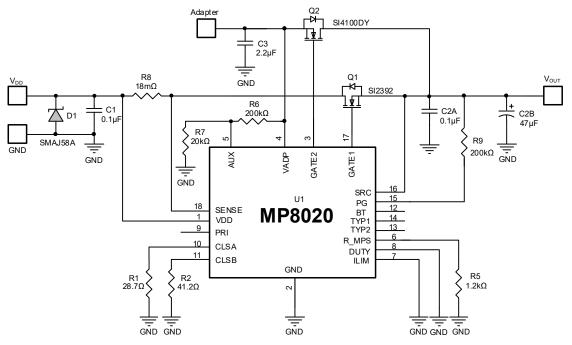

## TYPICAL APPLICATION

## CH2: VDD 20V/div. CH1: Vour 20V/div. CH3: PG 20V/div.

Mach Horizontal Trigger Acce 200 ms/div / 32.8 V Sam 58:5.00 kS/s

#### **ORDERING INFORMATION**

| Part Number | Package         | Top Marking | MSL Rating |

|-------------|-----------------|-------------|------------|

| MP8020GQV*  | QFN-18(3mmx5mm) | See Below   | 1          |

\* For Tape & Reel, add suffix -Z (e.g. MP8020GQV-Z).

## **TOP MARKING**

## MPYW

### 8020

LLL

MP: MPS prefix Y: Year code W: Week code 8020: First four digits of the part number LLL: Lot number

## PACKAGE REFERENCE

## **PIN FUNCTIONS**

| Pin # | Name  | Description                                                                                                                                                                                                                      |

|-------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1     | VDD   | Positive power supply terminal from the Power over Ethernet (PoE) input power rail.                                                                                                                                              |

| 2     | GND   | Negative power supply terminal.                                                                                                                                                                                                  |

| 3     | GATE2 | External N-channel MOSFET GATE driver for the adapter power supply.                                                                                                                                                              |

| 4     | VADP  | Positive power supply terminal from the adapter.                                                                                                                                                                                 |

| 5     | AUX   | Adapter power input detector pin. The AUX pin configures the adapter's auxiliary power under-voltage lockout (UVLO) voltage. Pull down AUX internally to GND via a resistor. If this pin is not used, pull it to GND externally. |

| 6     | R_MPS | Automatic maintain power signature load resistor connection. The R_MPS pin generates a 24V output pulse when the maintain power signature function is triggered.                                                                 |

| 7     | ILIM  | <b>Internal hot-swap MOSFET current limit configuration</b> . See the Hot-Swap MOSFET and Current Limit section on page 17 for more details.                                                                                     |

| 8     | DUTY  | Automatic maintain power signature output duty setting pin. See the Automatic Maintain Power Signature section on page 19 for more details.                                                                                      |

| 9     | PRI   | <b>Power-sourcing equipment (PSE) power and adapter power priority setting pin</b> . Pull up this pin internally to the internal 5V power source via a resistor. If PRI is low, then the PSE power source has a higher priority. |

| 10    | CLSA  | Power class signature pin. CLSA is used during the first two class events.                                                                                                                                                       |

| 11    | CLSB  | <b>Power class signature pin.</b> CLSB is used during the third class event and all subsequent class events.                                                                                                                     |

| 12    | BT    | PSE type indicator. BT is an open-drain output.                                                                                                                                                                                  |

| 13    | TYP2  | Allocated PSE power type indicator. TYP2 is an open-drain output.                                                                                                                                                                |

| 14    | TYP1  | Allocated PSE power type indicator. TYP1 is an open-drain output.                                                                                                                                                                |

| 15    | PG    | Power good (PG) indicator. PG is an open-drain output. Pull this pin active high.                                                                                                                                                |

| 16    | SRC   | Hot-swap MOSFET source pin. SRC is the power output from both the internal and external hot-swap MOSFETs.                                                                                                                        |

| 17    | GATE1 | External, parallel N-channel MOSFET GATE driver for the PSE power supply.                                                                                                                                                        |

| 18    | SENSE | External MOSFET current-sense pin. If not used, connect this pin to VDD.                                                                                                                                                         |

## ABSOLUTE MAXIMUM RATINGS (1)

| VDD, SENSE, SRC, TYP1, TYP2, PG, AUX,                               |

|---------------------------------------------------------------------|

| VADP, BT0.3V to +100V                                               |

| R_MPS0.3V to +30V                                                   |

| GATE1 to SRC0.3V to +6.5V                                           |

| GATE2 to VADP0.3V to +6.5V                                          |

| SENSE to VDD6.5V to +0.3V                                           |

| All other pins0.3V to +6.5V                                         |

| PG, TYP1, TYP2, BT sinking current5mA                               |

| Continuous power dissipation ( $T_A = 25^{\circ}C$ ) <sup>(2)</sup> |

|                                                                     |

| Junction temperature150°C                                           |

| Lead temperature                                                    |

| Storage temperature65°C to +150°C                                   |

#### **Recommended Operating Conditions** <sup>(3)</sup>

| PSE supply voltage (V <sub>DD</sub> )0V            | to 57V |

|----------------------------------------------------|--------|

| Adapter supply voltage (V <sub>ADP</sub> )0V       | to 57V |

| PG, TYP1, TYP2, BT max sink current                | 3mA    |

| Operating junction temp (T <sub>J</sub> )40°C to - | +125°C |

####

#### Notes:

- 1) Exceeding these ratings may damage the device.

- 2) The maximum allowable power dissipation is a function of the maximum junction temperature, T<sub>J</sub> (MAX), the junction-toambient thermal resistance,  $\theta_{JA}$ , and the ambient temperature, T<sub>A</sub>. The maximum allowable continuous power dissipation at any ambient temperature is calculated by P<sub>D</sub> (MAX) = (T<sub>J</sub> (MAX) - T<sub>A</sub>) /  $\theta_{JA}$ . Exceeding the maximum allowable power dissipation can produce an excessive die temperature, which may cause the regulator to go into thermal shutdown. Internal thermal shutdown circuitry protects the device from permanent damage.

- The device is not guaranteed to function outside of its operating conditions.

- 4) Measured on the EV8020-QV-00A, a 1oz, 2-layer (63mmx63mm) PCB.

- 5) The value of  $\theta_{JA}$  given in this table is only valid for comparison with other packages and cannot be used for design purposes. These values were calculated in accordance with JESD51-7, and simulated on a specified JEDEC board. They do not represent the performance obtained in an actual application.

## **ELECTRICAL CHARACTERISTICS**

$V_{DD}$  = 54V,  $T_J$  = -40°C to +125°C <sup>(6)</sup>, typical values are tested at  $T_J$  = 25°C, unless otherwise noted.

| Parameter                                       | Symbol                | Condition                                                                   | Min        | Тур        | Мах        | Units   |

|-------------------------------------------------|-----------------------|-----------------------------------------------------------------------------|------------|------------|------------|---------|

| Detection                                       |                       | ·                                                                           |            |            |            |         |

| Detection on                                    | V <sub>DET-ON</sub>   | V <sub>DD</sub> rising                                                      |            | 1          | 1.4        | V       |

| Detection off                                   | VDET-OFF              | V <sub>DD</sub> rising                                                      | 10.1       | 11         |            | V       |

| Bias current                                    | IBIAS                 | V <sub>DD</sub> = 10.1V, not in mark event,<br>measure I <sub>SUPPLY</sub>  |            |            | 12         | μA      |

| Detection resistance                            | Rdet                  | $V_{\text{DD}}$ from 1.5V to 10.1V, calculate with $\Delta V$ / $\Delta I$  | 24.1       | 25         | 26.1       | kΩ      |

| Classification                                  | -                     |                                                                             |            |            |            |         |

| Classification stability time                   |                       | Stable output voltage ( $V_{OUT}$ ) from $V_{CL-ON}$ to CLSA or CLSB        |            | 0.4        | 1          | ms      |

| CLSA and CLSB class                             | V <sub>CLSA</sub>     |                                                                             |            |            |            |         |

| voltage (V <sub>CLASS</sub> ) output<br>voltage | V <sub>CLSB</sub>     | 13V < V <sub>DD</sub> < 21V,<br>1mA < I <sub>CLASS</sub> < 44mA             | 1.11       | 1.16       | 1.21       | V       |

|                                                 |                       | Measure input current, 13 ≤ V <sub>DD</sub> ≤                               | ≦ 21V, gua | aranteed b | y Vclsa ar | d Vclsb |

|                                                 |                       | $R_{CLASS} = 578\Omega$ , $13 \le V_{DD} \le 21V$                           | 1.8        | 2          | 2.4        |         |

| Classification current for                      |                       | $R_{CLASS} = 110\Omega, 13 \le V_{DD} \le 21V$                              | 9.9        | 10.55      | 11.3       | mA      |

| CLSA and CLSB                                   | ICLASS                | $R_{CLASS} = 62\Omega, 13 \le V_{DD} \le 21V$                               | 17.7       | 18.7       | 19.8       |         |

|                                                 |                       | $R_{CLASS} = 41.2\Omega, 13 \le V_{DD} \le 21V$                             | 26.6       | 28.15      | 29.7       |         |

|                                                 |                       | $R_{CLASS} = 28.7\Omega, 13 \le V_{DD} \le 21V$                             | 38.2       | 40.4       | 42.6       |         |

| Long first class event                          | t <sub>LCE</sub>      | Determine type 3 and type 4<br>PoE from trigger V <sub>CL-ON</sub>          | 76         | 81.5       | 87         | ms      |

| Classification lower<br>threshold               | V <sub>CL-ON</sub>    | Regulator turns on, VDD rising                                              | 12         | 12.5       | 13         | V       |

| Classification lower<br>threshold hysteresis    | V <sub>CL-L-HYS</sub> | Low threshold hysteresis                                                    | 1.3        | 1.5        | 1.7        | V       |

| Classification upper threshold                  | Vcl-off               | Regulator turns off, VDD rising                                             | 21         | 22         | 23         | V       |

| Classification upper<br>threshold hysteresis    | V <sub>CL-H-HYS</sub> | High threshold hysteresis                                                   |            | 0.5        |            | V       |

| Mark event reset threshold                      | VMARK-L               |                                                                             | 4.5        | 5          | 5.5        | V       |

| Max mark event voltage                          | Vmark-h               |                                                                             | 10.5       | 11         | 11.5       | V       |

| Mark event current                              | Imark                 |                                                                             | 0.5        | 1.1        | 2          | mA      |

| Mark event resistance                           | Rmark                 | 2-point measurement at 5.5V and 10.1V, calculate with $\Delta V / \Delta I$ |            |            | 12         | kΩ      |

| IC supply current during classification         | IIN-CLASS             | $V_{DD}$ = 17.5V, float CLSA and CLSB                                       |            | 180        | 300        | μA      |

| Class leakage current                           | I <sub>LEAKAGE</sub>  | $V_{CLSA} = V_{CLSB} = 0V, V_{DD} = 57V,$<br>test both CLSA and CLSB        |            |            | 1          | μA      |

## ELECTRICAL CHARACTERISTICS (continued)

$V_{DD}$  = 54V,  $T_J$  = -40°C to +125°C <sup>(6)</sup>, typical values are tested at  $T_J$  = 25°C, unless otherwise noted.

| Parameter                             | Symbol              | Condition                                                                             | Min    | Тур      | Max      | Units               |

|---------------------------------------|---------------------|---------------------------------------------------------------------------------------|--------|----------|----------|---------------------|

| Under-Voltage Lockout (UV             | ′LO)                | ·                                                                                     | •<br>• | <u>.</u> | <u>.</u> |                     |

| V <sub>DD</sub> turn-on threshold     | Vdd_r               | V <sub>DD</sub> rising                                                                | 37     | 38.5     | 40       | V                   |

| V <sub>DD</sub> turn-off threshold    | Vdd_f               | V <sub>DD</sub> falling                                                               | 30     | 31.5     | 33       | V                   |

| V <sub>DD</sub> UVLO hysteresis       | VDD_HYS             |                                                                                       | 5      | 7        |          | V                   |

| IC supply current during operation    | l <sub>iN</sub>     | No load and no R_MPS resistor                                                         |        | 1        | 1.5      | mA                  |

| Input leakage current                 |                     | V <sub>DD</sub> = 29.5V                                                               |        | 150      | 250      | μA                  |

| Hot-Swap MOSFET and Cu                | rrent Limit         |                                                                                       |        |          |          |                     |

| Internal MOSFET on<br>resistance      | R <sub>DS(ON)</sub> | I <sub>SRC</sub> = 500mA                                                              |        | 0.35     |          | Ω                   |

| Leakage current                       | Isrc-lk             | $V_{DD} = 57V, V_{SRC} = 0V,$<br>AUX = high, PRI = high                               |        | 1        | 15       | μA                  |

| ILIM detection period                 |                     |                                                                                       |        | 270      |          | μs                  |

| ILIM detection current                |                     |                                                                                       | 130    | 165      | 180      | μA                  |

| ILIM voltage threshold                |                     | 0.9A setting voltage range                                                            |        |          | 0.8      | V                   |

|                                       |                     | 1.6A setting voltage range                                                            | 1      |          | 2.2      | V                   |

|                                       |                     | V <sub>SRC</sub> drops from V <sub>DD</sub> , V <sub>DD</sub> - V <sub>SRC</sub> = 1V |        |          |          |                     |

| Internal MOSFET current               | Ішміт               | ILIM = 0V                                                                             | 0.75   | 0.9      | 1.05     | А                   |

| limit                                 |                     | Connect ILIM to GND via a<br>7.15kΩ resistor                                          | 1.4    | 1.6      | 1.8      | А                   |

|                                       |                     | V <sub>SRC</sub> ramps up from low to high, V <sub>DD</sub> - V <sub>SRC</sub> = 1V   |        |          |          |                     |

| Internal MOSFET inrush                |                     | ILIM = 0V                                                                             | 70     | 130      | 190      | mA                  |

| limit                                 | IINRUSH             | Connect ILIM to GND via a<br>7.15kΩ resistor                                          | 170    | 230      | 290      | mA                  |

| Inrush current termination            | I <sub>TERM</sub>   | V <sub>SRC</sub> rising, I <sub>TERM</sub> / I <sub>INRUSH</sub>                      |        | 75%      |          | I <sub>INRUSH</sub> |

| Inrush to operation mode delay        | t <sub>DELAY</sub>  |                                                                                       | 80     | 90       | 100      | ms                  |

| Current foldback threshold            |                     | Vsrc falling, Vdd - Vsrc                                                              | 8.2    | 10       | 11.8     | V                   |

| Foldback deglitch time <sup>(7)</sup> |                     | V <sub>SRC</sub> falling to inrush current foldback                                   |        | 1        |          | ms                  |

| GATE1 source current                  |                     | V <sub>GATE1</sub> - V <sub>SRC</sub> = 4V                                            |        | 10       |          | μA                  |

| GATE1 sink current                    |                     | V <sub>GATE1</sub> - V <sub>SRC</sub> = 4V                                            |        | 30       |          | μA                  |

| GATE1 max driving voltage             |                     |                                                                                       |        | 6        |          | V                   |

| External MOSFET current limit         |                     | V <sub>DD</sub> - V <sub>SENSE</sub>                                                  | 22     | 26       | 30       | mV                  |

| SENSE leakage current                 |                     | V <sub>SENSE</sub> = V <sub>DD</sub> = 54V                                            |        |          | 0.1      | μA                  |

| PG, BT, TYP1, TYP2                    |                     |                                                                                       |        |          |          |                     |

| Output low voltage                    |                     | I <sub>SINK</sub> = 1mA                                                               |        | 0.2      | 0.4      | V                   |

| Leakage current                       |                     | Logic = high, connect to 57V                                                          |        |          | 1        | μA                  |

## ELECTRICAL CHARACTERISTICS (continued)

$V_{DD}$  = 54V,  $T_J$  = -40°C to +125°C <sup>(6)</sup>, typical values are tested at  $T_J$  = 25°C, unless otherwise noted.

| Parameter                                                               | Symbol              | Condition                                                                   | Min  | Тур  | Max  | Units |

|-------------------------------------------------------------------------|---------------------|-----------------------------------------------------------------------------|------|------|------|-------|

| Maintain Power Signature                                                |                     |                                                                             |      |      |      |       |

| Automatic maintain power<br>signature current enable<br>threshold       | IPORT-MPS           | Load current drops                                                          |      | 36   |      | mA    |

| Automatic maintain power<br>signature current threshold<br>hysteresis   |                     | Load current rises to disable the maintain power signature current again    |      | 10   |      | mA    |

| R_MPS output voltage                                                    |                     | 1mA to 20mA                                                                 | 23   | 24   | 25   | V     |

| Type 1 and type 2 power                                                 |                     | Duty                                                                        |      | 37   |      | %     |

| sourcing equipment (PSE),                                               |                     | On period                                                                   | 75   | 85   | 95   | ms    |

| R_MPS output duty cycle                                                 |                     | Off period                                                                  | 115  | 140  | 165  | ms    |

| Type 3 and type 4 PSE,                                                  |                     | Duty                                                                        |      | 6    |      | %     |

| R_MPS output duty cycle                                                 |                     | On period                                                                   | 14   | 16   | 18   | ms    |

| with DUTY short to GND                                                  |                     | Off period 210 250 290                                                      |      | 290  | ms   |       |

| Type 3 and type 4 PSE,                                                  |                     | Duty                                                                        |      | 11.5 |      | %     |

| R_MPS output duty cycle                                                 |                     | On period                                                                   | 26   | 31   | 36   | ms    |

| with DUTY to GND via a<br>7.15kΩ resistor                               |                     | Off period                                                                  | 200  | 235  | 270  | ms    |

| Type 3 and type 4 PSE,<br>R_MPS output duty cycle<br>with DUTY floating |                     | Duty                                                                        |      | 17   |      | %     |

|                                                                         |                     | On period                                                                   | 39   | 45   | 52   | ms    |

|                                                                         |                     | Off period                                                                  | 190  | 221  | 260  | ms    |

| External MOSFET voltage drop control threshold                          |                     | V <sub>DS</sub> = V <sub>SENSE</sub> - V <sub>SRC</sub>                     |      | 26   |      | mV    |

| DUTY detection current                                                  |                     |                                                                             | 130  | 165  | 180  | μA    |

| DUTY detection period                                                   |                     |                                                                             |      | 130  |      | μs    |

|                                                                         |                     | 6% duty setting voltage range                                               |      |      | 0.8  | V     |

| DUTY voltage threshold                                                  |                     | 11.5% duty setting voltage range                                            | 1    |      | 2.2  | V     |

|                                                                         |                     | 17% duty setting voltage range                                              | 2.5  |      |      | V     |

| Adapter Supply                                                          |                     |                                                                             |      |      |      |       |

| VADP UVLO rising threshold                                              | ADP <sub>UV-R</sub> |                                                                             | 7.8  | 8.3  | 8.8  | V     |

| V <sub>ADP</sub> UVLO falling threshold                                 | ADP <sub>UV-F</sub> |                                                                             | 6.5  | 7    | 7.5  | V     |

| AUX high threshold voltage                                              | V <sub>AUX-H</sub>  |                                                                             | 1.92 | 2    | 2.08 | V     |

| AUX threshold hysteresis                                                | VAUX-HYS            |                                                                             |      | 0.15 |      | V     |

| ALIX lookago ourropt                                                    |                     | V <sub>AUX</sub> = 2V                                                       |      | 1    |      | μA    |

| AUX leakage current                                                     |                     | V <sub>AUX</sub> = 57V                                                      |      | 2.5  |      | μA    |

| GATE2 source current                                                    |                     | V <sub>GATE2</sub> - V <sub>ADP</sub> = 4V                                  |      | 20   |      | μA    |

| GATE2 sink current                                                      |                     | V <sub>GATE2</sub> - V <sub>ADP</sub> = 4V                                  | 200  |      |      | μA    |

| GATE2 max driving voltage                                               |                     | GATE2 to VADP                                                               |      | 6    |      | V     |

| GATE2 turn-on threshold                                                 |                     | V <sub>ADP</sub> - V <sub>SRC</sub> voltage after adapter supply is enabled | 0    |      | 0.45 | V     |

## ELECTRICAL CHARACTERISTICS (continued)

#### $V_{DD}$ = 54V, $T_J$ = -40°C to +125°C <sup>(6)</sup>, typical values are tested at $T_J$ = 25°C, unless otherwise noted.

| Parameter                       | Symbol           | Condition                       | Min | Тур | Мах | Units |

|---------------------------------|------------------|---------------------------------|-----|-----|-----|-------|

| Power Priority                  |                  |                                 |     |     |     |       |

| PRI input high voltage          |                  |                                 | 2   |     |     | V     |

| PRI input low voltage           |                  |                                 |     |     | 0.4 | V     |

| PRI internal pull up resistor   |                  | Pull up to internal 5V $V_{CC}$ |     | 1   |     | mΩ    |

| Thermal Shutdown                |                  |                                 |     |     |     |       |

| Thermal shutdown<br>temperature | Tsd              |                                 |     | 150 |     | °C    |

| Thermal shutdown<br>hysteresis  | T <sub>HYS</sub> |                                 |     | 20  |     | °C    |

Notes:

6) Guaranteed by over-temperature correlation. Not tested in production.

7) Guaranteed by characterization. Not tested in production.

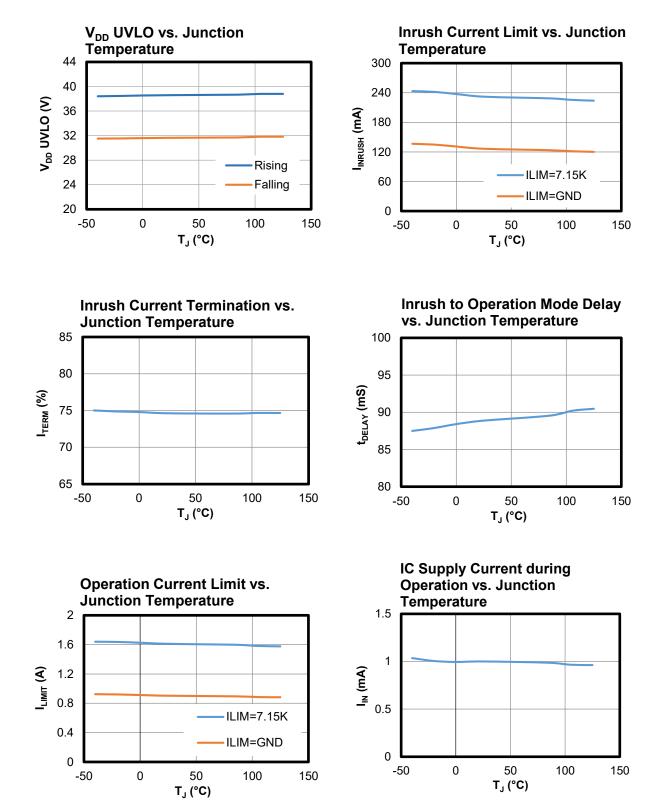

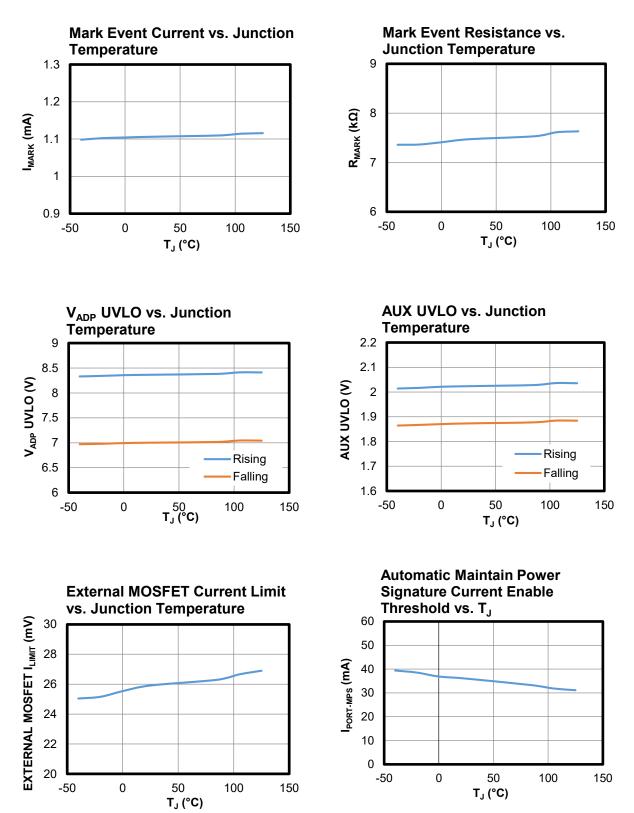

## **TYPICAL CHARACTERISTICS**

$V_{DD}$  = 54V,  $V_{ADP}$  = 24V,  $T_A$  = 25°C, unless otherwise noted.

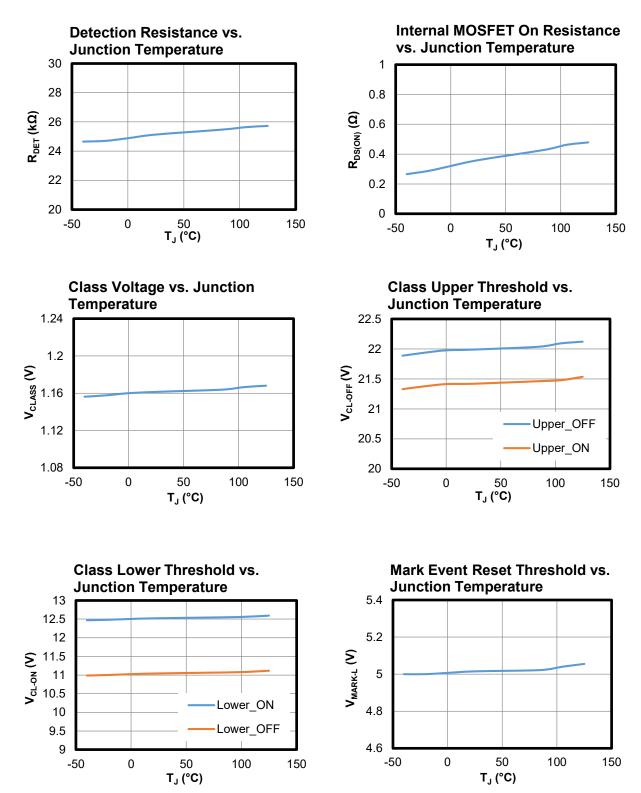

## TYPICAL CHARACTERISTICS (continued)

$V_{DD}$  = 54V,  $V_{ADP}$  = 24V,  $T_A$  = 25°C, unless otherwise noted.

## TYPICAL CHARACTERISTICS (continued)

$V_{DD}$  = 54V,  $V_{ADP}$  = 24V,  $T_A$  = 25°C, unless otherwise noted.

MP8020 Rev. 1.0 2/17/2022

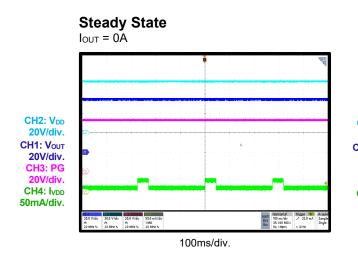

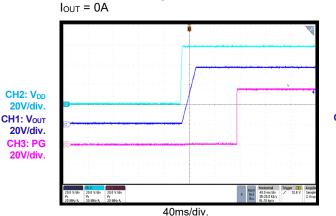

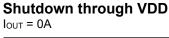

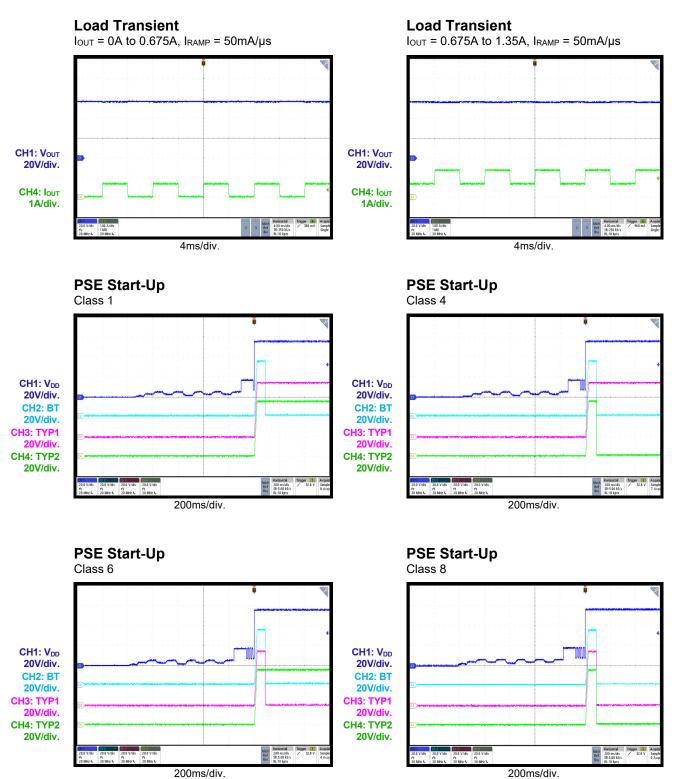

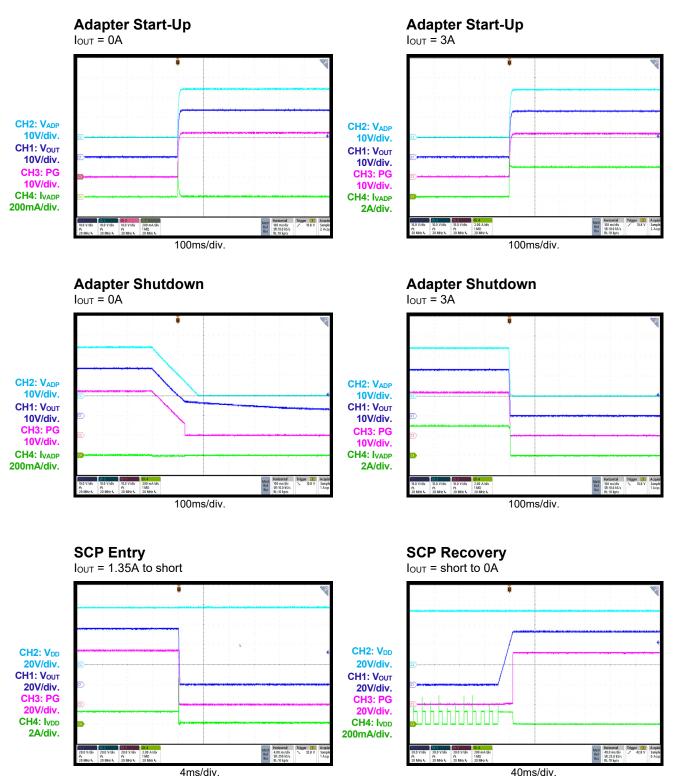

## **TYPICAL PERFORMANCE CHARACTERISTICS**

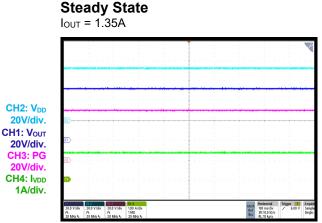

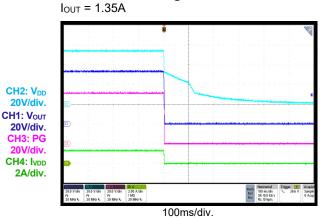

$V_{DD}$  = 54V,  $V_{ADP}$  = 24V,  $T_A$  = 25°C, unless otherwise noted.

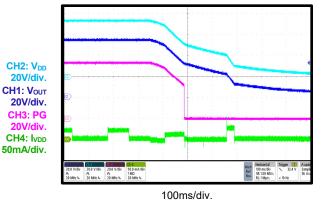

## Start-Up through VDD

100ms/div.

### Start-Up through VDD

## Shutdown through VDD

## TYPICAL PERFORMANCE CHARACTERISTICS (continued)

$V_{DD}$  = 54V,  $V_{ADP}$  = 24V,  $T_A$  = 25°C, unless otherwise noted.

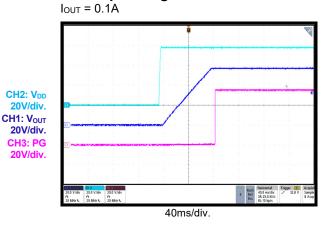

## **TYPICAL PERFORMANCE CHARACTERISTICS** (continued)

$V_{DD}$  = 54V,  $V_{ADP}$  = 24V,  $T_A$  = 25°C, unless otherwise noted.

40ms/div.

## FUNCTIONAL BLOCK DIAGRAM

Figure 1: Functional Block Diagram

## OPERATION

The MP8020 is an IEEE802.3af/at/bt-compliant, Power over Ethernet (PoE), powered device (PD). The device includes all the functions of IEEE 802.3af/at/bt, including detection, classification, input current ( $I_{IN}$ ) control, a 100V hot-swap MOSFET, and automatic maintain power signature functionality.

#### Detection

The MP8020 integrates an internal detection resistor. When the power-sourcing equipment

(PSE) applies two safe voltages between 2.7V and 10.1V to the MP8020, the MP8020 typically shows a  $25k\Omega$  resistance between the VDD and GND pins.

#### Classification

The PSE distributes power to the PDs based on the classification results. Classification mode is active between 14.5V and 20.5V. The MP8020 presents different currents in classification mode (see Table 1).

| PD<br>Class | Power<br>Rating (W) | Class Cycle with<br>Max Power | CLSA<br>Signature | CLSB<br>Signature | CLSA<br>Resistor | CLSB<br>Resistor |

|-------------|---------------------|-------------------------------|-------------------|-------------------|------------------|------------------|

| 0           | 0.44 to 12.95       | 1                             | 0                 | 0                 | 578              | 578              |

| 1           | 0.44 to 3.84        | 1                             | 1                 | 1                 | 110              | 110              |

| 2           | 3.84 to 6.49        | 1                             | 2                 | 2                 | 62               | 62               |

| 3           | 6.49 to 12.95       | 1                             | 3                 | 3                 | 41.2             | 41.2             |

| 4           | 12.95 to 25.5       | 2, 3                          | 4                 | 4                 | 28.7             | 28.7             |

| 5           | 25.5 to 40          | 4                             | 4                 | 0                 | 28.7             | 578              |

| 6           | 40 to 51            | 4                             | 4                 | 1                 | 28.7             | 110              |

| 7           | 51 to 62            | 5                             | 4                 | 2                 | 28.7             | 62               |

| 8           | 62 to 71.3          | 5                             | 4                 | 3                 | 28.7             | 41.2             |

Table 1: Different Classification Power Rating and Setting with the MP8020

IEEE802.3bt supports an 8-level class power rating, with up to 5 classification cycle operations. These classification cycles have the below functions:

- All PSEs perform one cycle classification for the class 0, class 1, class 2, and class 3 PDs.

- Type 2 PSEs perform 2-cycle classification if a class 4 signature is detected during the first class cycle.

- Type 3 and type 4 PSEs start their third cycle classification if a class 4 signature is detected during the first and second class-cycle. Based on the third cycle classification result, the Type 3 and Type 4 PSEs follow one of the operations listed below:

- If the third classification result is a class

4 signature, classification stops and there is a class 4 PD.

- If the third classification results in a class 0 or class 1 signature, the devices continue to the fourth cycle classification.

If the third classification result is class 2 or class 3 signature, the type 4 PSE performs a fourth and fifth cycle classification.

The MP8020 performs a class signature signal with the CLSA pin during the first and second class cycles. The device performs a class signature signal with the CLSB pin in the remaining class cycles, unless V<sub>DD</sub> drops to the mark event reset threshold.

Both CLSA and CLSB use the same output voltage ( $V_{OUT}$ ) for classification. The maximum output current ( $I_{OUT}$ ) is limited for self-protection.

# Under-Voltage Lockout (UVLO) and the Power Supply Voltage

The MP8020 integrates one under-voltage lockout (UVLO) circuit with a large hysteresis. The UVLO block ensures that the MP8020 starts up when  $V_{DD}$  exceeds 40V and shuts down when  $V_{DD}$  drops below 30V.

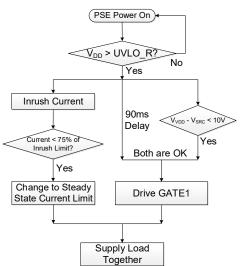

The MP8020 also has an inrush current limit function during start-up. This current is about 1/7 of the steady state current limit, which is configured by the ILIM pin.

#### Hot-Swap MOSFET and Current Limit

The MP8020 integrates one 100V MOSFET for output disconnect.

When the PD voltage is powered by the PSE and  $V_{DD}$  exceeds the UVLO turn-on threshold, the hot-swap MOSFET starts passing a limited current ( $I_{INRUSH}$ ) to charge the downstream DC/DC converter's input bulk capacitor. The inrush current limit function works until  $I_{INRUSH}$ drops below 75% of the inrush current limit, and then the current limit changes to the normal current limit threshold.

To meet different power ratings, the MP8020 supports current limit configuration via the ILIM pin. The ILIM pin sources a current after  $V_{DD}$  reaches the UVLO threshold. This current detects the configured current limit level. Table 2 shows the ILIM configurations.

**Table 2: ILIM Configurations**

| ILIM to GND Resistance (kΩ) |      |      | Current Limit |

|-----------------------------|------|------|---------------|

| Min Typ Max                 |      | Max  | (A)           |

| 0                           | 0    | 1.4  | 0.9           |

| 5.76                        | 7.15 | 9.09 | 1.6           |

The GATE1 pin can drive one external Nchannel MOSFET, which is connected in parallel with the internal  $0.35\Omega$  MOSFET. GATE1 turns on the external MOSFET after a delay time (t<sub>DELAY</sub>, 90ms) completes. If V<sub>DD</sub> -V<sub>SRC</sub> exceeds 10V after t<sub>DELAY</sub>, then over-current protection (OCP) is triggered and GATE1 does not turn on. If V<sub>SRC</sub> is below V<sub>DD</sub> by less than 10V, GATE1 turns on to charge the bulk capacitor. The MP8020 turns off the external MOSFET under light-load conditions.

The internal MOSFET and external MOSFET have different current limit control loops. The internal MOSFET current limit is configured by the ILIM pin, while the external MOSFET current limit is configured by a resistor ( $R_{SENSE}$ ) between the VDD and SENSE pins. To reduce additional power loss and cost, the external MOSFET current limit can be disabled by removing  $R_{SENSE}$  (connecting the SENSE pin to the VDD pin). It is typically recommended for  $R_{SENSE}$  to be  $18m\Omega$ . When an external  $18m\Omega$  $R_{SENSE}$  is used, it is recommended to connect the ILIM pin to GND for the lowest total current limit. Figure 2 shows the internal and external MOSFET start-up sequence.

#### Figure 2: Internal MOSFET and External MOSFET Start-Up Sequence

The internal and external MOSFETs have fastoff current protection in the event of short-circuit protection (SCP) being triggered. If this occurs, GATE1 turns off, the internal MOSFET recovers if  $V_{DD}$  -  $V_{SRC}$  < 10V.

If an overload event occurs when both the internal MOSFET and external MOSFET are connected, the current limit function can work in one of several ways:

- If the internal MOSFET triggers a current limit first, then the internal current is limited and additional current goes through the external MOSFET. If the external MOSFET also triggers the current limit, then the external MOSFET pulls GATE1 low and  $V_{\text{SRC}}$  drops. If  $V_{\text{DD}}$  -  $V_{\text{SRC}}$  exceeds 10V for 1ms, then the external MOSFET turns off and the internal MOSFET current limit switches to the inrush limit threshold. At the same time, PG pulls low to disable the downstream DC/DC converter, then begins a new start-up cycle with the inrush current limit. During this over-current (OC) condition, PG recovers without a 90ms delay after the inrush completes.

- If the external MOSFET triggers the current limit first, GATE1 pulls low, additional current goes through the internal MOSFET, and then triggers the internal current limit. After both current limits are triggered and

the device enters current foldback mode (reaches the inrush current limit),  $V_{SRC}$  drops. At the same time, PG is pulled low.

• If the internal MOSFET or external MOSFET triggers the fast-off current limit, the MP8020 quickly turns off the related MOSFET and then restarts with a delay.

#### Power Good (PG) and Delay

The MP8020 has one PG output to enable the downstream DC/DC converter after the inrush period finishes and the PSE is ready to provide high power. PG is an open-drain output with a voltage rating up to 100V.

PG goes to a high-impedance (Hi-Z) state when the device meets all of the following conditions:

- The device has changed to the steady current limit, which means that the inrush period is complete.

- The 90ms delay (t<sub>DELAY</sub>) from UVLO has completed.

- A wall power adapter is detected on AUX, and V<sub>ADP</sub> exceeds the UVLO threshold (see Figure 3).

The PG signal resets when the  $V_{DD}$  UVLO turnoff threshold ( $V_{DD_F}$ ) is triggered, overtemperature protection (OTP) occurs, or if  $V_{DD}$  - $V_{SRC} > 10V$  for more than 1ms. The 90ms timer only works after  $V_{DD}$  UVLO is triggered.

#### **PSE and Allocated Power Indicators**

IEEE802.3bt supports 4 different PSE power supplies. The BT, TYP1, and TYP2 pins indicate the PSE-allocated power type. Table 3 on page 19 shows the detailed power level indicators. Note that the indicator only displays high when it is in logic high and pulled up to a high voltage via an external pull-up resistor.

The TYP1, TYP2, and BT signals are active after a  $t_{DELAY}$  of 90ms (same as the PG signal). The outputs become inactive (high-impedance) when  $V_{DD}$  falls below its UVLO threshold, or if OTP is triggered. The BT, TYP1, and TYP2 signals are latched in the MP8020 after start-up and do not reset until  $V_{DD}$  drops to the mark event reset threshold.

If an adapter is detected, the TYP1 and TYP2 pins go low and BT goes high.

Table 4 on page 19 shows some power demotion cases.

Figure 3: PG Logic

|          | $ \begin{array}{ c c c c c c c } \hline Class 0 & 12.95W & & & & \\ \hline Class 1 & 3.84W & & 1 & & \\ \hline Class 2 & 6.49W & & 1 & & \\ \hline Class 3 & 12.95W & & & \\ \hline Class 4 & 25.5W & 2 & & \\ \hline Class 0 & 12.95W & & & \\ \hline Class 0 & 12.95W & & & \\ \hline Class 1 & 3.84W & & 1 & & \\ \hline Class 2 & 6.49W & & 1 & & \\ \hline Class 3 & 12.95W & & & \\ \hline Class 4 & 25.5W & & 2,3 & & \\ \hline Class 4 & 25.5W & & 2,3 & & \\ \hline Class 5 & 40W & & & \\ \hline \end{array} $ |                     |                        |       |       |       |  |

|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|------------------------|-------|-------|-------|--|

| PSE Type | PD Class                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | PSE Allocated Power | Number of Class Cycles | BT    | TYP1  | TYP2  |  |

|          | Class 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 12.95W              |                        |       |       |       |  |

| Type 1   | Class 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 3.84W               | 1                      | Lliab | Lliab | Lligh |  |

| Type 2   | Class 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 6.49W               | I                      | піgп  | підп  | підп  |  |

|          | Class 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 12.95W              |                        |       |       |       |  |

| Type 2   | Class 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 25.5W               | 2                      | High  | High  | Low   |  |

|          | Class 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 12.95W              |                        |       |       |       |  |

|          | Class 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 3.84W               | 1                      | Low   | Lliab | Lligh |  |

| Turne O  | Class 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 6.49W               | I                      | LOW   | підп  | підп  |  |

| Type 3   | Class 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 12.95W              |                        |       |       |       |  |

| Type 4   | Class 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 25.5W               | 2, 3                   | Low   | High  | Low   |  |

|          | Class 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 40W                 | 4                      | Low   | Low   | Lligh |  |

|          | Class 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 51W                 | 4                      | LOW   | LOW   | підп  |  |

| Tune 4   | Class 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 62W                 | 5                      | Low   | Low   |       |  |

| Type 4   | Class 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 71.3W               | 5                      | Low   | Low   | Low   |  |

Table 3: PSE and Allocated Power Indicator

Table 4: Power Demotion Cases

| PSE Type         | PD Class    | PSE Allocated Power | Number of Class Cycles | BT   | TYP1 | TYP2 |

|------------------|-------------|---------------------|------------------------|------|------|------|

| Type 2           | Class 4     | 12.95W              | 1                      | High | High | High |

| Type 3<br>Type 4 | Classes 4~8 | 12.95W              | 1                      | Low  | High | High |

| Type 3<br>Type 4 | Classes 5~8 | 25.5W               | 2, 3                   | Low  | High | Low  |

| Type 3<br>Type 4 | Classes 7~8 | 51W                 | 4                      | Low  | Low  | High |

#### **Automatic Maintain Power Signature**

To maintain the PSE power supply, the MP8020 supports automatic maintain power signature, and the current is configured by a resistor on the R\_MPS pin.

The MP8020 also has one DUTY pin to configure the R\_MPS pin's voltage duty cycle, which can compensate the effects of the long cable and bulk bus capacitors. After  $V_{DD}$  reaches the UVLO rising threshold, the DUTY pin sources one pulse current to detect the maintain power signature function duty cycle setting. Table 5 shows the DUTY pin's configuration options. Once  $V_{DD}$  falls to the VDD UVLO falling threshold, the DUTY signal resets.

Table 5: DUTY Configurations

| DUTY to GND Resistance (kΩ) |       |       | R_MPS Duty |

|-----------------------------|-------|-------|------------|

| Min                         | Тур   | Max   | Cycle (%)  |

| 0                           | 0     | 1.4   | 6          |

| 5.76                        | 7.15  | 9.09  | 11.5       |

| 17.4                        | Float | Float | 17         |

With type 1 and type 2 PSE inputs, the MP8020 generates a voltage on the R\_MPS pin with a fixed 37% duty cycle.

Wall Adapter Power Supply

For applications where an auxiliary power source such as a wall adapter is used to power the device, the MP8020 features wall power adapter detection. Once the adapter voltage  $(V_{ADP})$  exceeds about 8.3V, the MP8020 enables wall adapter detection.

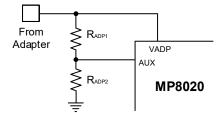

The resistor divider connected from VADP to AUX detects the adapter status. Once the AUX voltage exceeds the internal reference voltage, the MP8020 switches the power source from the PSE to the adapter if the adapter has higher priority.

GATE2 drives the external N-channel MOSFET and provides a smooth switch between the PSE and auxiliary wall adapter with less power loss than a traditional diode input. After the adapter supply is enabled, the PG signal is high, the TYP1 and TYP2 pins output low, and the BT pin remains high.

When PRI is high, pull AUX high to disable the DET, CLS, and maintain power signature functions. When PRI is low, pulling AUX high cannot disable DET, CLS, and maintain power signature functions.

If an adapter is available, the PG signal is pulled high under all conditions. If the adapter has a higher priority and replaces the PSE power supply, then BT, TYP1, and TYP2 are updated once the AUX and ADP\_UV signals are working. If the PSE has a higher priority and replaces the adapter supply, then the MP8020 changes the BT, TYP1, and TYP2 statuses to Hi-Z once PSE UVLO occurs. The statuses change to indicate the PSE power type after inrush is complete and the 90ms delay has finished.

#### **Power Priority**

The adapter is available when both AUX and  $V_{ADP}$  exceed the threshold. The MP8020 can source a current from the adapter or PSE if both the adapter and PSE are connected. This is determined by the PRI and AUX pin settings.

The PRI pin is internally pulled up to the internal VCC. If the PRI pin is floating (the adapter has higher priority) and  $V_{ADP}/AUX$  exceed their thresholds, the MP8020 disables the PSE power supply, and enables the adapter power source. If AUX is below its falling threshold, then the PSE supplies power to the output even when PRI is floating.

If the PRI pin is connected to GND, the PSE has the higher priority. Regardless of the AUX

signal, the PSE outputs power unless  $V_{DD}$  is below UVLO.

If the PSE has a higher priority and the adapter is connected before PSE plug-in, a reverse blocking MOSFET must be added to reverse block the power from the adapter during PoE detection and classification (see Figure 4). At the same time, the output downstream DC/DC converter should lower the power rating so that the inrush current charges the MP8020's output capacitor ( $C_{OUT}$ ) quickly. If  $C_{OUT}$  is not charged quickly, then the current limit is triggered and the device fails to start up.

Figure 4: Reverse Block Solution

#### **Thermal Protection**

Thermal shutdown prevents the IC from operating at exceedingly high temperatures. If the die temperature exceeds 150°C, the IC shuts down. Once the die temperature drops to 20°C, the device resumes normal operation.

## **APPLICATION INFORMATION**

#### Selecting a TVS Diode

To limit the input transient voltage within the absolute maximum ratings, a TVS diode should be placed across the rectified voltage (between VDD and GND). For general indoor applications, it is recommended to use an SMAJ58A diode. or one with an equivalent protection voltage. Outdoor transient levels and special applications typically require additional protection.

#### Selecting an Input Capacitor

A  $0.05\mu$ F to  $0.12\mu$ F input bypass capacitor must be placed from VDD to GND for IEEE 802.3bt standard specifications. A  $0.1\mu$ F, 100V ceramic capacitor is typically used.

# Selecting the Classification Resistors ( $R_{CLSA}$ and $R_{CLSB}$ )

Connect a resistor from CLSA and CLSB to GND to configure the classification current according to the IEEE 802.3bt standard. The assigned class power should correspond to the maximum average power drawn by the PD during operation. To select  $R_{CLSA}$  and  $R_{CLSB}$ , see Table 1 on page 16.

#### Wall Power Adapter Detection Circuit

The MP8020 features wall power adapter detection. Once  $V_{DD}$  (between VADP and GND) exceeds about 8.3V, the MP8020 enables wall adapter detection. At this point, the resistor divider from the VADP to AUX pin can configure the threshold to switch from the PSE to an adapter.

#### Figure 5: Wall Adapter Threshold Setting

#### **PG Pin Setting**

The PG pin is an active high, open-drain output that requires an external pull-up resistor. The PG pin's maximum sink current should be limited below 3mA. It is recommended to connect a  $20k\Omega$  to  $100k\Omega$  pull-up resistor from SRC to PG. Connect PG to the downstream

DC/DC converter's EN pin to enable the DC/DC converter.

PG goes to a high-impedance state if all of the following conditions are met:

- The steady current limit changes, which means the inrush period is complete.

- t<sub>DELAY</sub> of 90ms from UVLO is complete.

- The wall power adapter is detected on AUX, and V<sub>ADP</sub> exceeds the UVLO threshold.

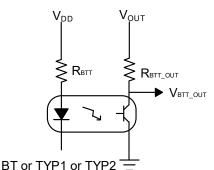

#### BT, TYP1, and TYP2 Indicator Connection

The BT, TYP1, and TYP2 pins are open-drain outputs that indicate the PSE type or the presence of a wall adapter. Optocouplers can interface these pins to circuitry on the converter's secondary side. Figure 6 shows the optocoupler interface design for the BT, TYP1, and TYP2 signals.

Figure 6: BT, TYP1, and TYP2 Interface

Where BT, TYP1, and TYP2 should have maximum sink currents of 3mA, and  $R_{BTT}$  should exceed 20k $\Omega$  to match the maximum 57V input.

When lighting an LED from VDD to BT/TYP1/TYP2 to indicate the PSE type, the resistance can be higher to match the LED's maximum current and reduce power loss.

#### **Configurable Current Limit**

After  $V_{DD}$  exceeds the UVLO threshold, the ILIM pin sources a current that detects the configurable current limit. By connecting ILIM to GND via a resistor (or shorting ILIM to GND), the MP8020's current limit can be configured to 1.6A or 0.9A (see Table 2 on page 17).

The MP8020 also has an inrush current limit function after start-up, which is about 1/7 of the steady state current limit.

#### Selecting the PoE Power MOSFET

The MP8020 internal hot-swap MOSFET has a maximum 1.6A current limit. For type 1, 2, and 3 PDs (≤51W), the internal hot-swap MOSFET is sufficient. For type 4 PDs (>51W), an external MOSFET must be placed in parallel with the internal hot-swap MOSFET. The GATE1 pin can drive one external N-channel MOSFET. The MOSFET should be selected to meet the following specifications:

- The voltage rating should be at least 100V for high-voltage surge environments.

- The on resistance  $(R_{DS(ON)})$  should be below 200m $\Omega$  for power dissipation and for light-load shutdown functions. A 100m $\Omega$   $R_{DS(ON)}$  is typically recommended.

- The gate charge  $(Q_G)$  should be as small as possible to provide faster response times under overload conditions. It is typically recommended for  $Q_G$  to be below 15nC  $(V_{GATE} = 4.5V)$ .

- The gate threshold voltage should be below 4V to fully drive the GATE1 and GATE2 voltages.

#### SENSE Pin Setting

The external parallel MOSFET current limit is configured by a resistor ( $R_{SENSE}$ ) between the VDD and SENSE pins. It is typically recommended for  $R_{SENSE}$  to be  $18m\Omega$ . The total current limit ( $I_{IN\_LIM}$ ) can be calculated using Equation (1):

$$I_{\text{IN}\_\text{LIM}} = I_{\text{INNER}} + \frac{26\text{mV}}{\text{R}_{\text{SENSE}}}$$

(1)

Where  $I_{IN\_LIM}$  is the PD current limit, and  $I_{INNER}$  is the MP8020 internal hot-swap MOSFET current limit.

When the external MOSFET is connected, it is recommended to set  $I_{\text{INNER}}$  to 0.9A.

#### Selecting the Adapter MOSFET

The GATE2 pin is designed to drive one external N-channel MOSFET for the adapter supply. Select the adapter MOSFET using the same guidelines as the PoE power MOSFET.

#### **Design Example**

Table 6 shows a design example following the application guidelines for the specifications below.

#### **Table 6: Design Example**

|     | •           | •    |

|-----|-------------|------|

| VDD | Class Level | VADP |

| 54V | Class 8     | 24V  |

For the detailed application schematic, see Figure 8 on page 24. For the typical performance and circuit waveforms, see the Typical Performance Characteristics section on page 12. For more device applications, refer to the related evaluation board datasheet.

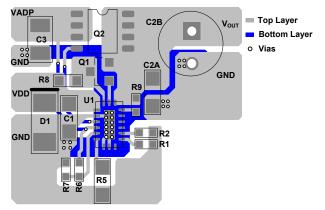

#### **PCB Layout Guidelines**

Efficient PCB layout is critical. Poor layout may result in reduced performance, resistive loss, and system instability. To ensure an optimal layout design, refer to Figure 7 and follow the guidelines below:

- 1. Ensure that all power connections are as short as possible with wide traces.

- 2. Place the current-sense resistor (R8) as close to the VDD pin as possible.

- 3. Use a Kelvin connection between the SENSE pin and R8 for an accurate current limit.

- 4. Place the PoE input capacitor as close to the VDD pin as possible.

- 5. Place the adapter's input capacitor as close to the VADP pin as possible.

- 6. Place the SRC capacitor as close to the SRC pin as possible.

7. Place a wide copper plane and vias under the MP8020, PoE power MOSFET, and adapter MOSFET to improve thermal performance.

Figure 7: Recommended PCB Layout <sup>(8)</sup>

Note:

8) Figure 7 is based on the Typical Application Circuit (see Figure 8 on page 24).

## **TYPICAL APPLICATION CIRCUIT**

Figure 8: Class-8 PD Solution with PSE and Adapter Supplies

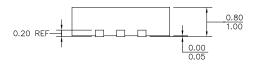

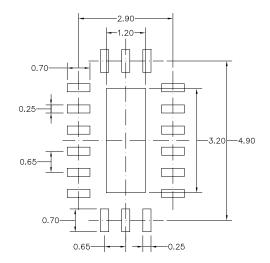

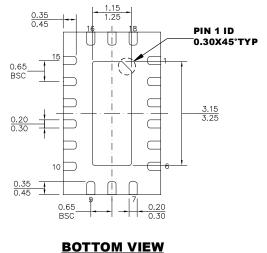

## **PACKAGE INFORMATION**

TOP VIEW

**SIDE VIEW**

#### **RECOMMENDED LAND PATTERN**

#### QFN-18 (3mmx5mm)

NOTE:

1) ALL DIMENSIONS ARE IN MILLIMETERS. 2) EXPOSED PADDLE SIZE DOES NOT INCLUDE MOLD FLASH.

3) LEAD COPLANARITY SHALL BE 0.08

MILLIMETERS MAX.

4) JEDEC REFERENCE IS MO-220.

5) DRAWING IS NOT TO SCALE.

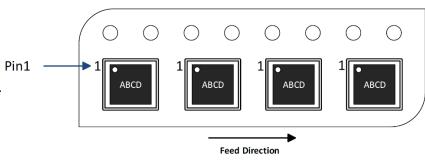

## **CARRIER INFORMATION**

| Part Number | Package             | Quantity/ | Quantity/ | Quantity/ | Reel     | Carrier    | Carrier    |

|-------------|---------------------|-----------|-----------|-----------|----------|------------|------------|

|             | Description         | Reel      | Tube      | Tray      | Diameter | Tape Width | Tape Pitch |

| MP8020GQV-Z | QFN-18<br>(3mmx5mm) | 5000      | N/A       | N/A       | 13in     | 12mm       | 8mm        |

## **REVISION HISTORY**

| Revision # | <b>Revision Date</b> | Description     | Pages Updated |

|------------|----------------------|-----------------|---------------|

| 1.0        | 2/17/2022            | Initial Release | -             |

**Notice:** The information in this document is subject to change without notice. Users should warrant and guarantee that thirdparty Intellectual Property rights are not infringed upon when integrating MPS products into any application. MPS will not assume any legal responsibility for any said applications.

# **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Power Switch ICs - POE/LAN category:

Click to view products by Monolithic Power Systems manufacturer:

Other Similar products are found below :

WC-PD30B120A MP8007HGV-Z SI34061-A-GMR PD70100ILD-TR MP3924GU-Z MP8020GQV-Z TPS23730RMTR TPS23882B1RTQR SI3471A-A01-IM TPS23861PWR Si3462-E01-GMR PD69101ILQ-TR PD69104B1ILQ-TR LTC4263CDE#TRPBF LTC4266IUHF#PBF LTC4269IDKD-1#PBF TPS2373-4RGWR MP8008GV-P TPS2388RTQT TPS2388RTQR LT4276BHUFD#PBF TPS2372-4RGWR LTC4257CS8-1#PBF 3244672 LTC4267CGN#PBF PI3L2500ZHEX PD69208T4ILQ-TR-LE PD69208MILQ-TR-LE PD70200ILD-TR SI3454-B01-IM MAX5969AETB+T MAX5980GTJ+T PD69201ILD-TR PD70101ILQ-TR PD70201ILQ-TR PD70210ILD-TR KTA1137AEUAB-TR PD70210AILD-TR MP8001DS-LF-Z MP8007GV-P MP8007GV-Z MP8008GV-Z SI3404-A-GMR PD70211ILQ-TR SI34061-A-GM Si34071-A01-GM Si3462-E01-GM Si3471A-A01-IM Si3471A-A01-IMR Si3474A-A01-IM