# High Effective Capacitance & High Ripple Current Chip Multilayer Ceramic Capacitors for General Purpose GR355XD72J224KW05\_ (2220, X7T:EIA, 0.22uF, DC630V)

: packaging code

# **Reference Sheet**

## 1.Scope

This product specification is applied to High Effective Capacitance & High Ripple Current Chip Multilayer Ceramic Capacitors used for General Electronic equipment. Do not use these products in any automotive power train or safety equipment including battery chargers for electric vehicles and plugin hybrids.

# 2.MURATA Part NO. System

# 3. Type & Dimensions

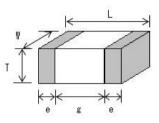

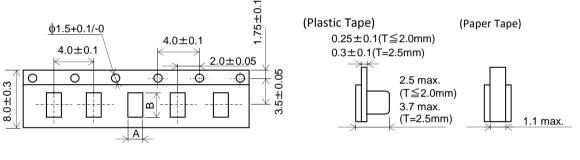

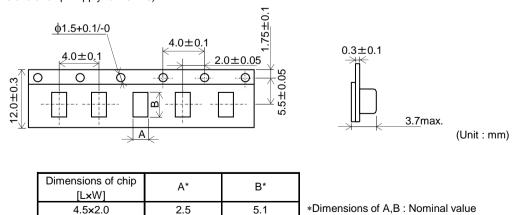

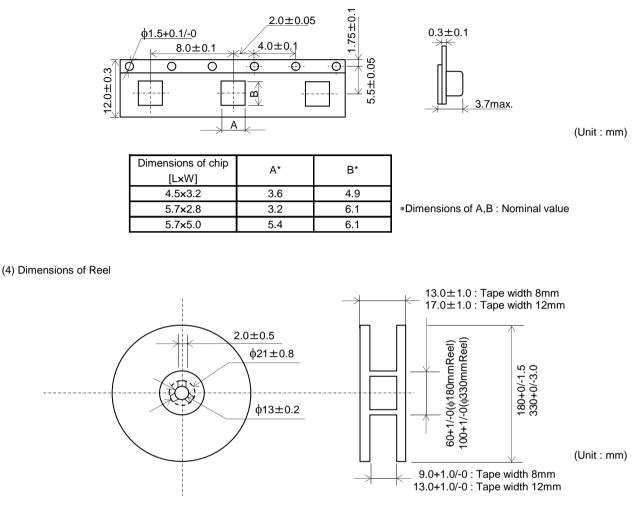

|         |         |            |          | (Unit:mm) |

|---------|---------|------------|----------|-----------|

| (1)-1 L | (1)-2 W | (2) T      | e        | g         |

| 5.7±0.4 | 5.0±0.4 | 2.7+0/-0.3 | 0.3 min. | 3.0 min.  |

## 4.Rated value

|   | () [                          | e Characteristics<br>ode):X7T(EIA) | (4)<br>Rated | (5) Nominal | (6)<br>Capacitance | Specifications and Test<br>Methods |

|---|-------------------------------|------------------------------------|--------------|-------------|--------------------|------------------------------------|

| ſ | Temp. coeff<br>or Cap. Change | Temp. Range<br>(Ref.Temp.)         | Voltage      | Capacitance | Tolerance          | (Operating<br>Temp. Range)         |

|   | -33 to 22 %                   | -55 to 125 ℃<br>(25 ℃)             | DC 630 V     | 0.22 uF     | ±10 %              | -55 to 125 °C                      |

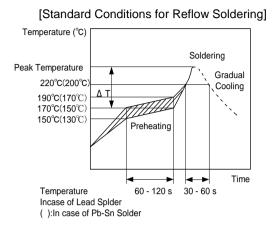

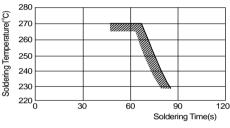

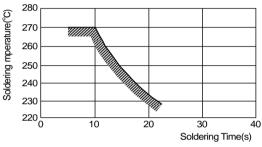

# Soldering Method

Reflow

## 5.Package

| mark | (8) Packaging                 | Packaging Unit |

|------|-------------------------------|----------------|

| L    | φ180mm Reel<br>EMBOSSED W12P8 | 500 pcs./Reel  |

Product specifications in this catalog are as of Sep.28,2018,and are subject to change or obsolescence without notice. Please consult the approval sheet before ordering.

Please read rating and !Cautions first.

# ■ Specifications and Test Methods

| No | Iter                                             | n                             | Specification                                                                          | Test Method<br>(Ref. Standard:JIS C 5101, IEC60384)                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|----|--------------------------------------------------|-------------------------------|----------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1  | Appearance                                       |                               | No defects or abnormalities.                                                           | Visual inspection.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 2  | Dimension                                        |                               | Within the specified dimensions.                                                       | Using calipers and micrometers.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 3  | Voltage proof                                    | ince(I.R.)                    | No defects or abnormalities.<br>More than 10000 MΩ or 100 MΩ•μF (Whichever is smaller) | Measurement Point       :       Between the terminations         Test Voltage       :       DC756V(120% of the rated voltage)         Applied Time       :       1 to 5 s         Charge/discharge current       :       50mA max.         Measurement Point       :       Between the terminations         Measurement Voltage       :       DC500+/-50V         Charging Time       :       60+/-5s         Measurement Temperature:       Room Temperature                                                              |

| 5  | Capacitance                                      |                               | Shown in Rated value.                                                                  | Measurement Temperature: Room Temperature<br>Measurement Frequency :1.0+/-0.1kHz                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 6  | Dissipation Facto                                | or (D.F.)                     | 0.01 max.                                                                              | Measurement Voltage AC1.0+/-0.2V(r.m.s.)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 7  | Temperature<br>Characteristics<br>of Capacitance |                               | D7 : Within +22/-33% (-55°C to +125°C)                                                 | The capacitance change should be measured after 5 min.<br>at each specified temp. stage.<br>Capacitance value as a reference is the value in step 3.<br>Step       Temperature(°C)         1       Reference Temp.+/-2         2       Min.Operating Temp. +/-3         3       Reference Temp. +/-2         4       Max.Operating Temp. +/-3         5       Reference Temp. +/-2         ·Pretreatment         Perform a heat treatment at 150+0/-10°C for 1h+/-5min and then<br>let sit for 24+/-2h at room condition*. |

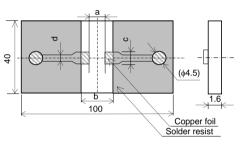

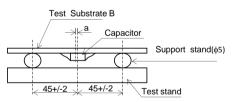

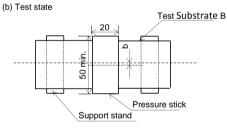

| 8  | Vibration                                        | Appearance                    | No defects or abnormalities.                                                           | Solder the capacitor on the test substrate A shown in "Complement of Test method".                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|    |                                                  | Capacitance                   | Within the specified initial value.                                                    | Kind of Vibration       :       A simple harmonic motion         10Hz to 55Hz to 10Hz (1min)         Total amplitude       :       1.5mm                                                                                                                                                                                                                                                                                                                                                                                   |

|    |                                                  | D.F.                          | Within the specified initial value.                                                    | This motion should be applied for a period of 2h in each 3 mutually perpendicular directions(total of 6h).                                                                                                                                                                                                                                                                                                                                                                                                                 |

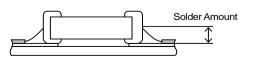

| 9  | Solderability                                    |                               | 95% of the terminations is to be soldered evenly and continuously.                     | Test Method       :       Solder bath method         Flux       :       Solution of rosin ethanol 25(wt)%         Preheat       :       80°C to 120°C for 10s to 30s         Solder       :       Sn-3.0Ag-0.5Cu (Lead Free Solder)         Solder Temp.       :       245+/-5°C         Immersion time       :       2+/-0.5s         Immersing in speed       :       25+/-2.5mm/s.                                                                                                                                      |

| 10 | Resistance<br>to                                 | Appearance                    | No defects or abnormalities.                                                           | Test Method         :         Solder bath method           Solder         :         Sn-3.0Ag-0.5Cu (Lead Free Solder)                                                                                                                                                                                                                                                                                                                                                                                                      |

|    | Soldering<br>Heat                                | Capacitance<br>Change<br>D.F. | Within +/-10%<br>Within the specified initial value.                                   | Solder Temp.       :       260+/-5°C         Immersion time       :       10+/-1s         Immersing in speed       :       25+/-2.5mm/s.         Exposure Time       :       24+/-2h at room condition*.                                                                                                                                                                                                                                                                                                                   |

|    |                                                  | I.R.                          | Within the specified initial value.                                                    | Exposure Time       : 24+/-2h at room condition*.         Preheat       : GR331 size max.: 120°C to 150°C for 1 min         GR332 size min. : 100°C to 120°C for 1 min         and 170°C to 200°C for 1 min                                                                                                                                                                                                                                                                                                                |

|    |                                                  | Voltage proof                 | No defects.                                                                            | •Pretreatment<br>Perform a heat treatment at 150+0/-10°C for 1h+/-5min and then<br>let sit for 24+/-2h at room condition*.                                                                                                                                                                                                                                                                                                                                                                                                 |

\*Room Condition : Temperature:15 to 35°C, Relative humidity:45 to 75%, Atmosphere pressure:86 to 106kPa

| of Termination     should occur.     method?.       12     Substrate     Appearance     No defects or abnormalities.     Solder the squark or on the test substrate and capacitor side.       12     Substrate     Appearance     No defects or abnormalities.     Solder the squark or on the test substrate and capacitor side.       13     Temperature Change     Within +/-12.5%     First the capacitor to the substrate A (gla show soldering)       14     Temperature Appearance     No defects or abnormalities.     First the capacitor to the substrate A (gla show soldering)       14     High     Capacitance Change     Within the specified initial value.     First the capacitor to the substrate A (gla show soldering)       14     High     Appearance     No defects.     First the capacitor to the substrate A (gla show in the 5 cycles acculting to the four heat treatment show in the 5 cycles acculting to the four heat treatment show in the 5 cycles acculting to the four heat treatment show in the 5 cycles acculting to the four heat treatment show in the 5 cycles acculting to the four heat treatment show in the 5 cycles acculting to the four heat treatment show in the 5 cycles acculting to the four heat treatment at four show in the show in the 5 cycles acculting to the four heat treatment show in the 5 cycles acculting the four heat treatment at four show in the show in t                                                                                                                                                                                                                                                                                                                                                       | of Termination | should occur.                                                                                                                                                           | meth                                                 |                                                                           | Test Method<br>(Ref. Standard:JIS C 5101, IEC60384) |                 |                   |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|---------------------------------------------------------------------------|-----------------------------------------------------|-----------------|-------------------|

| 12         Substrate<br>Bending test         Appearance<br>Capacitance<br>Change         No defects or abnormalities.         Substrate<br>Bending test         Appearance<br>Capacitance<br>Change         No defects or abnormalities.           13         Temperature<br>Sudier Change         No defects or abnormalities.         Substrate<br>Bending test of "Complement of Test method".           13         Temperature<br>Sudier Change         No defects or abnormalities.         Substrate<br>Capacitance         No defects or abnormalities.           13         Temperature<br>Sudier Change         No defects or abnormalities.         Fix the capacitor to the supporting Test substrate A (glis<br>shown in "Complement of Test method".           14         High<br>Temperature<br>Sudier Change         Within +         No defects.         Time<br>test method".           14         High<br>Temperature<br>Fight<br>Humidity<br>(Steady)         No defects or abnormalities.         Fix the capacitor to the supporting Test substrate A (glis<br>shown in "Complement at 150+0/-10*C for th+/-Snin<br>test test 24+/-2h at room condition".           14         High<br>Temperature<br>Humidity<br>(Steady)         No defects or abnormalities.         Fix the capacitor to the supporting Test substrate A (glis<br>shown in "Complement at 150+0/-10*C for th+/-Snin<br>test test 24+/-2h at room condition".           14         High<br>Temperature<br>Humidity<br>(Steady)         No defects or abnormalities.         Fix the capacitor to the supporting Test substrate A (glis<br>shown in "Complement of Test method".           15         Durabi                                                                                                                                                                                                                                                                                                                                                                                                     | Substrate      |                                                                                                                                                                         |                                                      | Solder the capacitor on the test substrate A shown in "Complement of Test |                                                     |                 | mplement of Test  |

| Image: 10 - 10 - 10 - 10 - 10 - 10 - 10 - 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                | nce No defects or abnormalities.                                                                                                                                        | Appl                                                 | 100".                                                                     |                                                     |                 |                   |

| Image: 10 - 10 - 10 - 10 - 10 - 10 - 10 - 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                | nce No defects or abnormalities.                                                                                                                                        | Appl                                                 | G                                                                         |                                                     |                 |                   |

| Image: space of the s |                | nce No defects or abnormalities.                                                                                                                                        | Appl                                                 |                                                                           |                                                     |                 |                   |

| Image: space of the s |                | nce No defects or abnormalities.                                                                                                                                        | Appl                                                 |                                                                           |                                                     |                 |                   |

| 12         Substrate<br>Bending test         Appearance         No defects or abnormalities.         Solder the capacitor on the test substrate B shown in "Complement of Complement Complement of Complement of Co                                   |                | nce No defects or abnormalities.                                                                                                                                        |                                                      | lied Direc                                                                |                                                     | bstrate and ve  | ertical with the  |

| Bending test         Image: Capacitance Change         Within +/-12.5%         method'.           13         Temperature Sudden Change         Appearance         No defects or abnormalities.         Fix the capacitor to the supporting Test substrate A (gls shown in "Complement of Test method".           13         Temperature Sudden Change         Appearance         No defects or abnormalities.         Fix the capacitor to the supporting Test substrate A (gls shown in "Complement of Test method".           14         Temperature Change         Appearance         Within +/-7.5%         Fix the capacitor to the supporting Test substrate A (gls shown in "Complement of Test method".           14         High         Temperature High         No defects.         Perform the 5 cycles according to the four heat treatment shown in the following table.           14         High         Appearance         No defects.         Perform a heat treatment at 150+0/-10°C for 1h+/-5min let sit for 24+/-2h at room condition".           14         High         Appearance         No defects or abnormalities.         Fix the capacitor to the supporting Test substrate A (gls shown in "Complement of Test method".           14         High         Capacitance         Within +/-12.5%         Fix the capacitor to the supporting Test substrate A (gls shown in "Complement of Test method".           14         High         Capacitance         Within +/-12.5%         Fix the capacitor to the supporting Tes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                |                                                                                                                                                                         | Sold                                                 | ler the ca                                                                |                                                     | shown in "Cor   | nolement of Test  |

| Image: Capacitance Change         Within +/-12.5%         Bending test* of "Complement of Test method".<br>Flexure : 2mm           13         Temperature Sudden Change         Appearance         No defects or abnormalities.         Fix the capacitor to the supporting Test substrate A (gla shown in the following table.           13         Temperature Sudden Change         Appearance         No defects or abnormalities.         Fix the capacitor to the supporting Test substrate A (gla shown in the following table.           14         Temperature High         No defects.         Temperature IT.R.         Within +/-7.5%           14         High         Appearance         No defects.         Temperature IT.R.           14         High         Appearance         No defects.         -Pretreatment Perform the solution to the substrate A (gla shown in 'Complement of Test method'.           14         High         Appearance         No defects or abnormalities.         -Pretreatment Perform a heat treatment at 150+0/-10°C for 1h+/-5min let sit for 24+/-2h at room condition*.           14         High         Appearance         No defects or abnormalities.         Fix the capacitor to the supporting Test substrate A (gla shown in 'Complement of Test method'.           14         High         Appearance         No defects or abnormalities.         Fix the capacitor to the supporting Test substrate A (gla shown in 'Complement of Test method'.           14 <t< td=""><td></td><td></td><td></td><td></td><td></td><td></td><td>inplement of Test</td></t<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                |                                                                                                                                                                         |                                                      |                                                                           |                                                     |                 | inplement of Test |

| Image: Change         Change         Flexure         2 mm<br>Holding Time         2 mm<br>Soldering           13         Temperature<br>Suden Change         Appearance         No defects or abnormalities.         Fix the capacitor to the supporting Test substrate A (gla<br>shown in "Complement of Test method".           13         Temperature<br>Suden Change         Appearance         No defects or abnormalities.         Fix the capacitor to the supporting Test substrate A (gla<br>shown in "Complement of Test method".           14         Fix         Temperature<br>(Tange)         Within +/-7.5%         Temperature<br>(Tange)         Step         Temperature<br>(Tange)           1         Mr.Operating Temp-40:4         304:-3<br>3         Temperature<br>(Tange)         Step         Step         Step         Step         Step         Step         Step                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                |                                                                                                                                                                         |                                                      |                                                                           |                                                     |                 | d of Substrate    |

| Image: Sude Change Figure 1         Appearance 2         No defects or abnormalities.         Fix the capacitor to the supporting Test substrate A (gla shown in "Complement of Test method".           13         Temperature Suden Change 2         Within +/-7.5%.         Fix the capacitor to the supporting Test substrate A (gla shown in "Complement of Test method".           14         Gapacitance Change 2         Within the specified initial value.         Step Immp. (C)         Immp. (C)           17.         Within the specified initial value.         Step Immp. (C)         Immp. (C)         Immp. (C)           18.         Within the specified initial value.         Step Immp. (C)         Immp. (C)         Immp. (C)           19.         I.R.         Within the specified initial value.         Step Immp. (C)         Immp. (C)         Immp. (C)           10.         No defects.         -Pretreatment         Fix the capacitor to the supporting Test substrate A (gla shown in "Complement of Test method".           14         High Temperature High High         Appearance Appapearance Appearance Appearance Appearance Appapea                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                | nce Within +/-12.5%                                                                                                                                                     |                                                      | •                                                                         | •                                                   | od".            |                   |

| 13         Temperature<br>Sudden Change         Appearance<br>Appearance         No defects or abnormalities.         Fix the capacitor to the supporting Test substrate A (gla<br>shown in "Complement of Test method".<br>Perform the 5 cycles according to the four heat treatment<br>shown in the following table.           13         Temperature<br>Sudden Change         Within +/-7.5%         Fix the capacitor to the supporting Test substrate A (gla<br>shown in "Complement of Test method".<br>Perform the 5 cycles according to the four heat treatment<br>shown in the following table.           14         Fix the capacitor to the supporting Test substrate A (gla<br>shown in "Complement of Test method".         Test Temperature<br>High<br>Humidity<br>(Steady)         Appearance<br>Capacitance<br>(Change         No defects or abnormalities.         Fix the capacitor to the supporting Test substrate A (gla<br>shown in "Complement of Test method".           14         High<br>Humidity<br>(Steady)         Appearance<br>Change         No defects or abnormalities.         Fix the capacitor to the supporting Test substrate A (gla<br>shown in "Complement of Test method".           15         Durability         Appearance<br>Voltage proof         No defects or abnormalities.         Fix the capacitor to the supporting Test substrate A (gla<br>shown in "Complement of Test method".           15         Durability         Appearance<br>Capacitance         No defects or abnormalities.         Fix the capacitor to the supporting Test substrate A (gla<br>shown in "Complement of Test method".           15         Durability         Appearance<br>Capacitance         No defects or abnormalities.                                                                                                                                                                                                                                                                                                                                      |                |                                                                                                                                                                         |                                                      |                                                                           |                                                     |                 |                   |

| Suden Change         shown in "Complement of Test method".<br>Perform the 5 cycles according to the four heat treatmethod.<br>Perform the 5 cycles according to the four heat treatmethod.<br>Temp. (C)         Sum in the following table.           D.F.         Within the specified initial value.         Step Temp. (C)         Temp. (C)           I.R.         Within the specified initial value.         Step Temp. (C)         Temp. (C)           Voltage proof         No defects.         Perform the 5 cycles according to the four heat treatment at 150+0/-10°C for 1h+/-5min let sit for 24+/-2h at room condition*.           14         High Temperature High         Appearance         No defects or abnormalities.         First the capacitor to the supporting Test substrate A (gla shown in *Complement of Test method".           15         Durability         Appearance         No defects or abnormalities.         First the capacitor to the supporting Test substrate A (gla shown in *Complement of Test method".           15         Durability         Appearance         No defects.         Pertereatment Apply test voltage for 1h+/-5min at test temperature.           16         Durability         Appearance         No defects.         First the capacitor to the supporting Test substrate A (gla shown in *Complement of Test method".           17         D.F.         0.02 max.         First the capacitor to the supporting Test substrate A (gla shown in *Complement of Test method".           16         Durability                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                |                                                                                                                                                                         | Sold                                                 | lering Me                                                                 | thod : Reflow soldering                             | g               |                   |

| Image: Construction of the specified in the specified initial value.         Perform the 5 cycles according to the four heat treatment shown in the following table.           Image: Change         Within the specified initial value.         Stown in the following table.           D.F.         Within the specified initial value.         Stown in the following table.           I.R.         Within the specified initial value.         Stown remp. +0/-3         30/+3           I.R.         Within the specified initial value.         Exposure Time         : 24+/-2h at room condition*.           Voltage proof         No defects.         Pretreatment         Perform a heat treatment at 150+0/-10°C for 1h+/-5min let sit for 24+/-2h at room condition*.           14         High         Appearance         No defects or abnormalities.         Fix the capacitor to the supporting Test substrate A (gla shown in "Complement of Test method".           Humidity         Capacitance         Within +/-12.5%         Test Temperature         : 40+1-2°C           Humidity         Capacitance         Within +/-12.5%         Test Time         : 200-200/CR Rated Voltage           D.F.         0.02 max.         Exposure Time         : 24+/-2h at room condition*.           I.R.         More than 1000 MΩ or 10 MΩ-µF (Whichever is smaller)         ·Pretreatment           ·Pretreatment         Applied Voltage for 1h+/-5min at test temperature. <td>Temperature</td> <td>nce No defects or abnormalities.</td> <td>Fix t</td> <td>he capac</td> <td>itor to the supporting Test subs</td> <td>strate A (glass</td> <td>epoxy board)</td>                                                                                                                                                                                                                                                                                                                                                                                                                    | Temperature    | nce No defects or abnormalities.                                                                                                                                        | Fix t                                                | he capac                                                                  | itor to the supporting Test subs                    | strate A (glass | epoxy board)      |

| Image: Capacitance Change         Within +/-7.5%         shown in the following table.           D.F.         Within the specified initial value.         Step         Tamp. (*C)         Time           I.R.         Within the specified initial value.         3 Max.Operating Temp.+3/-0         3 0/+3           I.R.         Within the specified initial value.         Exposure Time         2 4/+2 h at room condition*.           Voltage proof         No defects.         Perform a heat treatment at 150+0/-10*C for 1h+/-5min let st for 24+/-2h at room condition*.           14         High         Appearance         No defects or abnormalities.         Perform a heat treatment at 150+0/-10*C for 1h+/-5min let st for 24+/-2h at room condition*.           14         High         Capacitance Within +/-12.5%         Test Temperature         40+2/2 C           Humidity         Capacitance Uithin +/-12.5%         Test Temperature : 40+/-2/C         40+2/2 C           LR.         More than 1000 MΩ or 10 MΩ+µF (Whichever is smaller)         ·Pretreatment Applied Voltage : DC630V(DC Rated Voltage Exposure Time : 24+/-2h at room condition*.           15         Durability         Appearance No defects or abnormalities.         Fix the capacitor to the supporting Test substrate A (gla shown in "Complement of Test method".           15         Durability         Appearance No defects or abnormalities.         Fix the capacitor to the supporting Test substrate A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Sudden Change  |                                                                                                                                                                         |                                                      |                                                                           |                                                     |                 |                   |

| Image         Step         Temp.(*C)         Time (min)           D.F.         Within the specified initial value.         Image: Step (min)         Image: S                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                | nce Within +/-7.5%                                                                                                                                                      |                                                      |                                                                           |                                                     | eat treatments  | 5                 |

| 1         Mm.Operating Temp.+4/-3         30+/-3           D.F.         Within the specified initial value.         1         Mm.Operating Temp.+4/-3         30+/-3           1         Room Temp         2 to 3         3         Max.Operating Temp.+4/-3         30+/-3           1         Room Temp         2 to 3         Max.Operating Temp.+3/-0         30+/-3         3           1.R.         Within the specified initial value.         Exposure Time         :         24+/-2h at room condition*.           Voltage proof         No defects.         -Pretreatment         Perform a heat treatment at 150+0/-10°C for 1h+/-5min let sit for 24+/-2h at room condition*.           14         High         Appearance         No defects or abnormalities.         -Pretreatment           Temperature         Humidity         Capacitance         Within +/-12.5%         Test Temperature         : 40+/-2°C           Humidity         D.F.         0.02 max.         Applied Voltage         : D0C630V(IC Rated Voltage Fxposure Time         : 24+/-2h at room condition*.           15         Durability         Appearance         No defects.         Fix the capacitor to the supporting Test substrate A (gla shown in "Complement of Test method".           15         Durability         Appearance         No defects.         Remove and let sit for 24+/-2h at room condit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                |                                                                                                                                                                         |                                                      | <b></b>                                                                   | _                                                   |                 | 1                 |

| 14       High<br>Temperature<br>High<br>Voltage proof       No defects.         14       High<br>Temperature<br>High<br>Ustage       Appearance<br>Capacitance<br>No defects.       No defects.         14       High<br>Temperature<br>High<br>Humidity<br>(Steady)       Appearance<br>No defects or abnormalities.       Fix the capacitor to the supporting Test substrate A (gla<br>shown in "Complement of Test method".         14       High<br>Temperature<br>Humidity<br>(Steady)       Appearance<br>No defects or abnormalities.       Fix the capacitor to the supporting Test substrate A (gla<br>shown in "Complement of Test method".         14       High<br>Temperature<br>Humidity<br>(Steady)       Appearance<br>No defects or abnormalities.       Fix the capacitor to the supporting Test substrate A (gla<br>shown in "Complement of Test method".         15       D.F.       0.02 max.       D.F.       0.02 max.         16.       More than 1000 MΩ or 10 MΩ*µF (Whichever is smaller)       ·Pretreatment<br>Applied Voltage for 1h+/-5min at test temperature.         15       Durability       Appearance<br>No defects.       No defects.       Fix the capacitor to the supporting Test substrate A (gla<br>shown in "Complement of Test method".         15       Durability       Appearance<br>Capacitance<br>Change       No defects or abnormalities.       Fix the capacitor to the supporting Test substrate A (gla<br>shown in "Complement of Test method".         15       Durability       Appearance<br>Change       No defects or abnormalities.       Fix the capacitor to the supporting Test                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                |                                                                                                                                                                         |                                                      | -                                                                         |                                                     |                 |                   |

| I.R.         Within the specified initial value.         4         Room Temp         2 to 3           Voltage proof         No defects.         Exposure Time         : 24+/-2h at room condition*.           14         High         Appearance         No defects.         ·Pretreatment           14         High         Appearance         No defects or abnormalities.         ·Fix the capacitor to the supporting Test substrate A (gla shown in "Complement of Test method".           14         High         Appearance         Within +/-12.5%         Test Furnidity         : 90% to 55% RH           (Steady)         D.F.         0.02 max.         O.02 max.         Applied Voltage         : DC630V(DC Rated Voltage Exposure Time           15         Durability         Appearance         No defects or abnormalities.         Fix the capacitor to the supporting Test substrate A (gla shown in "Complement of Test method".           15         Durability         Appearance         No defects.         Perfectation*.           15         Durability         Appearance         No defects or abnormalities.         Fix the capacitor to the supporting Test substrate A (gla shown in "Complement of Test method".           15         Durability         Appearance         No defects.         Remove and let sit for 24+/-2h at room condition*.           15         Durability         A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                | Within the specified initial value.                                                                                                                                     |                                                      | 2                                                                         | Room Temp                                           | 2 to 3          |                   |

| I.R.       Within the specified initial value.       Exposure Time       :       24+/-2h at room condition*.         Voltage proof       No defects.       ·Pretreatment       Perform a heat treatment at 150+0/-10°C for 1h+/-5min let sit for 24+/-2h at room condition*.         14       High       Appearance       No defects or abnormalities.       Fix the capacitor to the supporting Test substrate A (gla shown in "Complement of Test method".         14       High       Capacitance       Within +/-12.5%       Test Temperature       :         Humidity       Change       0.02 max.       Test Temperature       :       90% to 95% RH         18.       D.F.       0.02 max.       O.02 max.       Pretreatment       Applied Voltage       :       DC630V(DC Rated Voltage         19.       D.F.       0.02 max.       Pretreatment       Applied Voltage       :       24+/-2h at room condition*.         118.       More than 1000 MΩ or 10 MΩ·μF (Whichever is smaller)       ·Pretreatment       Apply test voltage for 1h+/-5min at test temperature.         15.       Durability       Appearance       No defects or abnormalities.       Fix the capacitor to the supporting Test substrate A (gla shown in "Complement of Test method".         15.       Durability       Appearance       No defects or abnormalities.       Fix the capacitor to the supporting Test substrate A (gla show                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                |                                                                                                                                                                         |                                                      | 3                                                                         | Max.Operating Temp.+3/-0                            | 30+/-3          |                   |

| 14         High<br>Temperature<br>High<br>(Steady)         Appearance<br>No defects.         No defects.         Pretreatment<br>Perform a heat treatment at 150+0/-10°C for 1h+/-5min<br>let sit for 24+/-2h at room condition*.           14         High<br>Temperature<br>High<br>(Steady)         Appearance<br>Capacitance<br>No defects or abnormalities.         No defects or abnormalities.         Fix the capacitor to the supporting Test substrate A (gla<br>shown in "Complement of Test method".           15         D.F.         0.02 max.         D.F.         0.02 max.           17         No defects.         Pretreatment<br>Applied Voltage         Pretreatment<br>= 24+/-2h at room condition*.           15         Durability         Appearance<br>Change         No defects or abnormalities.         Fix the capacitor to the supporting Test substrate A (gla<br>shown in "Complement of Test method".           15         Durability         Appearance<br>Capacitance<br>Change         No defects or abnormalities.         Fix the capacitor to the supporting Test substrate A (gla<br>shown in "Complement of Test method".           15         Durability         Appearance<br>Capacitance<br>Change         No defects or abnormalities.         Fix the capacitor to the supporting Test substrate A (gla<br>shown in "Complement of Test method".           15         Durability         Appearance<br>Capacitance<br>Change         No defects or abnormalities.         Fix the capacitor to the supporting Test substrate A (gla<br>shown in "Complement of Test method".           Test Temperature<br>Capacitance                                                                                                                                                                                                                                                                                                                                                                                                                                   |                | Within the specified initial value                                                                                                                                      |                                                      | 4                                                                         | Room Temp                                           | 2 to 3          |                   |

| 14       High<br>Temperature<br>High<br>Humidity<br>(Steady)       Appearance<br>Appearance       No defects or abnormalities.       Fix the capacitor to the supporting Test substrate A (glasshown in "Complement of Test method".         14       High<br>Temperature<br>High<br>(Steady)       Appearance<br>D.F.       No defects or abnormalities.       Fix the capacitor to the supporting Test substrate A (glasshown in "Complement of Test method".         17       D.F.       0.02 max.       Test Temperature<br>D.F.       0.02 max.         18.       More than 1000 MΩ or 10 MΩ•µF (Whichever is smaller)       ·Pretreatment<br>Applied Voltage       : DC630V(DC Rated Voltage<br>Exposure Time         15       Durability       Appearance<br>Capacitance<br>Change       No defects or abnormalities.       Fix the capacitor to the supporting Test substrate A (glasshown in "Complement of Test method".         15       Durability       Appearance<br>Capacitance<br>Change       No defects or abnormalities.       Fix the capacitor to the supporting Test substrate A (glasshown in "Complement of Test method".         15       Capacitance<br>Change       Within +/-12.5%       Fix the capacitor to the supporting Test substrate A (glasshown in "Complement of Test method".         15       Capacitance<br>Change       Within +/-12.5%       Fix the capacitor to the supporting Test substrate A (glasshown in "Complement of Test method".         16       Capacitance<br>Change       Within +/-12.5%       Fix Temperature<br>Capacitance       Max. Operating Temp. +/-3<br>Test Ti                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                |                                                                                                                                                                         | Expo                                                 | osure Tin                                                                 | ne : 24+/-2h at room                                | n condition*.   |                   |

| 14       High<br>Temperature<br>High<br>Humidity<br>(Steady)       Appearance<br>Appearance       No defects or abnormalities.       Fix the capacitor to the supporting Test substrate A (glasshown in "Complement of Test method".         14       High<br>Temperature<br>High<br>(Steady)       Appearance<br>D.F.       No defects or abnormalities.       Fix the capacitor to the supporting Test substrate A (glasshown in "Complement of Test method".         17       D.F.       0.02 max.       Test Temperature<br>D.F.       0.02 max.         18.       More than 1000 MΩ or 10 MΩ•µF (Whichever is smaller)       ·Pretreatment<br>Applied Voltage       : DC630V(DC Rated Voltage<br>Exposure Time         15       Durability       Appearance<br>Capacitance<br>Change       No defects or abnormalities.       Fix the capacitor to the supporting Test substrate A (glasshown in "Complement of Test method".         15       Durability       Appearance<br>Capacitance<br>Change       No defects or abnormalities.       Fix the capacitor to the supporting Test substrate A (glasshown in "Complement of Test method".         15       Capacitance<br>Change       Within +/-12.5%       Fix the capacitor to the supporting Test substrate A (glasshown in "Complement of Test method".         15       Capacitance<br>Change       Within +/-12.5%       Fix the capacitor to the supporting Test substrate A (glasshown in "Complement of Test method".         16       Capacitance<br>Change       Within +/-12.5%       Fix Temperature<br>Capacitance       Max. Operating Temp. +/-3<br>Test Ti                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                |                                                                                                                                                                         |                                                      |                                                                           |                                                     |                 |                   |

| Image: Mark and  |                |                                                                                                                                                                         | -                                                    |                                                                           |                                                     | r 1h+/-5min ar  | nd then           |

| Temperature<br>High       Image       Shown in "Complement of Test method".         Humidity<br>(Steady)       Capacitance<br>Change       Within +/-12.5%       Test Temperature : 40+/-2°C<br>Test Humidity : 90% to 95% RH<br>Test Time : 500+24/-0h         D.F.       0.02 max.       D.F.       DC630V(DC Rated Voltage<br>Exposure Time : 24+/-2h at room condition*.         I.R.       More than 1000 MΩ or 10 MΩ•µF (Whichever is smaller)       ·Pretreatment<br>Apply test voltage for 1h+/-5min at test temperature.         Voltage proof       No defects.       Remove and let sit for 24+/-2h at room condition*.         15       Durability       Appearance       No defects or abnormalities.         Fix the capacitor to the supporting Test substrate A (gla<br>shown in "Complement of Test method".         Test Temperature :       Max. Operating Temp. +/-3<br>Test Temperature :         Capacitance<br>Change       Within +/-12.5%       Test Time : 1000+48/-0h<br>Applied Voltage : DC756V(120% of the rated                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                |                                                                                                                                                                         | let si                                               | it for 24+                                                                | /-2h at room condition*.                            |                 |                   |

| Temperature<br>High       Image       Shown in "Complement of Test method".         Humidity<br>(Steady)       Capacitance<br>Change       Within +/-12.5%       Test Temperature : 40+/-2°C<br>Test Humidity : 90% to 95% RH<br>Test Time : 500+24/-0h         D.F.       0.02 max.       D.F.       DC630V(DC Rated Voltage<br>Exposure Time : 24+/-2h at room condition*.         I.R.       More than 1000 MΩ or 10 MΩ•µF (Whichever is smaller)       ·Pretreatment<br>Apply test voltage for 1h+/-5min at test temperature.         Voltage proof       No defects.       Remove and let sit for 24+/-2h at room condition*.         15       Durability       Appearance       No defects or abnormalities.         Fix the capacitor to the supporting Test substrate A (gla<br>shown in "Complement of Test method".         Test Temperature :       Max. Operating Temp. +/-3<br>Test Temperature :         Capacitance<br>Change       Within +/-12.5%       Test Time : 1000+48/-0h<br>Applied Voltage : DC756V(120% of the rated                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Hiah           | nce No defects or abnormalities.                                                                                                                                        | Fix t                                                | he capac                                                                  | itor to the supporting Test subs                    | strate A (glass | epoxy board)      |

| Humidity<br>(Steady)       Change       Test Humidity       90% to 95%RH         D.F.       0.02 max.       Test Time       500+24/-0h         D.F.       0.02 max.       Applied Voltage       DC630V(DC Rated Voltage<br>Exposure Time       24+/-2h at room condition*.         I.R.       More than 1000 MΩ or 10 MΩ•µF (Whichever is smaller)       -Pretreatment<br>Apply test voltage for 1h+/-5min at test temperature.         Voltage proof       No defects.       Remove and let sit for 24+/-2h at room condition*.         15       Durability       Appearance       No defects or abnormalities.       Fix the capacitor to the supporting Test substrate A (gla<br>shown in "Complement of Test method".         Capacitance       Within +/-12.5%       Test Time       1000+48/-0h         Applied Voltage       DC756V(120% of the rated<br>Applied Voltage       DC756V(120% of the rated                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | -              |                                                                                                                                                                         |                                                      |                                                                           |                                                     |                 |                   |

| (Steady)       Image: Constraint of the supporting Test substrate A (glasshown in "Complement of Test method".         15       Durability         Appearance       Within +/-12.5%         Capacitance       Within +/-12.5%         Change       Within +/-12.5%                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | -              | nce Within +/-12.5%                                                                                                                                                     |                                                      | •                                                                         |                                                     |                 |                   |

| Image: Line state of the support o          | -              |                                                                                                                                                                         |                                                      |                                                                           |                                                     |                 |                   |

| I.R.       More than 1000 MΩ or 10 MΩ•μF (Whichever is smaller)       ·Pretreatment         ·Pretreatment       Apply test voltage for 1h+/-5min at test temperature.         Voltage proof       No defects.         15       Durability       Appearance         Appearance       No defects or abnormalities.         Capacitance       Within +/-12.5%         Change       Within +/-12.5%                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                | 0.02 max.                                                                                                                                                               |                                                      |                                                                           | -                                                   |                 |                   |

| Image: style styl         |                | More than 1000 MΩ or 10 MΩ•uF (Whichever is smalle                                                                                                                      |                                                      | osure Tin                                                                 | ne : 24+/-2h at room                                | n condition*.   |                   |

| Voltage proof       No defects.       Remove and let sit for 24+/-2h at room condition*.         15       Durability       Appearance       No defects or abnormalities.       Fix the capacitor to the supporting Test substrate A (gla shown in "Complement of Test method".<br>Test Temperature : Max. Operating Temp. +/-3         Capacitance       Within +/-12.5%       Test Time : 1000+48/-0h         Change       Dc756V(120% of the rated                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                |                                                                                                                                                                         |                                                      | treatmer                                                                  | nt                                                  |                 |                   |