74HC40105 4-bit x 16-word FIFO register

Rev. 5 — 19 April 2019

## 1. General description

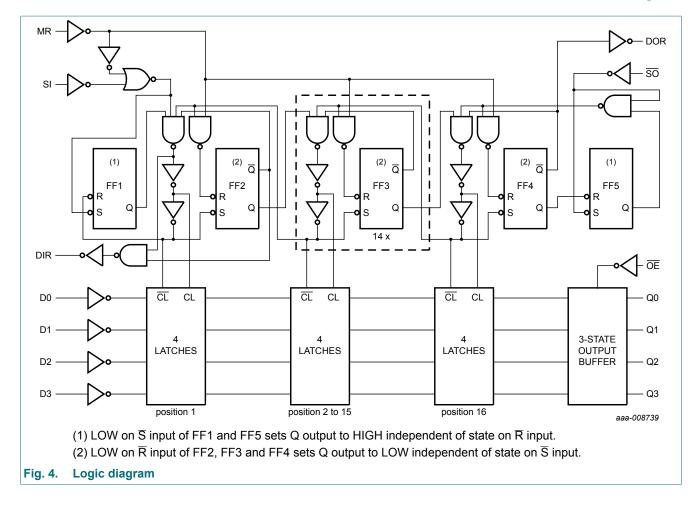

The 74HC40105 is a first-in/first-out (FIFO) "elastic" storage register that can store 16 4-bit words. It can handle input and output data at different shifting rates. This feature makes it particularly useful as a buffer between asynchronous systems. Each word position in the register is clocked by a control flip-flop, which stores a marker bit. A logic 1 signifies that the data at that position is filled and a logic 0 denotes a vacancy in that position. The control flip-flop detects the state of the preceding flip-flop and communicates its own status to the succeeding flip-flop. When a control flip-flop is in the logic 0 state and sees a logic 1 in the preceding flip-flop, it generates a clock pulse. The clock pulse transfers data from the preceding four data latches into its own four data latches and resets the preceding flip-flop to logic 0. The first and last control flip-flops have buffered outputs. All empty locations "bubble" automatically to the input end, and all valid data ripples through to the output end. As a result, the status of the first control flip-flop (data-in ready output - DIR) indicates if the FIFO is full. The status of the last flip-flop (data-out ready output - DOR) indicates whether the FIFO contains data. As the earliest data is removed from the bottom of the data stack (output end), all data entered later will automatically ripple toward the output. Inputs include clamp diodes that enable the use of current limiting resistors to interface inputs to voltages in excess of V<sub>CC</sub>.

## 2. Features and benefits

- · Independent asynchronous inputs and outputs

- Expandable in either direction

- Reset capability

- Status indicators on inputs and outputs

- 3-state outputs

- CMOS input levels

- Complies with JEDEC standard JESD7A

- ESD protection:

- HBM JESD22-A114F exceeds 2000 V

- MM JESD22-A115-A exceeds 200 V

- Specified from -40 °C to +85 °C and from -40 °C to +125 °C

## 3. Ordering information

#### Table 1. Ordering information

| Type number Package |                   |      |                                                               |          |  |  |

|---------------------|-------------------|------|---------------------------------------------------------------|----------|--|--|

|                     | Temperature range | Name | Description                                                   | Version  |  |  |

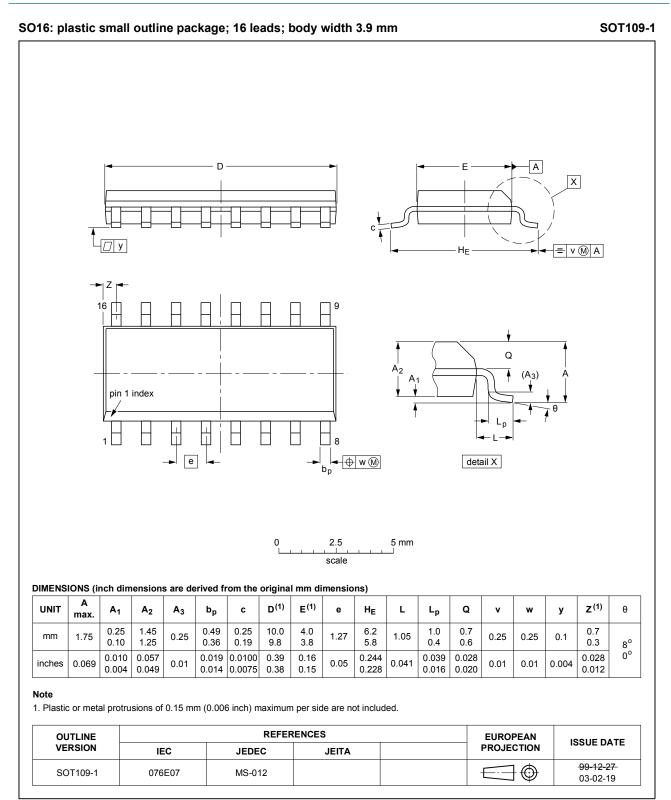

| 74HC40105D          | -40 °C to +125 °C | SO16 | plastic small outline package; 16 leads;<br>body width 3.9 mm | SOT109-1 |  |  |

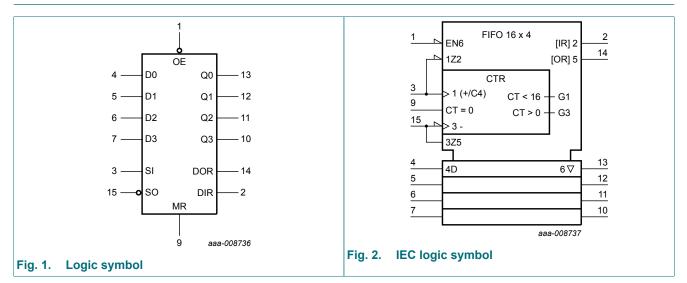

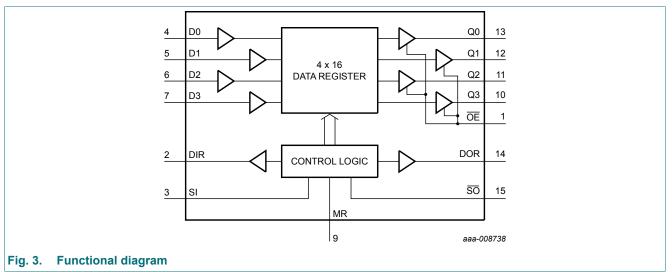

# 4. Functional diagram

### 4-bit x 16-word FIFO register

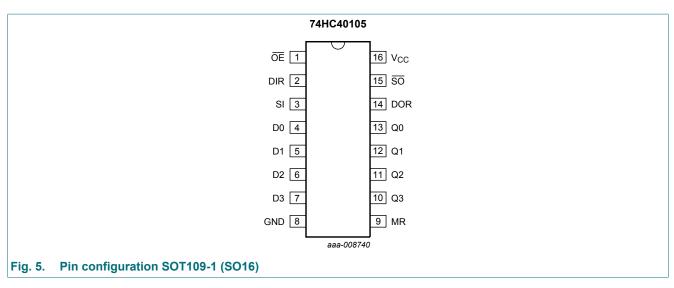

## 5. Pinning information

## 5.1. Pinning

| Table 2. Pin descripti | Fable 2. Pin description |                                               |  |  |  |  |  |  |  |

|------------------------|--------------------------|-----------------------------------------------|--|--|--|--|--|--|--|

| Symbol                 | Pin                      | Description                                   |  |  |  |  |  |  |  |

| ŌĒ                     | 1                        | output enable input (active LOW)              |  |  |  |  |  |  |  |

| DIR                    | 2                        | data-in-ready output                          |  |  |  |  |  |  |  |

| SI                     | 3                        | shift-in input (LOW-to-HIGH, edge triggered)  |  |  |  |  |  |  |  |

| D0 to D3               | 4, 5, 6, 7               | parallel data input                           |  |  |  |  |  |  |  |

| GND                    | 8                        | ground (0 V)                                  |  |  |  |  |  |  |  |

| MR                     | 9                        | asynchronous master-reset input (active HIGH) |  |  |  |  |  |  |  |

| Q0 to Q3               | 13, 12, 11, 10           | data output                                   |  |  |  |  |  |  |  |

| DOR                    | 14                       | data-out-ready output                         |  |  |  |  |  |  |  |

| SO                     | 15                       | shift-out input (HIGH-to-LOW, edge triggered) |  |  |  |  |  |  |  |

| V <sub>CC</sub>        | 16                       | supply voltage                                |  |  |  |  |  |  |  |

## 5.2. Pin description

## 6. Functional description

## 6.1. Inputs and outputs

## Data inputs (D0 to D3)

As there is no weighting of the inputs, any input can be assigned as the MSB. The size of the FIFO memory can be reduced from the 4 x 16 configuration. For example, it can be reduced to 3 x 16, down to 1 x 16, by tying unused data input pins to  $V_{CC}$  or GND.

## Data outputs (Q0 to Q3)

As there is no weighting of the outputs, any output can be assigned as the MSB. The size of the FIFO memory can be reduced from the 4 x 16 configuration as described for data inputs. In a reduced format, the unused data outputs pins must be left open circuit.

## Master-reset (MR)

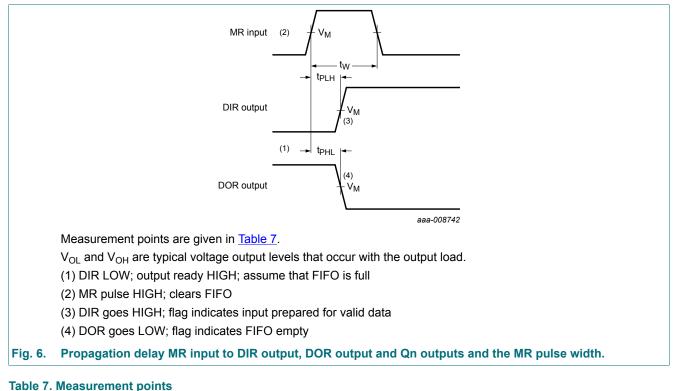

When MR is HIGH, the control functions within the FIFO are cleared, and date content is declared invalid. The data-in ready (DIR) flag is set HIGH and the data-out-ready (DOR) flag is set LOW. The output stage remains in the state of the last word that was shifted out, or in the random state existing at power-up.

## Status flag outputs (DIR, DOR)

Two status flags, data-in-ready (DIR) and data-out-ready (DOR), indicate the status of the FIFO:

- 1. DIR = HIGH indicates that the input stage is empty and ready to accept valid data;

- DIR = LOW indicates that the FIFO is full or that a previous shift-in operation is not complete (busy);

- DOR = HIGH assures valid data is present at the outputs Q0 to Q3 (does not indicate that new data is awaiting transfer into the output stage);

- 4. DOR = LOW indicates that the output stage is busy or there is no valid data.

### Shift-in control (SI)

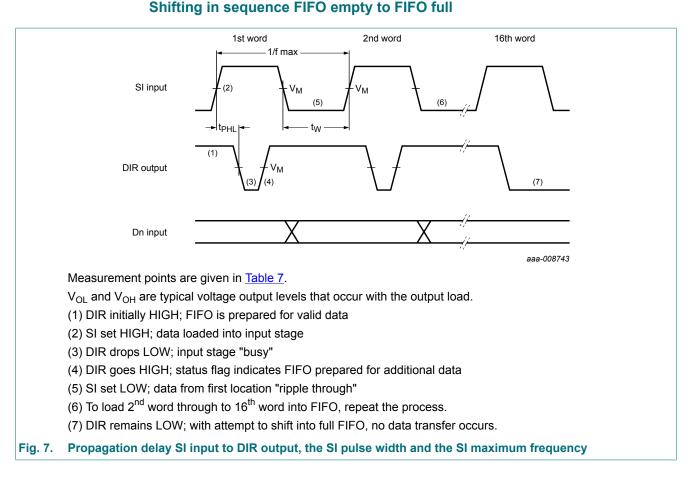

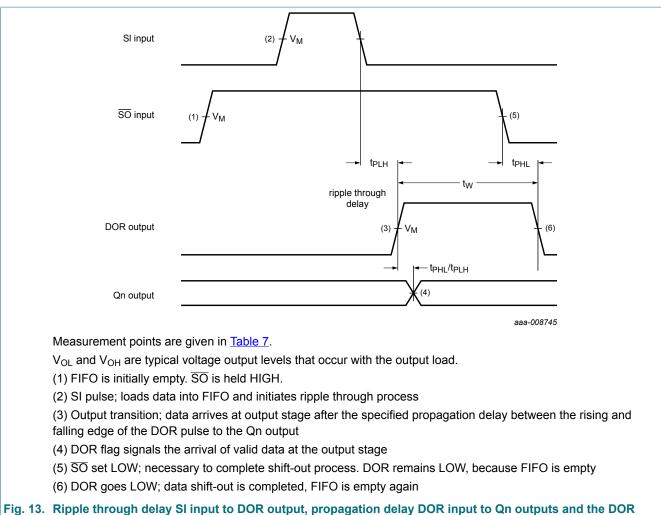

Data is loaded into the input stage on a LOW-to-HIGH transition of SI. It also triggers an automatic data transfer process (ripple through). If SI is held HIGH during reset, data is loaded at the falling edge of the MR signal.

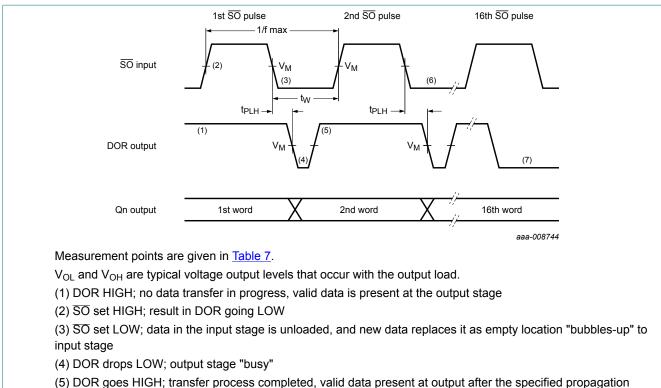

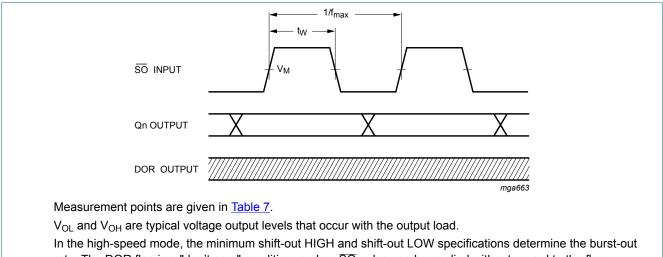

### Shift-out control (SO)

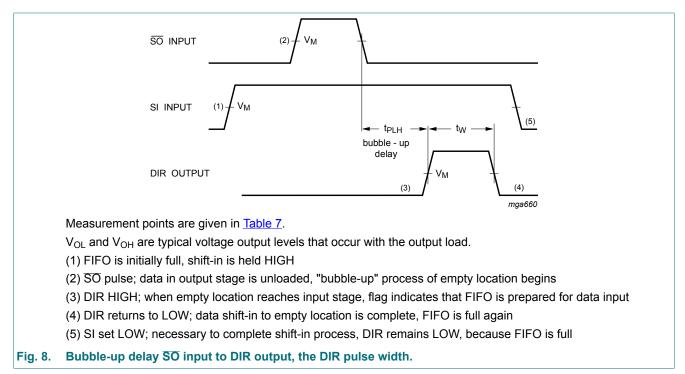

A HIGH-to-LOW transition of  $\overline{SO}$  causes the DOR flags to go LOW. A HIGH-to-LOW transition of  $\overline{SO}$  causes upstream data to move into the output stage, and empty locations to move towards the input stage (bubble-up).

## Output enable (OE)

The outputs Q0 to Q3 are enabled when  $\overline{OE}$  = LOW. When  $\overline{OE}$  = HIGH the outputs are in the high impedance OFF-state.

## 6.2. Data input

Following power-up, the master-reset (MR) input is pulsed HIGH to clear the FIFO memory (see Fig. 6). The data-in-ready flag (DIR = HIGH) indicates that the FIFO input stage is empty and ready to receive data. When DIR is valid (HIGH), data present at D0 to D3 can be shifted-in using the SI control input. With SI = HIGH, data is shifted into the input stage. DIR going LOW provides a busy indication. The data remains at the first location in the FIFO until DIR is set to HIGH and data moves through the FIFO to the output stage, or to the last empty location. If the FIFO is not full after the SI pulse, DIR again becomes valid (HIGH) to indicate that space is available in the FIFO. The DIR flag remains LOW if the FIFO is full (see Fig. 7). To complete the shift-in process, the SI use must be made LOW. With the FIFO full, SI can be held HIGH until a shift-out (SO) pulse occurs. Then, following a shift-out of data, an empty location appears at the FIFO input and DIR goes HIGH to allow the next data to be shifted-in. This data remains at the first FIFO location until SI goes LOW (see Fig. 8).

## 6.3. Data transfer

After data has been transferred from the input stage of the FIFO following SI = LOW, data moves through the FIFO asynchronously and is stacked at the output end of the register. Empty locations appear at the input end of the FIFO as data moves through the device.

## 6.4. Data output

The data-out-ready flag (DOR = HIGH) indicates that there is valid data at the output (Q0 to Q3). The initial master-reset at power-on (MR = HIGH) sets DOR to LOW (see Fig. 6). After MR = LOW, data shifted into the FIFO moves through to the output stage causing DOR to go HIGH. As the DOR flag goes HIGH, data can be shifted-out using the  $\overline{SO}$  = HIGH, data in the output stage is shifted out. DOR going LOW provides a busy indication. When  $\overline{SO}$  is made LOW, data moves through the FIFO to fill the output stage and an empty location appears at the input stage. When the output stage is filled DOR goes HIGH, but if the last of the valid data has been shifted-out leaving the FIFO empty the DOR flag remains LOW (see Fig. 10). With the FIFO empty, the last word that was shifted-out is latched at the output Q0 to Q3.

With the FIFO empty, the  $\overline{SO}$  input can be held HIGH until the SI control input is used. Following an SI pulse, data moves through the FIFO to the output stage, resulting in the DOR flag pulsing HIGH and a shift-out of data occurring. The  $\overline{SO}$  control must be made LOW before additional data can be shifted-out (see Fig. 13).

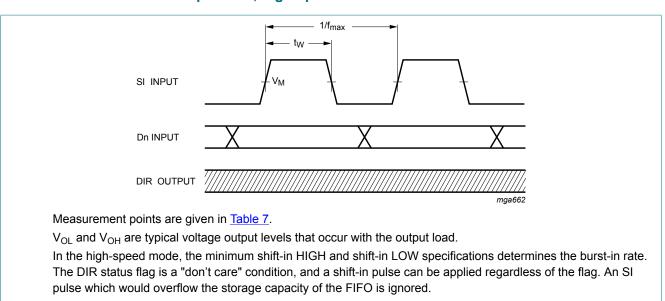

## 6.5. High-speed burst mode

Assuming the shift-in/shift-out pulses are not applied until the respective status flags are valid, it follows that the status flags determine the shift-in/shift-out rates. However, without the status flags, a high-speed burst can be implemented. In this mode, pulse widths determine the burst-in/burst-out

#### 4-bit x 16-word FIFO register

rates of the shift-in/shift-out inputs. Burst rates of 35 MHz can be obtained. Shift pulses can be applied without regard to the status flags but shift-in pulses that would overflow the storage capacity of the FIFO are not allowed (see Fig. 11 and Fig. 12).

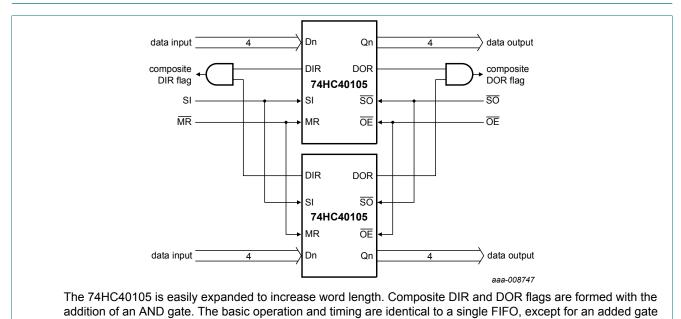

## 6.6. Expanded format

With the addition of a logic gate, the FIFO is easily expanded to increase word length (see Fig. 18). The basic operation and timing are identical to a single FIFO, except for an additional gate delay on the flag outputs. If during application, the following occurs:

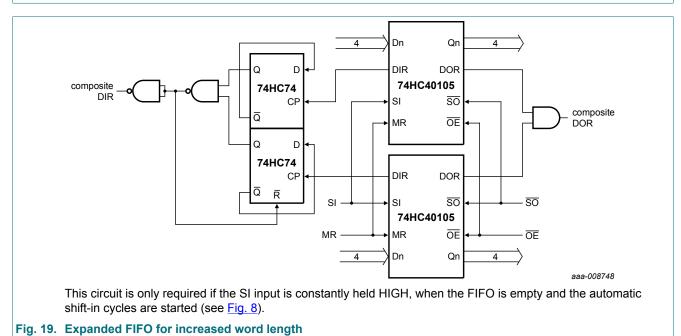

SI is held HIGH when the FIFO is empty, some additional logic is required to produce a composite DIR pulse (see Fig. 8 and Fig. 19).

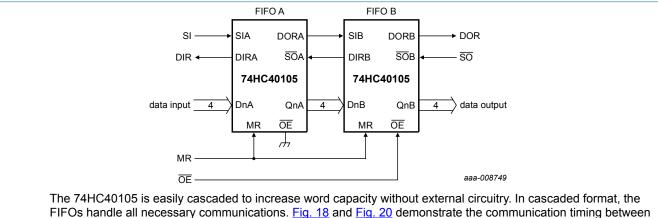

Due to the part-to-part spread of the ripple through time, the SI signals of FIFO A and FIFO B do not always coincide. As a result, the AND-gate does not produce a composite flag signal. The solution is given in Fig. 19. The 74HC40105 is easily cascaded to increase the word capacity and no external components are needed. In the cascaded configuration, the FIFOs perform all necessary communications and timing. The minimum flag pulse widths and the flag delays determine the intercommunication speed. The data rate of cascaded devices is typically 25 MHz. Word-capacity can be expanded to and beyond 32-words x 4-bits (see Fig. 20).

## 7. Limiting values

#### Table 3. Limiting values

In accordance with the Absolute Maximum Rating System (IEC 60134). Voltages are referenced to GND (ground = 0 V).

| Symbol           | Parameter               | Conditions                                                                  | Min  | Мах  | Unit |

|------------------|-------------------------|-----------------------------------------------------------------------------|------|------|------|

| V <sub>CC</sub>  | supply voltage          |                                                                             | -0.5 | +7   | V    |

| I <sub>IK</sub>  | input clamping current  | $V_{I} < -0.5 V \text{ or } V_{I} > V_{CC} + 0.5 V$ [1]                     | -    | ±20  | mA   |

| Ι <sub>ΟΚ</sub>  | output clamping current | $V_{\rm O} < -0.5 \text{ V or } V_{\rm O} > V_{\rm CC} + 0.5 \text{ V}$ [1] | -    | ±20  | mA   |

| lo               | output current          | $V_{\rm O}$ = -0.5 V to (V <sub>CC</sub> + 0.5 V)                           | -    | ±25  | mA   |

| I <sub>CC</sub>  | supply current          |                                                                             | -    | +50  | mA   |

| I <sub>GND</sub> | ground current          |                                                                             | -50  | -    | mA   |

| T <sub>stg</sub> | storage temperature     |                                                                             | -65  | +150 | °C   |

| P <sub>tot</sub> | total power dissipation | [2]                                                                         | -    | 500  | mW   |

[1] The input and output voltage ratings may be exceeded if the input and output current ratings are observed.

[2] For SO16 packages: above 70 °C the value of Ptot derates linearly with 8 mW/K.

## 8. Recommended operating conditions

#### Table 4. Recommended operating conditions

Voltages are referenced to GND (ground = 0 V)

| Symbol           | Parameter                           | Conditions              | Min | Тур  | Max             | Unit |

|------------------|-------------------------------------|-------------------------|-----|------|-----------------|------|

| V <sub>CC</sub>  | supply voltage                      |                         | 2.0 | 5.0  | 6.0             | V    |

| VI               | input voltage                       |                         | 0   | -    | V <sub>CC</sub> | V    |

| Vo               | output voltage                      |                         | 0   | -    | V <sub>CC</sub> | V    |

| T <sub>amb</sub> | ambient temperature                 |                         | -40 | +25  | +125            | °C   |

| Δt/ΔV            | input transition rise and fall rate | V <sub>CC</sub> = 2.0 V | -   | -    | 625             | ns/V |

|                  |                                     | V <sub>CC</sub> = 4.5 V | -   | 1.67 | 139             | ns/V |

|                  |                                     | V <sub>CC</sub> = 6.0 V | -   | -    | 83              | ns/V |

# 9. Static characteristics

### Table 5. Static characteristics

At recommended operating conditions; voltages are referenced to GND (ground = 0 V).

| Symbol                     | Parameter                           | Conditions                                                                                       |      | 25 °C |      |      | °C to<br>5 °C | -40 °C to<br>+125 °C |       | Unit |

|----------------------------|-------------------------------------|--------------------------------------------------------------------------------------------------|------|-------|------|------|---------------|----------------------|-------|------|

|                            |                                     |                                                                                                  | Min  | Тур   | Мах  | Min  | Мах           | Min                  | Max   |      |

| VIH                        | HIGH-level                          | V <sub>CC</sub> = 2.0 V                                                                          | 1.5  | 1.2   | -    | 1.5  | -             | 1.5                  | -     | V    |

|                            | input voltage                       | V <sub>CC</sub> = 4.5 V                                                                          | 3.15 | 2.4   | -    | 3.15 | -             | 3.15                 | -     | V    |

|                            |                                     | V <sub>CC</sub> = 6.0 V                                                                          | 4.2  | 3.2   | -    | 4.2  | -             | 4.2                  | -     | V    |

| V <sub>IL</sub>            | LOW-level                           | V <sub>CC</sub> = 2.0 V                                                                          | -    | 0.8   | 0.5  | -    | 0.5           | -                    | 0.5   | V    |

|                            | input voltage                       | V <sub>CC</sub> = 4.5 V                                                                          | -    | 2.1   | 1.35 | -    | 1.35          | -                    | 1.35  | V    |

|                            |                                     | V <sub>CC</sub> = 6.0 V                                                                          | -    | 2.8   | 1.8  | -    | 1.8           | -                    | 1.8   | V    |

| V <sub>OH</sub> HIGH-level | $V_{I} = V_{IH} \text{ or } V_{IL}$ |                                                                                                  |      |       |      |      |               |                      |       |      |

|                            | output voltage                      | I <sub>O</sub> = -20 μA; V <sub>CC</sub> = 2.0 V                                                 | 1.9  | 2.0   | -    | 1.9  | -             | 1.9                  | -     | V    |

|                            |                                     | I <sub>O</sub> = -20 μA; V <sub>CC</sub> = 4.5 V                                                 | 4.4  | 4.5   | -    | 4.4  | -             | 4.4                  | -     | V    |

|                            |                                     | I <sub>O</sub> = -20 μA; V <sub>CC</sub> = 6.0 V                                                 | 5.9  | 6.0   | -    | 5.9  | -             | 5.9                  | -     | V    |

|                            |                                     | I <sub>O</sub> = -4 mA; V <sub>CC</sub> = 4.5 V                                                  | 3.98 | 4.32  | -    | 3.84 | -             | 3.7                  | -     | V    |

|                            |                                     | I <sub>O</sub> = -5.2 mA; V <sub>CC</sub> = 6.0 V                                                | 5.48 | 5.81  | -    | 5.34 | -             | 5.2                  | -     | V    |

| V <sub>OL</sub>            | LOW-level                           | $V_{I} = V_{IH} \text{ or } V_{IL}$                                                              |      |       |      |      |               |                      |       |      |

|                            | output voltage                      | I <sub>O</sub> = 20 μA; V <sub>CC</sub> = 2.0 V                                                  | -    | 0     | 0.1  | -    | 0.1           | -                    | 0.1   | V    |

|                            |                                     | I <sub>O</sub> = 20 μA; V <sub>CC</sub> = 4.5 V                                                  | -    | 0     | 0.1  | -    | 0.1           | -                    | 0.1   | V    |

|                            |                                     | I <sub>O</sub> = 20 μA; V <sub>CC</sub> = 6.0 V                                                  | -    | 0     | 0.1  | -    | 0.1           | -                    | 0.1   | V    |

|                            |                                     | I <sub>O</sub> = 4 mA; V <sub>CC</sub> = 4.5 V                                                   | -    | 0.15  | 0.26 | -    | 0.33          | -                    | 0.4   | V    |

|                            |                                     | I <sub>O</sub> = 5.2 mA; V <sub>CC</sub> = 6.0 V                                                 | -    | 0.15  | 0.26 | -    | 0.33          | -                    | 0.4   | V    |

| I                          | input leakage current               | $V_{I} = V_{CC}$ or GND; $V_{CC} = 6.0$ V                                                        | -    | -     | ±0.1 | -    | ±1.0          | -                    | ±1.0  | μA   |

| I <sub>OZ</sub>            | OFF-state<br>output current         | $V_{I} = V_{IH} \text{ or } V_{IL};$<br>$V_{O} = V_{CC} \text{ or } GND; V_{CC} = 6.0 \text{ V}$ | -    | -     | ±0.5 | -    | ±5.0          | -                    | ±10.0 | μA   |

| I <sub>CC</sub>            | supply current                      | $V_I = V_{CC}$ or GND; $I_O = 0$ A;<br>$V_{CC} = 6.0$ V                                          | -    | -     | 8    | -    | 80            | -                    | 160   | μA   |

| CI                         | input<br>capacitance                |                                                                                                  | -    | 3.5   | -    | -    | -             | -                    | -     | pF   |

**Product data sheet**

# **10.** Dynamic characteristics

### Table 6. Dynamic characteristics

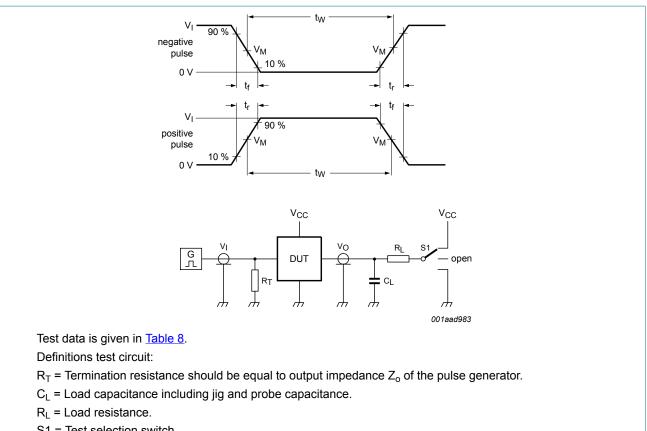

Voltages are referenced to GND (ground = 0 V);  $C_L$  = 50 pF unless otherwise specified; for test circuit, see Fig. 17.

| Symbol           | Parameter    | Conditions                                    |     | 25 °C |      | -40 °C to<br>+85 °C |      | -40 °C to<br>+125 °C |      | Unit |

|------------------|--------------|-----------------------------------------------|-----|-------|------|---------------------|------|----------------------|------|------|

|                  |              |                                               | Min | Тур   | Max  | Min                 | Мах  | Min                  | Max  |      |

| t <sub>pd</sub>  | propagation  | MR to DIR or DOR; see Fig. 6 [1]              |     |       |      |                     |      |                      |      |      |

|                  | delay        | V <sub>CC</sub> = 2.0 V                       | -   | 52    | 175  | -                   | 220  | -                    | 265  | ns   |

|                  |              | V <sub>CC</sub> = 4.5 V                       | -   | 19    | 35   | -                   | 44   | -                    | 53   | ns   |

|                  |              | V <sub>CC</sub> = 5 V; C <sub>L</sub> = 15 pF | -   | 16    | -    | -                   | -    | -                    | -    | ns   |

|                  |              | V <sub>CC</sub> = 6.0 V                       | -   | 15    | 30   | -                   | 37   | -                    | 45   | ns   |

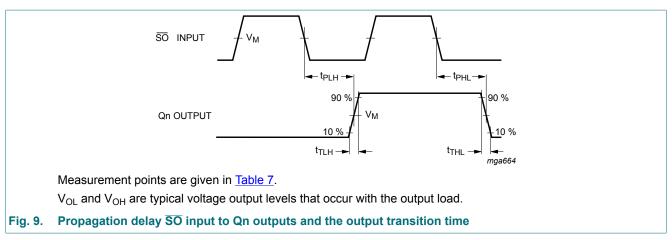

|                  |              | SO to Qn; see Fig. 9 [1]                      |     |       |      |                     |      |                      |      |      |

|                  |              | V <sub>CC</sub> = 2.0 V                       | -   | 116   | 400  | -                   | 500  | -                    | 600  | ns   |

|                  |              | V <sub>CC</sub> = 4.5 V                       | -   | 42    | 80   | -                   | 100  | -                    | 120  | ns   |

|                  |              | V <sub>CC</sub> = 5 V; C <sub>L</sub> = 15 pF | -   | 37    | -    | -                   | -    | -                    | -    | ns   |

|                  |              | V <sub>CC</sub> = 6.0 V                       | -   | 34    | 68   | -                   | 85   | -                    | 102  | ns   |

| t <sub>PHL</sub> | HIGH to LOW  | SI to DIR; see Fig. 7 [1]                     |     |       |      |                     |      |                      |      |      |

|                  | propagation  | V <sub>CC</sub> = 2.0 V                       | -   | 52    | 210  | -                   | 265  | -                    | 315  | ns   |

|                  | delay        | V <sub>CC</sub> = 4.5 V                       | -   | 19    | 42   | -                   | 53   | -                    | 63   | ns   |

|                  |              | V <sub>CC</sub> = 5 V; C <sub>L</sub> = 15 pF | -   | 16    | -    | -                   | -    | -                    | -    | ns   |

|                  |              | V <sub>CC</sub> = 6.0 V                       | -   | 15    | 36   | -                   | 45   | -                    | 54   | ns   |

|                  |              | SO to DOR; see Fig. 10 [1]                    |     |       |      |                     |      |                      |      |      |

|                  |              | V <sub>CC</sub> = 2.0 V                       | -   | 55    | 210  | -                   | 265  | -                    | 315  | ns   |

|                  |              | V <sub>CC</sub> = 4.5 V                       | -   | 20    | 42   | -                   | 53   | -                    | 63   | ns   |

|                  |              | V <sub>CC</sub> = 5 V; C <sub>L</sub> = 15 pF | -   | 17    | -    | -                   | -    | -                    | -    | ns   |

|                  |              | V <sub>CC</sub> = 6.0 V                       | -   | 16    | 36   | -                   | 45   | -                    | 54   | ns   |

| t <sub>PLH</sub> | LOW to HIGH  | SI to DOR; see Fig. 13 [1][2]                 |     |       |      |                     |      |                      |      |      |

|                  | propagation  | V <sub>CC</sub> = 2.0 V                       | -   | 564   | 2000 | -                   | 2500 | -                    | 3000 | ns   |

|                  | delay        | V <sub>CC</sub> = 4.5 V                       | -   | 205   | 400  | -                   | 500  | -                    | 600  | ns   |

|                  |              | V <sub>CC</sub> = 6.0 V                       | -   | 165   | 340  | -                   | 425  | -                    | 510  | ns   |

|                  |              | SO to DIR; see Fig. 8         [1][3]          |     |       |      |                     |      |                      |      |      |

|                  |              | V <sub>CC</sub> = 2.0 V                       | -   | 701   | 2500 | -                   | 3125 | -                    | 3750 | ns   |

|                  |              | V <sub>CC</sub> = 4.5 V                       | -   | 255   | 500  | -                   | 625  | -                    | 750  | ns   |

|                  |              | V <sub>CC</sub> = 6.0 V                       | -   | 204   | 425  | -                   | 532  | -                    | 638  | ns   |

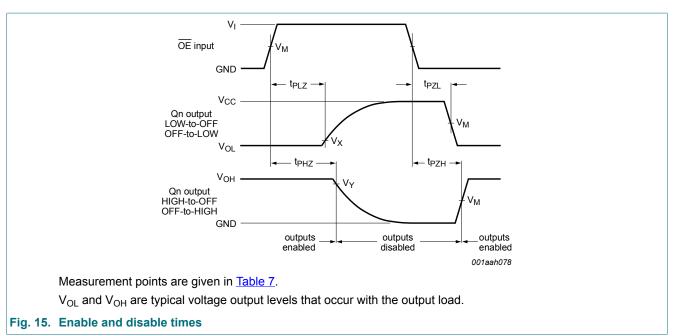

| t <sub>en</sub>  | enable time  | OE to Qn; see Fig. 15 [4]                     |     |       |      |                     |      |                      |      |      |

|                  |              | V <sub>CC</sub> = 2.0 V                       | -   | 41    | 150  | -                   | 190  | -                    | 225  | ns   |

|                  |              | V <sub>CC</sub> = 4.5 V                       | -   | 15    | 30   | -                   | 38   | -                    | 45   | ns   |

|                  |              | V <sub>CC</sub> = 6.0 V                       | -   | 12    | 26   | -                   | 33   | -                    | 38   | ns   |

| t <sub>dis</sub> | disable time | OE to Qn; see Fig. 15         [5]             |     |       |      |                     |      |                      |      | 1    |

|                  |              | V <sub>CC</sub> = 2.0 V                       | -   | 41    | 140  | -                   | 175  | -                    | 210  | ns   |

|                  |              | V <sub>CC</sub> = 4.5 V                       | -   | 15    | 28   | -                   | 35   | -                    | 42   | ns   |

|                  |              | V <sub>CC</sub> = 6.0 V                       | -   | 12    | 24   | -                   | 30   | -                    | 36   | ns   |

## 4-bit x 16-word FIFO register

| Symbol           | Parameter       | Conditions                   |     | 25 °C |     | -40 °C to<br>+85 °C |     | -40 °C to<br>+125 °C |     | Unit |

|------------------|-----------------|------------------------------|-----|-------|-----|---------------------|-----|----------------------|-----|------|

|                  |                 |                              | Min | Тур   | Max | Min                 | Max | Min                  | Max |      |

| t <sub>t</sub>   | transition time | Qn; see <u>Fig. 9</u> [6]    |     |       |     |                     |     |                      |     |      |

|                  |                 | V <sub>CC</sub> = 2.0 V      | -   | 19    | 75  | -                   | 95  | -                    | 110 | ns   |

|                  |                 | V <sub>CC</sub> = 4.5 V      | -   | 7     | 15  | -                   | 19  | -                    | 22  | ns   |

|                  |                 | V <sub>CC</sub> = 6.0 V      | -   | 6     | 13  | -                   | 16  | -                    | 19  | ns   |

| t <sub>vv</sub>  | pulse width     | SI HIGH or LOW; see Fig. 7   |     |       |     |                     |     |                      |     |      |

|                  |                 | V <sub>CC</sub> = 2.0 V      | 80  | 19    | -   | 100                 | -   | 120                  | -   | ns   |

|                  |                 | V <sub>CC</sub> = 4.5 V      | 16  | 7     | -   | 20                  | -   | 24                   | -   | ns   |

|                  |                 | V <sub>CC</sub> = 6.0 V      | 14  | 6     | -   | 17                  | -   | 20                   | -   | ns   |

|                  |                 | SO HIGH or LOW; see Fig. 10  |     |       |     |                     |     |                      |     |      |

|                  |                 | V <sub>CC</sub> = 2.0 V      | 120 | 39    | -   | 150                 | -   | 180                  | -   | ns   |

|                  |                 | V <sub>CC</sub> = 4.5 V      | 24  | 14    | -   | 30                  | -   | 36                   | -   | ns   |

|                  |                 | V <sub>CC</sub> = 6.0 V      | 20  | 11    | -   | 26                  | -   | 31                   | -   | ns   |

|                  |                 | DIR HIGH; see Fig. 8         |     |       |     |                     |     |                      |     |      |

|                  |                 | V <sub>CC</sub> = 2.0 V      | 12  | 58    | 180 | 10                  | 225 | 10                   | 270 | ns   |

|                  |                 | V <sub>CC</sub> = 4.5 V      | 6   | 21    | 36  | 5                   | 45  | 5                    | 54  | ns   |

|                  |                 | V <sub>CC</sub> = 6.0 V      | 5   | 17    | 31  | 4                   | 38  | 4                    | 46  | ns   |

|                  |                 | DOR LOW; see Fig. 13         |     |       |     |                     |     |                      |     |      |

|                  |                 | V <sub>CC</sub> = 2.0 V      | 12  | 55    | 170 | 10                  | 215 | 10                   | 255 | ns   |

|                  |                 | $V_{\rm CC} = 4.5 V$         | 6   | 20    | 34  | 5                   | 43  | 5                    | 51  | ns   |

|                  |                 | $V_{\rm CC} = 6.0 \text{ V}$ | 5   | 16    | 29  | 4                   | 37  | 4                    | 43  | ns   |

|                  |                 | MR HIGH; see Fig. 6          |     |       |     |                     |     |                      |     |      |

|                  |                 | V <sub>CC</sub> = 2.0 V      | 80  | 22    | -   | 100                 | -   | 120                  | -   | ns   |

|                  |                 | $V_{\rm CC} = 4.5  \rm V$    | 16  | 8     | -   | 20                  | -   | 24                   | -   | ns   |

|                  |                 | $V_{\rm CC} = 6.0 \text{ V}$ | 14  | 6     | -   | 17                  | -   | 20                   | -   | ns   |

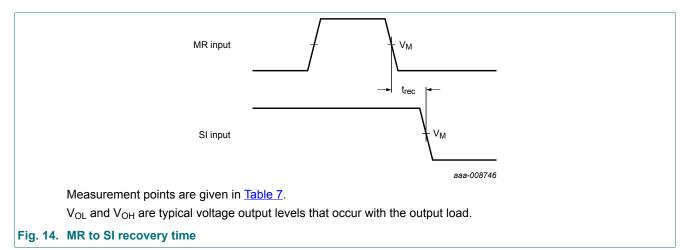

| t <sub>rec</sub> | recovery time   | MR to SI; see Fig. 14        |     |       |     |                     |     |                      |     |      |

|                  | -               | V <sub>CC</sub> = 2.0 V      | 50  | 14    | -   | 65                  | -   | 75                   | -   | ns   |

|                  |                 | V <sub>CC</sub> = 4.5 V      | 10  | 5     | -   | 13                  | -   | 15                   | -   | ns   |

|                  |                 | V <sub>CC</sub> = 6.0 V      | 9   | 4     | -   | 11                  | -   | 13                   | -   | ns   |

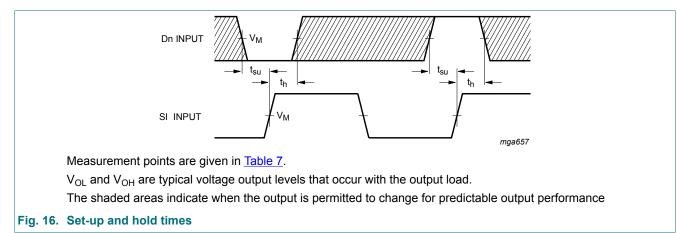

| t <sub>su</sub>  | set-up time     | Dn to SI; see Fig. 16        |     |       |     |                     |     |                      |     |      |

|                  |                 | V <sub>CC</sub> = 2.0 V      | -5  | -39   | -   | -5                  | -   | -5                   | -   | ns   |

|                  |                 | V <sub>CC</sub> = 4.5 V      | -5  | -14   | -   | -5                  | -   | -5                   | -   | ns   |

|                  |                 | V <sub>CC</sub> = 6.0 V      | -5  | -11   | -   | -5                  | -   | -5                   | -   | ns   |

| t <sub>h</sub>   | hold time       | Dn to SI; see Fig. 16        |     |       |     |                     |     |                      |     |      |

|                  |                 | V <sub>CC</sub> = 2.0 V      | 125 | 44    | -   | 155                 | -   | 190                  | -   | ns   |

|                  |                 | V <sub>CC</sub> = 4.5 V      | 25  | 16    | -   | 31                  | -   | 38                   | -   | ns   |

|                  |                 | V <sub>CC</sub> = 6.0 V      | 21  | 13    | -   | 26                  | -   | 32                   | -   | ns   |

### 4-bit x 16-word FIFO register

| Symbol          | Parameter                           | rameter Conditions                                                                                                                                      |     | 25 °C |     | -40 °C to<br>+85 °C |     | -40 °C to<br>+125 °C |     | Unit |

|-----------------|-------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------|-----|---------------------|-----|----------------------|-----|------|

|                 |                                     |                                                                                                                                                         | Min | Тур   | Max | Min                 | Max | Min                  | Max |      |

| max             | maximum<br>frequency                | SI, $\overline{SO}$ using flags or burst mode;<br>see $\underline{Fig. 7}$ , $\underline{Fig. 10}$ , $\underline{Fig. 11}$ and<br>$\underline{Fig. 12}$ |     |       |     |                     |     |                      |     |      |

|                 |                                     | V <sub>CC</sub> = 2.0 V                                                                                                                                 | 3.6 | 10    | -   | 2.8                 | -   | 2.4                  | -   | MHz  |

|                 |                                     | V <sub>CC</sub> = 4.5 V                                                                                                                                 | 18  | 30    | -   | 14                  | -   | 12                   | -   | MHz  |

|                 |                                     | V <sub>CC</sub> = 5 V; C <sub>L</sub> = 15 pF                                                                                                           | -   | 33    | -   | -                   | -   | -                    | -   | MHz  |

|                 |                                     | V <sub>CC</sub> = 6.0 V                                                                                                                                 | 21  | 36    | -   | 16                  | -   | 14                   | -   | MHz  |

|                 |                                     | SI, $\overline{SO}$ cascaded; see $\underline{Fig. 7}$ and $\underline{Fig. 10}$                                                                        |     |       |     |                     |     |                      |     |      |

|                 |                                     | V <sub>CC</sub> = 2.0 V                                                                                                                                 | 3.6 | 10    | -   | 2.8                 | -   | 2.4                  | -   | MHz  |

|                 |                                     | $V_{CC} = 4.5 V$                                                                                                                                        | 18  | 30    | -   | 14                  | -   | 12                   | -   | MHz  |

|                 |                                     | V <sub>CC</sub> = 6.0 V                                                                                                                                 | 21  | 36    | -   | 16                  | -   | 14                   | -   | MHz  |

| C <sub>PD</sub> | power<br>dissipation<br>capacitance | $V_{I} = GND \text{ to } V_{CC}$ [7]                                                                                                                    | -   | 134   | -   | -                   | -   | -                    | -   | pF   |

$t_{\text{pd}}$  is the same as  $t_{\text{PLH}}$  and  $t_{\text{PHL}}$  . This is the ripple through delay. [1] [2]

This is the bubble-up delay. [3]

[4]  $t_{en}$  is the same as  $t_{PZH}$  and  $t_{PZL}$ .

[5] t<sub>dis</sub> is the same as t<sub>PLZ</sub> and t<sub>PHZ</sub>.

[6]

$t_{dis}$  is the same as  $t_{TLL}$  and  $t_{TLH}$ .  $C_{PD}$  is used to determine the dynamic power dissipation ( $P_D$  in  $\mu$ W).  $P_D = C_{PD} \times V_{CC}^2 \times f_i \times N + \sum (C_L \times V_{CC}^2 \times f_o)$  where: [7]

$f_i$  = input frequency in MHz;

$f_o$  = output frequency in MHz;

$C_L$  = output load capacitance in pF;

V<sub>CC</sub> = supply voltage in V;

N = number of inputs switching;  $\Sigma(C_L \times V_{CC}^2 \times f_0)$  = sum of outputs.

## 10.1. Waveforms and test circuit

## Master reset applied with FIFO full

| Input              | Output             |                    |                    |

|--------------------|--------------------|--------------------|--------------------|

| V <sub>M</sub>     | V <sub>M</sub>     | V <sub>X</sub>     | V <sub>Y</sub>     |

| 0.5V <sub>CC</sub> | 0.5V <sub>CC</sub> | 0.1V <sub>CC</sub> | 0.9V <sub>CC</sub> |

### 4-bit x 16-word FIFO register

## With FIFO full; SI held HIGH in anticipation of empty location

© Nexperia B.V. 2019. All rights reserved

### 4-bit x 16-word FIFO register

## Shifting out sequence; FIFO full to FIFO empty

delay

(6) To unload the 3<sup>rd</sup> through the 16<sup>th</sup> word from FIFO, repeat the process

(7) DOR remains LOW; FIFO is empty

Fig. 10. Propagation delay SO input to DOR output, the SO pulse width and the SO maximum frequency.

### 4-bit x 16-word FIFO register

## Shift-in operation; high-speed burst mode

Fig. 11. The SI pulse width and the SI maximum frequency, in high-speed shift-in burst mode

### Shift-out operation; high-speed burst mode

rate. The DOR flag is a "don't care" condition, and an SO pulse can be applied without regard to the flag.

#### Fig. 12. The SO pulse width and the SO maximum frequency, in high-speed shift-out burst mode

### 4-bit x 16-word FIFO register

## With FIFO empty; SO is held HIGH in anticipation

### MR to SI recovery time

### 4-bit x 16-word FIFO register

## Enable and disable times

## Set-up and hold times

### 4-bit x 16-word FIFO register

S1 = Test selection switch.

### Fig. 17. Test circuit for measuring switching times

#### Table 8. Test data

| Input           |                                 | Load         |      | S1 position                         |                                     |                                     |  |

|-----------------|---------------------------------|--------------|------|-------------------------------------|-------------------------------------|-------------------------------------|--|

| VI              | t <sub>r</sub> , t <sub>f</sub> | CL           | RL   | t <sub>PHL</sub> , t <sub>PLH</sub> | t <sub>PZH</sub> , t <sub>PHZ</sub> | t <sub>PZL</sub> , t <sub>PLZ</sub> |  |

| V <sub>CC</sub> | 6 ns                            | 15 pF, 50 pF | 1 kΩ | open                                | GND                                 | V <sub>CC</sub>                     |  |

**Product data sheet**

### 4-bit x 16-word FIFO register

## **11. Application information**

delay on the flags.

### Fig. 18. Expanded FIFO for increased word length; 16 words x 8 bits

## 11.1. Expanded format

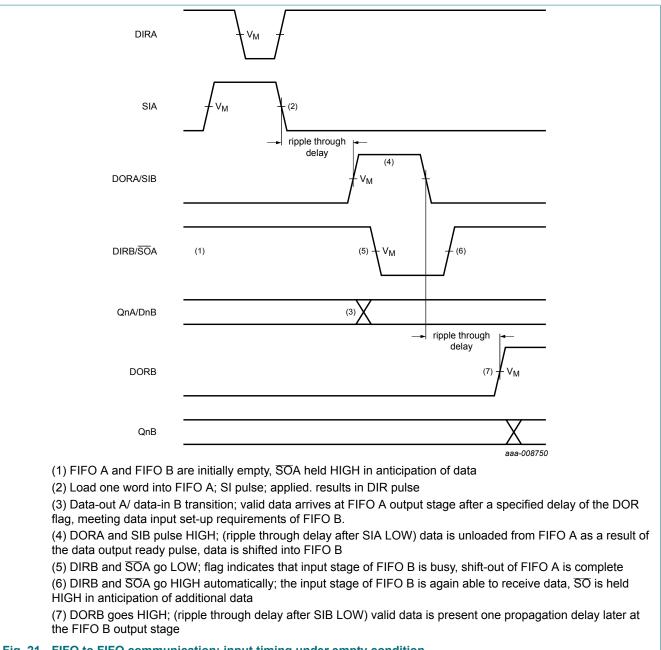

Fig. 20 shows two cascaded FIFOs providing a capacity of 32 words x 4 bits. Fig. 21 shows the signals on the nodes of both FIFOs after the application of the SI pulse, when both FIFOs are initially empty. After a ripple through delay, data arrives at the output of FIFO A. Due to SOA being HIGH, a DORA pulse is generated. The DORA pulse width and the timing between the rising edge of DORA and QnA satisfy the requirements of SIB and DnB. After a second ripple through delay data arrives at the output of FIFO B.

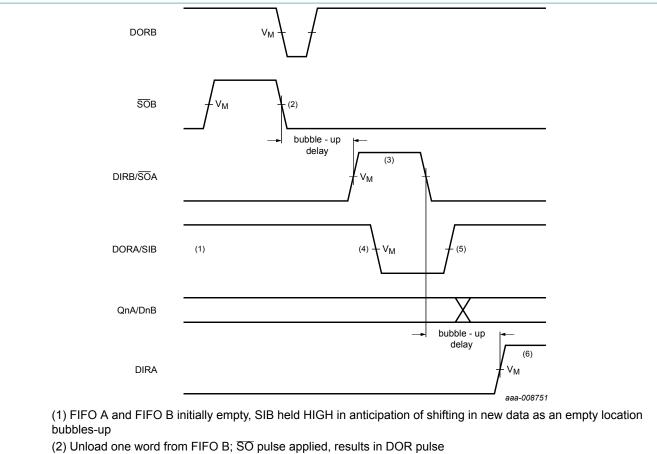

Fig. 22 shows the signals on the nodes of both FIFOs after the application of the SOB pulse, when both FIFOs are initially full. After a bubble-up delay, a DIRB pulse is generated, which acts as a SOA pulse for FIFO A. One word is transferred from the output of FIFO A to the input of FIFO B. The pulse width of DORB satisfy the requirements of the SOA pulse for FIFO A. After a second bubble-up delay, an empty space arrives at DnA, at which time DIRA goes HIGH. Fig. 23 shows the waveforms at all external nodes of both FIFOs during a complete shift-in and shift-out sequence.

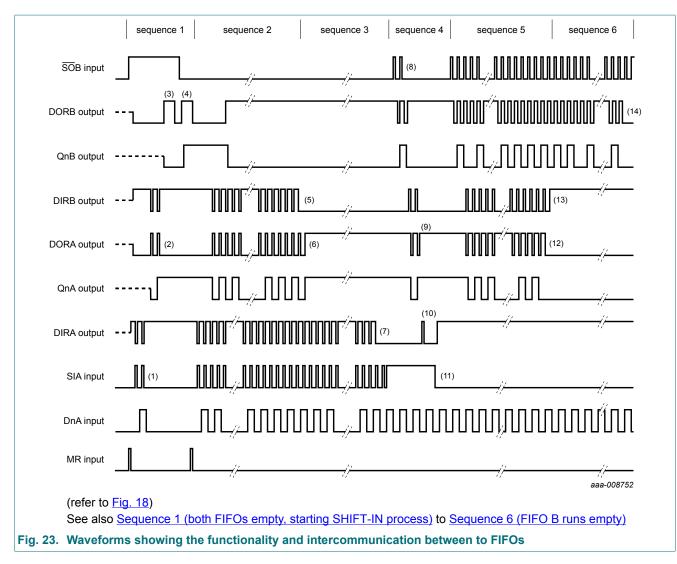

FIFOs handle all necessary communications. Fig. 18 and Fig. 20 demonstrate the communication timing between FIFO A and FIFO B. Fig. 23 provides an overview of pulses and timing of two cascaded FIFOs, when shifted full and shifted empty again.

Fig. 20. Cascading for increased word capacity; 32 words x 4 bits

74HC40105

#### 4-bit x 16-word FIFO register

Fig. 21. FIFO to FIFO communication; input timing under empty condition

74HC40105

#### 4-bit x 16-word FIFO register

(3) DIRB and SOA pulse HIGH; (bubble-up delay after SOB LOW) data is loaded into FIFO B as a result of the DIR pulse, data is shifted out of FIFO A

(4) DORA and SIB go LOW; flag indicates that the output stage of FIFO A is busy, shift-in of FIFO B is complete (5) DORA and SIB go HIGH; flag indicates that valid data is again available at FIFO A output stage, SIB is held HIGH, awaiting bubble-up of empty location.

(6) DIRA goes HIGH; (bubble-up delay after SOA LOW) an empty location is present at input stage of FIFO A

Fig. 22. FIFO to FIFO communication; output timing under full condition

#### 4-bit x 16-word FIFO register

## Sequence 1 (both FIFOs empty, starting SHIFT-IN process)

After an MR pulse has been applied, FIFO A and FIFO B are empty. The DOR flags of FIFO A and FIFO B go LOW due to no valid data being present at the outputs. The DIR flags are set HIGH due to the FIFOs being ready to accept data. SOB is held HIGH and two SIA pulses are applied (1). These pulses allow two data words to ripple through the output stage of FIFO A and the input stage of FIFO B (2). When data arrives at the output of FIFO B, a DORB pulse is generated (3). When SOB goes LOW, the first bit is shifted out and a second bit ripples through to the output after which DORB goes high (4).

### Sequence 2 (FIFO B runs full)

After the MR pulse, a series of 16 SI pulses are applied. When 16 words are shifted in, DIRB remains LOW due to FIFO B being full (5). DORA goes LOW due to FIFO A being empty.

### Sequence 3 (FIFO A runs full)

When 17 words are shifted in, DORA remains HIGH due to valid data remaining at the output of FIFO A. QnA remains HIGH, being the polarity of the 17<sup>th</sup> word (6). After the 32<sup>th</sup> SI pulse, DIR remains LOW and both FIFOs are full (7). Additional pulses have no effect.

#### 4-bit x 16-word FIFO register

## Sequence 4 (both FIFOs full, starting SHIFT-OUT)

SIA is held HIGH and two SOB pulses are applied (8). These pulses shift out two words and thus allow two empty locations to bubble-up to the input stage of FIFO B, and proceed to FIFO A (9). When the first empty location arrives at the input of FIFO A, a DIRA pulse is generated (10) and a new word is shifted into FIFO A. SIA is made LOW and now the second empty location reaches the input stage of FIFO A, after which DIRA remains HIGH (11).

### Sequence 5 (FIFO A runs empty)

At the start of sequence 5, FIFO A contains 15 valid words due to two words being shifted out and one word being shifted in, in sequence 4. And additional series of  $\overline{SOB}$  pulses are applied. After 15  $\overline{SOB}$  pulses, all words from FIFO A are shifted in FIFO B. DORA remains LOW (12).

#### Sequence 6 (FIFO B runs empty)

After the next  $\overline{SOB}$  pulse, DIRB remains HIGH due to the input stage of FIFO B being empty (13). After another 15  $\overline{SOB}$  pulses, DORB remains LOW due to both FIFOs being empty (14). Additional  $\overline{SOB}$  pulses have no effect. The last word remains available at the output Qn.

74HC40105

## 12. Package outline

#### Fig. 24. Package outline SOT109-1 (SO16)

74HC40105

## 13. Abbreviations

| Acronym | Description                             |

|---------|-----------------------------------------|

| CMOS    | Complementary Metal-Oxide Semiconductor |

| DUT     | Device Under Test                       |

| ESD     | ElectroStatic Discharge                 |

| FIFO    | First In First Out                      |

| HBM     | Human Body Model                        |

| MM      | Machine Model                           |

| MSB     | Most Significant Bit                    |

## 14. Revision history

### Table 10. Revision history

| Document ID           | Release date                                                                                                                                                                                                              | Data sheet status                                                                                                                      | Change notice                                               | Supersedes            |  |  |  |

|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|-----------------------|--|--|--|

| 74HC40105 v.5         | 20190419                                                                                                                                                                                                                  | Product data sheet                                                                                                                     | -                                                           | 74HC_HCT40105 v. 4    |  |  |  |

| Modifications:        | of Nexperia.<br>• Legal texts h<br>• Type number<br>• Type number                                                                                                                                                         | f this data sheet has been<br>ave been adapted to the ne<br>r 74HCT40105D (SOT109-<br>rs 74HC40105DB and 74H<br>r 74HC40105PW (SOT403- | ew company nam<br>1) removed.<br>CT40105DB (SO <sup>-</sup> |                       |  |  |  |

| 74HC_HCT40105 v. 4    | 20160129                                                                                                                                                                                                                  | Product data sheet                                                                                                                     | -                                                           | 74HC_HCT40105 v. 3    |  |  |  |

| Modifications:        | Type number                                                                                                                                                                                                               | rs 74HC40105N and 74HC                                                                                                                 | T40105N (SOT38                                              | 3-4) removed.         |  |  |  |

| 74HC_HCT40105 v. 3    | 20130925                                                                                                                                                                                                                  | Product data sheet                                                                                                                     | -                                                           | 74HC_HCT40105_CNV v.2 |  |  |  |

| Modifications:        | <ul> <li>The format of this data sheet has been redesigned to comply with the new identity guidelines of NXP Semiconductors.</li> <li>Legal texts have been adapted to the new company name where appropriate.</li> </ul> |                                                                                                                                        |                                                             |                       |  |  |  |

| 74HC_HCT40105_CNV v.2 | 19980123                                                                                                                                                                                                                  | Product specification                                                                                                                  | -                                                           | -                     |  |  |  |

4-bit x 16-word FIFO register

# 15. Legal information

#### Data sheet status

| Document status<br>[1][2]         | Product<br>status [3] | Definition                                                                                  |

|-----------------------------------|-----------------------|---------------------------------------------------------------------------------------------|

| Objective [short]<br>data sheet   | Development           | This document contains data from<br>the objective specification for<br>product development. |

| Preliminary [short]<br>data sheet | Qualification         | This document contains data from the preliminary specification.                             |

| Product [short]<br>data sheet     | Production            | This document contains the product specification.                                           |

Please consult the most recently issued document before initiating or completing a design.

[2] The term 'short data sheet' is explained in section "Definitions".

[3] The product status of device(s) described in this document may have changed since this document was published and may differ in case of multiple devices. The latest product status information is available on the internet at <u>https://www.nexperia.com</u>.

#### **Definitions**

**Draft** — The document is a draft version only. The content is still under internal review and subject to formal approval, which may result in modifications or additions. Nexperia does not give any representations or warranties as to the accuracy or completeness of information included herein and shall have no liability for the consequences of use of such information.

Short data sheet — A short data sheet is an extract from a full data sheet with the same product type number(s) and title. A short data sheet is intended for quick reference only and should not be relied upon to contain detailed and full information. For detailed and full information see the relevant full data sheet, which is available on request via the local Nexperia sales office. In case of any inconsistency or conflict with the short data sheet, the full data sheet shall prevail.

**Product specification** — The information and data provided in a Product data sheet shall define the specification of the product as agreed between Nexperia and its customer, unless Nexperia and customer have explicitly agreed otherwise in writing. In no event however, shall an agreement be valid in which the Nexperia product is deemed to offer functions and qualities beyond those described in the Product data sheet.

#### **Disclaimers**

Limited warranty and liability — Information in this document is believed to be accurate and reliable. However, Nexperia does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information. Nexperia takes no responsibility for the content in this document if provided by an information source outside of Nexperia.

In no event shall Nexperia be liable for any indirect, incidental, punitive, special or consequential damages (including - without limitation - lost profits, lost savings, business interruption, costs related to the removal or replacement of any products or rework charges) whether or not such damages are based on tort (including negligence), warranty, breach of contract or any other legal theory.

Notwithstanding any damages that customer might incur for any reason whatsoever, Nexperia's aggregate and cumulative liability towards customer for the products described herein shall be limited in accordance with the Terms and conditions of commercial sale of Nexperia.

Right to make changes — Nexperia reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof.

Suitability for use — Nexperia products are not designed, authorized or warranted to be suitable for use in life support, life-critical or safety-critical systems or equipment, nor in applications where failure or malfunction of an Nexperia product can reasonably be expected to result in personal

injury, death or severe property or environmental damage. Nexperia and its suppliers accept no liability for inclusion and/or use of Nexperia products in such equipment or applications and therefore such inclusion and/or use is at the customer's own risk.

**Quick reference data** — The Quick reference data is an extract of the product data given in the Limiting values and Characteristics sections of this document, and as such is not complete, exhaustive or legally binding.

**Applications** — Applications that are described herein for any of these products are for illustrative purposes only. Nexperia makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

Customers are responsible for the design and operation of their applications and products using Nexperia products, and Nexperia accepts no liability for any assistance with applications or customer product design. It is customer's sole responsibility to determine whether the Nexperia product is suitable and fit for the customer's applications and products planned, as well as for the planned application and use of customer's third party customer(s). Customers should provide appropriate design and operating safeguards to minimize the risks associated with their applications and products.

Nexperia does not accept any liability related to any default, damage, costs or problem which is based on any weakness or default in the customer's applications or products, or the application or use by customer's third party customer(s). Customer is responsible for doing all necessary testing for the customer's applications and products using Nexperia products in order to avoid a default of the applications and the products or of the application or use by customer's third party customer(s). Nexperia does not accept any liability in this respect.

Limiting values — Stress above one or more limiting values (as defined in the Absolute Maximum Ratings System of IEC 60134) will cause permanent damage to the device. Limiting values are stress ratings only and (proper) operation of the device at these or any other conditions above those given in the Recommended operating conditions section (if present) or the Characteristics sections of this document is not warranted. Constant or repeated exposure to limiting values will permanently and irreversibly affect the quality and reliability of the device.

Terms and conditions of commercial sale — Nexperia products are sold subject to the general terms and conditions of commercial sale, as published at <u>http://www.nexperia.com/profile/terms</u>, unless otherwise agreed in a valid written individual agreement. In case an individual agreement is concluded only the terms and conditions of the respective agreement shall apply. Nexperia hereby expressly objects to applying the customer's general terms and conditions with regard to the purchase of Nexperia products by customer.

No offer to sell or license — Nothing in this document may be interpreted or construed as an offer to sell products that is open for acceptance or the grant, conveyance or implication of any license under any copyrights, patents or other industrial or intellectual property rights.

**Export control** — This document as well as the item(s) described herein may be subject to export control regulations. Export might require a prior authorization from competent authorities.

Non-automotive qualified products — Unless this data sheet expressly states that this specific Nexperia product is automotive qualified, the product is not suitable for automotive use. It is neither qualified nor tested in accordance with automotive testing or application requirements. Nexperia accepts no liability for inclusion and/or use of non-automotive qualified products in automotive equipment or applications.

In the event that customer uses the product for design-in and use in automotive applications to automotive specifications and standards, customer (a) shall use the product without Nexperia's warranty of the product for such automotive applications, use and specifications, and (b) whenever customer uses the product for automotive applications beyond Nexperia's specifications such use shall be solely at customer's own risk, and (c) customer fully indemnifies Nexperia for any liability, damages or failed product claims resulting from customer design and use of the product for automotive applications beyond Nexperia's standard warranty and Nexperia's product specifications.

**Translations** — A non-English (translated) version of a document is for reference only. The English version shall prevail in case of any discrepancy between the translated and English versions.

#### Trademarks

Notice: All referenced brands, product names, service names and trademarks are the property of their respective owners.

## Contents

| 1. General description              | 1  |

|-------------------------------------|----|

| 2. Features and benefits            | 1  |

| 3. Ordering information             | 1  |

| 4. Functional diagram               | 2  |

| 5. Pinning information              | 3  |

| 5.1. Pinning                        | 3  |

| 5.2. Pin description                | 4  |

| 6. Functional description           | 4  |

| 6.1. Inputs and outputs             | 4  |

| 6.2. Data input                     | 5  |

| 6.3. Data transfer                  | 5  |

| 6.4. Data output                    | 5  |

| 6.5. High-speed burst mode          | 5  |

| 6.6. Expanded format                | 6  |

| 7. Limiting values                  | 6  |

| 8. Recommended operating conditions | 6  |

| 9. Static characteristics           | 7  |

| 10. Dynamic characteristics         | 8  |

| 10.1. Waveforms and test circuit    | 11 |

| 11. Application information         | 18 |

| 11.1. Expanded format               | 19 |

| 12. Package outline                 | 24 |

| 13. Abbreviations                   | 25 |

| 14. Revision history                | 25 |

| 15. Legal information               | 26 |

© Nexperia B.V. 2019. All rights reserved

For more information, please visit: http://www.nexperia.com For sales office addresses, please send an email to: salesaddresses@nexperia.com Date of release: 19 April 2019

**Product data sheet**

# **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Registers category:

Click to view products by Nexperia manufacturer:

Other Similar products are found below :

31-5369 74SSTUBF32869ABKG8 74HC40105D.652 74HC595D 74FCT162374ATPAG 74FCT162374ATPVG8 74FCT162374CTPAG 74FCT162374ETPAG 74FCT16374ATPVG 74FCT374CTSOG 74FCT574ATQG 74HC670N SY100E452JY SY10E143JZ 74HC40105D,653 PCA8550PW,118 MC14549BDWR2G MC14559BDWR2G MC100E143FNG MC10E143FNR2G MC14559BCPG CD74HC670E 5962-9221802MRA PCA8550DB,118 74FCT16374ATPAG 74HC670D,652 5962-9221806M2A 74HC7030N 74HCT280N 74HC40105N CD40105BE CD74HC40105E CD74HC40105M96 CD74HC670M96 CD74HCT40105E CD74HCT40105M CD74HCT670E CD74HC670M SN74LS670NSR