# nRF24AP2

nRF24AP2-1CH, nRF24AP2-8CH

# Single-chip ANT<sup>TM</sup> ultra-low power wireless network solution

# Product Specification v1.2

## **Key Features**

- Second generation single chip ANT solution

- nRF24AP2-1CH supports 1 ANT (logic) channel – ideal for sensors

- nRF24AP2-8CH supports up to eight ANT (logic) channels – ideal for hubs

- World wide 2.4 GHz ISM band operation

- Fully embedded, enhanced ANT protocol stack

- True ultra-low power operation

- · Typically years of battery lifetime on a coin cell

- · Built-in device search and pairing

- · Built-in timing and power management

- · Built-in interference handling

- Configurable channel period 5.2 ms 2 s

- Broadcast, Acknowledged and Burst communication modes

- Burst data rate up to 20 kbps

- Simple to complex network topologies:

Peer-to-peer, star, tree and practical mesh

- Supports public, private and managed networks

- Support for ANT+ device profile implementations enabling multivendor interoperability

- Fully interoperable with nRF24AP1 and Dynastream ANT chipset / module based products and other nRF24AP2 variants

- Simple asynchronous/ synchronous host interface

- Single 1.9 3.6V power supply

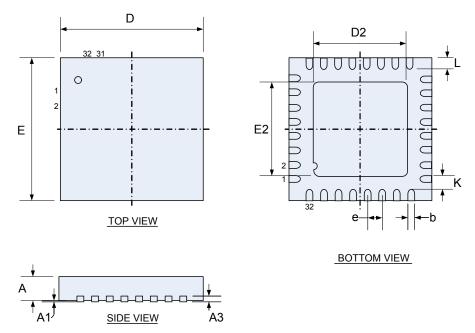

- RoHS compliant 5×5 mm 32-pin QFN package

- Low cost external 16 MHz crystal

- Optional on-chip 32.768 kHz crystal oscillator

## **Applications**

- Sports

- Wellness

- · Home health monitoring

- Home/industrial automation

- Environmental sensor networks

- · Active RFID

- · Logistics/goods tracking

- · Audience-response systems

# Liability disclaimer

Nordic Semiconductor ASA reserves the right to make changes without further notice to the product to improve reliability, function or design. Nordic Semiconductor ASA does not assume any liability arising out of the application or use of any product or circuits described herein.

All application information is advisory and does not form part of the specification.

# **Limiting values**

Stress above one or more of the limiting values may cause permanent damage to the device. These are stress ratings only and operation of the device at these or at any other conditions above those given in the specifications are not implied. Exposure to limiting values for extended periods may affect device reliability.

# Life support applications

Nordic Semiconductor's products are not designed for use in life support appliances, devices, or systems where malfunction of these products can reasonably be expected to result in personal injury. Nordic Semiconductor ASA customers using or selling these products for use in such applications do so at their own risk and agree to fully indemnify Nordic Semiconductor ASA for any damages resulting from such improper use or sale.

| Datasheet status                  |                                                                          |

|-----------------------------------|--------------------------------------------------------------------------|

| Objective product specification   | This product specification contains target specifications for Nordic     |

|                                   | Semiconductor's product development.                                     |

| Preliminary product specification | This product specification contains preliminary data; supplementary      |

|                                   | data may be published from Nordic Semiconductor ASA later.               |

| Product specification             | This product specification contains final product specifications. Nordic |

|                                   | Semiconductor ASA reserves the right to make changes at any time         |

|                                   | without notice in order to improve design and supply the best possible   |

|                                   | product.                                                                 |

#### **Contact details**

For your nearest dealer, please see www.nordicsemi.com.

#### Main office:

Otto Nielsens veg 12 7004 Trondheim Phone: +47 72 89 89 00 Fax: +47 72 89 89 89

www.nordicsemi.com

#### **RoHS statement**

Nordic Semiconductor's products meets the requirements of Directive 2002/95/EC of the European Parliament and of the Council on the Restriction of Hazardous Substances (RoHS). Complete hazardous substance reports as well as material composition reports for all active Nordic Semiconductor products can be found on our web site <a href="https://www.nordicsemi.com">www.nordicsemi.com</a>.

# **Revision History**

| Date       | Version | Description                                 |  |  |  |

|------------|---------|---------------------------------------------|--|--|--|

| April 2010 | 1.1     | Updated schematics. Added section 2.4.1     |  |  |  |

|            |         | on page 12, updated sections 8.1 on page    |  |  |  |

|            |         | 43 and 8.2 on page 46.                      |  |  |  |

| June 2010  | 1.2     | Updated sections 2.1 on page 8 and 2.4 on   |  |  |  |

|            |         | page 11, Table 4. on page 22, section 4.2.2 |  |  |  |

|            |         | on page 16, section 8.1 on page 43, and     |  |  |  |

|            |         | chapter 11 on page 49.                      |  |  |  |

# **Contents**

| 1                      | Introduction                                                         | 6              |

|------------------------|----------------------------------------------------------------------|----------------|

| 1.1                    | Prerequisites                                                        | 6              |

| 1.2                    | Writing conventions                                                  | 6              |

| 2                      | Product overview                                                     | 7              |

| 2.1                    | Features                                                             | 8              |

| 2.2                    | Block diagram                                                        | 9              |

| 2.3                    | Pin Assignments                                                      | 10             |

| 2.4                    | Pin Functions                                                        |                |

| 2.4.1                  | Reset pin                                                            | 12             |

| 3                      | RF Transceiver                                                       |                |

| 3.1                    | Features                                                             |                |

| 3.2                    | Block diagram                                                        |                |

| 4                      | ANT overview                                                         |                |

| 4.1                    | Block diagram                                                        |                |

| 4.2                    | Functional description                                               |                |

| 4.2.1                  |                                                                      |                |

| 4.2.2                  |                                                                      |                |

| 4.2.3                  | <b>5</b>                                                             |                |

| 4.2.4                  |                                                                      |                |

| 4.2.5                  | 9                                                                    |                |

| 4.2.6                  |                                                                      |                |

| 4.2.7                  | 3 P                                                                  |                |

| 5                      | Host interface                                                       |                |

| 5.1                    | Features                                                             |                |

| 5.2                    | Asynchronous serial interface                                        |                |

| 5.2.1                  |                                                                      |                |

| 5.2.2                  |                                                                      |                |

| 5.2.3                  | , , , , , , , , , , , , , , , , , , , ,                              |                |

| 5.2.4                  |                                                                      |                |

| 5.2.5                  | 1                                                                    |                |

| 5.3                    | Synchronous serial interface                                         |                |

| 5.3.1                  | 3                                                                    |                |

| 5.3.2                  | ,                                                                    |                |

| 5.3.3                  | -,                                                                   |                |

| 5.3.4                  | , , , , , , , , , , , , , , , , , , , ,                              |                |

| 5.3.5                  | ,                                                                    |                |

| 5.3.6                  | , , , , , , , , , , , , , , , , , , , ,                              |                |

| 5.3.7                  | Serial enable control                                                | .,,,           |

|                        |                                                                      |                |

| 6                      | On-chip oscillator                                                   | 34             |

| <b>6</b><br>6.1        | On-chip oscillatorFeatures                                           | 3 <b>4</b>     |

| <b>6</b><br>6.1<br>6.2 | On-chip oscillatorFeaturesBlock diagrams                             | 34<br>34<br>34 |

| <b>6</b><br>6.1        | On-chip oscillator  Features  Block diagrams  Functional description | 34<br>34<br>34 |

# nRFAP2 Product Specification

| 6.3.2 | External 16 MHz clock              | 36 |

|-------|------------------------------------|----|

| 6.3.3 | 32.768 kHz crystal oscillator      | 36 |

| 6.3.4 | Synthesized 32.768 kHz clock       | 36 |

| 6.3.5 | External 32.768 kHz clock          | 37 |

| 7     | Operating conditions               | 38 |

| 8     | Electrical specifications          | 40 |

| 8.1   | Current consumption                | 43 |

| 8.2   | Current calculations examples      | 46 |

| 9     | Absolute maximum ratings           | 47 |

| 10    | Mechanical specification           | 48 |

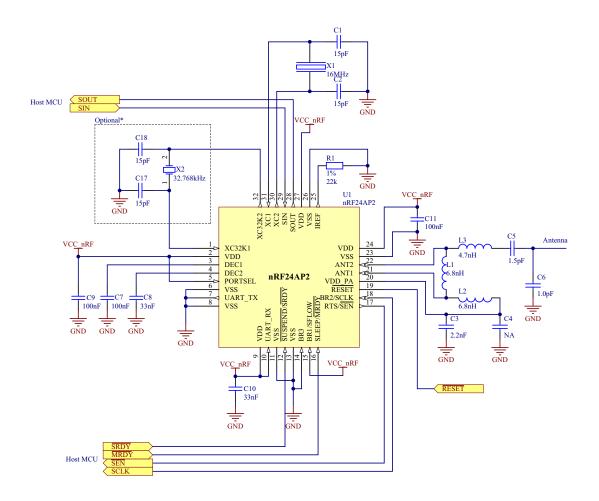

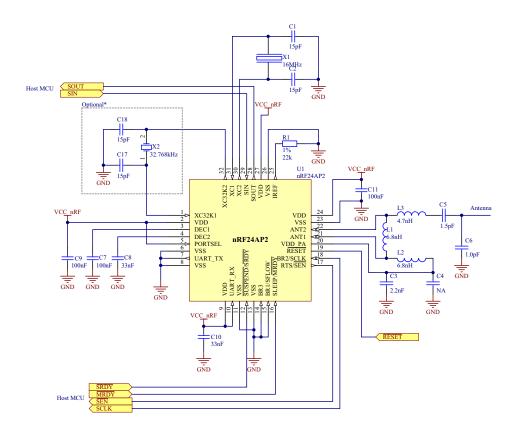

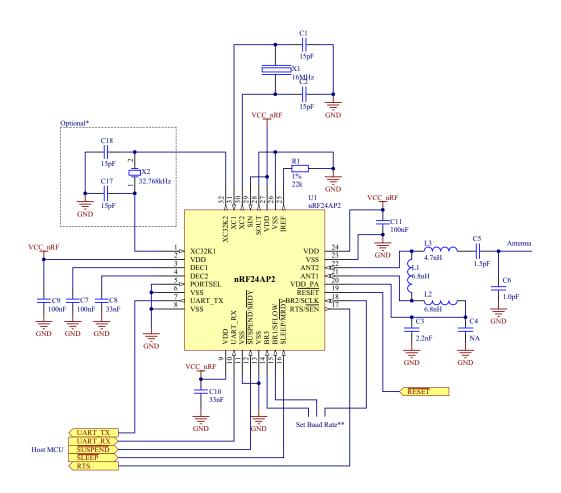

| 11    | Reference circuitry                | 49 |

| 11.1  | PCB guidelines                     | 49 |

| 11.2  | Synchronous (bit) mode schematics  | 50 |

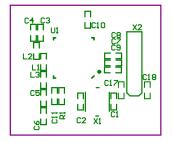

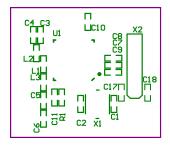

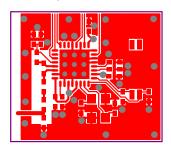

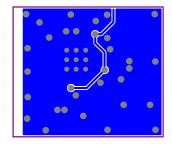

| 11.3  | Layout                             | 51 |

| 11.4  | Synchronous (byte) mode schematics | 52 |

| 11.5  | Layout                             |    |

| 11.6  | Asynchronous mode schematics       | 54 |

| 11.7  | Layout                             |    |

| 11.8  | Bill Of Materials (BOM)            | 55 |

| 12    | Ordering information               | 56 |

| 12.1  | Package marking                    | 56 |

| 12.1. | 1 Abbreviations                    | 56 |

| 12.2  | Product options                    |    |

| 12.2. |                                    | 56 |

| 12.2. | 2 Development tools                | 57 |

| 13    | Glossary                           | 58 |

#### 1 Introduction

nRF24AP2 is a member of Nordic Semiconductor's low-cost, high-performance family of 2.4 GHz ISM single-chip connectivity devices with the ANT protocol stack embedded. nRF24AP2 offers the market's most efficient, single chip, transceiver solution for Ultra Low Power (ULP) networks, through the integration of the extremely power efficient ANT protocol stack, the world leading Nordic Semiconductor 2.4 GHz RF technology as well as critical low-power oscillator and timing features.

This document covers the two products:

- nRF24AP2-1CH

- nRF24AP2-8CH

#### 1.1 Prerequisites

In order to fully understand the product specification, a good knowledge of electronics and software engineering is necessary. Please also refer to the document *ANT Message Protocol and Usage* when reading this product specification. You can download the document from Nordic's web site <a href="https://www.nordicsemi.com">www.nordicsemi.com</a> or from <a href="https://www.nordicsemi.com">www.thisisant.com</a>.

# 1.2 Writing conventions

This product specification follows a set of typographic rules to ensure that the document is consistent and easy to read. The following writing conventions are used:

- Commands, bit state conditions, and register names are written in Courier New.

- Pin names and pin signal conditions are written in Courier New bold.

- Cross references are underlined and highlighted in blue.

#### 2 Product overview

ANT is a demonstrably superior Wireless Sensor Network (WSN) RF protocol for almost all practical ultralow power networking applications – from simple point-to-point links to complex networks. Embedded in nRF24AP2 devices, it is paired up with Nordic Semiconductor's market leading 2.4 GHz radio technology. The combination gives you high performance, ultra-low-power network connectivity to applications, and requires minimal resources in the application's microcontroller. Less than 1 kB of code space, and an Asynchronous or Synchronous serial interface are all it takes to enable ANT connectivity in your application.

The nRF24AP2 variants meet the specific requirements of end nodes and central nodes in a network. nRF24AP2-1CH offers one logic communication channel (ANT channel) for end nodes like sensors to connect to data collectors. nRF24AP2-8CH can manage up to eight ANT channels to collect data from multiple sensors.

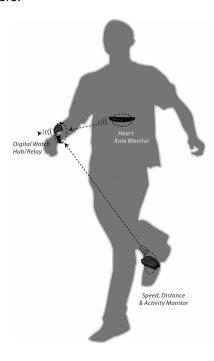

<u>Figure 1.</u> shows a network in which a network node with nRF24AP2-8CH embedded, communicates with ANT nodes with nRF24AP2-1CH devices embedded. An example might be a sports watch collecting data from several sensors (like heart rate-, speed- and distance sensors). Of course, the 8-channel node can also set up ANT channels with other central nodes (gym equipment, for instance). These central nodes are in turn connected to additional sensors.

Figure 1. Simple setup with nRF24AP2

See <u>Figure 10. on page 21</u> for more complex ANT-network topologies.

#### 2.1 Features

Features of the 1-channel nRF24AP2-1CH and 8-channel nRF24AP2-8CH include:

- Ultra low power 2.4 GHz transceiver

- World wide 2.4 GHz ISM band operation

- · Based on nRF24L01+ transceiver

- GFSK modulation

- 1 Mbps on-air data rate

- 1 MHz frequency resolution

- 78 RF channels

- -85 dBm sensitivity

- Up to 0 dBm output power

- ANT protocol stack

- Full implementation of the physical, data link, network- and transport OSI layers

- Packet-based communication 8 byte payload per packet

- Optimized for ultra-low power operation

- ANT channels

- Logic communication channel between ANT nodes

- nRF24AP2-1CH supports 1 channel

ideal for sensors

- nRF24AP2-8CH support up to 8 channels – ideal for hubs

- · Built-in timing and power management

- · Built-in interference handling

- Configurable channel period

5.2 ms 2 s

- Broadcast, acknowledged and burst communication modes

- · Burst data rate up to 20 kbps

- Device search and pairing

- Wild-card searches

- · Proximity searches

- · Specific searches

- Automatic link establishment if correct device is found

- Automatic re-link attempt if link is lost

- · Configurable search timeout

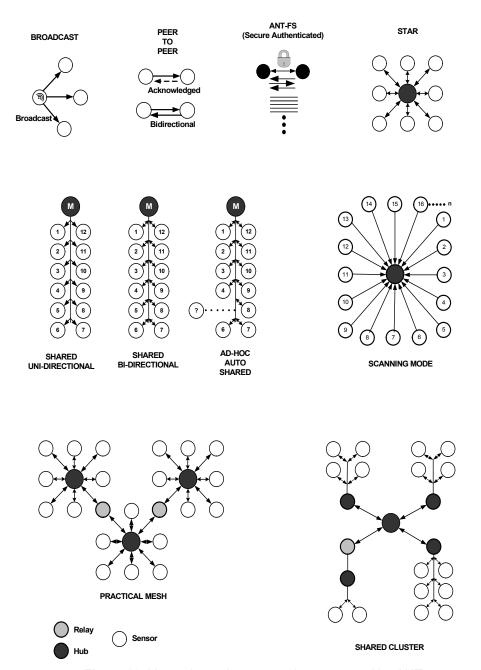

- Network topologies

- Point-to- point and star networks using independent ANT channels

- Shared networks: Polled data collection (N:1) by using ANT shared channel option

- Broadcast networks: Mass distribution of data (1:N)

- · Network management / ANT+

- Supports public and private (managed) networks

- Support for ANT+ system implementations enabling multi-vendor interoperability

- · ANT core stack enhancements

- · Background scanning channel

- · Continuous scanning mode

- · High density node support

- Improved channel search

- Channel ID management

- Improved transmission power control on a per channel basis

- · Frequency agility

- · Proximity search

- Power Management

- · Fully controlled by ANT protocol stack

- On-chip voltage regulator

- · Single DC supply operation

- 1.9 to 3.6V supply range

- Ultra low power operation

- Up to 50% lower average compared to nRF24AP1

- Up to 40% lower peak current compared to nRF24AP1

- 20 µA average current consumption at 1 Hz broadcast

- 71 µA average current consumption at 4 Hz broadcast

- On-chip oscillators and clock inputs

- 16 MHz crystal oscillator supporting low-cost crystals

- · 16 MHz clock input

- Ultra low power 32.768 kHz crystal oscillator

- 32.768 kHz clock input

- Host interface

- Supports asynchronous and synchronous modes

- 5-pins for asynchronous

- 6-pins for synchronous

# 2.2 Block diagram

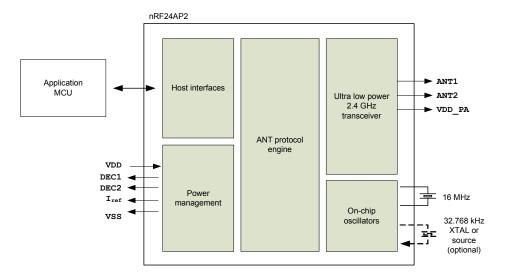

nRF24AP2 is composed of five main blocks as shown in <u>Figure 2</u>. The blocks indicate the interface, power management, the ANT protocol engine, on-chip oscillators and the RF transceiver.

Figure 2. Block diagram of nRF24AP2 solution

To find more information about each block in the diagram, see <u>Table 1</u>.

| Name                | Reference            |

|---------------------|----------------------|

| RF Transceiver      | Chapter 3 on page 13 |

| ANT protocol engine | Chapter 4 on page 15 |

| Host interfaces     | Chapter 5 on page 23 |

| On-chip oscillators | Chapter 6 on page 34 |

| Power management    | Chapter 8 on page 40 |

Table 1. Block diagram cross references

# 2.3 Pin Assignments

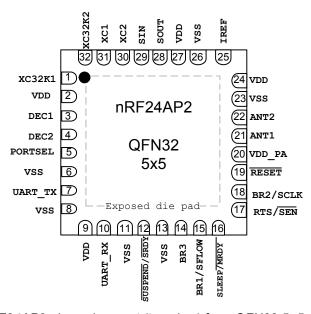

Figure 3. nRF24AP2 pin assignment (top view) for a QFN32 5×5 mm package

# 2.4 Pin Functions

| Pin | Pin name                               | Pin functions                         | Description                                                                     |  |  |

|-----|----------------------------------------|---------------------------------------|---------------------------------------------------------------------------------|--|--|

| 1   | XC32K1                                 | Analog input                          |                                                                                 |  |  |

|     |                                        |                                       | optionally a synthesized or external 32.768 kHz clock                           |  |  |

|     |                                        |                                       | can be used as described in <u>chapter 6 on page 34</u>                         |  |  |

| 2   | VDD                                    | Power                                 | Power Supply (1.9-3.6V DC)                                                      |  |  |

| 3   | DEC1                                   | Power                                 | Power supply outputs for de-coupling purposes                                   |  |  |

|     |                                        |                                       | (100nF)                                                                         |  |  |

| 4   | DEC2                                   | Power                                 | Power supply outputs for de-coupling purposes                                   |  |  |

|     |                                        |                                       | (33nF)                                                                          |  |  |

| 5   | PORTSEL                                | Digital input                         | Port Select                                                                     |  |  |

|     |                                        |                                       | Asynchronous serial interface: Tie to VSS                                       |  |  |

|     |                                        |                                       | Synchronous serial interface: Tie to VDD                                        |  |  |

| 6   | VSS                                    | Power                                 | Ground (0V)                                                                     |  |  |

| 7   | UART_TX                                | Digital IO                            | Asynchronous mode: Transmit data signal                                         |  |  |

|     |                                        |                                       | Synchronous mode: Tie to VSS or VDD.                                            |  |  |

| 8   | VSS                                    | Power                                 | Ground (0V)                                                                     |  |  |

| 9   | VDD                                    | Power                                 | Power Supply (1.9-3.6V DC)                                                      |  |  |

| 10  | UART_RX                                | Digital input                         | Asynchronous mode: Receive data signal                                          |  |  |

| 44  |                                        | Davisa                                | Synchronous mode: Tie to VDD                                                    |  |  |

| 11  | VSS                                    | Power                                 | Ground (0V)                                                                     |  |  |

| 12  |                                        | Digital input                         | Asynchronous mode: Suspend control                                              |  |  |

| 40  | SUSPEND/SRDY                           | Power                                 | Synchronous mode: Serial port ready                                             |  |  |

| 13  | VSS                                    |                                       | Ground (0V)                                                                     |  |  |

| 14  | BR3                                    | Digital input                         | Asynchronous mode: Baud rate selection                                          |  |  |

| 45  | DD1 /077 077                           | Digital innest                        | Synchronous mode: Tie to VSS                                                    |  |  |

| 15  | BR1/SFLOW                              | Digital input                         | Asynchronous mode: Suspend Control                                              |  |  |

|     |                                        |                                       | Synchronous mode: Bit or Byte flow control select (Bit:                         |  |  |

| 16  |                                        | Digital input                         | Tie to VDD, Byte: Tie to VSS)                                                   |  |  |

| 10  | OT EED/MDDV                            | Digital input                         | Asynchronous mode: Sleep mode enable Synchronous mode: Message ready indication |  |  |

| 17  | SLEEP/MRDY                             | Digital output                        | Asynchronous mode: Request to send                                              |  |  |

| 17  | RTS/SEN                                | Digital output                        | Synchronous mode: Request to send Synchronous mode: Serial enable signal        |  |  |

| 18  | BR2 / SCLK                             | Digital IO                            | Asynchronous mode: Baud rate selection                                          |  |  |

| 10  | BRZ / SCLR                             | Digital 10                            | Synchronous mode: Clock output signal                                           |  |  |

| 19  |                                        | Digital input                         | Reset, active low. Internal pull up. Leave unconnected                          |  |  |

| 13  | RESET                                  | Digital Input                         | if not used.                                                                    |  |  |

| 20  | VDD PA                                 | Power output                          | Power supply output (+1.8V) for on-chip RF Power                                |  |  |

| 20  | ************************************** | i oveci output                        | amplifier                                                                       |  |  |

| 21  | ANT1                                   | RF                                    | Differential antenna connection (TX and RX)                                     |  |  |

| 22  | ANT2                                   | RF                                    | Differential antenna connection (TX and TXX)                                    |  |  |

| 23  | VSS                                    | Power                                 | Ground (0V)                                                                     |  |  |

| 24  | VDD                                    | Power                                 | Power Supply (1.9-3.6V DC)                                                      |  |  |

| 25  | IREF                                   | Analog output                         | , , , ,                                                                         |  |  |

|     |                                        | i i i i i i i i i i i i i i i i i i i | reference resistor on PCB.                                                      |  |  |

| 26  | vss                                    | Power                                 | Ground (0V)                                                                     |  |  |

| 27  | VDD                                    | Power                                 | Power Supply (1.9-3.6V DC)                                                      |  |  |

| 28  | SOUT                                   | Digital IO                            | Asynchronous mode: Tie to VSS or VDD.                                           |  |  |

|     |                                        | 3                                     | Synchronous mode: Data output                                                   |  |  |

| 29  | SIN                                    | Digital input                         | Asynchronous mode: Tie to VDD                                                   |  |  |

|     |                                        |                                       | Synchronous mode: Data input                                                    |  |  |

| 30  | XC2                                    | Analog output                         | Crystal connection for 16 MHz crystal oscillator                                |  |  |

|     | ACZ                                    | , andiog output                       | Signal confidence for the will be digital confiden                              |  |  |

# nRFAP2 Product Specification

| Pin             | Pin name | Pin functions | Description                                                                                                                                                  |

|-----------------|----------|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31              | XC1      | Analog Input  | Crystal connection for 16 MHz crystal oscillator                                                                                                             |

| 32              | XC32K2   |               | Crystal connection for 32.768 kHz crystal oscillator, optionally a synthesized or external 32.768 kHz clock can be used as described in chapter 6 on page 34 |

| Exposed die pad | VSS      | Power         | Connects the die pad to vss                                                                                                                                  |

Table 2. nRF24AP2 pin functions

# 2.4.1 Reset pin

The **RESET** pin provides an optional reset when the nRF24AP2 is placed in a system that has a master reset source. This pin is not needed for normal application. Pull **RESET** pin low for minimum 0.2 µs and return to high, this will reset the nRF24AP2 to the default state. Leave unconnected if not used in the application.

#### 3 RF Transceiver

All transceiver operations are controlled solely by the ANT protocol stack. Configuration of the ANT protocol stack occurs through a serial interface by issuing ANT commands to nRF24AP2.

#### 3.1 Features

Features of the RF transceiver include:

- General

- Worldwide 2.4 GHz ISM band operation

- · Common antenna interface in transmit and receive

- GFSK modulation

- 1 Mbps on air data rate

- Transmitter

- Programmable output power: 0, -6, -12 or -18 dBm

- Receiver

- · Integrated channel filters

- · -85 dBm sensitivity

- RF Synthesizer

- Fully integrated synthesizer

- 1 MHz frequency programming resolution

- 78 RF channels in the 2.4 GHz ISM band

- Accepts low cost ± 50 ppm 16 MHz crystal

- 1 MHz non-overlapping channel spacing

# 3.2 Block diagram

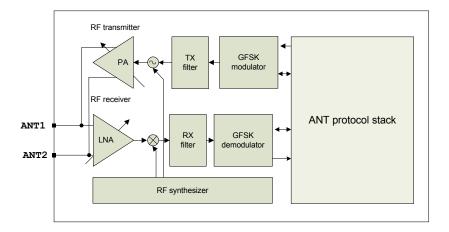

Figure 4. shows a block diagram of the RF transceiver in nRF24AP2.

Figure 4. Internal circuitry of RF transceiver relative to ANT

#### 4 ANT overview

The ANT protocol has been engineered for simplicity and efficiency. In operation, this results in ultra-low power consumption, maximized battery life, a minimal burden on system resources, simpler network designs and lower implementation costs.

# 4.1 Block diagram

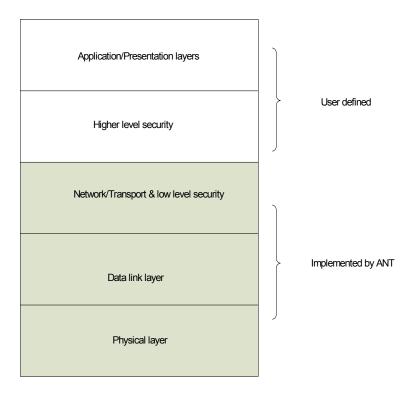

Figure 5. OSI layer model of ANT protocol stack

ANT provides carefree handling of the Physical, Data Link, Network, and Transport OSI layers. See <u>Figure 5.</u> In addition, it incorporates key, low-level security features that form the foundation for user-defined, sophisticated, network-security implementations. ANT ensures adequate user control while considerably easing the computational burden, by providing a simple yet effective wireless networking solution.

# 4.2 Functional description

A brief overview of the ANT concept is presented here for convenience. A complete description of the ANT protocol is found in the ANT Message Protocol and Usage document available at <a href="https://www.nordicsemi.com">www.nordicsemi.com</a> or <a href="https://www.nordicsemi.com"

#### 4.2.1 ANT nodes

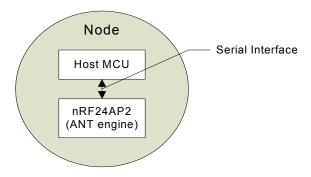

All ANT networks are built up of nodes. See the ANT node represented in <u>Figure 6</u>. on <u>page 16</u>. A node can be anything from a simple sensor to a complex, collection unit like a watch or computer. Common to all

nodes is that they contain an ANT engine (nRF24AP2) handling all connectivity to other nodes and a host processor handling the application features. nRF24AP2 interfaces to the host processor through a serial interface, and all configuration and control are performed using a simple command library.

Figure 6. The ANT node

#### 4.2.2 ANT channels

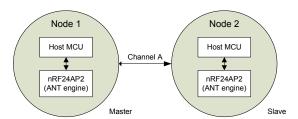

nRF24AP2 can establish one or up to eight logic channels, called ANT channels, to other ANT nodes. The number of ANT channels available depends on the nRF24AP2 variant being used.

Figure 7. ANT nodes and the channel between them

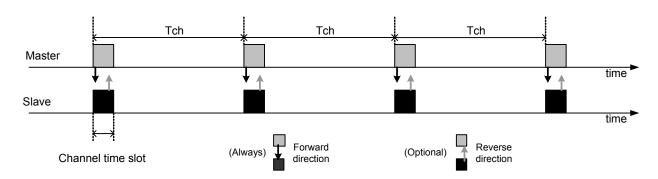

The simplest ANT channel is called an independent channel and consists of two nodes, one acting as master, the other as slave for this channel. For each ANT channel opened, nRF24AP2 will set up and manage a synchronous wireless link, exchanging data packets with other ANT nodes at preset time intervals called channel periods. See <a href="Figure 8.">Figure 8.</a> on <a href="page 17">page 17</a>. The master controls the timing of a channel, that is to say, it will always initiate communication between the nodes. The slave locks on to the timing set by the master, receives the transmissions from the master and can then (if configured so) send acknowledge and/or data (if any) back to the master.

Figure 8. Channel communication showing forward and reverse directions. Not to scale

At each time slot an ANT channel can transfer user data (8 bytes) both ways as simple broadcasts, broadcast with acknowledgement from the receiver, or transfer data as bursts (this will extend the time slot used) to accommodate transfer of larger blocks of user data. The total available payload bandwidth in an ANT node is shared between active ANT channels through a Time Division Multiple Access (TDMA) scheme. If a channel time slot comes up, but there is no new data from the master. The master will still send the last packet to keep the timing of the channel and enable the slave to send data back if needed.

Each ANT channel available in the nRF24AP2 can for example be configured as a simple, uni-directional (broadcast) or bi-directional independent channel; or as a more complex, shared channel where a master interfaces to multiple slaves (1:N topologies). Please see the ANT Message Protocol and Usage document for further details on shared ANT channels.

#### 4.2.3 ANT channel configuration

Unique to ANT is that the setup of each ANT channel is independent from all the other ANT channels in the network, including other channels in the same node. This means that one ANT node can act as master on one ANT channel while being a slave to another. Since there is no overall 'network master' present in ANT networks, ANT allows you to configure and run each ANT channel solely based on the needs of the nodes on that channel. Search- and pairing algorithms in ANT let you easily set up and shut down ANT channels in an ad-hoc fashion. This gives you ultimate flexibility in adjusting ANT channel parameters like data rate and latency versus power consumption. Moreover, you only make the network as complex as it needs to be at any given time. In order for two ANT nodes to set up an ANT channel, they must share a common channel configuration and channel ID. The necessary configuration parameters are summarized in <a href="Table 3. on page 18">Table 3. on page 18</a>.

| Parameter         | Comment                                                 |  |  |  |

|-------------------|---------------------------------------------------------|--|--|--|

|                   | Channel configuration                                   |  |  |  |

| Channel period    | Time interval between data exchanges on this            |  |  |  |

|                   | channel (5.2 ms - 2 s)                                  |  |  |  |

| RF frequencies    | Which of the 78 available RF frequencies is used        |  |  |  |

|                   | by this channel                                         |  |  |  |

| Channel type      | Bi-directional slave, bi-directional master, shared     |  |  |  |

|                   | bi-directional slave, Slave Receive only                |  |  |  |

| Network type      | Network type Decides if this ANT channel is going to be |  |  |  |

|                   | generally accessible (public) to all ANT nodes, or if   |  |  |  |

|                   | it shall limit its connectivity to devices belonging to |  |  |  |

|                   | a managed or private network                            |  |  |  |

|                   | Channel ID                                              |  |  |  |

| Transmission type | 1 byte – Identifying characteristics of the             |  |  |  |

|                   | transmission, can for instance contain codes on         |  |  |  |

|                   | how payload is to be interpreted                        |  |  |  |

| Device type       | 1 byte - ID to identify the device type of the          |  |  |  |

|                   | channel master (Ex: heart rate belt, temperature        |  |  |  |

|                   | sensor etc.)                                            |  |  |  |

| Device number     | 2 byte - Unique ID for this channel                     |  |  |  |

Table 3. ANT channel ID

The channel configuration parameters are static, system parameters that must match in the master and slave, and the channel ID is included in all transmissions identifying the two nodes for each other. For indepth details on each parameter please refer to *ANT Message Protocol and Usage*.

#### Network

In addition to setting the content of the channel ID, which is the primary ID of an ANT node, ANT nodes can limit their connectivity to a selection of other ANT nodes by defining a network for each ANT channel. The limited access to certain networks is managed through unique network keys

The defined ANT networks are:

- 1. **Public networks:** These are open ANT networks with no limitation on connectivity. All ANT nodes sharing the same channel configuration (by design or by accident) will be able to connect. This is the default setting in nRF24AP2.

- 2. Managed networks: These are ANT networks managed by special interest groups or alliances. An example is the ANT+ alliance for sport and wellness products. To join the ANT+ alliance, visit <a href="https://www.thisisant.com">www.thisisant.com</a>. By joining the ANT+ alliance and complying with the ANT+ device profiles set by the alliance, you achieve two goals:

- Limited connectivity: Only other ANT+ compliant devices can connect to this channel.

- Interoperability: Your node can connect to ANT+ compliant products from other vendors.

- 3. **Private networks:** Your own protected networks, and no other devices, will be able to connect to your ANT nodes unless you share the network key with someone outside the network. Please note that this requires purchase of a unique network key from ANT, see <a href="https://www.thisisant.com">www.thisisant.com</a>.

Since the network parameter can be chosen independently for each ANT channel, one ANT node (1 nRF24AP2-8CH) can have up to eight ANT channels, operating on different networks at the same time.

**Note:** The network parameter has no impact on the network topologies you can build. It is merely a tool to protect your ANT network and prevent accidental or deliberate access from other ANT nodes.

#### Channel ID, search and pairing

The primary parameters which two ANT nodes use to identify each other make up the **channel ID**. Once an ANT channel is established, the **channel ID parameters** must of course match; but they don't have to be known by both nodes (pre-configured) to be able to establish an ANT channel.

When an nRF24AP2 configured as a master (set in channel type) opens an ANT channel, it will broadcast its entire **channel ID**. Hence you must configure all three **channel ID** parameters before opening an ANT channel as a master.

On the other hand, in a slave you can configure nRF24AP2 to search for and connect with both known and unknown masters. To connect with a known master you must configure the **Transmission type**, **Device type** and **Device number** in nRF24AP2 before opening the ANT channel.

You can also configure the nRF24AP2 to conduct wild-card searches on one or more of the three parameters in the **channel ID** to enable it to pair up with unknown masters. You can for instance set only the **Device type** of the masters you want to link up with, and set wild cards on the **Transmission type** and **Device number**. If a new master with a matching **Device type** is found, the slave device will connect and store the unknown parts of the **channel ID**. The new parts of the **channel ID** can then be stored in the host MCU to enable specific searches for this master later.

#### 4.2.4 Proximity search

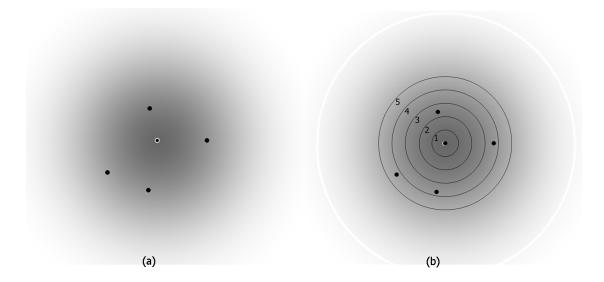

When using the basic search and pairing algorithm a slave will automatically identify and connect to the first master it finds matching the search criteria. In areas where you either have a high density of similar master nodes or high density of independent ANT networks, there is always the chance that multiple masters are found within the coverage area. This presents the risk that it is not the master you wanted to connect to that is found first. The proximity search feature in ANT designates 'bins' of proximity from 1 (closest) to 10 (furthest) as shown in Figure 9.

Figure 9. Standard search (a), Proximity search (b), showing bins 1-5 (of maximum 10)

This 'binning' enables you to further control your search by for instance only accepting the master that is closest (only accept masters that fall in bin 1-2). This makes it easy for a user to pair up network nodes and prevent accidental connection to nodes possibly belonging to another network close by.

#### 4.2.5 Continuous scanning mode

Continuous scanning mode allows for fully asynchronous communication between an ANT node using continuous scanning mode, and any other ANT node using a standard master channel. This has two main advantages over only using standard ANT channels. The first is that the latency to initiate communication with the scanning node is reduced to zero and every message sent by a master channel in proximity will be received by the scanning device. Secondly, the requirement to maintain communication for the purpose of synchronization while in proximity is removed. This means that it is possible for nodes to come and go very quickly or to turn off for long periods of time in between communication events. This saves power on the transmitting node.

The disadvantage of continuous scanning mode is that it consumes much more power than standard ANT channels and will therefore only typically be used on devices that are plugged in and not mobile such as a computer (USB dongle). Another disadvantage is that a node in scanning mode can no longer be configured to have discoverable master channels because scanning mode disables standard ANT channel functionality. It is worth noting that two ANT nodes in scanning mode cannot communicate with one another because neither will be able to spontaneously generate communication.

Standard ANT channels are recommended over scanning channels, even in dynamic systems where devices are coming and going. This is because scanning channels are not recommended for mobile networks which is the primary area of application for ANT. Scanning channels will typically be used in statically located networks where the scanning channel node is plugged in and not mobile.

#### 4.2.6 ANT network topologies

By combining ANT channels with different features depending on local needs, you can build anything from very simple peer-to-peer links and star networks to complex networks as shown in <u>Figure 10</u>. on page 21.

Figure 10. Network topology examples supported by ANT

# 4.2.7 ANT message protocol

All the configuration and control of the various ANT node and channel parameters in nRF24AP2 are handled by the host microcontroller over a simple serial interface by using the command library. See the document *ANT Message Protocol and Usage* for further details on the command library.

| Class         | Туре                        | Commands in ANT command library               | Reply | From     |

|---------------|-----------------------------|-----------------------------------------------|-------|----------|

| Config.       | Unassign Channel            | ANT_UnassignChannel()                         | Yes   | Host     |

| messages      | Assign Channel              | ANT_AssignChannel()                           | Yes   | Host     |

|               | Channel ID                  | ANT_SetChannelld()                            | Yes   | Host     |

|               | Channel Period              | ANT SetChannelPeriod()                        | Yes   | Host     |

|               | Search Timeout              | ANT SetChannelSearchTimeout()                 | Yes   | Host     |

|               | Channel RF Frequency        | ANT_SetChannelRFFreq()                        | Yes   | Host     |

|               | Set Network                 | ANT_SetNetworkKey()                           | Yes   | Host     |

|               | Transmit Power              | ANT_SetTransmitPower()                        | Yes   | Host     |

|               | ID List Add                 | ANT_AddChannelID() <sup>a</sup>               | Yes   | Host     |

|               | ID List Config              | ANT_ConfigList() <sup>a</sup>                 | Yes   | Host     |

|               |                             | ANT_SetChannelTxPower()                       | Yes   | Host     |

|               | Low Priority Search Timeout | ANT_SetLowPriorityChannelSearchTi meout()     | Yes   | Host     |

|               | Enable Ext RX Mesgs         | ANT RxExtMesgsEnable()                        | Yes   | Host     |

|               | Crystal Enable              | ANT CrystalEnable()                           | Yes   | Host     |

|               | Frequency Agility           | ANT_ConfigFrequencyAgility()                  | Yes   | Host     |

|               | Proximity Search            | ANT_SetProximitySearch()                      | Yes   | Host     |

| Notifications | Startup Message             | → ResponseFunc( -, 0x6F)                      | -     | ANT      |

| Control       | SystemReset                 | ANT_ResetSystem()                             | No    | Host     |

| Messages      | Open Channel                | ANT_OpenChannel()                             | Yes   | Host     |

|               | Close Channel               | ANT_CloseChannel()                            | Yes   | Host     |

|               | Open Rx Scan Mode           | ANT_OpenRxScanMode() <sup>a</sup>             | Yes   | Host     |

|               | Request Message             | ANT_RequestMessage()                          | Yes   | Host     |

|               | Sleep Message               | ANT_SleepMessage()                            | No    | Host     |

| Data Messages | Broadcast Data              | ANT_SendBroadcastData()                       | No    | Host/ANT |

|               |                             | → ChannelEventFunc(Chan,EV)                   |       |          |

|               | Acknowledge Data            | ANT_SendAcknowledgedData()                    | No    | Host/ANT |

|               |                             | → ChannelEventFunc(Chan, EV)                  |       |          |

|               | Burst Transfer Data         | ANT_SendBurstTransferPacket()                 | No    | Host/ANT |

| 01            | Olympia I Daniel I          | → ChannelEventFunc(Chan, EV)                  |       | ANIT     |

| Channel Event | •                           | → ChannelEventFunc(Chan,                      | -     | ANT      |

| Messages      | Event                       | MessageCode) or                               |       |          |

|               | 01 1011                     | → ResponseFunc(Chan, MsgID)                   |       | A > 1 T  |

| Requested     | Channel Status              | → ResponseFunc(Chan, 0x52)                    | -     | ANT      |

| Response      | Channel ID                  | → ResponseFunc(Chan, 0x51)                    | -     | ANT      |

| Messages      | ANT Version                 | → ResponseFunc(Chan, 0x51)                    | -     | ANT      |

|               | Capabilities                | → ResponseFunc(-, 0x3E)                       | -     | ANT      |

| Test Mode     | CW Init                     | ANT InitCWTestMode()                          | Yes   | Host     |

| F.4.D-4-      | CW Test                     | ANT SetCWTestMode()                           | Yes   | Host     |

| Ext Data      | Extended Broadcast Data     | ANT SendExtBroadcastData() <sup>b</sup>       | No    | Host     |

| messages      |                             | → ChannelEventFunc(Chan, EV)                  |       |          |

|               | Extended Ack. Data          | ANT SendExtAcknowledgedData() <sup>b</sup>    | No    | Host     |

|               |                             | → ChannelEventFunc(Chan, EV)                  |       |          |

|               | Extended Burst Data         | ANT SendExtBurstTransferPacket() <sup>b</sup> | No    | Host     |

|               |                             | → ChannelEventFunc(Chan, EV)                  |       |          |

a. This is only supported by the nRF24AP2-8CH.

Table 4. ANT message summary supported by nRF24AP2

b. nRF24AP2 does not send these ChannelEventFunctions() to the host. nRF24AP2 will send extended messages by appending the additional bytes to standard broadcast, acknowledged and burst data.

#### 5 Host interface

The host microcontroller can configure and control all of the nRF24AP2 features through a simple serial interface. Three interface options are available, enabling both high and low end microcontrollers to be used.

#### 5.1 Features

Serial interfaces supported by nRF24AP2:

- Asynchronous (UART)

- · Interface requires 5 pins to host microcontroller

- Configurable baud rate from 4800 to 57600 baud

- Synchronous

- · Bit or byte flow

- · Interface requires 6 pins to host microcontroller

# 5.2 Asynchronous serial interface

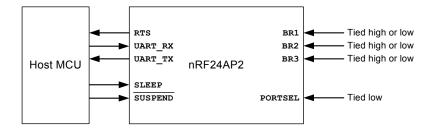

The host MCU and nRF24AP2 may communicate using the asynchronous mode of the serial interface. Asynchronous mode is selected by the PORTSEL input being tied low.

#### 5.2.1 Block diagram

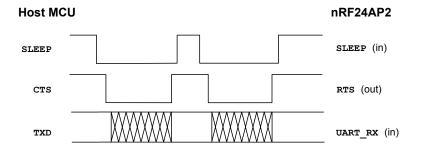

The asynchronous serial interface between nRF24AP2 and the host MCU is shown in Figure 11.

Figure 11. Asynchronous mode connections

The **UART** communication is for one start bit, one stop bit, 8 bits of data and no parity. Data is sent and received LSBit first.

#### 5.2.2 Baud rate

The baud rate of the asynchronous communication between the host and ANT is controlled by the speed select signals BR1, BR2 and BR3. <u>Table 5.</u> shows the relationship between the states of the speed select signals and the corresponding baud rates.

| BR3 | BR2 | BR1 | Baud rate |

|-----|-----|-----|-----------|

| 0   | 0   | 0   | 4800      |

| 0   | 1   | 0   | 19200     |

| 0   | 0   | 1   | 38400     |

| 0   | 1   | 1   | 50000     |

| 1   | 0   | 0   | 1200      |

| 1   | 1   | 0   | 2400      |

| 1   | 0   | 1   | 9600      |

| 1   | 1   | 1   | 57600     |

Table 5. Relationship between states of speed-select signals and corresponding baud rates

**Note:** The baud rate may have a significant impact on system current consumption. Refer to <u>section</u> 8.2 on page 46 for application-specific current consumption figures.

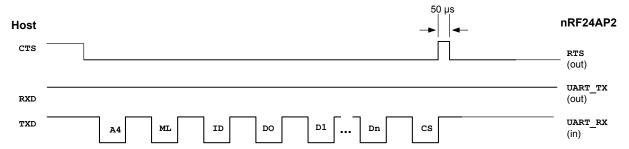

#### 5.2.3 Asynchronous Port Control (RTS)

When nRF24AP2 is configured in asynchronous mode, a full duplex asynchronous serial port is provided with flow control for data transmission from the host to ANT. The flow control is performed by the RTS signal, which conforms to standard hardware flow control CMOS signal levels. The signal may therefore be attached to a computer serial port (with use of an RS-232 level shifter), or to any other RS-232 device. The RTS signal is de-asserted for approximately 50 µs after each correctly formatted message has been received. This RTS signal duration is independent of the baud rate. Incorrect messages or partial messages are not acknowledged.

Figure 12. RTS signal following a serial host -> nRF24AP2 transfer

When nRF24AP2 raises the RTS signal high, the host MCU may not send any more data until the RTS signal is lowered again. There is no flow control for data being transmitted from nRF24AP2 to the host controller, and therefore the host controller must be able to receive data at any time. RTS is toggled following a reset.

The RTS signal is raised by nRF24AP2 after the last byte of a message has been received, and nRF24AP2 will therefore lose any bytes that were sent, or in the process of being sent, before the RTS signal is acted upon by the host MCU, and the transmission is halted. To avoid this problem, either the messages need to be spaced apart by the host MCU or 0-pad bytes need to be added to the end of each message being transmitted to handle whatever byte pipeline is in place. For example, when considering computer

#### nRFAP2 Product Specification

communication, two 0-bytes must be appended to every message, since computers interpret CTS at the driver- rather than the hardware level.

nRF24AP2 will discard 0-pad bytes received. This issue usually occurs only when using burst transfers from the host to nRF24AP2 and high data rates are expected.

## 5.2.4 Sleep enable (SLEEP)

The **SLEEP** input signal allows nRF24AP2 to sleep when the serial port is not required. The signal is essential for conserving power when using the asynchrnous serial interface. This control mechanism is illustrated in Figure 13.

Figure 13. nRF24AP2 sleep control

If the **SLEEP** signal is not used, then it must be tied low. In this configuration, the nRF24AP2 will never sleep and will always be ready to receive data. The **SUSPEND** functionality cannot be used if the **SLEEP** signal is not used.

The **SLEEP** and **RTS** signals only affect the data being transferred from the host MCU to nRF24AP2. nRF24AP2 will send data to the host, when available, regardless of the state of these two signals.

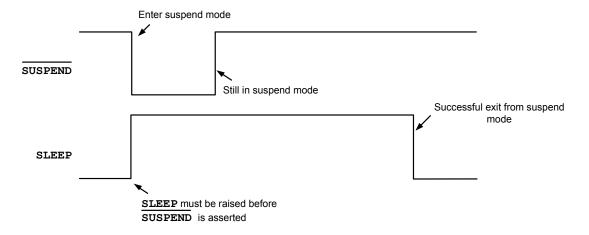

#### 5.2.5 Suspend mode control (SUSPEND)

When using the asynchronous serial interface, you also have a SUSPEND signal available. The assertion of the SUSPEND signal will cause nRF24AP2 to terminate all RF and serial port activity and power down. This will happen immediately, regardless of the state of the nRF24AP2 system. This signal provides support for use in USB applications, where USB devices are required to quickly enter a low-power state through hardware control.

Entering and exiting from the suspend mode require the use of the SLEEP signal, in addition to the SUSPEND signal. The assertion of SUSPEND is only recognized if SLEEP is also asserted at the time. Deassertion of the SLEEP signal is the only method for exiting from suspend mode, as shown in Figure 14. on

<u>page 26</u>. Following exit, all previous transactions and configurations will be lost – nRF24AP2 will be in its power-up state.

Figure 14. SUSPEND signal use

# 5.3 Synchronous serial interface

This section explains in detail the synchronous serial interface between nRF24AP2 and a host MCU. This mode is selected by connecting the **PORTSEL** input high.

When operating in synchronous mode, careful attention to reset behavior is required to prevent inadvertent deadlock conditions between nRF24AP2 and the host MCU.

In synchronous mode, nRF24AP2 uses a half-duplex synchronous master serial interface with message flow control. The host must be configured as a synchronous slave. The interface is meant to accommodate either a hardware synchronous slave port or a simple I/O control on the host MCU. The host MCU retains full control of the message flow and can halt incoming messages as required.

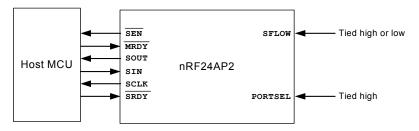

#### 5.3.1 Block diagram

The synchronous serial interface between nRF24AP2 and the host MCU is shown in <u>Figure 15</u>. The **PORTSEL** signal should be connected to logic high for synchronous serial mode.

Figure 15. Synchronous mode connections

#### 5.3.2 Flow Control Select (SFLOW)

The Flow Control Select signal is used to configure the synchronous serial port for either Byte or Bit flow control.

| SFLOW | Flow control      |

|-------|-------------------|

| 0     | Byte flow control |

| 1     | Bit flow control  |

Please note that Byte flow control assumes that the host contains synchronous communication hardware which can be configured for synchronous slave communication. Bit flow control can be used by all microcontrollers. It is especially useful for microcontrollers that offer no hardware serial interface, and which require the serial interface to be emulated in software on the host MCU. The differences between byte and bit flow control are detailed in the remaining sections of this chapter.

#### 5.3.3 Synchronous interface handshaking

A basic description of the communications mechanism follows.

- The synchronous serial port provided by nRF24AP2 is a half-duplex synchronous master.

- Two handshake signals (SEN, MRDY) are used to set up communication.

- Being a master, the nRF24AP2 will forward all incoming radio messages to the host as they become available.

- The host must request the use of the serial port and get acknowledge from nRF24AP2 before a transaction can take place.

- SRDY enables flow control in both directions.

- The first byte in each message is always sent from the nRF24AP2 and indicates the direction of this message.

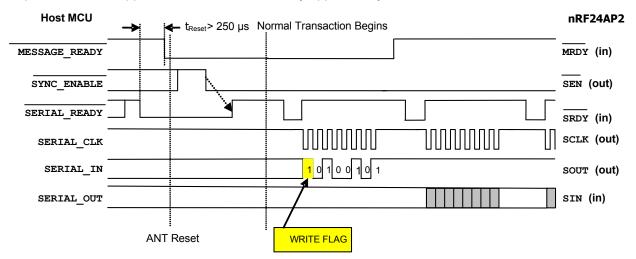

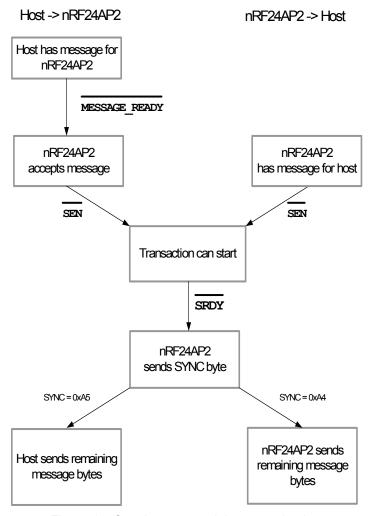

The steps needed to initiate synchronous message transfers in both directions are shown in <u>Figure 16. on page 27</u>.

#### 5.3.3.1 Synchronization

In order for the host MCU to guarantee synchronization with nRF24AP2 in startup conditions, a reset sequence must be applied to nRF24AP2. This only applies to synchronous mode communication.

Figure 16. Synchronization with nRF24AP2 upon startup

#### 5.3.3.2 Power up/power down

nRF24AP2 will <u>automatically</u> place itself into idle mode when all radio channels are closed and there is no activity on the <u>MRDY</u> input signal. The host MCU should ensure these conditions during times that the nRF24AP2 radio is not required in order to maximize product battery life. Upon every power up, the host must apply the Synchronous Reset sequence.

Figure 17. Synchronous serial communication

<u>Figure 17. on page 28</u> and timing diagrams in <u>Figure 18. on page 29</u> and <u>Figure 19. on page 30</u> illustrate the basic, message transaction sequence:

For a message from host->nRF24AP2:

The host will assert the MRDY signal indicating it has a message for the nRF24AP2.

For messages in either direction:

- 1. nRF24AP2 will assert **sen** to indicate the start of a message transfer.

- 2. After <u>SEN</u> has <u>been</u> asserted, the host will assert <u>SRDY</u> to indicate it is ready for communication.

- 3. After SEN and SRDY are both asserted, nRF24AP2 always transmits the first (for example SYNC) byte. This is output from SOUT, and clocked with SCLK (see chapter 8 on page 40 for details of clock frequency). The LSB of the SYNC byte indicates the direction of the remaining message bytes (0 : Message Receive, nRF24AP2 → host; 1: Message Transmit, host → nRF24AP2).

- 4. If the **SYNC** byte indicates a message receive (nRF24AP2->host), the additional message bytes will be transmitted the same way as the **SYNC** byte.

- 5. If the **SYNC** byte indicates a message transmit (host->nRF24AP2), the host must output its data to nRF24AP2 **SIN** at the clock rate provided by nRF24AP2 **SCLK**.

Data is transmitted least-significant-bit (LSB) first.

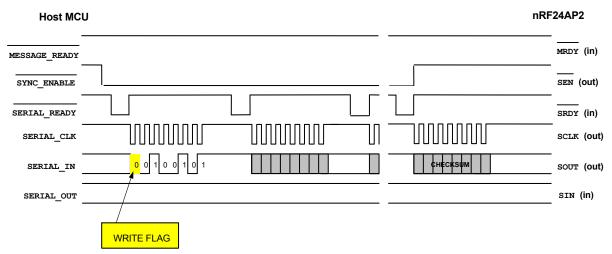

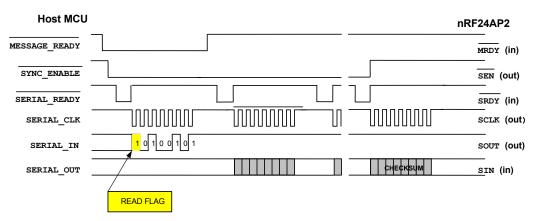

#### 5.3.4 Synchronous messaging with byte flow control

Byte flow-control mode is used when a synchronous hardware serial port is available.

The host MCU flow-control signal **SRDY** must be toggled for each byte and can either be implemented with a software controlled I/O line, or in some cases may be controlled by the host's hardware serial port. Data bits change state on the falling edge of **SCLK** and are read on the rising edge of **SCLK**. This is true for transactions in either direction.

The first byte in the transaction sequence is always sent from nRF24AP2 to the host MCU. The first bit of the first byte dictates the direction for the remaining bytes in the transaction.

<u>Figure 18. on page 29</u> and <u>Figure 19. on page 30</u> show transactions between the host and nRF24AP2 in byte synchronous mode.

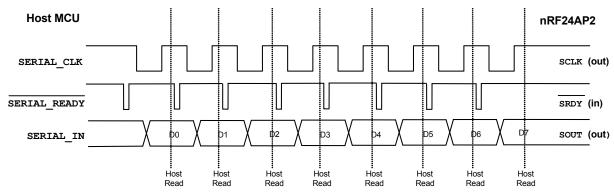

Figure 18. nRF24AP2 → host transaction

The nRF24AP2 asserts **SEN** and waits for the host to assert **SRDY**. Once both **SEN** and **SRDY** have been asserted, nRF24AP2 will send the SYNC byte from **SOUT**.

For hardware <u>SRDY</u>, this signal will be de-asserted on the first <u>SCLK</u> transition, if a software controlled I/O line is used for <u>SRDY</u>, it only needs to stay asserted for 2.5 µs minimum before the host can de-assert it again. The LSB of the SYNC byte will notify the host of the message direction (that is to say,

nRF24AP2 -> host), and once ready, the host will once again assert **SRDY** to receive the next message byte from nRF24AP2. After the last message byte, **SRDY** must remain de-asserted until the next message transaction is requested.

The process for nRF24AP2 to host transactions with software SRDY (Figure 21.) is very similar as for hardware SRDY. The sole difference is that the host can just pulse SRDY and does not have to wait until the first SCLK transition.

Figure 19. Host → nRF24AP2 transaction

For host to nRF24AP2 transactions with hardware SRDY (See Figure 19.) the process is very similar. The main difference is that the host first asserts MRDY to inform nRF24AP2 that it wished to send a message. nRF24AP2 will respond by asserting SEN and then waiting for the host to assert SRDY. Once both SEN and SRDY have been asserted, nRF24AP2 will the send the SYNC byte. For hardware SRDY, this signal will be de-asserted on the first SCLK transition. The first bit of the SYNC byte will notify the host of the message direction (meaning host-> nRF24AP2), and the host will once again assert SRDY and then send the next message byte to nRF24AP2 on host SOUT at the rate of SCLK. Again, the hardware SRDY will de-assert on the first SCLK transition and re-assert after each byte until the entire message has been transferred. After the last message byte, SRDY will remain de-asserted until the next message transaction is requested.

The process for host to nRF24AP2 transactions with software **SRDY** (See <u>Figure 19.</u>) is very similar as for hardware **SRDY**. The only difference is that the host can pulse **SRDY** and does not have to wait until the first **SCLK** transition.

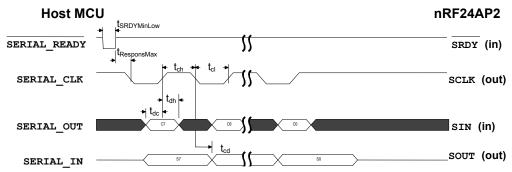

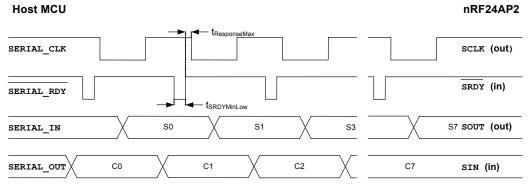

#### 5.3.5 Synchronous timing with byte flow control

Synchronous mode with byte flow is compatible with a host microcontroller, hardware SPI slave, configured as mode 3 and polarity 1. In <u>Figure 20.</u> signals to the left indicate pins on the host MCU. Signals on the right-hand side indicate pins on nRF24AP2. Shaded areas indicate "don't care" values.

Figure 20. Synchronous byte flow timing

| Symbol                   | Parameter (condition)                 | Notes | Min | Тур  | Max | Units |

|--------------------------|---------------------------------------|-------|-----|------|-----|-------|

| <b>SCLK</b> frequency    | Synchronous clock frequency (byte     |       |     | 500  |     | kHz   |

| ,                        | mode)                                 |       |     |      |     |       |

| t <sub>dc</sub>          | Data to SCK Setup (byte mode)         |       | 100 |      |     | ns    |

| t <sub>dh</sub>          | SCK to Data Hold (byte mode)          |       | 20  |      |     | ns    |

| t <sub>cd</sub>          | SCK to Data Valid (byte mode)         |       |     |      | 60  | ns    |

| t <sub>cl</sub>          | SCK Low Time (byte mode)              |       | 900 | 1000 |     | ns    |

| t <sub>ch</sub>          | SCK High Time (byte mode)             |       | 900 | 1000 |     | ns    |

| t <sub>SRDY</sub> MinLow |                                       |       | 2.5 |      |     | μs    |

|                          | Minimum SRDY low time                 |       |     |      |     |       |

| t <sub>Reset</sub>       |                                       |       | 250 |      |     | μs    |

|                          | Synchronous reset. SRDY falling edge  |       |     |      |     |       |

|                          | to MRDY falling edge                  |       |     |      |     |       |

| t <sub>POR</sub>         | Power on reset time (supply rise time | а     |     |      | 2.0 | ms    |

|                          | not included)                         |       |     |      |     |       |

| t <sub>SoftReset</sub>   | Software reset (synchronous reset     | а     |     |      | 1.5 | ms    |

|                          | suspend reset and reset command)      |       |     |      |     |       |

| t <sub>ResponseMax</sub> | Time the nRF24AP2 will take to        |       |     |      | 1.0 | ms    |

| 3 apraisa mark           | respond to input signal               |       |     |      |     |       |

a. Defines the time before the host MCU can start to configure the nRF24AP2 after a reset.

Table 6. Synchronous serial timing

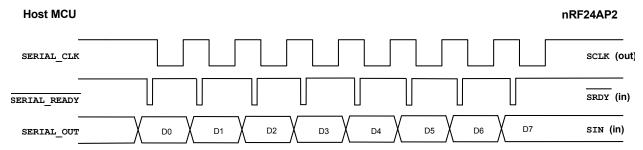

# 5.3.6 Synchronous messaging with bit flow control

If no hardware serial port is available on the host MCU, nRF24AP2 can still be controlled using bit flow control. Using this method, the serial lines are implemented with software controlled I/O lines. All of the signaling at the message transaction level remains the same as above. However, instead of pulsing after every byte, SRDY is pulsed for each bit of the message as shown below in Figure 21. on page 32.

Figure 21. nRF24AP2 → host transaction

Figure 22. Host → nRF24AP2 transaction

It is important to note that the host MCU will do all bit processing on the rising edge of the SCLK signal, with the exception being when the byte is being transmitted from the host MCU to nRF24AP2, where the first data bit will need to be asserted prior to the first clock edge. The final rising edge of the byte transaction will be the event to drive byte processing.

Figure 23. Synchronous bit flow timing

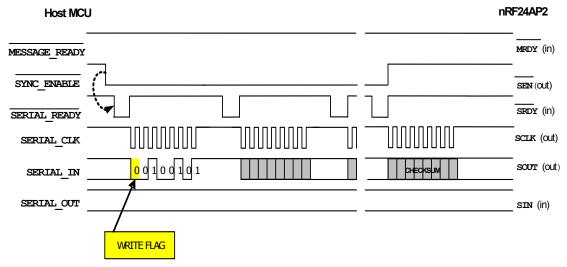

#### 5.3.7 Serial enable control

The **SEN** signal will be asserted by nRF24AP2 prior to all message transmissions. It can therefore be used as a serial port enable signal, which is useful in cases where the host serial port requires hardware activation.

Figure 24. Serial enable control using nRF24AP2

## 6 On-chip oscillator

In order to provide the necessary clocks for the ANT protocol stack, nRF24AP2 contains one high frequency oscillator used by the RF transceiver. and two optional low frequency oscillators for ANT protocol timing. The mandatory, high frequency clock source must be a 16 MHz crystal oscillator. The low frequency clock source can be generated by a 32.768 kHz crystal oscillator or synthesized 32.768 kHz from the 16 MHz crystal oscillator clock. External 16 MHz and 32.768 kHz clocks may also be used instead of the on-chip oscillators of nRF24AP2. For ultra low-power applications, we recommend you use the 32.768 kHz crystal oscillator or provide a 32.768 kHz clock signal, to achieve the lowest possible current consumption.

#### 6.1 Features

- Low-power, amplitude regulated 16 MHz crystal oscillator

- Ultra low-power amplitude regulated 32.768 kHz crystal oscillator

- Low power, synthesized 32.768 kHz clock from the 16 MHz crystal oscillator

# 6.2 Block diagrams

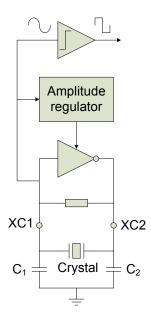

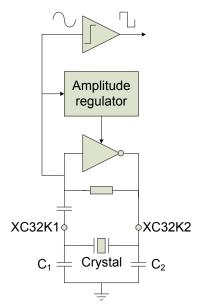

Figure 25. Block diagram of 16 MHz crystal oscillator

Figure 26. Block diagram of 32.768 kHz crystal oscillator

# 6.3 Functional description

#### 6.3.1 16 MHz crystal oscillator

The 16 MHz crystal oscillator is designed to be used with an AT-cut quartz crystal in parallel resonant mode. To achieve correct oscillation frequency it is very important that the load capacitance matches the specification in the crystal datasheet. The load capacitance is the total capacitance from the perspective of the crystal across its terminals:

$$C_{LOAD} = \frac{C_{1}^{'} \cdot C_{2}^{'}}{C_{1}^{'} + C_{2}^{'}}$$

$$C_{1}^{'} = C_{1} + C_{PCB1} + C_{PIN}$$

$$C_{2}^{'} = C_{2} + C_{PCB2} + C_{PIN}$$

$C_1$  and  $C_2$  are ceramic SMD capacitors connected between each crystal terminal and VSS,  $C_{PCB1}$  and  $C_{PCB2}$  are stray capacitances on the PCB, while  $C_{PIN}$  is the input capacitance on the **xc1** and **xc2** pins of nRF24AP2 (typically 1pF).  $C_1$  and  $C_2$  should be of the same value, or as close as possible.

To ensure a functional radio link the frequency accuracy must be  $\pm$  50 ppm or better. The initial tolerance of the crystal, drift over temperature, aging and frequency pulling due to incorrect load capacitance must all be taken into account. For reliable operation the crystal load capacitance, shunt capacitance, equivalent series resistance (ESR) and drive level must comply with the specifications in <u>Table 9. on page 42</u>. It is recommended to use a crystal with lower than maximum ESR if the load capacitance and/or shunt capacitance is high. This will give faster start-up and lower current consumption.

The start-up time is typically about 1 ms for a crystal with 9pF load capacitance and an ESR specification of  $60\Omega$  max. This value is valid for crystals in a 3.2×2.5 mm can. If you use the smallest crystal cans (like 2.0×2.5 mm), pay particular attention to the start-up time of the crystal. These crystals have a longer start

up than crystals in larger cans. To make sure the start-up time is <1.24 ms use a crystal for load capacitance of 6pF. A low load capacitance will reduce both start-up time and current consumption.

For more details regarding how to measure the start up of a specific crystal, please see the nAN24-13 application note. This application note describes measurements on the nRF24LE1, which has an equal crystal oscillator. The start-up time must be measured to <1.5 ms in this setup since it includes a debounce time of 256  $\mu$ s.

#### 6.3.2 External 16 MHz clock

nRF24AP2 may be used with an external 16 MHz clock applied to the **xc1** pin. The input signal must be analog, coming from the crystal oscillator of a microcontroller, for example. An input amplitude of 0.8V peak-to-peak or higher is recommended to achieve low current consumption and a good signal-to-noise ratio. The DC level is not important as long as the applied signal never rises above VDD or drops below VSS. The **xc1** pin will load the microcontroller's crystal with approximately 1pF in addition to PCB routing. **xc2** shall not be connected.

**Note:** A frequency accuracy of  $\pm 50$  ppm or better is required to achieve device performance as outlined in chapter 8 on page 40.

#### 6.3.3 32.768 kHz crystal oscillator

The crystal must be connected between port pins xC32K2 and xC32K1. To achieve correct oscillation frequency it is important that the load capacitance matches the specification in the crystal datasheet. The load capacitance is the total capacitance seen by the crystal across its terminals:

$$C_{LOAD} = \frac{C_{1}^{'} \cdot C_{2}^{'}}{C_{1}^{'} + C_{2}^{'}}$$

$$C_{1}^{'} = C_{1} + C_{PCB1} + C_{PIN}$$

$$C_{2}^{'} = C_{2} + C_{PCB2} + C_{PIN}$$

C1 and C2 are ceramic SMD capacitors connected between each crystal terminal and VSS, CPCB1 and CPCB2 are stray capacitances on the PCB, while CPIN is the input capacitance on the xc32x2 and xc32x1 pins of nRF24AP2. C1 and C2 should be of the same value, or as close as possible. The oscillator uses an amplitude regulated design similar to the 16 MHz crystal oscillator. For reliable operation the crystal load capacitance, shunt capacitance, equivalent series resistance (ESR) and drive level must comply with the specifications in Table 9. on page 42.

It is recommended to use a crystal with lower than maximum ESR if the load capacitance and/or shunt capacitance is high. This will give faster start-up and lower current consumption.

**Note:** A frequency accuracy of  $\pm$  50 ppm or better is required to get reliable ANT functionality. The ANT\_CrystalEnable() must be executed in order to enable external, crystal oscillator.

#### 6.3.4 Synthesized 32.768 kHz clock

The low frequency clock can also be synthesized from the 16 MHz crystal oscillator clock. This saves the cost of a crystal but increases average power consumption. The synthesized clock is enabled by connecting xc32k1 to VSS and leaving xc32k2 unconnected.

#### 6.3.5 External 32.768 kHz clock

nRF24AP2 may be used with an external 32.768 kHz clock applied to the xc32x1 port pin. The external clock must be a rail-to-rail digital signal. xc32x2 must not be connected.

**Note:** A frequency accuracy of ±50 ppm or better is required to get reliable ANT functionality. The ANT\_CrystalEnable() must be executed in order to enable external, clock.

# 7 Operating conditions

| Symbol             | Parameter                     | Notes | Min. | Тур. | Max.  | Units |

|--------------------|-------------------------------|-------|------|------|-------|-------|

| VDD                | Supply voltage                |       | 1.9  | 3.0  | 3.6   | V     |

| t <sub>R_VDD</sub> | Supply rise time (0V to 1.9V) | а     | 1 µs |      | 50 ms |       |

| T <sub>A</sub>     | Operating temperature         |       | -40  |      | +85   | °C    |

a. The power-on reset circuitry may not function properly for rise times outside the specified interval.

Table 7. Operating conditions

### nRFAP2 Product Specification

| Symbol             | Parameter (condition)                   | Notes | Min. | Тур.   | Max. | Unit |

|--------------------|-----------------------------------------|-------|------|--------|------|------|

|                    | 16 MHz crystal                          |       |      |        |      |      |

| f <sub>NOM</sub>   | Nominal frequency (parallel resonant)   |       |      | 16.000 |      | MHz  |

| f <sub>TOL</sub>   | Frequency tolerance                     | а     |      |        | ±50  | ppm  |

| C <sub>L</sub>     | Load capacitance                        |       |      | 9      | 16   | pF   |

| C <sub>0</sub>     | Shunt capacitance                       |       |      | 3      | 7    | pF   |

| ESR                | Equivalent series resistance            |       |      | 50     | 100  | Ω    |

| $P_{D}$            | Drive level                             |       |      |        | 100  | μW   |

| T <sub>START</sub> | Required 16 MHz oscillator startup time | b     |      |        | 1.24 | ms   |

|                    | Bias resistor (IREF pin to GND)         |       |      |        |      |      |

| Rref               | Resistance                              |       |      | 22     |      | kΩ   |

| Rrefacc            | Tolerance                               |       |      |        | 1    | %    |

|                    | 32.768 kHz crystal                      |       |      |        |      |      |

| f <sub>TOL</sub>   | Frequency tolerance                     |       |      |        | ±50  | ppm  |

| f <sub>NOM</sub>   | Crystal frequency (parallel resonant)   |       |      | 32.768 |      | kHz  |

| CL                 | Load capacitance                        |       |      | 9      | 12.5 | pF   |

| C <sub>0</sub>     | Shunt capacitance                       |       |      | 1      | 2    | pF   |

| ESR                | Equivalent series resistance            |       |      | 50     | 80   | kΩ   |

| $P_{D}$            | Drive level                             |       |      |        | 1    | μW   |

a. Includes initial accuracy, stability over temperature, aging and frequency pulling due to incorrect load capacitance.

Table 8. External circuitry specification

b. Crystal oscillator start up time must not exceed 1.24 ms. Please see section 6.3 on page 35.

### 8 Electrical specifications

This section contains electrical and timing specifications.

Conditions: VDD = 3.0V,  $T_A = -40$ °C to +85°C (unless otherwise noted)

| 30 2483.5             | MHz<br>MHz<br>MHz<br>kHz<br>kbps<br>MHz |

|-----------------------|-----------------------------------------|

|                       | MHz<br>MHz<br>kHz<br>kbps               |

|                       | MHz<br>kHz<br>kbps                      |

|                       | kHz<br>kbps                             |

|                       | kbps                                    |

|                       | _                                       |

|                       | MHz                                     |

| 1 .4                  |                                         |

|                       |                                         |

| +4                    | dBm                                     |

| 20                    | dB                                      |

| ±4                    | dB                                      |

| 1100                  | kHz                                     |

| -20                   | dBc                                     |

| -40                   | dBc                                     |

|                       | 1                                       |