# 4-channel I2C-bus switch with interrupt logic and reset

Datasheet (EN) 1.1

#### **Product Overview**

The NCA9545 is a quad bidirectional translating switch controlled via the I<sup>2</sup>C bus. The SCL/SDA upstream pair fans out to four downstream pairs, or channels. Any individual SCn/SDn channel or combination of channels can be selected, determined by the contents of the programmable control register. Four interrupt inputs (INT3–INT0), one for each of the downstream pairs, are provided. One interrupt (INT) output acts as an AND of the four interrupt inputs.

An active-low reset  $(\overline{RESET})$  input allows the NCA9545 to recover from a situation in which one of the downstream I<sup>2</sup>C buses is stuck in a low state. Pulling  $\overline{RESET}$  low resets the I<sup>2</sup>C state machine and causes all the channels to be deselected, as does the internal power-on reset function.

The pass gates of the switches are constructed such that the VCC terminal can be used to limit the maximum high voltage, which will be passed by the NCA9545. This allows the use of different bus voltages on each pair, so that 1.8-V, 2.5-V, or 3.3-V parts can communicate with 5-V parts, without any additional protection. External pull-up resistors pull the bus up to the desired voltage level for each channel. All I/O terminals are 5.5 V tolerant.

### **Key Features**

- 1-of-4 Bidirectional Translating Switches

- I<sup>2</sup>C Bus and SMBus Compatible

- Four Active-Low Interrupt Inputs

- Active-Low Interrupt Output

- Active-Low Reset Input

- Two Address Terminals, Allowing up to Four Devices on the l<sup>2</sup>C Bus

- Channel Selection via I<sup>2</sup>C Bus, in Any Combination

- Power-Up With All Switch Channels Deselected

- Low R<sub>ON</sub> Switches

- Allows Voltage-Level Translation Between 1.8-V, 2.5-V, 3.3-V, and 5-V Buses

- No Glitch on Power-Up

- Supports Hot Insertion

- Low Standby Current

- Operating Power-Supply Voltage Range of 2.3 V to 5.5 V

- 5.5 V Tolerant Inputs

- 0 to 400-kHz Clock Frequency

- Latch-Up Performance Exceeds 100 mA per JESD 78

- ESD Protection Exceeds JESD 22

- 2000-V Human-Body Model (A114-A)

- 1000-V Charged-Device Model (C101)

### **Applications**

- Servers

- Routers (Telecom Switching Equipment)

- Factory Automation

- Products With I<sup>2</sup>C Slave Address Conflicts (e.g. Multiple, Identical Temp Sensors)

### **Device Information**

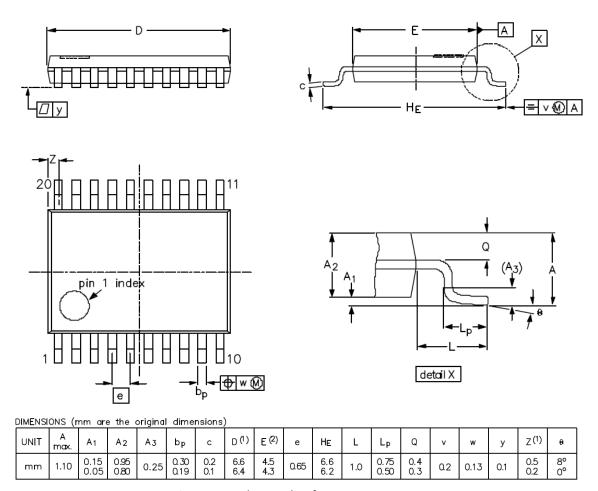

| Part Number  | Package | Body Size   |  |  |

|--------------|---------|-------------|--|--|

| NCA9545_DTSR | TSSOP20 | 6.5mm*4.5mm |  |  |

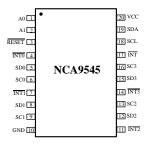

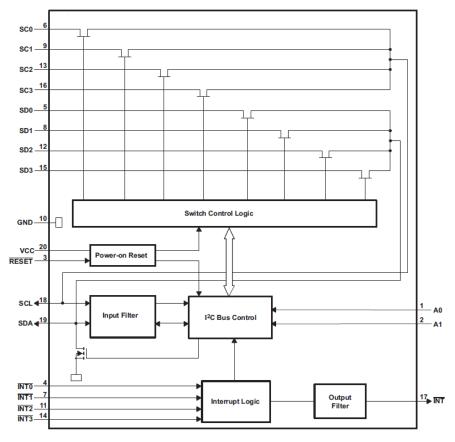

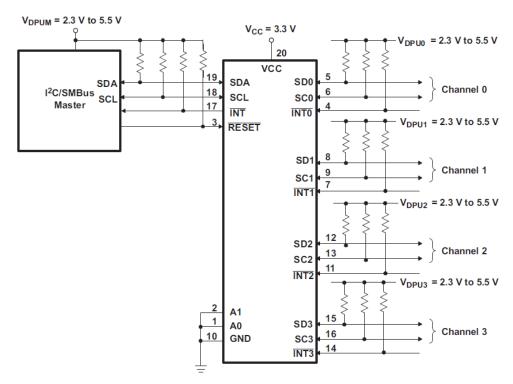

### **Functional Block Diagrams**

Figure 1. NCA9545 Block Diagram

# NCA9545

### Index

| 1. PIN CC    | DNFIGURATION AND FUNCTIONS        | 3  |

|--------------|-----------------------------------|----|

| 2. ABSOL     | UTE MAXIMUM RATINGS               | 4  |

| 3. RECON     | MMENDED OPERATING CONDITIONS      | 4  |

| 4. THERN     | //AL INFORMATION                  | 4  |

| 5. SPECIF    | FICATIONS                         | 5  |

| 5.1.         | ELECTRICAL CHARACTERISTICS        |    |

| 5.1.<br>5.2. | DYNAMIC CHARACTERISTICS           |    |

| 5.2.<br>5.3. | PARAMETER MEASUREMENT INFORMATION |    |

| 6. DETAII    | LED DESCRIPTION                   | 9  |

| 6.1.         | Overview                          | 9  |

| 6.2.         | FUNCTIONAL BLOCK DIAGRAM          |    |

| 6.3.         | FEATURE DESCRIPTION               |    |

| 6.4.         | DEVICE FUNCTIONAL MODES           | _  |

| 6.5.         | RESET INPUT                       | 10 |

| 6.6.         | POWER-ON RESET                    | 10 |

| 6.7.         | Programming                       | 10 |

| 6.8.         | I <sup>2</sup> C Interface        | 10 |

| 6.9.         | CONTROL REGISTER                  |    |

| 6.10.        | DEVICE ADDRESS                    |    |

| 6.11.        | CONTROL REGISTER DESCRIPTION      |    |

| 6.12.        | CONTROL REGISTER DEFINITION       |    |

| 6.13.        | Interrupt Handling                | 13 |

| 7. APPLIC    | CATION AND IMPLEMENTATION         | 13 |

| 7.1.         | TYPICAL APPLICATION               |    |

| 7.2.         | DESIGN REQUIREMENTS               | 14 |

| 7.3.         | DETAILED DESIGN PROCEDURE         |    |

| 7.4.         | NCA9545 Application Curves        | 15 |

| 8. LAYOU     | т                                 | 15 |

| 8.1.         | LAYOUT GUIDELINES                 | 15 |

| 9. PACKA     | GE INFORMATION                    | 16 |

| 10. ORDI     | ER INFORMATION                    | 16 |

| 11. DOCI     | JMENTATION SUPPORT                | 16 |

| 12. TAPE     | AND REEL INFORMATION              | 17 |

| 12 DE\//4    | SION LIICTORY                     | 10 |

# 1. Pin Configuration and Functions

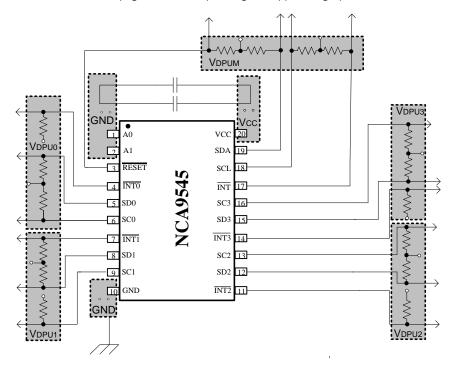

Figure 1.1 NCA9545 Package

Table 1.1 Pin Configuration and Description

| Symbol | Pin | Description                                                                                    |

|--------|-----|------------------------------------------------------------------------------------------------|

| A0     | 1   | Address input 0. Connect directly to VCC or ground.                                            |

| A1     | 2   | Address input 1. Connect directly to VCC or ground.                                            |

| RESET  | 3   | Active-low reset input. Connect to VCC or $V_{DPUM}^1$ through a pull-up resistor if not used. |

| ĪNTO   | 4   | Active-low interrupt input 0. Connect to $V_{DPU0}^{-1}$ through a pull-up resistor.           |

| SD0    | 5   | Serial data 0. Connect to $V_{DPU0}^{-1}$ through a pul-up resistor.                           |

| SC0    | 6   | Serial clock 0. Connect to $V_{DPU0}^{-1}$ through a pull-up resistor.                         |

| ĪNT1   | 7   | Active-low interrupt input 1. Connect to $V_{DPU1}^{1}$ through a pull-up resistor.            |

| SD1    | 8   | Serial data 1. Connect to V <sub>DPU1</sub> <sup>1</sup> through a pull-up resistor.           |

| SC1    | 9   | Serial clock 1. Connect to $V_{	t DPU1}^1$ through a pull-up resistor.                         |

| GND    | 10  | Ground                                                                                         |

| ĪNT2   | 11  | Active-low interrupt input 2. Connect to $V_{DPU2}^{-1}$ through a pull-up resistor.           |

| SD2    | 12  | Serial data 2. Connect to V <sub>DPU2</sub> <sup>1</sup> through a pull-up resistor.           |

| SC2    | 13  | Serial clock 2. Connect to $V_{DPU2}^{-1}$ through a pull-up resistor.                         |

| ĪNT3   | 14  | Active-low interrupt input 3. Connect to $V_{\text{DPU3}}^{1}$ through a pull-up resistor.     |

| SD3    | 15  | Serial data 3. Connect to V <sub>DPU3</sub> <sup>1</sup> through a pull-up resistor.           |

| SC3    | 16  | Serial clock 3. Connect to V <sub>DPU3</sub> <sup>1</sup> through a pull-up resistor.          |

| ĪNT    | 17  | Active-low interrupt output. Connect to $V_{\text{DPUM}}^1$ through a pull-up resistor.        |

| SCL    | 18  | Serial clock line. Connect to $V_{\text{DPUM}}^{1}$ through a pull-up resistor.                |

| SDA    | 19  | Serial data line. Connect to $V_{\text{DPUM}}^1$ through a pull-up resistor.                   |

| VCC    | 20  | Supply power                                                                                   |

$<sup>^{1}</sup>$   $V_{DPUX}$  is the pull-up reference voltage for the associated data line.  $V_{DPUM}$  is the master I<sup>2</sup>C master reference voltage and  $V_{DPU0}$ – $V_{DPU3}$  are the slave channel reference voltages.

# 2. Absolute Maximum Ratings

| Parameters                            | Symbol                         | Min  | Max   | Unit       | Conditions         |

|---------------------------------------|--------------------------------|------|-------|------------|--------------------|

| Supply Voltage                        | V <sub>CC</sub>                | -0.5 | 7     | V          |                    |

| Input/output Voltage                  | V <sub>I</sub> /V <sub>O</sub> | -0.5 | 7     | V          |                    |

| Input current                         | I <sub>I</sub>                 |      | ±25   | mA         |                    |

| Output current                        | Io                             |      | ±25   | mA         | V <sub>0</sub> <0V |

| Continuous current through VCC or GND | I <sub>cc</sub>                |      | ±100  | mA         |                    |

| Operating Temperature                 | Topr                           | -40  | 85    | $^{\circ}$ |                    |

| Storage Temperature                   | Tstg                           | -40  | 150   | $^{\circ}$ |                    |

|                                       | НВМ                            |      | ±2000 | V          |                    |

| Electrostatic discharge               | CDM                            |      | ±1000 | V          |                    |

# 3. Recommended Operating Conditions

| Parameters                     | Symbol   | Min                 | Max                  | Unit          | Conditions               |

|--------------------------------|----------|---------------------|----------------------|---------------|--------------------------|

| Supply voltage                 | $V_{CC}$ | 1.65                | 5.5                  | V             |                          |

| High-level input voltage       | V        | 0.7*V <sub>cc</sub> | 6                    | V             | SCL, SDA                 |

|                                | $V_{IH}$ | 0.7*V <sub>CC</sub> | V <sub>CC</sub> +0.5 | V             | A1, A0, INT3-INTO, RESET |

| Low lovel input veltage        | V        | -0.5                | 0.3*V <sub>CC</sub>  | V             | SCL, SDA                 |

| Low-level input voltage        | $V_{IL}$ | -0.5                | 0.3*V <sub>CC</sub>  | V             | A1, A0, INT3-INTO, RESET |

| Operating free-air temperature | $T_A$    | -40                 | 85                   | ${\mathbb C}$ |                          |

# 4. Thermal Information

| Parameters                               | Symbol                 |       | Unit |

|------------------------------------------|------------------------|-------|------|

| Junction-to-ambient thermal resistance   | $\theta$ <sub>JA</sub> | 115.3 | °C/W |

| Junction-to-case(top) thermal resistance | θ <sub>JC (top)</sub>  | 48.7  | °C/W |

| Junction-to-board thermal resistance     | θ <sub>JB</sub>        | 66.4  | °C/W |

# 5. Specifications

### 5.1. Electrical Characteristics

$V_{CC}$  = 2.7V to 5.5V;  $T_{amb}$  =-40 °C to +85 °C; unless otherwise noted. Typical specification are at  $T_A$ =25 °C,  $V_{CC}$ =3.3V

| Parameters                   | Symbol            | Min                 | Тур  | Max                 | Unit | Conditions                                                                              |

|------------------------------|-------------------|---------------------|------|---------------------|------|-----------------------------------------------------------------------------------------|

| Supply                       |                   |                     |      |                     |      |                                                                                         |

| Supply voltage<br>Range      | V <sub>cc</sub>   | 1.65                | -    | 5.5                 | V    |                                                                                         |

| Power On Reset rising        | V <sub>PORR</sub> | -                   | 1.15 | 1.4                 | V    | no load; $V_I = V_{CC}$ or GND                                                          |

| Power On Reset falling       | V <sub>PORF</sub> | 0.9                 | 1.08 |                     | V    | no load; VI = V <sub>cc</sub> or GND                                                    |

| Supply current               | Icc               | -                   | -    | 10                  | μΑ   | Operating mode; $V_{CC}$ = 5.5 V; $V_I$ = $V_{CC}$ or GND; no load; $f_{SCL}$ = 100 kHz |

| Standby current              | I <sub>stb</sub>  | -                   | 0.3  | 5                   | uA   | Standby mode; $V_{CC} = 5.5 \text{ V}$ ; $V_I = V_{CC} \text{ or GND}$ ; no load        |

| Input SCL; Input/O           | utput SDA         |                     |      |                     |      |                                                                                         |

| LOW-level input<br>voltage   | V <sub>IL</sub>   | -0.5                | -    | 0.3*V <sub>cc</sub> | V    |                                                                                         |

| HIGH-level input voltage     | V <sub>IH</sub>   | 0.7*V <sub>cc</sub> | -    | 6                   | V    |                                                                                         |

| LOW-level output             | I <sub>OL</sub>   | 2.5                 | 15   | -                   | mA   | V <sub>OL</sub> = 0.4 V                                                                 |

| current                      |                   | 4                   | 20   |                     | mA   | V <sub>OL</sub> =0.6V                                                                   |

| Input leakage<br>current     | IL                | -1                  | -    | +1                  | μΑ   | $V_1 = V_{CC}$ or GND                                                                   |

| Input<br>capacitance         | C <sub>i</sub>    | -                   | 15   |                     | pF   | $V_1 = GND$                                                                             |

| Select inputs A0,A1          | L,INTO,INT1,INT2, | .INT3,RESET         | 7    |                     |      |                                                                                         |

| LOW-level input<br>voltage   | V <sub>IL</sub>   | -0.5                | -    | 0.3*V <sub>CC</sub> | V    |                                                                                         |

| HIGH-level input<br>voltage  | V <sub>IH</sub>   | 0.7*V <sub>cc</sub> | -    | 6                   | V    |                                                                                         |

| Leakage current              | IL                | -1                  | -    | 1                   | uA   | $V_1 = V_{CC}$ or GND                                                                   |

| Input<br>capacitance         | C <sub>i</sub>    | -                   | 1.6  | 3                   | pF   | V <sub>I</sub> = GND                                                                    |

| INT output                   |                   |                     |      |                     |      |                                                                                         |

| HIGH-level<br>output current | Іон               | -                   | -    | ±1                  | uA   |                                                                                         |

# **NCA9545**

| LOW-level output | I <sub>OL</sub>          | 3   | 12   | -   | mA | $V_{CC} = 3.6 \text{V}, V_{OL} = 0.4 \text{V}^{[2]}$           |

|------------------|--------------------------|-----|------|-----|----|----------------------------------------------------------------|

| current          |                          | 4   | 17   | -   | mA | V <sub>CC</sub> =3.6V,V <sub>OL</sub> = 0.6 V <sup>[2]</sup>   |

| Pass gate        |                          |     |      |     |    |                                                                |

| On-state         | R <sub>on</sub>          | 4   | 14   | 20  | Ω  | Vo=0.4 V, I <sub>0</sub> = 15 mA, V <sub>CC</sub> = 4.5V       |

| resistance       |                          | 5   | 16   | 25  | Ω  | Vo=0.4 V, I <sub>0</sub> = 15 mA, V <sub>CC</sub> = 3V         |

|                  |                          | 6   | 19   | 30  |    | Vo=0.4 V, I <sub>0</sub> = 10 mA, V <sub>CC</sub> = 2.3V       |

|                  |                          | 10  | 28   | 40  |    | Vo=0.4 V, I <sub>0</sub> = 10 mA, V <sub>CC</sub> = 1.65V      |

| Switch output    | V <sub>O(SW)</sub>       |     | 3.64 |     | V  | V <sub>CC</sub> = 5 V, I <sub>O(SW)</sub> =-100uA              |

| voltage          |                          | 2.6 |      | 4.5 |    | V <sub>CC</sub> = 4.5V to 5.5 V, I <sub>O(SW)</sub> =-100uA    |

|                  |                          |     | 2.15 |     |    | V <sub>CC</sub> = 3.3 V, I <sub>O(SW)</sub> =-100uA            |

|                  |                          | 1.6 |      | 2.8 | V  | V <sub>CC</sub> = 3 V to 3.6 V, I <sub>O(SW)</sub> =-100uA     |

|                  |                          |     | 1.46 |     |    | V <sub>CC</sub> = 2.5 V, I <sub>O(SW)</sub> =-100uA            |

|                  |                          | 1   |      | 1.9 |    | V <sub>CC</sub> = 2.3 V to 2.7 V, I <sub>O(SW)</sub> =-100uA   |

|                  |                          |     | 0.99 |     | V  | V <sub>CC</sub> = 1.8 V, I <sub>O(SW)</sub> =-100uA            |

|                  |                          | 0.5 |      | 1.2 |    | V <sub>CC</sub> = 1.65 V to 1.95 V, I <sub>O(SW)</sub> =-100uA |

| Leakage current  | IL                       | -1  | -    | +1  | μΑ | $V_1 = V_{CC}$ or GND                                          |

| C <sub>io</sub>  | Input/output capacitance | -   | -    | 6   | pF | V <sub>I</sub> =GND                                            |

### **5.2.** Dynamic Characteristics

| Parameters                                       | Symbol                           | Standard-mode I2C-<br>bus |      | Fast-mode I2C-bus |     | Unit |

|--------------------------------------------------|----------------------------------|---------------------------|------|-------------------|-----|------|

|                                                  |                                  | Min                       | Max  | Min               | Max |      |

| propagation delay                                | t <sub>PD</sub> <sup>1</sup>     |                           | 0.3  |                   | 0.3 | ns   |

| SCL clock frequency                              | f <sub>SCL</sub>                 | 0                         | 100  | 0                 | 400 | kHz  |

| bus free time between a STOP and START condition | t <sub>BUF</sub>                 | 4.7                       | -    | 1.3               | -   | μs   |

| hold time (repeated) START condition             | t <sub>HD;STA</sub> <sup>2</sup> | 4.0                       | -    | 0.6               | -   | μs   |

| set-up time for a repeated START condition       | t <sub>su;sta</sub>              | 4.7                       | -    | 0.6               | -   | μs   |

| set-up time for STOP condition                   | t <sub>su;sto</sub>              | 4.0                       | -    | 0.6               | -   | μs   |

| data valid acknowledge time                      | t <sub>VD;ACK</sub>              | 0.3                       | 3.45 | 0.1               | 0.9 | μs   |

| data hold time                                   | t <sub>HD;DAT</sub> <sup>3</sup> | 0                         | -    | 0                 | -   | ns   |

| data valid time                                  | t <sub>VD;DAT</sub> <sup>4</sup> | 300                       | -    | 50                | -   | ns   |

| data set-up time                                 | t <sub>su;dat</sub>              | 250                       | -    | 100               | -   | ns   |

### **NCA9545**

| t <sub>LOW</sub>           | 4.7                                                                          | -             | 1.3                                                                                                                                                                                                                                                                                                                                                                                                                                 | -                                                     | μs                                                    |

|----------------------------|------------------------------------------------------------------------------|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|-------------------------------------------------------|

| t <sub>HIGH</sub>          | 4.0                                                                          | -             | 0.6                                                                                                                                                                                                                                                                                                                                                                                                                                 | -                                                     | μs                                                    |

| t <sub>f</sub>             | -                                                                            | 300           | 20 +<br>0.1C <sub>b</sub> <sup>5</sup>                                                                                                                                                                                                                                                                                                                                                                                              | 300                                                   | ns                                                    |

| t <sub>r</sub>             | -                                                                            | 1000          | 20 +<br>0.1C <sub>b</sub> <sup>5</sup>                                                                                                                                                                                                                                                                                                                                                                                              | 300                                                   | ns                                                    |

| t <sub>SP</sub>            | -                                                                            | 50            | -                                                                                                                                                                                                                                                                                                                                                                                                                                   | 50                                                    | ns                                                    |

| t <sub>v(Q)</sub>          | -                                                                            | 200           | -                                                                                                                                                                                                                                                                                                                                                                                                                                   | 200                                                   | ns                                                    |

| t <sub>su(D)</sub>         | 150                                                                          | -             | 150                                                                                                                                                                                                                                                                                                                                                                                                                                 | -                                                     | ns                                                    |

| t <sub>h(D)</sub>          | 1                                                                            | -             | 1                                                                                                                                                                                                                                                                                                                                                                                                                                   | -                                                     | μs                                                    |

|                            |                                                                              |               |                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                       |                                                       |

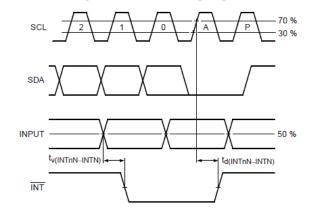

| t <sub>iv(INTnN-INT)</sub> | -                                                                            | 4             | -                                                                                                                                                                                                                                                                                                                                                                                                                                   | 4                                                     | μs                                                    |

| t <sub>ir(INTnN-INT)</sub> | -                                                                            | 2             | -                                                                                                                                                                                                                                                                                                                                                                                                                                   | 2                                                     | μs                                                    |

| T <sub>w(rej)L</sub>       | 1                                                                            | -             | 1                                                                                                                                                                                                                                                                                                                                                                                                                                   | -                                                     | μs                                                    |

| T <sub>w(rej)H</sub>       | 0.5                                                                          | -             | 0.5                                                                                                                                                                                                                                                                                                                                                                                                                                 | -                                                     | μs                                                    |

|                            |                                                                              |               |                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                       |                                                       |

| $T_{w(rst)L}$              | 4                                                                            |               | 4                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                       | ns                                                    |

| t <sub>rst</sub>           | 500                                                                          |               | 500                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                       | ns                                                    |

|                            | 0                                                                            |               | 0                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                       | ns                                                    |

|                            | thigh  tf  tr  tsp  tv(Q)  tsu(D)  th(D)  tiv(INTnN-INT)  Tw(rej)L  Tw(rej)H | thigh 4.0  tf | town       thigh       4.0       -         tf       -       300         tr       -       1000         tsp       -       50         tv(Q)       -       200         tsu(D)       150       -         th(D)       1       -         tiv(INTnN-INT)       -       4         tir(INTnN-INT)       -       2         Tw(rej)L       1       -         Tw(rej)H       0.5       -         Tw(rst)L       4       4         trst       500 | $\begin{array}{c ccccccccccccccccccccccccccccccccccc$ | $\begin{array}{c ccccccccccccccccccccccccccccccccccc$ |

$<sup>^{1}\!</sup>Pass$  gate propagation delay is calculated from the 20  $\Omega$  typical Ron and the 15 pF load capacitance.

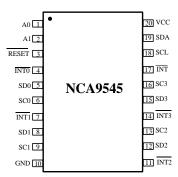

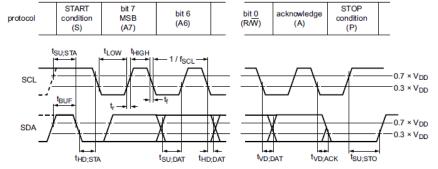

### 5.3. Parameter Measurement Information

Figure 5.1 Definition of timing on I<sup>2</sup>C-bus

<sup>&</sup>lt;sup>2</sup>After this period, the first clock pulse is generated.

$<sup>^{3}</sup>$ A device must internally provide a hold time of at least 300 ns for the SDA signal (referred to the  $V_{IH(min)}$  of the SCL signal) in order to bridge the undefined region of the falling edge of SCL.

$<sup>^4\</sup>text{Measurements}$  taken with 1 k  $\Omega\,$  pull-up resistor and 50 pF load.

$<sup>{}^5</sup>C_b$  = total capacitance of one bus line in pF.

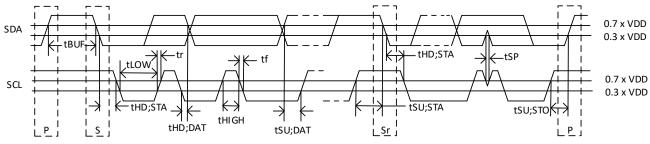

Figure 5.2 Definition of RESET timing

Figure 5.3 I<sup>2</sup>C-bus timing diagram

Figure 5.4 Expanded view of read input port register

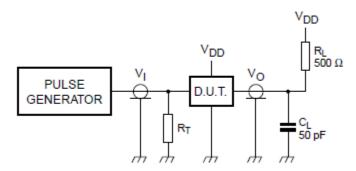

Definitions test circuit:

$R_L$  = Load resistance.

$C_L$  = Load capacitance including jig and probe capacitance.

$R_T$  = Termination resistance should be equal to the output impedance Zo of the pulse generator.

Figure 5.5 Test circuitry for switching times

### 6. Detailed Description

#### 6.1. Overview

The NCA9545 is a 4-channel, bidirectional translating I<sup>2</sup>C switch. The master SCL/SDA signal pair is directed to four channels of slave devices, SC0/SD0-SC3/SD3. Any individual downstream channel can be selected as well as any combination of the four channels. The NCA9545 also supports interrupt signals in order for the master to detect an interrupt on the  $\overline{\text{INT}}$  output terminal that can result from any of the slave devices connected to the  $\overline{\text{INT3}}$ - $\overline{\text{INT0}}$  input terminals.

The device offers an active-low  $\overline{RESET}$  input which resets the state machine and allows the NCA9545 to recover should one of the downstream I<sup>2</sup>C buses get stuck in a low state. The state machine of the device can also be reset by cycling the power supply,  $V_{CC}$ , also known as a power-on reset (POR) Both the RESET function and a POR will cause all channels to be deselected.

The connections of the I<sup>2</sup>C data path are controlled by the same I<sup>2</sup>C master device that is switched to communicate with multiple I<sup>2</sup>C slaves. After the successful acknowledgment of the slave address (hardware selectable by A0 and A1 terminals), a single 8-bit control register is written to or read from to determine the selected channels and state of the interrupts.

The NCA9545 may also be used for voltage translation, allowing the use of different bus voltages on each SCn/SDn pair such that 1.8-V, 2.5-V, or 3.3-V parts can communicate with 5-V parts. This is achieved by using external pull-up resistors to pull the bus up to the desired voltage for the master and each slave channel.

#### 6.2. Functional Block Diagram

Figure 6.1 NCA9545 Functional block

#### 6.3. Feature Description

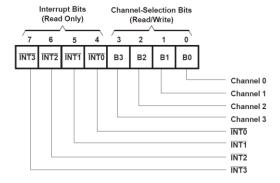

The NCA9545 is a 4-channel, bidirectional translating switch for I<sup>2</sup>C buses that supports Standard-Mode (100 kHz) and Fast-Mode (400 kHz) operation. The NCA9545 features I<sup>2</sup>C control using a single 8-bit control register in which the four least significant bits control the enabling and disabling of the 4 switch channels of I<sup>2</sup>C data flow.

The NCA9545 also supports interrupt signals for each slave channel and this data is held in the four most significant bits of the control register. Depending on the application, voltage translation of the  $I^2C$  bus can also be achieved using the NCA9545 to allow 1.8-V, 2.5-V, or 3.3-V parts to communicate with 5-V parts. Additionally, in the event that communication on the  $I^2C$  bus enters a fault state, the NCA9545 can be reset to resume normal operation using the  $\overline{RESET}$  pin feature or by a power-on reset which results from cycling power to the device.

#### 6.4. Device Functional Modes

#### 6.5. RESET Input

The  $\overline{RESET}$  input can be used to recover the NCA9545 from a bus-fault condition. The registers and the I<sup>2</sup>C state machine within this device initialize to their default states if this signal is asserted low for a minimum of  $t_{WL}$ .

All channels also are deselected in this case. RESET must be connected to V<sub>CC</sub> through a pull-up resistor.

#### 6.6. Power-On Reset

When power is applied to VCC, an internal power-on reset holds the NCA9545 in a reset condition until  $V_{CC}$  has reached  $V_{PORR}$ . At this point, the reset condition is released and the NCA9545 registers and  $I^2C$  state machine are initialized to their default states, all zeroes, causing all the channels to be deselected. Thereafter,  $V_{CC}$  must be lowered below at least  $V_{PORF}$  to reset the device.

#### 6.7. Programming

#### 6.8. I<sup>2</sup>C Interface

The I<sup>2</sup>C bus is for two-way two-line communication between different ICs or modules. The two lines are a serial data line (SDA) and a serial clock line (SCL). Both lines must be connected to a positive supply via a pull-up resistor when connected to the output stages of a device. Data transfer can be initiated only when the bus is not busy.

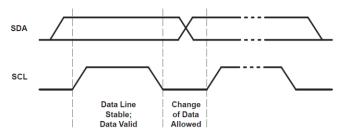

One data bit is transferred during each clock pulse. The data on the SDA line must remain stable during the high period of the clock pulse, as changes in the data line at this time are interpreted as control signals (see Figure 6.1)

Figure 6.1 Bit Transfer

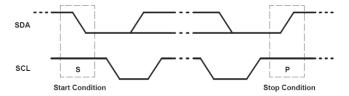

Both data and clock lines remain high when the bus is not busy. A high-to-low transition of the data line while the clock is high is defined as the start condition (S). A low-to-high transition of the data line while the clock is high is defined as the stop condition (P) (see Figure 6.2).

Figure 6.2 Definition of Start and Stop Conditions

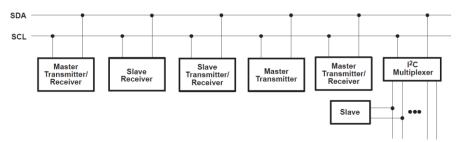

A device generating a message is a transmitter; a device receiving a message is the receiver. The device that controls the message is the master, and the devices that are controlled by the master are the slaves (see Figure 6.3).

Figure 6.3 System Configuration

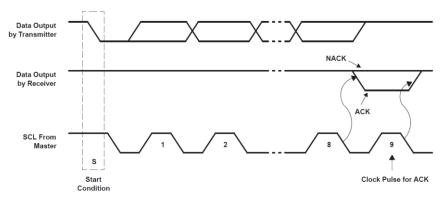

The number of data bytes transferred between the start and the stop conditions from transmitter to receiver is not limited. Each byte of eight bits is followed by one acknowledge (ACK) bit. The transmitter must release the SDA line before the receiver can send an ACK bit.

When a slave receiver is addressed, it must generate an ACK after the reception of each byte. Also, a master must generate an ACK after the reception of each byte that has been clocked out of the slave transmitter. The device that acknowledges must pull down the SDA line during the ACK clock pulse so that the SDA line is stable low during the high pulse of the ACK-related clock period (see Figure 6.4). Setup and hold times must be taken into account.

Figure 6.4 Acknowledgment on the I<sup>2</sup>C Bus

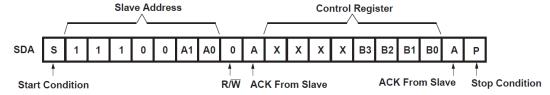

A master receiver must signal an end of data to the transmitter by not generating an acknowledge (NACK) after the last byte has been clocked out of the slave. This is done by the master receiver by holding the SDA line high. In this event, the transmitter must release the data line to enable the master to generate a stop condition. Data is transmitted to the NCA9545 control register using the write mode shown in Figure 6.5.

Figure 6.5 Write Control Register

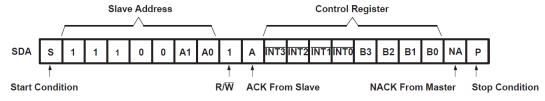

Data is read from the NCA9545 control register using the read mode shown in Figure 6.6.

Figure 6.6 Read Control Register

#### 6.9. Control Register

#### 6.10. Device Address

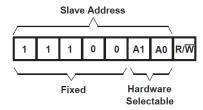

Following a start condition, the bus master must output the address of the slave it is accessing. The address of the NCA9545 is shown in Figure 6.7 To conserve power, no internal pull-up resistors are incorporated on the hardware-selectable address terminals, and they must be pulled high or low.

Figure 6.7 NCA9545 Address

The last bit of the slave address defines the operation to be performed. When set to a logic 1, a read is selected, while a logic 0 selects a write operation.

### **6.11. Control Register Description**

Following the successful acknowledgment of the slave address, the bus master sends a byte to the NCA9545, which is stored in the control register (see Figure 6.8). If multiple bytes are received by the NCA9545, it saves the last byte received. This register can be written and read via the I<sup>2</sup>C bus.

Figure 6.8 Control Register

#### **6.12. Control Register Definition**

One or several SCn/SDn downstream pairs, or channels, are selected by the contents of the control register (see Table 1). After the NCA9545 has been addressed, the control register is written. The four LSBs of the control byte are used to determine which channel or channels are to be selected. When a channel is selected, the channel becomes active after a stop condition has been placed on the I2C bus. This ensures that all SCn/SDn lines are in a high state when the channel is made active, so that no false conditions are generated at the time of connection. A stop condition must occur always right after the acknowledge cycle.

| (2.12.1.1.2.1.2.1.2.1.2.1.2.1.2.1.2.1.2. |      |      |      |    |       |           |     |                                                   |                   |                    |  |                   |

|------------------------------------------|------|------|------|----|-------|-----------|-----|---------------------------------------------------|-------------------|--------------------|--|-------------------|

| ĪNT3                                     | ĪNT2 | INT1 | ĪNT0 | В3 | B2    | B1        | В0  | COMMAND                                           |                   |                    |  |                   |

| Х                                        | X    | X    | X    | V  | V     | V         | 0   | Channel 0 disabled                                |                   |                    |  |                   |

| ^                                        | ^    | ^    | ^    |    |       | X   X   X |     | X X X                                             |                   | X X                |  | Channel 0 enabled |

| V                                        | V    | V    | V    | X  | V     | 0         | X   | Channel 1 disabled                                |                   |                    |  |                   |

| X                                        | X    | X    | X    | X  | X     | 1         | ^   | Channel 1 enabled                                 |                   |                    |  |                   |

| V                                        | V    | V    | X    | V  | X     | V         | 0   | V                                                 | V                 | Channel 2 disabled |  |                   |

| ^                                        | ^    | X    | ^    | X  | 1     | 1 X       | X   | Channel 2 enabled                                 |                   |                    |  |                   |

| V                                        | V    | V    | V    | 0  | V     | V         | V   | Channel 3 disabled                                |                   |                    |  |                   |

| X                                        | X    | X    | X    | 1  | ^   ^ | X         | X X | X                                                 | Channel 3 enabled |                    |  |                   |

| 0                                        | 0    | 0    | 0    | 0  | 0     | Х         | 0   | No channel selected, power-up/reset default state |                   |                    |  |                   |

Table 1. Control Register Write (Channel Selection), Control Register Read (Channel Status)

$^{1}$  Several channels can be enabled at the same time. For example, B3 = 0, B2 = 1, B1 = 1, B0 = 0 means that channels 0 and 3 are disabled, and channels 1 are 2 and enabled. Care should be taken not to exceed the maximum bus capacity.

#### 6.13.Interrupt Handling

The NCA9545 provides four interrupt inputs (one for each channel) and one open-drain interrupt output (see Table 2). When an interrupt is generated by any device, it is detected by the NCA9545 and the interrupt output is driven low. The channel does not need to be active for detection of the interrupt. A bit also is set in the control register. Bits 4–7 of the control register correspond to channels 0–3 of the NCA9545, respectively. Therefore, if an interrupt is generated by any device connected to channel 1, the state of the interrupt inputs is loaded into the control register when a read is accomplished. Likewise, an interrupt on any device connected to channel 0 would cause bit 4 of the control register to be set on the read. The master then can address the NCA9545 and read the contents of the control register to determine which channel contains the device generating the interrupt. The master then can reconfigure the NCA9545 to select this channel and locate the device generating the interrupt and clear it.

It should be noted that more than one device can provide an interrupt on a channel, so it is up to the master to ensure that all devices on a channel are interrogated for an interrupt.

The interrupt inputs can be used as general-purpose inputs if the interrupt function is not required.

If unused, interrupt input(s) must be connected to VCC.

INT3 INT2 INT1 **INTO B3** B<sub>2</sub> B<sub>0</sub> COMMAND 0 No interrupt on channel 0 Χ Χ Χ Χ Χ Χ Χ 1 Interrupt on channel 0 0 No interrupt on channel 1 Χ Χ Χ X X Χ Χ Interrupt on channel 1 1 0 No interrupt on channel 2 Χ Χ X X Χ X Χ 1 Interrupt on channel 2 0 No interrupt on channel 3 Χ Χ Χ Χ Χ X Χ 1 Interrupt on channel 3

Table 2. Control Register Read (Interrupt)(1)

### 7. Application and Implementation

Applications of the NCA9545 will contain an I<sup>2</sup>C (or SMBus) master device and up to four I<sup>2</sup>C slave devices. The downstream channels are ideally used to resolve I<sup>2</sup>C slave address conflicts. For example, if four identical digital temperature sensors are needed in the application, one sensor can be connected at each channel: 0, 1, 2, and 3. When the temperature at a specific location needs to be read, the appropriate channel can be enabled and all other channels switched off, the data can be retrieved, and the I<sup>2</sup>C master can move on and read the next channel.

In an application where the I<sup>2</sup>C bus will contain many additional slave devices that do not result in I<sup>2</sup>C slave address conflicts, these slave devices can be connected to any desired channel to distribute the total bus capacitance across multiple channels. If multiple switches will be enabled simultaneously, additional design requirements must be considered (See Design Requirements and Detailed Design Procedure).

#### 7.1. Typical Application

A typical application of the NCA9545 will contain anywhere from 1 to 5 separate data pull-up voltages,  $V_{DPUX}$ , one for the master device  $(V_{DPUM})$  and one for each of the selectable slave channels  $(V_{DPU0} - V_{DPU3})$ . In the event where the master device and all slave devices operate at the same voltage, then the pass voltage,  $V_{pass} = V_{DPUX}$ . Once the maximum Vpass is known, Vcc can be selected easily using Figure 7.2 In an application where voltage translation is necessary, additional design requirements must be considered (See Design Requirements).

Figure 7.1 shows an application in which the NCA9545 can be used.

<sup>&</sup>lt;sup>1</sup> Several interrupts can be active at the same time. For example, INT3 = 0, INT2 = 1, INT1 = 1, INT0 = 0 means that there is no interrupt on channels 0 and 3, and there is interrupt on channels 1 and 2.

Figure 7.1 Typical Application Schematic

#### 7.2. Design Requirements

The pull-up resistors on the INT3-INT0 terminals in the application schematic are not required in all applications. If the device generating the interrupt has an open-drain output structure or can be tri-stated, a pull-up resistor is required. If the device generating the interrupt has a push-pull output structure and cannot be tri-stated, a pull-up resistor is not required. The interrupt inputs should not be left floating in the application.

The A0 and A1 terminals are hardware selectable to control the slave address of the NCA9545. These terminals may be tied directly to GND or VCC in the application.

If multiple slave channels will be activated simultaneously in the application, then the total  $I_{OL}$  from SCL/SDA to GND on the master side will be the sum of the currents through all pull-up resistors,  $R_p$ .

The pass-gate transistors of the NCA9545 are constructed such that the VCC voltage can be used to limit the maximum voltage that is passed from one  $I^2C$  bus to another.

Figure 7.2 shows the voltage characteristics of the pass-gate transistors (note that the graph was generated using data specified in the Electrical Characteristics section of this data sheet). In order for the NCA9545 to act as a voltage translator, the  $V_{pass}$  voltage must be equal to or lower than the lowest bus voltage. For example, if the main bus is running at 5 V and the downstream buses are 3.3 V and 2.7 V,  $V_{pass}$  must be equal to or below 2.7 V to effectively clamp the downstream bus voltages. As shown in Figure 7.2, Vpass(max) is 2.7 V when the NCA9545A supply voltage is 4 V or lower, so the NCA9545A supply voltage could be set to 3.3 V. Pull-up resistors then can be used to bring the bus voltages to their appropriate levels (see Figure 7.1).

#### 7.3. Detailed Design Procedure

Once all the slaves are assigned to the appropriate slave channels and bus voltages are identified, the pull-up resistors,  $R_p$ , for each of the buses need to be selected appropriately. The minimum pull-up resistance is a function of  $V_{DPUX}$ ,  $V_{OL,(max)}$ , and  $I_{OL}$ :

$$R_{p(min)} = \frac{V_{DPUV} - V_{OL(max)}}{I_{OL}}$$

(1)

The maximum pull-up resistance is a function of the maximum rise time, tr (300 ns for fast-mode operation,  $f_{SCL}$  = 400 kHz) and bus capacitance,  $C_b$ :

$$R_{p(max)} = \frac{t_r}{0.8473 \times C_h} \tag{2}$$

The maximum bus capacitance for an  $I^2C$  bus must not exceed 400 pF for fast-mode operation. The bus capacitance can be approximated by adding the capacitance of the NCA9545,  $C_{io(OFF)}$ , the capacitance of wires/connections/traces, and the capacitance of each individual slave on a given channel. If multiple channels will be activated simultaneously, each of the slaves on all channels will contribute to total bus capacitance.

### 7.4. NCA9545 Application Curves

Figure 7.2 Pass-Gate Voltage (V<sub>pass</sub>) vs Supply Voltage(V<sub>CC</sub>) at Three Temperature Points

Figure 7.3 Maximum Pull-Up resistance(R<sub>p(max)</sub>) vs Bus Capacitance(C<sub>b</sub>)

Figure 7.4 Minimum Pull-Up resistance( $R_{p(min)}$ ) vs Pull-up reference voltage( $V_{DPUX}$ )

### 8. Layout

#### 8.1. Layout Guidelines

For PCB layout of the NCA9545, common PCB layout practices should be followed but additional concerns related to high-speed data transfer such as matched impedances and differential pairs are not a concern for I<sup>2</sup>C signal speeds. It is common to have a dedicated ground plane on an inner layer of the board and terminals that are connected to ground should have a low-impedance path to the ground plane in the form of wide polygon pours and multiple vias. By-pass and de-coupling capacitors are commonly used to control the voltage on the VCC terminal, using a larger capacitor to provide additional power in the event of a short power supply glitch and a smaller capacitor to filter out high-frequency ripple.

In an application where voltage translation is not required, all VDPUX voltages and VCC could be at the same potential and a single copper plane could connect all of pull-up resistors to the appropriate reference voltage. In an application where voltage translation is required, V<sub>DPU0</sub>, V<sub>DPU1</sub>, V<sub>DPU2</sub>, and V<sub>DPU3</sub> may all be on the same layer of the board with split planes to isolate different voltage potentials.

To reduce the total I2C bus capacitance added by PCB parasitics, data lines (SCn, SDn and INTn) should be a short as possible and the widths of the traces should also be minimized (e.g. 5-10 mils depending on copper weight).

Figure 8.1 Typical Application PCB

# 9. Package Information

Figure 9.1 Package outline for TSSOP20

### 10. Order information

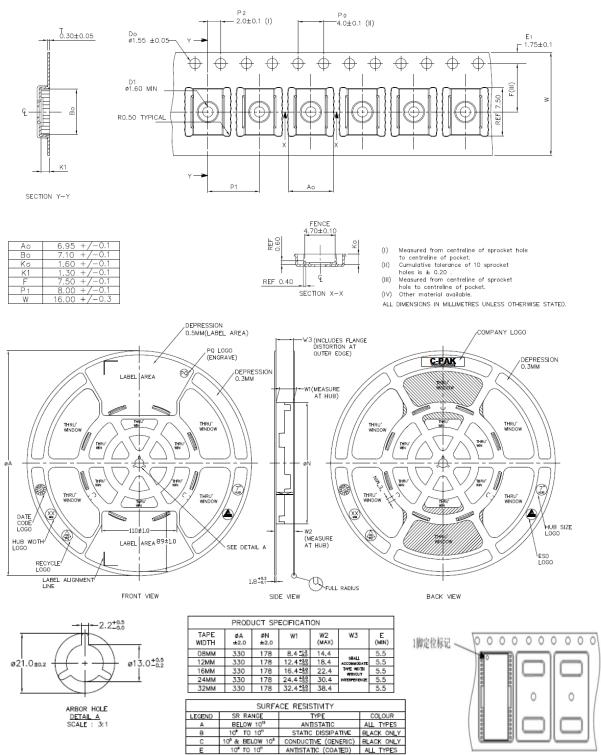

| Part Number  | Pins | Temperature | MSL | Package Type | Package Drawing | Package Qty |

|--------------|------|-------------|-----|--------------|-----------------|-------------|

| NCA9545-DTSR | 20   | -40 to 85℃  | 1   | TSSOP20      | TSSOP           | 2500        |

# 11. Documentation Support

| Part Number | Product Folder | Datasheet  | Technical Documents | Isolator selection guide |

|-------------|----------------|------------|---------------------|--------------------------|

| NCA9545     | Click here     | Click here | Click here          | Click here               |

### 12. Tape and Reel Information

Figure 12.1 Tape and Reel Information of TSSOP

# **13.** Revision History

| Revision | Description                     | Date      |

|----------|---------------------------------|-----------|

| 1.0      | Initial version                 | 2020/4/29 |

| 1.1      | Added tape and reel information | 2020/7/6  |

# **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Interface - Specialised category:

Click to view products by NOVOSENSE manufacturer:

Other Similar products are found below:

CY7C910-51LMB MC33689DPEWR2 MC33975ATEKR2 MEC1632-AUE MC33978AEK RKSAS4 FTP-637DSL633R MC33978AEKR2

TDA8035HN/C2/S1J MC34978AEK PCA9704PWJ S6BT112A01SSBB202 TC358870XBG(NOK) TC7PCI3212MT,LF(S MCW1001A

I/SS HOA6241-001 TDA8026ET/C2,518 AS3935-BQFT NCN8025MTTBG C100N50Z4A SN65HVD63RGTT TDA8034AT/C1,112

ISL35411DRZ-TS TDA8035HN/C1/S1J TDA8034HN/C1,118 ECSNOASP NCS2300MUTAG AD5700-1ACPZ-RL7 AD5700-1BCPZ-R5

AD5700ACPZ-RL7 LTC6820HMS#3ZZTRPBF AP 50 B10 AP 50 B420L VC120648D101RP DHR 100 C420 XL1192D XD7135

SP339EER1-L SP331CT-L SP336EEY-L SP337EUCY-L SP3508CF-L XR34350IL MC33972TEW MC33975ATEK HAIS 400-P HAIS

50-P HAIS 100-P HAS 200-S ST8024CTR