### NTE937M Integrated Circuit JFET Input Operational Amplifier

#### **Description:**

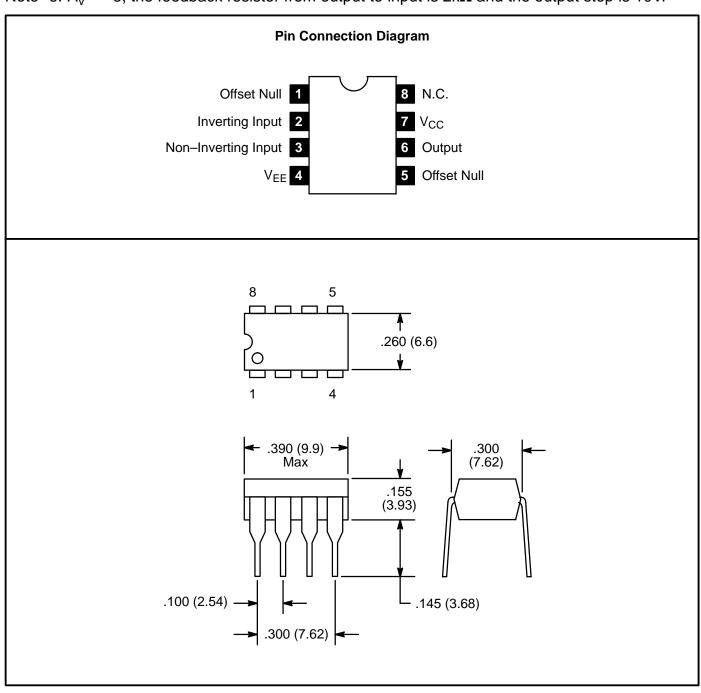

The NTE937M is a monolithic JFET input operational amplifier in an 8–Lead DIP type package incorporating well–matched, high voltage JFET's on the same chip with standard bi–polar transistors. This amplifier features low input bias and offset currents, low offset voltage and offset voltage drift, coupled with offset adjust which does not degrade drift or common–mode rejection. It is also designed for high slew rate, wide bandwidth, extremely fast settling time, low voltage and current noise and a low 1/f noise corner.

#### **Advantages:**

- Replaces Expensive Hybrid and Module FET OP Amps

- Rugged JFET's Allow Blow-Out Free Handling Compared with MOSFET Input Device

- Excellent for Low Noise Applications using either High or Low Source Impedance Very Low 1/f Corner

- Offset Adjust does not Degrade Drift or Common–Mode Rejection as in Most Monolithic Amplifiers

- New Output Stage Allows use of Large Capacitive Loads (10,000pF) without Stability Problems

- Internal Compensation and Large Differential Input Voltage Capability

#### **Applications:**

- Precision High Speed Integrators

- Fast D/A and A/D Converters

- High Impedance Buffers

- Wideband, Low Noise, Low Drift Amplifiers

- Logarithmic Amplifiers

- Photocell Amplifiers

- Sample and Hold Circuits

#### **Absolute Maximum Ratings:**

| Supply Voltage                                                      | ±18V             |

|---------------------------------------------------------------------|------------------|

| Maximum Power Dissipation (at +25°C, Note 1), P <sub>d</sub>        | 500mW            |

| Differential Input Voltage                                          | ±30V             |

| Input Voltage Range (Note 2)                                        | ±16V             |

| Output Short–Circuit Duration                                       | Continuous       |

| Maximum Operating Junction Temperature (Note 1), T <sub>J</sub> max | +100°C           |

| Storage Temperature Range, T <sub>stg</sub>                         | . –65° to +150°C |

| Lead Temperature (During Soldering, 10sec), T <sub>L</sub>          | +300°C           |

| Thermal Resistance, Junction–to–Ambient (Note 1), R <sub>thJC</sub> | +155°C/W         |

- Note 1. The maximum power dissipation for this device must be derated at elevated temperatures and is dictated by  $T_J$ max,  $R_{thJC}$ , and the ambient temperature,  $T_A$ . The maximum available power dissipation at any temperature is  $P_d = (T_J$ max  $T_A)/R_{thJC}$  or the +25°C  $P_d$ max, whichever is less.

- Note 2. Unless otherwise specified, the absolute maximum negative input voltage is equal to the negative power supply voltage.

#### **DC Electrical Characteristics:** $(T_A = +25C, V_S = \pm 15V \text{ unless otherwise specified})$

| Parameter      | Symbol          | Test Conditions | Min | Тур | Max | Unit |

|----------------|-----------------|-----------------|-----|-----|-----|------|

| Supply Current | I <sub>CC</sub> |                 | _   | 5   | 10  | mA   |

# <u>DC Electrical Characteristics:</u> $(V_S = \pm 15V, \, 0^\circ \le T_A \le +70^\circ C, \, T_{HIGH} = +70^\circ C \, unles \, otherwise \, specified)$

| Parameter                                        | Symbol                   | Test Conditions                               | Min | Тур              | Max   | Unit |  |

|--------------------------------------------------|--------------------------|-----------------------------------------------|-----|------------------|-------|------|--|

| Input Offset Voltage                             | Vos                      | $R_S = 50\Omega, T_A = +25^{\circ}C$          | _   | 3                | 10    | mV   |  |

|                                                  |                          | Over Temperature                              | _   | _                | 13    | mV   |  |

| Average TC of Input Offset Voltage               | $\Delta V_{OS}/\Delta T$ | $R_S = 50\Omega$ – 5 –                        |     |                  |       |      |  |

| Change in Average TC with V <sub>OS</sub> Adjust | ΔTC/ΔV <sub>OS</sub>     | $R_S = 50\Omega$ , Note 3                     | 0.5 | _                | μV/°C |      |  |

| Input Offset Current                             | Ios                      | $T_J = +25^{\circ}C$ , Note 4                 | _   | 3                | 50    | pА   |  |

|                                                  |                          | $T_J \le T_{HIGH}$                            | _   | _                | 2     | nA   |  |

| Input Bias Current                               | Ι <sub>Β</sub>           | $T_J = +25^{\circ}C$ , Note 4                 | _   | 30               | 200   | рА   |  |

|                                                  |                          | $T_J \le T_{HIGH}$                            | _   | _                | 8     | nA   |  |

| Input Resistance                                 | R <sub>IN</sub>          | $T_J = +25^{\circ}C$                          | _   | 10 <sup>12</sup> | _     | Ω    |  |

| Large Signal Voltage Gain                        | A <sub>VOL</sub>         | $T_A = +25$ °C, $V_O = \pm 10$ V, $R_L = 2$ k | 25  | 200              | _     | V/mV |  |

|                                                  |                          | Over Temperature                              | 15  | _                | _     | V/mV |  |

| Output Voltage Swing                             | Vo                       | R <sub>L</sub> = 10k                          | ±12 | ±13              | _     | V    |  |

|                                                  |                          | $R_L = 2k$                                    | ±10 | ±12              | _     | V    |  |

| Input Common–Mode Voltage Range                  | V <sub>CM</sub>          |                                               | ±10 | +15.1<br>-12     | _     | V    |  |

| Common–Mode Rejection Ratio                      | CMRR                     |                                               | _   | 80               | 100   | dB   |  |

| Supply Voltage Rejection Ratio                   | PSRR                     | Note 5 – 80 100                               |     |                  |       | dB   |  |

- Note 3. The temperature coeficient of the adjust input offset voltage changes only a small amount (0.5μV/°C typically) for each mV of adjustment from its original unadjusted value. Common—mode rejection and open loop voltage gain are also unaffected by offset adjustment.

- Note 4. The input bias currents are junction leakage currents which approximately double for every 10°C increase in the junction temperature, T<sub>J</sub>. Due to limited production test time, the input bias currents measured are correlated to junction temperature. In normal operation the junction temperature rises above the ambient temperature as a result of internal power dissipation, P<sub>d</sub>. T<sub>J</sub> = T<sub>A</sub> + R<sub>thJC</sub> P<sub>d</sub> where R<sub>thJC</sub> is the thermal resistance from junction to ambient. Use of a heat sink is recommended if input bias current is to be kept to a minimum.

- Note 5. Supply Voltage Rejection is measured for both supply magnitudes increasing or decreasing simultaneously, in accordance with common practice.

# <u>AC Electrical Characteristics:</u> $(T_A = +25C, V_S = \pm 15V \text{ unless otherwise specified)}$

| Parameter                      | Symbol          | Test Co                 | Min        | Тур | Max  | Unit |                    |

|--------------------------------|-----------------|-------------------------|------------|-----|------|------|--------------------|

| Slew Rate                      | SR              | $A_V = 5$               |            | 30  | 50   | _    | V/µs               |

| Gain Bandwidth Product         | GBW             |                         | _          | 20  | _    | MHz  |                    |

| Settling Time to 0.01%         | ts              | Note 6                  | _          | 1.5 | _    | μs   |                    |

| Equivalent Input Noise Voltage | e <sub>N</sub>  | $R_S = 100\Omega$       | f = 100Hz  | _   | 15   | _    | nV/√ <del>Hz</del> |

|                                |                 |                         | f = 1000Hz | _   | 12   | _    | nV/√ <del>Hz</del> |

| Equivalent Input Current Noise | i <sub>N</sub>  | f = 100Hz<br>f = 1000Hz |            | _   | 0.01 | _    | pA/√Hz             |

|                                |                 |                         |            | _   | 0.01 | _    | pA/√ <del>Hz</del> |

| Input Capacitance              | C <sub>IN</sub> |                         |            | _   | 3    | _    | pF                 |

Note 6.  $A_V = -5$ , the feedback resistor from output to input is  $2k\Omega$  and the output step is 10V.

## **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Operational Amplifiers - Op Amps category:

Click to view products by NTE manufacturer:

Other Similar products are found below:

OPA2991IDSGR OPA607IDCKT 007614D 633773R 635798C 635801A 702115D 709228FB 741528D NCV33072ADR2G SC2903DR2G SC2903VDR2G LM258AYDT LM358SNG 430227FB 430228DB 460932C AZV831KTR-G1 409256CB 430232AB LM2904DR2GH LM358YDT LT1678IS8 042225DB 058184EB 070530X 714228XB 714846BB 873836HB MIC918YC5-TR TS912BIYDT NCS2004MUTAG NCV33202DMR2G M38510/13101BPA NTE925 SC2904DR2G SC358DR2G LM358EDR2G AZV358MTR-G1 AP4310AUMTR-AG1 HA1630D02MMEL-E NJM358CG-TE2 HA1630S01LPEL-E LM324AWPT HA1630Q06TELL-E NJM4558CG-TE2 AZV358MMTR-G1 SCY33178DR2G NCS4325DR2G LM7301SN1T1G