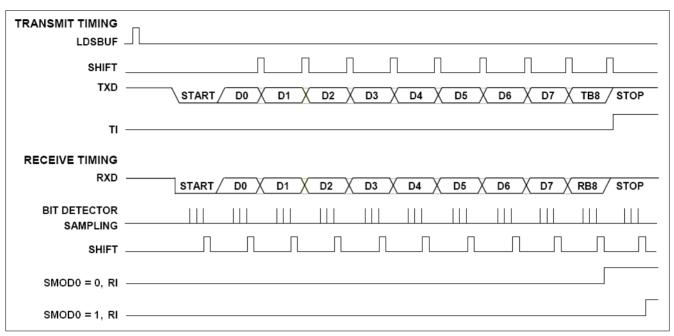

# **Nuvoton 1T 8051-based Microcontroller**

# N76E003

Datasheet

# TABLE OF CONTENTS

| 1. GENERAL DESCRIPTION                 |                             |           |

|----------------------------------------|-----------------------------|-----------|

| 2. FEATURES                            |                             |           |

| 3. BLOCK DIAGRAM                       |                             |           |

| 4. PIN CONFIGURATION                   |                             |           |

| 5. MEMORY ORGANIZATION                 |                             |           |

| 5.1 Program Memory                     |                             |           |

| 5.2 Data Memory                        |                             |           |

| 5.3 On-Chip XRAM                       |                             |           |

| 5.4 Non-Volatile Data Storage          |                             |           |

| 6. SPECIAL FUNCTION REGISTER (SFR)     |                             |           |

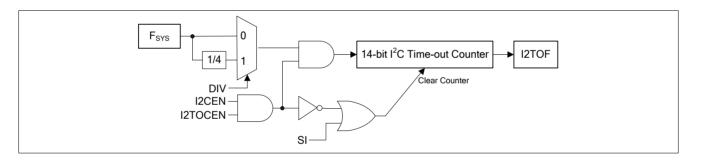

| 6.1 ALL SFR DESCRIPTION                |                             |           |

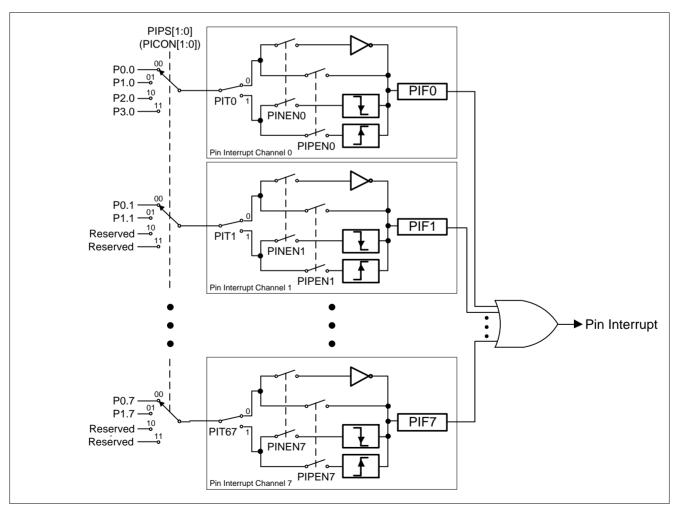

| 7. I/O PORT STRUCTURE AND OPERATION    | ۱                           |           |

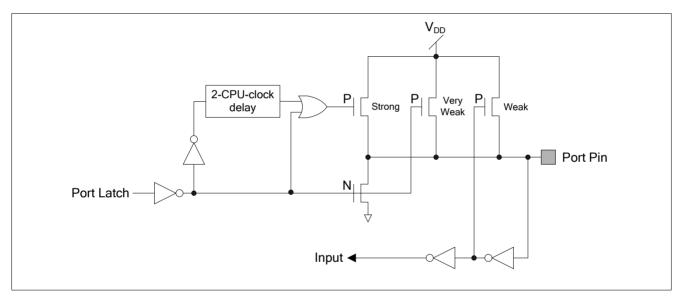

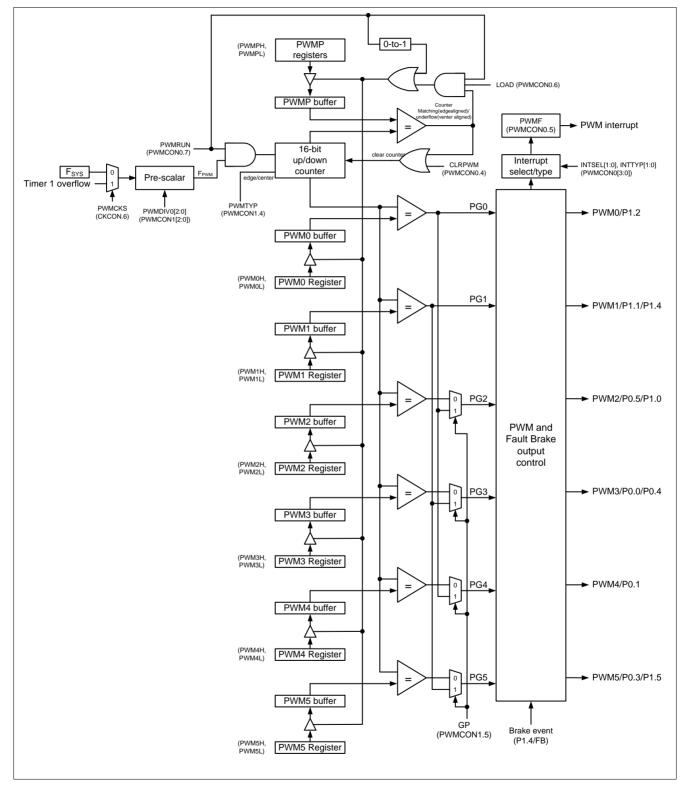

| 7.1 Quasi-Bidirectional Mode           |                             |           |

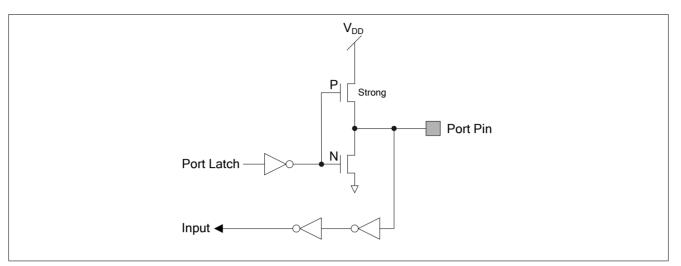

| 7.2 Push-Pull Mode                     |                             |           |

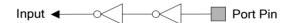

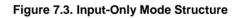

| 7.3 Input-Only Mode                    |                             |           |

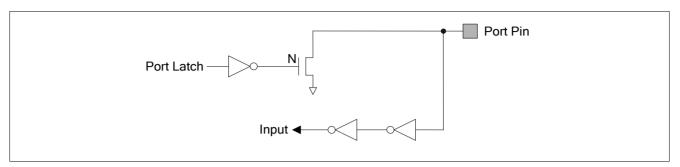

| 7.4 Open-Drain Mode                    |                             |           |

| 7.5 Read-Modify-Write Instructions     |                             |           |

| 7.6 Control Registers of I/O Ports     |                             |           |

| 7.6.1 Input and Output Data Control    |                             |           |

| 7.6.2 Output Mode Control              |                             |           |

| 7.6.3 Input Type                       |                             |           |

| 7.6.4 Output Slew Rate Control         |                             |           |

| 8. TIMER/COUNTER 0 AND 1               |                             |           |

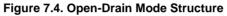

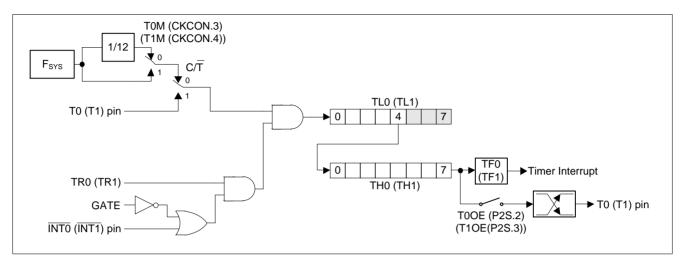

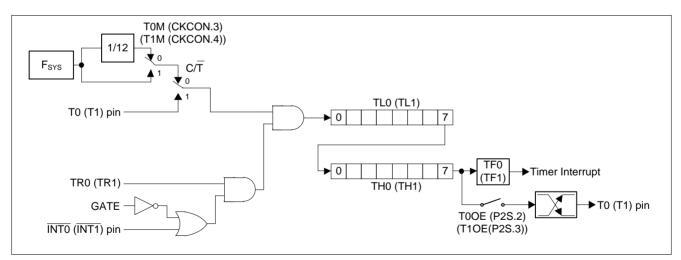

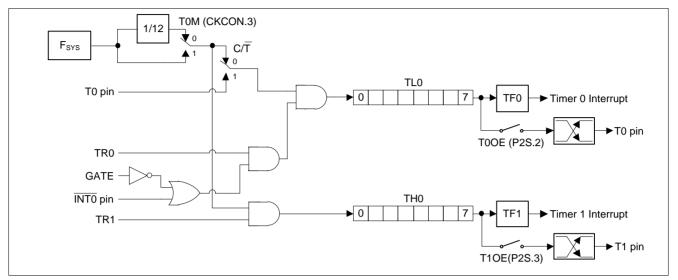

| 8.1 Mode 0 (13-Bit Timer)              |                             |           |

| 8.2 Mode 1 (16-Bit Timer)              |                             |           |

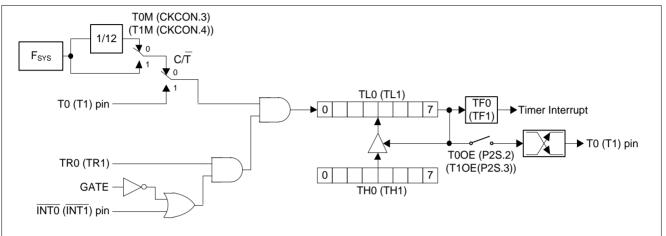

| 8.3 Mode 2 (8-Bit Auto-Reload Timer)   |                             |           |

| 8.4 Mode 3 (Two Separate 8-Bit Timers) |                             |           |

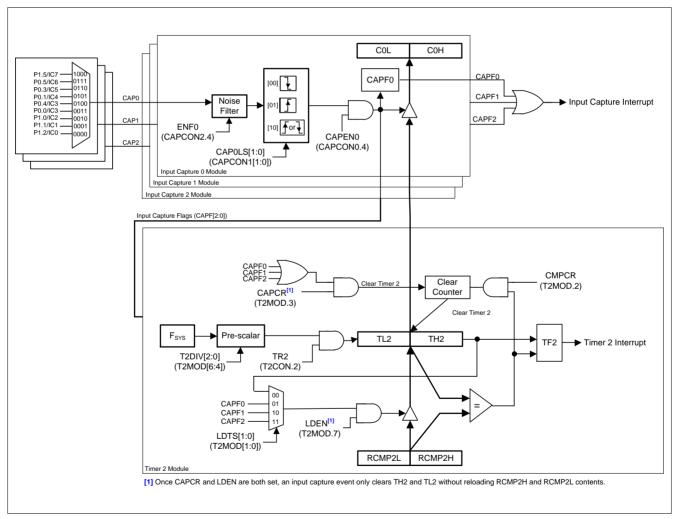

| 9. TIMER 2 AND INPUT CAPTURE           |                             |           |

| 9.1 Auto-Reload Mode                   |                             |           |

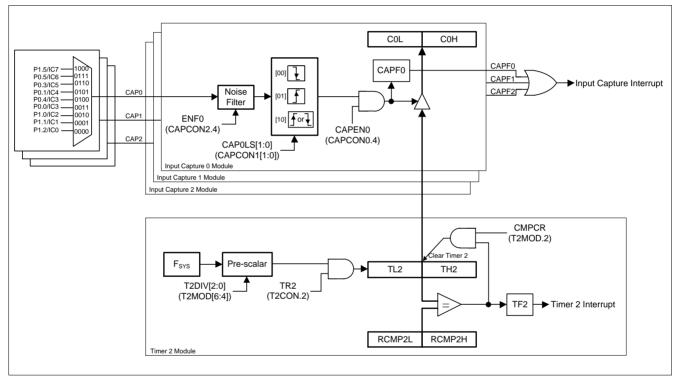

| 9.2 Compare Mode                       |                             |           |

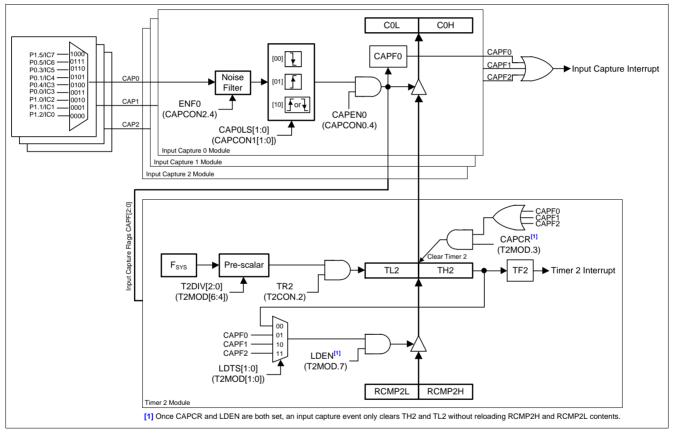

| 9.3 Input Capture Module               |                             |           |

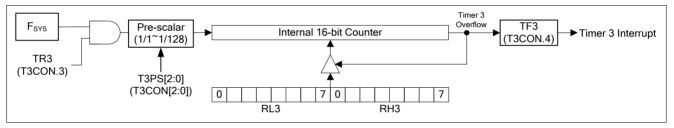

| 10. TIMER 3                            |                             |           |

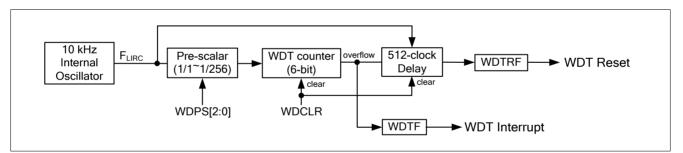

| 11. WATCHDOG TIMER (WDT)               |                             |           |

| 11.1 Time-Out Reset Timer              |                             |           |

| 11.2 General Purpose Timer             |                             |           |

| 12. SELF WAKE-UP TIMER (WKT)           |                             |           |

| 13. SERIAL PORT (UART)                 |                             |           |

| 13.1 Mode 0                            |                             |           |

|                                        |                             |           |

| 13.2 Mode 1                            |                             |           |

| 13.3 Mode 2                            |                             |           |

| 13.4 Mode 3                            |                             |           |

| 13.5 Baud Rate                         |                             |           |

| 13.6 Framing Error Detection           |                             |           |

| 13.7 Multiprocessor Communication      |                             |           |

| 13.8 Automatic Address Recognition     |                             |           |

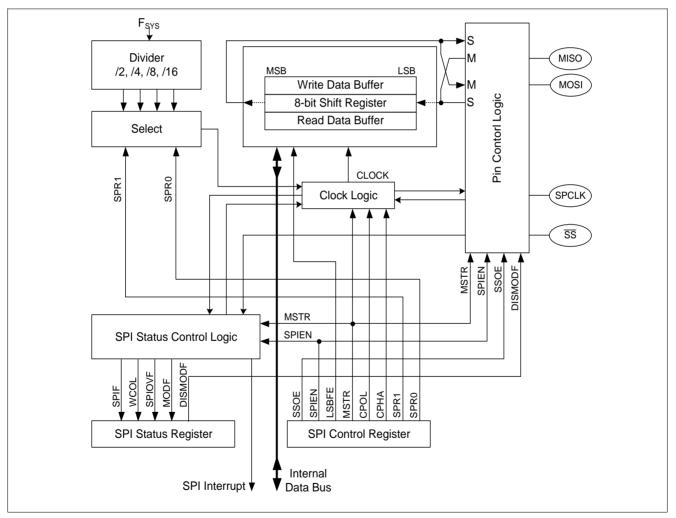

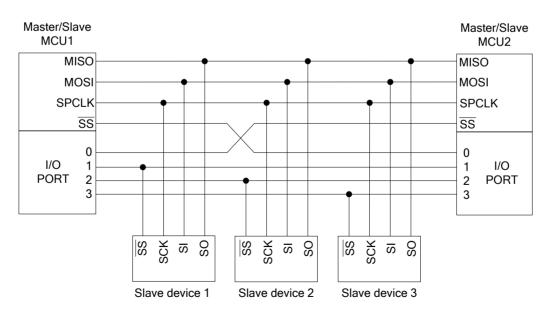

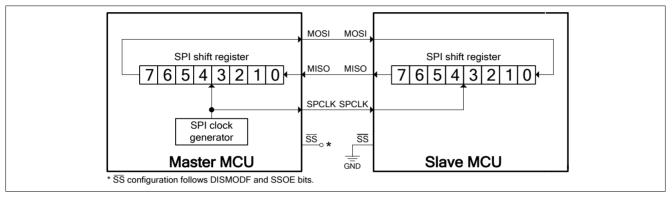

| 14. SERIAL PERIPHERAL INTERFACE (SPI)  |                             |           |

| 14.1 Functional Description            |                             |           |

| Dec. 13, 2017                          | Page <b>2</b> of <b>273</b> | Rev. 1.04 |

# ηυνοΤοη

| 14.2 Operating Modes                     |                                       | 147       |

|------------------------------------------|---------------------------------------|-----------|

|                                          |                                       |           |

|                                          |                                       |           |

|                                          | ata Transfer                          |           |

|                                          | iguration                             |           |

|                                          |                                       |           |

|                                          |                                       |           |

|                                          |                                       |           |

|                                          |                                       |           |

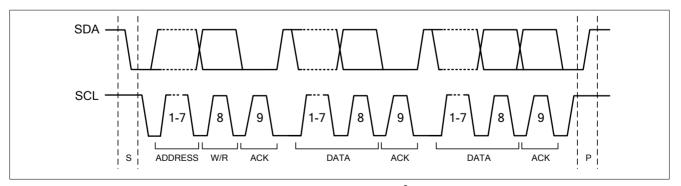

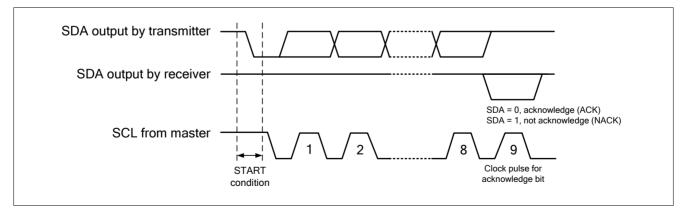

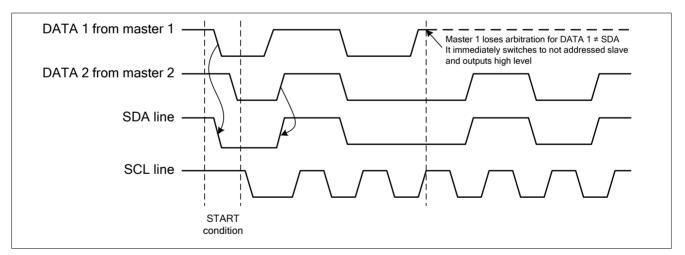

| 15. INTER-INTEGRATED CIRC                | CUIT (I <sup>2</sup> C)               |           |

|                                          | 1                                     |           |

|                                          | OP Condition                          |           |

|                                          | vith Data Format                      |           |

|                                          |                                       |           |

|                                          |                                       |           |

| 15.2 Control Registers of I <sup>2</sup> | C                                     |           |

|                                          | -                                     |           |

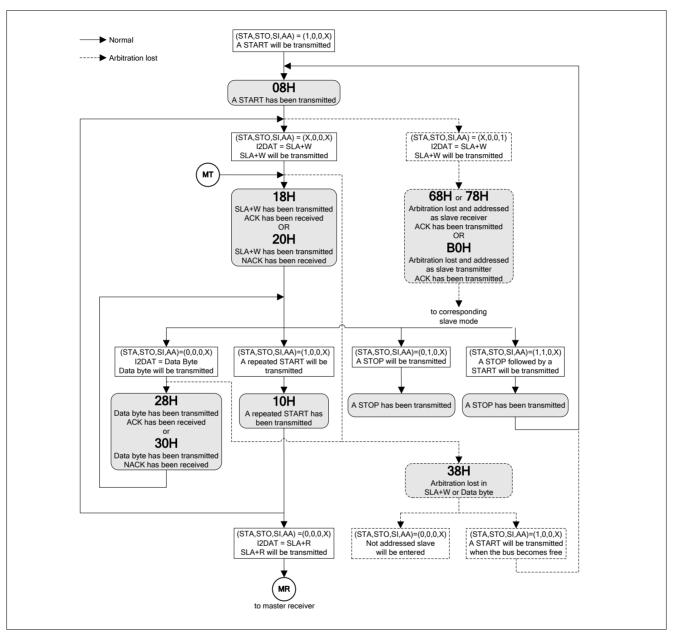

|                                          | itter Mode                            |           |

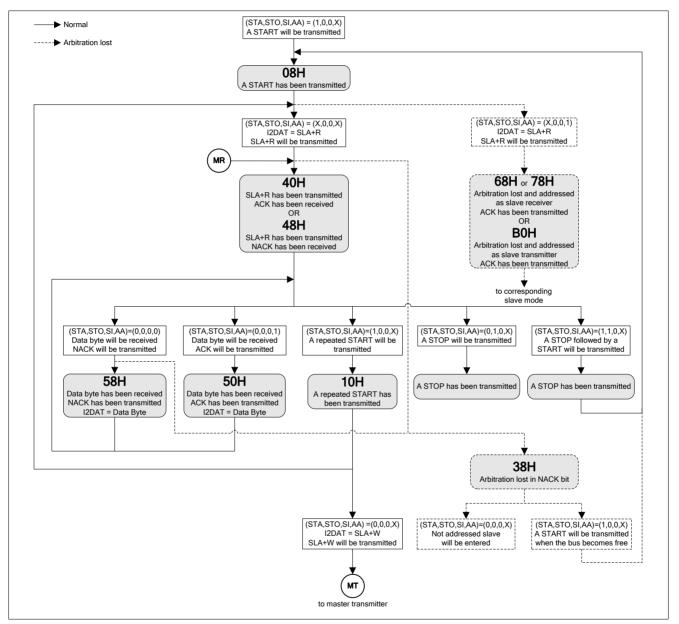

|                                          | er Mode                               |           |

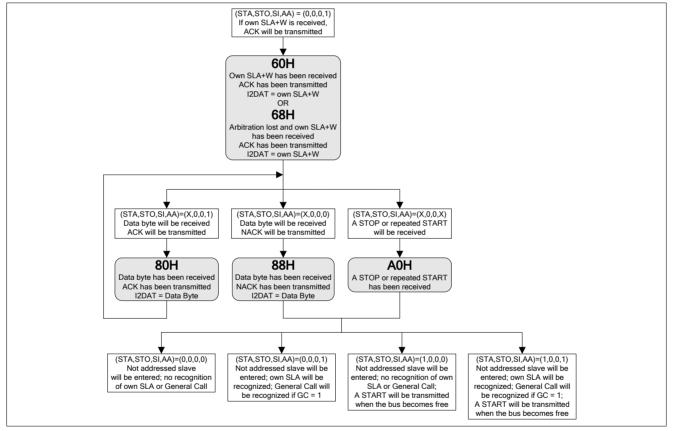

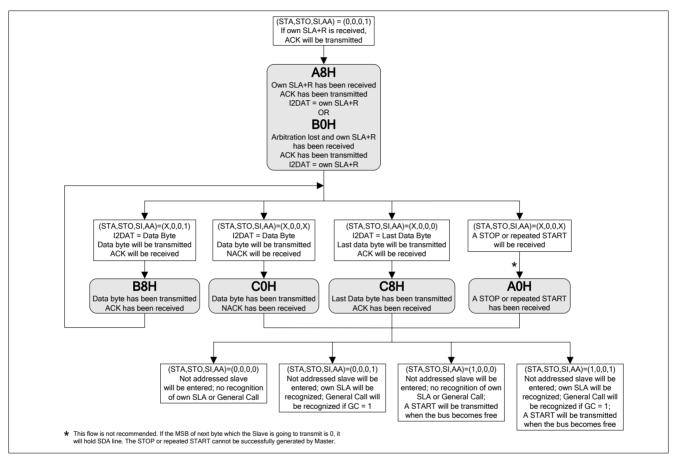

|                                          | Mode                                  |           |

|                                          | ter Mode                              |           |

|                                          |                                       |           |

| 15.3.6 Miscellaneous                     | States                                |           |

| 15.4 Typical Structure of I <sup>2</sup> | C Interrupt Service Routine           |           |

|                                          | · · · · · · · · · · · · · · · · · · · |           |

|                                          |                                       |           |

| •                                        |                                       |           |

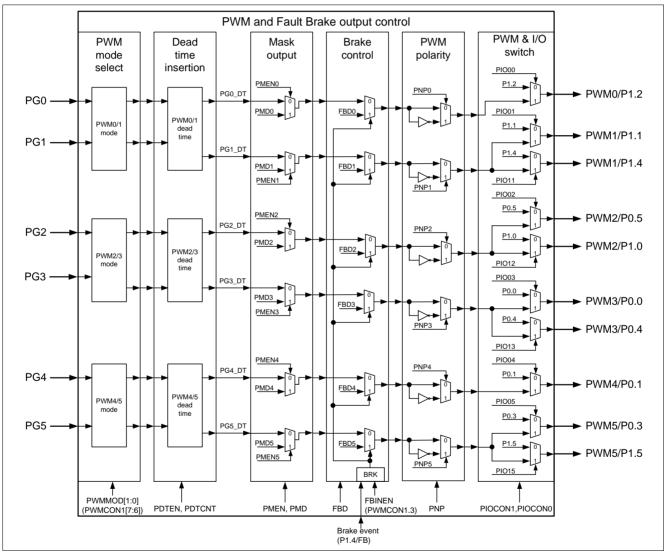

|                                          | ED (PWM)                              |           |

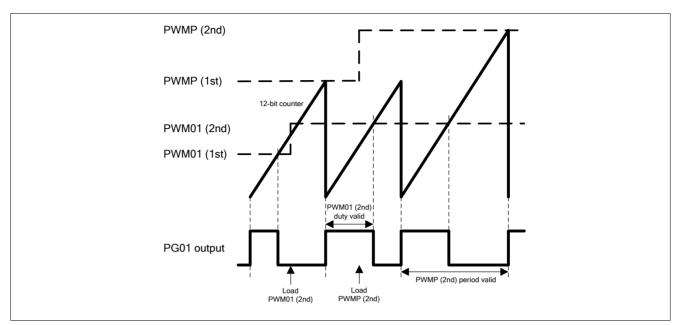

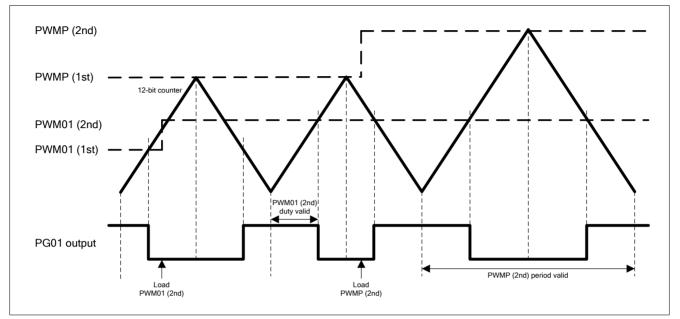

|                                          | ()                                    |           |

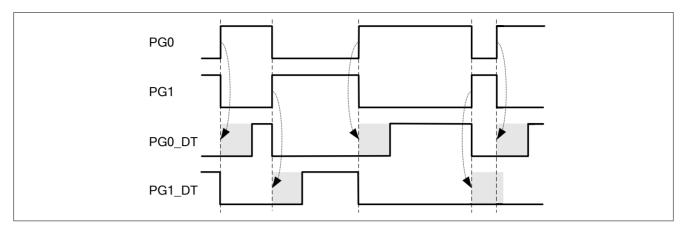

|                                          | )r                                    |           |

|                                          |                                       |           |

|                                          | es                                    |           |

|                                          | ontrol                                |           |

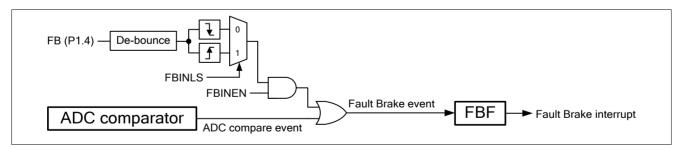

| 17.1.5 Fault Brake                       |                                       |           |

| 17.1.6 Polarity Control                  | l                                     |           |

|                                          |                                       |           |

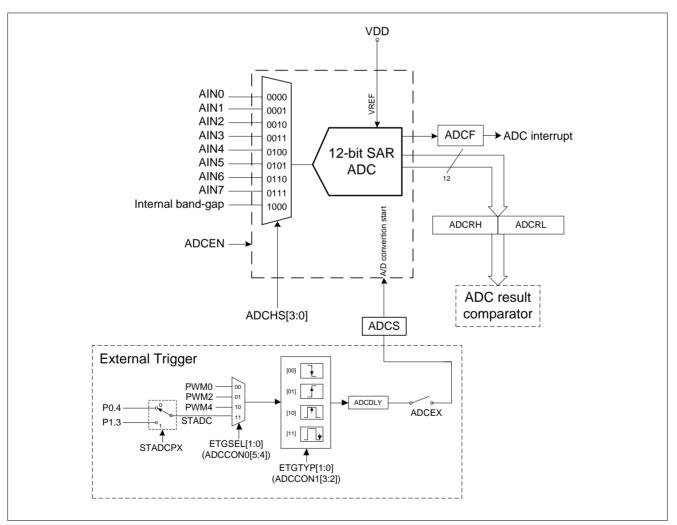

| 18. 12-BIT ANALOG-TO-DIGIT               | TAL CONVERTER (ADC)                   |           |

| •                                        | ۱                                     |           |

| 18.1.1 ADC Operation                     |                                       |           |

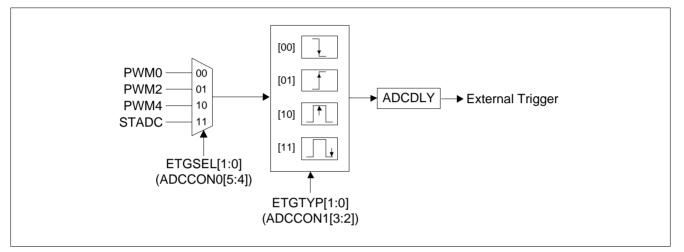

|                                          | on Triggered by External Source       |           |

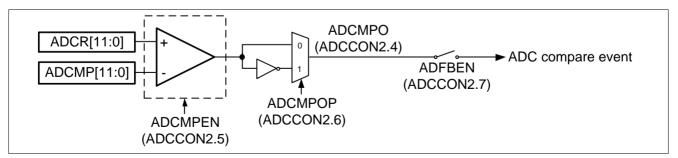

|                                          | on Result Comparator                  |           |

|                                          | ap                                    |           |

| 18.2 Control Registers of A              | DC                                    |           |

|                                          | TION (TA)                             |           |

|                                          |                                       |           |

|                                          |                                       |           |

|                                          |                                       |           |

| •                                        | -                                     |           |

| Dec. 13, 2017                            | Page <b>3</b> of <b>273</b>           | Rev. 1.04 |

|     | 20.4 Interrupt Service                         |     |

|-----|------------------------------------------------|-----|

|     | 20.5 Interrupt Latency                         | 217 |

|     | 20.6 External Interrupt Pins                   | 217 |

| 21. | IN-APPLICATION-PROGRAMMING (IAP)               | 219 |

|     | 21.1 IAP Commands                              | 222 |

|     | 21.2 IAP User Guide                            |     |

|     | 21.3 Using Flash Memory as Data Storage        | 223 |

|     | 21.4 In-System-Programming (ISP)               |     |

| 22. | POWER MANAGEMENT                               |     |

|     | 22.1 Power-Down Mode                           |     |

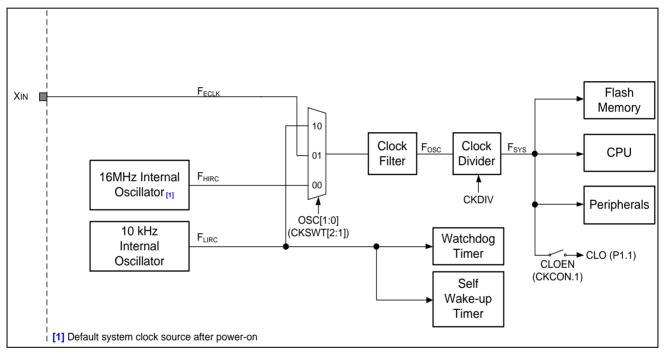

| 23. | CLOCK SYSTEM                                   |     |

|     | 23.1 System Clock Sources                      |     |

|     | 23.1.1 Internal Oscillators                    |     |

|     | 23.2 System Clock Switching                    |     |

|     | 23.3 System Clock Divider                      |     |

|     | 23.4 System Clock Output                       |     |

| 24  | POWER MONITORING                               |     |

|     | 24.1 Power-On Reset (POR)                      |     |

|     | 24.2 Brown-Out Detection (BOD)                 |     |

| 25. | RESET                                          |     |

| _0. | 25.1 Power-On Reset                            |     |

|     | 25.2 Brown-Out Reset                           |     |

|     | 25.3 External Reset                            |     |

|     | 25.4 Hard Fault Reset                          |     |

|     | 25.5 Watchdog Timer Reset                      | -   |

|     | 25.6 Software Reset                            |     |

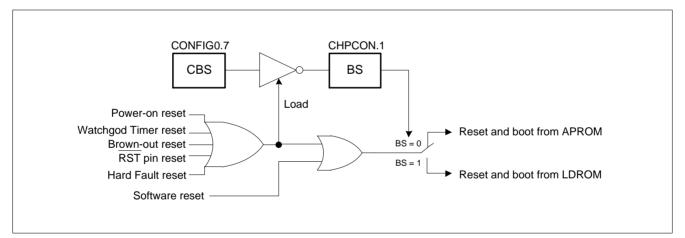

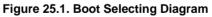

|     | 25.7 Boot Select                               |     |

|     | 25.8 Reset State                               |     |

| 26. | AUXILIARY FEATURES                             |     |

|     | 26.1 Dual DPTRs                                |     |

|     | 26.2 96-bit UID                                |     |

| 27. | ON-CHIP-DEBUGGER (OCD)                         |     |

|     | 27.1 Functional Description                    |     |

|     | 27.2 Limitation of OCD                         |     |

| 28. | CONFIG BYTES                                   |     |

| 29. | IN-CIRCUIT-PROGRAMMING (ICP)                   | 256 |

|     | INSTRUCTION SET                                |     |

| 31. | ELECTRICAL CHARACTERISTICS                     | 261 |

|     | 31.1 Absolute Maximum Ratings                  |     |

|     | 31.2 D.C. Electrical Characteristics           |     |

|     | 31.3 A.C. Electrical Characteristics           | 263 |

|     | 31.4 Analog Electrical Characteristics         |     |

|     | 31.5 ESD Characteristics                       |     |

|     | 31.6 EFT Characteristics                       |     |

|     | 31.7 Flash DC Electrical Characteristics       |     |

| 32. | PACKAGE DIMENSIONS                             |     |

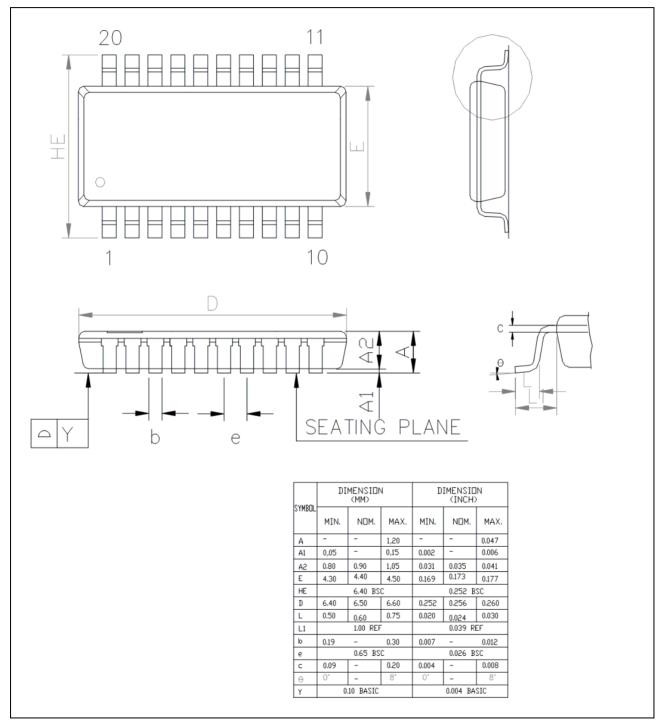

|     | 32.1 20-pin TSSOP - 4.4 X 6.5 mm               |     |

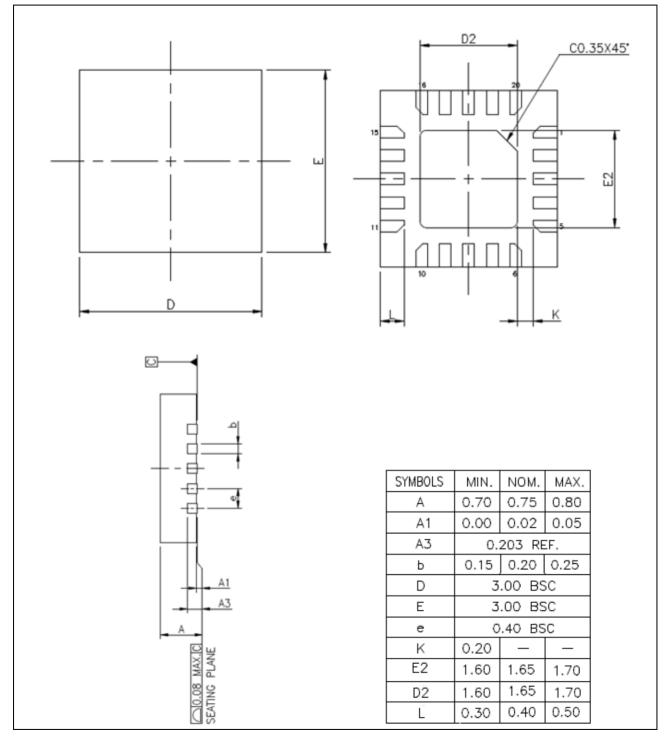

|     | 32.2 20-pin QFN – 3.0 X 3.0 mm for N76E003AQ20 | 270 |

|     |                                                |     |

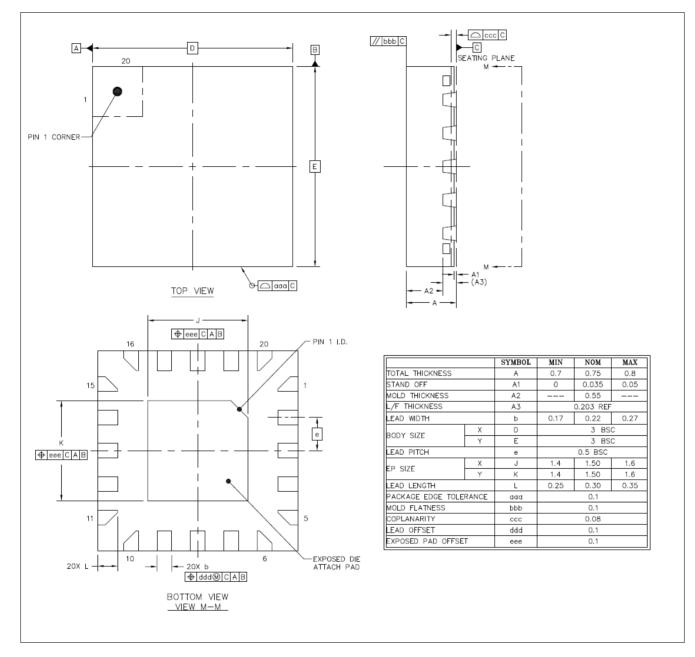

| 32.3 20-pin QFN – 3.0 X 3.0 mm for N76E003BQ20 27 | 1 |

|---------------------------------------------------|---|

| 33. DOCUMENT REVISION HISTORY 27                  | 2 |

### **1. GENERAL DESCRIPTION**

The N76E003 is an embedded flash type, 8-bit high performance 1T 8051-based microcontroller. The instruction set is fully compatible with the standard 80C51 and performance enhanced.

The N76E003 contains a up to 18K Bytes of main Flash called APROM, in which the contents of User Code resides. The N76E003 Flash supports In-Application-Programming (IAP) function, which enables on-chip firmware updates. IAP also makes it possible to configure any block of User Code array to be used as non-volatile data storage, which is written by IAP and read by IAP or MOVC instruction. There is an additional Flash called LDROM, in which the Boot Code normally resides for carrying out In-System-Programming (ISP). The LDROM size is configurable with a maximum of 4K Bytes. To facilitate programming and verification, the Flash allows to be programmed and read electronically by parallel Writer or In-Circuit-Programming (ICP). Once the code is confirmed, user can lock the code for security.

The N76E003 provides rich peripherals including 256 Bytes of SRAM, 768 Bytes of auxiliary RAM (XRAM), Up to 18 general purpose I/O, two 16-bit Timers/Counters 0/1, one 16-bit Timer2 with three-channel input capture module, one Watchdog Timer (WDT), one Self Wake-up Timer (WKT), one 16-bit auto-reload Timer3 for general purpose or baud rate generator, two UARTs with frame error detection and automatic address recognition, one SPI, one I<sup>2</sup>C, five enhanced PWM output channels, eight-channel shared pin interrupt for all I/O, and one 12-bit ADC. The peripherals are equipped with 18 sources with 4-level-priority interrupts capability.

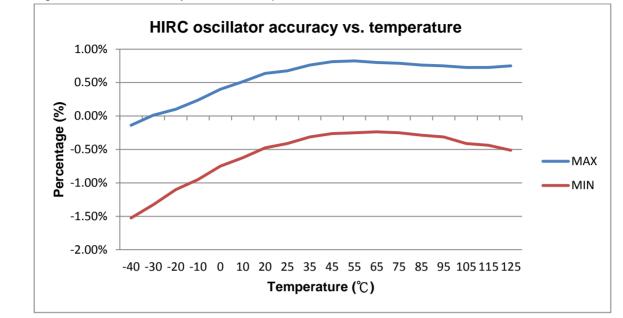

The N76E003 is equipped with three clock sources and supports switching on-the-fly via software. The three clock sources include external clock input, 10 kHz internal oscillator, and one 16 MHz internal precise oscillator that is factory trimmed to  $\pm$ 1% at room temperature. The N76E003 provides additional power monitoring detection such as power-on reset and 4-level brown-out detection, which stabilizes the power-on/off sequence for a high reliability system design.

The N76E003 microcontroller operation consumes a very low power with two economic power modes to reduce power consumption — Idle and Power-down mode, which are software selectable. Idle mode turns off the CPU clock but allows continuing peripheral operation. Power-down mode stops the whole system clock for minimum power consumption. The system clock of the N76E003 can also be slowed down by software clock divider, which allows for a flexibility between execution performance and power consumption.

With high performance CPU core and rich well-designed peripherals, the N76E003 benefits to meet a general purpose, home appliances, or motor control system accomplishment.

# 2. FEATURES

- CPU:

- Fully static design 8-bit high performance 1T 8051-based CMOS microcontroller.

- Instruction set fully compatible with MCS-51.

- 4-priority-level interrupts capability.

- Dual Data Pointers (DPTRs).

- Operating:

- Wide supply voltage from 2.4V to 5.5V.

- Wide operating frequency up to 16 MHz.

- Industrial temperature grade: -40 $^{\circ}$ C to +105 $^{\circ}$ C.

- Memory:

- Up to 18K Bytes of APROM for User Code.

- Configurable 4K/3K/2K/1K/0K Bytes of LDROM, which provides flexibility to user developed Boot Code.

- Flash Memory accumulated with pages of 128 Bytes each.

- Built-in In-Application-Programmable (IAP).

- Code lock for security.

- 256 Bytes on-chip RAM.

- Additional 768 Bytes on-chip auxiliary RAM (XRAM) accessed by MOVX instruction.

- Clock sources:

- 16 MHz high-speed internal oscillator trimmed to  $\pm$ 1% when V<sub>DD</sub> 5.0V,  $\pm$ 2% in all conditions.

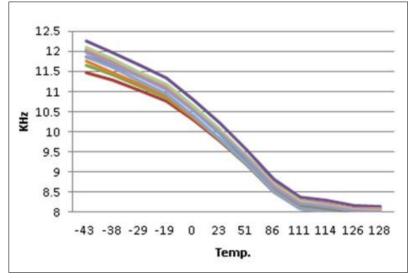

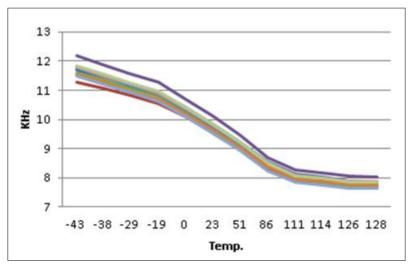

- 10 kHz low-speed internal oscillator.

- External clock input.

- On-the-fly clock source switch via software.

- Programmable system clock divider up to 1/512.

- Peripherals:

- Up to 17 general purpose I/O pins and one input-only pin. All output pins have individual 2-level slew rate control.

- Standard interrupt pins INTO and INT1.

- Two 16-bit Timers/Counters 0 and 1 compatible with standard 8051.

- One 16-bit Timer 2 with three-channel input capture module and 9 input pin can be selected.

- One 16-bit auto-reload Timer 3, which can be the baud rate clock source of UARTs.

- One 16-bit PWM counter interrupt for timer.

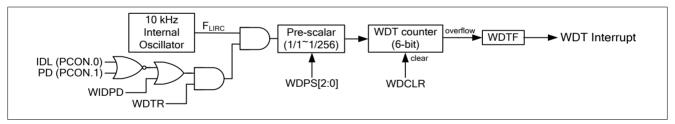

- One programmable Watchdog Timer (WDT) clocked by dedicated 10 kHz internal source.

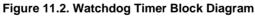

- One dedicated Self Wake-up Timer (WKT) for self-timed wake-up for power reduced modes.

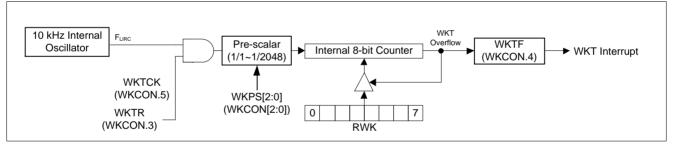

- Two full-duplex UART ports with frame error detection and automatic address recognition. TXD and RXD pins of UART0 exchangeable via software.

- One SPI port with master and slave modes, up to 8 Mbps when system clock is 16 MHz.

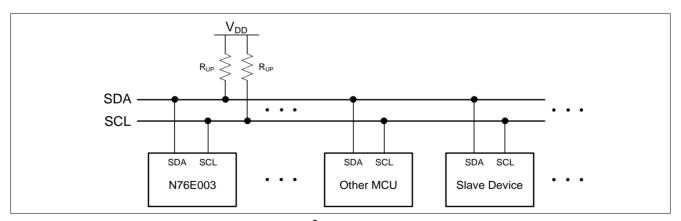

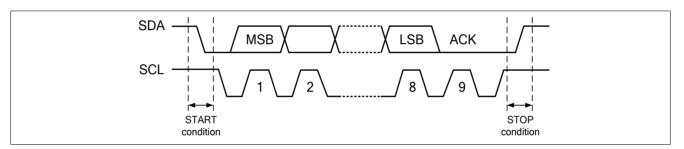

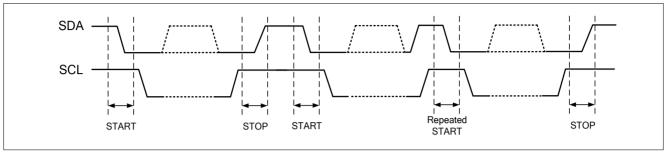

- One  $I^2C$  bus with master and slave modes, up to 400 kbps data rate.

- Three pairs, six channels of pulse width modulator (PWM) output, 10 output pins can be selected., up to 16-bit resolution, with different modes and Fault Brake function for motor control.

- Eight channels of pin interrupt, shared for all I/O ports, with variable configuration of edge/level detection.

- One 12-bit ADC, up to 500 ksps converting rate, hardware triggered and conversion result compare facilitating motor control.

- Power management:

- Two power reduced modes: Idle and Power-down mode.

- Power monitor:

NUVOTON

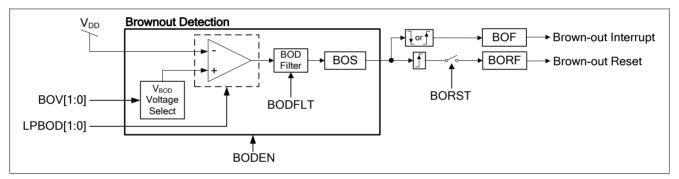

- Brown-out detection (BOD) with low power mode available, 4-level selection, interrupt or reset options.

- Power-on reset (POR).

- Strong ESD and EFT immunity.

- Development Tools:

- Nuvoton On-Chip-Debugger (OCD) with  $KEIL^{TM}$  development environment.

- Nuvoton In-Circuit-Programmer (ICP).

- Nuvoton In-System-Programming (ISP) via UART.

• Part numbers and packages:

| Part Number | APROM                       | LDROM          | Package  |

|-------------|-----------------------------|----------------|----------|

| N76E003AT20 | 18K Bytes shared with LDROM | Up to 4K Bytes | TSSOP 20 |

| N76E003AQ20 | 18K Bytes shared with LDROM | Up to 4K Bytes | QFN 20   |

| N76E003BQ20 | 18K Bytes shared with LDROM | Up to 4K Bytes | QFN 20   |

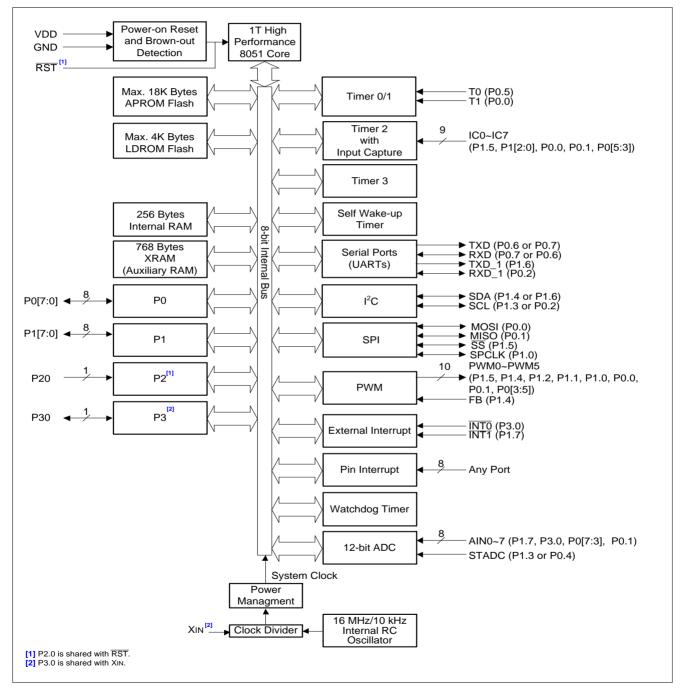

# **3. BLOCK DIAGRAM**

Figure 3.1 shows the N76E003 functional block diagram and gives the outline of the device. User can find all the peripheral functions of the device in the diagram.

Figure 3.1. Functional Block Diagram

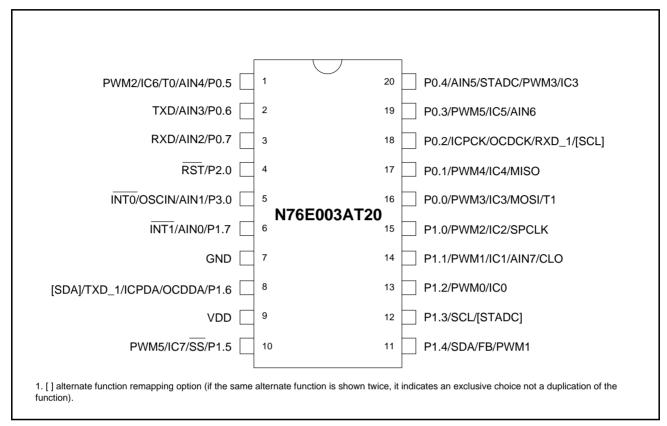

# 4. PIN CONFIGURATION

Figure 4.1. Pin Assignment of TSSOP-20 Package

# nuvoTon

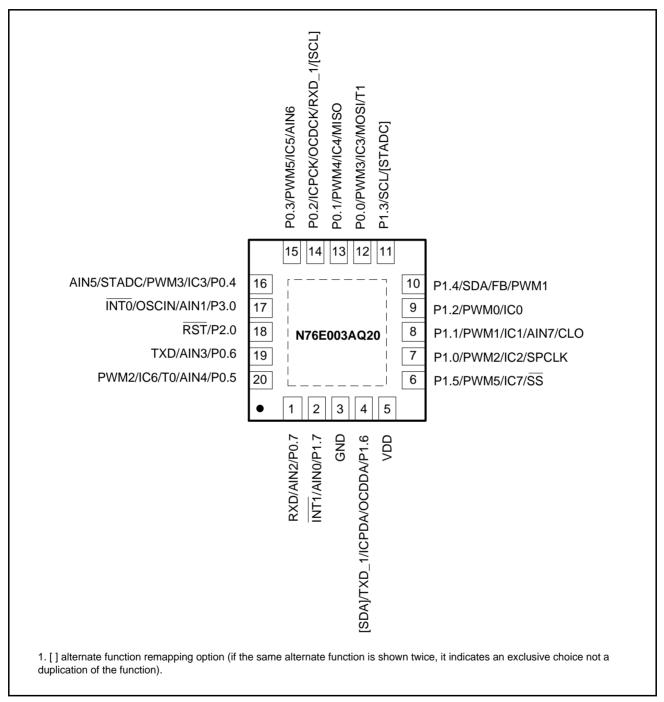

Figure 4.2. Pin Assignment of QFN-20 Package for N76E003AQ20

# nuvoTon

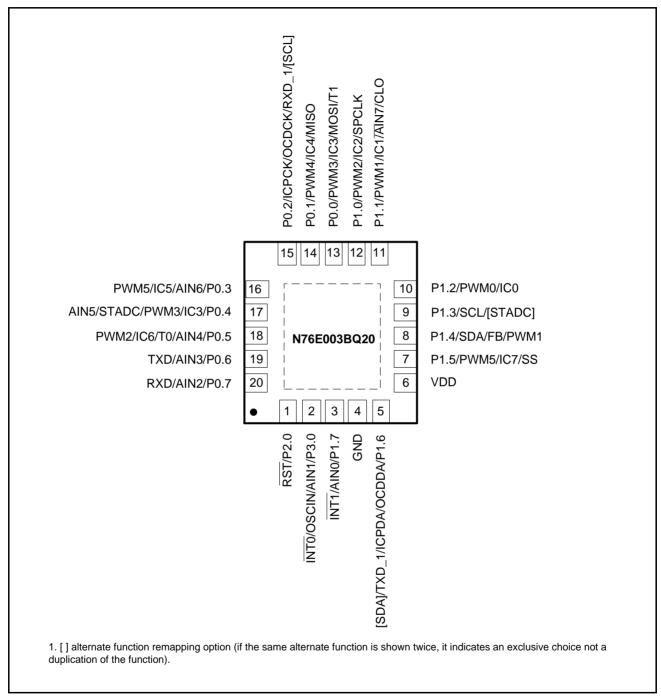

Figure 4.3. Pin Assignment of QFN-20 Package for N76E003BQ20

٦

# nuvoTon

Г

|             | Pin Number  |             | Cumhal                   | Multi-Function Description <sup>[1]</sup>                          |

|-------------|-------------|-------------|--------------------------|--------------------------------------------------------------------|

| N76E003AT20 | N76E003AQ20 | N76E003BQ20 | Symbol                   | Multi-Function Description**                                       |

| 9           | 5           | 6           | VDD                      | <b>POWER SUPPLY:</b> Supply voltage V <sub>DD</sub> for operation. |

| 7           | 3           | 4           | GND                      | GROUND: Ground potential.                                          |

| ,           | 0           |             |                          | <b>P0.0:</b> Port 0 bit 0.                                         |

|             |             |             |                          | PWM3: PWM output channel 3.                                        |

|             |             |             |                          | MOSI: SPI master output/slave input.                               |

| 16          | 12          | 13          | P0.0/PWM3/IC3/MOSI/T1    | IC3: Input capture channel 3.                                      |

|             |             |             |                          | <b>T1:</b> External count input to Timer/Counter 1 or its          |

|             |             |             |                          | toggle output.                                                     |

|             |             |             |                          | <b>P0.1:</b> Port 0 bit 1.                                         |

|             |             |             |                          | <b>PWM4:</b> PWM output channel 4.                                 |

| 17          | 13          | 14          | P0.1/PWM4/IC4/MISO       | IC4: Input capture channel 4.                                      |

|             |             |             |                          | MISO: SPI master input/slave output.                               |

|             |             |             |                          | <b>P0.2:</b> Port 0 bit 2.                                         |

|             |             |             |                          | ICPCK: ICP clock input.                                            |

| 18          | 14          | 15          | P0.2/ICPCK/OCDCK/        | OCDCK: OCD clock input.                                            |

| 10          | 17          | 10          | RXD_1/[SCL]              | <b>RXD_1:</b> Serial port 1 receive input.                         |

|             |             |             |                          | [SCL] <sup>[3]</sup> : I <sup>2</sup> C clock.                     |

|             |             |             |                          | <b>P0.3:</b> Port 0 bit 3.                                         |

|             |             |             |                          | <b>PWM5:</b> PWM output channel                                    |

| 19          | 15          | 16          | P0.3/PWM5/IC5/AIN6       | IC5: Input capture channel 5.                                      |

|             |             |             |                          | AIN6: ADC input channel 6.                                         |

|             |             |             |                          | <b>P0.4:</b> Port 0 bit 4.                                         |

|             |             |             |                          | AIN5: ADC input channel 5.                                         |

| 20          | 16          | 17          | P0.4/AIN5/STADC/         | STADC: External start ADC trigger                                  |

| 20          | 10          | 17          | PWM3/IC3                 | <b>PWM3:</b> PWM output channel 3.                                 |

|             |             |             |                          | IC3: Input capture channel 3.                                      |

|             |             |             |                          | <b>P0.5:</b> Port 0 bit 5.                                         |

|             |             |             |                          | <b>PWM2:</b> PWM output channel 2.                                 |

| 1           | 20          | 18          | P0.5/PWM2/IC6/T0/AIN4    | IC6: Input capture channel 6.                                      |

|             | 20          | 10          | 1 0.3/1 WWZ/100/10/All 4 | <b>T0:</b> External count input to Timer/Counter 0 or its          |

|             |             |             |                          | toggle output.                                                     |

|             |             |             |                          | <b>P0.6:</b> Port 0 bit 6.                                         |

| 2           | 19          | 19          | P0.6/TXD/AIN3            | <b>TXD</b> <sup>[2]</sup> : Serial port 0 transmit data output.    |

| -           | 10          | 10          |                          | AIN3: ADC input channel 3.                                         |

|             |             |             |                          | <b>P0.7:</b> Port 0 bit 7.                                         |

| 3           | 1           | 20          | P0.7/RXD/AIN2            | <b>RXD:</b> Serial port 0 receive input.                           |

| U U         |             |             |                          | AIN2: ADC input channel 2.                                         |

|             |             |             |                          | <b>P1.0:</b> Port 1 bit 0.                                         |

|             |             |             |                          | <b>PWM2:</b> PWM output channel 2.                                 |

| 15          | 7           | 12          | P1.0/PWM2/IC2/SPCLK      | IC2: Input capture channel 2.                                      |

|             |             |             |                          | SPCLK: SPI clock.                                                  |

|             |             | 1           |                          | <b>P1.1:</b> Port 1 bit 1                                          |

|             |             |             |                          | <b>PWM1:</b> PWM output channel 1.                                 |

| 14          | 8           | 11          | P1.1/PWM1/IC1/AIN7/      | IC1: Input capture channel 1.                                      |

|             | 2           |             | CLO                      | AIN7: ADC input channel 7.                                         |

|             |             |             |                          | CLO: System clock output.                                          |

|             |             |             |                          | <b>P1.2:</b> Port 1 bit 2.                                         |

| 13          | 9           | 10          | P1.2/PWM0/IC0            | <b>PWM0:</b> PWM output channel 0.                                 |

# ηυνοτοη

| Pin Number  |             |             | Symbol                           | Multi-Function Description <sup>[1]</sup>                                           |  |

|-------------|-------------|-------------|----------------------------------|-------------------------------------------------------------------------------------|--|

| N76E003AT20 | N76E003AQ20 | N76E003BQ20 | Symbol                           | Multi-Function Description                                                          |  |

|             |             |             |                                  | IC0: Input capture channel 0.                                                       |  |

|             |             |             |                                  | <b>P1.3:</b> Port 1 bit 3.                                                          |  |

| 12          | 11          | 9           | P1.3/SCL/[STADC]                 | SCL: I <sup>2</sup> C clock.                                                        |  |

|             |             |             |                                  | [STADC] <sup>[4]</sup> : External start ADC trigger                                 |  |

|             |             |             |                                  | <b>P1.4:</b> Port 1 bit 4.                                                          |  |

|             | 10          |             |                                  | <b>SDA:</b> I <sup>2</sup> C data.                                                  |  |

| 11          | 10          | 8           | P1.4/SDA/FB/PWM1                 | FB: Fault Brake input.                                                              |  |

|             |             |             |                                  | <b>PWM1:</b> PWM output channel 1.                                                  |  |

|             |             |             |                                  | <b>P1.5:</b> Port 1 bit 5.                                                          |  |

| 10          | <u> </u>    | 7           |                                  | <b>PWM5:</b> PWM output channel 5.                                                  |  |

| 10          | 6           | 7           | P1.5/PWM5/IC7/SS                 | IC7: Input capture channel 7.                                                       |  |

|             |             |             |                                  | <b>SS:</b> SPI slave select input.                                                  |  |

|             |             |             |                                  | <b>P1.6:</b> Port 1 bit 6.                                                          |  |

|             |             |             |                                  | ICPDA: ICP data input or output.                                                    |  |

| 8           | 4           | 5           | P1.6/ICPDA/OCDDA/<br>TXD_1/[SDA] | OCDAT: OCD data input or output.                                                    |  |

|             |             |             |                                  | <b>TXD_1:</b> Serial port 1 transmit data output.                                   |  |

|             |             |             |                                  | [SDA] <sup>[3]</sup> : I <sup>2</sup> C data.                                       |  |

|             |             |             |                                  | <b>P1.7:</b> Port 1 bit 7.                                                          |  |

| 6           | 2           | 3           | P1.7/INT1/AIN0                   | <b>INT1:</b> External interrupt 1 input.                                            |  |

|             |             |             |                                  | AIN0: ADC input channel 0.                                                          |  |

|             |             |             |                                  | <b>P2.0:</b> Port 2 bit 0 input pin available when RPD                              |  |

|             |             |             |                                  | (CONFIG0.2) is programmed as 0.                                                     |  |

| 4           | 18          | 1           | P2.0/RST                         | <b>RST</b> : RST pin is a Schmitt trigger input pin for                             |  |

| 4           | 18          | 1           | P2.0/RS1                         | hardware device reset. A low on this pin resets                                     |  |

|             |             |             |                                  | the device. RST pin has an internal pull-up                                         |  |

|             |             |             |                                  | resistor allowing power-on reset by simply connecting an external capacitor to GND. |  |

|             |             |             |                                  | <b>P3.0:</b> Port 3 bit 0 available when the internal                               |  |

|             |             |             |                                  | oscillator is used as the system clock.                                             |  |

| _           |             |             |                                  | <b>INTO:</b> External interrupt 0 input.                                            |  |

| 5           | 17          | 12          | P3.0/INT0/OSCIN/AIN1             | XIN: If the ECLK mode is enabled, XIN is the                                        |  |

|             |             |             |                                  | external clock input pin.                                                           |  |

|             |             |             |                                  | AIN1: ADC input channel 1.                                                          |  |

[1] All I/O pins can be configured as a interrupt pin. This feature is not listed in multi-function description. See <u>Section 16.</u> "Pin Interrupt".

[2] TXD and RXD pins of UART0 are software exchangeable by UART0PX (AUXR1.2).

[3] [I2C] alternate function remapping option. I2C pins is software switched by I2CPX (I2CON.0).

[4] [STADC] alternate function remapping option. STADC pin is software switched by STADCPX(ADCCON1.6).

[5] PIOx register decides which pins are PWM or GPIO.

### 5. MEMORY ORGANIZATION

A standard 80C51 based microcontroller divides the memory into two different sections, Program Memory and Data Memory. The Program Memory is used to store the instruction codes, whereas the Data Memory is used to store data or variations during the program execution.

The Data Memory occupies a separate address space from Program Memory. In N76E003, there are 256 Bytes of internal scratch-pad RAM. For many applications those need more internal RAM, the N76E003 provides another on-chip 768 Bytes of RAM, which is called XRAM, accessed by MOVX instruction.

The whole embedded flash, functioning as Program Memory, is divided into three blocks: Application ROM (APROM) normally for User Code, Loader ROM (LDROM) normally for Boot Code, and CONFIG bytes for hardware initialization. Actually, APROM and LDROM function in the same way but have different size. Each block is accumulated page by page and the page size is 128 Bytes. The flash control unit supports Erase, Program, and Read modes. The external writer tools though specific I/O pins, In-Application-Programming (IAP), or In-System-Programming (ISP) can both perform these modes.

### 5.1 Program Memory

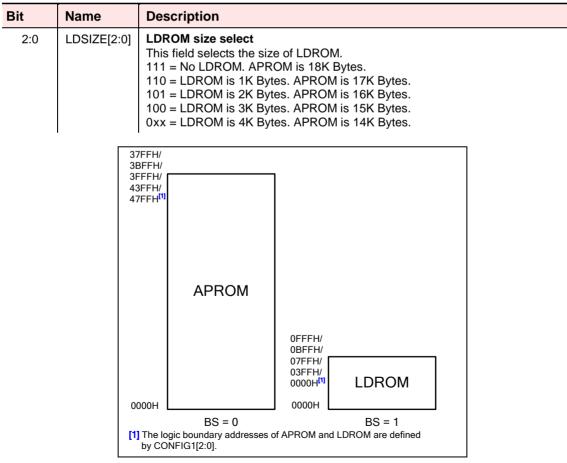

The Program Memory stores the program codes to execute as shown in <u>Figure 5.1</u>. After any reset, the CPU begins execution from location 0000H.

To service the interrupts, the interrupt service locations (called interrupt vectors) should be located in the Program Memory. Each interrupt is assigned with a fixed location in the Program Memory. The interrupt causes the CPU to jump to that location with where it commences execution of the interrupt service routine (ISR). External Interrupt 0, for example, is assigned to location 0003H. If External Interrupt 0 is going to be used, its service routine should begin at location 0003H. If the interrupt is not going to be used, its service location is available as general purpose Program Memory.

The interrupt service locations are spaced at an interval of eight Bytes: 0003H for External Interrupt 0, 000BH for Timer 0, 0013H for External Interrupt 1, 001BH for Timer 1, etc. If an interrupt service routine is short enough (as is often the case in control applications), it can reside entirely within the 8-Byte interval. However longer service routines should use a JMP instruction to skip over subsequent interrupt locations if other interrupts are in use.

The N76E003 provides two internal Program Memory blocks APROM and LDROM. Although they both behave the same as the standard 8051 Program Memory, they play different rules according to their ROM size. The

APROM on N76E003 can be up to 18K Bytes. User Code is normally put inside. CPU fetches instructions here for execution. The MOVC instruction can also read this region.

The other individual Program Memory block is called LDROM. The normal function of LDROM is to store the Boot Code for ISP. It can update APROM space and CONFIG bytes. The code in APROM can also re-program LDROM. For ISP details and configuration bit setting related with APROM and LDROM, see <u>Section 21.4 "In-System-Programming (ISP)" on page 225</u>. Note that APROM and LDROM are hardware individual blocks, consequently if CPU re-boots from LDROM, CPU will automatically re-vector Program Counter 0000H to the LDROM start address. Therefore, CPU accounts the LDROM as an independent Program Memory and all interrupt vectors are independent from APROM.

#### CONFIG1

| 7 | 6 | 5 | 4 | 3 | 2 | 1           | 0 |

|---|---|---|---|---|---|-------------|---|

| - | - | - | - | - |   | LDSIZE[2:0] |   |

| - | - | - | - | - |   | R/W         |   |

Factory default value: 1111 1111b

# ηυνοτοη

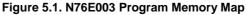

# 5.2 Data Memory

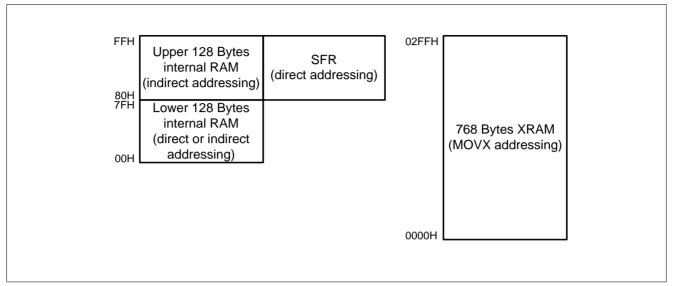

Figure 5.2 shows the internal Data Memory spaces available on N76E003. Internal Data Memory occupies a separate address space from Program Memory. The internal Data Memory can be divided into three blocks. They are the lower 128 Bytes of RAM, the upper 128 Bytes of RAM, and the 128 Bytes of SFR space. Internal Data Memory addresses are always 8-bit wide, which implies an address space of only 256 Bytes. Direct addressing higher than 7FH will access the special function registers (SFRs) space and indirect addressing higher than 7FH will access the upper 128 Bytes of RAM. Although the SFR space and the upper 128 Bytes of RAM share the same logic address, 80H through FFH, actually they are physically separate entities. Direct addressing to distinguish with the higher 128 Bytes of RAM can only access these SFRs. Sixteen addresses in SFR space are either byte-addressable or bit-addressable. The bit-addressable SFRs are those whose addresses end in 0H or 8H.

The lower 128 Bytes of internal RAM are present in all 80C51 devices. The lowest 32 Bytes as general purpose registers are grouped into 4 banks of 8 registers. Program instructions call these registers as R0 to R7. Two bits RS0 and RS1 in the Program Status Word (PSW[3:4]) select which Register Bank is used. It benefits more efficiency of code space, since register instructions are shorter than instructions that use direct addressing. The next 16 Bytes above the general purpose registers (byte-address 20H through 2FH) form a block of bit-addressable memory space (bit-address 00H through 7FH). The 80C51 instruction set includes a wide selection of single-bit instructions, and the 128 bits in this area can be directly addressed by these instructions. The bit addresses in this area are 00H through 7FH.

Either direct or indirect addressing can access the lower 128 Bytes space. But the upper 128 Bytes can only be accessed by indirect addressing.

Another application implemented with the whole block of internal 256 Bytes RAM is used for the stack. This area is selected by the Stack Pointer (SP), which stores the address of the top of the stack. Whenever a JMP, CALL or interrupt is invoked, the return address is placed on the stack. There is no restriction as to where the stack can begin in the RAM. By default however, the Stack Pointer contains 07H at reset. User can then change this to any value desired. The SP will point to the last used value. Therefore, the SP will be incremented and then address saved onto the stack. Conversely, while popping from the stack the contents will be read first, and then the SP is decreased.

# nuvoTon

Figure 5.2. Data Memory Map

Figure 5.3. Internal 256 Bytes RAM Addressing

### 5.3 On-Chip XRAM

The N76E003 provides additional on-chip 768 bytes auxiliary RAM called XRAM to enlarge the RAM space. It occupies the address space from 00H through 2FFH. The 768 bytes of XRAM are indirectly accessed by move external instruction MOVX @DPTR or MOVX @Ri. (See the demo code below.) Note that the stack pointer cannot be located in any part of XRAM.

XRAM demo code:

| MOV<br>MOV  | RO,#23H<br>A,#5AH | ;write #5AH to XRAM with address @23H   |

|-------------|-------------------|-----------------------------------------|

| MOVX<br>MOV | @R0,A<br>R1,#23H  | ;read from XRAM with address @23H       |

| MOV         | A, @R1            | , IEad IIOM ARAM WICH address 025h      |

| MOVX        | DPTR, #0023H      | ;write #5BH to XRAM with address @0023H |

| MOV         | A,#5BH            | wille gobi to main with dadiess goozon  |

| MOVX        | @DPTR,A           |                                         |

| MOV         | DPTR, #0023H      | ;read from XRAM with address @0023H     |

| MOVX        | A, @DPTR          |                                         |

### 5.4 Non-Volatile Data Storage

By applying IAP, any page of APROM or LDROM can be used as non-volatile data storage. For IAP details, please see <u>Section 21. "In-Application-Programming (IAP)" on page 219</u>.

# 6. SPECIAL FUNCTION REGISTER (SFR)

The N76E003 uses Special Function Registers (SFRs) to control and monitor peripherals and their modes. The SFRs reside in the register locations 80 to FFH and are accessed by direct addressing only. SFRs those end their addresses as 0H or 8H are bit-addressable. It is very useful in cases where user would like to modify a particular bit directly without changing other bits via bit-field instructions. All other SFRs are byte-addressable only. The N76E003 contains all the SFRs presenting in the standard 8051. However some additional SFRs are built in. Therefore, some of unused bytes in the original 8051 have been given new functions. The SFRs are listed below.

To accommodate more than 128 SFRs in the 0x80 to 0xFF address space, SFR paging has been implemented. By default, all SFR accesses target SFR page 0. During device initialization, some SFRs located on SFR page 1 may need to be accessed. The register SFRS is used to switch SFR addressing page. Note that this register has TA write protection. Most of SFRs are available on both SFR page 0 and 1.

#### SFRS – SFR Page Selection (TA protected)

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0       |

|---|---|---|---|---|---|---|---------|

| - | - | - | - | - | - | - | SFRPAGE |

| - | - | - | - | - | - | - | R/W     |

|   |   |   |   |   |   |   |         |

Address: 91H

Reset value: 0000 0000b

| Bit | Name    | Description                                                                                   |

|-----|---------|-----------------------------------------------------------------------------------------------|

| 0   | SFRPAGE | SFR page select<br>0 = Instructions access SFR page 0.<br>1 = Instructions access SFR page 1. |

#### Switch SFR page demo code:

| MOV<br>MOV<br>ORL | TA,#0AAH<br>TA,#55H<br>SFRS,#01H  | ;switch t | to SFR | page | 1 |

|-------------------|-----------------------------------|-----------|--------|------|---|

| MOV<br>MOV<br>ANL | TA,#0AAH<br>TA,#55H<br>SFRS,#0FEH | ;switch t | to SFR | page | 0 |

# nuvoTon

#### Table 6-1. SFR Memory Map

| SFR<br>Page | Addr       | 0/8     | 1/9         | 2/A          | 3/B           | 4/C            | 5/D          | 6/E            | 7/F            |

|-------------|------------|---------|-------------|--------------|---------------|----------------|--------------|----------------|----------------|

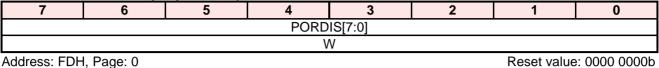

| 0<br>1      | F8         | SCON_1  | PDTEN       | PDTCNT       | PMEN          | PMD            | PORDIS<br>-  | EIP1<br>-      | EIPH1<br>-     |

| 0<br>1      | F0         | В       | CAPCON3     | CAPCON4      | SPCR<br>SPCR2 | SPSR           | SPDR<br>-    | AINDIDS        | EIPH<br>-      |

| 0<br>1      | E8         | ADCCON0 | PICON       | PINEN        | PIPEN         | PIF            | C2L          | C2H            | EIP<br>-       |

| 0<br>1      | E0         | ACC     | ADCCON1     | ADCCON2      | ADCDLY        | COL            | СОН          | C1L            | C1H            |

| 0<br>1      | D8         | PWMCON0 | PWMPL       | PWM0L        | PWM1L         | PWM2L          | PWM3L        | PIOCON0        | PWMCON1        |

| 0<br>1      | D0         | PSW     | PWMPH       | PWM0H        | PWM1H         | PWM2H          | PWM3H        | PNP            | FBD            |

| 0<br>1      | C8         | T2CON   | T2MOD       | RCMP2L       | RCMP2H        | TL2<br>PWM4L   | TH2<br>PWM5L | ADCMPL         | ADCMPH         |

| 0<br>1      | C0         | I2CON   | I2ADDR      | ADCRL        | ADCRH         | T3CON<br>PWM4H | RL3<br>PWM5H | RH3<br>PIOCON1 | ТА             |

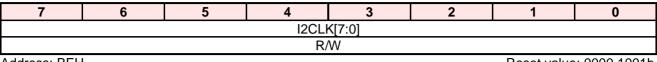

| 0<br>1      | B8         | IP      | SADEN       | SADEN_1      | SADDR_1       | I2DAT          | I2STAT       | I2CLK          | I2TOC          |

| 0<br>1      | В0         | P3      | P0M1<br>P0S | P0M2<br>P0SR | P1M1<br>P1S   | P1M2<br>P1SR   | P2S          | -              | IPH<br>PWMINTC |

| 0<br>1      | <b>A</b> 8 | IE      | SADDR       | WDCON        | BODCON1       | P3M1<br>P3S    | P3M2<br>P3SR | IAPFD          | IAPCN          |

| 0<br>1      | A0         | P2      | -           | AUXR1        | BODCON0       | IAPTRG         | IAPUEN       | IAPAL          | IAPAH          |

| 0<br>1      | 98         | SCON    | SBUF        | SBUF_1       | EIE           | EIE1           | -            | -              | CHPCON         |

| 0<br>1      | 90         | P1      | SFRS        | CAPCON0      | CAPCON1       | CAPCON2        | CKDIV        | CKSWT          | CKEN           |

| 0<br>1      | 88         | TCON    | TMOD        | TLO          | TL1           | TH0            | TH1          | CKCON          | WKCON          |

| 0<br>1      | 80         | P0      | SP          | DPL          | DPH           | RCTRIM0        | RCTRIM1      | RWK            | PCON           |

Unoccupied addresses in the SFR space marked in "-" are reserved for future use. Accessing these areas will have an indeterminate effect and should be avoided.

nuvoTon

| Symbol                | Definition                                     | Address<br>/(Page) | MSB            |                 |                 |                       |                 |                 |                | LSB <sup>[1]</sup> | Reset | Value <sup>[2]</sup> |

|-----------------------|------------------------------------------------|--------------------|----------------|-----------------|-----------------|-----------------------|-----------------|-----------------|----------------|--------------------|-------|----------------------|

| EIPH1                 | Extensive interrupt<br>priority high 1         | FFH/(0)            | -              | -               | -               | -                     | -               | PWKTH           | PT3H           | PSH_1              | 0000  | 0000                 |

| EIP1                  | Extensive interrupt<br>priority 1              | FEH/(0)            | -              | -               | -               | -                     | -               | PWKT            | PT3            | PS_1               | 0000  | 0000                 |

| PMD                   | PWM mask data                                  | FCH                | -              | -               | PMD5            | PMD4                  | PMD3            | PMD2            | PMD1           | PMD0               | 0000  | 00001                |

| PMEN                  | PWM mask enable                                | FBH                | -              | -               | PMEN5           | PMEN4                 | PMEN3           | PMEN2           | PMEN1          | PMEN0              | 0000  | 0000                 |

| PDTCNT <sup>[4]</sup> | PWM dead-time counter                          | FAH                |                |                 |                 | PDTCN                 | T[7:0]          |                 |                |                    | 0000  | 00006                |

| PDTEN <sup>[4]</sup>  | PWM dead-time enable                           | F9H                |                | _               | -               | PDTCNT.8              |                 | PDT45EN         | PDT23EN        | PDT01EN            | 0000  | 0000k                |

|                       |                                                | 1.011              | (FF)           |                 |                 |                       |                 |                 |                |                    |       |                      |

| SCON_1                | Serial port 1 control                          | F8H                | SM0_1/<br>FE_1 | (FE)<br>SM1_1   | (FD)<br>SM2_1   | (FC)<br>REN_1         | (FB)<br>TB8_1   | (FA)<br>RB8_1   | (F9)<br>TI_1   | (F8)<br>RI_1       | 0000  | 0000                 |

| EIPH                  | Extensive interrupt<br>priority high           | F7H                | PT2H           | PSPIH           | PFBH            | PWDTH                 | PPWMH           | PCAPH           | PPIH           | PI2CH              | 0000  | 0000                 |

| AINDIDS               | ADC channel digital<br>input disable           | F6H                | P11DIDS        | P03DIDS         | P04DIDS         | P05DIDS               | P06DIDS         | P07DIDS         | P30DIDS        | P17DIDS            | 0000  | 0000                 |

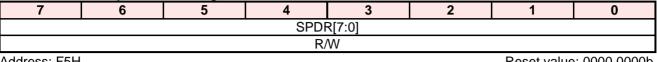

| SPDR                  | SPI data                                       | F5H(0)             |                |                 |                 | SPDF                  | R[7:0]          |                 |                |                    | 0000  | 0000k                |

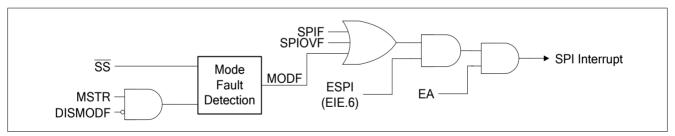

| SPSR                  | SPI status                                     | F4H                | SPIF           | WCOL            | SPIOVF          | MODF                  | DISMODF         | TXBUF           | -              | -                  | 0000  |                      |

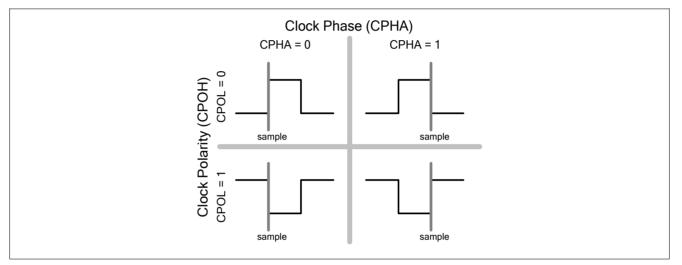

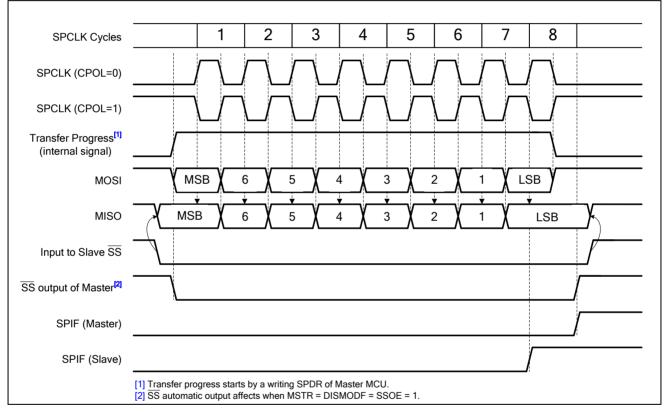

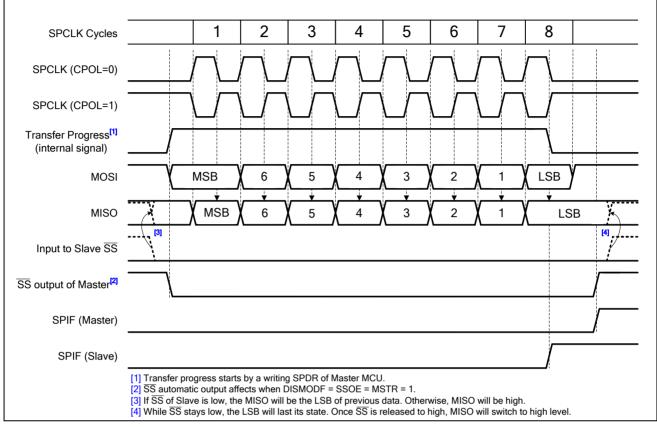

| SPCR                  | SPI control                                    | F3H(0)             | SSOE           | SPIEN           | LSBFE           | MSTR                  | CPOL            | CPHA            |                | R[1:0]             |       | 0000b                |

| SPCR2                 | SPI control 2                                  | F3H(1)             | -              | -               | -               | -                     | -               | -               |                | S[1:0]             | 0000  |                      |

| CAPCON4               | Input capture control 4                        | F2H                | -              | -               | -               | -                     | CAP23           | CAP22           | CAP21          | CAP20              |       | 0000k                |

| CAPCON3               | Input capture control 3                        | F1H                | CAP13          | CAP12           | CAP11           | CAP10                 | CAP03           | CAP02           | CAP01          | CAP00              | 0000  | 0000                 |

| В                     | B register                                     | F0H                | (F7)<br>B.7    | (F6)<br>B.6     | (F5)<br>B.5     | (F4)<br>B.4           | (F3)<br>B.3     | (F2)<br>B.2     | (F1)<br>B.1    | (F0)<br>B.0        | 0000  | 0000b                |

| EIP                   | Extensive interrupt<br>priority                | EFH                | PT2            | PSPI            | PFB             | PWDT                  | PPWM            | PCAP            | PPI            | PI2C               | 0000  | 00006                |

| C2H                   | Input capture 2 high byte                      | EEH                |                |                 |                 | C2H                   | [7:0]           |                 |                |                    | 0000  |                      |

| C2L                   | Input capture 2 low byte                       | EDH                |                |                 | -               | C2L[                  |                 |                 | •              |                    | 0000  |                      |

| PIF                   | Pin interrupt flag                             | ECH                | PIF7           | PIF6            | PIF5            | PIF4                  | PIF3            | PIF2            | PIF1           | PIF0               | 0000  | 0000b                |

| PIPEN                 | Pin interrupt high<br>level/rising edge enable | EBH                | PIPEN7         | PIPEN6          | PIPEN5          | PIPEN4                | PIPEN3          | PIPEN2          | PIPEN1         | PIPEN0             | 0000  | 0000b                |

| PINEN                 | Pin interrupt low<br>level/falling edge enable | EAH                | PINEN7         | PINEN6          | PINEN5          | PINEN4                | PINEN3          | PINEN2          | PINEN1         | PINEN0             | 0000  | 0000b                |

| PICON                 | Pin interrupt control                          | E9H                | PIT67          | PINENO<br>PIT45 | PINEINS<br>PIT3 | PINEIN4<br>PIT2       | PINEIN3<br>PIT1 | PINEINZ<br>PIT0 |                |                    | 0000  | 00006                |

| ADCCON0               | ADC control 0                                  | E8H                | (EF)<br>ADCF   | (EE)<br>ADCS    | (ED)            | (EC)<br>ETGSEL0       | (EB)            | (EA)<br>ADCHS2  | (E9)<br>ADCHS1 | (E8)<br>ADCHS0     |       | 0000t                |

| C1H                   | Input capture 1 high byte                      | E7H                |                |                 |                 | C1H                   |                 |                 |                |                    | 0000  | 0000k                |

| C1L                   | Input capture 1 low byte                       | E6H                |                |                 |                 | C1L                   |                 |                 |                |                    | 0000  | 0000b                |

| C0H                   | Input capture 0 high byte                      | E5H                |                |                 |                 | C0H                   | [7:0]           |                 |                |                    | 0000  | 0000b                |

| COL                   | Input capture 0 low byte                       | E4H                |                |                 |                 | C0L[                  | 7:0]            |                 |                |                    | 0000  | 0000b                |

| ADCDLY                | ADC trigger delay                              | E3H                |                |                 |                 | ADCDL                 | Y[7:0]          |                 |                |                    | 0000  |                      |

| ADCCON2               | ADC control 2                                  | E2H                | ADFBEN         | ADCMPOP         | ADCMPEN         | ADCMPO                | -               | -               | -              | ADCDLY.8           | 0000  | 0000b                |

| ADCCON1               | ADC control 1                                  | E1H                | -              | STADCPX         | -               | -                     |                 | YP[1:0]         | ADCEX          | ADCEN              | 0000  | 0000b                |

| ACC                   | Accumulator                                    | E0H                | (E7)<br>ACC.7  | (E6)<br>ACC.6   | (E5)<br>ACC.5   | (E4)<br>ACC.4         | (E3)<br>ACC.3   | (E2)<br>ACC.2   | (E1)<br>ACC.1  | (E0)<br>ACC.0      | 0000  | 0000b                |

| PWMCON1               | PWM control 1                                  | DFH                | PWMM           | IOD[1:0]        | GP              | PWMTYP                | FBINEN          |                 | PWMDIV[2:0     |                    | 0000  |                      |

| PIOCON0               | PWM I/O switch 0                               | DEH                | -              | -               | PIO05           | PIO04                 | PIO03           | PIO02           | PIO01          | PIO00              | 0000  | 0000k                |

| PWM3L                 | PWM3 duty low byte                             | DDH                |                |                 |                 | PWM                   |                 |                 |                |                    | 0000  | 0000b                |

| PWM2L                 | PWM2 duty low byte                             | DCH                |                |                 |                 | PWM                   |                 |                 |                |                    | 0000  |                      |

| PWM1L                 | PWM1 duty low byte                             | DBH                |                |                 |                 | PWM <sup>2</sup>      |                 |                 |                |                    |       | 00006                |

| PWMOL                 | PWM0 duty low byte                             | DAH                |                |                 |                 | PWM                   |                 |                 |                |                    |       | 0000b                |

| PWMPL<br>PWMCON0      | PWM period low byte<br>PWM control 0           | D9H<br>D8H         | (DF)<br>PWMRUN | (DE)<br>LOAD    | (DD)<br>PWMF    | PWM<br>(DC)<br>CLRPWM | (DB)            | (DA)            | (D9)           | (D8)               |       | 0000b                |

| FBD                   | Brake data                                     | D6H<br>D7H         | FBF            | FBINLS          | FBD5            | FBD4                  | FBD3            | -<br>FBD2       | -<br>FBD1      | -<br>FBD0          | 0000  | 0000b                |

| PNP                   | PWM negative polarity                          | D6H                | -              | -               | PNP5            | PNP4                  | PNP3            | PNP2            | PNP1           | PNP0               |       | 0000t                |

| PWM3H                 | PWM3 duty high byte                            | D5H                |                |                 | 1110            | PWM3                  |                 | 1 141 2         | 1              | 11410              |       | 00000                |

| PWM2H                 | PWM2 duty high byte                            | D4H                |                |                 |                 | PWM2                  |                 |                 |                |                    |       | 0000k                |

| PWM1H                 | PWM1 duty high byte                            | D3H                |                |                 |                 | PWM1                  |                 |                 |                |                    |       | 00006                |

| PWM0H                 | PWM0 duty high byte                            | D2H                |                |                 |                 | PWM0                  |                 |                 |                |                    |       | 00006                |

| PWMPH                 | PWM period high byte                           | D1H                |                |                 |                 | PWMF                  |                 |                 |                |                    | 0000  |                      |

| PSW                   | Program status word                            | D0H                | (D7)<br>CY     | (D6)<br>AC      | (D5)<br>F0      | (D4)<br>RS1           | (D3)<br>RS0     | (D2)<br>OV      | (D1)<br>-      | (D0)<br>P          |       | 0000b                |

| ADCMPH                | ADC compare high byte                          | CFH                |                |                 |                 | ADCM                  | P[11:4]         |                 |                |                    |       | 0000b                |

| ADCMPL                | ADC compare low byte                           | CEH                | -              | -               | -               | -                     |                 | ADCN            | /IP[3:0]       |                    |       | 0000b                |

| PWM5L                 | PWM5 duty low byte                             | CDH(1)             |                |                 |                 | PWM                   | 5[7:0]          |                 |                |                    | 0000  | 0000b                |

Dec. 13, 2017

| Symbol                 | Definition                                   | Address<br>/(Page) | MSB         |               |              |             |                |             |             | LSB <sup>[1]</sup> | Reset                                          | Value <sup>[2]</sup>    |

|------------------------|----------------------------------------------|--------------------|-------------|---------------|--------------|-------------|----------------|-------------|-------------|--------------------|------------------------------------------------|-------------------------|

| TH2                    | Timer 2 high byte                            | CDH(0)             |             |               |              | TH2[        | 7:0]           |             |             |                    | 0000                                           | 0000b                   |

| PWM4L                  | PWM4 duty low byte                           | CCH(1)             |             |               |              | PWM4        | 4[7:0]         |             |             |                    | 0000                                           | 0000b                   |

| TL2                    | Timer 2 low byte                             | CCH(0)             |             |               |              | TL2[        | 7:0]           |             |             |                    | 0000                                           | 0000b                   |

| RCMP2H                 | Timer 2 compare high byte                    | СВН                |             |               |              | RCMP2       | 2H[7:0]        |             |             |                    | 0000                                           | 0000b                   |

| RCMP2L                 | Timer 2 compare low byte                     | CAH(0)             |             |               |              | RCMP2       | 2L[7:0]        |             |             |                    | 0000                                           | 0000b                   |

| T2MOD                  | Timer 2 mode                                 | C9H                | LDEN        |               | T2DIV[2:0]   |             | CAPCR          | CMPCR       | LDT         | S[1:0]             | 0000                                           | 0000b                   |

| T2CON                  | Timer 2 control                              | C8H                | (CF)<br>TF2 | (CE)          | (CD)         | (CC)<br>-   | (CB)<br>-      | (CA)<br>TR2 | (C9)<br>-   | (C8)<br>CM/RL2     | 0000                                           | 0000b                   |

| ТА                     | Timed access protection                      | C7H                |             |               | 1            | TA          | 7:0]           |             |             |                    | 0000                                           | 0000b                   |

| PIOCON1                | PWM I/O switch 1                             | C6H(1)             | -           | -             | PIO15        | - 1         | PIO13          | PIO12       | PIO11       | -                  | 0000                                           | 0000b                   |

| RH3                    | Timer 3 reload high byte                     | C6H(0)             |             |               |              | RH3         | 7:0]           |             |             |                    | 0000                                           | 0000b                   |

| PWM5H                  | PWM5 duty high byte                          | C5H(1)             |             |               |              | PWM5        | [15:8]         |             |             |                    | 0000                                           | 0000b                   |

| RL3                    | Timer 3 reload low byte                      | C5H(0)             |             |               |              | RL3[        | 7:0]           |             |             |                    | 0000                                           | 0000b                   |

| PWM4H                  | PWM4 duty high byte                          | C4H(1)             |             |               |              | PWM4        |                |             |             |                    | 0000                                           | 0000b                   |

| T3CON                  | Timer 3 control                              | C4H(0)             | SMOD_1      | SMOD0_1       | BRCK         | TF3         | TR3            |             | T3PS[2:0]   |                    | 0000                                           | 0000b                   |

| ADCRH                  | ADC result high byte                         | C3H                |             |               | 1            | ADCR        | [11:4]         |             |             |                    | 0000                                           | 0000b                   |

| ADCRL                  | ADC result low byte                          | C2H                | -           | -             | -            | -           |                | ADCI        | R[3:0]      |                    | 0000                                           | 0000b                   |

| I2ADDR                 | I <sup>2</sup> C own slave address           | C1H                |             |               |              | 2ADDR[7:1]  |                |             | • •         | GC                 | 0000                                           | 0000b                   |

| I2CON                  | I <sup>2</sup> C control                     | COH                | (C7)        | (C6)<br>I2CEN | (C4)<br>STA  | (C4)<br>STO | (C3)<br>SI     | (C2)<br>AA  | (C1)        | (C0)<br>I2CPX      |                                                | 0000b                   |

| I2TOC                  | I <sup>2</sup> C time-out counter            | BFH                |             | IZOEN         | -            | 010         | 01             | 12TOCEN     | DIV         | I2TOF              | 0000                                           | 0000b                   |

| I2TOC<br>I2CLK         |                                              | BEH                | -           | _             | _            | I2CLK       | -<br>([7:0]    | 12100LIN    | DIV         | 12101              |                                                | 1001b                   |

| -                      | 2                                            |                    |             |               |              | IZULN       | [ <i>1</i> :0] |             | <u>^</u>    |                    |                                                |                         |

| I2STAT                 | I <sup>2</sup> C status                      | BDH                |             | I.            | 2STAT[7:3]   |             |                | 0           | 0           | 0                  | 1111                                           | 1000b                   |

| I2DAT                  | I <sup>2</sup> C data                        | BCH                |             |               |              | I2DAT       |                |             |             |                    |                                                | 0000b                   |

| SADDR_1                | Slave 1 address                              | BBH                |             |               |              | SADDR       | _1[7:0]        |             |             |                    |                                                | 0000b                   |

| SADEN_1                | Slave 1 address mask                         | BAH                |             |               |              | SADEN       |                |             |             |                    | 0000                                           |                         |

| SADEN                  | Slave 0 address mask                         | B9H                |             |               |              |             |                |             |             | 0000               | 0000b                                          |                         |

| IP                     | Interrupt priority                           | B8H                | (BF)<br>-   | (BE)<br>PADC  | (BD)<br>PBOD | (BC)<br>PS  | (BB)<br>PT1    | (BA)<br>PX1 | (B9)<br>PT0 | (B8)<br>PX0        | 0000                                           | 0000b                   |

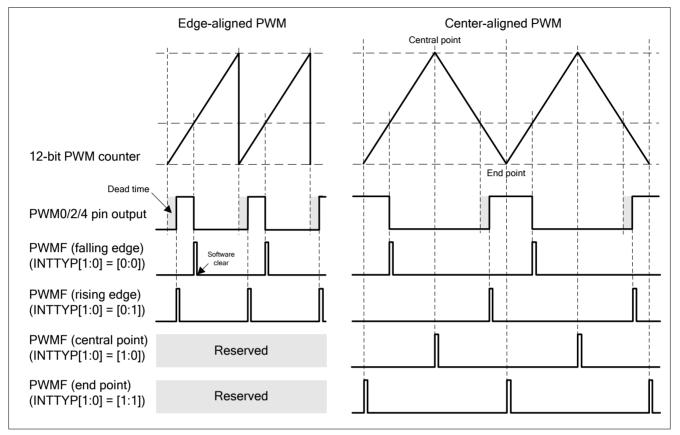

| PWMINTC                | PWM Interrupt Control                        | B7H(1)             | -           | -             | INTTYP1      | INTTYP0     | -              | INTSEL2     | INTSEL1     | INTSEL0            | 0000                                           | 0000b                   |

| IPH                    | Interrupt priority high                      | B7H(0)             | -           | PADCH         | PBODH        | PSH         | PT1H           | PX1H        | PT0H        | PX0H               | 0000                                           | 0000b                   |

| P2S                    | P20 Setting and<br>Timer0/1 Output Enable    | B5H                | P20UP       | -             | -            | -           | T1OE           | T0OE        | -           | P2S.0              | 0000                                           | 0000b                   |

| P1SR                   | P1 slew rate                                 | B4H/(1)            | P1SR.7      | P1SR.6        | P1SR.5       | P1SR.4      | P1SR.3         | P1SR.2      | P1SR.1      | P1SR.0             | 0000                                           | 0000b                   |

| P1M2                   | P1 mode select 2                             | B4H/(0)            | P1M2.7      | P1M2.6        | P1M2.5       | P1M2.4      | P1M2.3         | P1M2.2      | P1M2.1      | P1M2.0             | 0000                                           | 0000b                   |

| P1S                    | P1 Schmitt trigger input                     | B3H/(1)            | P1S.7       | P1S.6         | P1S.5        | P1S.4       | P1S.3          | P1S.2       | P1S.1       | P1S.0              | 0000                                           | 0000b                   |

| P1M1                   | P1 mode select 1                             | B3H/(0)            | P1M1.7      | P1M1.6        | P1M1.5       | P1M1.4      | P1M1.3         | P1M1.2      | P1M1.1      | P1M1.0             | 1111                                           | 1111b                   |

| P0SR                   | P0 slew rate                                 | B2H/(1)            | P0SR.7      | P0SR.6        | P0SR.5       | P0SR.4      | P0SR.3         | P0SR.2      | P0SR.1      | P0SR.0             | 0000                                           | 0000b                   |

| P0M2                   | P0 mode select 2                             | B2H/(0)            | P0M2.7      | P0M2.6        | P0M2.5       | P0M2.4      | P0M2.3         | P0M2.2      | P0M2.1      | P0M2.0             | 0000                                           | 0000b                   |

| P0S                    | P0 Schmitt trigger input                     | B1H/(1)            | P0S.7       | P0S.6         | P0S.5        | P0S.4       | P0S.3          | P0S.2       | P0S.1       | P0S.0              | 0000                                           | 0000b                   |

| P0M1                   | P0 mode select 1                             | B1H/(0)            | P0M1.7      | P0M1.6        | P0M1.5       | P0M1.4      | P0M1.3         | P0M1.2      | P0M1.1      | P0M1.0             | 1111                                           | 1111b                   |

| P3                     | Port 3                                       | B0H                | (B7)<br>0   | (B6)<br>0     | (B5)<br>0    | (B4)<br>0   | (B3)<br>0      | (B2)<br>0   | (B1)<br>0   | (B0)<br>P3.0       | Input,                                         | 0001b                   |

|                        |                                              |                    |             |               |              |             |                |             |             |                    |                                                | 000Xb <sup>[3]</sup>    |

| IAPCN                  | IAP control                                  | AFH                | IAPA        | [17:16]       | FOEN         | FCEN        | 17.01          | FCTR        | L[3:0]      |                    |                                                | 0000b                   |

| IAPFD                  | IAP flash data                               | AEH                |             |               |              | IAPFD       | זע/:0]         |             |             | DAGE               |                                                | 0000b                   |

| P3SR                   | P3 slew rate                                 | ADH/(1)            | -           | -             | -            | -           | -              | -           | -           | P3SR.0             |                                                | 0000b                   |

| P3M2                   | P3 mode select 2                             | ADH/(0)            | -           | -             | -            | -           | -              | -           | -           | P3M2.0             |                                                | 0000b                   |

| P3S<br>P3M1            | P3 Schmitt trigger input<br>P3 mode select 1 | ACH/(1)            | -           | -             | -            | -           | -              | -           | -           | P3S.0<br>P3M1.0    |                                                | 0000b                   |

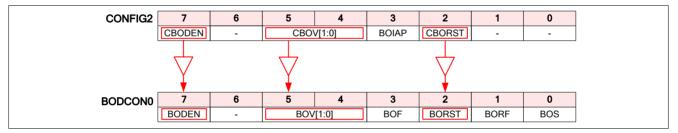

| BODCON1 <sup>[4]</sup> | Brown-out detection<br>control 1             | ACH/(0)<br>ABH     | -           | -             | -            | -           | -              | -<br>LPBO   | -<br>D[1:0] | BODFLT             | POR,                                           | 0001b<br>0001b          |

| WDCON <sup>[4]</sup>   | Watchdog Timer control                       | AAH                | WDTR        | WDCLR         | WDTF         | WIDPD       | WDTRF          |             | WDPS[2:0]   |                    | 0000<br>POR,<br>0000<br>WDT,<br>0000<br>Others | 0UUUb<br>0111b<br>1UUUb |

| Symbol                 | Definition                                    | Address<br>/(Page) | MSB                  |              |              |                     |                    |                      |                   | LSB <sup>[1]</sup> | Reset                                                         | Value <sup>[2]</sup>                    |

|------------------------|-----------------------------------------------|--------------------|----------------------|--------------|--------------|---------------------|--------------------|----------------------|-------------------|--------------------|---------------------------------------------------------------|-----------------------------------------|

| SADDR                  | Slave 0 address                               | A9H                |                      |              |              | SADD                | R[7:0]             |                      |                   |                    | 0000                                                          | 0000b                                   |

| IE                     | Interrupt enable                              | A8H                | (AF)                 | (AE)         | (AD)         | (AC)                | (AB)               | (AA)                 | (A9)              | (A8)               | 0000                                                          | 0000b                                   |

|                        |                                               |                    | EA                   | EADC         | EBOD         | ES                  | ET1                | EX1                  | ET0               | EX0                |                                                               |                                         |

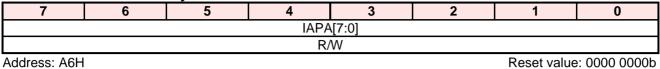

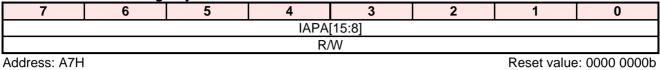

| IAPAH<br>IAPAL         | IAP address high byte<br>IAP address low byte | A7H<br>A6H         |                      |              |              | IAPA[<br>IAPA       |                    |                      |                   |                    |                                                               | 0000b<br>0000b                          |

|                        | IAP update enable                             | A5H                | -                    | -            | -            |                     | [7.0]<br>-         | CFUEN                | LDUEN             | APUEN              | 00000                                                         |                                         |