#### NAU88L21 Ultra-Low Power Audio CODEC Ground-Referenced Headphone Amplifier

#### **GENERAL DESCRIPTION**

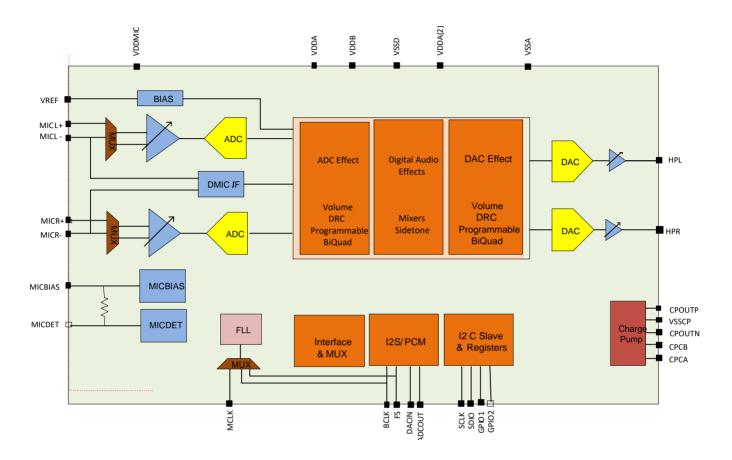

The NAU88L21 is an ultra-low power high performance audio codec that supports both analog and digital audio functions. It includes one I2S/PCM interface, one digital microphone interface, one digital mixer, two high quality DACs and ADC's, and one stereo class G headphone amplifier. The advanced on-chip signal processing engine that includes dynamic range compressor (DRC), programmable biquad filter, as well as an integrated frequency locked loop (FLL) to support various input clocks.

#### FEATURES

- DAC: 105dB SNR, (A-weighted) @ 0dB gain, 1.8V and -88dB THD @ 20mW and RL= 32Ω, DAC playback to headphone output mode

- ADC: 103dB SNR (A-weighted) @ 0dB MIC gain, 1.8V, Fs = 48kHz and -93dB THD, 1.8V, MIC gain 0dB, OSR 256x

- 1 Digital I2S/PCM I/O port

- Two mono differential or one stereo differential analog microphone inputs, two single-ended microphone inputs or one stereo digital microphone input

- Cap-free Low noise Microphone bias with 7uVrms noise between 20Hz-20kHz, internal pull high resistor for microphone.

- Class G Headphone Amplifier (28mW @ 32Ω, 1% THD+N)

- Sampling rate from 8k to 192 kHz

- Dynamic Range Compressor (DRC)Programmable Biquad filter Integrated DSP with specific functions:Input automatic level control (ALC/AGC)/limiter

- Output dynamic-range-compressor/limiter

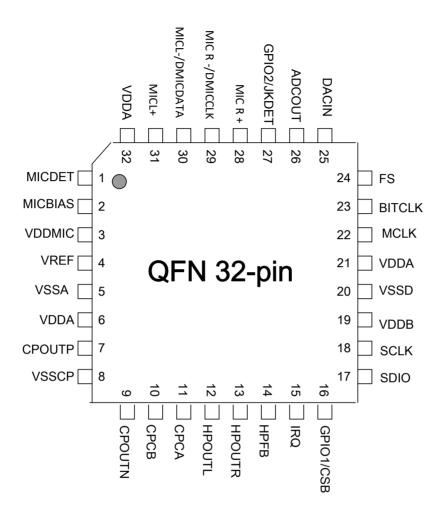

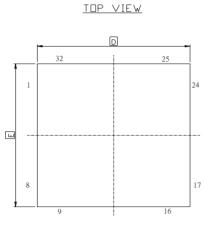

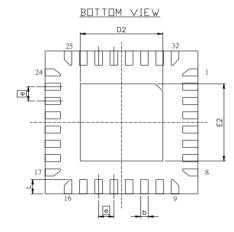

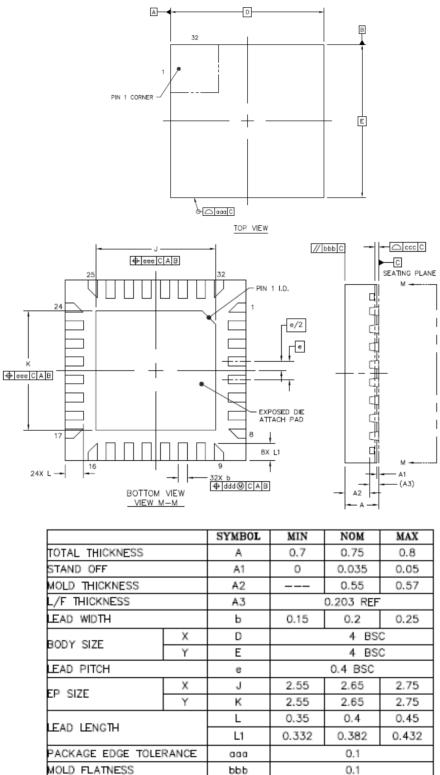

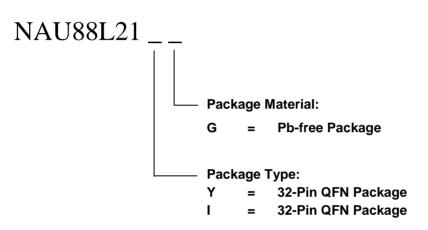

- Package: 32 Pin QFN package

#### Applications

- Gaming controller

- Wireless Headset

- Smart Remote Controller

## Block Diagram : QFN32

| Table             | of Contents                 |                            |            |

|-------------------|-----------------------------|----------------------------|------------|

| BLOC              | K DIAGRAM : QFN32           |                            | 2          |

| <b>PIN D</b>      | IAGRAM :                    |                            | 5          |

| PIN D             | ESCRIPTION                  |                            | 6          |

| ELEC              | TRICAL CHARACTERIST         | ICS                        | 7          |

|                   |                             |                            |            |

| 1.1               |                             |                            |            |

| 1.2               | -                           |                            |            |

| 1.3               | ADC, DAC and Digital Signal | Processing                 | 10         |

| 1.4               | Digital Interfaces          |                            |            |

| 2. P              | OWER SUPPLY                 |                            |            |

| 2.1               |                             |                            |            |

| 3. IN             | IPUT PATH DETAILED DE       | SCRIPTIONS                 |            |

| 3.1               | <b>e</b>                    |                            |            |

| 3.2               |                             |                            |            |

| 3.3               |                             |                            |            |

| 3.4               |                             |                            |            |

| <b>3.5</b><br>3.5 |                             |                            |            |

|                   |                             |                            |            |

| 4.1               |                             | ssors (DRC)                |            |

| 4.1               |                             |                            |            |

| 4.1               | .2 Static Curve             |                            | 18         |

| 4.2               | ADC Digital Volume Control  |                            | 19         |

| 4.3               | ADC Programmable Biquad F   | ilter                      |            |

| 4.4               |                             |                            |            |

| 4.5               |                             | otes                       |            |

|                   |                             |                            |            |

| 5.1               |                             | (DRC)                      |            |

| 5.1<br>5.1        |                             |                            |            |

| 5.2               |                             | Aute and Channel selection |            |

| 5.2<br>5.3        | -                           |                            |            |

| 5.4               |                             |                            |            |

| 5.5               |                             | ide tone                   |            |

| 5.6               | -                           |                            |            |

| 5.6               | .1 μ-law                    |                            | 25         |

| 5.6               |                             | <b>D D D C</b>             |            |

|                   | NAU88L21 Datasheet Rev1.9   | Page 3 of 68               | June, 2020 |

| 6. C   | LOCKING AND SAMPLE RATES                                      | 26 |

|--------|---------------------------------------------------------------|----|

| 6.1    | I2S/PCM Clock Generation                                      | 27 |

| 6.2    | Frequency Locked Loop(FLL)                                    | 29 |

| 7. C   | ONTROL INTERFACES                                             | 31 |

| 7.1    | 2-Wire-Serial Control Mode (I <sup>2</sup> C Style Interface) | 31 |

| 7.2    | 2-Wire Protocol Convention                                    | 31 |

| 7.3    | 2-Wire Write Operation                                        | 32 |

| 7.4    | 2-Wire Read Operation                                         | 33 |

| 7.5    | Digital Serial Interface Timing                               | 34 |

| 7.6    | Software Reset                                                | 34 |

| 8. D   | GITAL AUDIO INTERFACES                                        | 35 |

| 8.1    | Right-Justified Audio Data                                    | 35 |

| 8.2    | Left-Justified Audio Data                                     | 35 |

| 8.3    | I2S Audio Data                                                | 35 |

| 8.4    | PCMA Audio Data                                               | 36 |

| 8.5    | PCMB Audio Data                                               | 36 |

| 8.6    | PCM Time Slot Audio Data                                      | 36 |

| 8.7    | TDM I2S Audio Data                                            | 37 |

| 8.8    | TDM PCMA Audio Data                                           | 37 |

| 8.9    | TDM PCMB Audio Data                                           | 38 |

| 8.10   | TDM PCM Offset Audio Data                                     | 38 |

| 9. O   | UTPUTS                                                        | 40 |

| 9.1    | Class G Headphone Driver and Charge Pump                      | 40 |

| 10. C  | ONTROL AND STATUS REGISTERS                                   | 41 |

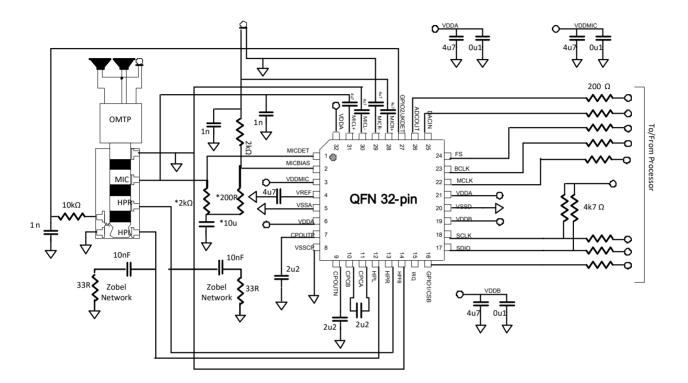

| 11. TY | PICAL APPLICATION DIAGRAM                                     | 63 |

| 12. P/ | ACKAGE INFORMATION                                            | 64 |

|        | RDERING INFORMATION                                           | -  |

|        |                                                               |    |

| -      | RTANT NOTICE                                                  | -  |

|        |                                                               |    |

## Pin Diagram :

## **Pin Description**

| Pin # | Name         | Туре                       | Functionality                                             |

|-------|--------------|----------------------------|-----------------------------------------------------------|

| 1     | MICDET       | Analog IO                  | Microphone/button detect, 2kOhm between Mic and Mic Bias  |

| 2     | MICBIAS      | Analog Output              | Microphone Bias Output                                    |

| 3     | VDDMIC       | Supply                     | Microphone supply                                         |

| 4     | VREF         | Analog I/O                 | Internal DAC & ADC voltage reference decoupling I/O       |

| 5     | VSSA         | Ground                     | Analog Ground                                             |

| 6     | VDDA         | Supply                     | Analog Supply                                             |

| 7     | CPOUTP       | Analog I/O                 | Charge Pump positive voltage                              |

| 8     | VSSCP        | Ground                     | Charge Pump Supply ground                                 |

| 9     | CPOUTN       | Analog I/O                 | Charge Pump negative voltage                              |

| 10    | СРСВ         | Analog I/O                 | Charge Pump switching capacitor node B                    |

| 11    | CPCA         | Analog I/O                 | Charge Pump switching capacitor node A                    |

| 12    | JKTIP(HPL)   | Analog Output              | Jack Tip; Headphone left channel output                   |

| 13    | JKR1(HPR)    | Analog Output              | Jack Ring1; Headphone right channel output                |

| 14    | HPFB         | Ground                     | Headphone Ground                                          |

| 15    | IRQ          | Digital I/O                | IRQ                                                       |

| 16    | GPIO1/CSB    | Digital I/O                | General Purpose IO/CSB                                    |

| 17    | SDIO         | Digital I/O                | Serial Data for I2C                                       |

| 18    | SCLK         | Digital Input              | Serial Data Clock for I2C                                 |

| 19    | VDDB         | Supply                     | Digital IO Supply                                         |

| 20    | VSSD         | Ground                     | Digital IO ground                                         |

| 21    | VDDA         | Supply                     | Analog supply                                             |

| 22    | MCLK         | Digital Input              | CODEC Master clock input                                  |

| 23    | BCLK         | Digital I/O                | Serial data bit clock input or output for I2S or PCM data |

| 24    | FS           | Digital I/O                | Frame Sync input or output for I2S or PCM data            |

| 25    | DACIN        | Digital Input              | Serial Audio data input for I2S or PCM data               |

| 26    | ADCOUT       | Digital Output             | Serial Audio data Output for I2S or PCM data              |

| 27    | JKDET        | Analog Input               | Jack detect input                                         |

| 28    | MICR+        | Analog Input               | PGA MICR+ Analog Input                                    |

| 29    | MICR-/DMCLK  | Analog/Digital Output      | PGA MICR- Analog Input / Digital Microphone Clk output    |

| 30    | MICL-/DMDATA | Analog Input/Digital Input | PGA MICL- Analog Input / Digital Microphone Data input    |

| 31    | MICL+        | Analog Input               | PGA MICL+ Analog Input                                    |

| 32    | VDDA         | Supply                     | Analog Supply                                             |

## **Electrical Characteristics**

Conditions:  $V_{DD}A = V_{DD}B = 1.8V$ ;  $V_{DD}MIC = 3.6V$ .  $R_L$ (Headphone) = 32  $\Omega$ , f = 1kHz, MCLK=12.88MHz, unless otherwise specified. Limits apply for  $T_A = 25^{\circ}C$

| Symbol            | Parameter                              | Conditions                                                                                                                                                                    | Typical   | Limit | Units             |

|-------------------|----------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|-------|-------------------|

|                   |                                        | V <sub>DD</sub> A                                                                                                                                                             | 4         | 16    |                   |

| ISD               | Shutdown Current                       | V <sub>DD</sub> B                                                                                                                                                             | 0.2       | 1     | μA                |

|                   |                                        | VDDMIC                                                                                                                                                                        | 0.2       | 1     |                   |

|                   | Headset Detection Standby<br>Mode      | MCLK off, Jack Insertion, IRQ enabled                                                                                                                                         |           | 10    | μA                |

| IDD               | Active Current Normal Playback<br>Mode | $f_S = 48$ kHz, Stereo HP DAC On, HP<br>On, P <sub>OUT</sub> = 0mW. R <sub>L(HP)</sub> = 32 $\Omega$                                                                          |           | 5     | mA                |

|                   |                                        | Headphone Amplifier                                                                                                                                                           | 1         |       |                   |

| Po                | Output Power                           | Stereo R <sub>L</sub> = $32\Omega$ , DAC Input, CPV <sub>VDD</sub> =<br>1.8V, f=1020Hz, 22kHz BW,<br>THD+N = 1% (QFN package),                                                | 28        |       | mW                |

| 10                |                                        | Stereo R <sub>L</sub> = 16 $\Omega$ , DAC Input, CPV <sub>VDD</sub> = 1.8V, f=1020Hz, 22kHz BW,<br>THD+N = 1% (QFN Package)                                                   | 33        |       | mW                |

| THD+N             | Total Harmonic Distortion +<br>Noise   | $R_L$ = 32 $\Omega$ , f=1020Hz, P <sub>0</sub> = 20mW                                                                                                                         | -88       |       | dB                |

|                   | Cigral to Naisa Datia                  | VOUT = 1VRMS, DAC Input,<br>DAC_Gain = 0dB, HP_Gain = 0dB,<br>Digital Zero Input, f=1020Hz, A-<br>Weighted)                                                                   | 105       |       | dB                |

| SNR S             | Signal to Noise Ratio                  | VOUT = 1 V <sub>RMS</sub> , DAC Input,<br>DAC_Gain = 0dB, HP_Gain = 0dB,<br>Digital Zero Input, f=1020Hz, A-<br>Weighted, auto attenuate enabled,                             | 108       |       | dB                |

|                   |                                        | f <sub>RIPPLE</sub> = 217Hz, V <sub>RIPPLE</sub> = 200mV <sub>P</sub> _P<br>Input Referred, HP_GAIN = 0dB<br>DAC Input, DAC_Gain = 0dB Ripple<br>Applied to V <sub>DD</sub> A | 90        |       | dB                |

| PSRR              | Power Supply Rejection Ratio           | Mono_Gain = 0dB Ripple Applied to<br>V <sub>DD</sub> A                                                                                                                        | 90        |       | dB                |

|                   |                                        | Stereo Single Ended Input Terminated,<br>Stereo_Gain = 0dB Ripple Applied<br>to V <sub>DD</sub> A                                                                             | 90        |       | dB                |

| X <sub>TALK</sub> | Channel Crosstalk                      | Left Channel to Right Channel, -<br>1dBFS, Gain = 0dB, f = 1020Hz                                                                                                             | 70        |       | dB                |

|                   | Interchannel Level Mismatch            |                                                                                                                                                                               | +/- 0.1   |       | dB                |

|                   | Frequency Response                     | F = 20Hz ~ 20kHz                                                                                                                                                              | +0.1/-0.2 |       | dB                |

|                   | Pop up Noise                           |                                                                                                                                                                               |           | 1     | mVrms             |

| eos               | Output Noise                           | DAC_Gain = 0dB, HP_Gain = 0dB,<br>f <sub>s</sub> =48kHz, OSR <sub>DAC</sub> = 128, A-<br>Weighted                                                                             | 4.4       |       | uV <sub>RMS</sub> |

|                   | Out of Band Noise Level                |                                                                                                                                                                               | -60dB     |       |                   |

| Vos               | Output Offset Voltage                  | HP_Gain = 0dB, DAC_Gain= 0dB,<br>DAC Input                                                                                                                                    |           | ±1    | mV                |

|                   | Power Consunption MP3 Mode             | No Load, No Signal, Amp on<br>$f_S = 48$ kHz, Stereo DAC On, Amp On,<br>$P_{OUT} = 0$ mW. $R_L = 32\Omega$                                                                    | 6         |       | mW                |

| Symbol | Parameter                       | Conditions                                                                                                                                                   | Typical      | Limit | Units            |

|--------|---------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|-------|------------------|

|        | Fs Accuracy (44.1 / 48 kHz)     |                                                                                                                                                              | +/-<br>0.02% |       |                  |

|        | Pop and Click Noise             | plug Into or out of DAC to Headphone                                                                                                                         | 1            |       | mVrms            |

|        |                                 | ADC                                                                                                                                                          |              |       |                  |

|        | ADC Total Harmonic Distortion + | MIC Input, MIC_GAIN = 0dB, VIN =<br>0.8Vrms, f=1020Hz, fs = 48KHz,<br>Mono Differential Input                                                                | -91          |       | dB               |

| THD+N  | Noise                           | MIC Input, MIC_GAIN = 30dB, Volume<br>= 0dB, Vin=28.5mVrms, f=1020Hz,<br>Digital Gain = 0dB, Mono<br>Differential Input                                      | -80          |       | dB               |

| SNR    | Signal to Noise Ratio           | Reference = VOUT(0dBFS), A-<br>Weighted, MIC Input, MIC Gain =<br>0dB,fs = 48kHz, Mono Differential<br>Input                                                 | 102          |       | dB               |

| ONIX   | Signal to Noise Ratio           | Reference = VOUT(0dBFS), A-<br>Weighted, MIC Input, MIC Gain =<br>6dB,fs = 48kHz, Mono Differential<br>Input                                                 | 101          |       | dB               |

| PSRR   | Power Supply Rejection Ratio    | V <sub>RIPPLE</sub> = 200mV <sub>PP</sub> applied to V <sub>DD</sub> A,<br>f <sub>RIPPLE</sub> = 217Hz, Input Referred,<br>MIC_GAIN = 0dB Differential Input | 90           |       | dB               |

| CMRR   | Common Mode Rejection Ratio     | Differential Input 100mVrms, PGA gain<br>= 20dB, frequency sweep from<br>20Hz to 20KHz                                                                       | 65           |       | dB               |

| FSADC  | ADC Full Scale Input Level      | V <sub>DD</sub> A= 1.8V                                                                                                                                      | 1            |       | V <sub>RMS</sub> |

|        | Minimum Input Impedance         |                                                                                                                                                              | 10           |       | kOhm             |

|        | Frequency Response              | f = 20Hz ~ 20kHz                                                                                                                                             | +0.1/-0.2    |       | dB               |

|        | Pop up Noise                    | TBD                                                                                                                                                          | 1            |       | mVrms            |

|        | Power Consumption               | No Signal, ADC on<br>f <sub>s</sub> = 44.1kHz                                                                                                                | 5            |       | mW               |

|        |                                 | MICBIAS                                                                                                                                                      |              |       |                  |

| VBIAS  | Output Voltage                  | Programmable 1.8V to 3.0V in 6 steps                                                                                                                         | 2.5          |       | V                |

| Ιουτ   | Output Current                  |                                                                                                                                                              |              | 4     | mA               |

| eos    | Output Noise                    | Low noise mode, at 1kHz                                                                                                                                      |              | 47    | nV/√Hz           |

#### Digital I/O

| Parameter         | Symbol          | Comments/Conditions     |                        | Min                    | Мах                    | Units |

|-------------------|-----------------|-------------------------|------------------------|------------------------|------------------------|-------|

| Input LOW level   | V⊫              | Vdd                     | B = 1.8V               |                        | 0.33*V <sub>DD</sub> B | V     |

|                   | VIL             | V <sub>DD</sub>         | B = 3.3V               |                        | 0.37*V <sub>DD</sub> B | v     |

| Input HIGH level  | V <sub>DD</sub> |                         | B = 1.8V               | 0.67*V <sub>DD</sub> B |                        | V     |

| Input HIGH level  | Vih             | $V_{DD}B = 3.3V$        |                        | 0.63*V <sub>DD</sub> B |                        | v     |

| Output HIGH level | Vон             | I <sub>Load</sub> = 1mA | V <sub>DD</sub> B=1.8V | 0.9*V <sub>DD</sub> B  |                        | V     |

| Output high level | VOH             | ILoad= IIIIA            | $V_{DD}B = 3.3V$       | 0.95*V <sub>DD</sub> B |                        | v     |

| Output LOW level  | Vol             | I <sub>Load</sub> = 1mA | $V_{DD}B = 1.8V$       |                        | 0.1*V <sub>DD</sub> B  | V     |

|                   | V OL            | ILoad= IIIIA            | V <sub>DD</sub> B=3.3V |                        | 0.05*V <sub>DD</sub> B | V     |

#### **Recommended Operating Conditions**

| Condition                      | Symbol | Min  | Typical | Мах  | Units |

|--------------------------------|--------|------|---------|------|-------|

| Digital I/O Supply Range       | VDDB   | 1.62 | 3.3     | 3.6  | V     |

| Analog Supply Range            | VddA   | 1.62 | 1.8     | 1.98 | V     |

| Headphone Supply Range         | VddA   | 1.62 | 1.8     | 1.98 | V     |

| Microphone Bias Supply Voltage | VDDMIC | 3.0  | 3.3     | 3.6  | V     |

| Temperature Range              | TA     | -40  |         | +85  | °C    |

#### Absolute Maximum Ratings

| Parameter                            | Min        | Max                   | Units |

|--------------------------------------|------------|-----------------------|-------|

| Digital Supply Range                 | -0.3       | 2.2                   | V     |

| Digital I/O Supply Range             | -0.3       | 4.0                   | V     |

| Analog Supply Range                  | -0.3       | 2.2                   | V     |

| Headphone Supply Range               | -0.3       | 2.2                   | V     |

| Microphone Bias Supply Voltage       | -0.3       | 4.0                   | V     |

| Voltage Input Digital Range          | DGND - 0.3 | V <sub>DD</sub> + 0.3 | V     |

| Voltage Input Analog Range           | AGND - 0.3 | V <sub>DD</sub> + 0.3 | V     |

| Junction Temperature, T <sub>J</sub> | -40        | +150                  | °C    |

| Storage Temperature                  | -65        | +150                  | °C    |

CAUTION: Do not operate at or near the maximum ratings listed for extended periods. Exposure to such conditions may adversely influence product reliability and result in failures not covered by warranty.

## 1. General Description

NAU88L21 is an ultra-low power CODECs that has both analog and digital blocks operating at 1.8V. This CODEC includes DSP functions including DRCs (Dynamic Range Compression) and programmable biquad filters. Mic bias supply is upgraded to support voltages up to 3V.

#### 1.1 Inputs

The NAU88L21 provides analog inputs to acquire and process audio signals from microphones with high fidelity and flexibility. There is a stereo input path that can be used to capture signals from single-ended or differential sources. The channel has a fully differential programmable gain amplifier (PGA). The outputs of the PGA connect to the ADC.

The NAU88L21 also has an input for one digital microphone. The NAU88L21 provides a DMCLK, the clock signal for the digital microphones.

The analog and the digital microphone inputs cannot be used simultaneously.

#### 1.2 Outputs

NAU88L21 has one pair of ground-referenced Class G headphone outputs that are fed by two DACs. The headphone amplifier has a gain range of -9dB to 0dB.

The Class G headphone amplifier is powered by the charge pump output voltages CPOUTP and CPOUTN. When there is no loading the CPOUTP is equal to VDDA, and CPOUTN is equal to –VDDA. This headphone output can also be used as a lineout.

#### **1.3 ADC, DAC and Digital Signal Processing**

The NAU88L21 has two independent high quality ADC's and DACs. These are high performance 24-bit sigma-delta converters, which are suitable for a very wide range of applications.

The ADCs and DACs have functions that individually support digital mixing and routing. The ADCs and DACs blocks also support advanced digital signal processing subsystems that enable a very wide range of programmable signal conditioning and signal optimizing functions. All digital processing is done with 24-bit precision to minimize processing artifacts and maximize the audio dynamic range supported by the NAU88L21.

The ADCs and DACs digital signal process can support two-point dynamic range compressors (DRCs), programmable biquad filters configurable for low pass filters, high pass filters, Notch filter, Bell, low shelf, and high shelf filters with various gain, Q, and frequency controls. Two-point DRCs can be programmed to limit the maximum output level and/or boost a low output level. The biquad filters can be configured as high pass filters intended for DC-blocking or low frequency noise reduction, such as reducing unwanted ambient noise or "wind noise" on a microphone inputs.

#### **1.4 Digital Interfaces**

Command and control of the device is accomplished by using the I2C interface.

The digital audio I/O data streams transfer separately from command and control using either I2S or PCM audio data protocols

These simple but highly flexible interface protocols are compatible with most commonly used serial data protocols, host drivers, and industry standard I2S and PCM devices.

### 2. Power Supply

This NAU88L21 has been designed to operate reliably using a wide range of power supply conditions and poweron/power-off sequences. Because of this, there are no special requirements for the sequence or rate at which the various power supply pins change. Any supply can rise or fall at any time without harming the device. However, pops and clicks may result from some sequences.

#### 2.1 Power on and off reset

The NAU88L21 includes a power on reset circuit on chip. The circuit resets the internal logic control at VDDA supply power up and this reset function is automatically generated internally when power supplies are too low for reliable operation. The reset threshold is approximately 0.55Vdc and 1.0Vdc for VDDA. It should be noted that these values are much lower than the required voltage for normal operation of the chip.

The reset is held on while the power levels for VDDA are below their respective thresholds. Once the power levels rise above their thresholds, the reset is released. Once the reset is released, the registers are ready to be written to. It is also important to note that all the registers should be kept in their reset state for at least 6µs.

An additional internal RC filter based circuit is added which helps the circuit respond for fast ramp rates (~10µs) and generate the desired reset period width (~10µs at typical corner). This filter is also used to eliminate supply glitches which can generate a false reset condition, typically 50ns.

For reliable operation, it is recommended to write any value to register upon power up. This will reset all registers to the known default state.

Note that when VDDA are below the power on reset threshold, then the digital IO pins will go into a tri-state condition.

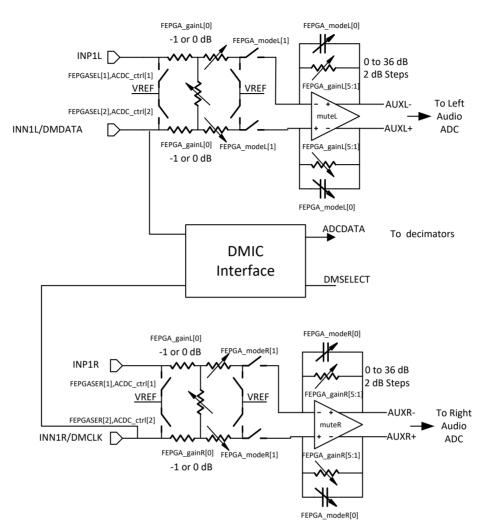

## 3. Input Path Detailed Descriptions

NAU88L21 has two low noise, high common mode rejection ratio analog microphone differential input. The microphone inputs MICL+/- & MICR+/- which are followed by -1dB to 36dB PGA gain stages that have a fixed 12kOhm input impedance.

Inputs are maintained at a DC bias of approximately ½ of the VDDA supply voltage. Connections to these inputs should be AC-coupled by means of external DC blocking capacitors suitable for the device application.

The differential microphone input structure is essential in noisy digital systems where amplification of low-amplitude analog signals is necessary such as in portable digital media devices and cell phones. Differential inputs are also very useful to reduce ground noise in systems in which there are ground voltage differences between different chips and components. When properly implemented, the differential input architecture offers an improved power-supply rejection ratio (PSRR) and higher ground noise immunity.

#### 3.1 Analog Microphone Inputs

The analog microphone inputs are routed to the FEPGA (Front End Programmable Gain Amplifier). The input stage can be configured in different modes. The FEPGA gain can be varied from -1dB to 36dB in 1dB steps. The gain stage has a fixed 12kOhm input impedance and can be individually enabled or disabled by using register.

Figure 1: Microphone Input Block Diagram with Registers

#### 3.2 Digital Microphone Input

The MICL- and MICR- pins can be used for the digital microphone input. MICR- is the clock for the digital microphones and the MICL- is the data in.

#### 3.3 VREF

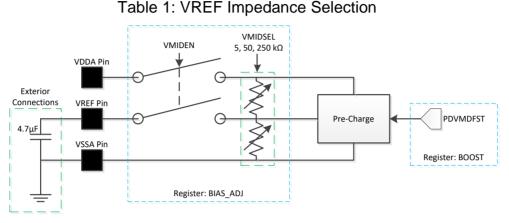

The NAU88L21 includes a mid-supply reference circuit that produces a voltage close to VDDA/2. This "VREF" pin should be decoupled to VSS through an external bypass capacitor. Because VREF is used as a reference voltage inside the NAU88L21, a large capacitance is required to achieve good power supply rejection at low frequency. Typically, a value of 4.7µF should be used. This larger capacitance may introduce longer rise time of VREF and delay the line output signal. However, a pre-charge circuit can be supported to help reduce the rise time. Due to the high impedance of the VREF pin, it is important to use a low leakage capacitor. A pre-charge circuit has been implemented to reduce the VREF rise time. Once charged, this can be disabled using to save power or prevent rapid changes in level due to fluctuations in VDDA. The below Table 1 shows the VREF tie-off resister selection.

| VMIDSEL | VREF Resistor Selection    | VREF Impedance               |

|---------|----------------------------|------------------------------|

| 00      | Open, no resistor selected | Open, no impedance installed |

| 01      | 50kOhm                     | 25kOhm                       |

| 10      | 250kOhm                    | 125kOhm                      |

| 11      | 5kOhm                      | 2.5kOhm                      |

Figure 2: VREF Circuitry

#### 3.4 MIC Bias

The NAU88L21 provides one MIC bias pin, which can be used to power various microphones. The output level of MIC Bias can be set between VDDA and 1.53 X VDDA using register settings.

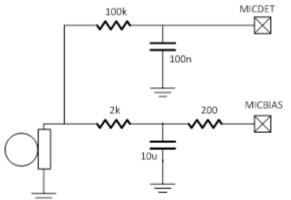

It is recommended that the microphones do not draw more than 4mA from the MICBIAS pin. There are options for connecting internal 2 Kohm resistor to the microphone and for low noise or low power mode. If MICBIAS is used in low power mode, typically 100nF or 200nF capacitor can be used along with MIC Bias level at VDDA. In the low noise mode, external 1uF or 4.7uF capacitor can be omitted by register settings when MIC Bias is used to power analog microphones.

#### 3.5 MIC detect

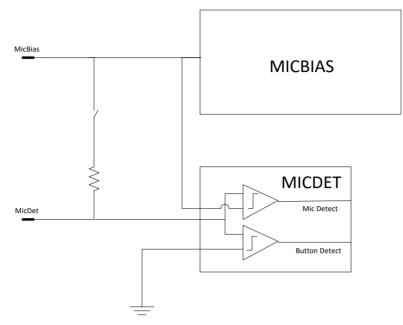

The MIC detect block can detect whether a microphone is connected between the MICBIAS output and the MICDET pin. Either the internal 2kOhm resistor or an external 2kOhm resistor can be used to connect the microphone to the MICDET pin and MICBIAS. See Figure 3, where the internal hookup of the MICDET and MICBIAS blocks is shown.

Figure 3. Mic Detect and MICBIAS blocks

Application note: Adding a simple RC on the MICDET pin can help reduce noise coupling. These may be board level related, or component related effects.

Figure 4. Reducing noise coupling effects

If the optional external 2KOhm resistor is used, then the internal 2K Ohm resistor (Between MICBIAS and MICDET) should be disabled.

## 3.5.1 Key Release

This feature detects the edge case where the key press interrupt is not followed by a release interrupt until later on in the sequence and clears the x11 register to prepare for further interrupts.

Figure 5. Key Release Flowchart

## 4. ADC Digital Block

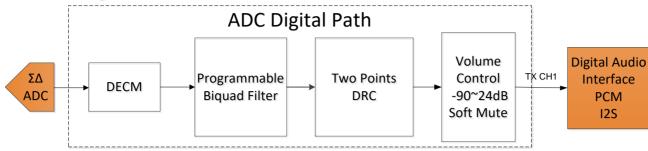

Figure 6: ADC Digital Path

The ADC digital block takes the output of the 24-bit Analog-to-Digital converter and performs signal processing aimed at producing a high quality audio sample stream to the audio path digital interface. The Figure 7 shows the various steps associated with the ADC digital path.

Oversampling is used to improve noise and distortion performance; however this does not affect the final audio sample rate. The oversampling rate configured between 32X and 256X using register settings.

The polarity of either ADC output signal can be changed independently on either ADC logic output as a feature sometimes useful in management of the audio phase. This feature can help minimize any audio processing that may be otherwise required as the data is passed to other stages in the system.

The full-scale input level is proportional to VDDA. For example, with a 1.8V supply voltage, the full-scale level is 1.0VRMS.

### 4.1 ADC Dynamic Range Compressors (DRC)

The ADC's in the digital signal path each support a two-point dynamic range compressor (DRC) for advanced signal processing. Each DRC can be programmed to limit the maximum output level and/or boost a low output level signal. The DRC's function consists of level estimation and static curve control.

#### 4.1.1 Level Estimation

The NAU88L21 uses Peak level estimation that depends on the attack and decay time settings, which can be programmable by register settings as shown in the Table 2.

| <b>BITS</b> | DRC_PK_COEF1_ADC | DRC_PK_COEF2_ADC |

|-------------|------------------|------------------|

| 0000        | Ts               | 63*Ts            |

| 0001        | 3*Ts             | 127*Ts           |

| 0010        | 7*Ts             | 255*Ts           |

| 0011        | 15*Ts            | 511*Ts           |

| 0100        | 31*Ts            | 1023*Ts          |

| 0101        | 63*Ts            | 2047*Ts          |

| 0110        | 127*Ts           | 4095*Ts          |

| 0111        | 255*Ts           | 8191*Ts          |

Table 2: ADC Level Estimation - Attack and Decay Time Register Settings

Please note that Ts is the sampling time given by 1/(Sampling Frequency)

#### 4.1.2 Static Curve

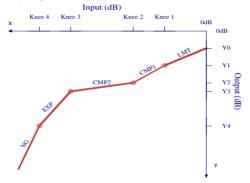

The DRC static curve supports up to five programmable sections as shown in the Figure 6.

Figure 8: DRC Static Characteristic

Each section on the characteristic (labeled NG, EXP, CMP2, CMP1, and LMT) can be controlled by setting the slope and knee point values, in their respective registers. The table below provides the corresponding register locations.

| Static Curve Section | Slope                                 | Knee Point                  |

|----------------------|---------------------------------------|-----------------------------|

| LMT                  | 0, 1/2, 1/4, 1/8, 1/16, 1/32, 1/64, 1 |                             |

| CMP1                 | 0, 1/2, 1/4, 1/8, 1/16, 1             | 0 to -31dB with -1dB step   |

| CMP2                 | 0, 1/2, 1/4, 1/8, 1/16, 1             | 0 to -63dB with -1dB step   |

| EXP                  | 1, 2, 4                               | -18 to -81dB with -1dB step |

| NG                   | 1, 2, 4, 8                            | -35 to -98dB with -1dB step |

#### Table 3: ADC DRC Static Curve control registers

The output Y values can be determined based on the slopes and knee points selected. Y1 is always equal to Knee 1, as an initial and default condition.

Y1 = Knee 1 Y0 = Y1 - (Knee 1) \* (LMT Slope) Y2 = (Knee 2 - Knee 1) \* (CMP1 Slope) + Y1 Y3 = (Knee 3 - Knee 2) \* (CMP2 Slope) + Y2 Y4 = (Knee 4 - Knee 3) \* (EXP Slope) + Y3 The attack time and decay time is programmable as shown in the Table 4. And the smooth knee filter can be also enabled by register setting.

| BITS | DRC ATK ADC CH## | DRC DCY ADC CH## |

|------|------------------|------------------|

| 0000 | Ts               | 63*Ts            |

| 0001 | 3*Ts             | 127*Ts           |

| 0010 | 7*Ts             | 255*Ts           |

| 0011 | 15*Ts            | 511*Ts           |

| 0100 | 31*Ts            | 1023*Ts          |

| 0101 | 63*Ts            | 2047*Ts          |

| 0110 | 127*Ts           | 4905*Ts          |

| 0111 | 255*Ts           | 8191*Ts          |

| 1000 | 511*Ts           | 16383*Ts         |

| 1001 | 1023*Ts          | 32757*Ts         |

| 1010 | 2047*Ts          | 65535*Ts         |

| 1011 | 4095*Ts          |                  |

| 1100 | 8191*Ts          |                  |

| Table 4: ADC Attack and | Decay Time | Register Settings |

|-------------------------|------------|-------------------|

|                         |            |                   |

### 4.2 ADC Digital Volume Control

The digital volume control feature allows adjustment of the audio volume coming from ADC using a two-stage volume control. This allows the gain to be adjusted from -103dB to +24dB. Also included is a mute value that will reduce the output signal of the ADCs to zero.

#### 4.3 ADC Programmable Biquad Filter

The NAU88L21 has 4 dedicated digital biquad filters. Two for the ADC path, and two for the DAC path. The biquad filter is a second-order recursive linear filter with two poles and two zeros. Its transfer function is the Z-domain consists of two quadratic functions:

$$H(z) = \frac{B_0 + B_1 Z^{-1} + B_2 Z^{-2}}{1 + A_1 Z^{-1} + A_2 Z^{-2}}$$

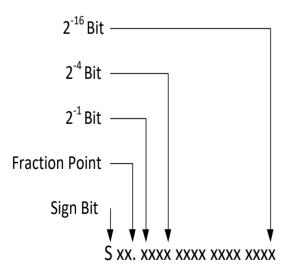

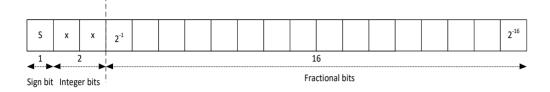

The coefficients A1, A2, B0, B1, B2 are represented in the 3.16 format described below

Each Biquad Coefficient has 19 bits in Sxx.16 format where

- S is the sign bit (1 bit),

- xx are integers (2bits)

- 16 fractional bits (16 bits)

Figure 9: Number format description for biquad filters coefficients.

#### 4.4 Companding

Companding is used in digital communication systems to optimize signal-to-noise ratios with reduced data bit rates using non-linear algorithms. The NAU88L21 supports the two main telecommunications companding standards on both transmit and receive sides: A-law and  $\mu$ -law. The A-law algorithm is primarily used in European communication systems and the  $\mu$ -law algorithm is primarily used by North America, Japan, and Australia.

## 4.5 Additional ADC Application Notes

The ADC clock polarity can be inverted if necessary by register setting. It is recommend to match ADC oversampling rate with ADC clock rate as shown in the Table 5.

| ADC_RATE    | CLK_ADC_SRC   |

|-------------|---------------|

| 00(OSR=32)  | 11(CODEC 1/8) |

| 01(OSR=64)  | 10(CODEC1/4)  |

| 10(OSR=128) | 01(CODEC 1/2) |

| 11(OSR=256) | 00(CODEC CLK) |

Table 5: ADC\_RATE and CLK\_ADC\_SRC Pairs

## 5. DAC Digital Block

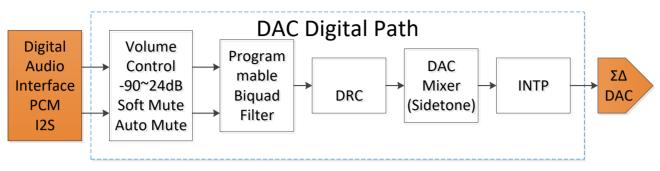

Figure 10: DAC Digital Path

The DAC digital block uses 24-bit signal processing to generate analog audio with a 16-bit digital sample stream input. This block consists of a sigma-delta modulator, digital decimator/filter, programmable biquad filter, and a DRC. The full-scale output level is proportional to VDDA. For example, with a 1.8V supply voltage, the full-scale level is 1.0 VRMS. The oversampling rate of the DAC can be changed from 32x to 256x for improved audio performance at higher power consumption. The DAC output signal polarity can be changed using register setting. This can help minimize any audio processing that may be required as the data is passed from other stages of the system.

## 5.1 DAC Dynamic Range Control (DRC)

The DAC DRC functions in the same way as the ADC DRC explained in Section 4.1. However, different control registers are used.

#### 5.1.1 Level Estimation

The Table 6 shows the attack and decay times for the peak level estimation. And, the time constant Ts is the the sampling time given by 1/(Sampling Frequency).

| BITS | DRC_PK_COEF1_ADC | DRC_PK_COEF2_ADC |

|------|------------------|------------------|

| 0000 | Ts               | 63*Ts            |

| 0001 | 3*Ts             | 127*Ts           |

| 0010 | 7*Ts             | 255*Ts           |

| 0011 | 15*Ts            | 511*Ts           |

| 0100 | 31*Ts            | 1023*Ts          |

| 0101 | 63*Ts            | 2047*Ts          |

| 0110 | 127*Ts           | 4095*Ts          |

| 0111 | 255*Ts           | 8191*Ts          |

Table 6: DAC Level Estimation Attack and Decay Time Register Settings

#### 5.1.2 Static Curve

The DRC static curve supports five programmable sections, and slope and knee points can be configured as shown in the Table 7.

| Static Curve<br>Section | Slope                                 | Knee Point                  |

|-------------------------|---------------------------------------|-----------------------------|

| LMT                     | 0, 1/2, 1/4, 1/8, 1/16, 1/32, 1/64, 1 |                             |

| CMP1                    | 0, 1/2, 1/4, 1/8, 1/16, 1             | 0 to -31dB with -1dB step   |

| CMP2                    | 0, 1/2, 1/4, 1/8, 1/16, 1             | 0 to -63dB with -1dB step   |

| EXP                     | 1, 2, 4, 8                            | -18 to -81dB with -1dB step |

| NG                      | 1, 2, 4, 8                            | -35 to -98dB with -1dB step |

Table 7: DAC DRC Static Curve Control Registers

The Table 8 shows the attack and decay time for DRC. And, it needs to be carefully used combination with cross talk function because DRC is the last blocks in the path after mixer. Small cross-talk signal might be filtered out by DRC. The smooth knee function can be also enabled by register setting.

| Вітз | DRC_ATK_DAC | DRC_DCY_DAC |

|------|-------------|-------------|

| 0000 | Ts          | 63*Ts       |

| 0001 | 3*Ts        | 127*Ts      |

| 0010 | 7*Ts        | 255*Ts      |

| 0011 | 15*Ts       | 511*Ts      |

| 0100 | 31*Ts       | 1023*Ts     |

| 0101 | 63*Ts       | 2047*Ts     |

| 0110 | 127*Ts      | 4095*Ts     |

| 0111 | 255*Ts      | 8191*Ts     |

| 1000 | 511*Ts      | 16383*Ts    |

| 1001 | 1023*Ts     | 32757*Ts    |

| 1010 | 2047*Ts     | 65535*Ts    |

| 1011 | 4095*Ts     |             |

| 1100 | 8191*Ts     |             |

Table 8: DAC Static Curve Attack and Delay Time Register Settings

### 5.2 DAC Digital Volume Control, Mute and Channel selection

DACL and DACR both have separate digital volume controls that allow the user to adjust the gain from -103dB to +24dB in 0.5dB steps as well as mutes. Left and Right channels can be adjusted separately and control is accessed through register settings.

### 5.3 DAC Soft Mute

The soft mute function ramps the DAC digital volume down to zero when enabled. When disabled, the volume increases to the register specified volume level for each channel. This feature provides a tool that is useful for using the DAC without introducing pop and click sounds.

#### 5.4 DAC Auto Attenuate

Auto-attenuate can greatly increase the perceived SNR during playback of silence. The last analog output stage is attenuated such that the noise contribution of the preceding stages is eliminated. The use of auto-attenuate by attenuating the analog output on a DAC path when the digital input represents a zero signal needs to be done gradually in order to avoid audible pops due to sudden offset changes. It is desirable to slowly ramp down the gain of the analog output stage to the maximum attenuation level. This function will be referred to as auto-attenuate. The auto-attenuate feature is used to increase the Signal to Noise Ratio. In addition, the auto attenuate logic can be used to attenuate the analog output manually,saving some software routines and allowing pop-less ramp up and down of the analog outputs with little register writes.

The auto-attenuate function can be enabled manually or automatically. In the automatic mode, if both the left and right channel receive 1024 consecutive samples of "0", then it will read and store the value of the headset driver volume control into internal temporary registers and then attenuate the headset driver output by 1dB for every 128 samples, until -54dB is reached (54 steps maximum). If , at any time, the I2S DACIN signal receives non-zero signal samples, the headset output driver gain is increased by 1dB per step and in 1, 16, 32 or 128 samples per step (programmable by register) until the gain will be stepped up until the original gain setting is reached. In the manual mode, once enabled, it will immediately start saving the volume control into temporary registers and attenuate signals by 1dB for every 128 samples until e-54dB is reached. If the manual attenuate is disabled, the gain will be fully recovered by 1dB step in 1, 16, 32, or 128 samples per step.

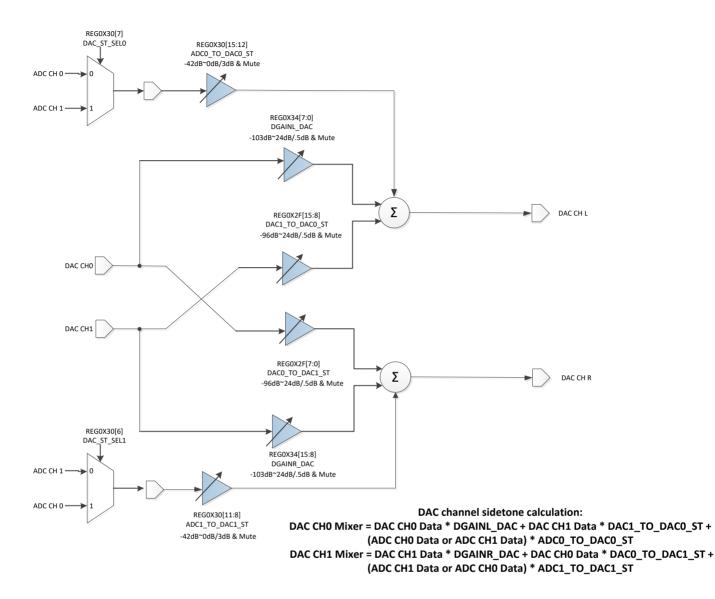

#### 5.5 DAC Path Digital Mixer with Side tone

The NAU88L21 implements a channel based digital mixer architecture. Each DAC outputs can be selected between the different inputs. The ADC input channels, I2S channels are capable of being mixed into either output of the DAC. The figure below shows a block diagram of how the mixer works along with the related registers.

Figure 11: DAC Path Digital Mixer with Side tone.

### 5.6 Companding

Companding is used in digital communication systems to optimize signal-to-noise ratios with reduced data bit rates using non-linear algorithms. The NAU88L21 supports the two main telecommunications companding standards on both transmit and receive sides: A-law and  $\mu$ -law. The A-law algorithm is primarily used in European communication systems and the  $\mu$ -law algorithm is primarily used by North America, Japan, and Australia.

Companding converts 14 bits ( $\mu$ -law) or 13 bits (A-law) to 8 bits using non-linear quantization resulting in 1 sign bit, 3 exponent bits and 4 mantissa bits. When the companding mode is enabled, 8 bit word operation must be enabled.

Sections 5.6.1 and 5.6.2 contain the compression equations set by the ITU-T G.711 standard and implemented in the NAU88L21.

#### 5.6.1 µ-law

$$F(x) -1 < x < 1$$

=  $\frac{\ln(1 + \mu \times |x|)}{\ln(1 + \mu)}$ ,  $\mu = 255$

#### 5.6.2 A-law

$$F(x) = \frac{A \times |x|}{(1 + \ln(A))'}, \qquad 0 < x < \frac{1}{A}$$

=  $\frac{(1 + \ln(A \times |x|))}{(1 + \ln(A))}, \qquad \frac{1}{A} \le x \le 1$

$$A = 87.6$$

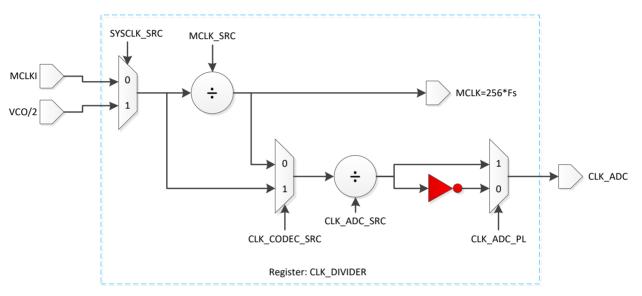

### 6. Clocking and Sample Rates

The internal clocks for the NAU88L21 are derived from a common internal clock source. This master system clock can set directly by the MCLK pin input or it can be generated from a Frequency Locked Loop (FLL) using the MCLK\_PIN, BCLK or FS as a reference. While most of the common audio sample rates can be derived directly from typical MCLK frequencies, the FLL provides additional flexibility for a wide range of MCLK inputs or as a free running clock in the absence of an external reference.

The figures below is a block diagram illustrating how the various register settings can be used to adjust/select the MCLK, BCLK, FS, and ADC\_CLK clock frequency.

| Bits | MCLK_SRC     |

|------|--------------|

| 0000 | Divide by 1  |

| 0001 | Invert       |

| 0010 | Divide by 2  |

| 0011 | Divide by 4  |

| 0100 | Divide by 8  |

| 0101 | Divide by 16 |

| 0110 | Divide by 32 |

| 0111 | Divide by 3  |

| 1001 | Invert       |

| 1010 | Divide by 6  |

| 1011 | Divide by 12 |

| 1100 | Divide by 24 |

| 1101 | Divide by 48 |

| 1110 | Divide by 96 |

| 1111 | Divide by 5  |

Table 9: Register Settings

| Bits | CLK ADC SRC |

|------|-------------|

| 00   | Divide by 1 |

| 01   | Divide by 2 |

| 10   | Divide by 4 |

| 11   | Divide by 8 |

#### Table 10: Register Settings

The internal clock frequency MCLK must be running at 256\*Fs (Fs = sample rate in Hz) in order to achieve the best performance. The internal clock frequency MCLK can also run at 400\*Fs or 500\*Fs, which may give a slightly lower performance. For example, when targeting 48 kHz sample rate audio, the MCLK must be set to 256\*48k = 12.288MHz, 400\*48k = 19.2MHz, or 500\*48k = 24MHz. When the input clock MCLKI is higher than this speed, register CLK\_DIVIDER.MCLK\_SRC REG0x03[3:0] provides a flexible divider selection to meet this requirement. The FLL can also be used to generate an MCLK that meets this requirement.

The OSR (over sampling rate) is defined as CLK\_ADC frequency divided by the audio sample rate.

$$OSR = \frac{CLK\_ADC}{Fs}$$

Available over-sampling rates are 32, 64, 128 or 256 as set in the <u>ADC\_RATE.ADC\_RATE REG0X2B[1:0]</u> register. CLK\_ADC frequency is set by <u>CLK\_DIVIDER.CLK\_CODEC\_SRC REG0X03[13]</u> and <u>CLK\_DIVIDER.CLK\_ADC\_SRC REG0X03[7:6]</u> registers.

It should be noted that the OSR and Fs must be selected so that the max frequency of CLK\_ADC is less than or equal to 6.144MHz. When CLK\_ADC is determined, <u>ADC\_RATE.ADC\_RATE REG0X2B[1:0]</u> should be set to provide appropriate down sampling through digital filters.

There are two special cases in which the OSR will be 100. If MCLK is 400 or 500 times the input sample rate of the DAC or the output sample rate of the ADC, the OSR will be 100. In the first case, set

CLK\_DIVIDER.CLK\_ADC\_SRC\_REG0X3[7:6]=2'b10 (1/4) for ADC path, and DAC path need to set CLK\_DIVIDER.CLK\_DAC\_SRC\_REG0X3[5:4]=2'b10 (1/4) and

DAC\_RATE.DAC\_CTRL1\_REG0X2C[2:0]=3b'000 , in the second case the clock to the ADC and DAC will be adjusted automatically.

#### Example 1:

To configure Fs = 48 kHz, MCLK = (256\*Fs) = 12.288MHz, and CLK\_ADC = 6.144MHZ Set:

- SYSCLK\_SRC = MCLK

- CLK\_ADC\_SRC = 1/2

- ADC OSR = 128

#### Example 2:

To configure Fs = 16 kHz, MCLKI = 12.288MHz, and CLK\_ADC = 4.096MHz Set:

- SYSCLK\_SRC = MCLK

- MCLK\_SRC = 1/3

- CLK\_ADC\_SRC = 1

- ADC OSR = 256

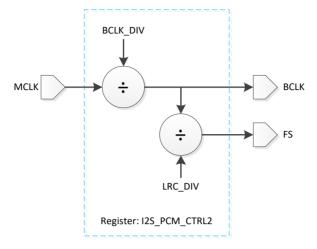

#### 6.1 I2S/PCM Clock Generation

In master mode, BCLK can be derived from MCLK via a programmable divider, and the FS can be derived from BCLK via another programmable divider.

To select specific Fs values, both dividers must be set according to the block diagram and the equation below.

$BCLK = Fs \times data \ length \times channels$

Figure 13: BCLK and FS Frequency Selection

| Bits | BCLK_DIV     |

|------|--------------|

| 000  | Divide by 1  |

| 001  | Divide by 2  |

| 010  | Divide by 4  |

| 011  | Divide by 8  |

| 100  | Divide by 16 |

| 101  | Divide by 32 |

Table 11: Register Settings

| Bits | LRC_DIV       |

|------|---------------|

| 000  | Divide by 256 |

| 001  | Divide by 128 |

| 010  | Divide by 64  |

| 101  | Divide by 32  |

Table 12: Register Settings

#### Example 1:

If we want an Fs of 48 kHz and 16 bit data is to be sent to the I2S bus (2 channel)

- BCLK = 48000\*16\*2 = 1.536MHz and MCLK = 48000\*256 = 12.288MHz

- Set BCLK\_DIV = 1/8

- Set LRC\_DIV = 1/32

Or 32 bit data is to be sent

- BCLK = 48000\*32\*2 = 3.073MHz and MCLK = 48000\*256 = 12.288MHz

- Set BCLK\_DIV = 1/4

- Set LRC\_DIV = 1/64

#### Example 2:

If we want an Fs of 16 kHz and 16 bit data is to be sent to the I2S bus (2 channel)

- BCLK = 16000\*16\*2 = 512kHz and MCLK = 16000\*256 = 4.096MHz

- Set BCLK\_DIV = 1/8

- Set LRC\_DIV = 1/32

32 bit data is to be sent,

- BCLK = 16000\*32\*2 = 1.024MHz and MCLK = 16000\*256 = 4.096MHz

- Set BCLK\_DIV = 1/4 NAU88L21 Datasheet Rev1.9

• Set LRC\_DIV = 1/64

#### Example 3:

If we want an Fs of 16 kHz and 32 bit data is to be sent to the I2S TDM bus (4 channels)

- BCLK = 16000\*32\*4 = 2.048MHz and MCLK = 16000\*256 = 4.096MHz

- Set BCLK\_DIV = 1/2

- Set LRC\_DIV = 1/128

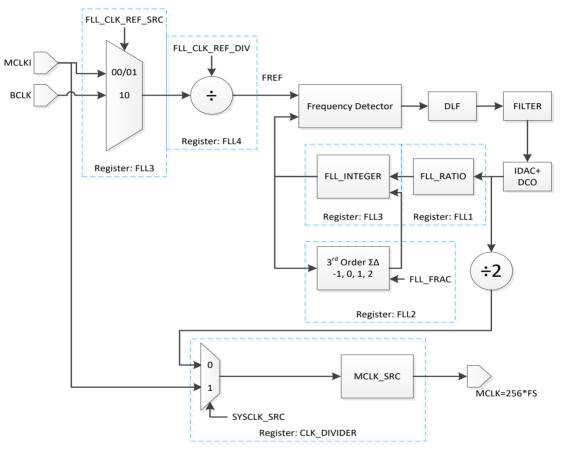

#### 6.2 Frequency Locked Loop(FLL)

Figure 14: FLL Block diagram

The integrated FLL can be used to generate a SYSMCLK from a wide variety of reference sources such as, MCLK, BCLK, and FS or as a free running clock in the absence of an external reference. It can also create a stable SYSMCLK from less stable sources due to its tolerance of jitter.

The FLL output frequency is determined by the following parameters.

- FLL\_RATIO based on input clock frequency

- MCLK\_SRC Divider

- FLL\_INTEGER: 10 bit Integer Input

- FLL\_FRAC: 16 bit Fractional Input

- FLL\_CLK\_REF\_DIV Divider

To determine these settings, the following output frequency equations are used.

- 1. FDCO = (FREF / FLL\_CLK\_REF\_DIV) X FLL\_INTEGER.FLL\_FRAC X FLL\_RATIO

- 2.  $MCLK = (FDCO X MCLK_SRC) / 2$

Where FREF is the reference clock frequency for FLL, MCLK is the desired system frequency, and FDCO is the frequency of DCO in decimal.

#### Example:

If the reference frequency (FREF) is 12MHz, the desired sampling rate (Fs) is 48 kHz, and SYSCLK = 256Fs, what are the output frequency parameters?

Using these requirements, the following can be determined.

- MCLK = 256 × 48kHz = 12.288MHz

- Using Equation 2:

FDCO =

- FDCO = 2 X MCLK / MCLK\_SRC = 2 X 12.288MHz X MCLK\_SRC

- For FDCO to remain between 90MHz 100MHz, MCLK\_SRC must be chosen to be 1/4. This and other values for MCLK\_SRC can be seen on the register tables.

- FDCO = (2 × 12.288MHz) / (1/4) = 98.304MHz

- Using Equation 1:

0

- FLL\_INTEGER.FLL\_FRAC = FDCO X FLL\_CLK\_REF\_DIV / (FREF X FLL\_RATIO)

- FDCO = 98.304MHz

- FLL\_RATIO = 1 because of FREF ≥ 512 kHz.

- FLL\_CLK\_REF\_DIV = 1 since FREF = MCLKI (12MHz)

- FLL\_INTEGER.FLL\_FRAC = 98.304MHz X 1 / (12MHz X 1) = 8.192

- Now retrieve or convert the parameter values into their corresponding HEX values

- FLL\_RATIO = 1 (for input clock frequency  $\geq$  512Khz)

- $\circ$  MCLK\_SRC = 1/4

- FLL\_INTEGER = 8

- FLL\_FRAC = 0.192 = 12583 (0.192 X 2^16) = 24'h3126

#### Please Note:

- FLL\_CLK\_REF\_DIV can be used to reduce the reference frequency for SYSMCLK by dividing the input by 1, 2, 4, or 8. Use this to ensure the reference clock frequency is less than or equal to 13.5MHz.

- FDCO must be within the 90MHz 100MHz or the FLL cannot be guaranteed across the full range of operation.

- FLL\_FRAC must be set to 0 for low power mode.

- FLL6.SDM\_EN REG0X09[14] to create decimal part of frequency, if (DCO frequency)/(FLL input reference frequency) is not a integer. If the ratio is integer, it still can be on for lower noise output but higher power consumption.

- When FLL uses free running mode, NAU88L21 needs to be set as a master in I2S\_PCM\_CTRL2.MS0 REG0X1D[3]=1

- Set FLL6.CHB\_FILTER\_EN REG0X08[14] = '1' to enable FLL Loop Filter. Select filter clock source by FLL6.CHB\_FILTER¬\_EN REG0X08[13]. Select DCO input by FLL6.FILTER\_SW REG0X08[12]. FLL6.CUTOFF500 REG0X09[13] & FLL6.CUTOFF600 REG0X09[12] can be used to define FLL cuttoff frequency at 500KHz or 600KHz. 500KHz will provide the best FLL performance but consume more power.

- set FLL6.FLL\_FLTR\_DITHER\_SEL REG0X09[7:6] = '01' or '10' or '11' as 1LSB / 2LSB / 3LSB random bits to Randomize the number of Filter Output Bits to average out output noise. If '00', there is no dither.

## 7. Control Interfaces

The NAU88L21 includes a serial control bus that provides access to all the device control registers, it may be configured as a 2-wire interface that conforms to industry standard implementations of the I<sup>2</sup>C serial bus protocol.

### 7.1 2-Wire-Serial Control Mode (I<sup>2</sup>C Style Interface)

The 2-wire bus is a bidirectional serial bus protocol. This protocol defines any device that sends data onto the bus as a transmitter (or master), and any device receiving data as the receiver (or slave). The NAU88L21 can function only as a slave when in the 2-wire interface configuration.

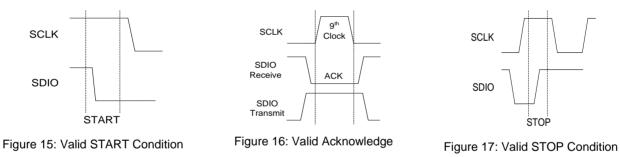

#### 7.2 2-Wire Protocol Convention

All 2-Wire interface operations must begin with a START condition, which is a HIGH-to-LOW transition of SDIO while SCLK is HIGH. All 2-Wire interface operations are terminated by a STOP condition, which is a LOW to HIGH transition of SDIO while SCLK is HIGH. A STOP condition at the end of a read or write operation places the device in a standby mode.

An acknowledge (ACK), is a software convention used to indicate a successful data transfer. To allow for the ACK response, the transmitting device releases the SDIO bus after transmitting eight bits. During the ninth clock cycle, the receiver pulls the SDIO line LOW to acknowledge the reception of the eight bits of data.

Following a START condition, the master must output a device address byte. This consists of a 7-bit device address, and the LSB of the device address byte is the R/W (Read/Write) control bit. When R/W=1, this indicates the master is initiating a read operation from the slave device, and when R/W=0, the master is initiating a write operation to the slave device. If the device address matches the address of the slave device, the slave will output an ACK during the period when the master allows for the ACK signal.

Please Note:

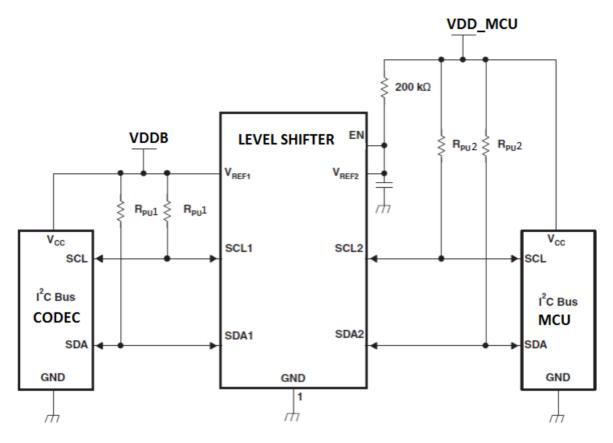

Sometimes, I2C needs to use level shifter between different supplies domains. During Acknowledge, such as Figure 16, receiver side (CODEC) will pull low, and transmit side (MCU) is disable and pull high by pull high resistor. Because NAU88L21 SDIO can sink 2mA by default setting (maximum up to 8mA,) shown as below Figure 18, RPU1 and RPU2 need to be select such that total current VDDB/RPU1+ VDD\_MCU/RPU2 during Acknowledge should not be too large to exceed SDIO sinking capability.

Figure 18: Typical I2C level shifter circuit

#### 7.3 2-Wire Write Operation

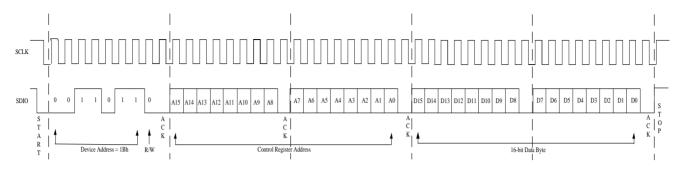

A Write operation consists of a three-byte instruction followed by one or more Data Bytes. A Write operation requires a START condition, followed by a valid device address byte with R/W=0, a valid control address byte, data byte(s), and a STOP condition.

The Device Address of the NAU88L21 is either 0x1B (CSB=0) or 0x54 (CSB=1). If the Device Address matches this value, the NAU88L21 will respond with the expected ACK signaling as it accepts the data being transmitted to it.

| 0   | 0   | I   | L   | 0   | 1   | 1  | R/W |

|-----|-----|-----|-----|-----|-----|----|-----|

|     |     |     |     |     |     |    |     |

| A15 | A14 | A13 | A12 | A11 | A10 | A9 | A8  |

|     |     |     |     |     |     |    |     |

| A7  | A6  | A5  | A4  | A3  | A2  | A1 | A0  |

|     |     |     |     |     |     |    |     |

| D15 | D14 | D13 | D12 | D11 | D10 | D9 | D8  |

|     |     |     |     |     |     |    |     |

| D7  | D6  | D5  | D4  | D3  | D2  | DI | D0  |

Figure 19: Slave Address Byte, Control Address Byte, and Data Byte

Figure 20:2-Wire Write Sequence

## 7.4 2-Wire Read Operation

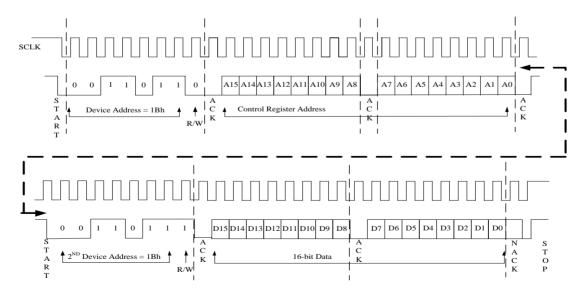

A Read operation consists of a three-byte Write instruction followed by a Read instruction of one or more data bytes. The bus master initiates the operation issuing the following sequence: a START condition, device address byte with the R/W bit set to "0", and a Control Register Address byte. This indicates to the slave device which of its control registers is to be accessed.

If the device address matches this value, the NAU88L21 will respond with the expected ACK signaling as it accepts the Control Register Address being transmitted into it. After this, the master transmits a second START condition, and a second instantiation of the same device address, but now with R/W=1.

After again recognizing its device address, the NAU88L21 transmits an ACK, followed by a two byte value containing the 16 bits of data from the selected control register inside the NAU88L21.

During this phase, the master generates the ACK signaling with each byte transferred from the NAU85L40. If there is no STOP signal from the master, the NAU88L21 will internally auto-increment the target Control Register Address and then output the two data bytes for this next register in the sequence.

This process will continue as long as the master continues to issue ACK signaling. If the Control Register Address being indexed inside the NAU88L21 reaches the value 0xFFFF (hexadecimal) and the value for this register is output, the index will roll over to 0x0000. The data bytes will continue to be output until the master terminates the read operation by issuing a STOP condition.

Figure 21:2-Wire Read Sequence

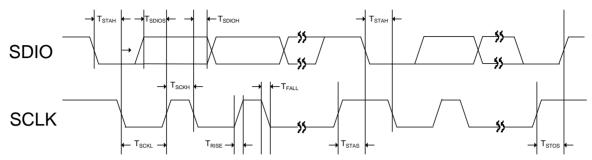

| Figure 22: T | wo-wire Contro | ol Mode Timing |

|--------------|----------------|----------------|

|--------------|----------------|----------------|

| Symbol             | Description                                                                             | min   | typ | max | unit |

|--------------------|-----------------------------------------------------------------------------------------|-------|-----|-----|------|

| TSTAH              | SDIO falling edge to SCLK falling edge hold timing in<br>START / Repeat START condition | 600   | -   | -   | ns   |

| Tstas              | SCLK rising edge to SDIO falling edge setup timing in<br>Repeat START condition         |       | -   | -   | ns   |

| Tstos              | SCLK rising edge to SDIO rising edge setup timing in<br>STOP condition                  | 600   | -   | -   | ns   |

| Тѕскн              | SCLK High Pulse Width                                                                   | 600   | -   | -   | ns   |

| T <sub>SCKL</sub>  | SCLK Low Pulse Width                                                                    | 1,300 | -   | -   | ns   |

| TRISE              | Rise Time for all 2-wire Mode Signals                                                   | -     | -   | 300 | ns   |

| T <sub>FALL</sub>  | Fall Time for all 2-wire Mode Signals                                                   | -     | -   | 300 | ns   |

| T <sub>SDIOS</sub> | SDIO to SCLK Rising Edge DATA Setup Time                                                | 100   | -   | -   | ns   |

| T <sub>SDIOH</sub> | SCLK falling Edge to SDIO DATA Hold Time                                                | 0     | -   | 600 | ns   |

#### 7.6 Software Reset

The NAU88L21 and all of its control registers can be reset to "default", initial conditions by writing any value to REG0X00 using the two-wire interface mode.

## 8. Digital Audio Interfaces

The NAU88L21 can be configured as either the master or the slave, and the Slave mode is the default if this bit is not written. In master mode, NAU88L21 outputs both Frame Sync (FS) and the audio data bit clock (BCLK) and has full control of the data transfer. In the slave mode, an external controller supplies BCLK and FS. Data is latched on the rising edge of BCLK; SDO clocks out ADC data, while SDI clocks in data for the DACs.

When not transmitting data, SDO pulls LOW in the default state. Depending on the application, the output can be configured to pull up or pull down. When the time slot function is enabled (see below), there are additional output state modes including controlled tristate capability.

NAU88L21 supports six audio formats; right justified, left justified, I2S, PCMA, PCMB, and PCM Time Slot.

#### 8.1 Right-Justified Audio Data

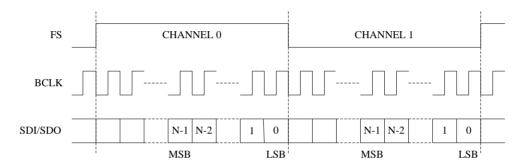

In right-justified mode, the LSB is clocked on the last BCLK rising edge before FS transitions. When FS is HIGH, channel\_0 data is transmitted and when FS is LOW, channel\_1 data is transmitted. This can be seen in the image below.

Figure 23: Right-Justified Audio Interface

#### 8.2 Left-Justified Audio Data

In left-justified mode, the MSB is clocked on the first BCLK rising edge after FS transitions. When FS is HIGH, channel\_0 data is transmitted and when FS is LOW, channel\_1 data is transmitted. This can be seen in the figure below.

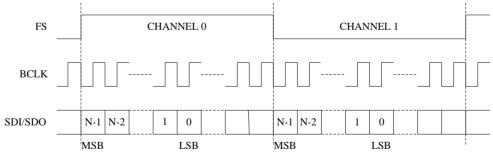

#### 8.3 I2S Audio Data

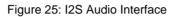

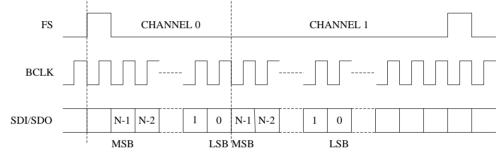

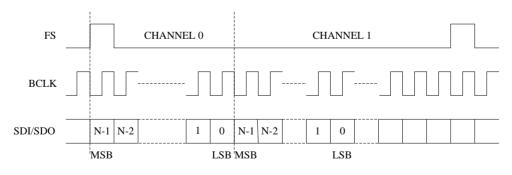

In I<sup>2</sup>S mode, the MSB is clocked on the second BCLK rising edge after FS transitions. When FS is LOW, left channel data is transmitted and when FS is HIGH, right channel data is transmitted. This can be seen in the figure below.

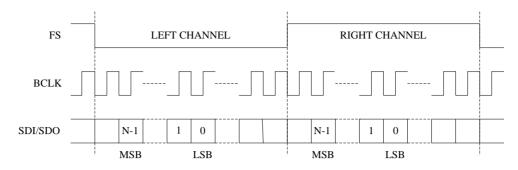

## 8.4 PCMA Audio Data

In the PCM A mode, channel 0 data is transmitted first followed immediately by channel 1 data. The channel 0 MSB is clocked on the second BCLK rising edge after the FS pulse rising edge, and channel 1 MSB is clocked on the next BCLK after the left channel LSB. This can be seen in the figure below.

Figure 26: PCMA Audio Interface

#### 8.5 PCMB Audio Data

In the PCMB mode, channel\_0 data is transmitted first followed immediately by channel\_1 data. Channel 0 MSB is clocked on the first BCLK rising edge after the FS pulse rising edge, and channel\_1 MSB is clocked on the next BCLK after channel\_0 LSB. This can be seen in the figure below.

Figure 27: PCMB Audio Interface

#### 8.6 PCM Time Slot Audio Data

The PCM time slot mode is used to allocate different time slots for ADC and DAC data. This can be useful when multiple NAU88L21 chips or other devices are sharing the same audio bus. This will allow each chip's audio to be delayed around each other without interference.

Normally, the DAC and ADC data are clocked immediately after the Frame Sync (FS), however, in the PCM time slot mode; the audio data can be delayed by left / right channel PCM time slot start value in the registers.

These delays can be seen before the MSB in the figure below.

Figure 28: PCM Time Slot Audio Interface

The PMC time slot mode can be also used to swap channel 0 and channel 1 audio or cause both channels to use the same data. When using the NAU88L21 with other driver chips, the SDO pin can be set to pull up or pull down or high impedance during no transmission. Tri-stating on the negative edge allows the transmission of data by multiple sources in adjacent timeslots with reduced risk of bus driver contention.

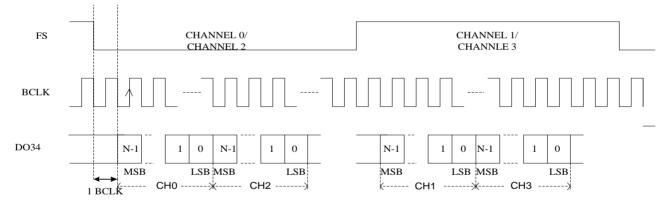

#### 8.7 TDM I2S Audio Data

In I2S mode, the MSB is clocked on the second BCLK rising edge after FS transitions. When FS is LOW, channel\_0 then channel\_2 data is transmitted and when FS is HIGH, channel\_1 then channel\_3 data is transmitted. This is shown in the figure below.

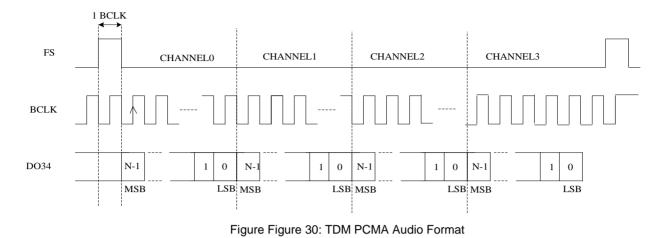

#### 8.8 TDM PCMA Audio Data

In the PCMA mode, channel\_0 data is transmitted first followed sequentially by channel\_1, 2, and 3 immediately after. The channel\_0 MSB is clocked on the second BCLK rising edge after the FS pulse rising edge, and the subsequent channel's MSB is clocked on the next BCLK after the previous channel's LSB. This is shown in the figure below.

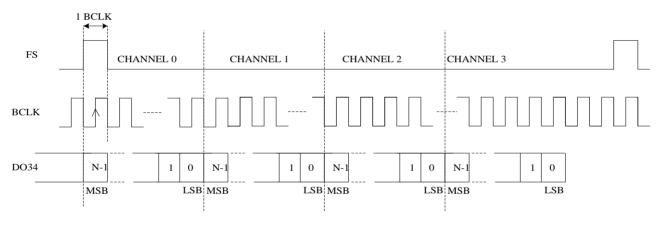

#### 8.9 TDM PCMB Audio Data

In TDM PCMB mode, channel\_0 data is transmitted first followed immediately by channel\_1 data. The channel\_0 MSB is clocked on the first BCLK rising edge after the FS pulse rising edge, and channel\_1 MSB is clocked on the next SCLK after channel\_0 LSB.

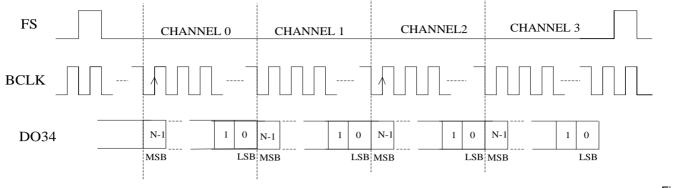

#### 8.10 TDM PCM Offset Audio Data

The PCM offset mode is used to delay the time at which DAC data is clocked. This increases the flexibility of the NAU88L21 to be used in a wide range of system designs. One key application of this feature is to enable multiple NAU88L21 or other devices to share the audio data bus, thus enabling more than four channels of audio. This feature may also be used to swap channel data, or to cause multiple channels to use the same data.

Normally, the DAC data are clocked immediately after the Frame Sync (FS). In this mode audio data is delayed by a delay count specified in the device control registers. The channel 0 MSB is clocked on the BCLK rising edge defined by the delay count set in .This can be seen in the figure below.

Figure 32: TDM PCM Offset Audio Format

#### 9. Outputs

The NAU88L21 provides a pair of Class G ground-reference headphone outputs.

#### 9.1 Class G Headphone Driver and Charge Pump

The NAU88L21 uses Class G speaker drivers powered by a charge pump for the headphones. For typical operation with large and small signals the charge pump provides  $\pm 1.8$ V and  $\pm 0.9$ V, respectively. These output drivers are driven by dedicated left and right DACs and can provide 30mW of power to a 32 $\Omega$  load (in CSP package).

Three capacitors are needed to generate the negative voltage from the positive 1.8V. Typically, 2µF ceramic capacitors are used.

- The Fly Back capacitor is connected between pins CPCA and CPCB.

- The Positive Output Decoupling capacitor is applied from pin CPVOUTP to ground (VSSCP).

- The Negative Output Decoupling capacitor is applied from pin CPOUTN to ground (VSSCP).

The Class G will be turned on only if DAC signal level is bigger than the threshold in the register settings, and the peak output can be also configured differently by register settings.

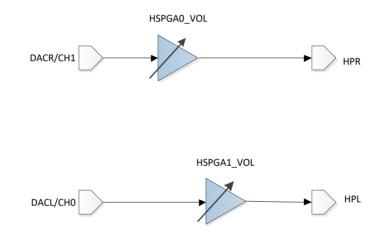

Figure 33: DAC to Headphone out path diagram

## 10. Control and Status Registers

| R      |                  |                   |        |        |        |        | -      |        |   | В | it |   |   |   |   |   |   |   |                                                                                                                   |

|--------|------------------|-------------------|--------|--------|--------|--------|--------|--------|---|---|----|---|---|---|---|---|---|---|-------------------------------------------------------------------------------------------------------------------|

| E<br>G | Function         | Name              | 1<br>5 | 1<br>4 | 1<br>3 | 1<br>2 | 1<br>1 | 1<br>0 | 9 | 8 | 7  | 6 | 5 | 4 | 3 | 2 | 1 | 0 | Description                                                                                                       |

| 0      | HARDWA<br>RE_RST | RESET_N1          |        |        |        |        |        |        |   |   |    |   |   |   |   |   |   |   | Hardware Reset<br>Write any value <b>once</b> to reset all the registers.                                         |

|        |                  | CMLCK_ENB         |        |        |        |        |        |        |   |   |    |   |   |   |   |   |   |   | PGA Common Mode Lock; '0'=enabled, '1'=disabled                                                                   |

|        |                  | CLK_DAC_IN<br>V   |        |        |        |        |        |        |   |   |    |   |   |   |   |   |   |   | DAC clock inversion in analog domain<br>1 = Enable<br>0 = Disable                                                 |

|        |                  | RDACEN            |        |        |        |        |        |        |   |   |    |   |   |   |   |   |   |   | Right Channel DAC Enable<br>1 = ON<br>0 = OFF                                                                     |

|        |                  | LDACEN            |        |        |        |        |        |        |   |   |    |   |   |   |   |   |   |   | Left Channel DAC Enable<br>1 = ON<br>0 = OFF                                                                      |

|        |                  | RADCEN            |        |        |        |        |        |        |   |   |    |   |   |   |   |   |   |   | Right Channel ADC Enable<br>1 = ON<br>0 = OFF<br>Left Channel ADC Enable                                          |

|        |                  | LADCEN            |        |        |        |        |        |        |   |   |    |   |   |   |   |   |   |   | 1 = ON<br>0 = OFF<br>ADC Clock Enable                                                                             |

| 1      | ENA_CTR<br>L     | DCLK_ADC_E<br>N   |        |        |        |        |        |        |   |   |    |   |   |   |   |   |   |   | 1 = ON<br>0 = OFF<br>DAC Clock Enable                                                                             |

|        |                  | DCLK_DAC_E<br>N   |        |        |        |        |        |        |   |   |    |   |   |   |   |   |   |   | 1 = ON<br>0 = OFF<br>IMM Clock Enable                                                                             |

|        |                  | CLK_IMM_EN        |        |        |        |        |        |        |   |   |    |   |   |   |   |   |   |   | 1 = ON<br>0 = OFF<br>12S Clock Enable                                                                             |

|        |                  | CLK_I2S_EN        |        |        |        |        |        |        |   |   |    |   |   |   |   |   |   |   | 1 = ON<br>0 = OFF<br>BIST Clock Enable                                                                            |

|        |                  | CLK_BIST_EN       |        |        |        |        |        |        |   |   |    |   |   |   |   |   |   |   | 1 = ON         0 = OFF           OTP Clock Enable                                                                 |

|        |                  | CLK_OTP_EN        |        |        |        |        |        |        |   |   |    |   |   |   |   |   |   |   | 0 = OFF<br>DRC Clock Enable                                                                                       |

|        |                  | CLK_DRC_EN        |        |        |        |        |        |        |   |   |    |   |   |   |   |   |   |   | 1 = ON<br>0 = OFF                                                                                                 |

|        |                  | Default           | 0      | 0      | 0      | 0      | 0      | 0      | 0 | 0 | 1  | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0x00ff                                                                                                            |