# **CX24118A**

# Advanced Modulation Digital Satellite Tuner Rev. 02 — 8 September 2009

Product data sheet

#### **Document information**

| Info     | Content |

|----------|---------|

| Keywords |         |

| Abstract |         |

## **Advanced Modulation Digital Satellite Tuner**

#### **Ordering information**

| Type number                   | Description                                 | Package    |

|-------------------------------|---------------------------------------------|------------|

| CX24118A-12Z*                 | Advanced Modulation Digital Satellite Tuner | 36-pin QFN |

| *Lead-free (Pb Free) and RoH! | S compliant                                 |            |

#### **Revision history**

| Revision | Date     | Description                                                 |

|----------|----------|-------------------------------------------------------------|

| 02       | 20090908 | Added Figure 12                                             |

| 01       | 20081125 | First NXP version based on the Conexant 102322A data sheet. |

## **Contact information**

For more information, please visit: http://www.nxp.com

For sales office addresses, please send an email to: <a href="mailto:salesaddresses@nxp.com">salesaddresses@nxp.com</a>

#### **Advanced Modulation Digital Satellite Tuner**

### **General description**

The CX24118A is a direct down-conversion satellite tuner intended for high-volume digital video, audio, and data receivers. The CX24118A offers excellent phase noise performance and very low implementation loss, required for advanced modulation systems such as 8PSK and DVB-S2.

The CX24118A has a built-in auto-tuning system that eliminates the need for software calibration. The on-chip fractional synthesizer enables fine frequency step size without adversely affecting lock time. The CX24118A does not require a balun, thus reducing external BOM cost. Its highly integrated design saves valuable board space and simplifies RF layout.

#### **Features**

- ◆ Single-chip RF-to-baseband satellite receiver

- Zero-IF architecture eliminates the need for image reject filtering

- Very low phase noise integrated Local Oscillators (LOs) for 8PSK and DVB-S2 applications

- Variable baseband filters for optimal interference rejection

- Auto-tuning system eliminates need for software calibration

- Very low power consumption

- Small (6 mm x 6 mm) footprint

- ◆ Lead-free package

## **Applications**

- 8PSK, DVB-S2, and advanced modulation set-top boxes

- Commercial digital video, audio, and PVR receivers

### **Product Specifications**

RF input: 925–2175 MHz

Symbol rate: 1–45 MSps

Noise figure: 10 dB, typical

Input IP3 at minimum gain: 10 dBm, typical

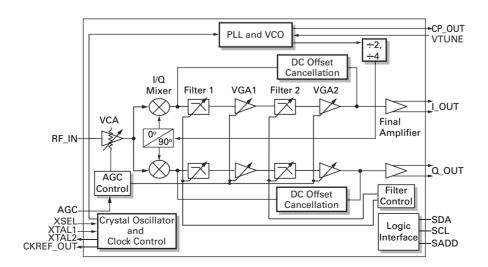

## **Block diagram**

| 1      | Pin Descriptions                                   | 11 |

|--------|----------------------------------------------------|----|

| 1.1    | Pin Diagram                                        | 11 |

| 1.2    | Pin Assignments                                    |    |

| 2      | Functional Descriptions                            | 15 |

| 2.1    | General Description                                | 15 |

| 2.2    | Downconverter and Baseband Filtering               | 15 |

| 2.3    | Gain Settings                                      |    |

| 2.4    | Local Oscillator and PLL                           | 17 |

| 2.5    | Crystal Oscillator and Reference Clock             |    |

| 2.6    | Automatic Tuning System                            | 20 |

| 2.6.1  | Auto-tuning Procedure                              | 20 |

| 3      | Serial Programming Interface and Registers         | 23 |

| 3.1    | Serial Programming Interface                       |    |

| 3.2    | Registers                                          |    |

| 3.3    | Register Index                                     |    |

| 3.4    | Register Detail                                    |    |

| 4      | Application Information                            |    |

| 4.1    | Thermal Recommendations                            | 37 |

| 4.2    | Sleep Mode Procedures                              |    |

| 4.2.1  | Changing from Normal Operation to Sleep Mode       |    |

| 4.2.2  | Changing from Sleep Mode to Normal Operation       |    |

| 5      | Electrical, Thermal, and Mechanical Specifications |    |

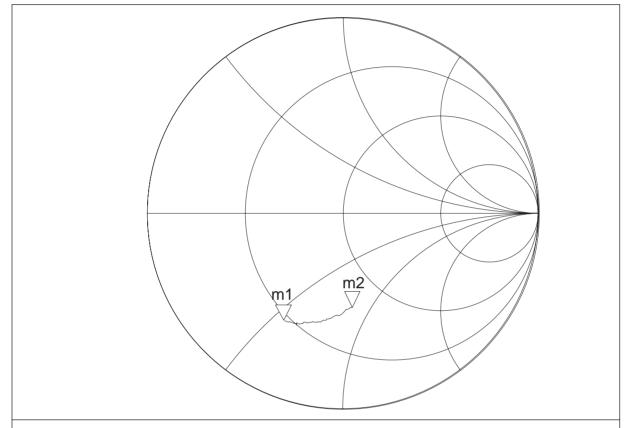

| 5.1    | S11 Plot                                           |    |

| 5.2    | Electrical and Thermal Specifications              |    |

| 5.2.1  | Absolute Maximum Ratings                           |    |

| 5.2.2  | Recommended Operating Conditions                   |    |

| 5.2.3  | Receiver Electrical and Thermal Specifications     |    |

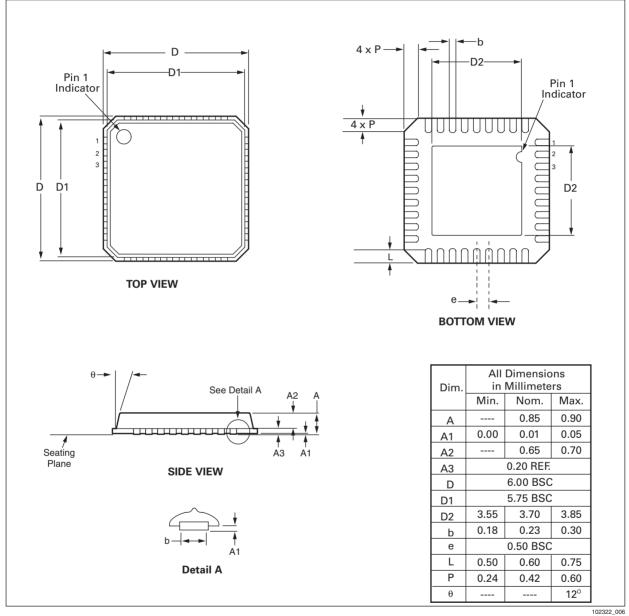

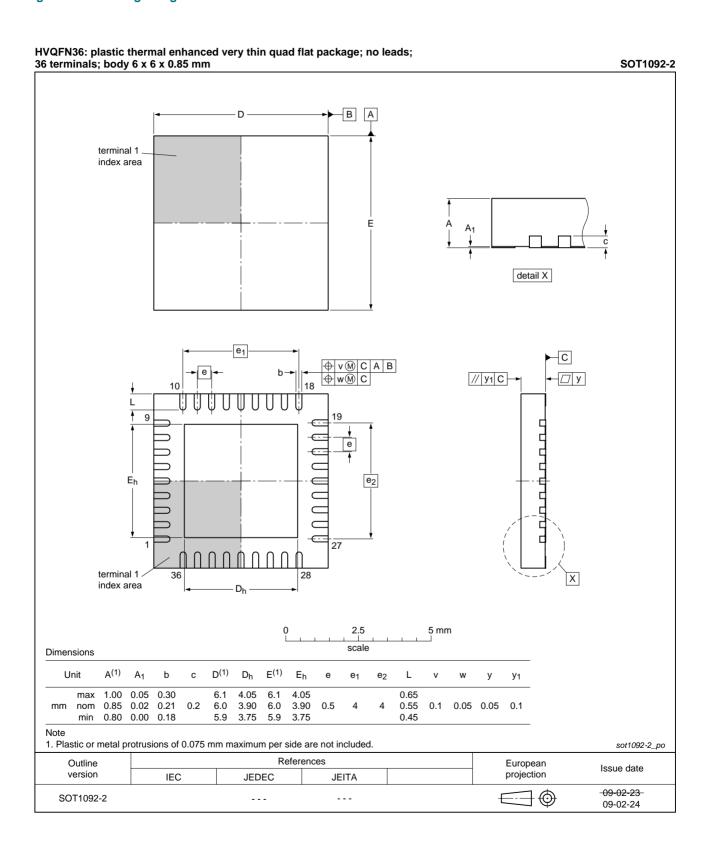

| 5.3    | Mechanical Specifications                          |    |

| l egal | information                                        | 45 |

| Fig. 1  | Pin Diagram                                                          | 11 |

|---------|----------------------------------------------------------------------|----|

| Fig. 2  | Detailed Block Diagram                                               | 15 |

| Fig. 3  | Recommended Divider Settings vs. Frequency When Using 40 MHz Crystal | 18 |

| Fig. 4  | Third-Overtone Crystal Oscillator External Circuit                   | 19 |

| Fig. 5  | Serial Clock and Data Signals                                        | 23 |

| Fig. 6  | Typical Single-Byte Write Procedure                                  | 24 |

| Fig. 7  | Typical Multiple-Bytes Write Procedure                               | 24 |

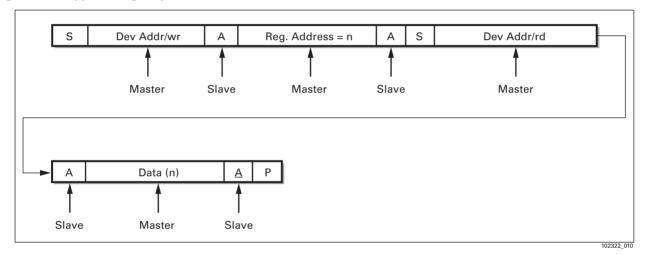

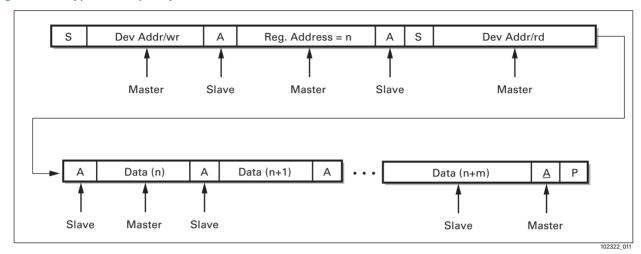

| Fig. 8  | Typical Single-Byte Read Procedure                                   |    |

| Fig. 9  | Typical Multiple-Bytes Read Procedure                                | 26 |

| Fig. 10 | S11 Plot                                                             | 39 |

| Fig. 11 | Package Diagram                                                      | 43 |

| Fig. 12 | Package Diagram                                                      | 44 |

| Table 1.  | Pin Assignments                                                                     | 12 |

|-----------|-------------------------------------------------------------------------------------|----|

| Table 2.  | Maximum Signal Level Settings                                                       | 16 |

| Table 3.  | Minimum Signal Level Settings                                                       | 17 |

| Table 4.  | Recommended Component Values for Third-Overtone Crystal Oscillator External Circuit | 19 |

| Table 5.  | Crystal Requirements                                                                | 20 |

| Table 6.  | Register Bit Map                                                                    | 26 |

| Table 7.  | Register Index                                                                      | 27 |

| Table 8.  | Thermal Recommendations                                                             | 37 |

| Table 9.  | Absolute Maximum Ratings                                                            | 40 |

| Table 10. | Recommended Operating Conditions                                                    | 40 |

| Table 11. | Receiver Electrical Specifications                                                  | 40 |

## **Chapter 1: Pin Descriptions**

Rev. 02 — 8 September 2009

Product data sheet

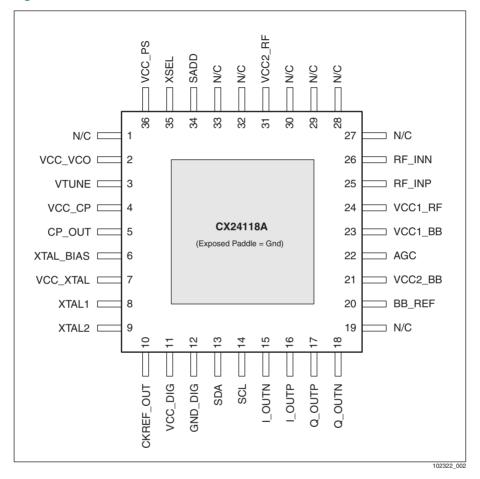

## 1.1 Pin Diagram

Figure 1 provides a pinout of the CX24118A.

Figure 1. Pin Diagram

## 1.2 Pin Assignments

Table 1 lists the CX24118A pin names, numbers, types, and descriptions.

Table 1. Pin Assignments

| Pin Name  | Pin Number | Туре   | Description                                                                                                                                                    |

|-----------|------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| N/C       | 1          | N/C    | Not internally connected.                                                                                                                                      |

| VCC_VCO   | 2          | Power  | 3.3V power supply for the VCO section.                                                                                                                         |

| VTUNE     | 3          | Input  | VCO tuning voltage input. The output of the external PLL loop filter is connected to this pin.                                                                 |

| VCC_CP    | 4          | Power  | 3.3V power supply for the charge pump section.                                                                                                                 |

| CP_OUT    | 5          | Output | Charge pump output. The input of the external PLL loop filter is connected to this pin.                                                                        |

| XTAL_BIAS | 6          | Input  | Crystal oscillator bias. For normal operation, leave this pin unconnected.                                                                                     |

| VCC_XTAL  | 7          | Power  | 3.3V power supply for the crystal oscillator section.                                                                                                          |

| XTAL1     | 8          | Input  | Crystal oscillator input pins. Use a 40 MHz or 40.444 MHz third-overtone crystal                                                                               |

| XTAL2     | 9          | Output | oscillator circuit.                                                                                                                                            |

| CKREF_OUT | 10         | Output | Clock reference output. The maximum load allowed at this pin is 10 k $\Omega$ // 20 pF.                                                                        |

| VCC_DIG   | 11         | Power  | 3.3 V power supply for digital section.                                                                                                                        |

| GND_DIG   | 12         | Ground | Digital ground.                                                                                                                                                |

| SDA       | 13         | I/O    | Serial programming interface data signal. Open drain.                                                                                                          |

| SCL       | 14         | Input  | Serial programming interface clock signal.                                                                                                                     |

| I_OUTN    | 15         | Output | The negative differential I channel output to demodulator. Zout = 1 k $\Omega$ // 10 pF.                                                                       |

| I_OUTP    | 16         | Output | The positive differential I channel output to demodulator. Zout = 1 k $\Omega$ // 10 pF.                                                                       |

| Q_OUTP    | 17         | Output | The positive differential Q channel output to demodulator. Zout = 1 k $\Omega$ // 10 pF.                                                                       |

| Q_OUTN    | 18         | Output | The negative differential Q channel output to demodulator. Zout = 1 k $\Omega$ // 10 pF.                                                                       |

| N/C       | 19         | N/C    | Not internally connected.                                                                                                                                      |

| BB_REF    | 20         | Input  | Current reference for baseband section. Place a 698 $\Omega$ ±1% resistor to ground.                                                                           |

| VCC2_BB   | 21         | Power  | 3.3 V power supply for the baseband section.                                                                                                                   |

| AGC       | 22         | Input  | AGC control input from the demodulator, which controls the gain of the RF attenuator and both baseband variable gain amplifiers. Zin = 10 k $\Omega$ // 20 pF. |

| VCC1_BB   | 23         | Power  | 3.3 V power supply for the baseband section.                                                                                                                   |

| VCC1_RF   | 24         | Power  | 3.3 V power supply pin for the RF section.                                                                                                                     |

| RF_INP    | 25         | Input  | The positive differential RF signal input pin.                                                                                                                 |

**Chapter 1: Pin Descriptions**

Table 1. Pin Assignments

| Pin Name       | Pin Number | Туре   | Description                                                                                                                                                                                             |

|----------------|------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RF_INN         | 26         | Input  | The negative differential RF signal input pin. This pin should be AC grounded with a capacitor to ground.                                                                                               |

| N/C            | 27         | N/C    | Not internally connected.                                                                                                                                                                               |

| N/C            | 28         | N/C    | Not internally connected.                                                                                                                                                                               |

| N/C            | 29         | N/C    | Not internally connected.                                                                                                                                                                               |

| N/C            | 30         | N/C    | Not internally connected.                                                                                                                                                                               |

| VCC2_RF        | 31         | Power  | 3.3 V power supply pin for the RF section.                                                                                                                                                              |

| N/C            | 32         | N/C    | Not internally connected.                                                                                                                                                                               |

| N/C            | 33         | N/C    | Not internally connected.                                                                                                                                                                               |

| SADD           | 34         | I/O    | Serial address select pin. This pin has an internal pull-up, so an open on this pin will be a logic level high (default address of 54) and a short to ground will be a logic level low (address of 14). |

| XSEL           | 35         | Input  | Crystal bias select pin. Leave floating for operation with a 40 MHz third-overtone crystal. This pin has an internal 30 k $\Omega$ pull-up resistor.                                                    |

| VCC_PS         | 36         | Power  | 3.3 V power supply for the prescaler section.                                                                                                                                                           |

| Exposed Paddle | '          | Ground | The exposed paddle at the bottom of the chip is the common chip ground and the thermal conductor.                                                                                                       |

**Chapter 1: Pin Descriptions**

## **Chapter 2: Functional Descriptions**

Rev. 02 — 8 September 2009

Product data sheet

#### 2.1 **General Description**

The CX24118A is a highly integrated direct conversion tuner requiring a minimum of off-chip components. It incorporates a low-noise amplifier with integrated Voltage Controlled Attenuator (VCA), quadrature down converter, variable bandwidth base-band filter/amplifier, fractional synthesizer, crystal oscillator with buffered output, and an automatic tuning system. The chip is controlled through a multi-byte read/write enabled I<sup>2</sup>C<sup>®</sup>-compatible interface.

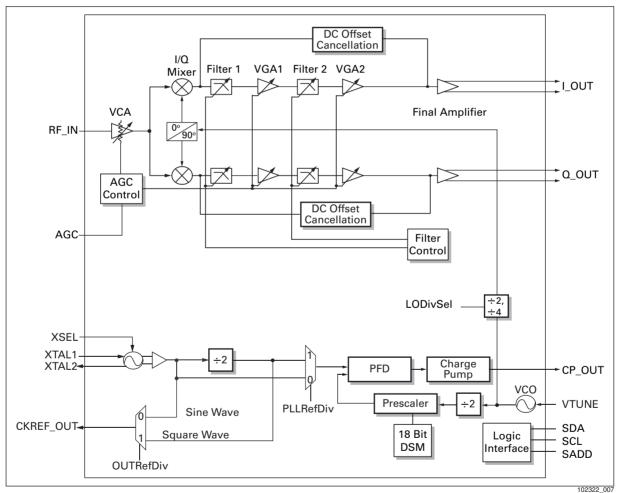

A CX24118A detailed block diagram is shown in Figure 2.

Figure 2. **Detailed Block Diagram**

#### 2.2 **Downconverter and Baseband Filtering**

The L band input from the LNB is fed into the CX24118A either differentially or single-ended. The input signal goes through a low-noise amplification block and is downconverted to a baseband frequency by quadrature downconversion. The output of the downconverter is band limited by a variable bandwidth filter that can be set to 35, 40, 65, or 100 MHz. A

CX24118A\_N\_2 © NXP B.V. 2009. All rights reserved.

#### **Chapter 2: Functional Descriptions**

variable gain baseband amplifier section provides further amplification. The baseband section includes a servo loop, which eliminates DC offset variations at the output. The baseband amplifier section also includes a filter with finer bandwidth control between 2 MHz and 65 MHz. The filter is optimized to provide stop band attenuation for anti-alias filtering and adjacent channel performance.

## 2.3 Gain Settings

The CX24118A is controlled by a single AGC signal, providing a dynamic range of 90 dB. The gain stages include an LNA (Low Noise Amplifier) and VCA (Voltage Controlled Attenuator), VGA1 (Variable Gain Amplifier 1), VGA2, and a final amplifier. These gain stages are shown in figure 2-1.

Table 2. Maximum Signal Level Settings

| Parameter      | Register Location | Register Setting | Meaning              |

|----------------|-------------------|------------------|----------------------|

| RFVCAOff[1:0]  | 0x20[3:2]         | 00b              | -70 dB               |

| BBVGA2Off[2:0] | 0x1F[5:3]         | 111b             | -27 dB               |

| BBVGA1Off[2:0] | 0x1F[2:0]         | 111b             | -22 dB               |

| BBAmpGain[3:0] | 0x1D[3:0]         | 0011b            | 31 dB <sup>(1)</sup> |

#### FOOTNOTES:

<sup>(1)</sup> This value is valid for the CX24116, CX24126, and CX24114 demodulators. For the CX24123 demodulator, use the setting that corresponds to 25 dB.

#### **Chapter 2: Functional Descriptions**

| Tubic o. Immuni digital Lovor Collings |                   |                  |                      |

|----------------------------------------|-------------------|------------------|----------------------|

| Parameter                              | Register Location | Register Setting | Meaning              |

| RFVCAOff[1:0]                          | 0x20[3:2]         | 10b              | -64 dB               |

| BBVGA2Off[2:0]                         | 0x1F[5:3]         | 011b             | -29 dB               |

| BBVGA1Off[2:0]                         | 0x1F[2:0]         | 010b             | -32 dB               |

| BBAmpGain[3:0]                         | 0x1D[3:0]         | 0011b            | 31 dB <sup>(1)</sup> |

Table 3. Minimum Signal Level Settings

#### FOOTNOTES:

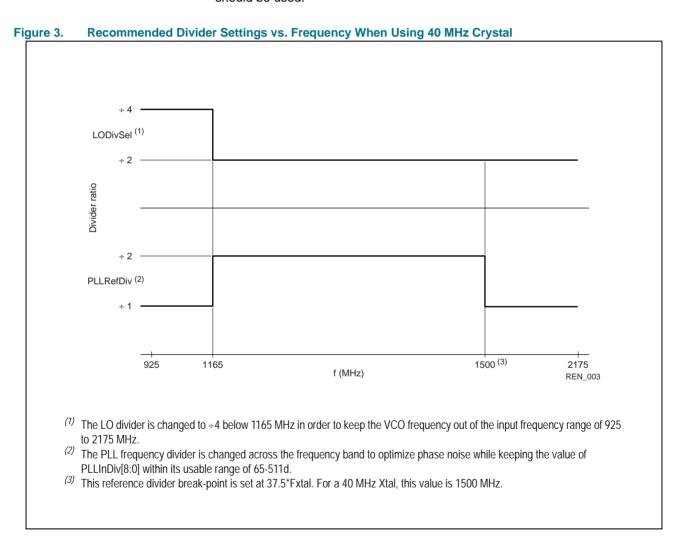

#### 2.4 Local Oscillator and PLL

A bank of six Voltage Controlled Oscillators (VCOs) cover the entire 925 MHz to 2175 MHz range for downconversion with adequate overlap between VCOs. Each VCO has two bands of operation, high and low, resulting in a total of 12 virtual VCOs. All the VCOs are integrated into the chip, eliminating the need for external varactor diodes. The automatic tuning system selects the appropriate VCO to generate the Local Oscillator (LO), eliminating the need for calibration during initialization or channel change. The VCOs can also be selected manually, overriding the automatic tuning system. For more information on the automatic tuning system, see Section 2.6

The on-chip fractional synthesizer generates the LO with a very fine step size. The fractional synthesizer consists of a 9-bit integer divider and an 18-bit sigma delta modulator with an 8-level quantizer. The sigma delta modulator dithers the fractional division ratio to convert spurious tones and quantization noise to white noise. The charge pump current selection is based on the VCO tuning voltage, i.e., VCO output frequency. The charge pump tuning system uses four tuning voltage ranges, and the charge pump current level for each range is set automatically at every channel change to give optimum integrated phase noise.

The values to be programmed into the PLL's integer and fractional divider registers are computed as follows:

- Set the dividers LODivSel (0x18[6]) and PLLRefDiv (0x02[1]) based on pre-defined or calculated frequency ranges.

- See <u>Figure 3</u> for recommended divider settings when using a 40 MHz crystal.

- 2. Calculate the total PLL division ratio.

$$\begin{split} & \text{N}_{\text{divider}} = \frac{F_{\text{VCO}} \times 1}{F_{\text{xtal}} \times 2} \text{ ; if PLLRefDiv} = 0 \\ & = \frac{F_{\text{VCO}} \times 2}{F_{\text{xtal}} \times 2} \text{ ; if PLLRefDiv} = 1 \end{split}$$

3. Calculate the integer divider PLLIntDiv[8:0].

$$PLLIntDiv[8:0] = Round[N_{divider}] - 32$$

- The Round function rounds the result to the nearest integer.

- PLLIntDiv[8:0] can range from 6d to 511d. This is taken into consideration when selecting the divider ranges.

CX24118A\_N\_2 © NXP B.V. 2009. All rights reserved

<sup>(1)</sup> This value is valid for the CX24116, CX24126, and CX24114 demodulators. For the CX24123 demodulator, use the setting that corresponds to 25 dB.

#### **Chapter 2: Functional Descriptions**

4. Calculate the fractional divider PLLFracDiv[17:0].

PLLFracDiv[17:0] = Round  $[2^{18} \times (N_{divider} - PLLIntDiv[8:0] - 32)]$

- To avoid fractional spurs, the fractional divider should not produce VCO frequencies within 250 kHz or 125 kHz of the frequencies generated by PLLFracDiv[17:0] = 0.0 or 0.5 respectively.

- When the requested frequency is within 250 kHz of the frequency generated by PLLFracDiv[17:0] = 0.0, the PLL should be put into integer mode. Integer mode is enabled by setting register bit DSMByp (0x10[6]) to 1.

- When the requested frequency is within 125 kHz of the frequency generated by PLLFracDiv[17:0] = 0.5, the closest fractional value outside of the keep-out range should be used.

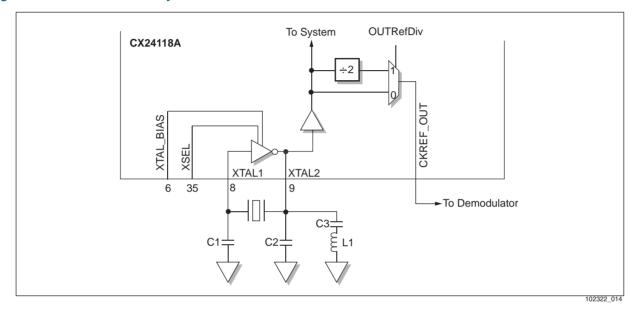

## 2.5 Crystal Oscillator and Reference Clock

The crystal oscillator should be used with a 40 MHz or 40.444 MHz third-overtone crystal. It generates the reference frequency for the fractional synthesizer and provides the clock for the rest of the system. It is also divided and buffered to produce an external clock that can be used as a clock signal for the demodulator. Register bit OutRefDiv (0x02[2]) sets the frequency of the reference clock output at pin CKREF\_OUT so that when OUTRefDiv = 0, a

#### **Chapter 2: Functional Descriptions**

40 MHz sinusoidal clock is produced, and when OUTRefDiv = 1, a 20 MHz square clock is produced (when OUTRefDiv = 1 mode is used, the XTAL\_BIAS pin needs to be grounded).

The third overtone crystal requires external circuitry to load the crystal properly at the thirdovertone frequency while suppressing the fundamental frequency. This circuit is shown in <u>Figure 4</u>, and the recommended component values are listed in <u>Table 4</u>. The external components should be RF type components (high Q) with good characteristics at 40 MHz.

Figure 4. Third-Overtone Crystal Oscillator External Circuit

Table 4. Recommended Component Values for Third-Overtone Crystal Oscillator External Circuit

| Component      | Value  |

|----------------|--------|

| $C_1$          | 22 pF  |

| $C_2$          | 56 pF  |

| $C_3$          | 1 nF   |

| L <sub>1</sub> | 390 nH |

The selected crystal should be a high-quality crystal with minimum drive level dependencies. <u>Table 5</u> lists the required crystal characteristics. Component tolerances should be 5 percent or better.

Table 5. Crystal Requirements

| Parameter                                      | Specification                           |

|------------------------------------------------|-----------------------------------------|

| Frequency                                      | 40.000 MHz (40.444 MHz <sup>(3)</sup> ) |

| Mode                                           | Parallel resonant, 3rd overtone         |

| Frequency tolerance at 25 °C                   | 25 ppm                                  |

| Frequency tolerance over temperature           | 50 ppm                                  |

| Maximum equivalent series resistance (ESR) (7) | 80                                      |

| Aging                                          | 5 ppm/Year                              |

| Load Capacitance                               | 18 pF                                   |

| Maximum Drive Level <sup>(2)</sup>             | 1 mW                                    |

| Operating Temperature Range                    | 0 °C to 70 °C                           |

#### FOOTNOTES:

## 2.6 Automatic Tuning System

The CX24118A uses an automatic tuning system to select the VCO and band during channel change. The system selects among the 12 virtual VCOs (VCO1–VCO6, each with a high and low band) based on preload values that are programmed during initialization. The automatic tuning system does not require time-consuming calibration during initialization or channel change. The procedure for using the automatic tuning system is given in <a href="Section 2.6.1">Section 2.6.1</a>.

#### 2.6.1 Auto-tuning Procedure

#### **During Initialization**

- Program the tuning system preload values with the values provided by Conexant and enable the automatic tuning system.

- a. Set register field TUN1[5:0] (0x14[5:0]) to 0x0F.

- Register 0x14 also contains the tuning system enable bits, TUNAutoEn[1:0], which should be programmed to 00b at the same time.

- b. Set register TUN2[7:0] (0x15[7:0]) to 0xFF.

- c. Set register TUN3[7:0] (0x16[7:0]) to 0xFF.

- d. Set register TUN4[7:0] (0x17[7:0]) to 0xF0.

- Program automatic charge pump levels with the values provided by Conexant. These values are selected based on the VCO tuning voltage.

- a. Set register field CPLevel1[1:0] (0x11[7:6]) to 11b.

- b. Set register field CPLevel2[1:0] (0x11[5:4]) to 11b.

- c. Set register field CPLevel3[1:0] (0x11[3:2]) to 10b.

CX24118A\_N\_2 © NXP B.V. 2009. All rights reserved

<sup>(1)</sup> This is the maximum crystal series resistance for reliable startup at low energy levels. Compliance with this spec at 10 nW is required. This number is also required at operating power levels.

<sup>(2)</sup> The power dissipated across the crystal will depend on the ESR of the crystal and the bias level of the oscillator. Leaving the XTAL\_BIAS pin open will create a lower bias current than if it were shorted to ground.

<sup>(3)</sup> A 40.444 MHz crystal is only needed when DVB symbol rates of 44–45 MSps are required for the CX24116 DVB-S2 demodulator.

#### **Chapter 2: Functional Descriptions**

- d. Set register field CPLevel4[1:0] (0x11[1:0]) to 00b.

- 3. There are other registers not directly related to tuning system initialization that must also be programmed. These values are not discussed here.

#### **During Channel Change**

- 1. Choose the appropriate dividers using register bits LODivSel (0x18[6]) and PLLRefDiv (0x02[1])). For more detail, see Section 2.4

- 2. Select the gain settings. The minimum signal level settings can be used at this point.

- 3. Set the bandwidths of the baseband filters using register fields BBFil1BW[1:0] and BBFil2BW[1:0] based on the symbol rate, roll-off, and desired carrier acquisition range.

- 4. Program the PLL dividers PLLIntDiv[8:0] and PLLFracDiv[17:0] using the values generated from the procedure given in <u>Section 2.4</u>, and start the tuning process as follows:

- a. Program registers 0x19-0x1B.

- b. Program the remaining PLL dividers into register 0x1C while setting the start bit TUNReset (0x1C[4]) to 1.

- Monitor PLL lock using register bit TUNLD. When lock has been achieved, measure the power to determine the appropriate gain settings. Set new gain settings if required. See Section 2.3 for more detail.

- a. After lock, the charge pump values are automatically selected, based on the VCO tuning voltage and the charge pump initialization values.

**Chapter 2: Functional Descriptions**

## CX24118A

## **Chapter 3: Serial Programming Interface and Registers**

Rev. 02 — 8 September 2009

Product data sheet

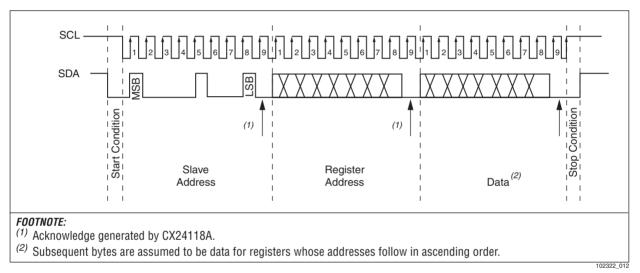

### 3.1 Serial Programming Interface

The CX24118A uses an I<sup>2</sup>C-compatible serial interface. The serial clock and data lines, SCL and SDA, are used to transfer data at a clock rate of up to 1 MHz. A direct, exclusive connection is preferred between controlling master and the tuner slave. If the chip is put on a common I<sup>2</sup>C bus shared by other devices, the ongoing traffic on the bus may cause RF interference. Both lines operate on 3.3 V I/O voltage levels. The SDA line is open drain, requiring an external pull-up resistor.

The serial clock and data signals for a typical transaction is shown in Figure 5.

Figure 5. Serial Clock and Data Signals

The START condition occurs on the falling edge of the SDA line when the SCL line is held high. A STOP condition occurs on the rising edge of the SDA line when the SCL line is held high. Every data word is 8 bits long with MSB first, followed by an acknowledge bit generated by the receiving device. Each data transaction occurs between a START and a STOP condition. The START condition is followed by a slave address. If this is the CX24118A address, it generates an acknowledge bit on the SDA line.

The following are some typical read/write sequences:

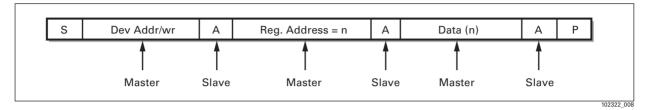

#### **Typical Single-Byte Write Procedure**

- 1. Send the Start condition.

- 2. Send the CX24118A slave address, a write bit, and receive an ACK.

- 3. Send the CX24118A desired register address = n, and receive an ACK.

- 4. Send the byte for a desired register = n, and receive an ACK.

- 5. Send the Stop condition.

The above-described single-byte write procedure is shown in Figure 6.

In the figure, the following abbreviations are used:

- ◆ S = Start

- Dev Addr/wr = Device address with a write command

- ♦ A = Acknowledge

- ◆ P = Stop

#### **Chapter 3: Serial Programming Interface and Registers**

Figure 6. Typical Single-Byte Write Procedure

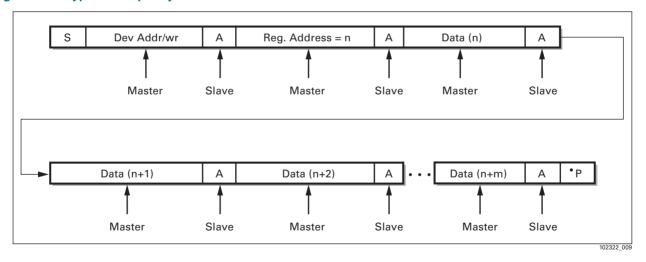

#### **Typical Multiple-Bytes Write Procedure**

- 1. Send the Start condition.

- 2. Send the CX24118A slave address, a write bit, and receive an ACK.

- 3. Send the CX24118A desired register address = n, and receive an ACK.

- 4. Send the byte destined for register n, and receive an ACK.

- 5. Send the byte destined for register n+1, and receive an ACK.

- 6. Send the byte destined for register n+2, and receive an ACK.

- 7. Send the data destined for register n+m, and receive an ACK

- 8. Send the Stop condition.

The above-described multiple-bytes write procedure is shown in Figure 7.

In the figure, the following abbreviations are used:

- ◆ S = Start

- ◆ Dev Addr/wr = Device address with a write command

- ◆ A = Acknowledge

- ◆ P = Stop

Figure 7. Typical Multiple-Bytes Write Procedure

#### **Typical Single-Byte Read Procedure**

- 1. Send the Start condition.

- 2. Send the CX24118A slave address, a write bit, and receive an ACK.

- 3. Send the CX24118A desired register address = n, and receive an ACK.

- 4. Send the Start condition.

- 5. Send the part's slave address, a read bit, and receive an ACK.

- 6. Receive the byte from the desired register n, and do not supply an ACK.

CX24118A\_N\_2 © NXP B.V. 2009. All rights reserved

**NXP Semiconductors**

#### **Chapter 3: Serial Programming Interface and Registers**

7. Send the Stop condition.

NOTE: When reading data from a slave, no ACK is supplied from master after the last desired byte.

The above-described single-byte read procedure is shown in Figure 8.

In the figure, the following abbreviations are used:

- ♦ S = Start

- Dev Addr/wr = Device address with a write command

- A = Acknowledge

- ◆ P = Stop

- Dev Addr/r = Device address with a read command

Figure 8. **Typical Single-Byte Read Procedure**

#### **Multiple-Bytes Read Procedure**

- 1. Send the Start condition.

- 2. Send the CX24118A slave address, a write bit, and receive an ACK.

- 3. Send the CX24118A desired register address = n, and receive an ACK.

- 4. Send the Start condition.

- 5. Send the part's slave address, a read bit, and receive an ACK.

- 6. Receive the byte from register n, and supply an ACK.

- 7. Receive the byte from register n+1, and supply an ACK.

- 8. Receive the byte from register n+2, and supply an ACK.

- 9. Receive the data from register n+m, and do not supply an ACK.

- 10. Send the Stop condition.

NOTE: When reading data from a slave, no ACK is supplied from master after the last desired byte.

The above-described multiple-bytes read procedure is shown in Figure 9.

In the figure, the following abbreviations are used:

- ♦ S = Start

- Dev Addr/wr = Device address with a write command

- A = Acknowledge

- P = Stop

- Dev Addr/r = Device address with a read command

CX24118A\_N\_2

#### **Chapter 3: Serial Programming Interface and Registers**

Figure 9. Typical Multiple-Bytes Read Procedure

## 3.2 Registers

The register bit map is shown in Table 6.

Table 6. Register Bit Map (Sheet 1 of 2)

| Tuner  10 DSMCIkPol DSMByp CPMan[1:0] CPDVal[1:0] TUNLD CPSel  11 CPLevel1[1:0] CPLevel2[1:0] CPLevel3[1:0] CPLevel4[1:0]  12 BSDelayVal[3:0] Reserved CPCtrl CPVal[1:0]  13 Reserved  14 TUNAutoEn[1:0] TUN1[5:0]  15 TUN2[7:0]  16 TUN3[7:0]  17 TUN4[7:0]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | olo ol Itoglotol Di             | t map (one   | ot 1 o. z,                                         |           |      |          |        |     |         |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|--------------|----------------------------------------------------|-----------|------|----------|--------|-----|---------|--|--|

| 00 CHPId[7:0] 01 CHPVer[7:0] 02 Reserved OUTRefDiv PLLRefDiv Reserved  Tuner  10 DSMCIkPol DSMByp CPMan[1:0] CPDVal[1:0] TUNLD CPSel 11 CPLevel1[1:0] CPLevel2[1:0] CPLevel3[1:0] CPLevel4[1:0] CPLevel4[1:0] 12 BSDelayVal[3:0] Reserved 14 TUNAutoEn[1:0] TUN1[5:0] 15 TUN2[7:0] 16 TUN3[7:0] 17 TUN4[7:0] 18 VCOSel[5] LODivSel VCOSel[4:0] VCOSel[4:0] VCOBandS 19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Register Address <sup>(1)</sup> | D7           | D6                                                 | D5        | D4   | D3       | D2     | D1  | D0      |  |  |

| 01 CHPVer[7:0]  02 Reserved OUTRefDiv PLLRefDiv Reserved  Tuner  10 DSMClkPol DSMByp CPMan[1:0] CPDVal[1:0] TUNLD CPSel  11 CPLevel1[1:0] CPLevel2[1:0] CPLevel3[1:0] CPLevel4[1:0]  12 BSDelayVal[3:0] Reserved CPCtrl CPVal[1:0]  13 Reserved  14 TUNAutoEn[1:0] TUN1[5:0]  15 TUN2[7:0]  16 TUN3[7:0]  17 TUN4[7:0]  18 VCOSel[5] LODivSel VCOSel[4:0] VCOSel[4:0] VCOBandS  19 PLLintDiv[8:1]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                 |              |                                                    | Glob      | pal  |          |        |     |         |  |  |

| Tuner   Tuner   Tunk   Tunk | 00                              |              |                                                    |           | СНР  | d[7:0]   |        |     |         |  |  |

| Tuner         Tuner           10         DSMClkPol         DSMByp         CPMan[1:0]         CPDVal[1:0]         TUNLD         CPSel           11         CPLevel1[1:0]         CPLevel3[1:0]         CPLevel4[1:0]         CPLevel4[1:0]           12         BsDelayVal[3:0]         Reserved         CPCtrl         CPVal[1:0]           13         Reserved         TUN1[5:0]         TUN1[5:0]           15         TUN2[7:0]         TUN3[7:0]           16         TUN3[7:0]         TUN4[7:0]           17         TUN4[7:0]         VCOSel[4:0]         VCOBandS           19         PLLIntDiv[8:1]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 01                              |              | CHPVer[7:0]                                        |           |      |          |        |     |         |  |  |

| 10         DSMClkPol         DSMByp         CPMan[1:0]         CPDVal[1:0]         TUNLD         CPSel           11         CPLevel1[1:0]         CPLevel3[1:0]         CPLevel4[1:0]         CPLevel4[1:0]           12         BsDelayVal[3:0]         Reserved         CPCtrl         CPVal[1:0]           13         Reserved         TUN1[5:0]         TUN1[5:0]           15         TUN2[7:0]         TUN3[7:0]           16         TUN4[7:0]         TUN4[7:0]           17         TUN4[7:0]         VCOSel[4:0]         VCOBandS           19         PLLIntDiv[8:1]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 02                              |              | Reserved OUTRefDiv PLLRefDiv Reserved              |           |      |          |        |     |         |  |  |

| 11 CPLevel1[1:0] CPLevel2[1:0] CPLevel3[1:0] CPLevel4[1:0]  12 BsDelayVal[3:0] Reserved CPCtrl CPVal[1:0]  13 Reserved  14 TUNAutoEn[1:0] TUN1[5:0]  15 TUN2[7:0]  16 TUN3[7:0]  17 TUN4[7:0]  18 VCOSel[5] LODivSel VCOSel[4:0] VCOSel[4:0]  19 PLLIntDiv[8:1]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Tuner                           |              |                                                    |           |      |          |        |     |         |  |  |

| 12   BsDelayVal[3:0]   Reserved   CPCtrl   CPVal[1:0]     13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 10                              | DSMClkPol    | SMCIkPol DSMByp CPMan[1:0] CPDVal[1:0] TUNLD CPSel |           |      |          |        |     |         |  |  |

| 13 Reserved  14 TUNAutoEn[1:0] TUN1[5:0]  15 TUN2[7:0]  16 TUN3[7:0]  17 TUN4[7:0]  18 VCOSel[5] LODivSel VCOSel[4:0] VCOBandS  19 PLLIntDiv[8:1]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 11                              | CPLeve       | CPLevel1[1:0]                                      |           |      |          |        |     |         |  |  |

| 14     TUNAutoEn[1:0]     TUN1[5:0]       15     TUN2[7:0]       16     TUN3[7:0]       17     TUN4[7:0]       18     VCOSel[5]     LODivSel     VCOSel[4:0]     VCOBandS       19     PLLIntDiv[8:1]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 12                              |              | BsDela                                             | yVal[3:0] |      | Reserved | CPCtrl | CPV | al[1:0] |  |  |

| 15 TUN2[7:0] 16 TUN3[7:0] 17 TUN4[7:0] 18 VCOSel[5] LODivSel VCOSel[4:0] VCOBandS 19 PLLIntDiv[8:1]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 13                              |              |                                                    |           | Rese | erved    |        |     |         |  |  |

| 16 TUN3[7:0]  17 TUN4[7:0]  18 VCOSel[5] LODivSel VCOSel[4:0] VCOBandS  19 PLLIntDiv[8:1]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 14                              | TUNAuto      | oEn[1:0]                                           |           |      | TUN      | 1[5:0] |     |         |  |  |

| 17 TUN4[7:0]  18 VCOSel[5] LODivSel VCOSel[4:0] VCOBandS  19 PLLIntDiv[8:1]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 15                              |              |                                                    |           | TUN  | 2[7:0]   |        |     |         |  |  |

| 18 VCOSel[5] LODivSel VCOSel[4:0] VCOBandS  19 PLLIntDiv[8:1]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 16                              |              |                                                    |           | TUN: | 3[7:0]   |        |     |         |  |  |

| 19 PLLIntDiv[8:1]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 17                              |              |                                                    |           | TUN  | 4[7:0]   |        |     |         |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 18                              | VCOSel[5]    | VCOSel[5] LODivSel VCOSel[4:0] VCOBandSe           |           |      |          |        |     |         |  |  |

| 1A PLLIntDiv[0] PLLFracDiv[17:11]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 19                              |              | PLLIntDiv[8:1]                                     |           |      |          |        |     |         |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 1A                              | PLLIntDiv[0] | PLLIntDiv[0] PLLFracDiv[17:11]                     |           |      |          |        |     |         |  |  |

CX24118A\_N\_2 © NXP B.V. 2009. All rights reserved.

**CX24118A NXP Semiconductors**

## **Chapter 3: Serial Programming Interface and Registers**

Table 6. Register Bit Map (Sheet 2 of 2)

| Register Address <sup>(1)</sup> | D7       | D6             | D5    | D4             | D3              | D2             | D1       | D0      |  |  |

|---------------------------------|----------|----------------|-------|----------------|-----------------|----------------|----------|---------|--|--|

| 1B                              |          |                |       | PLLFrac        | :Div[10:3]      |                |          |         |  |  |

| 1C                              |          | PLLFracDiv[2:0 | ]     | TUNReset       |                 | Reserved       |          |         |  |  |

| 1D                              |          | Res            | erved |                | BBFAmpGain[3:0] |                |          |         |  |  |

| 1E                              | BBFil1l  | BW[1:0]        |       |                | BBFil2          | BW[5:0]        |          |         |  |  |

| 1F                              | Rese     | erved          |       | BBVGA2Off[2:0] | l               | BBVGA10ff[2:0] |          |         |  |  |

| 20                              |          | Reserved       |       |                | RFVCA           | Off[1:0]       | Rese     | erved   |  |  |

| 21                              | Reserved |                | CPEn  | PSEn           | BBEn            | DCCorrEn       | Reserved | RFVCAEn |  |  |

#### FOOTNOTES:

#### **Register Index** 3.3

The register index is shown in Table 7.

**Register Index** Table 7.

| Field Name      | Address <sup>(1)</sup> | Description                           |

|-----------------|------------------------|---------------------------------------|

| BBEn            | 21[3]                  | Baseband Enable.                      |

| BBFAmpGain[3:0] | 1D[3:0]                | Final Baseband Amplifier Gain.        |

| BBFil1BW[1:0]   | 1E[7:6]                | Baseband Filter 1 Bandwidth.          |

| BBFil2BW[5:0]   | 1E[5:0]                | Baseband Filter 2 Bandwidth.          |

| BBVGA1Off[2:0]  | 1F[2:0]                | Baseband VGA1 Offset Control.         |

| BBVGA2Off[2:0]  | 1F[5:3]                | Baseband VGA2 Offset Control.         |

| BsDelayVal[3:0] | 12[7:4]                | VCO Tuning System Delay.              |

| CHPId[7:0]      | 00[7:0]                | Chip Identification Number.           |

| CHPVer[7:0]     | 01[7:0]                | Chip Version Number.                  |

| CPCtrl          | 12[2]                  | Charge Pump Control.                  |

| CPDVal[1:0]     | 10[3:2]                | Digital Charge Pump Valve.            |

| CPEn            | 21[5]                  | Charge Pump Enable.                   |

| CPLevel1[1:0]   | 11[7:6]                | Automatic Charge Pump Level 1 Select. |

| CPLevel2[1:0]   | 11[5:4]                | Automatic Charge Pump Level 2 Select. |

| CPLevel3[1:0]   | 11[3:2]                | Automatic Charge Pump Level 3 Select. |

| CPLevel4[1:0]   | 11[1:0]                | Automatic Charge Pump Level 4 Select. |

<sup>(1)</sup> The values in this column are hexadecimal.

CX24118A **NXP Semiconductors**

## **Chapter 3: Serial Programming Interface and Registers**

Table 7. **Register Index**

| Field Name       | Address <sup>(1)</sup>          | Description                                            |

|------------------|---------------------------------|--------------------------------------------------------|

| CPMan[1:0]       | 10[5:4]                         | Manual Analog Charge Pump Select.                      |

| CPSel            | 10[0]                           | Manual Override of Automatic Charge Pump Level Select. |