# DAC1405D750

# Dual 14-bit DAC, up to 750 Msps; 4x and 8x interpolating

Rev. 4 — 7 June 2011

Product data sheet

#### **General description** 1.

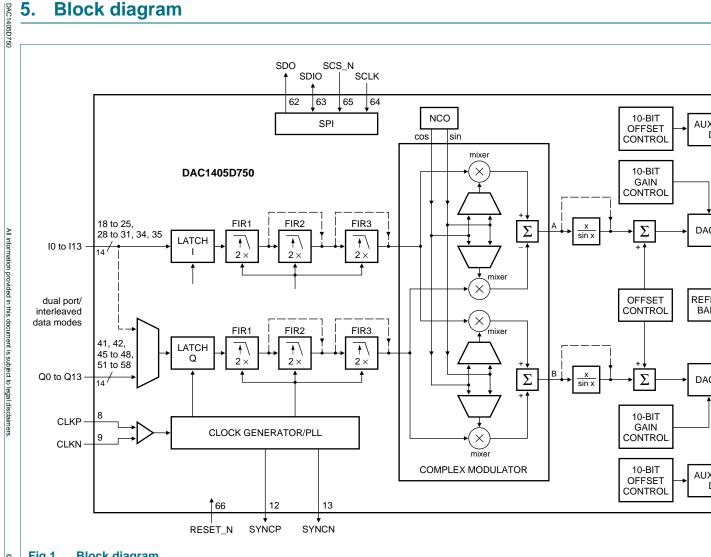

The DAC1405D750 is a high-speed 14-bit dual channel Digital-to-Analog Converter (DAC) with selectable 4× or 8× interpolating filters optimized for multi-carrier wireless transmitters.

Thanks to its digital on-chip modulation, the DAC1405D750 allows the complex I and Q inputs to be converted from BaseBand (BB) to IF. The mixing frequency is adjusted via a Serial Peripheral Interface (SPI) with a 32-bit Numerically Controlled Oscillator (NCO) and the phase is controlled by a 16-bit register.

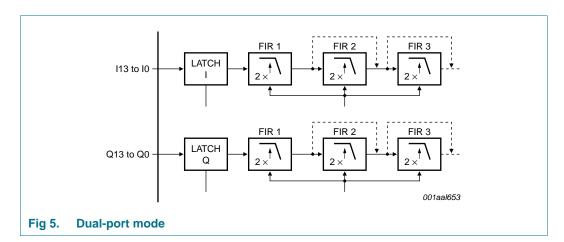

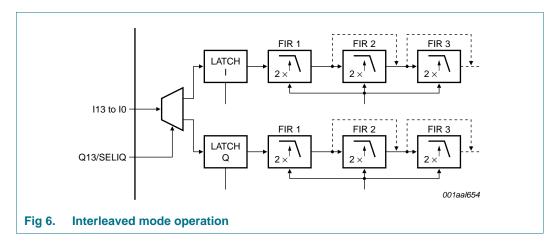

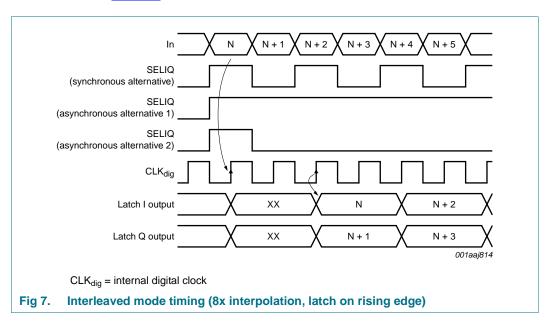

Two modes of operation are available: separate data ports or a single interleaved high-speed data port. In the Interleaved mode, the input data stream is demultiplexed into its original I and Q data and then latched.

A 4× and 8× clock multiplier enables the DAC1405D750 to provide the appropriate internal clocks from the internal PLL. The internal PLL can be bypassed enabling the use of an external high frequency clock. The voltage regulator enables adjustment of the output full-scale current.

#### 2. **Features and benefits**

|  | Dual | 14-bit | resolution |

|--|------|--------|------------|

|--|------|--------|------------|

- 750 Msps maximum update rate

- Input data rate up to 185 Msps

- 32-bit programmable NCO frequency

- Dual port or Interleaved data modes

- 1.8 V and 3.3 V power supplies

- LVDS compatible clock

- Two's complement or binary offset data format

- 1.8 V/3.3 V CMOS input data buffers

- IMD3: 74 dBc; f<sub>s</sub> = 737.28 Msps;  $f_0 = 140 \text{ MHz}$

- ACPR: 72 dBc; 2-carrier WCDMA;  $f_s = 737.28 \text{ Msps}; f_o = 153.6 \text{ MHz}$

- Selectable 4× or 8× interpolation filters Typical 1.2 W power dissipation at 4× interpolation, PLL off and 740 Msps

- Power-down and Sleep modes

- Very low noise cap-free integrated PLL

Differential scalable output current from 1.6 mA to 22 mA

- On-chip 1.25 V reference

- External analog offset control (10-bit auxiliary DACs)

- Internal digital offset control

- Inverse x / (sin x) function

- Fully compatible SPI port

- Industrial temperature range from -40 °C to +85 °C

DAC1405D750

Dual 14-bit DAC, up to 750 Msps; 4× and 8× interpolating

## 3. Applications

- Wireless infrastructure: LTE, WiMAX, GSM, CDMA, WCDMA, TD-SCDMA

- Communication: LMDS/MMDS, point-to-point

- Direct Digital Synthesis (DDS)

- Broadband wireless systems

- Digital radio links

- Instrumentation

- Automated Test Equipment (ATE)

## 4. Ordering information

#### Table 1. Ordering information

| Type number   | Package  |                                                                                                              |          |  |

|---------------|----------|--------------------------------------------------------------------------------------------------------------|----------|--|

|               | Name     | Description                                                                                                  | Version  |  |

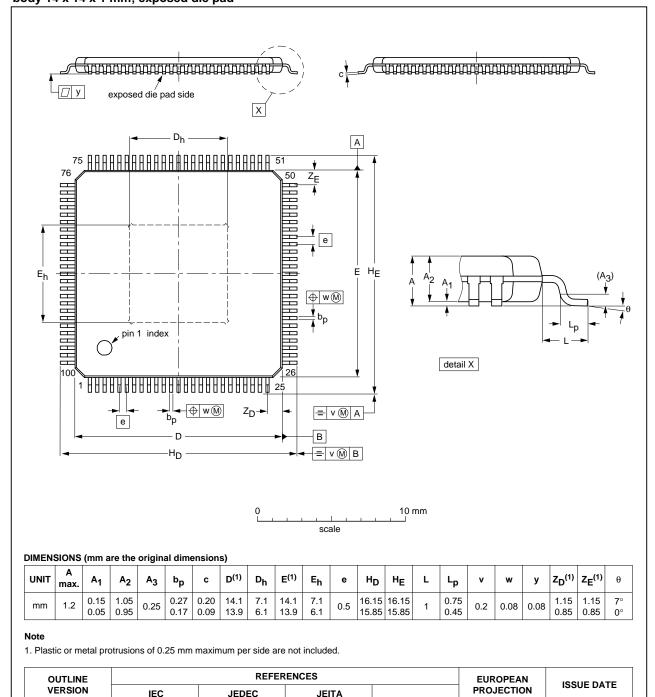

| DAC1405D750HW | HTQFP100 | plastic thermal enhanced thin quad flat package; 100 leads; body $14 \times 14 \times 1$ mm; exposed die pad | SOT638-1 |  |

#### **Block diagram 5**.

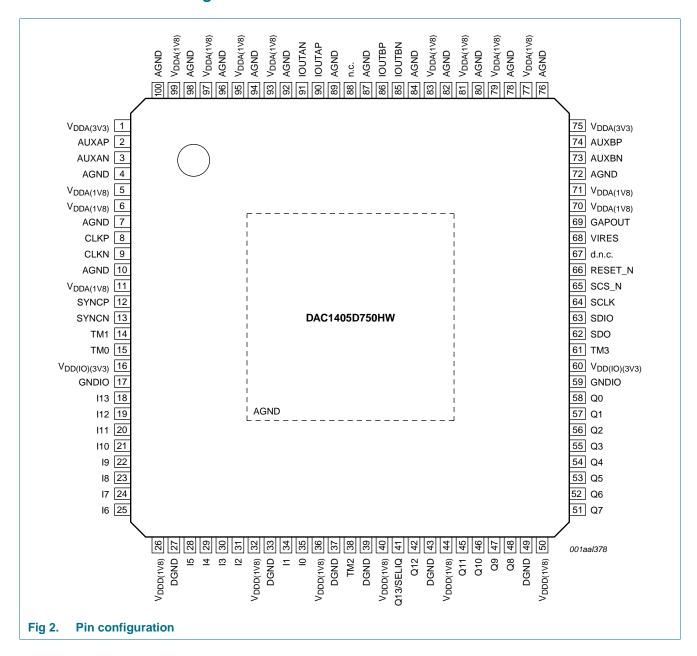

## 6. Pinning information

### 6.1 Pinning

Dual 14-bit DAC, up to 750 Msps;  $4\times$  and  $8\times$  interpolating

## 6.2 Pin description

Table 2. Pin description

| Table 2.                 | Pin descript |                     |                                              |

|--------------------------|--------------|---------------------|----------------------------------------------|

| Symbol                   | Pin          | Type <sup>[1]</sup> | Description                                  |

| $V_{\text{DDA}(3V3)}$    | 1            | Р                   | analog supply voltage 3.3 V                  |

| AUXAP                    | 2            | 0                   | auxiliary DAC B output current               |

| AUXAN                    | 3            | 0                   | complementary auxiliary DAC B output current |

| AGND                     | 4            | G                   | analog ground                                |

| V <sub>DDA(1V8)</sub>    | 5            | Р                   | analog supply voltage 1.8 V                  |

| V <sub>DDA(1V8)</sub>    | 6            | Р                   | analog supply voltage 1.8 V                  |

| AGND                     | 7            | G                   | analog ground                                |

| CLKP                     | 8            | l                   | clock input                                  |

| CLKN                     | 9            | I                   | complementary clock input                    |

| AGND                     | 10           | G                   | analog ground                                |

| $V_{\text{DDA(1V8)}}$    | 11           | Р                   | analog supply voltage 1.8 V                  |

| SYNCP                    | 12           | 0                   | synchronous clock output                     |

| SYNCN                    | 13           | 0                   | complementary synchronous clock output       |

| TM1                      | 14           | I/O                 | test mode 1 (connected to DGND)              |

| TM0                      | 15           | I/O                 | test mode 0 (connected to DGND)              |

| V <sub>DD(IO)(3V3)</sub> | 16           | Р                   | input/output buffers supply voltage 3.3 V    |

| GNDIO                    | 17           | G                   | input/output buffers ground                  |

| l13                      | 18           | I                   | I data input bit 13 (MSB)                    |

| l12                      | 19           | I                   | I data input bit 12                          |

| l11                      | 20           | I                   | I data input bit 11                          |

| I10                      | 21           | I                   | I data input bit 10                          |

| 19                       | 22           | I                   | I data input bit 9                           |

| 18                       | 23           | I                   | I data input bit 8                           |

| 17                       | 24           | I                   | I data input bit 7                           |

| 16                       | 25           | I                   | I data input bit 6                           |

| V <sub>DDD(1V8)</sub>    | 26           | Р                   | digital supply voltage 1.8 V                 |

| DGND                     | 27           | G                   | digital ground                               |

| 15                       | 28           | I                   | I data input bit 5                           |

| 14                       | 29           | I                   | I data input bit 4                           |

| 13                       | 30           | 1                   | I data input bit 3                           |

| 12                       | 31           | I                   | I data input bit 2                           |

| V <sub>DDD(1V8)</sub>    | 32           | Р                   | digital supply voltage 1.8 V                 |

| DGND                     | 33           | G                   | digital ground                               |

| <b>I</b> 1               | 34           | I                   | I data input bit 1                           |

| 10                       | 35           | I                   | I data input bit 0 (LSB)                     |

| V <sub>DDD(1V8)</sub>    | 36           | Р                   | digital supply voltage 1.8 V                 |

| DGND                     | 37           | G                   | digital ground                               |

| TM2                      | 38           | -                   | test mode 2 (to connect to DGND)             |

| DGND                     | 39           | G                   | digital ground                               |

Table 2.

Pin description ...continued

| Symbol                   | Pin  | Type <sup>[1]</sup> | Description                                             |

|--------------------------|------|---------------------|---------------------------------------------------------|

| V <sub>DDD(1V8)</sub>    | 40   | Р                   | digital supply voltage 1.8 V                            |

| Q13/SELIC                | Q 41 | I                   | Q data input bit 13 (MSB)/select IQ in Interleaved mode |

| Q12                      | 42   | I                   | Q data input bit 12                                     |

| DGND                     | 43   | G                   | digital ground                                          |

| V <sub>DDD(1V8)</sub>    | 44   | Р                   | digital supply voltage 1.8 V                            |

| Q11                      | 45   | I                   | Q data input bit 11                                     |

| Q10                      | 46   | I                   | Q data input bit 10                                     |

| Q9                       | 47   | I                   | Q data input bit 9                                      |

| Q8                       | 48   | I                   | Q data input bit 8                                      |

| DGND                     | 49   | G                   | digital ground                                          |

| V <sub>DDD(1V8)</sub>    | 50   | Р                   | digital supply voltage 1.8 V                            |

| Q7                       | 51   | I                   | Q data input bit 7                                      |

| Q6                       | 52   | I                   | Q data input bit 6                                      |

| Q5                       | 53   | I                   | Q data input bit 5                                      |

| Q4                       | 54   | I                   | Q data input bit 4                                      |

| Q3                       | 55   | I                   | Q data input bit 3                                      |

| Q2                       | 56   | I                   | Q data input bit 2                                      |

| Q1                       | 57   | I                   | Q data input bit 1                                      |

| Q0                       | 58   | I                   | Q data input bit 0 (LSB)                                |

| GNDIO                    | 59   | G                   | input/output buffers ground                             |

| V <sub>DD(IO)(3V3)</sub> | ) 60 | Р                   | input/output buffers supply voltage 3.3 V               |

| TM3                      | 61   | I/O                 | test mode 3 (to connect to DGND)                        |

| SDO                      | 62   | 0                   | SPI data output                                         |

| SDIO                     | 63   | I/O                 | SPI data input/output                                   |

| SCLK                     | 64   | I                   | SPI clock input                                         |

| SCS_N                    | 65   | I                   | SPI chip select (active LOW)                            |

| RESET_N                  | 66   | I                   | general reset (active LOW)                              |

| d.n.c.                   | 67   | -                   | do not connect                                          |

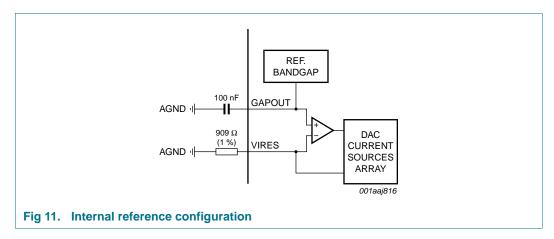

| VIRES                    | 68   | I/O                 | DAC biasing resistor                                    |

| GAPOUT                   | 69   | I/O                 | bandgap input/output voltage                            |

| V <sub>DDA(1V8)</sub>    | 70   | Р                   | analog supply voltage 1.8 V                             |

| V <sub>DDA(1V8)</sub>    | 71   | Р                   | analog supply voltage 1.8 V                             |

| AGND                     | 72   | G                   | analog ground                                           |

| AUXBN                    | 73   | 0                   | auxiliary DAC B output current                          |

| AUXBP                    | 74   | 0                   | complementary auxiliary DAC B output current            |

| V <sub>DDA(3V3)</sub>    | 75   | Р                   | analog supply voltage 3.3 V                             |

| AGND                     | 76   | G                   | analog ground                                           |

| V <sub>DDA(1V8)</sub>    | 77   | Р                   | analog supply voltage 1.8 V                             |

| AGND                     | 78   | G                   | analog ground                                           |

| V <sub>DDA(1V8)</sub>    | 79   | Р                   | analog supply voltage 1.8 V                             |

| AGND                     | 80   | G                   | analog ground                                           |

6 of 42

Table 2.

Pin description ...continued

| Symbol                | Pin  | Type[1] | Description                        |

|-----------------------|------|---------|------------------------------------|

| V <sub>DDA(1V8)</sub> | 81   | Р       | analog supply voltage 1.8 V        |

| AGND                  | 82   | G       | analog ground                      |

| V <sub>DDA(1V8)</sub> | 83   | Р       | analog supply voltage 1.8 V        |

| AGND                  | 84   | G       | analog ground                      |

| IOUTBN                | 85   | 0       | complementary DAC B output current |

| IOUTBP                | 86   | 0       | DAC B output current               |

| AGND                  | 87   | G       | analog ground                      |

| n.c.                  | 88   | -       | not connected                      |

| AGND                  | 89   | G       | analog ground                      |

| IOUTAP                | 90   | 0       | DAC A output current               |

| IOUTAN                | 91   | 0       | complementary DAC A output current |

| AGND                  | 92   | G       | analog ground                      |

| V <sub>DDA(1V8)</sub> | 93   | Р       | analog supply voltage 1.8 V        |

| AGND                  | 94   | G       | analog ground                      |

| V <sub>DDA(1V8)</sub> | 95   | Р       | analog supply voltage 1.8 V        |

| AGND                  | 96   | G       | analog ground                      |

| V <sub>DDA(1V8)</sub> | 97   | Р       | analog supply voltage 1.8 V        |

| AGND                  | 98   | G       | analog ground                      |

| V <sub>DDA(1V8)</sub> | 99   | Р       | analog supply voltage 1.8 V        |

| AGND                  | 100  | G       | analog ground                      |

| AGND                  | H[2] | G       | analog ground                      |

<sup>[1]</sup> P = power supply

G = ground

I = input

O = output

<sup>[2]</sup> H = heatsink (exposed die pad to be soldered)

# 7. Limiting values

Table 3. Limiting values

In accordance with the Absolute Maximum Rating System (IEC 60134).

| Symbol                | Parameter                           | Conditions                                                                                      | Min  | Max  | Unit |

|-----------------------|-------------------------------------|-------------------------------------------------------------------------------------------------|------|------|------|

| $V_{DD(IO)(3V3)}$     | input/output supply voltage (3.3 V) |                                                                                                 | -0.5 | +4.6 | V    |

| V <sub>DDA(3V3)</sub> | analog supply voltage (3.3 V)       |                                                                                                 | -0.5 | +4.6 | V    |

| V <sub>DDA(1V8)</sub> | analog supply voltage (1.8 V)       |                                                                                                 | -0.5 | +3.0 | V    |

| V <sub>DDD(1V8)</sub> | digital supply voltage (1.8 V)      |                                                                                                 | -0.5 | +3.0 | V    |

| V <sub>I</sub>        | input voltage                       | pins CLKP, CLKN, VIRES and GAPOUT referenced to pin AGND                                        | -0.5 | +3.0 | V    |

|                       |                                     | pins I13 to I0, Q13 to Q0, SDO, SDIO, SCLK, SCS_N and RESET_N referenced to GNDIO               | -0.5 | +4.6 | V    |

| Vo                    | output voltage                      | pins IOUTAP, IOUTAN, IOUTBP, IOUTBN,<br>AUXAP, AUXAN, AUXBP and AUXBN<br>referenced to pin AGND | -0.5 | +4.6 | V    |

|                       |                                     | pins SYNCP and SYNCN referenced to pin AGND                                                     | -0.5 | +3.0 | V    |

| T <sub>stg</sub>      | storage temperature                 |                                                                                                 | -55  | +150 | °C   |

| T <sub>amb</sub>      | ambient temperature                 |                                                                                                 | -40  | +85  | °C   |

| Tj                    | junction temperature                |                                                                                                 | -    | 125  | °C   |

## 8. Thermal characteristics

Table 4. Thermal characteristics

| Symbol               | Parameter                                   | Conditions | Тур              | Unit |

|----------------------|---------------------------------------------|------------|------------------|------|

| $R_{th(j-a)}$        | thermal resistance from junction to ambient |            | [ <u>1]</u> 19.8 | K/W  |

| R <sub>th(j-c)</sub> | thermal resistance from junction to case    |            | <u>[1]</u> 7.7   | K/W  |

<sup>[1]</sup> In compliance with JEDEC test board, in free air.

## 9. Characteristics

#### Table 5. Characteristics

$V_{DDA(1V8)} = V_{DDD(1V8)} = 1.8 \text{ V}; V_{DDA(3V3)} = V_{DD(1O)(3V3)} = 3.3 \text{ V}; AGND, DGND and GNDIO shorted together;}$   $T_{amb} = -40 \text{ }^{\circ}\text{C}$  to +85  $\text{ }^{\circ}\text{C}$ ; typical values measured at  $T_{amb} = 25 \text{ }^{\circ}\text{C}$ ;  $R_L = 50 \text{ }^{\Omega}$  differential;  $I_{O(fs)} = 20 \text{ }^{\circ}\text{M}$ ; PLL off unless otherwise specified.

| Symbol                   | Parameter                           | Conditions                                                                                  | Test[1] | Min | Тур  | Max  | Unit |

|--------------------------|-------------------------------------|---------------------------------------------------------------------------------------------|---------|-----|------|------|------|

| $V_{DD(IO)(3V3)}$        | input/output supply voltage (3.3 V) |                                                                                             | I       | 3.0 | 3.3  | 3.6  | V    |

| V <sub>DDA(3V3)</sub>    | analog supply voltage<br>(3.3 V)    |                                                                                             | I       | 3.0 | 3.3  | 3.6  | V    |

| V <sub>DDA(1V8)</sub>    | analog supply voltage<br>(1.8 V)    |                                                                                             | I       | 1.7 | 1.8  | 1.9  | V    |

| V <sub>DDD(1V8)</sub>    | digital supply voltage (1.8 V)      |                                                                                             | I       | 1.7 | 1.8  | 1.9  | V    |

| I <sub>DD(IO)(3V3)</sub> | input/output supply current (3.3 V) | $f_o = 19 \text{ MHz};$<br>$f_s = 740 \text{ Msps};$<br>$4 \times$ interpolation;<br>NCO on | I       | -   | 0.5  | 0.7  | mA   |

| I <sub>DDA(3V3)</sub>    | analog supply current (3.3 V)       | $f_o = 19 \text{ MHz};$<br>$f_s = 740 \text{ Msps};$<br>$4 \times$ interpolation;<br>NCO on | I       | -   | 44   | 50   | mA   |

| I <sub>DDD(1V8)</sub>    | digital supply current (1.8 V)      | $f_o = 19$ MHz;<br>$f_s = 740$ Msps;<br>$4 \times$ interpolation;<br>NCO on                 | I       | -   | 181  | 210  | mA   |

| I <sub>DDA(1V8)</sub>    | analog supply current<br>(1.8 V)    | $f_o = 19 \text{ MHz};$<br>$f_s = 740 \text{ Msps};$<br>$4 \times$ interpolation;<br>NCO on | I       | -   | 360  | 391  | mA   |

| I <sub>DDD</sub>         | digital supply current              | for x / (sin x) function only                                                               | I       | -   | 70   | -    | mA   |

| P <sub>tot</sub>         | total power dissipation             | $f_o = 19 \text{ MHz};$<br>$f_s = 740 \text{ Msps}$                                         |         |     |      |      |      |

|                          |                                     | 4× interpolation                                                                            |         |     |      |      |      |

|                          |                                     | NCO off; DAC B off                                                                          | С       | -   | 0.74 | -    | W    |

|                          |                                     | NCO off                                                                                     | С       | -   | 0.89 | -    | W    |

|                          |                                     | NCO on; all V <sub>DD</sub>                                                                 | С       | -   | 1.12 | 1.32 | W    |

|                          |                                     | 8× interpolation                                                                            |         |     |      |      |      |

|                          |                                     | NCO on                                                                                      | I       | -   | 1.11 | -    | W    |

|                          |                                     | Power-down mode:                                                                            |         |     |      |      |      |

|                          |                                     | full power-down;<br>all V <sub>DD</sub>                                                     | I       | -   | 0.03 | 0.06 | W    |

|                          |                                     | DAC A and DAC B<br>Sleep mode; NCO on                                                       | I       | -   | 0.63 | -    | W    |

Table 5.

Characteristics ...continued

$V_{DDA(1V8)} = V_{DDD(1V8)} = 1.8 \ V; \ V_{DDA(3V3)} = V_{DD(1O)(3V3)} = 3.3 \ V; \ AGND, \ DGND \ and \ GNDIO \ shorted \ together;$   $T_{amb} = -40 \ ^{\circ}\text{C}$  to +85  $^{\circ}\text{C}$ ; typical values measured at  $T_{amb} = 25 \ ^{\circ}\text{C}$ ;  $R_L = 50 \ \Omega$  differential;  $I_{O(fs)} = 20 \ mA$ ; PLL off unless otherwise specified.

| Symbol              | Parameter                            | Conditions                       | Test[1] | Min             | Тур                         | Max                   | Unit      |

|---------------------|--------------------------------------|----------------------------------|---------|-----------------|-----------------------------|-----------------------|-----------|

| Clock input         | s (CLKP and CLKN)[2]                 |                                  |         |                 |                             |                       |           |

| V <sub>i</sub>      | input voltage                        | CLKN $ V_{gpd} $ < 50 mV or CLKP | С       | <u>[3]</u> 825  | -                           | 1575                  | mV        |

| $V_{idth}$          | input differential threshold voltage | $ V_{gpd}  < 50 \text{ mV}$      | С       | <u>[3]</u> –100 | -                           | +100                  | mV        |

| R <sub>i</sub>      | input resistance                     |                                  | D       | -               | 10                          | -                     | $M\Omega$ |

| Ci                  | input capacitance                    |                                  | D       | -               | 0.5                         | -                     | pF        |

| Clock outpu         | uts (SYNCP and SYNCN)                |                                  |         |                 |                             |                       |           |

| V <sub>o(cm)</sub>  | common-mode output voltage           |                                  | С       | -               | V <sub>DDA(1V8)</sub> – 0.3 | -                     | V         |

| $V_{O(dif)}$        | differential output voltage          |                                  | С       | -               | 1.2                         | -                     | V         |

| R <sub>o</sub>      | output resistance                    |                                  | D       | -               | 80                          | -                     | Ω         |

| Digital inpu        | ts (I0 to I13, Q0 to Q13)            |                                  |         |                 |                             |                       |           |

| $V_{IL}$            | LOW-level input voltage              |                                  | С       | GNDIO           | -                           | 0.8                   | V         |

| $V_{IH}$            | HIGH-level input voltage             |                                  | С       | 1.6             | -                           | $V_{DD(IO)(3V3)}$     | V         |

| I <sub>IL</sub>     | LOW-level input current              | $V_{IL} = 0.8 V$                 | I       | -               | 60                          | -                     | μΑ        |

| I <sub>IH</sub>     | HIGH-level input current             | $V_{IH} = 2.3 \text{ V}$         | I       | -               | 80                          | -                     | μΑ        |

| Digital inpu        | ts (SDO, SDIO, SCLK, SCS_I           | N and RESET_N)                   |         |                 |                             |                       |           |

| $V_{IL}$            | LOW-level input voltage              |                                  | С       | GNDIO           | -                           | 1.0                   | V         |

| $V_{IH}$            | HIGH-level input voltage             |                                  | С       | 2.3             | -                           | $V_{DD(IO)(3V3)}$     | V         |

| I <sub>IL</sub>     | LOW-level input current              | V <sub>IL</sub> = 1.0 V          | I       | -               | 20                          | -                     | nA        |

| I <sub>IH</sub>     | HIGH-level input current             | $V_{IH} = 2.3 \text{ V}$         | I       | -               | 20                          | -                     | nA        |

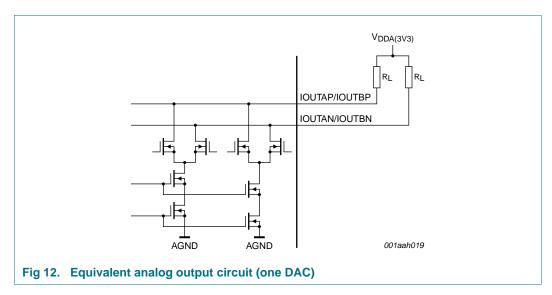

| Analog out          | puts (IOUTAP, IOUTAN, IOUT           | BP and IOUTBN)                   |         |                 |                             |                       |           |

| I <sub>O(fs)</sub>  | full-scale output current            | register value = 00h             | С       | -               | 1.6                         | -                     | mA        |

|                     |                                      | default register                 | С       | -               | 20                          | -                     | mA        |

| Vo                  | output voltage                       | compliance range                 | С       | 1.8             | -                           | $V_{\text{DDA(3V3)}}$ | V         |

| R <sub>o</sub>      | output resistance                    |                                  | D       | -               | 250                         | -                     | $k\Omega$ |

| Co                  | output capacitance                   |                                  | D       | -               | 3                           | -                     | pF        |

| ΔE <sub>O</sub>     | offset error variation               |                                  | С       | -               | 6                           | -                     | ppm/°C    |

| $\Delta E_G$        | gain error variation                 |                                  | С       | -               | 18                          | -                     | ppm/°C    |

| Reference v         | oltage output (GAPOUT)               |                                  |         |                 |                             |                       |           |

| V <sub>O(ref)</sub> | reference output voltage             | T <sub>amb</sub> = 25 °C         | I       | 1.2             | 1.25                        | 1.30                  | V         |

| $\Delta V_{O(ref)}$ | reference output voltage variation   |                                  | С       | -               | 117                         | -                     | ppm/°C    |

| I <sub>O(ref)</sub> | reference output current             | external voltage 1.25 V          | D       | -               | 40                          | -                     | μΑ        |

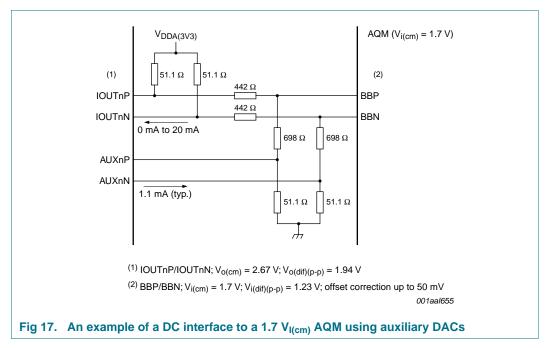

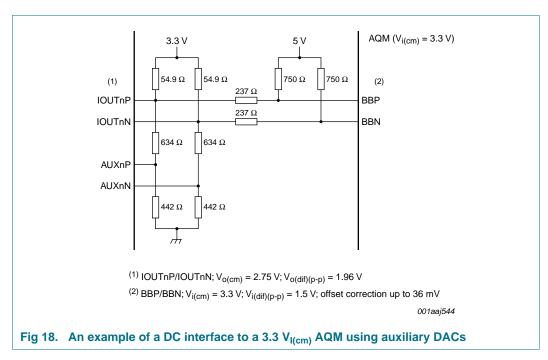

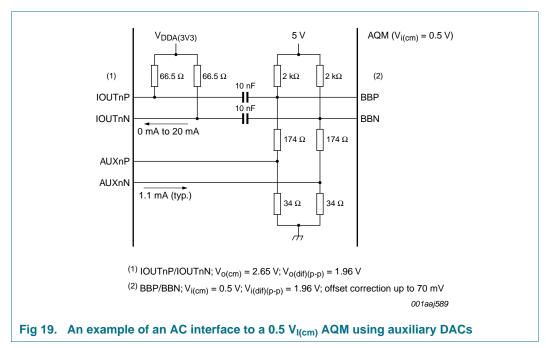

| Analog aux          | iliary outputs (AUXAP, AUXA          | N, AUXBP and AUXBN)              |         |                 |                             |                       |           |

| I <sub>O(aux)</sub> | auxiliary output current             | differential outputs             | 1       | -               | 2.2                         | -                     | mA        |

| V <sub>O(aux)</sub> | auxiliary output voltage             | compliance range                 | С       | 0               | -                           | 2                     | V         |

|                     | auxiliary DAC monotonicity           | guaranteed                       | D       | -               | 10                          | _                     | bit       |

DAC1405D750

## Dual 14-bit DAC, up to 750 Msps; 4× and 8× interpolating

Table 5.

Characteristics ...continued

$V_{DDA(1V8)} = V_{DDD(1V8)} = 1.8 \ V; \ V_{DDA(3V3)} = V_{DD(1O)(3V3)} = 3.3 \ V; \ AGND, \ DGND \ and \ GNDIO \ shorted \ together;$   $T_{amb} = -40 \ ^{\circ}\text{C}$  to +85  $^{\circ}\text{C}$ ; typical values measured at  $T_{amb} = 25 \ ^{\circ}\text{C}$ ;  $R_L = 50 \ \Omega$  differential;  $I_{O(fs)} = 20 \ mA$ ; PLL off unless otherwise specified.

| Symbol              | Parameter                 | Conditions                                | Test[1]               | Min      | Тур            | Max  | Unit  |

|---------------------|---------------------------|-------------------------------------------|-----------------------|----------|----------------|------|-------|

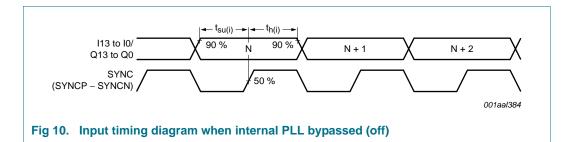

| Input timing        | g (see <u>Figure 10</u> ) |                                           |                       |          |                |      |       |

| f <sub>data</sub>   | data rate                 | Dual-port mode input                      | С                     | -        | -              | 185  | MHz   |

| $t_{w(CLK)}$        | CLK pulse width           |                                           | С                     | 40       | -              | 60   | %     |

| t <sub>h(i)</sub>   | input hold time           |                                           | С                     | 1.6      | -              | -    | ns    |

| t <sub>su(i)</sub>  | input set-up time         |                                           | С                     | 8.0      | -              | -    | ns    |

| SYNC signa          | I                         |                                           |                       |          |                |      |       |

| $t_d$               | delay time                | $f_{SYNC} = f_s / 4$                      | С                     | -        | 0.21           | -    | ns    |

|                     |                           | $f_{SYNC} = f_s / 8$                      | С                     | -        | 0.3            | -    | ns    |

|                     |                           | variation                                 | С                     | -        | 0.27           | -    | ps/°C |

| Output timi         | ng                        |                                           |                       |          |                |      |       |

| fs                  | sampling frequency        |                                           | С                     | -        | -              | 750  | Msps  |

| t <sub>s</sub>      | settling time             | to $\pm$ 0.5 LSB                          | D                     | -        | 20             | -    | ns    |

| NCO freque          | ency range                |                                           |                       |          |                |      |       |

| f <sub>NCO</sub>    | NCO frequency             | register values                           |                       |          |                |      |       |

|                     |                           | 00000000h                                 | D                     | -        | 0              | -    | MHz   |

|                     |                           | FFFFFFFh                                  | D                     | -        | 740            | -    | MHz   |

| f <sub>step</sub>   | step frequency            |                                           | D                     | -        | 0.172          | -    | Hz    |

| Low-power           | NCO frequency range       |                                           |                       |          |                |      |       |

| f <sub>NCO</sub>    | NCO frequency             | register values                           |                       |          |                |      |       |

|                     |                           | 00000000h                                 | D                     | -        | 0              | -    | MHz   |

|                     |                           | F8000000h                                 | D                     | -        | 716.875        | -    | MHz   |

| f <sub>step</sub>   | step frequency            |                                           | D                     | -        | 23.125         | -    | MHz   |

| Dynamic pe          | erformance                |                                           |                       |          |                |      |       |

| SFDR                | spurious-free dynamic     | $f_s = 737.28 \text{ Msps}$               |                       |          |                |      |       |

|                     | range                     | $f_{data} = 92.16 \text{ MHz}; B = f$     | <sub>data</sub> / 2   |          |                |      |       |

|                     |                           | f <sub>o</sub> = 4 MHz; 0 dBFS            | С                     | -        | 77             | -    | dBc   |

|                     |                           | f <sub>data</sub> = 184.32 MHz; B =       | f <sub>data</sub> / 2 |          |                |      |       |

|                     |                           | f <sub>o</sub> = 19 MHz; 0 dBFS           | I                     | -        | 74             | -    | dBc   |

|                     |                           | f <sub>o</sub> = 70 MHz; 0 dBFS           | С                     | -        | 86             | -    | dBc   |

| SFDR <sub>RBW</sub> | restricted bandwidth      |                                           |                       |          |                |      |       |

|                     | spurious-free dynamic     | $f_0 = 153.6 \text{ MHz}; 0 \text{ dBFS}$ | $S; f_{data} = 18$    | 4.32 MHz | $f_s = 737.28$ | Msps |       |

|                     | range                     | B = 20 MHz                                | С                     | -        | 86             | -    | dBc   |

|                     |                           | B = 100 MHz                               | С                     | -        | 80.5           | -    | dBc   |

|                     |                           | B = 20 MHz; 8-tone;<br>500 kHz spacing    | С                     | -        | 76             | -    | dBc   |

NXP Semiconductors DAC1405D750

### Dual 14-bit DAC, up to 750 Msps; 4× and 8× interpolating

Table 5.

Characteristics ...continued

$V_{DDA(1V8)} = V_{DDD(1V8)} = 1.8 \ V; \ V_{DDA(3V3)} = V_{DD(IO)(3V3)} = 3.3 \ V; \ AGND, \ DGND \ and \ GNDIO \ shorted \ together;$   $T_{amb} = -40 \ ^{\circ}\text{C}$  to +85  $^{\circ}\text{C}$ ; typical values measured at  $T_{amb} = 25 \ ^{\circ}\text{C}$ ;  $R_L = 50 \ \Omega$  differential;  $I_{O(fs)} = 20 \ mA$ ; PLL off unless otherwise specified.

| Symbol | Parameter                   | Conditions                                                                          | Test[1]  | Min                | Тур   | Max | Unit    |  |  |

|--------|-----------------------------|-------------------------------------------------------------------------------------|----------|--------------------|-------|-----|---------|--|--|

| IMD3   | third-order intermodulation |                                                                                     |          |                    |       |     |         |  |  |

|        | distortion                  | $f_{data} = 184.32 \text{ MHz}; f_s =$                                              | 737.28 N | 1sps               |       |     |         |  |  |

|        |                             | $f_{o1} = 95 \text{ MHz};$<br>$f_{o2} = 97 \text{ MHz}$                             | С        | [4] -              | 77    | -   | dBc     |  |  |

|        |                             | $f_{o1} = 137 \text{ MHz};$<br>$f_{o2} = 143 \text{ MHz}$                           | С        | [4] _              | 74    | -   | dBc     |  |  |

|        |                             | $f_{o1} = 152.5 \text{ MHz};$<br>$f_{o2} = 153.5 \text{ MHz}$                       | I        | [4] -              | 74    | -   | dBc     |  |  |

| ACPR   | adjacent channel power      |                                                                                     |          |                    |       |     |         |  |  |

|        | ratio                       | $f_{data} = 184.32 \text{ MHz}; f_s =$                                              | 737.28 N | $1$ sps; $f_0 = 9$ | 6 MHz |     |         |  |  |

|        |                             | 1-carrier; B = 5 MHz                                                                | I        | -                  | 75    | -   | dBc     |  |  |

|        |                             | 2-carrier; B = 10 MHz                                                               | С        | -                  | 72    | -   | dBc     |  |  |

|        |                             | 4-carrier; B = 20 MHz                                                               | С        | -                  | 68.5  | -   | dBc     |  |  |

|        |                             | $f_{data} = 184.32 \text{ MHz}; f_s = 737.28 \text{ Msps}; f_o = 153.6 \text{ MHz}$ |          |                    |       |     |         |  |  |

|        |                             | 1-carrier; B = 5 MHz                                                                | С        | -                  | 73    | -   | dBc     |  |  |

|        |                             | 2-carrier; B = 10 MHz                                                               | С        | -                  | 71    | -   | dBc     |  |  |

|        |                             | 4-carrier; B = 20 MHz                                                               | С        | -                  | 67    | -   | dBc     |  |  |

| NSD    | noise spectral density      |                                                                                     |          |                    |       |     |         |  |  |

|        |                             | $f_{data} = 184.32 \text{ MHz}; f_s =$                                              | 737.28 N | 1sps               |       |     |         |  |  |

|        |                             | f <sub>o</sub> = 19 MHz; 0 dBFS                                                     | С        | -                  | -161  | -   | dBFS/Hz |  |  |

|        |                             | $f_0 = 153.6 \text{ MHz};$ 0 dBFS;                                                  | С        | -                  | -156  | -   | dBFS/Hz |  |  |

|        |                             | $f_0 = 153.6 \text{ MHz};$<br>-10 dBFS                                              | С        | -                  | -158  | -   | dBFS/Hz |  |  |

<sup>[1]</sup> D = guaranteed by design; C = guaranteed by characterization; I = 100 % industrially tested.

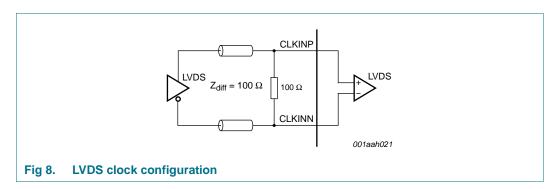

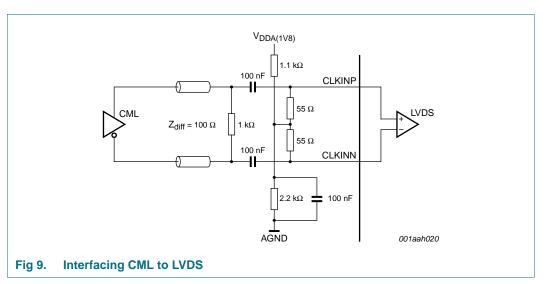

<sup>[2]</sup> CLKP and CLKN inputs are at differential LVDS levels. An external differential resistor with a value of between 80  $\Omega$  and 120  $\Omega$  should be connected across the pins (see Figure 8).

<sup>[3] |</sup>V<sub>gpd</sub>| represents the ground potential difference voltage. This is the voltage that results from current flowing through the finite resistance and the inductance between the receiver and the driver circuit ground voltages.

<sup>[4]</sup> IMD3 rejection with -6 dBFS/tone.

## 10. Application information

### 10.1 General description

The DAC1405D750 is a dual 14-bit DAC which operates at up to 750 Msps. Each DAC consists of a segmented architecture, comprising a 6-bit thermometer sub-DAC and an 8-bit binary weighted sub-DAC.

The input data rate of up to 185 MHz combined with the maximum output sampling rate of 750 Msps make the DAC1405D750 extremely flexible in wide bandwidth and multi-carrier systems. The device's quadrature modulator and 32-bit NCO simplifies system frequency selection. This is also possible because the  $4\times$  and  $8\times$  interpolation filters remove undesired images.

A SYNC signal is provided to synchronize data when the PLL is in the off state.

Two modes are available for the digital input. In Dual-port mode, each DAC uses its own data input line. In Interleaved mode, both DACs use the same data input line.

The on-chip PLL enables generation of the internal clock signals for the digital circuitry and the DAC from a low speed clock. The PLL can be bypassed enabling the use of an external, high-speed clock.

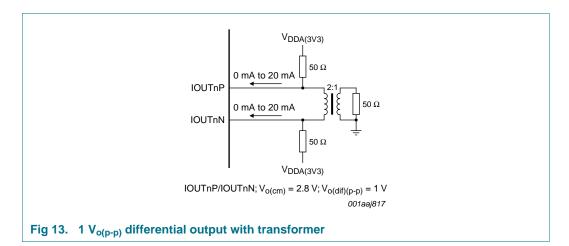

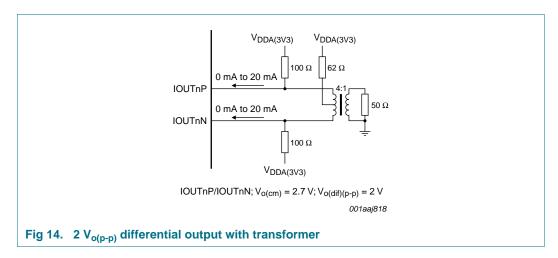

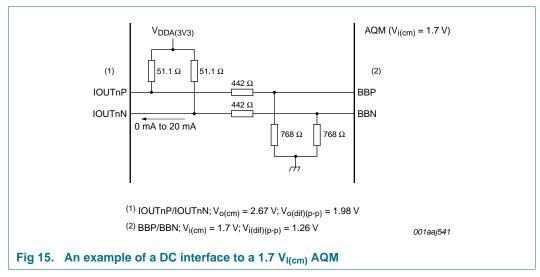

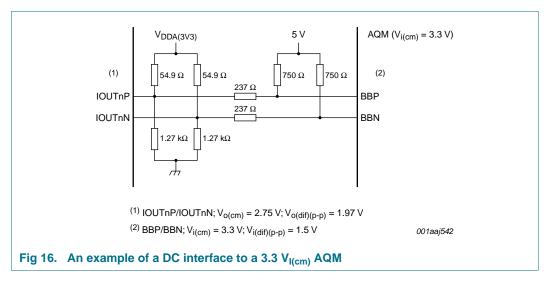

Each DAC generates two complementary current outputs on pins IOUTAP/IOUTAN and IOUTBP/IOUTBN. This provides a full-scale output current ( $I_{O(fs)}$ ) up to 22 mA. An internal reference is available for the reference current which is externally adjustable using pin VIRES.

There are also some embedded features to provide an analog offset correction (auxiliary DACs) and digital offset control as well as for gain adjustment. All the functions can be set using the SPI.

The DAC1405D750 operates at both 3.3 V and 1.8 V each of which has separate digital and analog power supplies. The digital input is 1.8 V and 3.3 V compliant and the clock input is LVDS compliant.

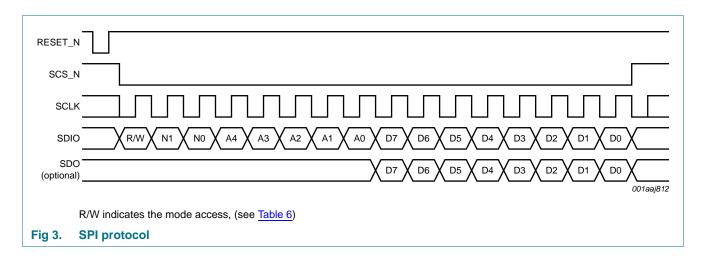

## 10.2 Serial peripheral interface

#### 10.2.1 Protocol description

The DAC1405D750 Serial Peripheral Interface (SPI) is a synchronous serial communication port allowing easy interfacing with many industry microprocessors. It provides access to the registers that define the operating modes of the chip in both write and read modes.

This interface can be configured as a 3-wire type (SDIO as a bidirectional pin) or a 4-wire type (SDIO and SDO as unidirectional pins, input and output port respectively). In both configurations, SCLK acts as the serial clock and SCS\_N acts as the serial chip select bar.

Each read/write operation is sequenced by the SCS\_N signal and enabled by a LOW assertion to drive the chip with 1 to 4 bytes, depending on the content of the instruction byte (see Table 7).

Table 6. Read or Write mode access description

| R/W | Description          |

|-----|----------------------|

| 0   | Write mode operation |

| 1   | Read mode operation  |

In Table 7 N1 and N0 indicate the number of bytes transferred after the instruction byte.

Table 7. Number of bytes transferred

| N1 | N0 | Number of bytes     |

|----|----|---------------------|

| 0  | 0  | 1 byte transferred  |

| 0  | 1  | 2 bytes transferred |

| 1  | 0  | 3 bytes transferred |

| 1  | 1  | 4 bytes transferred |

A0 to A4: indicate which register is being addressed. In the case of a multiple transfer, this address concerns the first register after which the next registers follow directly in a decreasing order according to Table 9 "Register allocation map".

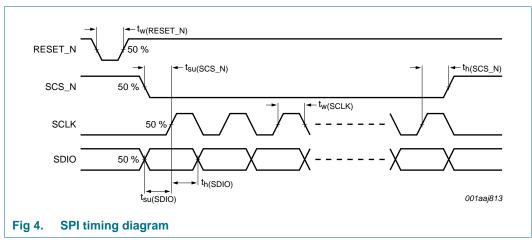

## 10.2.2 SPI timing description

The interface can operate at a frequency of up to 15 MHz. The SPI timing is shown in Figure 4.

DAC1405D750

All information provided in this document is subject to legal disclaimers.

© NXP B.V. 2011. All rights reserved.

The SPI timing characteristics are given in <a>Table 8</a>.

Table 8. SPI timing characteristics

| $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                         |                     |     |     |     |      |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|---------------------|-----|-----|-----|------|

| $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Symbol                  | Parameter           | Min | Тур | Max | Unit |

| $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | f <sub>SCLK</sub>       | SCLK frequency      | -   | -   | 15  | MHz  |

| $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | t <sub>w(SCLK)</sub>    | SCLK pulse width    | 30  | -   | -   | ns   |

| $t_{\text{su(SDIO)}}$ SDIO set-up time 10 - ns $t_{\text{h(SDIO)}}$ SDIO hold time 5 - ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | t <sub>su(SCS_N)</sub>  | SCS_N set-up time   | 20  | -   | -   | ns   |

| $t_{h(SDIO)}$ SDIO hold time 5 - ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | t <sub>h(SCS_N)</sub>   | SCS_N hold time     | 20  | -   | -   | ns   |

| This is the second of the seco | t <sub>su(SDIO)</sub>   | SDIO set-up time    | 10  | -   | -   | ns   |

| t <sub>w(RESET_N)</sub> RESET_N pulse width 30 ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | t <sub>h(SDIO)</sub>    | SDIO hold time      | 5   | -   | -   | ns   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | t <sub>w(RESET_N)</sub> | RESET_N pulse width | 30  | -   | -   | ns   |

## 10.2.3 Detailed descriptions of registers

An overview of the details for all registers is provided in <u>Table 9</u>.

| DAC1405D750                                          | Addr | ess | Register name | R/W | Bit definition | 1                          |                      |             |              |            |               |          |  |

|------------------------------------------------------|------|-----|---------------|-----|----------------|----------------------------|----------------------|-------------|--------------|------------|---------------|----------|--|

| 750                                                  | Dec  | Hex |               |     | Bit 7          | Bit 7 Bit 6                |                      | Bit 4       | Bit 3        | Bit 2      | Bit 1         | ı        |  |

|                                                      | 0    | 00h | COMMon        | R/W | 3W_SPI         | SPI_RST                    | CLK_SEL              | -           | MODE_<br>SEL | CODING     | IC_PD         | GA       |  |

|                                                      | 1    | 01h | TXCFG         | R/W | NCO_ON         | NCO_LP_<br>SEL             | INV_SIN_<br>SEL      | ı           | MODULATIC    | N[2:0]     | INTERPOL      | ATIO     |  |

|                                                      | 2    | 02h | PLLCFG        | R/W | PLL_PD         | -                          | PLL_DIV_<br>PD       | PLL         | _DIV[1:0]    | DAC_CLK_   | DELAY[1:0]    | DA:      |  |

|                                                      | 3    | 03h | FREQNCO_LSB   | R/W |                |                            |                      | FREQ        | _NCO[7:0]    |            |               |          |  |

|                                                      | 4    | 04h | FREQNCO_LISB  | R/W |                |                            |                      | FREQ_       | NCO[15:8]    |            |               |          |  |

|                                                      | 5    | 05h | FREQNCO_UISB  | R/W |                |                            | F                    | FREQ_       | NCO[23:16]   |            |               |          |  |

| <u>}</u>                                             | 6    | 06h | FREQNCO_MSB   | R/W |                |                            | F                    | FREQ_       | NCO[31:24]   |            |               |          |  |

| 2                                                    | 7    | 07h | PHINCO_LSB    | R/W |                |                            |                      | PH_NCO[7:0] |              |            |               |          |  |

| 3                                                    | 8    | 08h | PHINCO_MSB    | R/W |                |                            |                      |             | PH_NCO[15:8] |            |               |          |  |

| All information provided in this document is subject | 9    | 09h | DAC_A_Cfg_1   | R/W | DAC_A_PD       | DAC_A_<br>SLEEP            | DAC_A_OFFSET[5:0]    |             |              |            |               |          |  |

| document is                                          | 10   | 0Ah | DAC_A_Cfg_2   | R/W | DAC_A<br>COAR  | _GAIN_<br>SE[1:0]          | DAC_A_GAIN_FINE[5:0] |             |              |            |               |          |  |

| 5                                                    | 11   | 0Bh | DAC_A_Cfg_3   | R/W | DAC_A<br>COAR  | _GAIN_<br>SE[3:2]          | DAC_A_OFFSET[11:6]   |             |              |            |               |          |  |

| logal disclaimore                                    | 12   | 0Ch | DAC_B_Cfg_1   | R/W | DAC_B_PD       | DAC_B_<br>SLEEP            | DAC_B_OFFSET[5:0]    |             |              |            |               |          |  |

| 3                                                    | 13   | 0Dh | DAC_B_Cfg_2   | R/W | DAC_B<br>COAR  | _GAIN_<br>SE[1:0]          | DAC_B_GAIN_FINE[5:0] |             |              |            | 5:0]          |          |  |

|                                                      | 14   | 0Eh | DAC_B_Cfg_3   | R/W |                | DAC_B_GAIN_<br>COARSE[3:2] |                      |             | DAC_B        | _OFFSET[11 | :6]           |          |  |

|                                                      | 15   | 0Fh | DAC_Cfg       | R/W |                |                            | -                    |             |              |            | MINUS_<br>3DB | NC<br>SH |  |

|                                                      | 16   | 10h | SYNC_Cfg      | R/W | SYNC_DIV       | SYNC_SEL                   |                      |             |              | -          |               | ,        |  |

| )<br>Z                                               | 26   | 1Ah | DAC_A_Aux_MSB | R/W |                |                            | AUX_A[9:2]           |             |              |            |               |          |  |

| NYD B \                                              | 27   | 1Bh | DAC_A_Aux_LSB | R/W | AUX_A_PD       |                            | - Al                 |             |              | AUX_       | A[1:0         |          |  |

| 2011                                                 | 28   | 1Ch | DAC_B_Aux_MSB | R/W |                |                            | AUX_B[9:2]           |             |              |            |               |          |  |

| All rights                                           | 29   | 1Dh | DAC_B_Aux_LSB | R/W | AUX_B_PD       |                            |                      | -           |              |            | AUX_          | B[1:0    |  |

## 10.2.4 Detailed register descriptions

Please refer to <u>Table 9</u> for the register overview and relevant default values. In the following tables, all the values shown in bold are the default values.

Table 10. COMMon register (address 00h) bit description

Default settings are shown highlighted.

| Bit | Symbol   | Access | Value | Description                                                    |

|-----|----------|--------|-------|----------------------------------------------------------------|

| 7   | 3W_SPI   | R/W    |       | serial interface bus type                                      |

|     |          |        | 0     | 4 wire SPI                                                     |

|     |          |        | 1     | 3 wire SPI                                                     |

| 6   | SPI_RST  | R/W    |       | serial interface reset                                         |

|     |          |        | 0     | no reset                                                       |

|     |          |        | 1     | performs a reset on all registers except 00h                   |

| 5   | CLK_SEL  | R/W    |       | data input latch                                               |

|     |          |        | 0     | at CLK rising edge                                             |

|     |          |        | 1     | at CLK falling edge                                            |

| 4   | -        | -      | -     | reserved                                                       |

| 3   | MODE_SEL | R/W    |       | input data mode                                                |

|     |          |        | 0     | dual port                                                      |

|     |          |        | 1     | interleaved                                                    |

| 2   | CODING   | R/W    |       | coding                                                         |

|     |          |        | 0     | binary                                                         |

|     |          |        | 1     | two's compliment                                               |

| 1   | IC_PD    | R/W    |       | power-down                                                     |

|     |          |        | 0     | disabled                                                       |

|     |          |        | 1     | all circuits (digital and analog, except SPI) are switched off |

| 0   | GAP_PD   | R/W    |       | internal bandgap power-down                                    |

|     |          |        | 0     | power-down disabled                                            |

|     |          |        | 1     | internal bandgap references are switched off                   |

Table 11. TXCFG register (address 01h) bit description

Default settings are shown highlighted.

| Bit | Symbol          | Access       | Value | Description                                                                              |

|-----|-----------------|--------------|-------|------------------------------------------------------------------------------------------|

| 7   | NCO_ON          | R/W          |       | NCO                                                                                      |

|     |                 |              | 0     | disabled (the NCO phase is reset to 0)                                                   |

|     |                 |              | 1     | enabled                                                                                  |

| 6   | NCO_LP_SEL      | D_LP_SEL R/W |       | low-power NCO                                                                            |

|     |                 |              | 0     | disabled                                                                                 |

|     |                 |              | 1     | NCO frequency and phase given by the five MSBs of the registers 06h and 08h respectively |

| 5   | INV_SIN_SEL R/W |              |       | x / (sin x) function                                                                     |

|     |                 |              | 0     | disabled                                                                                 |

|     |                 |              | 1     | enabled                                                                                  |

**Table 11. TXCFG register (address 01h) bit description** ...continued Default settings are shown highlighted.

| Bit    | Symbol             | Access | Value                                        | Description                                  |

|--------|--------------------|--------|----------------------------------------------|----------------------------------------------|

| 4 to 2 | MODULATION[2:0]    | R/W    |                                              | modulation                                   |

|        |                    |        | 000                                          | dual DAC: no modulation                      |

|        |                    |        | 001                                          | positive upper single sideband up-conversion |

|        |                    |        | 010                                          | positive lower single sideband up-conversion |

|        |                    | 011    | negative upper single sideband up-conversion |                                              |

|        |                    |        | 100                                          | negative lower single sideband up-conversion |

| 1 to 0 | INTERPOLATION[1:0] | R/W    |                                              | interpolation                                |

|        |                    |        | 01                                           | reserved                                     |

|        |                    |        | 10                                           | 4×                                           |

|        |                    |        | 11                                           | 8×                                           |

Table 12. PLLCFG register (address 02h) bit description

Default settings are shown highlighted.

| Bit    | Symbol             | Access | Value   | Description                         |                     |  |

|--------|--------------------|--------|---------|-------------------------------------|---------------------|--|

|        |                    |        |         | PLL ON                              | PLL OFF             |  |

| 7      | PLL_PD             | R/W    |         | PLL                                 |                     |  |

|        |                    |        | 0       | switched on                         |                     |  |

|        |                    |        | 1       | switched off                        |                     |  |