# Data Sheet: Technical Data

An Energy Efficient Solution by Freescale

MPR03X Rev 7, 7/2012

# Proximity Capacitive Touch Sensor Controller

The MPR03X is an Inter-Integrated Circuit Communication ( $I^2C$ ) driven Capacitive Touch Sensor Controller, optimized to manage two electrodes with interrupt functionality, or three electrodes with the interrupt disabled. It can accommodate a wide range of implementations due to increased sensitivity and a specialized feature set.

#### Features

- 6 µA supply current with two electrodes being monitored with 32 ms response time and IRQ enabled

- Compact 2 x 2 x 0.65 mm 8-lead µDFN package

- Supports up to 3 touch pads

- Only one external component needed

- Intelligent touch detection capacity

- 4 µA maximum shutdown current

- 1.71 V to 2.75 V operation

- Threshold based detection with hysteresis

- I<sup>2</sup>C interface, with optional IRQ

- Multiple devices in a system allow for up to 6 electrodes (need MPR032 with second I<sup>2</sup>C address)

- -40°C to +85°C operating temperature range

### Implementations

- Switch Replacements

- Touch Pads

### **Typical Applications**

- PC Peripherals

- MP3 Players

- Remote Controls

- Mobile Phones

- Lighting Controls

| ORDERING INFORMATION                                                                   |                |                   |        |      |               |

|----------------------------------------------------------------------------------------|----------------|-------------------|--------|------|---------------|

| Device Name Temperature Range Case Number Touch Pads I <sup>2</sup> C Address Shipping |                |                   |        |      |               |

| MPR031EPR2                                                                             | -40°C to +85°C | 1944 (8-Pin μDFN) | 3-pads | 0x4A | Tape and Reel |

| MPR032EPR2                                                                             | -40°C to +85°C | 1944 (8-Pin μDFN) | 3-pads | 0x4B | Tape and Reel |

© 2008, 2009, 2011, 2012 Freescale Semiconductor, Inc. All rights reserved.

# 1 Device Overview

### 1.1 Introduction

MPR03X is a small outline, low profile, low voltage touch sensor controller in a 2 mm x 2 mm  $\mu$ DFN which manages up to three touch pad electrodes. An I<sup>2</sup>C interface communicates with the host controller at data rates up to 400 kbits/sec. An optional interrupt output advises the host of electrode status changes. The interrupt output is a multiplexed with the third electrode output, so using the interrupt output reduces the number of electrode inputs to two. The MPR03X includes three levels of input signal filtering to detect pad input condition changes due to touch without any processing by the application.

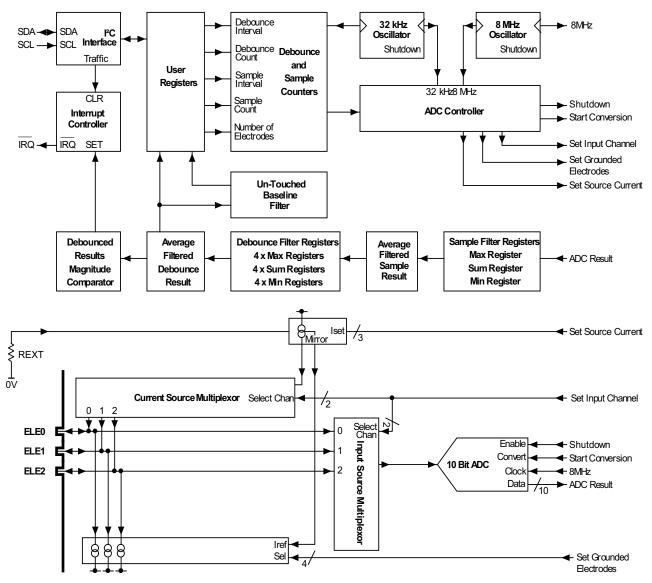

## 1.2 Internal Block Diagram

Figure 2. Functional Block Diagram

### MPR03X

2

# 2 External Signal Description

## 2.1 Device Pin Assignment

Table 1 shows the pin assignment for the MPR03X. For a more detailed description of the functionality of each pin, refer to the appropriate chapter.

### Table 1. Device Pin Assignment

| Pin | Name            | Function                                                                                         |

|-----|-----------------|--------------------------------------------------------------------------------------------------|

| 1   | SCL             | I <sup>2</sup> C Serial Clock Input                                                              |

| 2   | SDA             | I <sup>2</sup> C Serial Data I/O                                                                 |

| 3   | V <sub>SS</sub> | Ground                                                                                           |

| 4   | V <sub>DD</sub> | Positive Supply Voltage                                                                          |

| 5   | REXT            | Reference Resistor Connect a 75 k $\Omega$ ±1% resistor from REXT to V_SS                        |

| 6   | ELE0            | Electrode 0                                                                                      |

| 7   | ELE1            | Electrode 1                                                                                      |

| 8   | IRQ/ELE2        | Interrupt Output or Touch Electrode Input 2<br>IRQ is the active-low open-drain interrupt output |

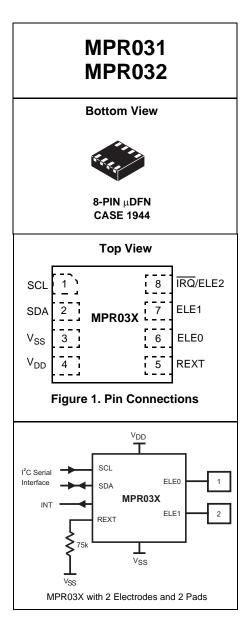

The package available for the MPR03X is a 2 x 2 mm 8 pin µDFN. The package and pinout is shown in Figure 3.

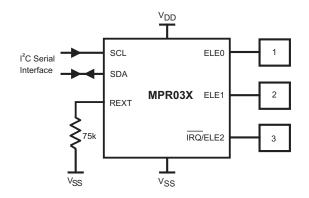

### 2.2 Recommended System Connections

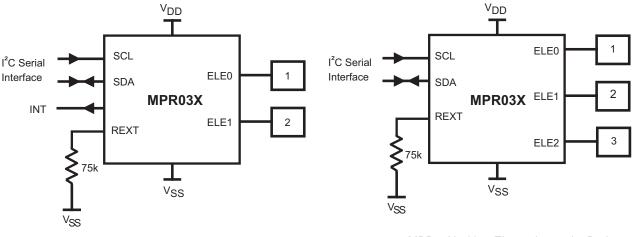

The MPR03X Capacitive Touch Sensor Controller requires one external passive component. As shown in Table 1, the REXT line should have a 75 k $\Omega$  connected from the pin to GND. This resistor needs to be 1% tolerance.

In addition to the one resistor, a bypass capacitor of 10  $\mu$ F should always be used between the V<sub>DD</sub> and V<sub>SS</sub> lines and a 4.7 k $\Omega$  pull-up resistor should be included on the IRQ. Note: This condition is when pin 8 is used for interrupt indication and not for electrode sensing.

The remaining two connections are SCL and SDA. Depending on the specific application, each of these control lines can be used by connecting them to a host controller. In the most minimal system, the SCL and SDA must be connected to a master  $I^2C$  interface to communicate with the MPR03X. All of the connections for the MPR03X are shown by the schematic in Figure 4.

### 2.3 Serial Interface

The MPR03X uses an  $I^2C$  Serial Interface. The  $I^2C$  protocol implementation and the specifics of communicating with the Touch Sensor Controller are detailed in the following sections.

### 2.3.1 Serial-Addressing

The MPR03X operates as a slave that sends and receives data through an I<sup>2</sup>C 2-wire interface. The interface uses a Serial Data Line (SDA) and a Serial Clock Line (SCL) to achieve bi-directional communication between master(s) and slave(s). A master (typically a microcontroller) initiates all data transfers to and from the MPR03X, and it generates the SCL clock that synchronizes the data transfer.

The MPR03X SDA line operates as both an input and an open-drain output. A pull-up resistor, typically  $4.7k\Omega$ , is required on SDA. The MPR03X SCL line operates only as an input. A pull-up resistor, typically  $4.7k\Omega$ , is required on SCL if there are multiple masters on the 2-wire interface, or if the master in a single-master system has an open-drain SCL output.

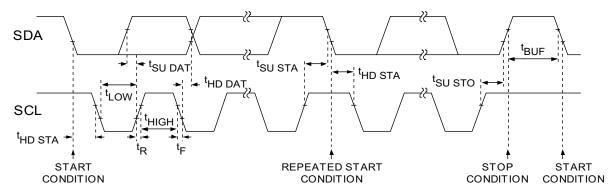

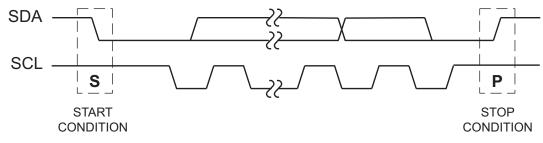

Each transmission consists of a START condition (Figure 5) sent by a master, followed by the MPR03X's 7-bit slave address plus R/W bit, a register address byte, one or more data bytes, and finally a STOP condition.

Figure 5. Wire Serial Interface Timing Details

### 2.3.2 Start and Stop Conditions

Both SCL and SDA remain high when the interface is not busy. A master signals the beginning of a transmission with a START (S) condition by transitioning SDA from high to low while SCL is high. When the master has finished communicating with the slave, it issues a STOP (P) condition by transitioning SDA from low to high while SCL is high. The bus is then free for another transmission.

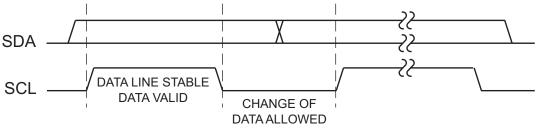

Figure 6. Bit Transfer

### 2.3.3 Bit Transfer

One data bit is transferred during each clock pulse (Figure 7). The data on SDA must remain stable while SCL is high.

Figure 7. Stop and Start Conditions

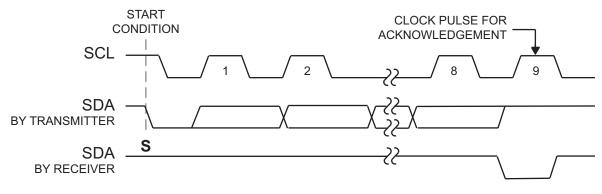

### 2.3.4 Acknowledge

The acknowledge bit is a clocked 9<sup>th</sup> bit (Figure 8) which the recipient uses to handshake receipt of each byte of data. Thus each byte transferred effectively requires 9 bits. The master generates the 9<sup>th</sup> clock pulse, and the recipient pulls down SDA during the acknowledge clock pulse, such that the SDA line is stable low during the high period of the clock pulse. When the master is transmitting to the MPR03X, the MPR03X generates the acknowledge bit, since the MPR03X is the recipient. When the MPR03X is transmitting to the master, the master generates the acknowledge bit, since the master is the recipient.

Figure 8. Acknowledge

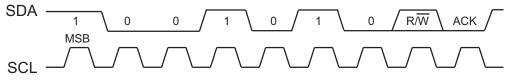

### 2.3.5 The Slave Address

The MPR03X has a 7-bit long slave address (Figure 9). The bit following the 7-bit slave address (bit eight) is the R/W bit, which is low for a write command and high for a read command.

Figure 9. Slave Address

The MPR03X monitors the bus continuously, waiting for a START condition followed by its slave address. When a MPR03X recognizes its slave address, it acknowledges and is then ready for continued communication.

The MPR031 and MPR032 slave addresses are show in Table 2.

| Table 2.    |                          |  |  |

|-------------|--------------------------|--|--|

| Part Number | I <sup>2</sup> C Address |  |  |

| MPR031      | 0x4A                     |  |  |

| MPR032      | 0x4B                     |  |  |

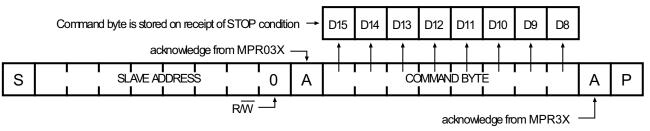

A write to the MPR03X comprises the transmission of the MPR03X's keyscan slave address with the R/W bit set to 0, followed by at least one byte of information. The first byte of information is the command byte. The command byte determines which register of the MPR03X is to be written by the next byte, if received. If a STOP condition is detected after the command byte is received, the MPR03X takes no further action (Figure 10) beyond storing the command byte. Any bytes received after the command byte are data bytes.

Figure 10. Command Byte Received

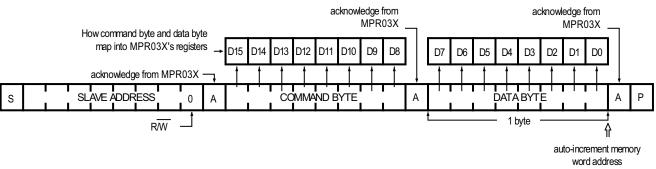

Any bytes received after the command byte are data bytes. The first data byte goes into the internal register of the MPR03X selected by the command byte (Figure 11).

Figure 11. Command and Single Data Byte Received

If multiple data bytes are transmitted before a STOP condition is detected, these bytes are generally stored in subsequent MPR03X internal registers because the command byte address generally auto-increments (Section 2.4).

## 2.3.7 Message Format for Reading the MPR03X

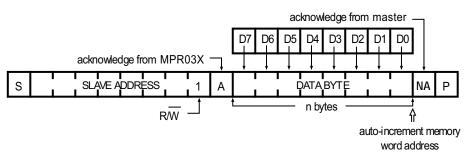

MPR03X is read using MPR03X's internally stored register address as address pointer, the same way the stored register address is used as address pointer for a write. The pointer generally auto-increments after each data byte is read using the same rules as for a write (Table 5). Thus, a read is initiated by first configuring MPR03X's register address by performing a write (Figure 10) followed by a repeated start. The master can now read 'n' consecutive bytes from MPR03X, with first data byte being read from the register addressed by the initialized register address.

Figure 12. Reading MPR03X

### 2.3.8 Operation with Multiple Master

The application should use repeated starts to address the MPR03X to avoid bus confusion between  $I^2C$  masters.On a  $I^2C$  bus, once a master issues a start/repeated start condition, that master owns the bus until a stop condition occurs. If a master that does not own the bus attempts to take control of that bus, then improper addressing may occur. An address may always be rewritten to fix this problem. Follow  $I^2C$  protocol for multiple master configurations.

## 2.4 Register Address Map

#### Table 3. Register Address Map

| Register                         | Register Address | Burst Mode<br>Auto-Increment<br>Address |

|----------------------------------|------------------|-----------------------------------------|

| Touch Status Register            | 0x00             |                                         |

| ELE0 Filtered Data Low Register  | 0x02             |                                         |

| ELE0 Filtered Data High Register | 0x03             |                                         |

| ELE1 Filtered Data Low Register  | 0x04             |                                         |

| ELE1 Filtered Data High Register | 0x05             |                                         |

| ELE2 Filtered Data Low Register  | 0x06             |                                         |

| ELE2 Filtered Data High Register | 0x07             |                                         |

| ELE0 Baseline Value Register     | 0x1A             |                                         |

| ELE1 Baseline Value Register     | 0x1B             |                                         |

| ELE2 Baseline Value Register     | 0x1C             |                                         |

| Max Half Delta Register          | 0x26             |                                         |

| Noise Half Delta Register        | 0x27             | Register Address + 1                    |

| Noise Count Limit Register       | 0x28             |                                         |

| ELE0 Touch Threshold Register    | 0x29             |                                         |

| ELE0 Release Threshold Register  | 0x2A             |                                         |

| ELE1 Touch Threshold Register    | 0x2B             |                                         |

| ELE1 Release Threshold Register  | 0x2C             |                                         |

| ELE2 Touch Threshold Register    | 0x2D             |                                         |

| ELE2 Release Threshold Register  | 0x2E             |                                         |

| AFE Configuration Register       | 0x41             |                                         |

| Filter Configuration Register    | 0x43             |                                         |

| Electrode Configuration Register | 0x44             | 0x00                                    |

# 3 Functional Overview

## 3.1 Introduction

The MPR03X has an analog front, a digital filter, and a touch recognition system. This data interpretation can be done many different ways but the method used in the MPR03X is explained in this chapter.

# 3.2 Understanding the Basics

MPR03X is a touch pad controller which manages two or three touch pad electrodes. An I<sup>2</sup>C interface communicates with the host, and an optional interrupt output advises the host of electrode status changes. The interrupt output is a multiplexed function with the third electrode input, so using the interrupt output reduces the number of electrode inputs to two.

The primary application for MPR03X is the management of user interface touch pads. Monitoring touch pads involves detecting small changes of pad capacitance. MPR03X incorporates a self calibration function which continually adjusts the baseline capacitance for each individual electrode. Therefore, the host only has to configure the delta thresholds to interpret a touch or release.

MPR03X uses a state machine to operate a capacitive measurement engine to analyze the electrodes and determine whether a pad has been touched or released. Between measurements the MPR03X draws negligible current. The application controls MPR03X's configuration, making trade-offs between noise rejection, touch response time, and power consumption.

## 3.3 Implementation

The touch sensor system can be tailored to specific applications by varying the following: a capacitance detector, a raw data low pass filter, a baseline management system, and a touch detection system. In the following sections, the functionality and configuration of each block will be described.

Electrodes can be connected to the MPR03X in two different configurations, one with an IRQ and one without (Figure 13).

MPR03X with 2 Electrodes and 2 Pads

MPR03X with 3 Electrodes and 3 Pads

Figure 13. MPR03X Pad and Interrupt Connection Options

# 4 Modes of Operation

## 4.1 Introduction

MPR03X's operation modes are Stop, Run1, and Run2. Stop mode is the start-up and configuration mode.

## 4.2 Stop Mode

In Stop mode, the MPR03X does not monitor any of the electrodes. This mode is the lowest power state.

### 4.2.1 Initial Power Up

On power-up, the device is in Stop mode, registers are reset to the initial values shown in Table 4, and MPR03X starts in Stop mode drawing minimal supply current. The user configurable pin IRQ/ELE2 defaults to being the interrupt output IRQ function. IRQ is reset on power-up, and so defaults to logic high. Since the IRQ is an open-drain output, IRQ will be high impedance.

#### Table 4. Power-Up Register Configurations

| Register                         | Power-Up Condition                                                                                    | Register Address | HEX Value |

|----------------------------------|-------------------------------------------------------------------------------------------------------|------------------|-----------|

| Touch Status Register            | Cleared                                                                                               | 0x00             | 0x00      |

| ELE0 Filtered Data Low Register  | Cleared                                                                                               | 0x02             | 0x00      |

| ELE0 Filtered Data High Register | Cleared                                                                                               | 0x03             | 0x00      |

| ELE1 Filtered Data Low Register  | Cleared                                                                                               | 0x04             | 0x00      |

| ELE1 Filtered Data High Register | Cleared                                                                                               | 0x05             | 0x00      |

| ELE2 Filtered Data Low Register  | Cleared                                                                                               | 0x06             | 0x00      |

| ELE2 Filtered Data High Register | Cleared                                                                                               | 0x07             | 0x00      |

| ELE0 Baseline Value Register     | Cleared                                                                                               | 0x1A             | 0x00      |

| ELE1 Baseline Value Register     | Cleared                                                                                               | 0x1B             | 0x00      |

| ELE2 Baseline Value Register     | Cleared                                                                                               | 0x1C             | 0x00      |

| Max Half Delta Register          | Cleared                                                                                               | 0x26             | 0x00      |

| Noise Half Delta Register        | Cleared                                                                                               | 0x27             | 0x00      |

| Noise Count Limit Register       | Cleared                                                                                               | 0x28             | 0x00      |

| ELE0 Touch Threshold Register    | Cleared                                                                                               | 0x29             | 0x00      |

| ELE0 Release Threshold Register  | Cleared                                                                                               | 0x2A             | 0x00      |

| ELE1 Touch Threshold Register    | Cleared                                                                                               | 0x2B             | 0x00      |

| ELE1 Release Threshold Register  | Cleared                                                                                               | 0x2C             | 0x00      |

| ELE2 Touch Threshold Register    | Cleared                                                                                               | 0x2D             | 0x00      |

| ELE2 Release Threshold Register  | Cleared                                                                                               | 0x2E             | 0x00      |

| AFE Configuration Register       | 6 AFE samples, 16 µA charge current                                                                   | 0x41             | 0x10      |

| Filter Configuration Register    | 16 ms detection sample interval,<br>4 samples for the second level filter,<br>0.5 $\mu$ S charge time | 0x43             | 0x24      |

| Electrode Configuration Register | Stop mode. ELE2/IRQ pin is interrupt function,                                                        | 0x44             | 0x00      |

### 4.2.2 Stop Mode Usage

In order to set the configuration registers, the device must be in stop mode. This is achieved by setting the EleEn field in the Electrode Configuration register to zero.

### 4.3 Run1 Mode

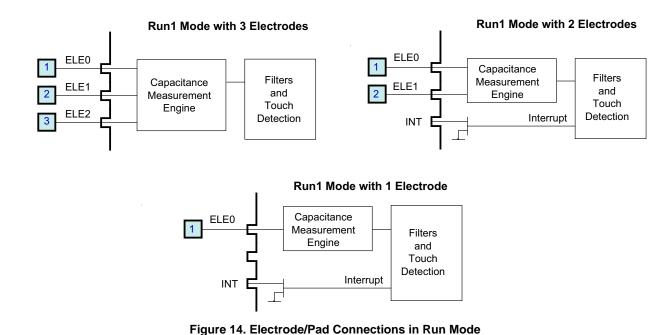

In Run1 Mode, the MPR03X monitors 1, 2, or 3 electrodes which are connected to a user defined array of touch pads. When only 1 or 2 electrodes are selected, the IRQ/ELE2 pin is automatically configured as an open drain interrupt output.

When 3 electrodes are selected in Run1 Mode, the IRQ/ELE2 pin becomes the third electrode input, ELE2 (Figure 14).

### 4.4 Run2 Mode

In Run2 Mode, all enabled electrodes act as a single electrode by internally connecting the electrode pins together. The entire surface of all the touch pads is used as a single pad, increasing the total area of the conductor.

When 2 electrodes are selected in Run2 Mode, the IRQ/ELE2 pin is automatically configured as an open drain interrupt output. When 3 electrodes are selected, the IRQ/ELE2 pin becomes the third electrode input, ELE2 (Figure 15).

Figure 15. Electrode/Pad Connections in Area Detection Mode

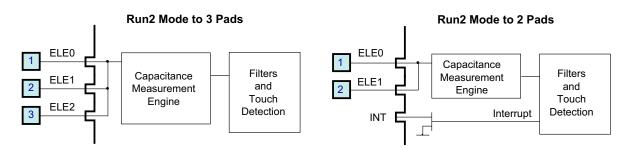

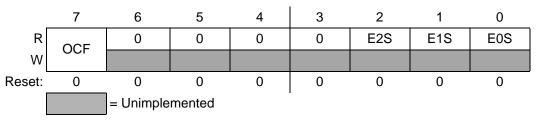

### 4.5 Electrode Configuration Register

The Electrode Configuration Register manages the configuration of the Electrode outputs in addition to the mode of the part. The address of the Electrode Configuration Register is 0x44.

| Field          | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6<br>CalLock   | <ul> <li>Calibration Lock – The Calibration Lock bit selects whether calibration is enabled or disabled.</li> <li>0 Enabled – In this state baseline calibration is enabled.</li> <li>1 Disabled – In this state baseline calibration is disabled.</li> </ul>                                                                                                                                                                                                                                         |

| 5:4<br>ModeSel | <ul> <li>Mode Select – The Mode Select field selects which Run Mode the sensor will operate in. This register is ignored when in Stop Mode.</li> <li>00 Encoding 0 – Run1 Mode is enabled.</li> <li>01 Encoding 1 – Run2 Mode is enabled.</li> <li>10 Encoding 2 – Run2 Mode is enabled.</li> <li>11 Encoding 3 – Run2 Mode is enabled.</li> </ul>                                                                                                                                                    |

| 3:0<br>EleEn   | Electrode Enable – The Electrode Enable Field selects the electrode and IRQ<br>functionality.<br>0000 Encoding 0 – Stop Mode<br>0001 Encoding 1 – Run Mode with ELE0 is enabled, ELE1 is disabled, IRQ is<br>enabled.<br>0010 Encoding 2 – Run Mode with ELE0 is enabled, ELE1 is enabled, IRQ is<br>enabled.<br>0011 Encoding 3 – Run Mode with ELE0 is enabled, ELE1 is enabled, ELE2 is<br>enabled.<br>~<br>1111 Encoding 15 – Run Mode with ELE0 is enabled, ELE1 is enabled, ELE2 is<br>enabled. |

# 5 Output Mechanisms

### 5.1 Introduction

The MPR03X has three outputs: the touch status, values from the second level filter (Section 8.3), and the calibrated baseline values. The application can either use the touch status or a combination of second level filter data with the baseline data to determine when a touch occurs.

## 5.2 Touch Status

Each Electrode has an associated single bit that denotes whether or not the pad is currently touched. This output is generated using the touch threshold and release threshold registers to determine when a pad is considered touched or untouched. Configuration of this system is discussed in Section 9.

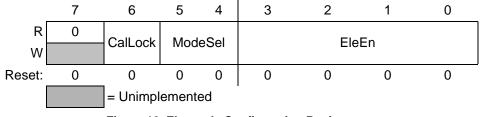

### 5.2.1 Touch Status Register

The Touch Pad Status Register is a read only register for determining the current status of the touch pad. The  $I^2C$  slave address of the Touch Pad Status Register is 0x00.

Figure 17. Touch Status Register

#### Table 6. Touch Pad Status Register Field Descriptions

| Field    | Description                                                                                                                                                                                                                                                                                                                                                                                                |

|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>OCF | <ul> <li>Over Current Flag – The Over Current Flag shows when too much current is on the REXT pin. If it is set all other status flags and registers are cleared and the device is set to Stop mode. When OCF is set, the MPR03X cannot be put back into a Run mode.</li> <li>0 – Current is within limits.</li> <li>1 – Current is above limits. Writing a 1 to this field will clear the OCF.</li> </ul> |

| 2<br>E2S | Electrode 2 Status – The Electrode 2 Status bit shows touched or not touched.<br>0 – Not Touched<br>1 – Touched                                                                                                                                                                                                                                                                                            |

| 1<br>E1S | Electrode 1 Status – The Electrode 1 Status bit shows touched or not touched.<br>0 – Not Touched<br>1 – Touched                                                                                                                                                                                                                                                                                            |

| 0<br>E0S | Electrode 0 Status – The Electrode 0 Status bit shows touched or not touched.<br>0 – Not Touched<br>1 – Touched                                                                                                                                                                                                                                                                                            |

## 5.3 Filtered Data

Each electrode has an associated filtered output. This output is generated through register settings and a low pass filter implementation (Section 8.4).

### 5.3.1 Filtered Data Low Register

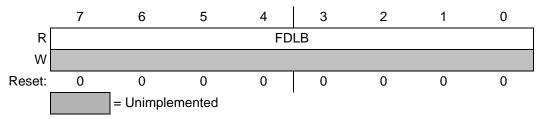

The Filtered Data Low register contains the data on each of the electrodes. It is paired with the Filtered Data High register for reading the 10 bit A/D value. The address of the ELE0 Filtered Data Low register is 0x02. The address of the ELE1 Filtered Data Low register is 0x04. The address of the ELE2 Filtered Data Low register is 0x06.

Figure 18. Filtered Data Low Register

#### Table 7. Filtered Data Low Register Field Descriptions

| Field       | Description                                                                                                                                                               |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0<br>FDLB | Filtered Data Low Byte – The Filtered Data Low Byte displays the lower 8 bits of<br>the 10 bit filtered A/D reading.<br>00000000 Encoding 0<br>~<br>11111111 Encoding 255 |

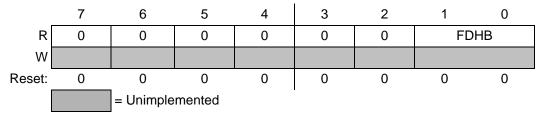

### 5.3.2 Filtered Data High Register

The Filtered Data High register contains the data on each of the electrodes. It is paired with the Filtered Data Low register for reading the 10 bit A/D value. The address of the ELE0 Filtered Data High register is 0x03. The address of the ELE1 Filtered Data High register is 0x05. The address of the ELE2 Filtered Data High register is 0x07.

#### Figure 19. Filtered Data High Register

#### Table 8. Filtered Data High Register Field Descriptions

| Field | Description                                                                         |

|-------|-------------------------------------------------------------------------------------|

| 7:0   | Filtered Data High Bits – The Filtered Data High Bits displays the higher 2 bits of |

| FDHB  | the 10 bit filtered A/D reading.                                                    |

|       | 00 Encoding 0                                                                       |

|       | ~                                                                                   |

|       | 11 Encoding 3                                                                       |

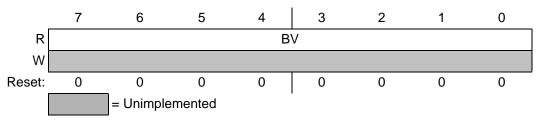

### 5.4 Baseline Values

In addition to the second level filter data, the data from the baseline filter (or third level filter) is also displayed. In this case, the least two significant bits are removed before the 10-bit value is displayed in the register.

### 5.4.1 Baseline Value Register

The Baseline Value register contains the third level filtered data on each of the electrodes. It is a truncated 10 bit A/D value displayed in the 8 bit register. The address of the ELE0 Baseline Value register is 0x1A. The address of the ELE1 Baseline Value register is 0x1B. The address of the ELE2 Baseline Value register is 0x1C.

Figure 20. Filtered Data High Register

Table 9. Filtered Data High Register Field Descriptions

| Field | Description                                                                                                                                                                                                                                                     |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BV    | Baseline Value – The Baseline Value byte displays the higher 8 bits of the 10 bit<br>baseline value.<br>00000000 Encoding 0 – The 10 bit baseline value is between 0 and 3.<br>~<br>11111111 Encoding 255 – The 10 bit baseline value is between 1020 and 1023. |

# 6 Interrupts

### 6.1 Introduction

The MPR03X has one interrupt output that is triggered on any touch related event. The interrupts trigger on both the up or down motion of a finger as defined by a set of configurable thresholds.

# 6.2 Triggering an Interrupt

An interrupt is asserted any time data changes in the Touch Status Register (Section 5.2). This means that if an electrode touch or release occurs, an interrupt will alert the application of the change.

## 6.3 Interrupt Handling

The MPR03X has one interrupt output that is asserted on any touch related event. The interrupts trigger on both the up or down motion of a finger as defined by a set of configurable thresholds as described in Section 9. To service an interrupt, the application must read the Touch Status Register (Section 5.2) and determine the current condition of the system. As soon as an  $I^2C$  read takes place the MPR03X will release the interrupt.

# 6.4 IRQ Pin

The  $\overline{IRQ}$  pin is an open-drain latching interrupt output which requires an external pull-up resistor. The pin will latch down based on the conditions in Section 6.2. The pin will de-assert when an I<sup>2</sup>C transaction reads from the MPR03X.

# 7 Theory of Operation

# 7.1 Introduction

The MPR03X utilizes the principle that a capacitor holds a fixed amount of charge at a specific electric potential. Both the implementation and the configuration will be described in this section.

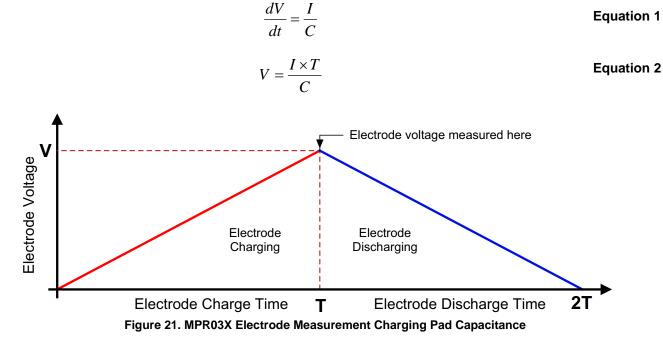

### 7.2 Capacitance Measurement

The basic measurement technique used by the MPR03X is to charge up the capacitor C on one electrode input with a DC current I for a time T (the charge time). Before measurement, the electrode input is grounded, so the electrode voltage starts from 0 V and charges up with a slope, Equation 1, where C is the pad capacitance on the electrode (Figure 21). All of the other electrodes are grounded during this measurement. At the end of time T, the electrode voltage is measured with a 10 bit ADC. The voltage is inversely proportional to capacitance according to Equation 2. The electrode is then discharged back to ground at the same rate it was charged.

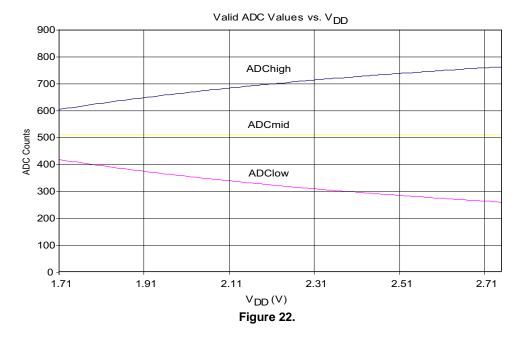

When measuring capacitance there are some inherent restrictions due to the methodology used. On the MPR03X the voltage after charging must be in the range that is shown in Figure 22.

The valid operating range of the electrode charging source is 0.7V to  $(V_{DD}-.7)V$ . This means that for a given  $V_{DD}$  the valid ADC (voltage visible to the digital interface) range is given by

$ADC_{low} = \frac{.7}{V_{DD}} (1024) , \qquad \text{Equation 3}$ and  $(V_{DD} = 7) \qquad \text{Equation 4}$

$$ADC_{high} = \frac{(V_{DD} - .7)}{V_{DD}} (1024)$$

Equation 4

These equations are represented in the graph. In the nominal case of  $V_{DD} = 1.8V$  the ADC range is shown below in Table 10.

Table 10.

| VDD | ADChigh  | ADClow   | ADCmid |

|-----|----------|----------|--------|

| 1.8 | 625.7778 | 398.2222 | 512    |

Any ADC counts outside of the range shown are invalid and settings must be adjusted to be within this range. If capacitance variation is of importance for an application after the current output, charge time and supply voltage are determined then the following equations can be used. The valid range for capacitance is calculated by using the minimum and maximum ADC values in the capacitance equation. Substituting the low and high ADC equations into the capacitance equation yields the equations for the minimum and maximum capacitance values which are

$$C_{low} = \frac{I \times T}{V_{DD} - .7}$$

and  $C_{high} = \frac{I \times T}{.7}$ . Equation 5

#### 7.3 Sensitivity

The sensitivity of the MPR03X is relative to the capacitance range being measured. Given the ADC value, current and time settings capacitance can be calculated,

$$C = \frac{I \times T \times 1024}{V_{DD} \times ADC}$$

Equation 6

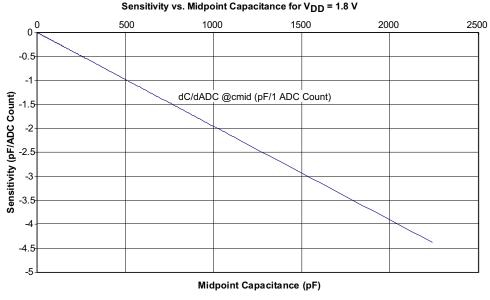

For a given capacitance the sensitivity can be measured by taking the derivative of this equation. The result of this is the following equation, representing the change in capacitance per one ADC count, where the ADC in the equation represents the current value.

$$\frac{dC}{dADC} = -\frac{I \times T \times 1024}{V_{DD} \times ADC^2}$$

Equation 7

This relationship is shown in the following graph by taking the midpoints off all possible ranges by varying the current and time settings. The midpoint is assumed to be 512 for ADC and the nominal supply voltage of 1.8V is used.

Smaller amounts of change indicate increased sensitivity for the capacitance sensor. Some sample values are shown in Table 11.

| Table ' | 11 |  |

|---------|----|--|

|---------|----|--|

| pF  | Sensitivity (pF/ADC count) |

|-----|----------------------------|

| 10  | -0.01953                   |

| 100 | -0.19531                   |

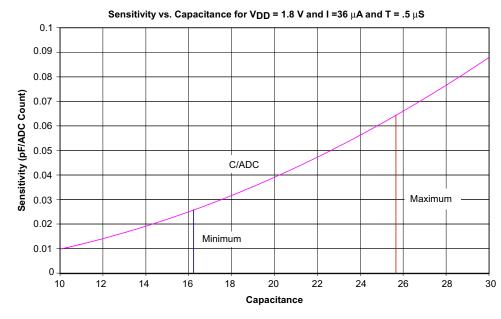

In the above cases, the capacitance is assumed to be in the middle of the range for specific settings. Within the capacitance range the equation is nonlinear, thus the sensitivity is best with the lowest capacitance. This graph shows the sensitivity derivative reading across the valid range of capacitances for a set I, T, and  $V_{DD}$ . For simple small electrodes (that are approximately 21 pF) and a nominal 1.8V supply the following graph is representative of this effect.

# 7.4 Configuration

From the implementation above, there are two elements that can be configured to yield a wide range of capacitance readings ranging from 0.455 pF to 2874.39 pF. The two configurable components are the electrode charge current and the electrode charge time.

The electrode charge current can be configured to equal a range of values between 1  $\mu$ A and 63  $\mu$ A. This value is set in the CDC in the AFE Configuration register (Section 7.4.1).

The electrode charge time can be configured to equal a range of values between 500 ns and 32  $\mu$ S. This value is set in the CDT in the Filter Configuration Register (Section 8.3.1).

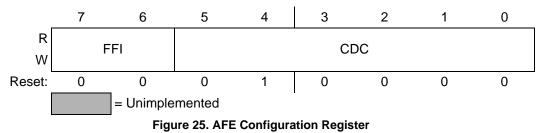

### 7.4.1 AFE Configuration Register

The AFE (Analog Front End) Configuration Register is used to set both the Charge/Discharge Current and the number of samples taken in the lowest level filter. The address of the AFE Configuration Register is 0x41.

#### Table 12. AFE Configuration Register Field Descriptions

| Field | Description                                                                               |  |  |  |  |

|-------|-------------------------------------------------------------------------------------------|--|--|--|--|

| 7:6   | First Filter Iterations – The first filter iterations field selects the number of samples |  |  |  |  |

| FFI   | taken as input to the first level of filtering.                                           |  |  |  |  |

|       | 00 Encoding 0 – Sets samples taken to 6                                                   |  |  |  |  |

|       | 01 Encoding 1 – Sets samples taken to 10                                                  |  |  |  |  |

|       | 10 Encoding 2 – Sets samples taken to 18                                                  |  |  |  |  |

|       | 11 Encoding 3 – Sets samples taken to 34                                                  |  |  |  |  |

| 5:0   | Charge Discharge Current – The Charge Discharge Current field selects the                 |  |  |  |  |

| CDC   | supply current to be used when charging and discharging an electrode.                     |  |  |  |  |

|       | 000000 Encoding 0 – Disables Electrode Charging                                           |  |  |  |  |

|       | 000001 Encoding 1 – Sets the current to 1uA                                               |  |  |  |  |

|       | ~                                                                                         |  |  |  |  |

|       | 111111 Encoding 63 – Sets the current to 63uA                                             |  |  |  |  |

# 8 Filtering

### 8.1 Introduction

The MPR03X has three levels of filtering. The first and second level filters will allow the application to condition the signal for undesired input variation. The third level filter can be configured to reject touch stimulus and be used as a baseline for touch detection. Each level of filtering will be further described in this section.

# 8.2 First Level

The first level filter is designed to filter high frequency noise by averaging samples taken over short periods of time. The number of samples can be configured to equal a set of values ranging from 6 to 34 samples. This value is set by the FFI in the AFE Configuration Register (Section 7.4.1). The timing of this filter is also determined by the configuration of the electrode charge time in the Filter Configuration Register (Section 8.3.1).

Note that the electrode charge time must be configured for the capacitance in the application. The resulting value will affect the period of the first level filter.

## 8.3 Second Level

The second level filter is designed to filter low frequency noise and reject false touches due to inconsistent data. The number of samples can be configured to equal a set of values ranging from 4 to 18. This value is set by the SFI in the Filter Configuration Register (Section 8.3.1). The timing of this filter is also determined by the configuration of ESI in the Filter Configuration Register (Section 8.3.1).

Note that the ESI (Electrode Sample Interval) must be configured to accommodate the low power requirements of a system. Thus, the resulting value will affect the period of the second level filter.

The raw data from the second level of filtering is output in the Filtered Data High and Filtered Data Low registers, as shown in Section 5.3.

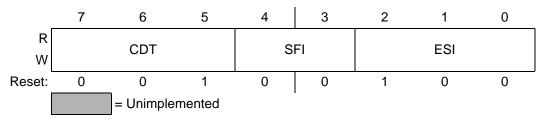

### 8.3.1 Filter Configuration Register

The Filter Configuration register is used to set the electrode charge/discharge time (CDT), second level filter iteration (SFI), and electrode sample intervals (ESI). The address of the Electrode Configuration Register is 0x43.

Figure 26. Filter Configuration Register

| Field | Description                                                                         |

|-------|-------------------------------------------------------------------------------------|

| 7:5   | Charge Discharge Time – The Charge Discharge Time field selects the amount          |

| CDT   | of time an electrode charges and discharges.                                        |

|       | 000 Encoding 0 – Invalid                                                            |

|       | 001 Encoding 1 – Time is set to 0.5 μs                                              |

|       | 010 Encoding 2 – Time is set to 1 μs                                                |

|       | ~                                                                                   |

|       | 111 Encoding 7 – Time is set to 32 μs.                                              |

| 4:3   | Second Filter Iterations – The Second Filter Iterations field selects the number of |

| SFI   | samples taken for the second level filter.                                          |

|       | 00 Encoding 0 – Number of samples is set to 4                                       |

|       | 01 Encoding 1 – Number of samples is set to 6                                       |

|       | 10 Encoding 2 – Number of samples is set to 10                                      |

|       | 11 Encoding 3 – Number of samples is set to 18                                      |

| 2:0   | Electrode Sample Interval – The Electrode Sample Interval field selects the         |

| ESI   | period between samples used for the second level of filtering.                      |

|       | 000 Encoding 0 – Period set to 1 ms                                                 |

|       | 001 Encoding 1 – Period set to 2 ms                                                 |

|       | ~                                                                                   |

|       | 111 Encoding 7 – Period set to 128 ms                                               |

#### Table 13. Filter Configuration Register Field Descriptions

### 8.4 Third Level Filter

The Third Level Filter is designed for varying implementations. It can be used as either an additional low pass filter for the electrode data or a baseline for touch detection. For it to function as a baseline filter, it must be used in conjunction with the touch detection system described in the next chapter. To use the filter as an additional layer for low pass filtering, the touch detection system must be disabled by setting all of the touch thresholds to zero (refer to Section 9.2). Although, in most cases the third level of filter will be used as a baseline filter. The primary difference between these implementations is this: if a touch is detected the baseline filter will hold its current value until the touch is released. The touch/release configuration will be described in Chapter 9.

When a touch is not currently detected, the baseline filter will operate based on a few conditions. These are configured through a set of registers including the Max Half Delta Register, the Noise Half Delta Register, and the Noise Count Limit.

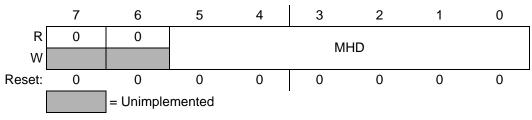

### 8.4.1 Max Half Delta Register

The Max Half Delta register is used to set the Max Half Delta for the Third Level Filter. The address of the Max Half Delta Register is 0x26.

Figure 27. Max Half Delta Register

| Field      | Description                                                                                                                                                                                                                                                                |  |  |  |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 5:0<br>MHD | Max Half Delta – The Max Half Delta determines the largest magnitude of<br>variation to pass through the third level filter.<br>000000 DO NOT USE THIS CODE<br>000001 Encoding 1 – Sets the Max Half Delta to 1<br>~<br>111111 Encoding 63 – Sets the Max Half Delta to 63 |  |  |  |

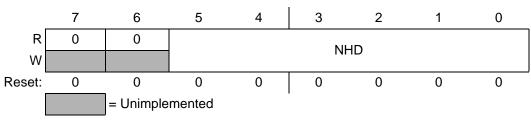

### 8.4.2 Noise Half Delta Register

The Noise Half Delta register is used to set the Noise Half Delta for the third level filter. The address of the Noise Half Delta Register is 0x27.

Figure 28. Noise Half Delta Register

#### Table 15. Noise Half Delta Register Field Descriptions

| Field | Description                                                                    |  |  |  |  |

|-------|--------------------------------------------------------------------------------|--|--|--|--|

| 5:0   | Noise Half Delta – The Noise Half Delta determines the incremental change when |  |  |  |  |

| NHD   | non-noise drift is detected.                                                   |  |  |  |  |

|       | 000000 DO NOT USE THIS CODE                                                    |  |  |  |  |

|       | 000001 Encoding 1 – Sets the Noise Half Delta to 1                             |  |  |  |  |

|       | ~                                                                              |  |  |  |  |

|       | 111111 Encoding 63 – Sets the Noise Half Delta to 63                           |  |  |  |  |

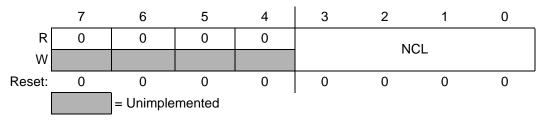

### 8.4.3 Noise Count Limit Register

The Noise Count Limit register is used to set the Noise Count Limit for the Third Level Filter. The address of the Noise Half Delta Register is 0x28.

Figure 29. Noise Count Limit Register

#### Table 16. Noise Count Limit Register Field Descriptions

| Field | Description                                                                                                                                                                                                                                                                    |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3:0   | Noise Count Limit – The Noise Count Limit determines the number of samples consecutively                                                                                                                                                                                       |

| NCL   | greater than the Max Half Delta necessary before it can be determined that it is non-noise.<br>0000 Encoding 0 – Sets the Noise Count Limit to 1 (every time over Max Half Delta)<br>0001 Encoding 1 – Sets the Noise Count Limit to 2 consecutive samples over Max Half Delta |

|       | ~<br>1111 Encoding 15 – Sets the Noise Count Limit to 15 consecutive samples over Max Half Delta                                                                                                                                                                               |

# 9 Touch Detection

## 9.1 Introduction

The MPR03X uses a threshold based system to determine when touches occur. This section will describe that mechanism.

### 9.2 Thresholds

When a touch pad is pressed, an increase in capacitance will be generated. The resulting effect will be a reduction in the ADC counts. When the difference between the second level filter value and the third level filter value is significant, the system will detect a touch. When a touch is detected, there are a couple of effects: the third level filter output becomes fixed (refer to Section 8.4), an interrupt is generated (refer to Section 6), and the touch status register (Section 5.2) is updated.

The touch detection system is controlled using two threshold registers for each independent electrode. The Touch Threshold register represents the delta at which the system will trigger a touch. The Release Threshold represents the difference at which a release would be detected. In either case the system will respond by changing the previously mentioned items.

### 9.2.1 Touch Threshold Register

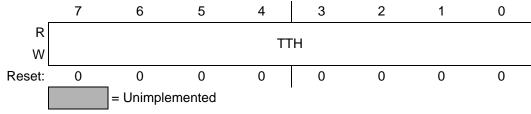

The Touch Threshold Register is used to set the touch threshold for each of the electrodes. The address of the ELE0 Touch Threshold Register is 0x29. The address of the ELE1 Touch Threshold Register is 0x2B. The address of the ELE2 Touch Threshold Register is 0x2D.

Figure 30. Touch Threshold Register

### Table 17. Touch Threshold Register Field Descriptions

| Field | Description                                                                    |

|-------|--------------------------------------------------------------------------------|

| 7:0   | Touch Threshold – The Touch Threshold Byte sets the trip point for detecting a |

| TTH   | touch.                                                                         |

|       | 00000000 Encoding 0                                                            |

|       | ~                                                                              |

|       | 11111111 Encoding 255                                                          |

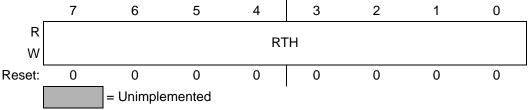

### 9.2.2 Release Threshold Register

The Release Threshold Register is used to set the release threshold for each of the electrodes. The address of the ELE0 Release Threshold Register is 0x2A. The address of the ELE1 Release Threshold Register is 0x2C. The address of the ELE2 Release Threshold Register is 0x2E.

Figure 31. Release Threshold Register

#### Table 18. Release Threshold Register Field Descriptions

| Field | Description                                                                      |  |  |  |  |

|-------|----------------------------------------------------------------------------------|--|--|--|--|

| 7:0   | Release Threshold – The Release Threshold Byte sets the trip point for detecting |  |  |  |  |

| RTH   | a touch.                                                                         |  |  |  |  |

|       | 00000000 Encoding 0                                                              |  |  |  |  |

|       | ~                                                                                |  |  |  |  |

|       | 11111111 Encoding 255                                                            |  |  |  |  |

# Appendix A Electrical Characteristics

### A.1 Introduction

This section contains electrical and timing specifications.

### A.2 Absolute Maximum Ratings

Absolute maximum ratings are stress ratings only, and functional operation at the maxima is not guaranteed. Stress beyond the limits specified in Table 19 may affect device reliability or cause permanent damage to the device. For functional operating conditions, refer to the remaining tables in this section. This device contains circuitry protecting against damage due to high static voltage or electrical fields; however, it is advised that normal precautions be taken to avoid application of any voltages higher than maximum-rated voltages to this high-impedance circuit.

#### Table 19. Absolute Maximum Ratings - Voltage (with respect to V<sub>SS</sub>)

| Rating                         | Symbol          | Value                                                          | Unit |

|--------------------------------|-----------------|----------------------------------------------------------------|------|

| Supply Voltage                 | V <sub>DD</sub> | -0.3 to +2.9                                                   | V    |

| Input Voltage<br>SCL, SDA, IRQ | V <sub>IN</sub> | V <sub>IN</sub> V <sub>SS</sub> - 0.3 to V <sub>DD</sub> + 0.3 |      |

| Operating Temperature Range    | TSG             | -40 to +85                                                     | °C   |

| Storage Temperature Range      | T <sub>SG</sub> | -40 to +125                                                    | °C   |

### A.3 ESD and Latch-up Protection Characteristics

Normal handling precautions should be used to avoid exposure to static discharge.

Qualification tests are performed to ensure that these devices can withstand exposure to reasonable levels of static without suffering any permanent damage. During the device qualification ESD stresses were performed for the Human Body Model (HBM), the Machine Model (MM) and the Charge Device Model (CDM).

A device is defined as a failure if after exposure to ESD pulses the device no longer meets the device specification. Complete DC parametric and functional testing is performed per the applicable device specification at room temperature followed by hot temperature, unless specified otherwise in the device specification.

#### Table 20. ESD and Latch-up Test Conditions

| Rating                                    | Symbol           | Value | Unit |

|-------------------------------------------|------------------|-------|------|

| Human Body Model (HBM)                    | V <sub>ESD</sub> | ±4000 | V    |

| Machine Model (MM)                        | V <sub>ESD</sub> | ±200  | V    |

| Charge Device Model (CDM)                 | V <sub>ESD</sub> | ±500  | V    |

| Latch-up current at T <sub>A</sub> = 85°C | ILATCH           | ±100  | mA   |

## A.4 DC Characteristics

This section includes information about power supply requirements and I/O pin characteristics.

#### Table 21. DC Characteristics (Temperature Range = -40°C to 85°C Ambient)

(Typical Operating Circuit,  $V_{DD}$  = 1.71 V to 2.75 V,  $T_A$  =  $T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted. Typical current values are at  $V_{DD}$  = 1.8 V,  $T_A$  = +25°C.)

| Parameter                                    | Symbol                            | Conditions                                             | Min                   | Тур   | Max                   | Units |   |

|----------------------------------------------|-----------------------------------|--------------------------------------------------------|-----------------------|-------|-----------------------|-------|---|

| Operating Supply Voltage                     | V <sub>DD</sub>                   |                                                        | 1.71                  | 1.8   | 2.75                  | V     |   |

| Average Supply Current                       | I <sub>DD</sub>                   | Run1 Mode @ 1 ms sample period                         |                       | 43    | 57.5                  | μA    | 1 |

| Average Supply Current                       | I <sub>DD</sub>                   | Run1 Mode @ 2 ms sample period                         |                       | 22    | 32                    | μA    | 2 |

| Average Supply Current                       | I <sub>DD</sub>                   | Run1 Mode @ 4 ms sample period                         |                       | 14    | 19.4                  | μA    |   |

| Average Supply Current                       | I <sub>DD</sub>                   | Run1 Mode @ 8 ms sample period                         |                       | 8     | 13.3                  | μA    |   |

| Average Supply Current                       | I <sub>DD</sub>                   | Run1 Mode @ 16 ms sample period                        |                       | 6     | 10.1                  | μA    |   |

| Average Supply Current                       | I <sub>DD</sub>                   | Run1 Mode @ 32 ms sample period                        |                       | 5     | 8.6                   | μA    | 2 |

| Average Supply Current                       | I <sub>DD</sub>                   | Run1 Mode @ 64 ms sample period                        |                       | 4     | 7.8                   | μA    |   |

| Average Supply Current                       | I <sub>DD</sub>                   | Run1 Mode @ 128 ms sample period                       |                       | 4     | 7.5                   | μA    |   |

| Measurement Supply Current                   | I <sub>DD</sub>                   | Peak of measurement duty cycle                         |                       | 1.25  | 1.5                   | mA    |   |

| Idle Supply Current                          | I <sub>DD</sub>                   | Stop Mode                                              |                       | 1.5   | 4                     | μA    |   |

| Electrode Charge Current<br>Accuracy<br>ELE_ |                                   | Relative to nominal values programmed in Register 0x41 | -6                    |       | +6                    | %     |   |

| Electrode Input Working Range<br>ELE_        |                                   | Electrode charge current accuracy within specification | 0.7                   |       | V <sub>DD</sub> - 0.7 | V     |   |

| Input Leakage Current ELE_                   | I <sub>IH</sub> , I <sub>IL</sub> |                                                        |                       | 0.025 | 1                     | μA    |   |

| Input Self-Capacitance ELE_                  |                                   |                                                        |                       |       | 15                    | pF    |   |

| Input High Voltage SDA, SCL                  | V <sub>IH</sub>                   |                                                        | 0.7 x V <sub>DD</sub> |       |                       | V     |   |

| Input Low Voltage SDA, SCL                   | V <sub>IL</sub>                   |                                                        |                       |       | 0.3 x V <sub>DD</sub> | V     |   |

| Input Leakage Current<br>SDA, SCL            | I <sub>IH</sub> , I <sub>IL</sub> |                                                        |                       | 0.025 | 1                     | μA    |   |

| Input Capacitance<br>SDA, SCL                |                                   |                                                        |                       |       | 7                     | pF    |   |

| Output Low Voltage<br>SDA, IRQ               | V <sub>OL</sub>                   | I <sub>OL</sub> = 6mA                                  |                       |       | 0.5V                  | V     |   |

| Power On Reset                               | V <sub>TLH</sub>                  | V <sub>DD</sub> rising                                 | 1.08                  | 1.35  | 1.62                  | V     |   |

|                                              | V <sub>THL</sub>                  | V <sub>DD</sub> falling                                | 0.88                  | 1.15  | 1.42                  | V     |   |

1. Parameters tested 100% at final test at room temperature; limits at -40°C and +85°C verified by characterization, not tested in production 2. Limits verified by characterization, not tested in production

## A.5 AC Characteristics

### AC CHARACTERISTICS

(Typical Operating Circuit,  $V_{DD}$  = 1.71V to 2.75V,  $T_A$  =  $T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted. Typical values are at  $V_{DD}$  = 1.8V,  $T_A$  = +25°C.)

| Parameter                  | Symbol         | Conditions | Min  | Тур | Max  | Units |

|----------------------------|----------------|------------|------|-----|------|-------|

| 8 MHz Internal Oscillator  | f <sub>H</sub> |            | 7.44 | 8   | 8.56 | MHz   |

| 32 kHz Internal Oscillator | fL             |            | 20.8 | 32  | 43.2 | kHz   |

1. Parameters tested 100% at final test at room temperature; limits at -40°C and +70°C verified by characterization, not tested in production 2. Limits verified by characterization, not tested in production.

# A.6 I<sup>2</sup>C AC Characteristics

This section includes information about I<sup>2</sup>C AC Characteristics.

#### Table 22. I<sup>2</sup>C AC Characteristics

(Typical Operating Circuit,  $V_{DD}$  = 1.71 V to 2.75 V,  $T_A$  =  $T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted. Typical current values are at  $V_{DD}$  = 1.8 V,  $T_A$  = +25°C.)

| Parameter                                          | Symbol               | Conditions | Min | Тур                      | Max | Units |

|----------------------------------------------------|----------------------|------------|-----|--------------------------|-----|-------|

| Serial Clock Frequency                             | f <sub>SCL</sub>     |            |     |                          | 400 | kHz   |

| Bus Free Time Between a STOP and a START Condition | t <sub>BUF</sub>     |            | 1.3 |                          |     | μs    |

| Hold Time, (Repeated) START Condition              | t <sub>HD, STA</sub> |            | 0.6 |                          |     | μs    |

| Repeated START Condition Setup Time                | t <sub>SU, STA</sub> |            | 0.6 |                          |     | μs    |

| STOP Condition Setup Time                          | t <sub>SU, STO</sub> |            | 0.6 |                          |     | μs    |

| Data Hold Time                                     | t <sub>HD, DAT</sub> |            |     |                          | 0.9 | μs    |

| Data Setup Time                                    | t <sub>SU, DAT</sub> |            | 100 |                          |     | ns    |

| SCL Clock Low Period                               | t <sub>LOW</sub>     |            | 1.3 |                          |     | μs    |

| SCL Clock High Period                              | t <sub>HIGH</sub>    |            | 0.7 |                          |     | μs    |

| Rise Time of Both SDA and SCL Signals, Receiving   | t <sub>R</sub>       |            |     | 20+0.1<br>C <sub>b</sub> | 300 | ns    |

| Fall Time of Both SDA and SCL Signals, Receiving   | t <sub>F</sub>       |            |     | 20+0.1<br>C <sub>b</sub> | 300 | ns    |

| Fall Time of SDA Transmitting                      | t <sub>F.TX</sub>    |            |     | 20+0.1<br>C <sub>b</sub> | 250 | ns    |

| Pulse Width of Spike Suppressed                    | t <sub>SP</sub>      |            |     | 25                       |     | ns    |

| Capacitive Load for Each Bus Line                  | Cb                   |            |     |                          | 400 | pF    |

# Appendix B Brief Register Descriptions

| REGISTER                         | Abrv  |         |              |  | Fie  | lds  |     |      |      | REGISTER<br>ADDRESS | Initial Value |

|----------------------------------|-------|---------|--------------|--|------|------|-----|------|------|---------------------|---------------|

| Touch Status Register            | TS    | OCF     |              |  |      |      | E2S | E1S  | E0S  | 0x00                | 0x00          |

| ELE0 Filtered Data Low Register  | E0FDL |         |              |  | E0F  | DLB  |     |      |      | 0x02                | 0x00          |

| ELE0 Filtered Data High Register | E0FDH |         |              |  |      |      |     | E0FI | OHB  | 0x03                | 0x00          |

| ELE1 Filtered Data Low Register  | E1FDL |         |              |  | E1F  | DLB  |     |      |      | 0x04                | 0x00          |

| ELE1 Filtered Data High Register | E1FDH |         |              |  |      |      |     | E1FI | OHB  | 0x05                | 0x00          |

| ELE2 Filtered Data Low Register  | E2FDL |         |              |  | E2F  | DLB  |     |      |      | 0x06                | 0x00          |

| ELE2 Filtered Data High Register | E2FDH |         |              |  |      |      |     | E2FI | OHB  | 0x07                | 0x00          |

| ELE0 Baseline Value Register     | E0BV  |         |              |  | E0   | BV   |     |      |      | 0x1A                | 0x00          |

| ELE1 Baseline Value Register     | E1BV  |         |              |  | E1   | BV   |     |      |      | 0x1B                | 0x00          |

| ELE2 Baseline Value Register     | E2BV  |         |              |  | E2   | BV   |     |      |      | 0x1C                | 0x00          |

| Max Half Delta Register          | MHD   |         | MHD          |  | 0x26 | 0x00 |     |      |      |                     |               |

| Noise Half Delta Register        | NHD   |         |              |  |      | N    | HD  |      |      | 0x27                | 0x00          |

| Noise Count Limit Register       | NCL   |         |              |  |      |      | N   | CL   |      | 0x28                | 0x00          |

| ELE0 Touch Threshold Register    | E0TTH |         |              |  | E01  | тн   |     |      |      | 0x29                | 0x00          |

| ELE0 Release Threshold Register  | E0RTH |         |              |  | EOF  | RTH  |     |      |      | 0x2A                | 0x00          |

| ELE1 Touch Threshold Register    | E1TTH |         |              |  | E17  | тн   |     |      |      | 0x2B                | 0x00          |

| ELE1 Release Threshold Register  | E1RTH |         | E1RTH        |  | 0x2C | 0x00 |     |      |      |                     |               |

| ELE2 Touch Threshold Register    | E2TTH |         | E2TTH        |  | 0x2D | 0x00 |     |      |      |                     |               |

| ELE2 Release Threshold Register  | E2RTH | E2RTH   |              |  | 0x2E | 0x00 |     |      |      |                     |               |

| AFE Configuration Register       | AFEC  | FFI CDC |              |  | 0x41 | 0x08 |     |      |      |                     |               |

| Filter Configuration Register    | FC    |         | CDT          |  | SFI  |      | ESI |      | 0x43 | 0x04                |               |

| Electrode Configuration Register | EC    |         | CalL ModeSel |  | Ele  | En   |     | 0x44 | 0x00 |                     |               |

# Appendix C Ordering Information

## C.1 Ordering Information

This section contains ordering information for MPR03X devices.

| ORDERING INFORMATION |                   |                   |            |                          |               |  |  |

|----------------------|-------------------|-------------------|------------|--------------------------|---------------|--|--|

| Device Name          | Temperature Range | Case Number       | Touch Pads | I <sup>2</sup> C Address | Shipping      |  |  |

| MPR031EPR2           | -40°C to +85°C    | 1944 (8-Pin μDFN) | 3-pads     | 0x4A                     | Tape and Reel |  |  |

| MPR032EPR2           | -40°C to +85°C    | 1944 (8-Pin μDFN) | 3-pads     | 0x4B                     | Tape and Reel |  |  |

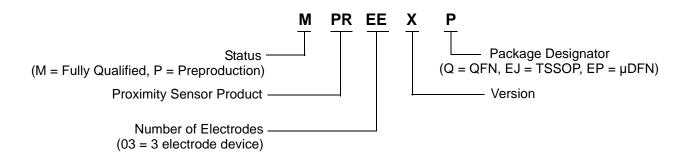

### C.2 Device Numbering Scheme

All Proximity Sensor Products have a similar numbering scheme. The below diagram explains what each part number in the family represents.

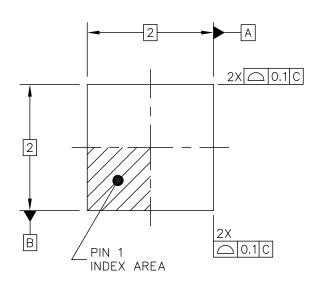

PACKAGE DIMENSIONS

| © FREESCALE SEMICONDUCTOR, INC.<br>ALL RIGHTS RESERVED. | LOUTLINE                        | PRINT VERSION NO                | T TO SCALE |  |

|---------------------------------------------------------|---------------------------------|---------------------------------|------------|--|

| TITLE: PLASTIC ULTRA-TH                                 |                                 | DOCUMENT NO: 98ASA10787D REV: A |            |  |

| FINE PITCH DUAL FLAT NOI<br>(UDFN) PACKAGE, 8 TEF       | CASE NUMBER: 1944-02 10 DEC 200 |                                 |            |  |

| 2 X 2 X 0.65, 0.5 P                                     | STANDARD: NO                    | N-JEDEC                         |            |  |

PAGE 1 OF 3

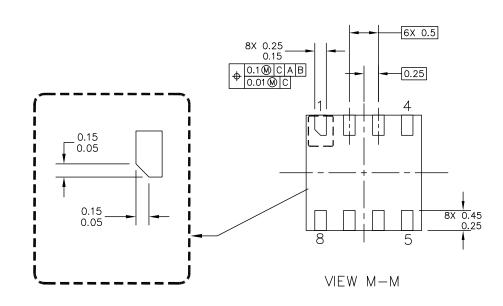

### PIN 1 BACKSIDE IDENTIFIER

DETAIL G VIEW ROTATED 90° CW

| © FREESCALE SEMICONDUCTOR, INC.<br>ALL RIGHTS RESERVED. | L OUTLINE | PRINT VERSION NO                | T TO SCALE |        |

|---------------------------------------------------------|-----------|---------------------------------|------------|--------|

| TITLE: PLASTIC ULTRA-TH                                 |           | DOCUMENT NO: 98ASA10787D REV: A |            | REV: A |

| FINE PITCH DUAL FLAT NOI<br>(UDFN) PACKAGE, 8 TEF       |           | CASE NUMBER: 1944-02 10 DEC 200 |            |        |

| 2 X 2 X 0.65, 0.5 P                                     |           | STANDARD: NO                    | N-JEDEC    |        |

PAGE 2 OF 3

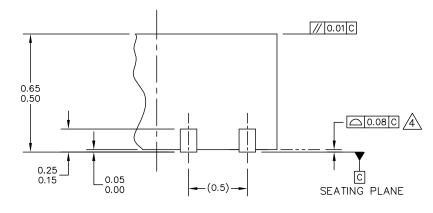

#### NOTES:

- 1. ALL DIMENSIONS ARE IN MILLIMETERS.

- 2. DIMENSIONING AND TOLERANCING PER ASME Y14.5M-1994.

- 3. THE COMPLETE JEDEC DESIGNATOR FOR THIS PACKAGE IS UF-PSON.

- 4. COPLANARITY APPLIES TO LEADS.

- 5. MIN. METAL GAP SHOULD BE 0.2 MM.

| © FREESCALE SEMICONDUCTOR, INC.<br>ALL RIGHTS RESERVED. | LOUTLINE                        | PRINT VERSION NO | DT TO SCALE    |        |

|---------------------------------------------------------|---------------------------------|------------------|----------------|--------|

| TITLE: PLASTIC ULTRA-TH                                 |                                 | DOCUMENT NO      | ): 98ASA10787D | REV: A |

| FINE PITCH DUAL FLAT NO<br>(UDFN) PACKAGE, 8 TEI        | CASE NUMBER: 1944-02 10 DEC 200 |                  |                |        |

| 2 X 2 X 0.65, 0.5 P                                     |                                 | STANDARD: NO     | N-JEDEC        |        |

PAGE 3 OF 3

### Table 23. Revision History

| Revision<br>number | Revision<br>date | Description of changes                                                                                                                                                                                                        |

|--------------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7                  | 07/2011          | <ul> <li>Changed Figure 25 AFE Configuration Register Reset From: 0 0 0 0 0 0 0 0 0, To: 0 0 0 1 0 0 0 0</li> <li>Changed Figure 26 Filter Configuration Register Reset From: 0 0 0 0 0 0 0 0, To: 0 0 1 0 0 1 0 0</li> </ul> |

### How to Reach Us:

Home Page: www.freescale.com

Web Support: http://www.freescale.com/support Information in this document is provided solely to enable system and software implementers to use Freescale products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits based on the information in this document.

Freescale reserves the right to make changes without further notice to any products herein. Freescale makes no warranty, representation, or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in Freescale data sheets and/or specifications can and do vary in different applications, and actual performance may vary over time. All operating parameters, including "typicals," must be validated for each customer application by customer's technical experts. Freescale does not convey any license under its patent rights nor the rights of others. Freescale sells products pursuant to standard terms and conditions of sale, which can be found at the following address: store.esellerate.net/store/Policy.asSelectorpx?Selector=RT&s=STR0326182960&pc.

Freescale, the Freescale logo, AltiVec, C-5, CodeTest, CodeWarrior, ColdFire, C-Ware, Energy Efficient Solutions logo, Kinetis, mobileGT, PowerQUICC, Processor Expert, QorIQ, Qorivva, StarCore, Symphony, and VortiQa are trademarks of Freescale Semiconductor, Inc., Reg. U.S. Pat. & Tm. Off. Airfast, BeeKit, BeeStack, ColdFire+, CoreNet, Flexis, MagniV, MXC, Platform in a Package, QorlQ Qonverge, QUICC Engine, Ready Play, SafeAssure, SMARTMOS, TurboLink, Vybrid, and Xtrinsic are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners.

© 2012 Freescale Semiconductor, Inc.

MPR03X Rev. 7 7/2012

# **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Optical Sensor Development Tools category:

Click to view products by NXP manufacturer:

Other Similar products are found below :

AR0330CS1C12SPKAH3-GEVB MT9V034C12STCH-GEVB MT9V115EBKSTCH-GEVB 416015300-3 ISL29102IROZ-EVALZ MT9M021IA3XTMH-GEVB AR1820HSSC12SHQAH3-GEVB AR1335CSSC11SMKAH3-GEVB MAXCAMOV10640# MT9M031I12STMH-GEVB TSL2581CS-DB TMD3700-DB NANOUSB2.2 ASX340AT3C00XPEDH3-GEVB AR0144ATSM20XUEAH3-GEVB AR0144CSSC00SUKAH3-GEVB AR0522SRSC09SURAH3-GEVB AR0522SRSM09SURAH3-GEVB AR0521SR2C09SURAH3-GEVB MARS1-MAX9295A-GEVK MARS1-MAX9296B-GEVB ISL29112IROZ-EVALZ AR0233AT2C17XUEAH3-GEVB AR0431CSSC14SMRAH3-GEVB MARS-DEMO3-MIPI-GEVB TCS3430-DB AR0234CSSC00SUKAH3-GEVB AR0130CSSM00SPCAH-GEVB AR0330CM1C00SHAAH3-GEVB EVALZ-ADPD2212 TMD2772EVM TMG3993EVM MIKROE-2103 TSL2672EVM 1384 MT9M114EBLSTCZDH-GEVB SEN0043 SEN0162 TMD2771EVM TMD3782EVM TSL4531EVM 1918 AS7225 DEMO KIT SEN0097 SEN0228 AR0134CSSC00SUEAH3-GEVB AP0100AT2L00XUGAH3-GEVB AR0144CSSM20SUKAH3-GEVB 725-28915 EVAL-ADPD1081Z-PPG