# 2.0 A switch-mode charger with intelligent power-path for 1-cell li-ion battery

The BC3770 is a fully programmable switching charger with dual-path output for single-cell Li-Ion and Li-Polymer battery. This dual-path output allows mobile applications with fully discharged battery or dead battery to boot up the system. High-efficiency and switch-mode operation of the BC3770 reduce heat dissipation and allow for higher current capability for a given package size. In addition, the BC3770 features single input with a 20 V withstanding input and charges the battery with the current up to 2.0 A. The charging parameters and operating modes are fully programmable over an I<sup>2</sup>C Interface that operates up to 400 kHz.

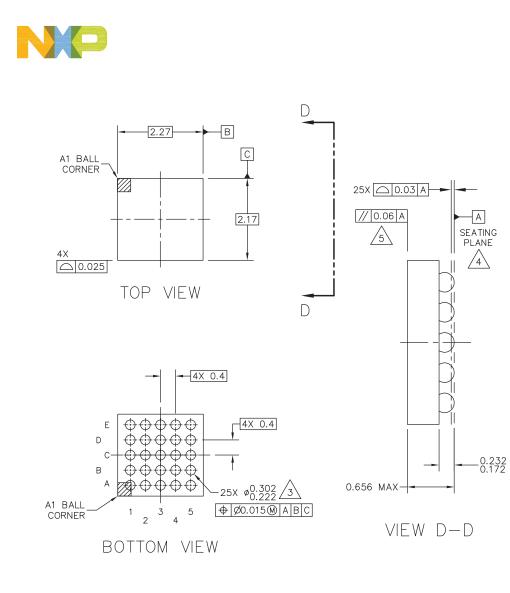

The BC3770 is a highly integrated synchronous switch-mode charger, featuring integrated OVP and Power FETs. The charger and boost regulator circuits switch at 1.5 MHz to minimize the size of external passive components. The BC3770 is able to operate as a boost regulator for USB-OTG function via either  $I^2C$  command or an external pin from the host/processor. The BC3770 is available in a 25-bump, 2.27 mm x 2.17 mm, WLCSP package.

#### Features

- · Dual-path output to power-up system in dead battery

- · Single input for USB/TA

- · High-efficiency synchronous switching regulator

- · 20 V maximum withstanding input voltage

- · Minimize the charging time with remote sense

- · Up to 2.0 A load current for system or battery

- Programmable charge parameters via I<sup>2</sup>C compatible interface

- 400 kHz full-speed I<sup>2</sup>C interface

- 1.5 MHz switching frequency

- · Charge reduction mode for maximizing charging efficiency

BC3770

#### Applications

- Internet of things (IoT)

- · Handheld consumer devices

- · Wearable application

- mPOS terminals

- Medical portable equipment

- · Consumer tablets

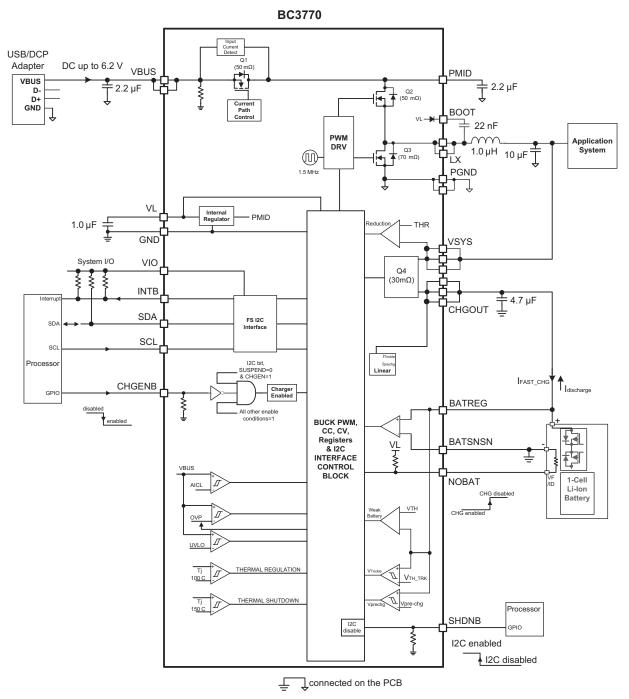

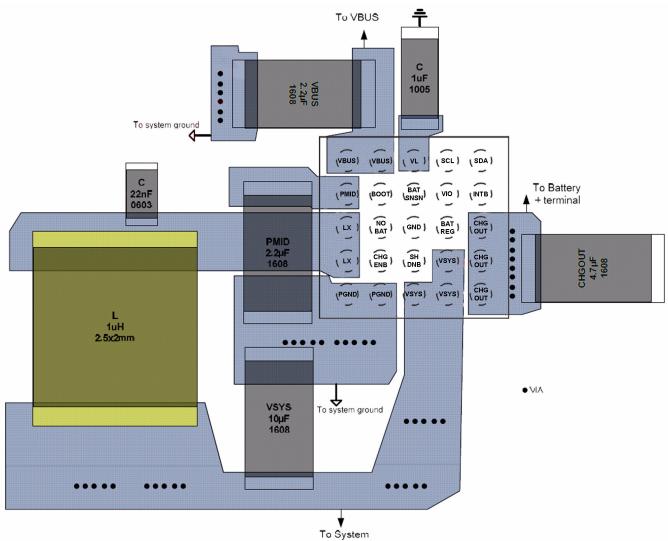

connected on the PCB

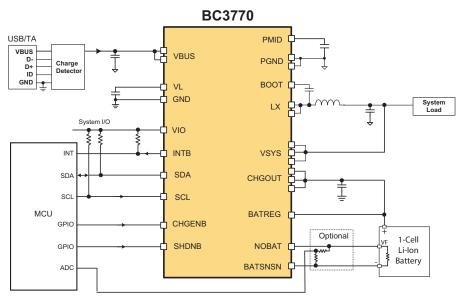

Figure 1. BC3770 simplified application diagram

\* This document contains certain information on a new product. Specifications and information herein are subject to change without notice.

# 1 Orderable parts

#### Table 1. Orderable part variations

| Part number    | Temperature (T <sub>A</sub> ) | Package                                |

|----------------|-------------------------------|----------------------------------------|

| MC32BC3770CSR2 | -40 °C to 85 °C               | 25 WLCSP, 2.27 mm x 2.17 mm, 0.4 pitch |

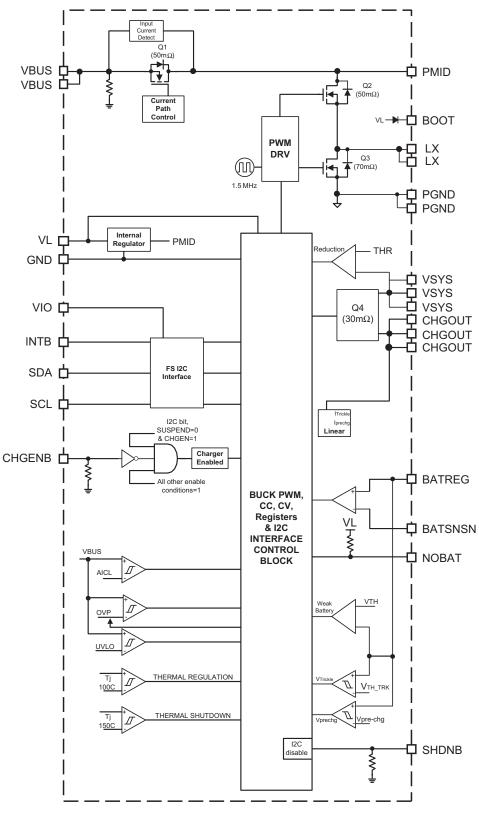

# 2 Internal block diagram

Figure 2. BC3770 simplified internal block diagram

# 3 Pin connections

TRANSPARENT TOP VIEW

| [ | A (VBUS) | 2<br>(VBUS) | 3<br>( <sup>VL</sup> ) | 4<br>(SCL)          | 5<br>(SDA) |

|---|----------|-------------|------------------------|---------------------|------------|

|   | B (PMID) | (BOOT)      | BAT<br>SNSN            | (VIO)               |            |

| 1 | c ( )    | NO<br>BAT   |                        | BAT<br>REG          | CHG<br>OUT |

|   |          | CHG<br>ENB  | SH<br>DNB              | ( <sup>VSYS</sup> ) | CHG<br>OUT |

|   |          | (PGND)      | (VSYS)                 | (VSYS)              | OUT )      |

Figure 3. BC3770 pin connections (transparent top view)

Functional descriptions of many of these pins can be found in the Functional Pin Description section beginning on page 13.

| Table 2. BC3770 pin definitions | Table 2. | BC3770 g | oin definitions |

|---------------------------------|----------|----------|-----------------|

|---------------------------------|----------|----------|-----------------|

| Pin    | Pin name | Pin<br>function  | Formal name                                                                   | Definition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|--------|----------|------------------|-------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A1, A2 | VBUS     | Input            | USB/DCP Adapter Input                                                         | Connect the pins to the output of USB or DCP (dedicated Charging Port) adapter. Bypass with a 2.2 $\mu$ F/10 V ceramic capacitor to the ground, in case the peak voltage on the pins is always below 10 V due to a clamp device. Otherwise, a 2.2 $\mu$ F/25 V or higher rating capacitor is recommended. The two VBUS pins must be connected together externally. These pins are used as an output in OTG mode. An embedded 100 k $\Omega$ discharge resistance is enabled in Charge mode. It is disconnected in the Boost mode. |

| A3     | VL       | Output           | Internal Regulator Output                                                     | The analog output for internal reference, bandgap and so on. DO NOT LOAD. Bypass with a 1.0 $\mu\text{F}/10$ V to ground.                                                                                                                                                                                                                                                                                                                                                                                                         |

| A4     | SCL      | Input            | Clock Input for FS I <sup>2</sup> C<br>Serial Interface with the<br>Processor | Use a pull-up resistor, 1.5 k $\Omega$ to 2.2 k $\Omega,$ to the VIO.                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| A5     | SDA      | Input/<br>Output | Data I/O for FS I <sup>2</sup> C Serial<br>Interface with the Processor       | Use a pull-up resistor, 1.5 k $\Omega$ to 2.2 k $\Omega,$ to the VIO.                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| B1     | PMID     | Output           | VBUS Bypass Output                                                            | High-side MOSFET connection node and VBUS bypass output. Bypass with a 2.2 $\mu F$ ceramic capacitor to PGND pins as close as possible. Do NOT LOAD any external applications.                                                                                                                                                                                                                                                                                                                                                    |

| B2     | BOOT     |                  | High-side MOSFET Driver<br>Supply                                             | Bypass BOOT to LX with a 22 nF/10 V ceramic capacitor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| В3     | BATSNSN  |                  | Battery - Terminal Sensing                                                    | Connect to negative terminal of battery cell as close as possible. If a sense resistor is used for a fuel gauge, connect the pin to the ground terminal of the sense resistor.                                                                                                                                                                                                                                                                                                                                                    |

| B4     | VIO      |                  | Supply for Internal Buffer                                                    | Connect to the system I/O supply voltage rail.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

#### Table 2. BC3770 pin definitions (continued)

| Pin        | Pin name | Pin<br>function | Formal name                                             | Definition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|------------|----------|-----------------|---------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| B5         | INTB     | Output          | Logic Output for Interrupt                              | An open-drain output with an external pull-up resistor, 200 k $\Omega$ , to the system I/O supply. Active-low when status change on interrupt registers occurs.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| C1, D1     | LX       |                 | Switching Node                                          | Connect a 1.0 $\mu\text{H}$ inductor. The two LX pins must be connected together externally.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

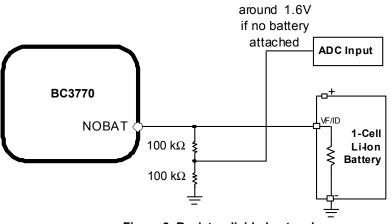

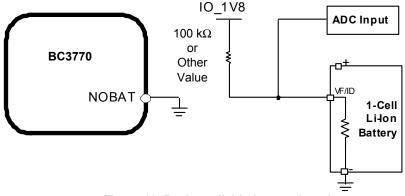

| C2         | NOBAT    | Input           | Logic Input for Battery<br>Presence Detection           | Connect the pin to VF or ID pin on the battery cell. It has an internal pull-up resistance, 300 k $\Omega$ typ, to the VL. If a logic-high threshold is detected on the pin, the charging is suspended immediately. If this pin is not used, connect it to ground.                                                                                                                                                                                                                                                                                                                                                                                   |

| C3         | GND      | Ground          | Device Ground                                           | Must be connected to the system ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| C4         | BATREG   |                 | Battery + Terminal Sensing                              | Connect to positive terminal of battery cell as close as possible.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| C5, D5, E5 | CHGOUT   | Output          | Battery Charger Output                                  | These pins must be connected together externally. Bypass with a 4.7 $\mu\text{F}/10$ V or higher to ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

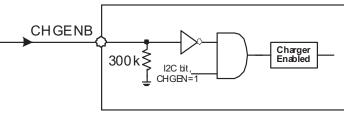

| D2         | CHGENB   | Input           | Charger Enable Logic Input                              | Logic-low to enable charger. Logic-high to disable the charger, not to disable buck converter. It has an internal 300 k $\Omega$ resistance to ground. If this pin is not used, leave it open or connect it to ground. The serial interface, I <sup>2</sup> C, is still available in CHGENB = High.                                                                                                                                                                                                                                                                                                                                                  |

| D3         | SHDNB    | Input           | Logic Input for Disabling I <sup>2</sup> C<br>Interface | If there is no valid input source, logic-low is to put the $l^2C$ interface into Disabled<br>mode to reduce the idle current as low as possible. In the Shutdown mode, $l^2C$<br>interface is not available but the Q4 FET is kept ON. A valid power source on<br>VBUS is able to overwrite to wake-up the device for Charge mode even in<br>SHDNB = Low. This pin is not effective as long as a valid input power source is<br>present.<br>This pin has an internal pull-down resistance, 300 k $\Omega$ typ. If this pin is not used,<br>tie it to the system I/O supply rail or an appropriate rail to reduce idle current as<br>low as possible. |

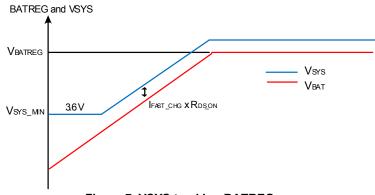

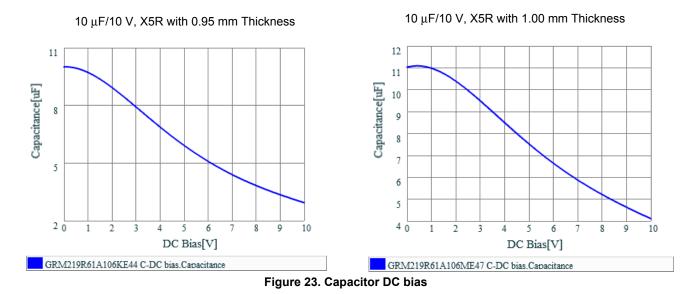

| D4, E3, E4 | VSYS     | Output          | System Supply Output                                    | VSYS is the power supply for the system load. When a valid power source at VBUS is attached, VSYS is regulated at 3.6 V until the BATREG hits the threshold of V <sub>SYS</sub> MIN x R <sub>DS(on)</sub> Q4. When the +Terminal on the battery cell is regulated at VBATREG, the VSYS output is regulated to the I <sub>FAST_CHG</sub> x R <sub>DS(on)</sub> Q4 above BATREG. Bypass with a 10 $\mu$ F/10 V ceramic capacitor to ground.                                                                                                                                                                                                            |

| E1, E2     | PGND     | Ground          | Power Ground for the Buck<br>Converter                  | The two PGND pins must be connected together externally.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

# 4 Electrical characteristics

## 4.1 Maximum ratings

Stress(es) beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the following operational sections of the specifications is not implied. Exposure to absolute maximum rating condition(s) for extended periods may affect device reliability.

#### Table 3. Maximum ratings

All voltages are with respect to ground unless otherwise noted.

| Symbol                                 | Rating                                                                        | Min. | Max.              | Unit | Notes      |

|----------------------------------------|-------------------------------------------------------------------------------|------|-------------------|------|------------|

| Electrical ratings                     |                                                                               | L    | 1                 |      | <u> </u>   |

|                                        | VBUS, PMID to GND                                                             | -0.3 | 20                | V    | (1)        |

|                                        | LX to GN                                                                      | -0.3 | 20                | V    | (1)        |

|                                        | BOOT to LX                                                                    | -0.3 | 5.5               | V    | (1)        |

|                                        | BOOT to GND                                                                   | -0.3 | 25.5              | V    |            |

|                                        | PGND, BATSNSN to GND                                                          | -0.3 | 0.3               | V    | (1)        |

|                                        | VL to GND                                                                     | -0.3 | 5.5               | V    |            |

|                                        | VSYS, CHGOUT, BATREG to GND                                                   | -0.3 | Continuous<br>6.0 | V    |            |

|                                        | PGND to GND                                                                   | -0.3 | 0.3               | V    | (1)        |

|                                        | All Other Pins to GND                                                         | -0.3 | 5.5               |      | (1)        |

| V <sub>ESD1</sub><br>V <sub>ESD3</sub> | ESD Voltage <ul> <li>Human Body Model (HBM)</li> <li>Machine Model</li> </ul> |      | 2000<br>200       | V    | (2)<br>(3) |

**Thermal ratings**

|                     | Continuous Power Dissipation<br>• $T_A \le 25 \text{ °C}$<br>• $T_A \le 70 \text{ °C}$<br>• $T_A \le 85 \text{ °C}$ |     | 2.08<br>1.14<br>0.832 | W    |          |

|---------------------|---------------------------------------------------------------------------------------------------------------------|-----|-----------------------|------|----------|

| T <sub>A</sub>      | Operating Temperature <ul> <li>Ambient</li> </ul>                                                                   | -40 | 85                    | °C   |          |

| TJ                  | Maximum Temperature <ul> <li>Junction</li> </ul>                                                                    | _   | 150                   | °C   |          |

| T <sub>STG</sub>    | Storage Ambient Temperature                                                                                         | -65 | 150                   | °C   |          |

| T <sub>SOLDER</sub> | Lead Soldering Temperature (within 10 s)                                                                            | _   | 300                   | °C   |          |

| Τ <sub>θJA</sub>    | Thermal Resistance Junction to Ambient                                                                              | _   | 48                    | °C/W | (4), (5) |

Notes

1. GND: all of the PGND and GND should be within the limit.

2. Human Body Model (HBM) per JESD22-A114 for all pins

3. Highly depends on the PCB heat dissipation. Tested with the Thermal Characteristics test condition below.

4. T<sub>A</sub> = 70 °C

5. Measured in still air, free convection condition (conforms to EIA/JESD51-2) on high effective thermal conductivity JESD51-7 test board.

## 4.2 Electrical characteristics

#### Table 4. BC3770 electrical characteristics

Characteristics noted under conditions:  $V_{VBUS}$  = 5.0 V,  $V_{BATREG}$  = 3.7 V,  $V_{VIO}$  = 1.8 V,  $C_{VBUS}$  =  $C_{PMID}$  = 2.2  $\mu$ F,  $C_{VSYS}$  = 10  $\mu$ F,  $C_{CHGOUT}$  = 4.7  $\mu$ F,  $C_{VL}$  = 1.0  $\mu$ F, L = 1.0  $\mu$ H,  $T_A$  = -40 °C to 85 °C \*). Typical values are at  $T_A$  = 25°C, unless otherwise noted. <sup>(6)</sup>

| Symbol                                     | Characteristic                                                                                                                                                                                                                                                                                                                                 | Min.                 | Тур.                  | Max.                     | Unit | Notes |

|--------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|-----------------------|--------------------------|------|-------|

| BUS supply                                 | 1                                                                                                                                                                                                                                                                                                                                              |                      |                       | 1                        | 1    |       |

| V <sub>BUS_OP</sub><br>V <sub>VIO_OP</sub> | Operating Range<br>• On VBUS<br>• On VIO                                                                                                                                                                                                                                                                                                       | 4.0<br>1.6           |                       | 6.2<br>3.3               | v    |       |

| V <sub>BUS_UVLO</sub>                      | UVLO Threshold <ul> <li>VBUS rising, 200 mV Hysteresis, VBUSOK bit set to 1</li> </ul>                                                                                                                                                                                                                                                         | 3.6                  | 3.8                   | 4.0                      | V    |       |

| V <sub>BUS_OVP</sub>                       | OVP Threshold <ul> <li>VBUS rising to turn off converter, 200 mV Hysteresis</li> </ul>                                                                                                                                                                                                                                                         | 6.3                  | 6.5                   | 6.7                      | V    | (7)   |

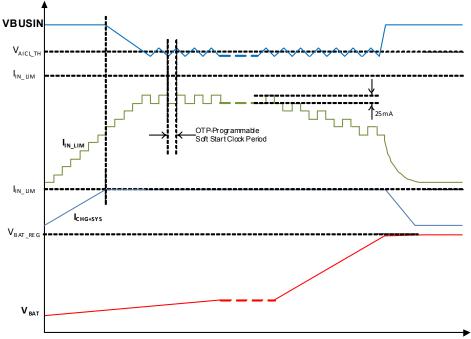

| V <sub>AICL_TH</sub>                       | Adaptive-Input Current Limit (AICL) Threshold Range <ul> <li>VBUS falling, Programmable in 100 mV steps, 4.5 V Default</li> </ul>                                                                                                                                                                                                              | 4.3                  | _                     | 4.9                      | V    |       |

| I <sub>VBUS_OP</sub>                       | Adaptive-Input Current Limit (AICL) Threshold Range <ul> <li>In charger enabled, I<sub>FAST_CHG</sub> = I<sub>SYS</sub> = 0 mA, SHDNB = H,</li> <li>SUSPEN = 0</li> <li>LX No switching, V<sub>VSYS</sub> = V<sub>BATREG</sub> = 4.4 V override</li> <li>LX switching w/VSYS = 3.7 V in PWM</li> <li>USB suspended mode in SUSPEN=1</li> </ul> |                      | 2.0<br>15<br>—        | <br><br>1.0              | mA   |       |

| I <sub>IN_LIM</sub>                        | Input Current Limit Programmable Range <ul> <li>500 mA default, test 100 mA, 500 mA, 900 mA and 1.9 A only in production</li> </ul>                                                                                                                                                                                                            | 100                  | _                     | 2050                     | mA   |       |

|                                            | <ul> <li>IIN_LIM Accuracy</li> <li>With respect to I<sub>IN_LIM</sub> = 100 mA</li> <li>With respect to I<sub>IN_LIM</sub> = 500 mA</li> <li>With respect to I<sub>IN_LIM</sub> = 900 mA</li> <li>With respect to I<sub>IN_LIM</sub> = 2000 mA</li> </ul>                                                                                      | 70<br>70<br>84<br>93 | 85<br>85<br>92<br>100 | 100<br>100<br>100<br>107 | %    | (7)   |

|                                            | VBUS Pull-down Resistance <ul> <li>Off in BOOST Mode</li> </ul>                                                                                                                                                                                                                                                                                | _                    | 100                   | _                        | kΩ   |       |

| L LDO regulator                            |                                                                                                                                                                                                                                                                                                                                                |                      |                       | 1                        |      |       |

| V <sub>OUT_VLLDO</sub>                     | Output Voltage<br>• V <sub>PMID</sub> = 5.0 V, I <sub>LOAD</sub> = 30 mA                                                                                                                                                                                                                                                                       | 4.65                 | 4.8                   | _                        | V    |       |

| ILOAD_LIM                                  | Current Limit<br>• V <sub>VLLDO</sub> = 3.8 V                                                                                                                                                                                                                                                                                                  | 50                   | _                     | _                        | mA   | (7)   |

| witching regulat                           | tor                                                                                                                                                                                                                                                                                                                                            |                      |                       | 1                        | •    |       |

| f <sub>SW</sub>                            | Switching Frequency <ul> <li>In PWM mode</li> </ul>                                                                                                                                                                                                                                                                                            | 1.35                 | 1.5                   | 1.65                     | MHz  | (7)   |

| D <sub>MAX</sub>                           | Maximum Duty Cycle                                                                                                                                                                                                                                                                                                                             | _                    | _                     | 99                       | %    |       |

| D <sub>MIN</sub>                           | Minimum Duty Cycle                                                                                                                                                                                                                                                                                                                             | 0.0                  | —                     | _                        | %    | 1     |

| I <sub>LIM_CHG</sub>                       | Cycle-by-cycle Current Limit for Charger Mode <ul> <li>For high-side MOSFET in charger mode</li> </ul>                                                                                                                                                                                                                                         | _                    | 3.5                   | 4.7                      | A    | (7)   |

|                                            | Minimum Output Capacitance <ul> <li>For stability</li> </ul>                                                                                                                                                                                                                                                                                   | -30%                 | 10                    | _                        | μF   | (7)   |

Notes

6. Specifications over the T<sub>A</sub> range are assured by design, characterized, and correlated with process control.

7. Guaranteed by design, characterization, and correlation with process controls. Not fully tested in production.

Characteristics noted under conditions:  $V_{VBUS}$  = 5.0 V,  $V_{BATREG}$  = 3.7 V,  $V_{VIO}$  = 1.8 V,  $C_{VBUS}$  =  $C_{PMID}$  = 2.2  $\mu$ F,  $C_{VSYS}$  = 10  $\mu$ F,  $C_{CHGOUT}$  = 4.7  $\mu$ F,  $C_{VL}$  = 1.0  $\mu$ F, L = 1.0  $\mu$ H,  $T_A$  = -40 °C to 85 °C \*). Typical values are at  $T_A$  = 25°C, unless otherwise noted. <sup>(6)</sup>

| Symbol                    | Characteristic                                                                                                                                                                                                                                                                       | Min.                         | Тур.                                                                | Max.                           | Unit | Notes    |

|---------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|---------------------------------------------------------------------|--------------------------------|------|----------|

| ower switches             |                                                                                                                                                                                                                                                                                      | I                            | I                                                                   | I I                            |      | <u> </u> |

| R <sub>DS(on)_Q1</sub>    | Reverse Blocking MOSFET On-resistance • Q1 FET                                                                                                                                                                                                                                       | _                            | 50                                                                  | —                              | mΩ   |          |

| R <sub>DS(on)_Q2</sub>    | Internal High-side MOSFET On-resistance • Q2 FET                                                                                                                                                                                                                                     | _                            | 50                                                                  | —                              | mΩ   |          |

| R <sub>DS(on)_Q3</sub>    | Internal Low-side MOSFET On-resistance • Q3 FET                                                                                                                                                                                                                                      | _                            | 70                                                                  | —                              | mΩ   |          |

| R <sub>DS(on)_Q4</sub>    | CHGOUT to VSYS MOSFET On-resistance<br>• Q4 FET                                                                                                                                                                                                                                      | _                            | 30                                                                  | _                              | mΩ   |          |

| /SYS output               |                                                                                                                                                                                                                                                                                      |                              | 1                                                                   | 11                             |      | 1        |

| V <sub>VSYS_MIN</sub>     | $\label{eq:VSYS} \begin{array}{l} \text{VSYS Min. Regulation Voltage in } I_{\text{IN}\_\text{LIM}} \geq I_{\text{VSYS}} \\ \bullet  \text{In both Trickle and pre-charge mode } (V_{\text{BATREG}} < V_{\text{VSYS}}_{\text{MIN}}), \\ I_{\text{SYS}} = 500 \text{ mA} \end{array}$ | 3.5                          | 3.6                                                                 | 3.71                           | V    |          |

| V <sub>VSYS_MIN_OLP</sub> | VSYS Min Regulation Voltage in I <sub>IN_LIM</sub> < I <sub>VSYS</sub> (VSYS overloaded)<br>• VSYS falling in VSYS overloaded in VBUSOK = 1                                                                                                                                          | 3.3                          | 3.4                                                                 | _                              | V    |          |

| V <sub>VSYS_MAX</sub>     | SYS Max Regulation Voltage<br>• In VBUSOK = 1, I <sub>SYS_LOAD</sub> = 0 mA, I <sub>CHG</sub> = 1.5 A                                                                                                                                                                                | _                            | V <sub>BATREG</sub> +<br>I <sub>CHG</sub> *<br>R <sub>DSON_Q4</sub> | V <sub>BATREG</sub> +<br>0.1 V | V    |          |

|                           | VSYSOK Threshold <ul> <li>VSYS rising in VBUSOK = 1, VSYSOK bit set to 1</li> </ul>                                                                                                                                                                                                  | 3.4                          | 3.5                                                                 | 3.61                           | V    | (8)      |

|                           | VSYSNG Threshold <ul> <li>VSYS falling, VSYSNG bit set to 1</li> </ul>                                                                                                                                                                                                               | 3.2                          | 3.3                                                                 | _                              | V    | (8)      |

| V <sub>SYS_REVERSE</sub>  | Ideal Diode Regulation Voltage <ul> <li>VSYS falling below BATREG, I<sub>SYS_LOAD</sub> = 3.0 A</li> </ul>                                                                                                                                                                           | _                            | V <sub>BATREG</sub> -<br>50 mV                                      | V <sub>BATREG</sub> -<br>75 mV | V    | (8)      |

| $\Delta_{ m VSYSLOAD}$    | Load Regulation in Transition<br>• I <sub>SYS</sub> = 1.0 mA to 1.0 A in t <sub>R</sub> = 20 μs                                                                                                                                                                                      | V <sub>BATREG</sub> -<br>0.2 | V <sub>BATREG</sub> -<br>0.1                                        | _                              | V    | (8)      |

| V <sub>SYS_UVLO</sub>     | VSYS Undervoltage Lockout Threshold <ul> <li>VSYS falling, 200 mV Hysteresis</li> </ul>                                                                                                                                                                                              | 2.3                          | 2.4                                                                 | 2.5                            | V    |          |

| t <sub>DIODE-ON</sub>     | Ideal Diode Turn-on Time                                                                                                                                                                                                                                                             | -                            | 10                                                                  |                                | μs   |          |

| t <sub>DIODE_OFF</sub>    | Ideal Diode Turn-off Time                                                                                                                                                                                                                                                            | -                            | 10                                                                  | —                              | μs   |          |

| Battery charger           | •                                                                                                                                                                                                                                                                                    | •                            | •                                                                   |                                |      | ·        |

| V <sub>BATREG_RNG</sub> | <ul><li>BATREG Programmable Voltage Range</li><li>Programmable in 25 mV steps</li></ul>                                                          | 4.1          | _    | 4.475      | V  |  |

|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|--------------|------|------------|----|--|

| V <sub>BAT_REG</sub>    | Voltage Accuracy<br>• $I_{FAST\_CHG} = 0$ mA, set to 4.2 V and 4.35 V at V <sub>BATREG</sub><br>$T_A = 25 \text{ °C}$<br>$T_A = -40$ to $85 \ge$ | -0.5<br>-1.0 | —    | 0.5<br>1.0 | %  |  |

| V <sub>RCH</sub>        | Recharge Threshold <ul> <li>V<sub>BATREG</sub> - V<sub>BAT_REG</sub></li> </ul>                                                                  |              | -100 | _          | mV |  |

Notes

8. Guaranteed by design, characterization, and correlation with process controls. Not fully tested in production.

9. Designed and simulated according to I<sup>2</sup>C specifications except general call support.

10. The regulation in boost is only guaranteed in the operation range.

Characteristics noted under conditions:  $V_{VBUS}$  = 5.0 V,  $V_{BATREG}$  = 3.7 V,  $V_{VIO}$  = 1.8 V,  $C_{VBUS}$  =  $C_{PMID}$  = 2.2  $\mu$ F,  $C_{VSYS}$  = 10  $\mu$ F,  $C_{CHGOUT}$  = 4.7  $\mu$ F,  $C_{VL}$  = 1.0  $\mu$ F, L = 1.0  $\mu$ H, T<sub>A</sub> = -40 °C to 85 °C \*). Typical values are at T<sub>A</sub> = 25°C, unless otherwise noted. <sup>(6)</sup>

| Symbol                 | Characteristic                                                                                                                                                                                         | Min.                       | Тур.                          | Max.                   | Unit  | Notes |

|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|-------------------------------|------------------------|-------|-------|

| ttery charger (        | continued)                                                                                                                                                                                             |                            | -                             |                        |       |       |

|                        | Stand-By Current                                                                                                                                                                                       |                            |                               |                        |       |       |

| I <sub>BAT_STD</sub>   | • No VBUS, $V_{BATREG}$ = 4.2 V, $I_{SYS}$ = 0 mA, SHDNB = H(I <sup>2</sup> C active), Q4 = On with OCP enabled, ENCOMPARATOR bit reset to 0, others with default                                      | —                          | 60                            | —                      | μA    |       |

| IBAT_SHDN              | Shutdown Current<br>• No VBUS, V <sub>BATREG</sub> = 4.2 V, charger disabled, Q4 = On with<br>OCP disabled, SHDNB = L (I <sup>2</sup> C inactive), ENCOMPARATOR bit<br>reset to 0, others with default | _                          | _                             | 20                     | μΑ    |       |

|                        | Charger Enable Threshold                                                                                                                                                                               |                            |                               |                        |       |       |

| V <sub>CHGEN_ON</sub>  | <ul> <li>V<sub>BUS</sub> - V<sub>BATREG</sub>, rising, valid VBUS detected to enable buck &amp; charging</li> </ul>                                                                                    | 100                        | 150                           | 200                    | mV    | (11)  |

| V <sub>CHGEN_OFF</sub> | <ul> <li>V<sub>BUS</sub> - V<sub>BATREG</sub>, falling, invalid VBUS detection to disable buck<br/>&amp; charging</li> </ul>                                                                           | 0.0                        | 50                            | —                      | mv    |       |

| V <sub>TRICKLE</sub>   | Trickle to Pre-charge Mode Change Threshold <ul> <li>V<sub>BATREG</sub> rising, 100 mV Hysteresis</li> </ul>                                                                                           | 2.4                        | 2.5                           | 2.7                    | v     | (11)  |

| I <sub>TRICKLE</sub>   | Trickle Charge Current<br>• Fixed, V <sub>BATREG</sub> = 2.3 V, V <sub>SYS</sub> = 3.6 V                                                                                                               | _                          | 90                            | _                      | mA    |       |

| I <sub>PRECHG</sub>    | <ul><li>Pre-charge Current Programmable Range</li><li>450 mA default and test in production</li></ul>                                                                                                  | 150                        | _                             | 450                    | mA    |       |

| I <sub>FAST_CHG</sub>  | <ul><li>Fast-charge Current Programmable Range</li><li>500 mA default, test 500 mA, 1.0 A only in production</li></ul>                                                                                 | 100                        | _                             | 2000                   | mA    |       |

| ITOPOFF                | Top-off Current Programmable Range <ul> <li>I<sub>FAST_CHG</sub> falling, 100 mA default, in 50 mA steps, test 100 mA and 300 mA only in production</li> </ul>                                         | 100                        | _                             | 65                     | mA    |       |

| V <sub>BAT_OVP</sub>   | Overvoltage Protection Threshold <ul> <li>BATREG rising</li> </ul>                                                                                                                                     | _                          | V <sub>BAT_REG</sub><br>+ 0.1 | _                      | V     |       |

|                        | Soft-start Slope Time <ul> <li>In fast charge mode</li> </ul>                                                                                                                                          | _                          | 1.17                          | _                      | mA/μs |       |

|                        | Minimum Output Capacitance <ul> <li>On CHGOUT, For stability</li> </ul>                                                                                                                                | -30%                       | 4.7                           | _                      | μF    | (11   |

|                        | Charge Current Accuracy <ul> <li>Pre-charge current at 150 mA</li> <li>Top-off current at 100 mA</li> <li>I<sub>FAST_CHG</sub> = 1000mA</li> <li>I<sub>FAST_CHG</sub> = 2000mA</li> </ul>              | -20<br>-20<br>-7.0<br>-7.0 | <br>                          | 20<br>20<br>7.0<br>7.0 | %     | (11)  |

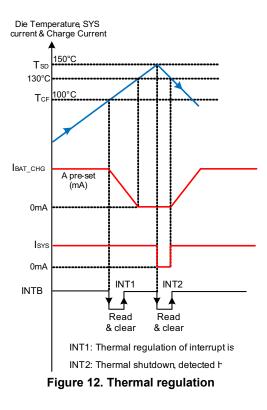

Thermal protection

| T <sub>SD</sub> | Thermal Shutdown Temperature <ul> <li>Temperature rising to shutdown with 20 °C hysteresis</li> </ul>                         | _ | 150  | _ | °C   | (11) |

|-----------------|-------------------------------------------------------------------------------------------------------------------------------|---|------|---|------|------|

| T <sub>CF</sub> | <ul> <li>Thermal Regulation Threshold</li> <li>Rising, charge current starts to reduce and the Interrupt triggered</li> </ul> | _ | 100  | _ | °C   |      |

|                 | Thermal Regulation Gain<br>• To have no charge current with respect to $I_{FAST\_CHG}$ ,<br>$T_{J} \ge 100 \ ^{\circ}C$       | _ | 3.33 | _ | %/°C |      |

Notes

11. Guaranteed by design, characterization, and correlation with process controls. Not fully tested in production.

Characteristics noted under conditions:  $V_{VBUS} = 5.0 \text{ V}$ ,  $V_{BATREG} = 3.7 \text{ V}$ ,  $V_{VIO} = 1.8 \text{ V}$ ,  $C_{VBUS} = C_{PMID} = 2.2 \mu\text{F}$ ,  $C_{VSYS} = 10 \mu\text{F}$ ,  $C_{CHGOUT} = 4.7 \mu\text{F}$ ,  $C_{VL} = 1.0 \mu\text{F}$ ,  $L = 1.0 \mu\text{H}$ ,  $T_A = -40 \text{ °C}$  to 85 °C \*). Typical values are at  $T_A = 25 \text{ °C}$ , unless otherwise noted. <sup>(6)</sup>

| Symbol                         | Characteristic                                                                                                                                                                             | Min. | Тур.                          | Max.     | Unit | Notes |

|--------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------------------------------|----------|------|-------|

| afety timer                    |                                                                                                                                                                                            |      | 1                             |          |      |       |

| t <sub>PRECHG_TMR</sub>        | Pre-charge Timer <ul> <li>Time for BAT from V<sub>TRICKLE</sub> to V<sub>SYS_MIN</sub></li> </ul>                                                                                          | _    | 45                            | _        | min. |       |

|                                | Timer Accuracy                                                                                                                                                                             | -10  | —                             | 10       | %    | (12)  |

| topoff_tmr                     | Top-off Timer <ul> <li>Programmable</li> </ul>                                                                                                                                             | 10   | _                             | 45       | min. |       |

| t <sub>fast_tmr</sub>          | Fast Charge Timer<br>• This timer is automatically disabled when the input current limit<br>is set to 100 mA<br>FASTTIME = 00<br>FASTTIME = 01<br>FASTTIME = 10<br>FASTTIME = 11 (default) |      | 3.5<br>4.5<br>5.5<br>disabled | <br><br> | hrs. |       |

| Deglitch timer <sup>(12)</sup> |                                                                                                                                                                                            |      |                               |          |      |       |

| t <sub>VBUS_OVP</sub>          | VBUS Supply OVP Release Deglitch Time <ul> <li>Duration VBUS stays below falling OVP before VSYS/Charger/<br/>OTG is enabled</li> </ul>                                                    | _    | 0.426                         | _        | ms   |       |

| t <sub>NOBAT</sub>             | NOBAT Release Deglitch Time <ul> <li>Duration V<sub>NOBAT</sub> stays logic low to enable the charger</li> </ul>                                                                           | _    | 1.0                           | _        | ms   |       |

| t <sub>BATOVP</sub>            | BATREG OVP Release Deglitch Time <ul> <li>Duration BATREG stays below falling OVP level to enable charger/OTG</li> </ul>                                                                   | _    | 7.0                           | _        | ms   |       |

| t <sub>TRICKLE</sub>           | Trickle to Pre-charge Release Deglitch Time <ul> <li>Duration BATREG stays above trickle charge level to enable pre-charge</li> </ul>                                                      | _    | 7.0                           | _        | ms   |       |

| t <sub>PRCHG</sub>             | <ul> <li>Pre-charge to Fast Charge Release Deglitch Time</li> <li>Duration BATREG stays above pre-charge level to enable fast charge</li> </ul>                                            | _    | 7.0                           | _        | ms   |       |

| t <sub>ITOPOFF</sub>           | Top-Off Deglitch Time <ul> <li>Duration I<sub>FAST_CHG</sub> stays below Top-off level to generate an interrupt</li> </ul>                                                                 | _    | 7.0                           | _        | ms   |       |

| t <sub>BAT_RECHG</sub>         | Recharge Deglitch Time <ul> <li>Duration V<sub>BATREG</sub> stays below the V<sub>RCH</sub> Threshold</li> </ul>                                                                           | _    | 27                            | _        | ms   |       |

| t <sub>WAIT</sub>              | Waiting Time to Initiate Trickle Charge Mode <ul> <li>From t<sub>START_VSYS</sub> expire to initiate trickle charge</li> </ul>                                                             |      | 27                            | _        | ms   | (12)  |

| tweak_deb                      | Weak Battery Deglitch Time <ul> <li>Duration V<sub>BATREG</sub> stays below V<sub>WEAK_HYS</sub> in ENCOMPARATOR bit = 1</li> </ul>                                                        | _    | 27                            | _        | ms   |       |

| t <sub>START_VSYS</sub>        | VSYS Start-up Time <ul> <li>From VBUS stays above UVLO to VSYS start-up</li> </ul>                                                                                                         | _    | 220                           | _        | ms   |       |

| t <sub>INT_MASK</sub>          | Interrupt Mask Time                                                                                                                                                                        | —    | 10                            | _        | μs   |       |

| t <sub>ITOPOFF</sub>           | Overcurrent Discharge Deglitch Time <ul> <li>Duration I<sub>FAST_DISCHG</sub> stays above the overcurrent threshold in Discharge mode to generate an interrupt</li> </ul>                  | _    | 7.0                           | _        | ms   |       |

Notes

12. Guaranteed by design, characterization, and correlation with process controls. Not fully tested in production.

Characteristics noted under conditions:  $V_{VBUS}$  = 5.0 V,  $V_{BATREG}$  = 3.7 V,  $V_{VIO}$  = 1.8 V,  $C_{VBUS}$  =  $C_{PMID}$  = 2.2  $\mu$ F,  $C_{VSYS}$  = 10  $\mu$ F,  $C_{CHGOUT}$  = 4.7  $\mu$ F,  $C_{VL}$  = 1.0  $\mu$ F, L = 1.0  $\mu$ H, T<sub>A</sub> = -40 °C to 85 °C \*). Typical values are at T<sub>A</sub> = 25°C, unless otherwise noted. <sup>(6)</sup>

| Symbol                         | Characteristic                                                                                                                                                                                                       | Min. | Тур. | Max. | Unit | Notes     |

|--------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|-----------|

| Deglitch timer <sup>(12)</sup> | (continued)                                                                                                                                                                                                          |      |      | I    | I    |           |

| tvsysok_deb                    | VSYSOK Deglitch Time <ul> <li>Duration VSYS stays above 3.6 V to set the VSYSOK interrupt</li> <li>bit = 1 and pull the INTB pin Low in</li> <li>VBUSOK = ENCOMPARATOR = 1</li> </ul>                                | _    | 27   | _    | ms   |           |

| tvsysng_deb                    | VSYSNG Deglitch Time<br>• Duration VSYS stays at/below the V <sub>VSYS_MIN_OLP</sub> threshold to<br>set the VSYSNG interrupt bit = 1 and pull the INTB pin Low in<br>Discharge mode and ENCOMPARATOR = 1            | _    | 27   | _    | ms   |           |

| tvsysolp_deb                   | VSYSOLP Deglitch Time <ul> <li>Duration VSYS stays at/below the V<sub>VSYS_MIN_OLP</sub> threshold to<br/>set the VSYSOLP interrupt bit = 1 and pull the INTB pin Low in<br/>Overload mode and VBUSOK = 1</li> </ul> | _    | 27   | _    | ms   |           |

| Boost converter                |                                                                                                                                                                                                                      |      |      | 1    |      |           |

| I <sub>S_OTG</sub>             | Boost Supply Current <ul> <li>In OTG enabled with no load</li> </ul>                                                                                                                                                 | —    | 3.0  | _    | mA   |           |

|                                | Output Regulation Voltage Range <ul> <li>Programmable at PMID</li> </ul>                                                                                                                                             | 5.0  | _    | 5.2  | V    |           |

| I <sub>LIM_OTG</sub>           | Cycle-by-Cycle Current Limit                                                                                                                                                                                         |      | 2.4  | —    | A    |           |

| V <sub>BO_REG</sub>            | Boost Output Regulation Voltage at VBUS<br>• 3.0 V $\leq$ V <sub>BATREG</sub> $\leq$ 4.45 V, set to 5.1 V at PMID, 0 mA $\leq$ I <sub>LOAD</sub> $\leq$ 900 mA                                                       | 4.75 | 5.0  | 5.25 | v    | (13), (14 |

| I <sub>BO_MAX</sub>            | Maximum Continuous Output Current at VBUS<br>• $3.0 \text{ V} \le \text{V}_{\text{BATREG}} \le 4.45 \text{ V}$                                                                                                       | 0.9  | _    | _    | A    | (13)      |

| V <sub>BAT_MAX_BO</sub>        | Battery Operation Voltage Range <ul> <li>For the regulated output</li> </ul>                                                                                                                                         | 3.0  | _    | 4.45 | V    | (13)      |

| V <sub>START_BO</sub>          | BATREG Start Threshold Voltage for Boost<br>• V <sub>BATREG</sub> rising                                                                                                                                             | _    | 2.9  | _    | V    |           |

| V <sub>STOP_BO</sub>           | BATREG Stop Threshold Voltage for Boost <ul> <li>V<sub>BATREG</sub> falling</li> </ul>                                                                                                                               | _    | 2.5  | _    | V    |           |

| V <sub>BUS_OVP_H</sub>         | Overvoltage Protection at VBUS <ul> <li>VBUS rising, 400 mV Hysteresis</li> </ul>                                                                                                                                    | _    | 5.4  | _    | V    |           |

| NTB                            |                                                                                                                                                                                                                      |      |      |      |      |           |

|                                | Output Low Voltage<br>• I <sub>SINK</sub> = 5.0 mA                                                                                                                                                                   | _    | _    | 0.4  | V    |           |

| ogic inputs (CH                | GENB, SHDNB, and NOBAT)                                                                                                                                                                                              |      |      |      |      |           |

| V <sub>IH</sub>                | Logic Input High Voltage                                                                                                                                                                                             | 1.2  | —    | —    | V    |           |

| V <sub>IL</sub>                | Logic Input Low Voltage                                                                                                                                                                                              |      |      | 0.4  | V    |           |

| R <sub>PD</sub>                | Pull-down Resistance to GND <ul> <li>On CHGENB &amp; SHDNB pin</li> </ul>                                                                                                                                            | _    | 300  | _    | kΩ   |           |

| R <sub>PU</sub>                | Pull-up Resistance to VL <ul> <li>On NOBAT pin</li> </ul>                                                                                                                                                            | _    | 300  | _    | kΩ   |           |

Notes

Guaranteed by design, characterization, and correlation with process controls. Not fully tested in production. 13.

The regulation in boost is only guaranteed in the operation range. 14.

#### BC3770

Characteristics noted under conditions:  $V_{VBUS}$  = 5.0 V,  $V_{BATREG}$  = 3.7 V,  $V_{VIO}$  = 1.8 V,  $C_{VBUS}$  =  $C_{PMID}$  = 2.2  $\mu$ F,  $C_{VSYS}$  = 10  $\mu$ F,  $C_{CHGOUT}$  = 4.7  $\mu$ F,  $C_{VL}$  = 1.0  $\mu$ F, L = 1.0  $\mu$ H,  $T_A$  = -40 °C to 85 °C \*). Typical values are at  $T_A$  = 25°C, unless otherwise noted. <sup>(6)</sup>

| Symbol                                    | Characteristic                                                                                  | Min. | Тур. | Max. | Unit | Notes |

|-------------------------------------------|-------------------------------------------------------------------------------------------------|------|------|------|------|-------|

| Weak battery det                          | ection                                                                                          | •    | •    | •    | L    |       |

| V <sub>WEAK_L</sub>                       | Weak Battery Programmable Range <ul> <li>BATREG falling, programmable in 50 mV steps</li> </ul> | 3.0  | _    | 3.75 | V    |       |

|                                           | Weak Battery Threshold Accuracy                                                                 | -5.0 | —    | 0.4  | %    | (15)  |

| V <sub>WEAK_HYS</sub>                     | Weak Battery Voltage Hysteresis <ul> <li>BATREG rising</li> </ul>                               | _    | 100  | _    | mV   |       |

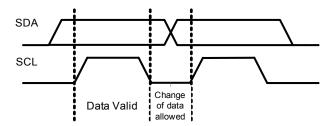

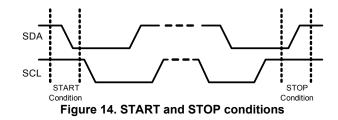

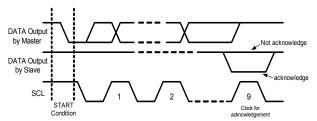

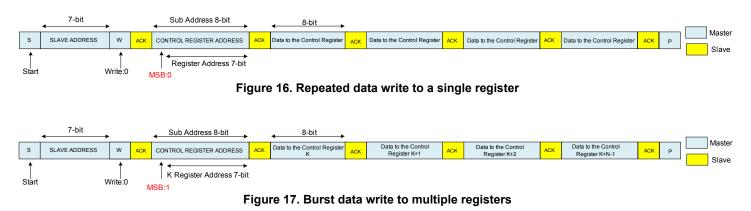

| <sup>2</sup> C interface <sup>(15),</sup> | (16)                                                                                            | ł    | •    | •    | L    |       |

| V <sub>IH_I2C</sub>                       | I <sup>2</sup> C Logic Input High Threshold Voltage <ul> <li>SDA, SCL</li> </ul>                | 1.2  | _    | _    | V    |       |

| V <sub>IL_I2C</sub>                       | I <sup>2</sup> C Logic Input Low Threshold Voltage <ul> <li>SDA. SCL</li> </ul>                 | _    | _    | 0.4  | V    |       |

| _                   | - 3DA, 30E                                                                                      |     |   |     |     |  |

|---------------------|-------------------------------------------------------------------------------------------------|-----|---|-----|-----|--|

| V <sub>OL_I2C</sub> | <ul> <li>I<sup>2</sup>C Logic Output Low Voltage</li> <li>SDA at 3.0 mA sink current</li> </ul> | _   |   | 0.4 | V   |  |

| f <sub>SCL</sub>    | SCL Clock Frequency                                                                             | 0.0 | _ | 400 | kHz |  |

|                     |                                                                                                 |     |   |     |     |  |

Notes

15. Guaranteed by design, characterization, and correlation with process controls. Not fully tested in production.

16. The regulation in boost is only guaranteed in the operation range.

# 5 Functional device operation

## 5.1 Introduction

The BC3770 is a fully programmable switching charger with a single-input for USB/DCP adapter and a dual-path output for single-cell Lilon and Li-Polymer batteries. The dual-path output allows mobile applications with a fully discharged or dead battery to boot up the system through the VSYS output. High-efficiency and switch-mode operation of the BC3770 reduce thermal dissipation and allows the battery to charge faster with a higher current capability. The BC3770 supports single input up to 20 V max. absolute voltage and charges the battery with the current up to 2.0 A. Owing to a high-efficiency in a wide range of input voltages and charging currents, the switch mode charger is a good choice for fast charging with less power loss and better thermal management than a linear charger. The charging parameters and operating modes are fully programmable over an I<sup>2</sup>C interface that operates up to 400 kHz in full speed. The BC3770 features a highly integrated synchronous switch-mode charger, intelligent power-path, VSYS stable control scheme in overload condition, and an automatic battery detection function. The charger and boost regulator circuit switches at 1.5 MHz, to minimize the size of external passive components.

To ensure USB compliance and minimize charging time, the input current is able to be limited to the value set through the  $I^2C$ . The setting of charge top-off current is also programmable over  $I^2C$ .

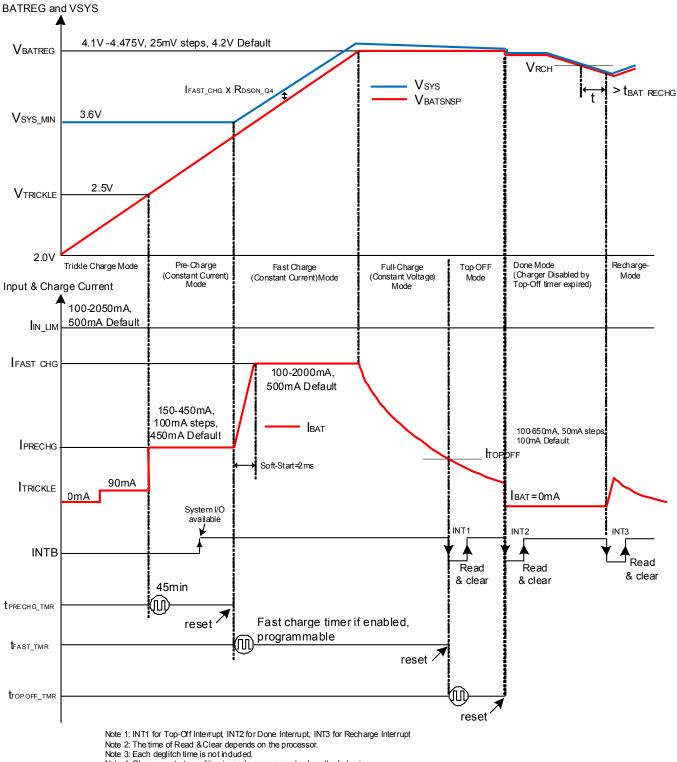

The BC3770 provides battery charging in four modes: trickle, pre-charge, fast charge (constant current), and full-charge (constant voltage). The charging restart circuit automatically restarts the fast-charge cycle in full-charge mode when the battery falls below an internal threshold over the deglitch time and detected top-off threshold. Input and charge status are reported to the processors through the interrupt pin, INTB. Charge current is reduced when the die temperature reaches 100 °C, while the system current is maintained. The BC3770 is able to operate as a boost regulator for USB-OTG devices over I<sup>2</sup>C.

## 5.2 Features

- · Dual-path output to power-up system in dead battery

- Single Input for USB/TA

- · High-efficiency synchronous switching regulator

- 20 V maximum withstanding input voltage

- Minimize the charging time with remote sense

- Up to 2.0 A load current for system or battery

- Programmable charge parameters via I<sup>2</sup>C compatible interface

- · Fast charge current

- Charge termination current

- · Battery regulation voltage

- Pre-charge current

- · Fast charge threshold voltage

- Charge reduction threshold voltage

- 400 kHz full-speed I<sup>2</sup>C interface

- 1.5 MHz switching frequency

- · Charge reduction mode for maximizing charging efficiency

- Protection

- Thermal protection

- Thermal regulation

- Input/output overvoltage protection

- Adaptive input current limit protection (AICL)

- · Reverse leakage protection

- No battery detection over pin detection

- Battery OVP protection

- Overcurrent protection in discharge mode

- Boost mode operation for USB OTG

- Output voltage: 5.0 V to 5.2 V, programmable at 900 mA

## 5.3 Operational modes

#### 5.3.1 Undervoltage lockout (UVLO)

The BC3770 has a typical undervoltage lockout threshold of 3.8 V, with a 200 mV hysteresis, rising on VBUS. VSYS also has a falling 2.5 V typical with 200 mV hysteresis. When the input supply voltage is below the 3.6 V typical UVLO falling level, the PWM buck converter turns off.

#### 5.3.2 Registers reset

All programmable registers in the device are reset to the default values when the following condition is met.

• Reset Condition: VSYS  $\leq$  V<sub>SYS\_UVLO</sub>

### 5.3.3 Q4 FET on in no valid VBUS

If the battery is connected with the voltage above a typical of 2.4 V and no any valid input power source is attached, the Q4 FET between VSYS and CHGOUT turns On and connects the Battery to the system, regardless of status of SHDNB. The VL regulator stays off.

## 5.3.4 Charge mode

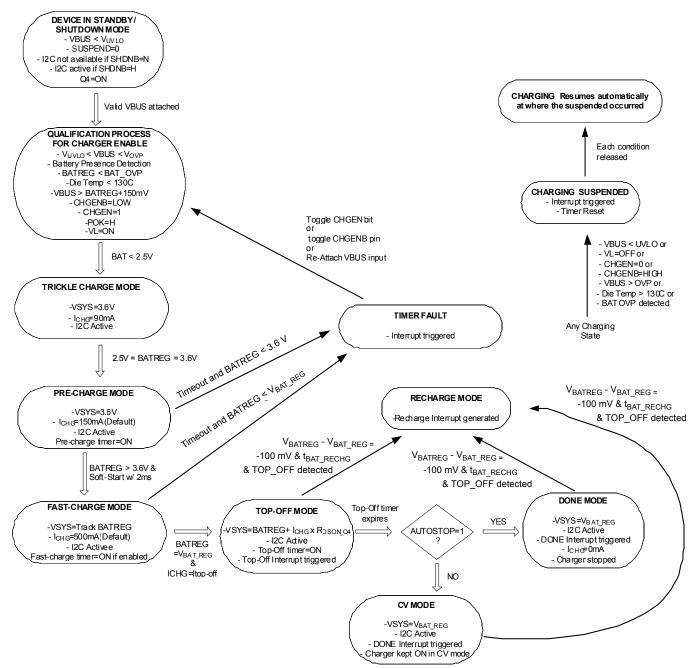

The BC3770 performs the following pre-qualification process before initiating the Charging mode:

- Input Voltage: Detect the validation of VBUS power source, charger enable threshold, and Adaptive-Input Current Limit (AICL) threshold. If the falling VBUS hits the AICL threshold, the charging current is reduced to limit the amount of drop on VBUS power source. In addition, the device senses the input voltage is at least above BATREG + 150 mV.

- Battery Presence Detection: Detect the status of battery presence through the NOBAT pin. If the voltage on the NOBAT pin is above the logic high threshold, the charging is suspended (Internal Q4 FET is open). However, VSYS is regulated at VVSYS\_MAX as long as a valid input source is attached.

- 3. Battery Voltage: Sense the battery voltage if it is less than the BAT OVP threshold.

- 4. Die Temperature: If the die temperature is above 130 °C or less than 150 °C, charging is suspended.

- 5. Overvoltage Detection (OVP): Sense if the VBUS is less than the OVP threshold. If the OVP condition is detected, the PWM converter is immediately shut off.

- 6. Validation of Software and Hardware Enable signals: Detect the status of software enable bit, CHGEN=1, SUSPEN=0, and hardware pin of CHGENB=LOW.

This pre-qualification process is continuously monitored and charging is suspended until all conditions are met.

### 5.3.5 Charging profile

#### 5.3.5.1 Trickle-charge mode

Trickle-charge mode is automatically enabled in 27 ms after the VSYS start-up time expires. The battery is charged with a fixed 90 mA charge current until the battery voltage reaches the threshold, 2.5 V typical in rising. This threshold is not programmable over I<sup>2</sup>C. As soon as the battery voltage crosses over the threshold, a pre-charge mode is activated automatically after the fixed deglitch time. This allows the protection circuit in the battery pack to be reset with no damage, and brings the battery voltage to a higher level.

#### 5.3.5.2 Pre-charge mode

The Pre-charge mode is enabled in  $t_{TRICKLE}$  when the battery voltage crosses over a typical 2.5 V. The safety timer called pre-charge timer,  $t_{PRECHG_TMR}$ , 45-minute counts at the same time as well. This timer is reset as soon as the Fast-charge mode is initiated. This allows a deeply discharged battery to charge safely. The pre-charge current is programmable from 150 mA to 450 mA in 100 mA steps over I<sup>2</sup>C. If the battery voltage does not exceed the V<sub>VSYS\_MIN</sub> threshold before the timer expires, charging is suspended and a fault signal is asserted via the INTB pin. If the VSYS voltage drops due to the limited input power source during the mode, the charge current is automatically reduce to maintain the VSYS as low as at 3.4 V. If the load is still overloaded, even in no charge current and limited input current, the VSYS can't help the collapse.

#### 5.3.5.3 Fast-charge mode (constant-current mode)

The Fast-charge mode is entered in  $t_{PRECHG}$  when the battery voltage exceeds the  $V_{VSYS\_MIN}$  threshold of a typical 3.6 V. During this mode, the battery is charged with a programmable fast-charge current. The fast-charge current is programmable from 100 mA to 2000 mA with a 500 mA default. Fast-charge current is always limited by the input current limit setting. As soon as the battery voltage reaches the  $V_{VSYS\_MIN}$  threshold, VSYS tracks the battery voltage through the Q4. This is called 'tracking mode". In tracking mode, power dissipation is minimized by RDSON\_Q4 x IFAST\_CHG. However, if the VSYS voltage drops during the fast-charge mode, the charge current is automatically reduce to keep the dropout voltage, to ensure proper operation of charging circuitry. During this fast-charge mode, the safety timer called fast charge timer,  $t_{FAST\_TMR}$ , counts. If the battery voltage does not reach the  $V_{BAT\_REG}$  threshold before the timer expires, charging is suspended and a fault signal is asserted via the INTB pin. This timer is programmable and is disabled by default. This timer is automatically disabled when the input current limit is set to 100 mA.

#### 5.3.5.4 Full-charge mode (constant-voltage mode)

As soon as the BATREG voltage reaches the  $V_{BAT_REG}$  threshold, the fast-charge current is reduced to a programmable top-off current. The  $V_{BAT_REG}$  regulation threshold is programmable from 4.1 V to 4.475 V in 25 mV steps.

#### 5.3.5.5 Top-off mode (constant-voltage mode)

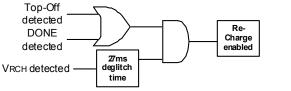

If the charge current down to a pre-programmed top-off current threshold is sensed over  $t_{ITOPOFF}$ , the safety timer called top-off timer,  $t_{TOPOFF\_TMR}$ , 45-minute by default, automatically counts. The top-off interrupt event is reported to the processor via the INTB. As soon as the processor reads the interrupt registers, the processor is able to turn off the charger by either CHGENB = H, CHGEN = 0, or wait until the timer expires in AUTOSTOP=1. The top-off current is programmable from 100 mA to 650 mA in 50 mA steps. 100 mA is the default.

#### 5.3.5.6 Done mode (constant-voltage mode)

After the top-off timer expires, the charger is Off automatically in AUTOSTOP=1. However, the charger stays at CV (Constant-voltage mode) in AUTOSTOP=0 even though the top-off timer expires. The interrupt signal of Done is reported to the processors via the INTB pin, regardless of the AUTOSTOP status.

## 5.3.6 Boost (OTG) mode

Similar to Charge mode operation, in OTG mode enabled by  $l^2C$  control bit, ENBOOST = 1, the device provides a regulated output voltage to VBUS from the battery. In Boost mode, the device first converts the battery voltage to a target voltage at PMID, then bypasses it to the VBUS pin with load current up to 900 mA to support USB OTG devices. In order to have a final regulated output at VBUS, the minimum input at BATREG should be at least or above 3.0 V. To activate Boost mode, all of the following conditions should be met in advance.

- 1. Either the CHGEN bit resets to "0" or CHGENB = HIGH (meaning for "charger disabled")

- 2. The VBUS voltage must be less than the UVLO falling threshold

- 3. No Fault Conditions

- 4. SUSPEN bit reset to "0"

Then set the ENBOOST bit to "1". In this Boost mode, the following functions are consequently disabled.

- AICL

- Charging

#### 5.3.6.1 Soft-start in Boost mode

When Boost mode is enabled, the PMID is regulated to a pre-programmed voltage. After PMID reaches a preset target regulation voltage, the FET between PMID and VBUS turns On slowly to minimize the inrush current. The output current limit is ramped up to the boost output current limit. This soft-start counter is not initialized when one of next conditions occur.

- 1. Die temperature exceeds  $T_{SD}$

- 2. No battery detection (NOBAT = H) on NOBAT

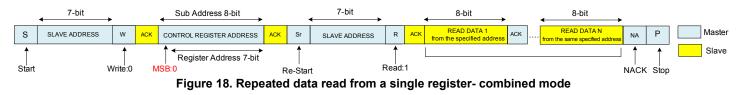

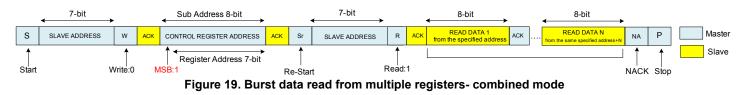

- 3. Voltage on VBUS rises over  $V_{\text{BUS}\_\text{OVP}}$