# Kinetis KE1xZ with up to 256 KB Flash

Up to 72 MHz ARM® Cortex®-M0+ Based Microcontroller

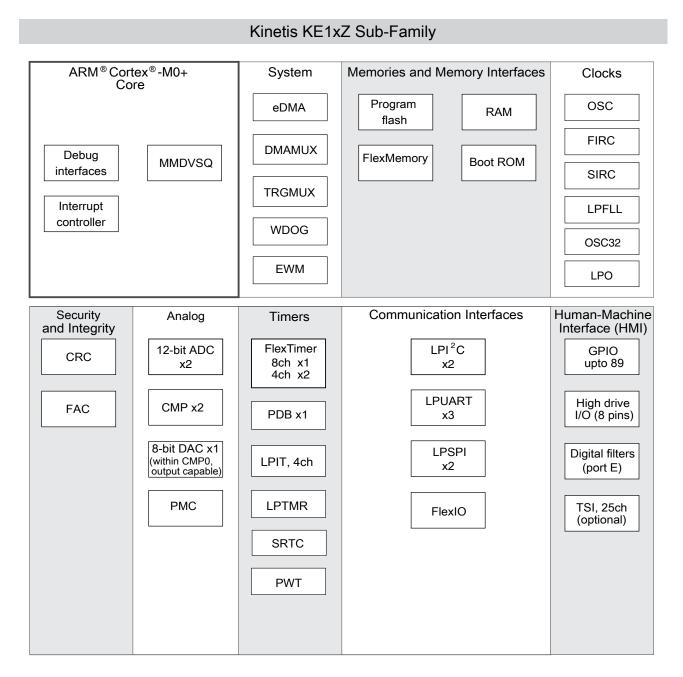

Kinetis KE1xZ256 MCUs are the leading parts for the KE1xZ familiy based on ARM<sup>®</sup> Cortex<sup>®</sup>-M0+ core. Providing up to 256 KB flash, up to 32 KB RAM, and the complete set of analog/ digital features, KE1xZ extends Kinetis E family to higher performance and broader scalability. Robust TSI provides highlevel stability and accuracy to customer's HMI system. 1 Msps ADC and FlexTimer help build a perfect solution for BLDC motor control systems.

#### MKE1xZ256VLL7 MKE1xZ256VLH7 MKE1xZ128VLL7 MKE1xZ128VLH7

#### **Core Processor and System**

- ARM<sup>®</sup> Cortex<sup>®</sup>-M0+ core, supports up to 72 MHz frequency

- ARM Core based on the ARMv6 Architecture and Thumb<sup>®</sup>-2 ISA

- Configurable Nested Vectored Interrupt Controller (NVIC)

- Memory-Mapped Divide and Square Root module (MMDVSQ)

- 8-channel DMA controller extended up to 63 channels with DMAMUX

#### Reliability, safety and security

- Flash Access Control (FAC)

- Cyclic Redundancy Check (CRC) generator module

- 128-bit unique identification (ID) number

- Internal watchdog (WDOG) with independent clock source

- External watchdog monitor (EWM) module

- ADC self calibration feature

- On-chip clock loss monitoring

#### Human-machine interface (HMI)

- Supports up to 32 interrupt request (IRQ) sources

- Up to 89 GPIO pins with interrupt functionality

- Touch sensing input (TSI) module

#### Memory and memory interfaces

- Up to 256 KB program flash

- · Up to 32 KB SRAM

- 32 KB FlexNVM for data flash and with EEPROM emulation

- 2 KB FlexRAM for EEPROM emulation

- 128 Bytes flash cache

- · Boot ROM with built in bootloader

#### **Mixed-signal analog**

- 2× 12-bit analog-to-digital converter (ADC) with up to 16 channel analog inputs per module, up to 1 Msps

- 2× high-speed analog comparators (CMP) with internal 8-bit digital to analog converter (DAC); the 8-bit DAC of CMP0 supports an output option to pad with a buffer

#### Timing and control

- 3× Flex Timers (FTM) for PWM generation, offering up to 8 standard channels

- 1× 16-bit Low-Power Timer (LPTMR) with flexible wake up control

- 1× Programmable Delay Block (PDB) with flexible trigger system

- 1× 32-bit Low-power Periodic Interrupt Timer (LPIT) with 4 channels

- Real timer clock (RTC)

NXP reserves the right to change the production detail specifications as may be required to permit improvements in the design of its products.

#### **Clock interfaces**

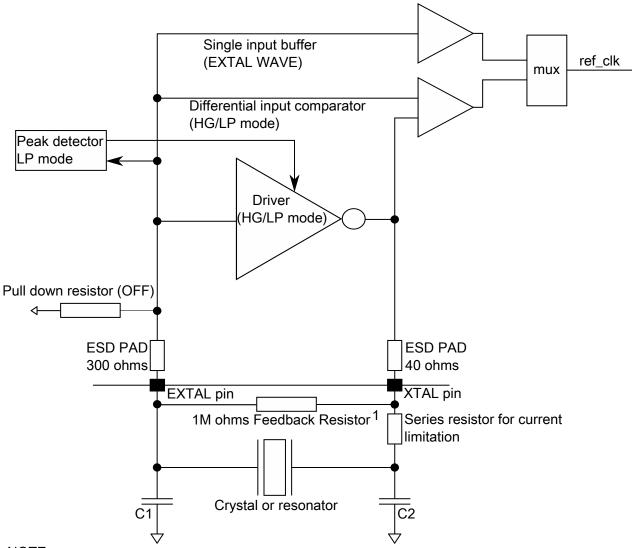

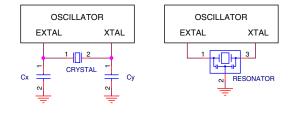

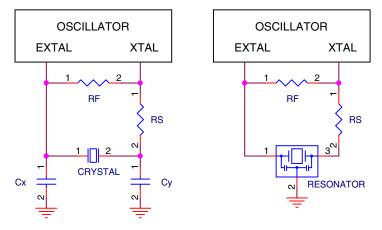

- 4 40 MHz fast external oscillator (OSC)

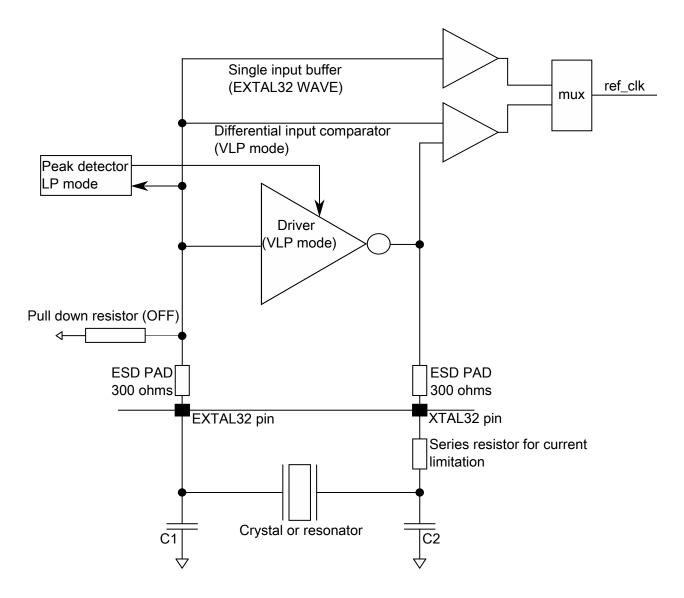

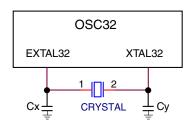

- 32 kHz slow external oscillator (OSC32)

- 48 60 MHz high-accuracy (up to ±1%) fast internal reference clock (FIRC) for normal Run

- 8 MHz / 2 MHz high-accuracy (up to ±3%) slow internal reference clock (SIRC) for low-speed Run

- 128 kHz low power oscillator (LPO)

- Low-power FLL (LPFLL)

- Up to 60 MHz DC external square wave input clock

- System clock generator (SCG)

- Real time counter (RTC)

#### **Power management**

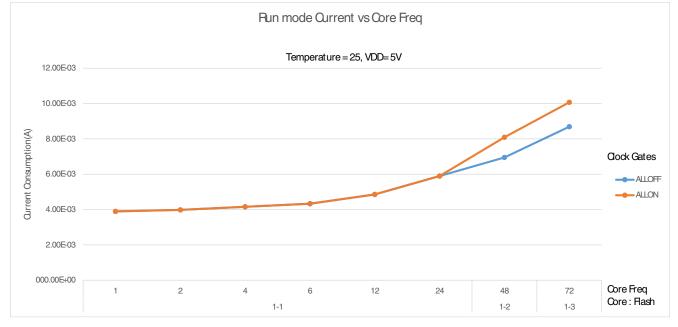

- Low-power ARM Cortex-M0+ core with excellent energy efficiency

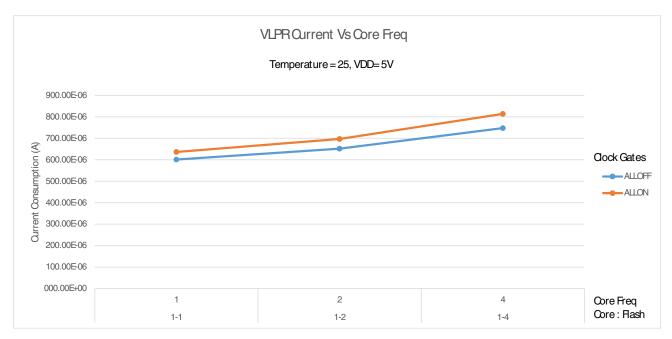

- Power management controller (PMC) with multiple power modes: Run, Wait, Stop, VLPR, VLPW and VLPS

- Supports clock gating for unused modules, and specific peripherals remain working in low power modes

- POR, LVD/LVR

#### **Connectivity and communications interfaces**

- 3× low-power universal asynchronous receiver/ transmitter (LPUART) modules with DMA support and low power availability

- 2× low-power serial peripheral interface (LPSPI) modules with DMA support and low power availability

- 2× low-power inter-integrated circuit (LPI2C) modules with DMA support and low power availability

- FlexIO module for flexible and high performance serial interfaces

#### **Debug functionality**

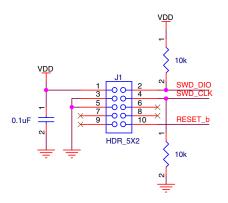

- · Serial Wire Debug (SWD) debug interface

- Debug Watchpoint and Trace (DWT)

- Micro Trace Buffer (MTB)

#### Operating Characteristics

- Voltage range: 2.7 to 5.5 V

- Ambient temperature range: -40 to 105 °C

#### **Related Resources**

| Туре                | Description                                                                                                                    | Resource                       |

|---------------------|--------------------------------------------------------------------------------------------------------------------------------|--------------------------------|

| Selector<br>Guide   | The Solution Advisor is a web-based tool that features interactive application wizards and a dynamic product selector.         | Solution Advisor               |

| Product Brief       | The Product Brief contains concise overview/summary information to enable quick evaluation of a device for design suitability. | KE1xZ256PB <sup>1</sup>        |

| Reference<br>Manual | The Reference Manual contains a comprehensive description of the structure and function (operation) of a device.               | KE1xZP100M72SF0RM <sup>1</sup> |

| Data Sheet          | The Data Sheet includes electrical characteristics and signal                                                                  | This document:                 |

|                     | connections.                                                                                                                   | KE1xZP100M72SF0                |

| Chip Errata         | The chip mask set Errata provides additional or corrective information for                                                     | Kinetis_E_1N36S <sup>1</sup>   |

|                     | a particular device mask set.                                                                                                  | Kinetis_E_2N36S <sup>1</sup>   |

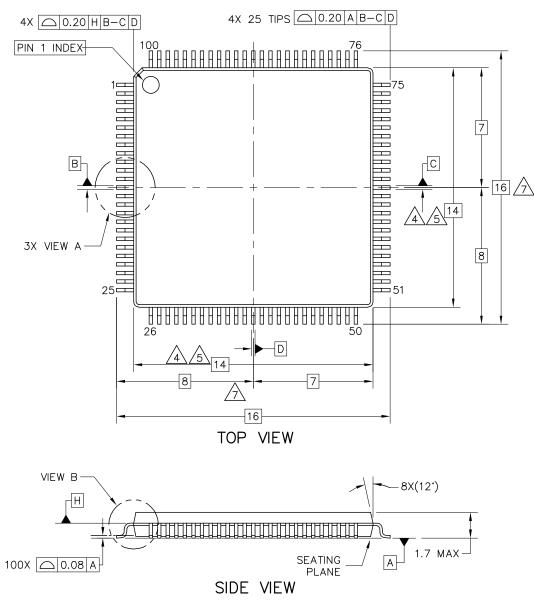

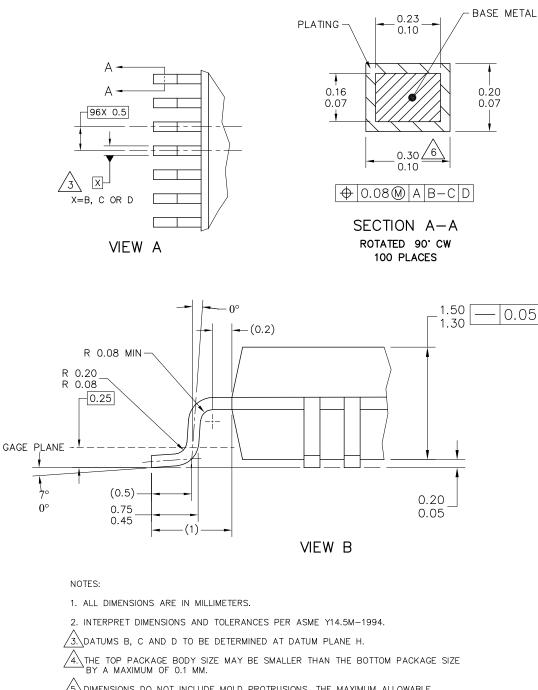

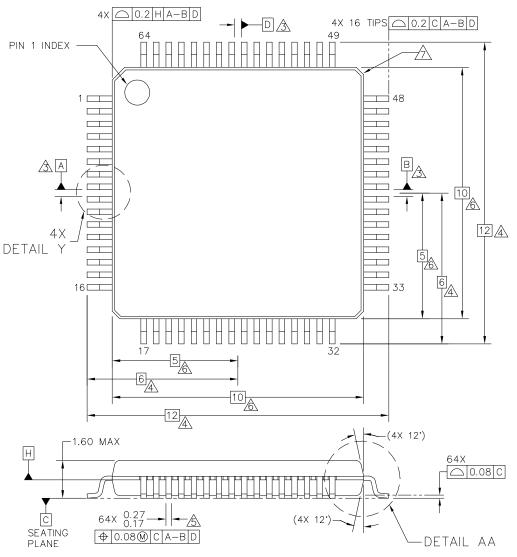

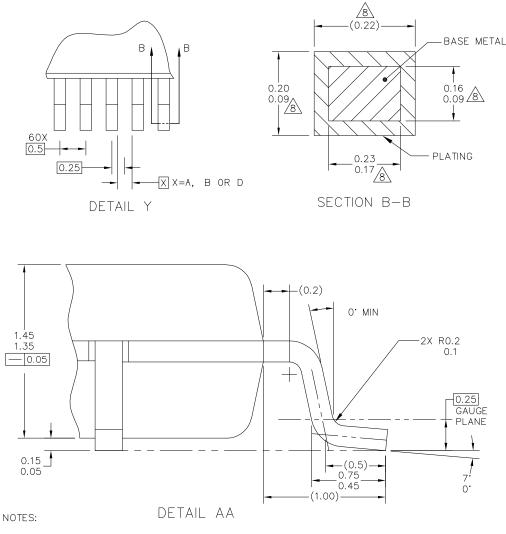

| Package             | Package dimensions are provided in package drawings.                                                                           | 100-LQFP: 98ASS23308W          |

| drawing             |                                                                                                                                | 64-LQFP: 98ASS23234W           |

1. To find the associated resource, go to http://www.nxp.com and perform a search using this term.

# **Table of Contents**

| 1 | Ord  | ering info  | rmation5                                |  |  |  |  |  |  |  |  |

|---|------|-------------|-----------------------------------------|--|--|--|--|--|--|--|--|

| 2 | Ove  | erview5     |                                         |  |  |  |  |  |  |  |  |

|   | 2.1  | System      | features6                               |  |  |  |  |  |  |  |  |

|   |      | 2.1.1       | ARM Cortex-M0+ core 6                   |  |  |  |  |  |  |  |  |

|   |      | 2.1.2       | NVIC7                                   |  |  |  |  |  |  |  |  |

|   |      | 2.1.3       | AWIC7                                   |  |  |  |  |  |  |  |  |

|   |      | 2.1.4       | Memory                                  |  |  |  |  |  |  |  |  |

|   |      | 2.1.5       | Reset and boot8                         |  |  |  |  |  |  |  |  |

|   |      | 2.1.6       | Clock options10                         |  |  |  |  |  |  |  |  |

|   |      | 2.1.7       | Security11                              |  |  |  |  |  |  |  |  |

|   |      | 2.1.8       | Power management12                      |  |  |  |  |  |  |  |  |

|   |      | 2.1.9       | Debug controller13                      |  |  |  |  |  |  |  |  |

|   | 2.2  | Peripher    | al features13                           |  |  |  |  |  |  |  |  |

|   |      | 2.2.1       | eDMA and DMAMUX 13                      |  |  |  |  |  |  |  |  |

|   |      | 2.2.2       | FTM14                                   |  |  |  |  |  |  |  |  |

|   |      | 2.2.3       | ADC14                                   |  |  |  |  |  |  |  |  |

|   |      | 2.2.4       | CMP15                                   |  |  |  |  |  |  |  |  |

|   |      | 2.2.5       | RTC16                                   |  |  |  |  |  |  |  |  |

|   |      | 2.2.6       | LPIT16                                  |  |  |  |  |  |  |  |  |

|   |      | 2.2.7       | PDB17                                   |  |  |  |  |  |  |  |  |

|   |      | 2.2.8       | LPTMR                                   |  |  |  |  |  |  |  |  |

|   |      | 2.2.9       | CRC 17                                  |  |  |  |  |  |  |  |  |

|   |      | 2.2.10      | LPUART                                  |  |  |  |  |  |  |  |  |

|   |      | 2.2.11      | LPSPI                                   |  |  |  |  |  |  |  |  |

|   |      | 2.2.12      | LPI2C                                   |  |  |  |  |  |  |  |  |

|   |      | 2.2.13      | FlexIO20                                |  |  |  |  |  |  |  |  |

|   |      | 2.2.14      | Port control and GPIO20                 |  |  |  |  |  |  |  |  |

| 3 | Mer  | nory map    |                                         |  |  |  |  |  |  |  |  |

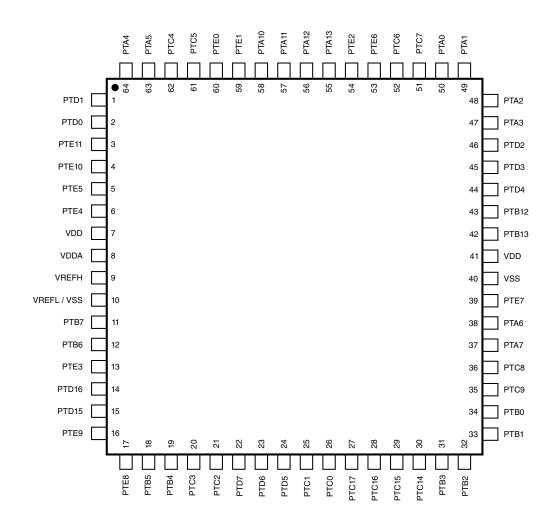

| 4 | Pind | outs        |                                         |  |  |  |  |  |  |  |  |

|   | 4.1  | KE1xZ S     | Signal Multiplexing and Pin Assignments |  |  |  |  |  |  |  |  |

|   | 4.2  | Port con    | trol and interrupt summary27            |  |  |  |  |  |  |  |  |

|   | 4.3  | Module      | Signal Description Tables28             |  |  |  |  |  |  |  |  |

|   | 4.4  | Pinout d    | iagram                                  |  |  |  |  |  |  |  |  |

|   | 4.5  | Package     | e dimensions                            |  |  |  |  |  |  |  |  |

| 5 | Elec | ctrical cha | aracteristics40                         |  |  |  |  |  |  |  |  |

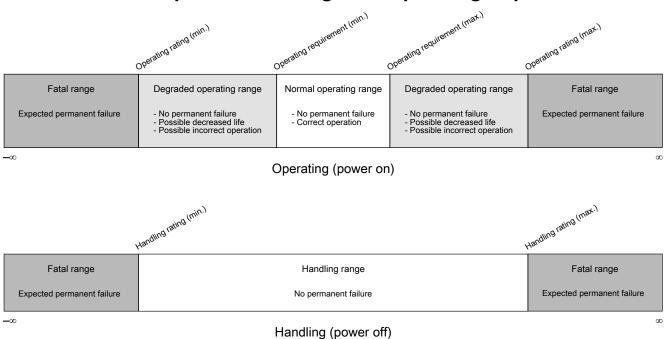

|   | 5.1  | Termino     | logy and guidelines40                   |  |  |  |  |  |  |  |  |

|   |      | 5.1.1       | Definitions 40                          |  |  |  |  |  |  |  |  |

|   |      | 5.1.2       | Examples                                |  |  |  |  |  |  |  |  |

|      | 5.1.3        | Typical-value conditions                   | 41 |

|------|--------------|--------------------------------------------|----|

|      | 5.1.4        | Relationship between ratings and operating | ıg |

|      |              | requirements                               | 41 |

|      | 5.1.5        | Guidelines for ratings and operating       |    |

|      |              | requirements                               | 42 |

| 5.   | 2 Rating     | S                                          | 42 |

|      | 5.2.1        | Thermal handling ratings                   | 42 |

|      | 5.2.2        | Moisture handling ratings                  | 43 |

|      | 5.2.3        | ESD handling ratings                       | 43 |

|      | 5.2.4        | Voltage and current operating ratings      | 43 |

| 5.   | 3 Genera     | al                                         | 44 |

|      | 5.3.1        | Nonswitching electrical specifications     | 44 |

|      | 5.3.2        | Switching specifications                   | 54 |

|      | 5.3.3        | Thermal specifications                     | 57 |

| 5.   | 4 Periph     | eral operating requirements and behaviors  | 60 |

|      | 5.4.1        | System modules                             | 60 |

|      | 5.4.2        | Clock interface modules                    | 60 |

|      | 5.4.3        | Memories and memory interfaces             | 67 |

|      | 5.4.4        | Security and integrity modules             | 69 |

|      | 5.4.5        | Analog                                     | 70 |

|      | 5.4.6        | Communication interfaces                   | 76 |

|      | 5.4.7        | Human-machine interfaces (HMI)             | 80 |

|      | 5.4.8        | Debug modules                              | 80 |

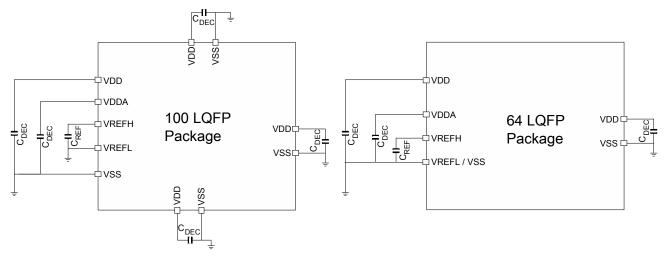

| 6 D  | esign con    | siderations                                | 81 |

| 6.   | 1 Hardwa     | are design considerations                  | 82 |

|      | 6.1.1        | Printed circuit board recommendations      | 82 |

|      | 6.1.2        | Power delivery system                      | 82 |

|      | 6.1.3        | Analog design                              | 82 |

|      | 6.1.4        | Digital design                             | 83 |

|      | 6.1.5        | Crystal oscillator                         | 86 |

| 6.   | 2 Softwa     | re considerations                          | 87 |

| 7 Pa | art identifi | cation                                     | 88 |

| 7.   | 1 Descrip    | ption                                      | 88 |

| 7.   | 2 Format     | t                                          | 88 |

| 7.   | 3 Fields.    |                                            | 88 |

| 7.   | 4 Examp      | le                                         | 89 |

| 8 R  | evision his  | story                                      | 89 |

|      |              |                                            |    |

# **1** Ordering information

The following chips are available for ordering.

| Product       | Memory        |              |                             | Pac          | kage        | IO ar | НМІ                                |                     |     |

|---------------|---------------|--------------|-----------------------------|--------------|-------------|-------|------------------------------------|---------------------|-----|

| Part number   | Flash<br>(KB) | SRAM<br>(KB) | FlexNVM/<br>FlexRAM<br>(KB) | Pin<br>count | Packag<br>e | GPIOs | GPIOs<br>(INT/HD<br>) <sup>1</sup> | ADC<br>channel<br>s | TSI |

| MKE15Z256VLL7 | 256           | 32           | 32/2                        | 100          | LQFP        | 89    | 89/8                               | 16+12               | Yes |

| MKE15Z256VLH7 | 256           | 32           | 32/2                        | 64           | LQFP        | 58    | 58/8                               | 16+11               | Yes |

| MKE15Z128VLL7 | 128           | 16           | 32/2                        | 100          | LQFP        | 89    | 89/8                               | 16+12               | Yes |

| MKE15Z128VLH7 | 128           | 16           | 32/2                        | 64           | LQFP        | 58    | 58/8                               | 16+11               | Yes |

| MKE14Z256VLL7 | 256           | 32           | 32/2                        | 100          | LQFP        | 89    | 89/8                               | 16+12               | No  |

| MKE14Z256VLH7 | 256           | 32           | 32/2                        | 64           | LQFP        | 58    | 58/8                               | 16+11               | No  |

| MKE14Z128VLL7 | 128           | 16           | 32/2                        | 100          | LQFP        | 89    | 89/8                               | 16+12               | No  |

| MKE14Z128VLH7 | 128           | 16           | 32/2                        | 64           | LQFP        | 58    | 58/8                               | 16+11               | No  |

Table 1. Ordering information

1. INT: interrupt pin numbers; HD: high drive pin numbers

# 2 Overview

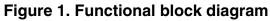

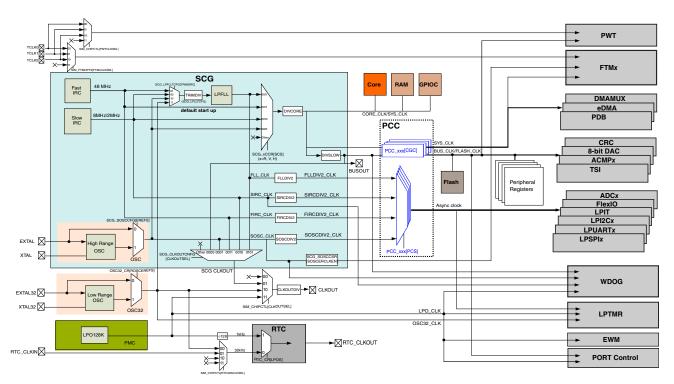

The following figure shows the system diagram of this device.

Overview

Figure 2. System diagram

The crossbar switch connects bus masters and slaves using a crossbar switch structure. This structure allows up to four bus masters to access different bus slaves simultaneously, while providing arbitration among the bus masters when they access the same slave.

## 2.1 System features

The following sections describe the high-level system features.

### 2.1.1 ARM Cortex-M0+ core

The enhanced ARM Cortex M0+ is the member of the Cortex-M Series of processors targeting microcontroller cores focused on very cost sensitive, low power applications. It has a single 32-bit AMBA AHB-Lite interface and includes an NVIC component. It also has hardware debug functionality including support for simple program trace capability. The processor supports the ARMv6-M instruction set (Thumb) architecture including all but three 16-bit Thumb opcodes (52 total) plus seven 32-bit instructions. It is upward compatible with other Cortex-M profile processors.

# 2.1.2 NVIC

The Nested Vectored Interrupt Controller supports nested interrupts and 4 priority levels for interrupts. In the NVIC, each source in the IPR registers contains 2 bits. It also differs in number of interrupt sources and supports 32 interrupt vectors.

The Cortex-M family uses a number of methods to improve interrupt latency to up to 15 clock cycles for Cortex-M0+. It also can be used to wake the MCU core from Wait and VLPW modes.

## 2.1.3 AWIC

The asynchronous wake-up interrupt controller (AWIC) is used to detect asynchronous wake-up events in Stop mode and signal to clock control logic to resume system clocking. After clock restarts, the NVIC observes the pending interrupt and performs the normal interrupt or event processing. The AWIC can be used to wake MCU core from Partial Stop, Stop and VLPS modes.

Wake-up sources for this SoC are listed as below:

| Wake-up source          | Description                                                                     |

|-------------------------|---------------------------------------------------------------------------------|

| Available system resets | RESET pin, WDOG, loss of clock(LOC) reset and loss of lock (LOL) reset          |

| Pin interrupts          | Port Control Module - Any enabled pin interrupt is capable of waking the system |

| ADCx                    | ADCx is optional functional with clock source from SIRC or OSC                  |

| CMPx                    | Functional in Stop/VLPS modes with clock source from SIRC or OSC                |

| LPI2C                   | Functional in Stop/VLPS modes with clock source from SIRC or OSC                |

| LPUART                  | Functional in Stop/VLPS modes with clock source from SIRC or OSC                |

Table 2. AWIC Stop and VLPS Wake-up Sources

Table continues on the next page...

| Wake-up source | Description                                                      |

|----------------|------------------------------------------------------------------|

| LPSPI          | Functional in Stop/VLPS modes with clock source from SIRC or OSC |

| LPIT           | Functional in Stop/VLPS modes with clock source from SIRC or OSC |

| FlexIO         | Functional in Stop/VLPS modes with clock source from SIRC or OSC |

| LPTMR          | Functional in Stop/VLPS modes                                    |

| RTC            | Functional in Stop/VLPS modes                                    |

| SCG            | Functional in Stop mode (Only SIRC)                              |

| TSI            | Touch sense wakeup                                               |

| NMI            | Non-maskable interrupt                                           |

#### Table 2. AWIC Stop and VLPS Wake-up Sources (continued)

#### 2.1.4 Memory

This device has the following features:

- Upto 256 KB of embedded program flash memory.

- Upto 32 KB of embedded RAM accessible (read/write) at CPU clock speed with 0 wait states.

- The non-volatile memory is divided into several arrays:

- 32 KB of embedded data flash memory

- 2 KB of Emulated EEPROM

- 8 KB ROM (built-in bootloader to support UART, I2C, and SPI interfaces)

The program flash memory contains a 16-byte flash configuration field that stores default protection settings and security information. The page size of program flash is 1 KB.

The protection setting can protect 32 regions of the program flash memory from unintended erase or program operations.

The security circuitry prevents unauthorized access to RAM or flash contents from debug port.

### 2.1.5 Reset and boot

The following table lists all the reset sources supported by this device.

#### NOTE

In the following table, Y means the specific module, except for the registers, bits or conditions mentioned in the footnote, is reset by the corresponding Reset source. N means the specific module is not reset by the corresponding Reset source.

| Reset            | Descriptions                                                 | Modules        |                |                |                |                            |                |                |     |           |            |

|------------------|--------------------------------------------------------------|----------------|----------------|----------------|----------------|----------------------------|----------------|----------------|-----|-----------|------------|

| sources          |                                                              | РМС            | SIM            | SMC            | RCM            | Reset<br>pin is<br>negated | WDO<br>G       | SCG            | RTC | LPTM<br>R | Other<br>s |

| POR reset        | Power-on reset (POR)                                         | Y              | Y              | Y              | Y              | Y                          | Y              | Y              | Y   | Y         | Y          |

| System<br>resets | Low-voltage detect<br>(LVD)                                  | Y <sup>1</sup> | Y              | Y              | Y              | Y                          | Y              | Y              | N   | Y         | Y          |

|                  | External pin reset<br>(RESET)                                | Y <sup>1</sup> | Y <sup>2</sup> | Y <sup>3</sup> | Y <sup>4</sup> | Y                          | Y <sup>5</sup> | Y <sup>6</sup> | N   | N         | Y          |

|                  | Watchdog (WDOG)<br>reset                                     | Y <sup>1</sup> | Y <sup>2</sup> | Y <sup>3</sup> | Y <sup>4</sup> | Y                          | Y <sup>5</sup> | Y <sup>6</sup> | N   | N         | Y          |

|                  | Multipurpose clock<br>generator loss of clock<br>(LOC) reset | Y <sup>1</sup> | Y <sup>2</sup> | Y <sup>3</sup> | Y <sup>4</sup> | Y                          | Y <sup>5</sup> | Y <sup>6</sup> | N   | N         | Y          |

|                  | Multipurpose clock<br>generator loss of lock<br>(LOL) reset  | Y <sup>1</sup> | Y <sup>2</sup> | Y <sup>3</sup> | Y <sup>4</sup> | Y                          | Y <sup>5</sup> | Y <sup>6</sup> | N   | N         | Y          |

|                  | Stop mode acknowledge error (SACKERR)                        | Y <sup>1</sup> | Y <sup>2</sup> | Y <sup>3</sup> | Y <sup>4</sup> | Y                          | Y <sup>5</sup> | Y <sup>6</sup> | N   | N         | Y          |

|                  | Software reset (SW)                                          | Y <sup>1</sup> | Y <sup>2</sup> | Y <sup>3</sup> | Y <sup>4</sup> | Y                          | Y <sup>5</sup> | Y <sup>6</sup> | Ν   | N         | Y          |

|                  | Lockup reset (LOCKUP)                                        | Y <sup>1</sup> | Y <sup>2</sup> | Y <sup>3</sup> | Y <sup>4</sup> | Y                          | Y <sup>5</sup> | Y <sup>6</sup> | N   | Ν         | Y          |

|                  | MDM DAP system reset                                         | Y <sup>1</sup> | Y <sup>2</sup> | Y <sup>3</sup> | Y <sup>4</sup> | Y                          | Y <sup>5</sup> | Y <sup>6</sup> | N   | Ν         | Y          |

| Debug reset      | Debug reset                                                  | Y <sup>1</sup> | Y <sup>2</sup> | Y <sup>3</sup> | Y <sup>4</sup> | Y                          | Y <sup>5</sup> | Y <sup>6</sup> | N   | Ν         | Y          |

Table 3.Reset source

1. Except PMC\_LVDSC1[LVDV] and PMC\_LVDSC2[LVWV]

- 2. Except SIM\_SOPT1

- 3. Except SMC\_PMPROT, SMC\_PMCTRL\_RUM, SMC\_PMCTRL\_STOPM, SMC\_STOPCTRL, SMC\_PMSTAT

- 4. Except RCM\_RPC, RCM\_MR, RCM\_FM, RCM\_SRIE, RCM\_SRS, RCM\_SSRS

- 5. Except WDOG\_CS[TST]

- 6. Except SCG\_CSR and SCG\_FIRCSTAT

This device supports booting from:

- internal flash

- boot ROM

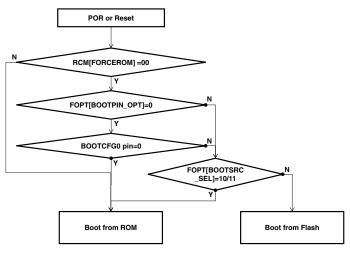

Figure 3. Boot flow chart

The blank chip is default to boot from ROM and remaps the vector table to ROM base address, otherwise, it remaps to flash address.

## 2.1.6 Clock options

The SCG module controls which clock source is used to derive the system clocks. The clock generation logic divides the selected clock source into a variety of clock domains, including the clocks for the system bus masters, system bus slaves, and flash memory. The clock generation logic also implements module-specific clock gating to allow granular shutoff of modules.

The following figure is a high level block diagram of the clock generation. For more details on the clock operation and configuration, see the Clocking chapter in the Reference Manual.

Figure 4. Clocking block diagram

## 2.1.7 Security

Security state can be enabled via programming flash configure field (0x40e). After enabling device security, the SWD port cannot access the memory resources of the MCU.

| External interface | Security  | Unsecure                                                                                                                                                       |  |  |  |

|--------------------|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| SWD port           | interface | the debugger can write to the Flash<br>Mass Erase in Progress field of the<br>MDM-AP Control register to trigger a<br>mass erase (Erase All Blocks)<br>command |  |  |  |

### 2.1.7.1 Flash Access Control (FAC)

The FAC is a native or third-party configurable memory protection scheme optimized to allow end users to utilize software libraries while offering programmable restrictions to these libraries. The flash memory is divided into equal size segments that provide protection to proprietary software libraries. The protection of these segments is controlled as the FAC provides a cycle-by-cycle evaluation of the access

rights for each transaction routed to the on-chip flash memory. Configurability allows an increasing number of protected segments while supporting two levels of vendors adding their proprietary software to a device.

### 2.1.8 Power management

The Power Management Controller (PMC) expands upon ARM's operational modes of Run, Sleep, and Deep Sleep, to provide multiple configurable modes. These modes can be used to optimize current consumption for a wide range of applications. The WFI or WFE instruction invokes a Wait or a Stop mode, depending on the current configuration. For more information on ARM's operational modes, See the ARM<sup>®</sup> Cortex<sup>®</sup> User Guide.

The PMC provides Normal Run (RUN), and Very Low Power Run (VLPR) configurations in ARM's Run operation mode. In these modes, the MCU core is active and can access all peripherals. The difference between the modes is the maximum clock frequency of the system and therefore the power consumption. The configuration that matches the power versus performance requirements of the application can be selected.

The PMC provides Wait (Wait) and Very Low Power Wait (VLPW) configurations in ARM's Sleep operation mode. In these modes, even though the MCU core is inactive, all of the peripherals can be enabled and operate as programmed. The difference between the modes is the maximum clock frequency of the system and therefore the power consumption.

The PMC provides Stop (Stop), Very Low Power Stop (VLPS) configurations in ARM's Deep Sleep operational mode. In these modes, the MCU core and most of the peripherals are disabled. Depending on the requirements of the application, different portions of the analog, logic, and memory can be retained or disabled to conserve power.

The Nested Vectored Interrupt Controller (NVIC), the Asynchronous Wake-up Interrupt Controller (AWIC) are used to wake up the MCU from low power states. The NVIC is used to wake up the MCU core from WAIT and VLPW modes. The AWIC is used to wake up the MCU core from STOP and VLPS modes.

For additional information regarding operational modes, power management, the NVIC, AWIC, please refer to the Reference Manual.

The following table provides information about the state of the peripherals in the various operational modes and the modules that can wake MCU from low power modes.

| Core mode  | Device mode         | Descriptions                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |

|------------|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Run mode   | Run                 | In Run mode, all device modules are operational.                                                                                                                                                                                                                                                                                       |  |  |  |  |  |

|            | Very Low Power Run  | In VLPR mode, all device modules are operational at a reduced frequency except the Low Voltage Detect (LVD) monitor, which is disabled.                                                                                                                                                                                                |  |  |  |  |  |

| Sleep mode | Wait                | In Wait mode, all peripheral modules are operational. The MCU core is placed into Sleep mode.                                                                                                                                                                                                                                          |  |  |  |  |  |

|            | Very Low Power Wait | In VLPW mode, all peripheral modules are operational at a reduced frequency except the Low Voltage Detect (LVD) monitor, which is disabled. The MCU core is placed into Sleep mode.                                                                                                                                                    |  |  |  |  |  |

| Deep sleep | Stop                | In Stop mode, most peripheral clocks are disabled and placed in a static state. Stop mode retains all registers and SRAMs while maintaining Low Voltage Detection protection. In Stop mode, the ADC, CMP, LPTMR, RTC, and pin interrupts are operational. The NVIC is disabled, but the AWIC can be used to wake up from an interrupt. |  |  |  |  |  |

|            | Very Low Power Stop | In VLPS mode, the contents of the SRAM are retained. The CMP (low speed), ADC, OSC, RTC, LPTMR, LPIT, FlexIO, LPUART, LPI2C,LPSPI, and DMA are operational, LVD and NVIC are disabled, AWIC is used to wake up from interrupt.                                                                                                         |  |  |  |  |  |

#### Table 5. Peripherals states in different operational modes

#### NOTE

When the MCU is in HSRUN or VLP mode, user cannot write FlexRAM (EEPROM), and cannot launch an FTFE command including flash programming/erasing.

### 2.1.9 Debug controller

This device has extensive debug capabilities including run control and tracing capabilities. The standard ARM debug port supports SWD interface.

## 2.2 Peripheral features

The following sections describe the features of each peripherals of the chip.

## 2.2.1 eDMA and DMAMUX

The eDMA is a highly programmable data-transfer engine optimized to minimize any required intervention from the host processor. It is intended for use in applications where the data size to be transferred is statically known and not defined within the

#### Overview

transferred data itself. The DMA controller in this device implements 8 channels which can be routed from up to 63 DMA request sources through DMA MUX module.

Main features of eDMA are listed below:

- All data movement via dual-address transfers: read from source, write to destination

- 8-channel implementation that performs complex data transfers with minimal intervention from a host processor

- Transfer control descriptor (TCD) organized to support two-deep, nested transfer operations

- Channel activation via one of three methods

- Fixed-priority and round-robin channel arbitration

- Channel completion reported via programmable interrupt requests

- Programmable support for scatter/gather DMA processing

- Support for complex data structures

# 2.2.2 FTM

This device contains three FlexTimer modules.

The FlexTimer module (FTM) is a two-to-eight channel timer that supports input capture, output compare, and the generation of PWM signals to control electric motor and power management applications. The FTM time reference is a 16-bit counter that can be used as an unsigned or signed counter.

Several key enhancements of this module are made:

- Signed up counter

- Deadtime insertion hardware

- Fault control inputs

- Enhanced triggering functionality

- Initialization and polarity control

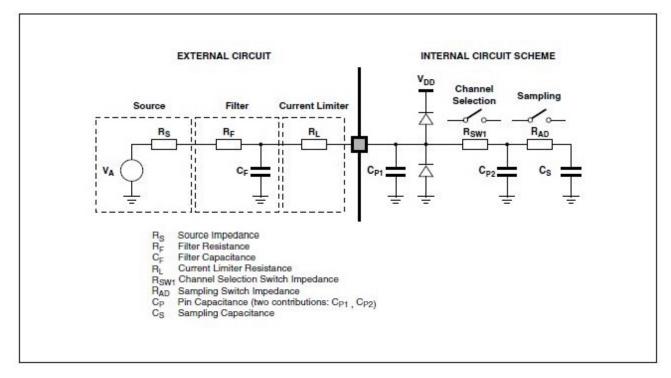

# 2.2.3 ADC

This device contains two 12-bit SAR ADC modules. The ADC module supports hardware triggers from FTM, LPTMR, PIT, RTC, external trigger pin and CMP output. It supports wakeup of MCU in low power mode when using internal clock source or external crystal clock.

ADC module has the following features:

- Linear successive approximation algorithm with up to 12-bit resolution

- Up to 16 single-ended external analog inputs

- Support 12-bit, 10-bit, and 8-bit single-ended output modes

- Single or continuous conversion

- Configurable sample time and conversion speed/power

- Input clock selectable from up to four sources

- Operation in low-power modes for lower noise

- Selectable hardware conversion trigger

- Automatic compare with interrupt for less-than, greater-than or equal-to, within range, or out-of-range, programmable value

- Temperature sensor

- Hardware average function

- Selectable Voltage reference: from external or alternate

- Self-Calibration mode

#### 2.2.3.1 Temperature sensor

This device contains one temperature sensor internally connected to the input channel of AD26, see ADC electrical characteristics for details of the linearity factor.

The sensor must be calibrated to gain good accuracy, so as to provide good linearity, see also AN3031 for more detailed application information of the temperature sensor.

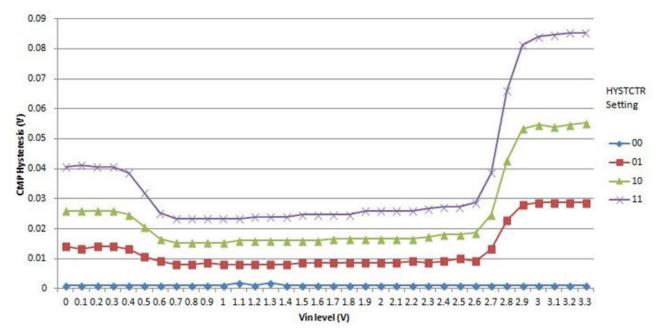

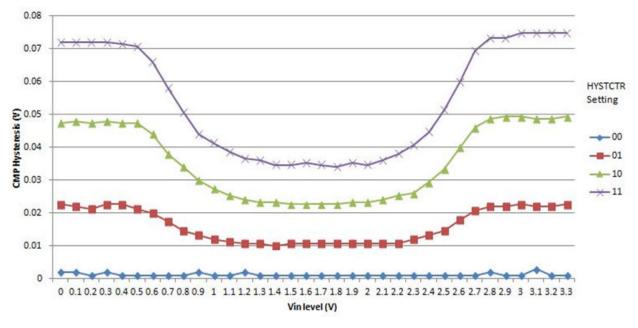

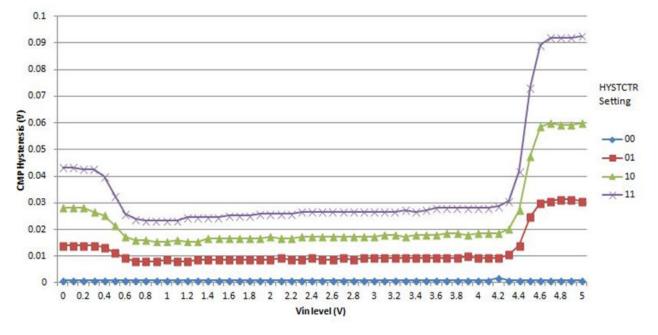

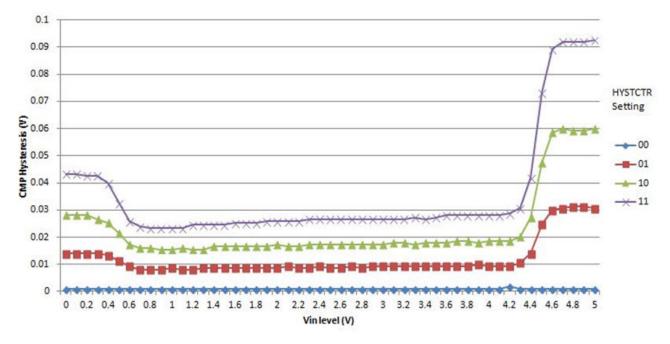

### 2.2.4 CMP

There are two analog comparators on this device.

- Each CMP has its own independent 8-bit DAC.

- Each CMP supports up to 6 analog inputs from external pins.

- Each CMP is able to convert an internal reference from the bandgap.

- Each CMP supports the round-robin sampling scheme. In summary, this allow the CMP to operate independently in VLPS and Stop modes, whilst being triggered periodically to sample up to 8 inputs. Only if an input changes state is a full wakeup generated.

The CMP has the following features:

- Inputs may range from rail to rail

- Programmable hysteresis control

- Selectable interrupt on rising-edge, falling-edge, or both rising and falling edges of the comparator output

- Selectable inversion on comparator output

- Capability to produce a wide range of outputs such as sampled, windowed, or digitally filtered

- External hysteresis can be used at the same time that the output filter is used for internal functions

- Two software selectable performance levels: Shorter propagation delay at the expense of higher power, and Low power with longer propagation delay

- DMA transfer support

- Functional in all power modes available on this MCU

- The window and filter functions are not available in STOP mode

- Integrated 8-bit DAC with selectable supply reference source and can be power down to conserve power

# 2.2.5 RTC

The RTC is an always powered-on block that remains active in all low power modes. The time counter within the RTC is clocked by a 32.768 kHz clock sourced from an external crystal using the oscillator, or clock directly from RTC\_CLKIN pin.

RTC is reset on power-on reset, and a software reset bit in RTC can also initialize all RTC registers.

The RTC module has the following features

- 32-bit seconds counter with roll-over protection and 32-bit alarm

- 16-bit prescaler with compensation that can correct errors between 0.12 ppm and 3906 ppm

- Register write protection with register lock mechanism

- 1 Hz square wave or second pulse output with optional interrupt

# 2.2.6 LPIT

The Low Power Periodic Interrupt Timer (LPIT) is a multi-channel timer module generating independent pre-trigger and trigger outputs. These timer channels can operate individually or can be chained together. The LPIT can operate in low power modes if configured to do so. The pre-trigger and trigger outputs can be used to trigger other modules on the device.

This device contains one LPIT module with four channels. The LPIT generates periodic trigger events to the DMAMUX.

# 2.2.7 PDB

The Programmable Delay Block (PDB) provides controllable delays from either an internal or an external trigger, or a programmable interval tick, to the hardware trigger inputs of ADCs and/or generates the interval triggers to DACs, so that the precise timing between ADC conversions and/or DAC updates can be achieved. The PDB can optionally provide pulse outputs (Pulse-Out's) that are used as the sample window in the CMP block.

The PDB module has the following capabilities:

- trigger input sources and one software trigger source

- 1 DAC refresh trigger output, for this device

- configurable PDB channels for ADC hardware trigger

- 1 pulse output, for this device

## 2.2.8 LPTMR

The low-power timer (LPTMR) can be configured to operate as a time counter with optional prescaler, or as a pulse counter with optional glitch filter, across all power modes, including the low-leakage modes. It can also continue operating through most system reset events, allowing it to be used as a time of day counter.

The LPTMR module has the following features:

- 16-bit time counter or pulse counter with compare

- Optional interrupt can generate asynchronous wakeup from any low-power mode

- Hardware trigger output

- Counter supports free-running mode or reset on compare

- Configurable clock source for prescaler/glitch filter

- Configurable input source for pulse counter

# 2.2.9 CRC

This device contains one cyclic redundancy check (CRC) module which can generate 16/32-bit CRC code for error detection.

The CRC module provides a programmable polynomial, WAS, and other parameters required to implement a 16-bit or 32-bit CRC standard.

#### Overview

The CRC module has the following features:

- Hardware CRC generator circuit using a 16-bit or 32-bit programmable shift register

- Programmable initial seed value and polynomial

- Option to transpose input data or output data (the CRC result) bitwise or bytewise.

- Option for inversion of final CRC result

- 32-bit CPU register programming interface

# 2.2.10 LPUART

This product contains three Low-Power UART modules, and can work in Stop and VLPS modes. The module also supports  $4 \times$  to  $32 \times$  data oversampling rate to meet different applications.

The LPUART module has the following features:

- Programmable baud rates (13-bit modulo divider) with configurable oversampling ratio from 4× to 32×

- Transmit and receive baud rate can operate asynchronous to the bus clock and can be configured independently of the bus clock frequency, support operation in Stop mode

- Interrupt, DMA or polled operation

- Hardware parity generation and checking

- Programmable 8-bit, 9-bit or 10-bit character length

- Programmable 1-bit or 2-bit stop bits

- Three receiver wakeup methods

- Idle line wakeup

- Address mark wakeup

- Receive data match

- Automatic address matching to reduce ISR overhead:

- Address mark matching

- Idle line address matching

- Address match start, address match end

- Optional 13-bit break character generation / 11-bit break character detection

- Configurable idle length detection supporting 1, 2, 4, 8, 16, 32, 64 or 128 idle characters

- Selectable transmitter output and receiver input polarity

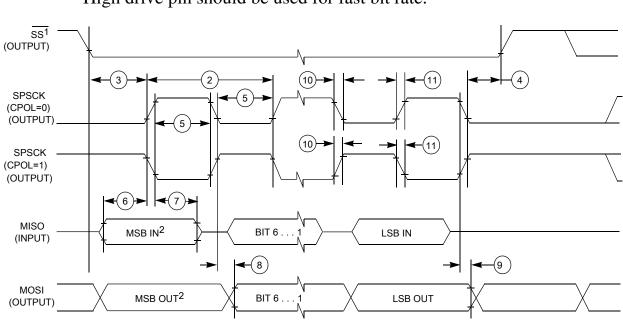

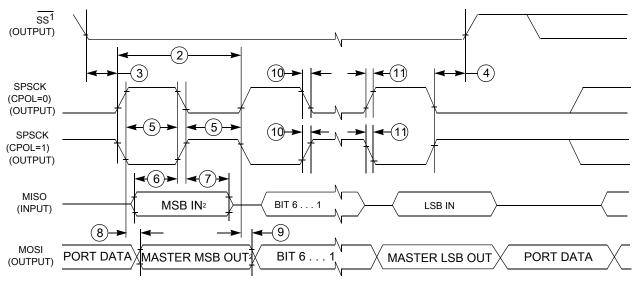

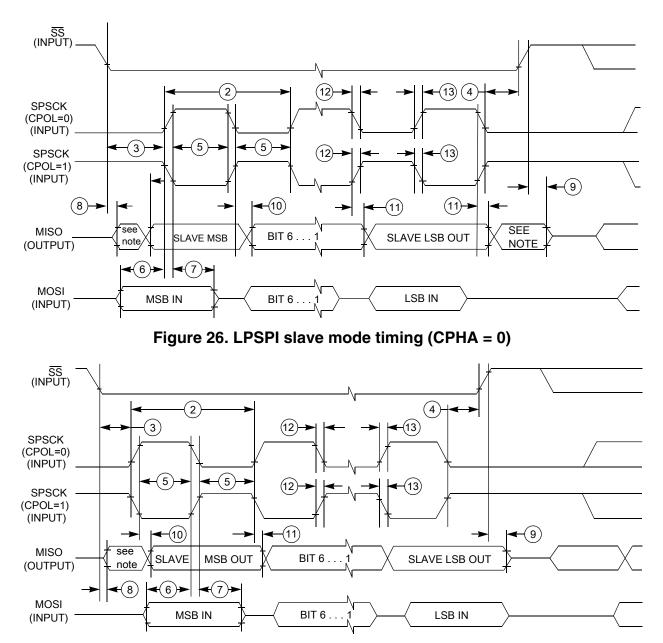

# 2.2.11 LPSPI

This device contains two LPSPI modules. The LPSPI is a low power Serial Peripheral Interface (SPI) module that supports an efficient interface to an SPI bus as a master and/or a slave. The LPSPI can continue operating in stop modes provided an appropriate clock is available and is designed for low CPU overhead with DMA offloading of FIFO register accesses.

The LPSPI module has the following features:

- Command/transmit FIFO of 4 words

- Receive FIFO of 4 words

- Host request input can be used to control the start time of an SPI bus transfer

## 2.2.12 LPI2C

This device contains two LPI2C modules. The LPI2C is a low power Inter-Integrated Circuit (I2C) module that supports an efficient interface to an I2C bus as a master and/or a slave. The LPI2C can continue operating in stop modes provided an appropriate clock is available and is designed for low CPU overhead with DMA offloading of FIFO register accesses. The LPI2C implements logic support for standard-mode, fast-mode, fast-mode plus and ultra-fast modes of operation. The LPI2C module also complies with the *System Management Bus (SMBus) Specification, version 2.*

The LPI2C modules have the following features:

- Standard, Fast, Fast+ and Ultra Fast modes are supported

- HS-mode supported in slave mode

- Multi-master support including synchronization and arbitration

- Clock stretching

- General call, 7-bit and 10-bit addressing

- Software reset, START byte and Device ID require software support

- For master mode:

- command/transmit FIFO of 4 words

- receive FIFO of 4 words

- For slave mode:

- separate I2C slave registers to minimize software overhead due to master/ slave switching

- support for 7-bit or 10-bit addressing, address range, SMBus alert and general call address

- transmit/receive data register supporting interrupt or DMA requests

# 2.2.13 FlexIO

The FlexIO is a highly configurable module providing a wide range of protocols including, but not limited to UART, I2C, SPI, Camera IF, LCD RGB, PWM/Waveform generation. The module supports programmable baud rates independent of bus clock frequency, with automatic start/stop bit generation.

The FlexIO module has the following features:

- Functional in VLPR/VLPW/Stop/VLPS mode provided the clock it is using remains enabled

- Four 32-bit double buffered shift registers with transmit, receive, and data match modes, and continuous data transfer

- The timing of the shifter's shift, load and store events are controlled by the highly flexible 16-bit timer assigned to the shifter

- Two or more shifters can be concatenated to support large data transfer sizes

- Each 16-bit timers operates independently, supports for reset, enable and disable on a variety of internal or external trigger conditions with programmable trigger polarity

- Flexible pin configuration supporting output disabled, open drain, bidirectional output data and output mode

- Supports interrupt, DMA or polled transmit/receive operation

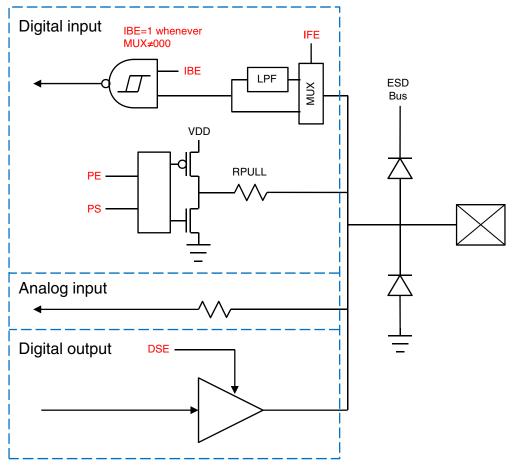

# 2.2.14 Port control and GPIO

The Port Control and Interrupt (PORT) module provides support for port control, digital filtering, and external interrupt functions. The GPIO data direction and output data registers control the direction and output data of each pin when the pin is configured for the GPIO function. The GPIO input data register displays the logic value on each pin when the pin is configured for any digital function, provided the corresponding Port Control and Interrupt module for that pin is enabled.

The following figure shows the basic I/O pad structure. Pseudo open-drain pins have the p-channel output driver disabled when configured for open-drain operation. None of the I/O pins, including open-drain and pseudo open-drain pins, are allowed to go above VDD.

#### NOTE

The RESET\_b pin is also a normal I/O pad with pseudo opendrain.

Figure 5. I/O simplified block diagram

The PORT module has the following features:

- all PIN support interrupt enable

- Configurable edge (rising, falling, or both) or level sensitive interrupt type

- Support DMA request

- Asynchronous wake-up in low-power modes

- Configurable pullup, pulldown, and pull-disable on select pins

- Configurable high and low drive strength on selected pins

- Configurable passive filter on selected pins

- Individual mux control field supporting analog or pin disabled, GPIO, and up to chip-specific digital functions

- Pad configuration fields are functional in all digital pin muxing modes.

The GPIO module has the following features:

- Port Data Input register visible in all digital pin-multiplexing modes

- Port Data Output register with corresponding set/clear/toggle registers

- Port Data Direction register

- GPIO support single-cycle access via fast GPIO.

# 3 Memory map

This device contains various memories and memory-mapped peripherals which are located in a 4 GB memory space. For more details of the system memory and peripheral locations, see the Memory Map chapter in the Reference Manual.

#### Memory map

|             |                                      | 0x0000_0000                        |                   |              |

|-------------|--------------------------------------|------------------------------------|-------------------|--------------|

|             |                                      |                                    | Flash *           |              |

|             |                                      | 0x0003_FFFF                        | Reserved          |              |

| 0x0000_0000 | Code space                           | 0x07FF_FFFF                        | neserveu          |              |

| 0x0800_0000 | Code space                           |                                    |                   |              |

| 0x1000_0000 | Reserved                             |                                    |                   |              |

| 0x1000_0000 | FlexNVM                              |                                    |                   |              |

| 0x1400_0000 | Reserved                             |                                    |                   |              |

| 0x1400_0000 | FlexRAM                              |                                    |                   |              |

| 0x1800_0000 | Reserved<br>Reserved                 | 0x1C00_0000                        |                   | ,<br>        |

| 0x1C00_0000 | 1636/760                             |                                    |                   |              |

|             | Boot ROM                             |                                    | ROM               |              |

|             | DOOLITION                            | 0x1C00_3FFF                        |                   |              |

| 0x1C00_4000 | Reserved                             | 0x1000_0111                        |                   |              |

| 0x1FF0_0000 |                                      | 0x1FF0_0000                        |                   |              |

|             | Data Space                           |                                    | SRAM_L            |              |

| 0x2010_0000 | Reserved                             | 0x2000_0000                        | SRAM_U            |              |

| 0x2200_0000 | Aliased to SRAM_U<br>bit-band region | 0x200F_FFFF                        |                   |              |

| 0x2400_0000 | Reserved                             |                                    |                   |              |

| 0x4000_0000 |                                      |                                    |                   |              |

|             | Public                               | 0x4000_0000                        |                   | /            |

|             | peripheral                           |                                    | AIPS              |              |

| 0x4010_0000 | Reserved                             |                                    | peripherals       |              |

| 0x4400_0000 |                                      | 0x4008_0000                        |                   |              |

|             | BME                                  |                                    | Reserved          | $\mathbf{X}$ |

| 0x6000_0000 |                                      | 0x400F_ <b>F000</b><br>0x400F_FFFF | GPIO              |              |

|             | Reserved                             | 0xE000_0000                        | Reserved          |              |

| 0xE000_0000 |                                      | 0xE000_E000                        |                   |              |

|             |                                      |                                    | System<br>control |              |

|             | Private                              |                                    | space             |              |

|             | peripheral                           | 0xE000_F000                        | Reserved          |              |

|             |                                      | 0xE00F_F000                        | Heserved          |              |

| 0xE010_0000 |                                      |                                    | Core<br>ROM table |              |

|             | Reserved                             | 0xE00F_FFFF                        |                   |              |

|             |                                      | 0xF000_0000                        | MTB               |              |

| 0xF000 0000 |                                      | 0xF000_1000                        | MTBDWT            |              |

| 000_0000    |                                      | 0xF000_2000                        |                   |              |

|             |                                      | 000_2000                           | ROM Table         |              |

|             | Private<br>peripheral                | 0xF000_3000                        | МСМ               |              |

|             | bus                                  |                                    |                   |              |

|             |                                      | 0xF000_4000                        | MMDVSQ            |              |

|             |                                      | 0xF000_5000                        |                   |              |

| 0xFFFF_FFFF |                                      |                                    | Reserved          |              |

|             |                                      | 0xF800_0000                        | IOPORT            |              |

|             |                                      | 0xFFFF_FFFF                        | 101 0111          | l            |

|             |                                      |                                    |                   |              |

Note:

The size of Flash and SRAM varies for devices with different part numbers.

See "Ordering information" in DataSheet for details.

| 0,4000,0000                |                                       |

|----------------------------|---------------------------------------|

| 0x4000_0000                | AIPS-Lite                             |

| 0x4000_1000                | Reserved                              |

| 0x4000_2000                | Reserved                              |

| 0x4000_8000<br>0x4000_9000 | eDMA                                  |

| 0x4000_9000<br>0x4000 A000 | DMA TCD                               |

| 7                          | Reserved                              |

| 0x4000_F000<br>0x4001_0000 | GPIO controller(aliased to 400F_F000) |

| 0x4001_0000<br>0x4002_0000 | Reserved                              |

|                            | Flash memory unit                     |

| 0x4002_1000<br>0x4002_2000 | DMAMUX0                               |

| 0x4002_2000                | Reserved                              |

| 0x4002_7000<br>0x4002_8000 | ADC1                                  |

| 0x4002_0000                | Reserved                              |

| 0x4002_0000<br>0x4002 D000 | LPSPIO                                |

| 0x4002_E000                | LPSPI1                                |

| 0x4003_2000                | Reserved<br>CRC                       |

| 0x4003_3000                |                                       |

| 0x4003_6000                | Reserved                              |

| 0x4003 7000                | PDB0<br>LPIT0                         |

| 0x4003_7000                | FTM0                                  |

| 0x4003_9000                | FTM0                                  |

| 0x4003_A000                | FTM1                                  |

| 0x4003_B000                | ADC0                                  |

| 0x4003_C000                | Reserved                              |

| 0x4003_D000                |                                       |

| 0x4003_E000                | RTC<br>Reserved                       |

| 0x4004_0000                | LPTMR0                                |

| 0x4004_1000                | Reserved                              |

| 0x4004_5000                | TSIO                                  |

| 0x4004_6000                | Reserved                              |

| 0x4004_8000                | SIM                                   |

| 0x4004_9000                | PORT A                                |

| 0x4004_A000                | PORT B                                |

| 0x4004_B000                | PORT C                                |

| 0x4004_C000                | PORT D                                |

| 0x4004_D000                | PORT E                                |

| 0x4004_E000                | Reserved                              |

| 0x4005_2000                | WDOG                                  |

| 0x4005_3000                | Reserved                              |

| 0x4005_6000                | PWT                                   |

| 0x4005_7000                | Reserved                              |

| 0x4005_A000                | FlexIO0                               |

| 0x4005_B000                | Reserved                              |

| 0x4006_0000                | OSC32                                 |

| 0x4006_1000                | EWM                                   |

| 0x4006_2000                | TRGMUX0                               |

| 0x4006_3000                | TRGMUX1                               |

| 0x4006_4000<br>0x4006_5000 | SCG                                   |

| 0x4006_5000<br>0x4006_6000 | PCC                                   |

| 0x4006_0000                | LPI2C0                                |

|                            | LPI2C1                                |

| 0x4006_8000                | Reserved                              |

| 0x4006_A000                | LPUART0                               |

| 0x4006_B000                | LPUART1                               |

| 0x4006_C000                | LPUART2                               |

| 0x4006_D000                | Reserved                              |

| 0x4007_3000                | CMP0                                  |

| 0x4007_4000                | CMP1                                  |

| 0x4007_5000                | Reserved                              |

| 0x4007_D000                | PMC                                   |

| 0x4007_E000                | SMC                                   |

| 0x4007_F000                | RCM                                   |

| 0x4007_FFFF                | TOW .                                 |

|                            |                                       |

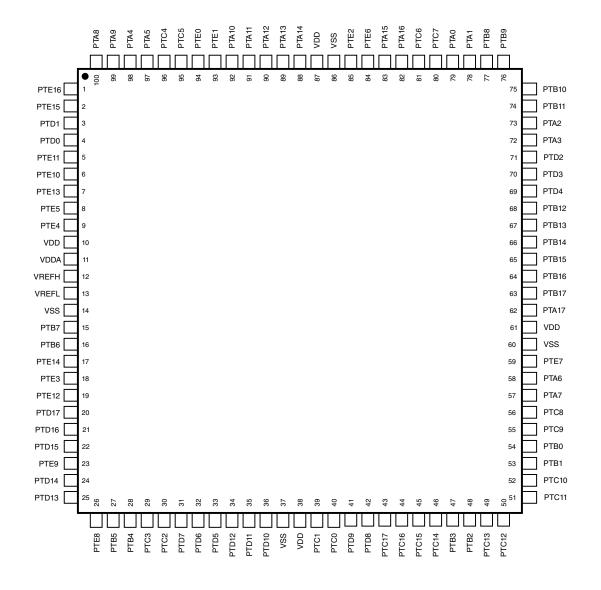

# 4.1 KE1xZ Signal Multiplexing and Pin Assignments

The following table shows the signals available on each pin and the locations of these pins on the devices supported by this document. The Port Control Module is responsible for selecting which ALT functionality is available on each pin.

#### NOTE

On this device, there are several special ADC channels which support hardware interleave between multiple ADCs. Taking ADC0\_SE4 and ADC1\_SE14 channels as an example, these two channels can work independently, but they can also be hardware interleaved. In the hardware interleaved mode, a signal on the pin PTB0 can be sampled by both ADC0 and ADC1. The interleaved mode is enabled by SIM\_CHIPCTL[ADC\_INTERLEAVE\_EN] bits. For more information, see "ADC Hardware Interleaved Channels" in the ADC chapter of Reference Manual.

| 100<br>LQFP | 64<br>LQFP | Pin Name      | Default       | ALT0          | ALT1  | ALT2     | ALT3            | ALT4     | ALT5 | ALT6    | ALT7            |

|-------------|------------|---------------|---------------|---------------|-------|----------|-----------------|----------|------|---------|-----------------|

| -           | 10         | VREFL/<br>VSS | VREFL/<br>VSS | VREFL/<br>VSS |       |          |                 |          |      |         |                 |

| 1           | _          | PTE16         | DISABLED      |               | PTE16 |          |                 |          |      | FXIO_D3 | TRGMUX_<br>OUT7 |

| 2           | -          | PTE15         | DISABLED      |               | PTE15 |          |                 |          |      | FXIO_D2 | TRGMUX_<br>OUT6 |

| 3           | 1          | PTD1          | TSI0_CH5      | TSI0_CH5      | PTD1  | FTM0_CH3 | LPSPI1_SIN      | FTM2_CH1 |      | FXIO_D1 | TRGMUX_<br>OUT2 |

| 4           | 2          | PTD0          | TSI0_CH4      | TSI0_CH4      | PTD0  | FTM0_CH2 | LPSPI1_SCK      | FTM2_CH0 |      | FXIO_D0 | TRGMUX_<br>OUT1 |

| 5           | 3          | PTE11         | TSI0_CH3      | TSI0_CH3      | PTE11 | PWT_IN1  | LPTMR0_<br>ALT1 |          |      | FXIO_D5 | TRGMUX_<br>OUT5 |

| 6           | 4          | PTE10         | TSI0_CH2      | TSI0_CH2      | PTE10 | CLKOUT   |                 |          |      | FXIO_D4 | TRGMUX_<br>OUT4 |

| 7           | —          | PTE13         | DISABLED      |               | PTE13 |          |                 |          |      |         |                 |

| 8           | 5          | PTE5          | TSI0_CH0      | TSI0_CH0      | PTE5  | TCLK2    | FTM2_QD_<br>PHA | FTM2_CH3 |      | FXIO_D7 | EWM_IN          |

| 9           | 6          | PTE4          | TSI0_CH1      | TSI0_CH1      | PTE4  | BUSOUT   | FTM2_QD_<br>PHB | FTM2_CH2 |      | FXIO_D6 | EWM_OUT_b       |

| 100<br>LQFP | 64<br>LQFP | Pin Name | Default                              | ALTO                                 | ALT1  | ALT2       | ALT3            | ALT4      | ALT5    | ALT6            | ALT7       |

|-------------|------------|----------|--------------------------------------|--------------------------------------|-------|------------|-----------------|-----------|---------|-----------------|------------|

| 10          | 7          | VDD      | VDD                                  | VDD                                  |       |            |                 |           |         |                 |            |

| 11          | 8          | VDDA     | VDDA                                 | VDDA                                 |       |            |                 |           |         |                 |            |

| 12          | 9          | VREFH    | VREFH                                | VREFH                                |       |            |                 |           |         |                 |            |

| 13          | -          | VREFL    | VREFL                                | VREFL                                |       |            |                 |           |         |                 |            |

| 14          | _          | VSS      | VSS                                  | VSS                                  |       |            |                 |           |         |                 |            |

| 15          | 11         | PTB7     | EXTAL                                | EXTAL                                | PTB7  | LPI2C0_SCL |                 |           |         |                 |            |

| 16          | 12         | PTB6     | XTAL                                 | XTAL                                 | PTB6  | LPI2C0_SDA |                 |           |         |                 |            |

| 17          | _          | PTE14    | DISABLED                             |                                      | PTE14 | FTM0_FLT1  |                 |           |         |                 |            |

| 18          | 13         | PTE3     | TSI0_CH24                            | TSI0_CH24                            | PTE3  | FTM0_FLT0  | LPUART2_<br>RTS |           |         | TRGMUX_IN6      |            |

| 19          | _          | PTE12    | DISABLED                             |                                      | PTE12 | FTM0_FLT3  | LPUART2_TX      |           |         |                 |            |

| 20          | _          | PTD17    | DISABLED                             |                                      | PTD17 | FTM0_FLT2  | LPUART2_RX      |           |         |                 |            |

| 21          | 14         | PTD16    | DISABLED                             |                                      | PTD16 | FTM0_CH1   |                 |           |         |                 |            |

| 22          | 15         | PTD15    | DISABLED                             |                                      | PTD15 | FTM0_CH0   |                 |           |         |                 |            |

| 23          | 16         | PTE9     | DAC0_OUT                             | DAC0_OUT                             | PTE9  | FTM0_CH7   | LPUART2_<br>CTS |           |         |                 |            |

| 24          | -          | PTD14    | DISABLED                             |                                      | PTD14 |            |                 |           |         |                 | CLKOUT     |

| 25          | _          | PTD13    | DISABLED                             |                                      | PTD13 |            |                 |           |         |                 | RTC_CLKOUT |

| 26          | 17         | PTE8     | ACMP0_IN3/<br>TSI0_CH11              | ACMP0_IN3/<br>TSI0_CH11              | PTE8  | FTM0_CH6   |                 |           |         |                 |            |

| 27          | 18         | PTB5     | TSI0_CH9                             | TSI0_CH9                             | PTB5  | FTM0_CH5   | LPSPI0_PCS1     |           |         | TRGMUX_IN0      | ACMP1_OUT  |

| 28          | 19         | PTB4     | ACMP1_IN2/<br>TSI0_CH8               | ACMP1_IN2/<br>TSI0_CH8               | PTB4  | FTM0_CH4   | LPSPI0_SOUT     |           |         | TRGMUX_IN1      |            |

| 29          | 20         | PTC3     | ADC0_SE11/<br>ACMP0_IN4/<br>EXTAL32  | ADC0_SE11/<br>ACMP0_IN4/<br>EXTAL32  | PTC3  | FTM0_CH3   |                 |           |         |                 |            |

| 30          | 21         | PTC2     | ADC0_SE10/<br>ACMP0_IN5/<br>XTAL32   | ADC0_SE10/<br>ACMP0_IN5/<br>XTAL32   | PTC2  | FTM0_CH2   |                 |           |         |                 |            |

| 31          | 22         | PTD7     | TSI0_CH10                            | TSI0_CH10                            | PTD7  | LPUART2_TX |                 | FTM2_FLT3 |         |                 |            |

| 32          | 23         | PTD6     | TSI0_CH7                             | TSI0_CH7                             | PTD6  | LPUART2_RX |                 | FTM2_FLT2 |         |                 |            |

| 33          | 24         | PTD5     | TSI0_CH6                             | TSI0_CH6                             | PTD5  | FTM2_CH3   | LPTMR0_<br>ALT2 |           | PWT_IN2 | TRGMUX_IN7      |            |

| 34          | -          | PTD12    | DISABLED                             |                                      | PTD12 | FTM2_CH2   | LPI2C1_HREQ     |           |         | LPUART2_<br>RTS |            |

| 35          | —          | PTD11    | DISABLED                             |                                      | PTD11 | FTM2_CH1   | FTM2_QD_<br>PHA |           |         | LPUART2_<br>CTS |            |

| 36          | 1          | PTD10    | DISABLED                             |                                      | PTD10 | FTM2_CH0   | FTM2_QD_<br>PHB |           |         |                 |            |

| 37          | —          | VSS      | VSS                                  | VSS                                  |       |            |                 |           |         |                 |            |

| 38          | -          | VDD      | VDD                                  | VDD                                  |       |            |                 |           |         |                 |            |

| 39          | 25         | PTC1     | ADC0_SE9/<br>ACMP1_IN3/<br>TSI0_CH23 | ADC0_SE9/<br>ACMP1_IN3/<br>TSI0_CH23 | PTC1  | FTM0_CH1   |                 |           |         |                 |            |

| 100<br>LQFP | 64<br>LQFP | Pin Name | Default                              | ALT0                                 | ALT1  | ALT2       | ALT3        | ALT4            | ALT5    | ALT6            | ALT7  |

|-------------|------------|----------|--------------------------------------|--------------------------------------|-------|------------|-------------|-----------------|---------|-----------------|-------|

| 40          | 26         | PTC0     | ADC0_SE8/<br>ACMP1_IN4/<br>TSI0_CH22 | ADC0_SE8/<br>ACMP1_IN4/<br>TSI0_CH22 | PTC0  | FTM0_CH0   |             |                 |         |                 |       |

| 41          | -          | PTD9     | ACMP1_IN5                            | ACMP1_IN5                            | PTD9  | LPI2C1_SCL |             | FTM2_FLT3       |         |                 |       |

| 42          | -          | PTD8     | DISABLED                             |                                      | PTD8  | LPI2C1_SDA |             | FTM2_FLT2       |         |                 |       |

| 43          | 27         | PTC17    | ADC0_SE15                            | ADC0_SE15                            | PTC17 | FTM1_FLT3  |             | LPI2C1_SCLS     |         |                 |       |

| 44          | 28         | PTC16    | ADC0_SE14                            | ADC0_SE14                            | PTC16 | FTM1_FLT2  |             | LPI2C1_SDAS     |         |                 |       |

| 45          | 29         | PTC15    | ADC0_SE13                            | ADC0_SE13                            | PTC15 | FTM1_CH3   |             |                 |         |                 |       |

| 46          | 30         | PTC14    | ADC0_SE12                            | ADC0_SE12                            | PTC14 | FTM1_CH2   |             |                 |         |                 |       |

| 47          | 31         | PTB3     | ADC0_SE7/<br>TSI0_CH21               | ADC0_SE7/<br>TSI0_CH21               | PTB3  | FTM1_CH1   | LPSPI0_SIN  | FTM1_QD_<br>PHA |         | TRGMUX_IN2      |       |

| 48          | 32         | PTB2     | ADC0_SE6/<br>TSI0_CH20               | ADC0_SE6/<br>TSI0_CH20               | PTB2  | FTM1_CH0   | LPSPI0_SCK  | FTM1_QD_<br>PHB |         | TRGMUX_IN3      |       |

| 49          | -          | PTC13    | DISABLED                             |                                      | PTC13 |            |             |                 |         |                 |       |

| 50          | -          | PTC12    | DISABLED                             |                                      | PTC12 |            |             |                 |         |                 |       |

| 51          | _          | PTC11    | DISABLED                             |                                      | PTC11 |            |             |                 |         |                 |       |

| 52          | _          | PTC10    | DISABLED                             |                                      | PTC10 |            |             |                 |         |                 |       |

| 53          | 33         | PTB1     | ADC0_SE5                             | ADC0_SE5                             | PTB1  | LPUART0_TX | LPSPI0_SOUT | TCLK0           |         |                 |       |

| 54          | 34         | PTB0     | ADC0_SE4                             | ADC0_SE4                             | PTB0  | LPUART0_RX | LPSPI0_PCS0 | LPTMR0_<br>ALT3 | PWT_IN3 |                 |       |

| 55          | 35         | PTC9     | DISABLED                             |                                      | PTC9  | LPUART1_TX |             |                 |         | LPUART0_<br>RTS |       |

| 56          | 36         | PTC8     | DISABLED                             |                                      | PTC8  | LPUART1_RX |             |                 |         | LPUART0_<br>CTS |       |

| 57          | 37         | PTA7     | ADC0_SE3/<br>ACMP1_IN1               | ADC0_SE3/<br>ACMP1_IN1               | PTA7  | FTM0_FLT2  |             | RTC_CLKIN       |         | LPUART1_<br>RTS |       |

| 58          | 38         | PTA6     | ADC0_SE2/<br>ACMP1_IN0               | ADC0_SE2/<br>ACMP1_IN0               | PTA6  | FTM0_FLT1  | LPSPI1_PCS1 |                 |         | LPUART1_<br>CTS |       |

| 59          | 39         | PTE7     | DISABLED                             |                                      | PTE7  | FTM0_CH7   |             |                 |         |                 |       |

| 60          | 40         | VSS      | VSS                                  | VSS                                  |       |            |             |                 |         |                 |       |

| 61          | 41         | VDD      | VDD                                  | VDD                                  |       |            |             |                 |         |                 |       |

| 62          | -          | PTA17    | DISABLED                             |                                      | PTA17 | FTM0_CH6   |             | EWM_OUT_b       |         |                 |       |

| 63          | -          | PTB17    | DISABLED                             |                                      | PTB17 | FTM0_CH5   | LPSPI1_PCS3 |                 |         |                 |       |

| 64          | -          | PTB16    | DISABLED                             |                                      | PTB16 | FTM0_CH4   | LPSPI1_SOUT |                 |         |                 |       |

| 65          | -          | PTB15    | DISABLED                             |                                      | PTB15 | FTM0_CH3   | LPSPI1_SIN  |                 |         |                 |       |

| 66          | _          | PTB14    | ADC1_SE9                             | ADC1_SE9                             | PTB14 | FTM0_CH2   | LPSPI1_SCK  |                 |         |                 |       |

| 67          | 42         | PTB13    | ADC1_SE8                             | ADC1_SE8                             | PTB13 | FTM0_CH1   |             |                 |         |                 |       |

| 68          | 43         | PTB12    | ADC1_SE7                             | ADC1_SE7                             | PTB12 | FTM0_CH0   |             |                 |         |                 |       |

| 69          | 44         | PTD4     | ADC1_SE6                             | ADC1_SE6                             | PTD4  | FTM0_FLT3  |             |                 |         |                 |       |

| 70          | 45         | PTD3     | NMI_b                                | ADC1_SE3                             | PTD3  |            | LPSPI1_PCS0 | FXIO_D5         |         | TRGMUX_IN4      | NMI_b |

| 71          | 46         | PTD2     | ADC1_SE2                             | ADC1_SE2                             | PTD2  |            | LPSPI1_SOUT | FXIO_D4         |         | TRGMUX_IN5      |       |

| 72          | 47         | PTA3     | ADC1_SE1                             | ADC1_SE1                             | PTA3  |            | LPI2C0_SCL  | EWM_IN          |         | LPUART0_TX      |       |

| 100<br>LQFP | 64<br>LQFP | Pin Name | Default                              | ALT0                                 | ALT1  | ALT2        | ALT3            | ALT4        | ALT5            | ALT6            | ALT7            |

|-------------|------------|----------|--------------------------------------|--------------------------------------|-------|-------------|-----------------|-------------|-----------------|-----------------|-----------------|

| 73          | 48         | PTA2     | ADC1_SE0                             | ADC1_SE0                             | PTA2  |             | LPI2C0_SDA      | EWM_OUT_b   |                 | LPUART0_RX      |                 |

| 74          | _          | PTB11    | DISABLED                             |                                      | PTB11 |             | LPI2C0_HREQ     |             |                 |                 |                 |

| 75          | -          | PTB10    | DISABLED                             |                                      | PTB10 |             | LPI2C0_SDAS     |             |                 |                 |                 |

| 76          | _          | PTB9     | DISABLED                             |                                      | PTB9  |             | LPI2C0_SCLS     |             |                 |                 |                 |

| 77          | _          | PTB8     | DISABLED                             |                                      | PTB8  |             |                 |             |                 |                 |                 |

| 78          | 49         | PTA1     | ADC0_SE1/<br>ACMP0_IN1/<br>TSI0_CH18 | ADC0_SE1/<br>ACMP0_IN1/<br>TSI0_CH18 | PTA1  | FTM1_CH1    | LPI2C0_SDAS     | FXIO_D3     | FTM1_QD_<br>PHA | LPUART0_<br>RTS | TRGMUX_<br>OUT0 |

| 79          | 50         | PTA0     | ADC0_SE0/<br>ACMP0_IN0/<br>TSI0_CH17 | ADC0_SE0/<br>ACMP0_IN0/<br>TSI0_CH17 | PTA0  | FTM2_CH1    | LPI2C0_SCLS     | FXIO_D2     | FTM2_QD_<br>PHA | LPUARTO_<br>CTS | TRGMUX_<br>OUT3 |

| 80          | 51         | PTC7     | ADC1_SE5/<br>TSI0_CH16               | ADC1_SE5/<br>TSI0_CH16               | PTC7  | LPUART1_TX  |                 |             |                 |                 |                 |

| 81          | 52         | PTC6     | ADC1_SE4/<br>TSI0_CH15               | ADC1_SE4/<br>TSI0_CH15               | PTC6  | LPUART1_RX  |                 |             |                 |                 |                 |

| 82          | -          | PTA16    | DISABLED                             |                                      | PTA16 | FTM1_CH3    | LPSPI1_PCS2     |             |                 |                 |                 |

| 83          | _          | PTA15    | DISABLED                             |                                      | PTA15 | FTM1_CH2    | LPSPI0_PCS3     |             |                 |                 |                 |

| 84          | 53         | PTE6     | ADC1_SE11                            | ADC1_SE11                            | PTE6  | LPSPI0_PCS2 |                 |             |                 | LPUART1_<br>RTS |                 |

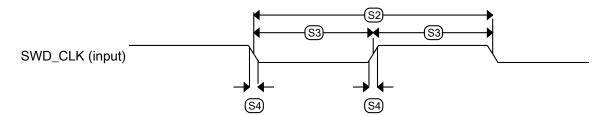

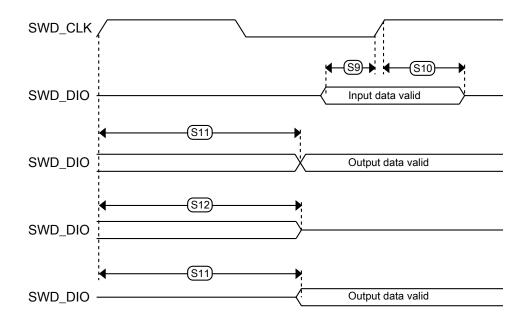

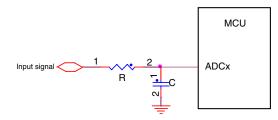

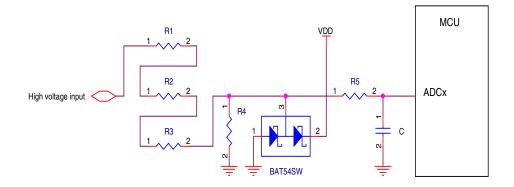

| 85          | 54         | PTE2     | ADC1_SE10/<br>TSI0_CH19              | ADC1_SE10/<br>TSI0_CH19              | PTE2  | LPSPI0_SOUT | LPTMR0_<br>ALT3 |             | PWT_IN3         | LPUART1_<br>CTS |                 |