**User manual**

#### Important Notice

NXP provides the enclosed product(s) under the following conditions:

This evaluation kit is intended for use of ENGINEERING DEVELOPMENT OR EVALUATION PURPOSES ONLY. It is provided as a sample IC pre-soldered to a printed circuit board to make it easier to access inputs, outputs, and supply terminals. This evaluation board may be used with any development system or other source of I/O signals by simply connecting it to the host MCU or computer board via off-the-shelf cables. This evaluation board is not a Reference Design and is not intended to represent a final design recommendation for any particular application. Final device in an application will be heavily dependent on proper printed circuit board layout and heat sinking design as well as attention to supply filtering, transient suppression, and I/O signal quality.

The goods provided may not be complete in terms of required design, marketing, and or manufacturing related protective considerations, including product safety measures typically found in the end product incorporating the goods. Due to the open construction of the product, it is the user's responsibility to take any and all appropriate precautions with regard to electrostatic discharge. In order to minimize risks associated with the customers applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards. For any safety concerns, contact NXP sales and technical support services.

Should this evaluation kit not meet the specifications indicated in the kit, it may be returned within 30 days from the date of delivery and will be replaced by a new kit.

NXP reserves the right to make changes without further notice to any products herein. NXP makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does NXP assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. Typical parameters can and do vary in different applications and actual performance may vary over time. All operating parameters, including Typical, must be validated for each customer application by customer's technical experts.

NXP does not convey any license under its patent rights nor the rights of others. NXP products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the NXP product could create a situation where personal injury or death may occur. Should the Buyer purchase or use NXP products for any such unintended or unauthorized application, the Buyer shall indemnify and hold by the failure of the failure of the super such unintended or unauthorized application, the Buyer shall indemnify and hold by the failure of the failure of the super such unintended or unauthorized application.

NXP and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges NXP was negligent regarding the design or manufacture of the part.

# 1 Introduction

This document is the user guide for the KITFS85AEEVM evaluation board. This document is intended for the engineers involved in the evaluation, design, implementation, and validation of FS8500 Fail-safe system basis chip with multiple SMPS and LDO.

The scope of this document is to provide the user with information to evaluate the FS8500 Fail-safe system basis chip with multiple SMPS and LDO. This document covers connecting the hardware, installing the software and tools, configuring the environment and using the kit.

The KITFS85AEEVM enables development on FS84/FS85 family of devices. The kit can be connected to the FlexGUI software which allows you to play with registers, try OTP configurations, and burn the part.

This kit is suitable for truck application running at 24 V nominal. It is able to sustain up to 60 V at  $V_{\text{BAT}}.$

It is delivered with empty OTP content in order to leave the opportunity to the user to burn the OTP configuration. Burning the OTP three times, gives a good flexibility. The board contains a superset device (MC33FS8530AE0S), allowing tests on all the FS84/ FS85 derivatives.

# 2 Finding kit resources and information on the NXP web site

NXP Semiconductors provides online resources for this evaluation board and its supported device(s) on <u>http://www.nxp.com</u>.

The information page for KITFS85AEEVM evaluation board is at <u>http://www.nxp.com/</u> <u>KITFS85AEEVM</u>. The information page provides overview information, documentation, software and tools, parametrics, ordering information and a **Getting Started** tab. The **Getting Started** tab provides quick-reference information applicable to using the KITFS85AEEVM evaluation board, including the downloadable assets referenced in this document.

## 2.1 Collaborate in the NXP community

The NXP community is for sharing ideas and tips, ask and answer technical questions, and receive input on just about any embedded design topic.

The NXP community is at http://community.nxp.com.

# 3 Getting ready

Working with the KITFS85AEEVM requires the kit contents, additional hardware and a Windows PC workstation with installed software.

#### 3.1 Kit contents

- Assembled and tested evaluation board in an anti-static bag

- 3.0 ft USB-STD A to USB-B-mini cable

- Two connectors, terminal block plug, 2 pos., str. 3.81 mm

- Three connectors, terminal block plug, 3 pos., str. 3.81 mm

• Jumpers mounted on board

### 3.2 Additional hardware

In addition to the kit contents, the following hardware is necessary or beneficial when working with this kit.

• Power supply with a range of 8.0 V to 60 V and a current limit set initially to 1.0 A

## 3.3 Windows PC workstation

This evaluation board requires a Windows PC workstation. Meeting these minimum specifications should produce great results when working with this evaluation board.

• USB-enabled computer with Windows 7 or Windows 10

#### 3.4 Software

Installing software is necessary to work with this evaluation board. All listed software is available on the evaluation board's information page at <u>http://www.nxp.com/</u><u>KITFS85AEEVM</u> or from the provided link.

- FlexGUI latest version

- FS85\_FS84\_OTP\_Config.xlsm

- Java installation <a href="https://www.oracle.com/technetwork/java/javase/downloads/jre8-downloads-2133155.html">https://www.oracle.com/technetwork/java/javase/downloads/jre8-downloads-2133155.html</a>

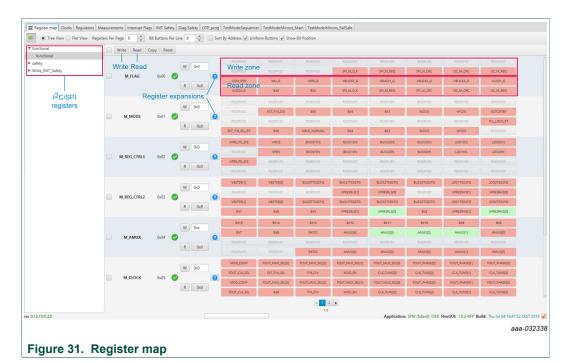

## 4 Getting to know the hardware

The KITFS85AEEVM provides flexibility to play with all the features of the device and make measurements on the main part of the application. The KL25Z MCU installed on the board, combined with the FlexGUI software allows access to the registers in read and write mode. All regulators are accessible through connectors. Nonuser signal, like DC/DC switcher node is mapped on test points. Digital signals (SPI, I2C, RSTB, etc.) are accessible through connectors. Pin WAKE1 has a switch to control (Ignition) them. A VBAT switch is available to power On or Off the device.

This board can be operated in Emulation mode or in OTP mode. In emulation mode, as long as the power is supplied, the board configuration stays valid. The OTP mode uses the fused configuration. The device can be fused three times. In OTP mode, the device always starts with the fused configuration, except if the user wants to overwrite OTP configuration using Emulation mode. This board is able to fuse the OTP without any extra tools or board.

## 4.1 Kit overview

The KITFS85AEEVM is a hardware evaluation tool that allows performance test. The FS85xx part soldered on the board can be fused three times (see <u>Section 7.3</u> "Programming the device with an OTP configuration").

An Emulation mode is possible to test as many configurations as needed. The voltage monitoring hardware configuration is done through resistors. Note this configuration can be changed by selecting the appropriate bridges resistors:

• VMON1: assigned to VPRE, 4.1 V

### KITFS85AEEVM evaluation board

- VMON2: assigned to EXT\_MON2, (VMON bridge for 3.3 V input)

- VMON3: assigned to BUCK3, 2.3 V

- VMON4: assigned to EXT\_MON4, (VMON bridge for 5.0 V input)

This configuration can be changed by installing appropriate bridge resistors. This board was designed to sustain up to 10 A total on VPRE. Layout is done using six layer PCB stack up.

The FS84/FS85 family can be evaluated with this board as it is populated with a superset part. The FS84xx supports ASIL B design, while FS85xx supports ASIL D design.

An external LDO provides VDDI2C voltage with a choice of 1.8 V or 3.3 V (default). VDDIO is assigned by default to VDDI2C. From USB voltage, an external DC/DC generates the OTP programming voltage (8.0 V) without any need for an external power supply.

#### 4.1.1 KITFS85AEEVM features

- VBAT power supply connectors (Jack and Phoenix)

- VPRE output capability up to 6.0 A (external MOSFET)

- VBUCK1/2 in Standalone (default) or Multiphase mode

- VBUCK3 up to 3.6 A peak

- VBOOST 5.0 V or 5.74 V, up to 400 mA

- LDO1 and LDO2, from 1.1 V to 5.0 V, up to 400 mA

- · Ignition key switch

- FS0B external safety pin

- Embedded USB connection for easy connection to software GUI (access to SPI/I2C bus, IOs, RSTB, FS0B, INTB, Debug, MUX\_OUT, regulators)

- · LEDs that indicate signal or regulator status

- · Support OTP fuse capabilities

- USB connection for register access, OTP emulation and programming

#### 4.1.2 VMON configuration

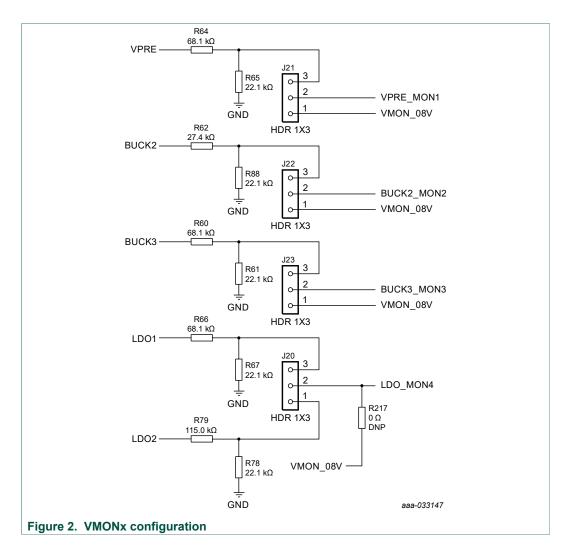

The VMONx configuration is highly dependent on the use case. This kit is delivered with a default configuration shown in <u>Figure 2</u>.

This configuration supports the following mapping:

- VPRE, assigned to VMON1; Bridge resistor set for 3.3 V

- BUCK2, assigned to VMON2; Bridge resistor set for 1.8 V

- BUCK3, assigned to VMON3; Bridge resistor set for 3.3 V

- LDO1, assigned to VMON4; Bridge resistor set for 3.3 V

- LDO2, assigned to VMON4; Bridge resistor set for 5.0 V

LDO1 and LDO2 use the same VMON, a reassignment is necessary to monitor both.

Due to the jumpers, VMONx can be tied to a 0.8 V to force a good voltage at pin level. This behaves like hardware disabling and makes debug easy in some cases.

UM11193

#### KITFS85AEEVM evaluation board

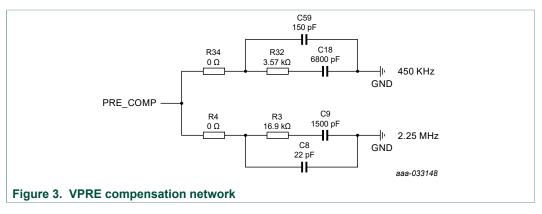

#### 4.1.3 VPRE compensation network

This board is delivered with a VPRE compensation network defined for VPRE 4.1 V at 450 kHz. All other VPRE configurations require a new calculation for these components.

#### KITFS85AEEVM evaluation board

| Table 1. Compensation network |                         |                                  |  |

|-------------------------------|-------------------------|----------------------------------|--|

| Components                    | VPRE 450 kHz            | VPRE 2.2 MHz                     |  |

| C18/C9                        | 6.8 nF                  | 1.5 nF                           |  |

| C59/C8                        | 150 pF                  | 22 pF                            |  |

| R32/R3                        | 3.57 kΩ                 | 16.9 kΩ                          |  |

| LPRE                          | 4.7 μH or <b>6.8 μH</b> | <b>1.5 μH</b> , 2.2 μH or 4.7 μH |  |

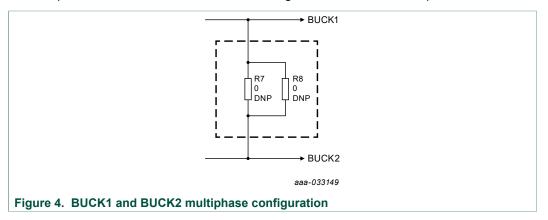

#### 4.1.4 BUCK1 and BUCK2 multiphase configuration

The board is designed to work independently with BUCK1 and BUCK2. Due to R7 and R8, it is possible to connect both connectors together and work in multiphase.

#### 4.1.5 SPI/I2C

The SPI and I2C buses are connected to KL25Z MCU. The user can use either one or the other. The choice can be done at start of the FlexGUI or at any time after launch (see <u>Section 8 "Using FlexGUI"</u>).

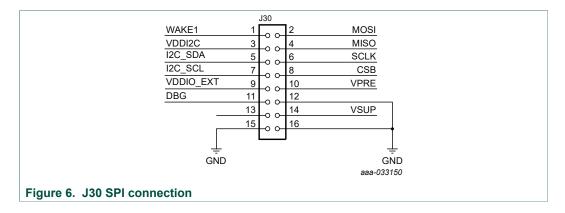

This kit uses a KL25Z MCU to communicate with FlexGUI. However, if the user wants to connect the SPI to another MCU, this is possible. In this case, remove J28 and appropriate jumpers to disconnect the KL25Z MCU (see Figure 5) and connect the external MCU on J30 connector as shown in Figure 6. In addition to this change, make sure that the VDDIO voltage domain is the same on MCU side and SBC side.

| [3] RSTb                          | J28<br>1 2                        | RSTb_SH    |  |  |

|-----------------------------------|-----------------------------------|------------|--|--|

| [3] FS0b -                        | 3 0 4                             | FS0b_SH    |  |  |

| [3] MISO →                        | 5 6                               | MISO_SH    |  |  |

| [3] MISU                          | 7 8                               | MOSI_SH    |  |  |

| [3] MOSI                          | 9 0 10                            | SCLK_SH    |  |  |

| [3] SCER -                        |                                   | CSB_SH     |  |  |

|                                   |                                   | aaa-032768 |  |  |

| Figure 5. SPI connection to KL25Z | Figure 5. SPI connection to KL25Z |            |  |  |

UM11193 User manual

## KITFS85AEEVM evaluation board

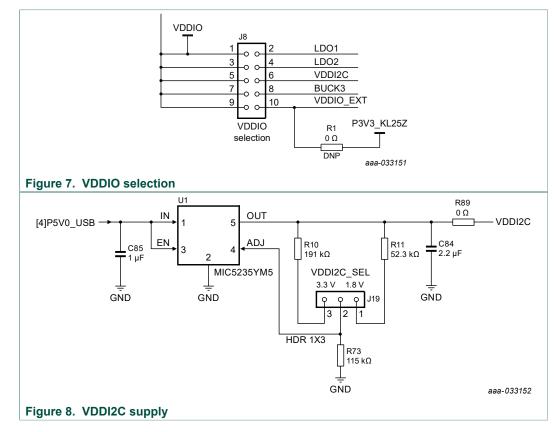

## 4.1.6 VDDI2C

As an option, an external LDO is provided to feed VDDI2C. This LDO can also be used to feed VDDIO, which is the default implementation.

The I2C is compatible with 1.8 V or 3.3 V, while VDDIO is compatible with 3.3 V and 5.0 V. For this reason, the LDO default configuration is 3.3 V. The LDO is supplied by 5.0 V coming from the USB.

## 4.2 Device OTP user configuration

It is recommended to learn about OTP before operating with the device. The device has a high level of flexibility due to parameter configuration available in the OTP. This

#### KITFS85AEEVM evaluation board

impacts the functionality of the device. It is key to understand how OTP parameters can be programmed, the interaction with mirror registers and the FS85 SoC.

The OTP related operations can be performed either in Emulation mode, where the product uses a given configuration as long as power supply is not switched Off or from OTP fuse content that is valid even after a power down/power up sequence.

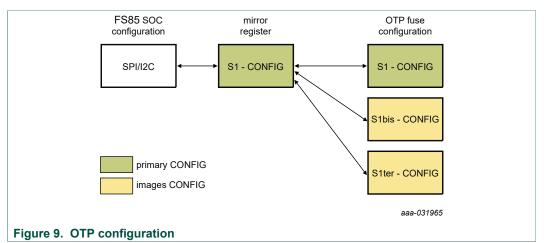

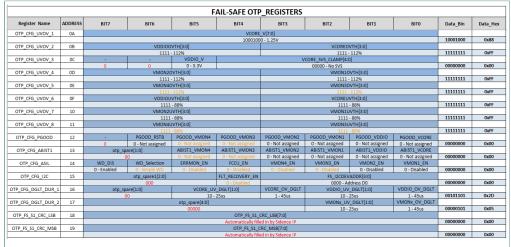

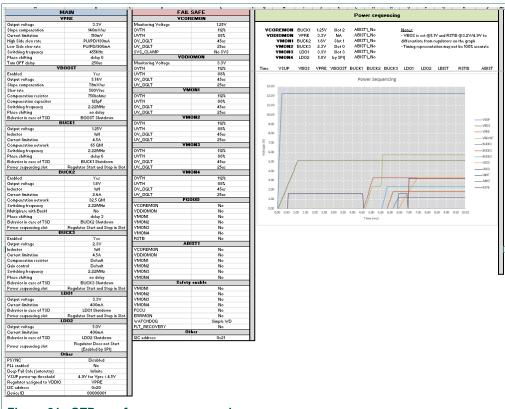

#### 4.2.1 OTP and mirrors registers

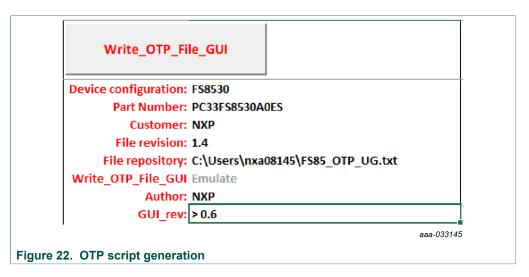

There are two OTP blocks in the device. One is for the main section, and the other for the fail-safe. During configuration, each of them are using dedicated sectors. The OTP configuration scheme is shown in Figure 9 (same implementation for main and fail-safe).

The device can be fused three times using mirror registers. The user can first load the mirror register content with the desired contents, then decide either to use the device in Emulation mode or to burn the next sector. The first sector to be burned is S1, the second S1bis and the third S1ter. FlexGUI automatically manages the next sector to be burned. It is not possible to revert back to the previous sector. When the user reaches the sector S1ter, there no other possibility for burn, however emulation mode is still available.

**Note:** When device is operating in Emulation mode using configuration from mirror registers, few parameters must be overwritten by SPI/I2C. This concerns regulator TSD behaviors; VPRE slew rate high-side and low-side VBOOST slew rate. See <u>Section 8.4.10 "TestMode:Mirrors\_Main and TestMode:Mirrors\_Failsafe"</u> for additional details.

At boot, the content of the valid sector is loaded into the Mirror Register Sector 1. The mirror register content is accessible from FlexGUI by using specific SPI/I2C commands. The mirror configuration is managed by the FlexGUI, which eases the access.

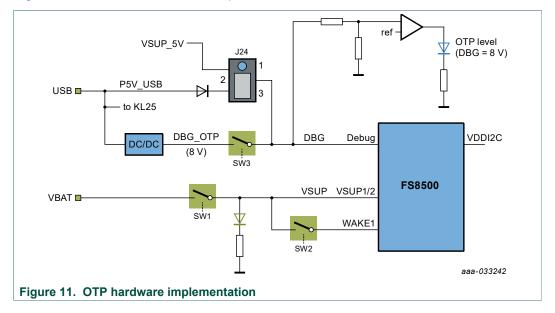

#### 4.2.2 OTP hardware implementation

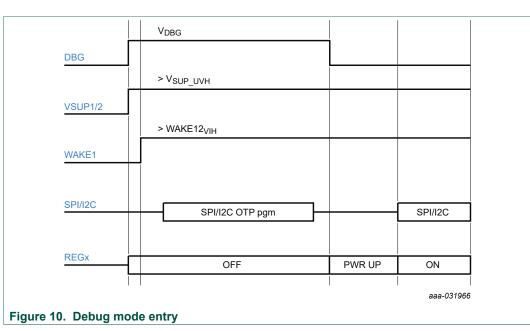

To work in OTP emulation or OTP programming, it is required to start the device in Debug mode.

<u>Figure 10</u> shows the sequence to be followed to enter in Debug mode. The voltage sequence on the kit is done using switches installed on the board, while the OTP registers configuration is managed by the FlexGUI GUI. This is described in detail in the following sections.

KITFS85AEEVM evaluation board

Figure 11 shows the hardware kit implementation.

#### 4.3 Kit featured components

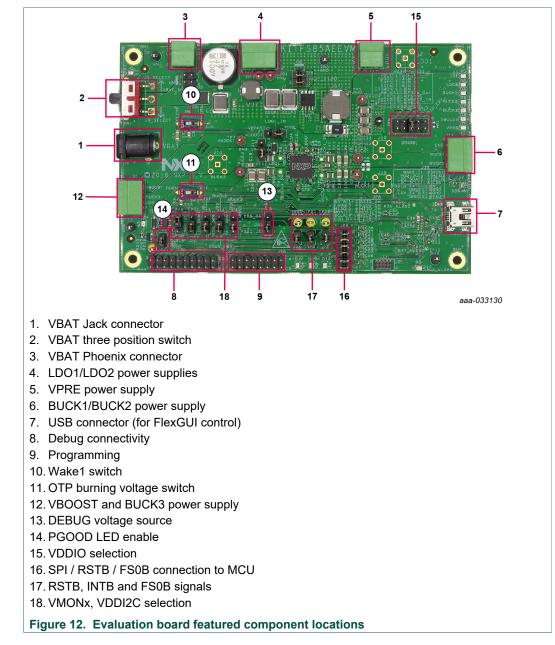

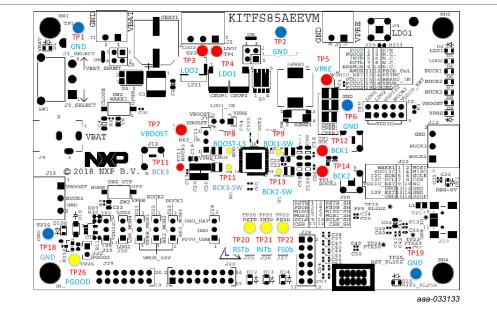

Figure 12 identifies important components on the board and <u>Table 2</u> provides additional details on these components.

### KITFS85AEEVM evaluation board

#### Table 2. Evaluation board board component descriptions

| Number | Description                                                                                                                                                                                                       |

|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1      | VBAT Jack connector                                                                                                                                                                                               |

| 2      | <ul> <li>VBAT three position switch</li> <li>Left position: board supplied by Jack connector</li> <li>Middle position: board not supplied</li> <li>Right position: board supplied by Phoenix connector</li> </ul> |

| 3      | VBAT Phoenix connector                                                                                                                                                                                            |

| 4      | LDO1/LDO2 power supply                                                                                                                                                                                            |

| 5      | VPRE power supply                                                                                                                                                                                                 |

| 6      | BUCK1/BUCK2 power supply                                                                                                                                                                                          |

UM11193 User manual © NXP B.V. 2020. All rights reserved.

#### KITFS85AEEVM evaluation board

| Number | Description                                                                                                                                |  |

|--------|--------------------------------------------------------------------------------------------------------------------------------------------|--|

| 7      | USB connector (for FlexGUI control)                                                                                                        |  |

| 8      | Debug connectivity. Access to:<br>• VSUP, GND<br>• FOUT/FIN<br>• PGOOD/RSTB/FS0B<br>• FCCUx<br>• WAKE2<br>• PSYNC, ERRMON, AMUX<br>• VMONx |  |

| 9      | Programming <ul> <li>SPI bus</li> <li>I2C bus</li> <li>Debug pin</li> <li>VPRE, VSUP, GND</li> </ul>                                       |  |

| 10     | Wake1 switch                                                                                                                               |  |

| 11     | OTP burning voltage switch                                                                                                                 |  |

| 12     | VBOOST and BUCK3 power supply                                                                                                              |  |

| 13     | DEBUG voltage source either from USB (recommended) or from VSUP                                                                            |  |

| 14     | PGOOD LED indicator (enabled when jumper is plugged)                                                                                       |  |

| 15     | VDDIO source from device regulators or external sources                                                                                    |  |

| 16     | SPI, RSTB or FS0B can be disconnected between device and MCU                                                                               |  |

| 17     | RSTB, INTB and FS0B signals available here (device pin level)                                                                              |  |

| 18     | Allows to select VMON from regulators or a fix 0.8 V<br>VDDI2C can be selected either 1.8 V or 3.3 V                                       |  |

#### 4.3.1 FS8500/FS8400: Fail-safe system basis chip with multiple SMPS and LDO

#### 4.3.1.1 General description

This device family is part of a global platform FS84 (fit for ASIL B) and FS85 (fit for ASIL D), pin to pin and software compatible. The FS85/FS84 is an automotive functionally safe multi-output power supply integrated circuit, with focus on Radar, Vision, ADAS domain controller, Radio and Infotainment applications. It includes multiple switch mode and linear voltage regulators. It offers external frequency synchronization input and output, for optimized system EMC performance.

The FS85/FS84 includes enhanced safety features, with fail-safe output, becoming a full part of a safety-oriented system partitioning, covering both ASIL B and ASIL D safety integrity level. It is developed in compliance with ISO 26262 standard. Several device versions are available, offering choice in number of output rails, output voltage setting, operating frequency and power up sequencing, to address multiple applications.

#### 4.3.1.2 Features

- 60 V DC maximum input voltage for 12 V and 24 V applications

- VPRE synchronous buck controller with external MOSFETs. Configurable output voltage, switching frequency, and current capability up to 10 A peak.

- Low voltage integrated synchronous BUCK1 converter, dedicated to MCU core supply with SVS capability. Configurable output voltage and current capability up to 3.6 A peak.

#### KITFS85AEEVM evaluation board

- **Based on part number:** low voltage integrated synchronous BUCK2 converter. Configurable output voltage and current capability up to 3.6 A peak. Multi-phase capability with BUCK1 to extend the current capability up to 7.2 A peak on a single rail. Static voltage scaling capability.

- **Based on part number**: low voltage integrated synchronous BUCK3 converter. Configurable output voltage and current capability up to 2.5 A typical peak.

- BOOST converter with integrated low-side switch. Configurable output voltage and max input current up to 1.5 A peak.

- EMC optimization techniques including SMPS frequency synchronization, spread spectrum, slew rate control, manual frequency tuning

- 2x linear voltage regulators for MCU IOs and ADC supply, external physical layer. Configurable output voltage and current capability up to 400 mA DC.

- Standby OFF mode with very low sleep current (10 µA typ)

- 2x input pins for wake-up detection and battery voltage sensing

- Device control via 32 bits SPI or I2C interface with CRC

- Power synchronization pin to operate 2x FS85 devices or FS85 plus an external PMIC

- Scalable portfolio from ASIL B to ASIL D with independent monitoring circuitry, dedicated interface for MCU monitoring, simple and challenger watchdog function, power good, reset and interrupt, built-in self-test, fail-safe output

- Configuration by OTP programming. Prototype enablement to support custom setting during project development in engineering mode.

#### 4.3.2 Indicators

The following LEDs are provided as visual output devices for the evaluation board:

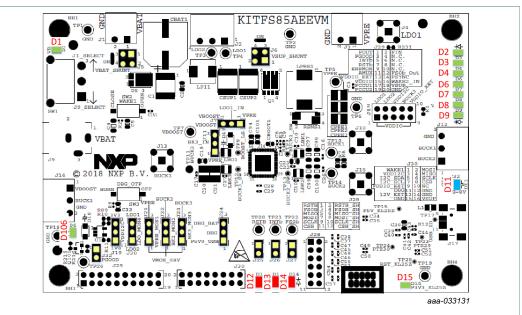

Figure 13. Evaluation board indicator locations

| Label | Name | Color | Description |  |

|-------|------|-------|-------------|--|

| D1    | VBAT | Green | VBAT On     |  |

| D2    | LDO1 | Green | LDO1 On     |  |

UM11193 User manual

## KITFS85AEEVM evaluation board

| Label | Name        | Color | Description                               |

|-------|-------------|-------|-------------------------------------------|

| D3    | LDO2        | Green | LDO2 On                                   |

| D4    | BUCK1       | Green | BUCK1 On                                  |

| D6    | BUCK2       | Green | BUCK2 On                                  |

| D7    | BUCK3       | Green | BUCK3 On                                  |

| D8    | VBOOST      | Green | VBOOST On                                 |

| D9    | VPRE        | Green | VPRE On                                   |

| D11   | DBG > 8.0 V | Blue  | DBG pin voltage > 8.0 V (OTP programming) |

| D12   | RSTB        | Red   | RSTb asserted (logic level = 0)           |

| D13   | INTB        | Red   | INTB asserted (logic level = 0)           |

| D14   | FS0B        | Red   | FS0B asserted (logic level = 0)           |

| D15   | P3V3_KL25   | Green | P3V3_KL25 On                              |

| D106  | PGOOD       | Green | PGOOD released                            |

#### 4.3.3 Connectors

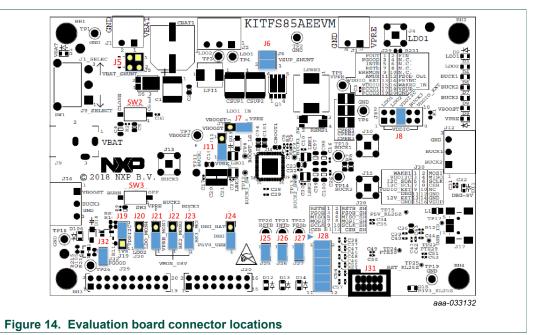

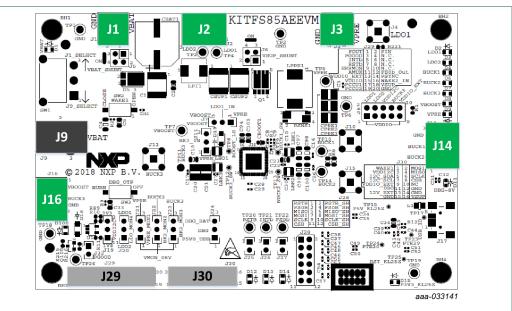

Figure 14 shows the location of connectors on the board.

## 4.3.3.1 VBAT connector (J1)

VBAT connects to the board through Phoenix connector (J1).

#### Table 4. V<sub>BAT</sub> Phoenix connector (J1)

| Schematic label | Signal name | Description                  |

|-----------------|-------------|------------------------------|

| J1-1            | VBAT        | Battery voltage supply input |

| J1-2            | GND         | Ground                       |

UM11193 User manual

#### 4.3.3.2 Output power supply connectors

#### Table 5. BUCK1/BUCK2 connector (J14)

| Schematic label | Signal name | Description               |

|-----------------|-------------|---------------------------|

| J14-1           | BUCK2       | BUCK2 power supply output |

| J14-2           | BUCK1       | BUCK1 power supply output |

| J14-3           | GND         | Ground                    |

#### Table 6. VBOOST/BUCK3 connector (J16)

| Schematic label | Signal name | Description               |

|-----------------|-------------|---------------------------|

| J16-1           | VBOOST      | VBOOST output             |

| J16-2           | BUCK3       | BUCK3 power supply output |

| J16-3           | GND         | Ground                    |

#### Table 7. LDO1/LDO2 connector (J2)

| Schematic label | Signal name | Description              |

|-----------------|-------------|--------------------------|

| J2-1            | LDO1        | LDO1 power supply output |

| J2-2            | LDO2        | LDO2 power supply output |

| J2-3            | GND         | Ground                   |

#### Table 8. VPRE connector (J3)

| Schematic label | Signal name | Description              |

|-----------------|-------------|--------------------------|

| J3-1            | VPRE        | VPRE power supply output |

| J3-2            | GND         | Ground                   |

## 4.3.3.3 Debug connector (J29)

#### Table 9. Debug connector (J29)

| Schematic label | Signal name | Description                      |

|-----------------|-------------|----------------------------------|

| J29-1           | FOUT        | Frequency synchronization output |

| J29-2           | FIN         | Frequency synchronization input  |

| J29-3           | PGOOD       | Power GOOD                       |

| J29-4           | n.c.        | not connected                    |

| J29-5           | INTB        | Interrupt, active low            |

| J29-6           | n.c.        | not connected                    |

| J29-7           | RSTB        | Reset, active low                |

| J29-8           | n.c.        | not connected                    |

| J29-9           | ERRMON      | Error monitoring                 |

| J29-10          | n.c.        | not connected                    |

| J29-11          | AMUX        | Analog multiplexer               |

| J29-12          | FS0B_Out    | Fail-safe, active low            |

| J29-13          | VDDIO_EXT   | VDDIO external reference         |

© NXP B.V. 2020. All rights reserved.

## KITFS85AEEVM evaluation board

| Schematic label | Signal name | Description                    |

|-----------------|-------------|--------------------------------|

| J29-14          | PSYNC       | Power synchronization          |

| J29-15          | VDDIO       | VDDIO used by FS85             |

| J29-16          | WAKE2_IN    | Wake2 input                    |

| J29-17          | FCCU1       | Fault collector control unit 1 |

| J29-18          | VSUP        | VSUP power supply              |

| J29-19          | FCCU2       | Fault collector control unit 2 |

| J29-20          | GND         | Ground                         |

#### 4.3.3.4 Program connector (J30)

| Schematic label | Signal name | Description                            |

|-----------------|-------------|----------------------------------------|

| J30-1           | WAKE1       | WAKE1 input                            |

| J30-2           | MOSI        | SPI master output slave input          |

| J30-3           | VDDI2C      | VDDI2C voltage                         |

| J30-4           | MISO        | SPI master input slave output          |

| J30-5           | I2C_SDA     | I2C serial data                        |

| J30-6           | SCLK        | SPI clock                              |

| J30-7           | I2C_SCL     | I2C serial clock                       |

| J30-8           | CSB         | SPI chip select                        |

| J30-9           | VDDIO_EXT   | VDDIO supplied from external regulator |

| J30-10          | VPRE        | VPRE output                            |

| J30-11          | DBG         | Connected to Debug pin                 |

| J30-12          | GND         | Ground                                 |

| J30-13          | n.c.        | not connected                          |

| J30-14          | VSUP        | Connected to VSUP pin                  |

| J30-15          | GND         | Ground                                 |

| J30-16          | GND         | Ground                                 |

## 4.3.4 Test points

The following test points provide access to various signals to and from the board.

## KITFS85AEEVM evaluation board

#### Figure 15. Evaluation board test points

| Test point name | Signal name | Description                  |

|-----------------|-------------|------------------------------|

| TP1             | GND         | Ground                       |

| TP2             | GND         | Ground                       |

| TP3             | LDO1        | LDO1 regulator output        |

| TP4             | LDO2        | LDO2 regulator output        |

| TP5             | VPRE        | VPRE DC/DC regulator output  |

| TP6             | GND         | Ground                       |

| TP7             | VBOOST      | VBOOST DC/DC output          |

| TP8             | BOOST_LS    | VBOOST low-side switcher     |

| TP9             | BUCK1_SW    | BUCK1 switcher               |

| TP10            | BUCK1       | BUCK1 DC/DC regulator output |

| TP11            | BUCK3       | BUCK3 DC/DC regulator output |

| TP12            | BUCK3_SW    | BUCK3 switcher               |

| TP13            | BUCK2_SW    | BUCK2 switcher               |

| TP14            | BUCK2       | BUCK2 DC/DC regulator output |

| TP19            | GND         | Ground                       |

| TP20            | RSTb        | Reset                        |

| TP21            | INTB        | Interruption                 |

| TP22            | FS0B        | Fail-safe output             |

| T26             | PGOOD       | Power GOOD                   |

#### Table 11. Evaluation board test point descriptions

# UM11193 KITFS85AEEVM evaluation board

#### 4.3.5 Jumpers

Figure 16. Evaluation board jumper locations

| Name | Function        | Pin<br>number | Jumper/pin function                                    |

|------|-----------------|---------------|--------------------------------------------------------|

| J5   | VBAT shunt      | 1-2           | Shunt switch SW1 for current > 5.0 A                   |

| 12   | VDAT Shuht      | 3-4           | Shunt switch SW1 for current > 5.0 A                   |

| J6   | VSUP shunt      | 1-2           | For current measurement (insert amperemeter)           |

| 30   | VSOF Shull      | 3-4           | For current measurement (insert amperemeter)           |

| J7   | LDO1 input      | 1-2           | LDO1_IN connected to VPRE                              |

| 57   |                 | 2-3           | LDO1_IN connected to VBOOST                            |

|      |                 | 1-2           | VDDIO tied to LDO1                                     |

|      |                 | 3-4           | VDDIO tied to LDO2                                     |

| J8   | VDDIO selection | 5-6           | VDDIO tied to VDDI2C (provided by external regulators) |

|      |                 | 7-8           | VDDIO tied to BUCK3                                    |

|      |                 | 9–10          | VDDIO tied to VDDIO external                           |

| J9   | VBAT Jack       | Jack          | Used for VBAT supply using jack connector              |

| J11  | BUCK3 input     | 1-2           | BUCK_INQ tied to VPRE                                  |

| 511  |                 | 2-3           | BUCK_INQ tied to VBOOST                                |

| J20  | VMON4           | 1-2           | VMON4 tied to LDO2                                     |

| 020  |                 | 2-3           | VMON4 tied to LDO1                                     |

| J21  | VMON1           | 1-2           | VMON1 tied to 0.8 V                                    |

| 021  |                 | 2-3           | VMON1 tied to VPRE                                     |

| J22  | VMON2           | 1-2           | VMON2 tied to 0.8 V                                    |

| 022  |                 | 2-3           | VMON2 tied to BUCK2                                    |

| J23  | VMON3           | 1-2           | VMON3 tied to 0.8 V                                    |

| 020  | VMUN3           | 2-3           | VMON3 tied to BUCK3                                    |

#### Table 12. Evaluation board jumper descriptions

UM11193 User manual

17 / 52

© NXP B.V. 2020. All rights reserved.

## KITFS85AEEVM evaluation board

| Name | Function | Pin<br>number | Jumper/pin function                                                                |

|------|----------|---------------|------------------------------------------------------------------------------------|

| 104  | Debug    | 1–2           | Debug pin tied to P5V0_USB (5.0 V provided by USB connector)                       |

| J24  | Debug    | 2-3           | Debug pin tied to VBAT (through external protection)<br>Do not use for OTP burning |

| J25  | RSTB     | 1-2           | Reset LED<br>Enabled when jumper is plugged                                        |

| J26  | INTB     | 1-2           | Interrupt LED<br>Enabled when jumper is plugged                                    |

| J27  | FS0B     | 1–2           | FS0B LED<br>Enabled when jumper is plugged                                         |

| J29  | —        | —             | -                                                                                  |

| J30  | —        | —             | _                                                                                  |

| J31  | —        | —             | Use only during board manufacturing                                                |

| J32  | PGOOD    | 1–2           | PGOOD LED<br>Enabled when jumper is plugged                                        |

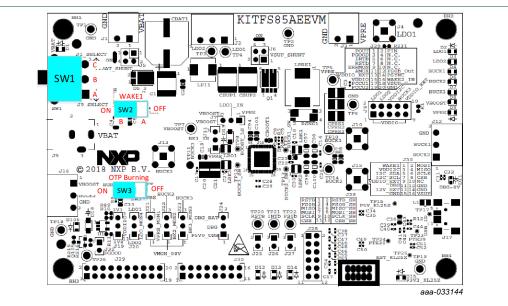

### 4.3.6 Switches

#### Figure 17. Switch locations

#### Table 13. SW3

| Position | Function            | Description                                                                          |

|----------|---------------------|--------------------------------------------------------------------------------------|

| RIGHT    | OTP programming Off | OTP burning not possible                                                             |

| LEFT     | OTP programming On  | 8.0 V on DBG pin allows OTP<br>burning (blue LED turns On to<br>indicate this state) |

UM11193 User manual

#### KITFS85AEEVM evaluation board

| Table 14. SW2 |              |                                      |  |

|---------------|--------------|--------------------------------------|--|

| Position      | Function     | Description                          |  |

| OFF           | WAKE1 open   | Wake1 pin not connected to $V_{SUP}$ |  |

| ON            | WAKE1 closed | Wake1 pin connected to $V_{SUP}$     |  |

#### Table 15. SW1

| Position | Function | Description        |

|----------|----------|--------------------|

| ТОР      | VBAT On  | VBAT from J1       |

| MIDDLE   | VBAT Off | Board not supplied |

| BOTTOM   | VBAT On  | VBAT from J9       |

#### 4.4 Schematic, board layout and bill of materials

The schematic, board layout and bill of materials for the KITFS85AEEVM evaluation board are available at <u>http://www.nxp.com/KITFS85AEEVM</u>.

## 5 Installing and configuring software and tools

This development kit uses FlexGUI software. FlexGUI software is based on Java JRE.

Preparing the Windows PC workstation consists of three steps.

- 1. Install the appropriate Java SE Runtime Environment (JRE).

- 2. Install Windows 7 FlexGUI driver.

- 3. Install FlexGUI software package.

#### 5.1 Installing the Java JRE

- Download Java JRE (Java SE Runtime Environment), available at <u>http://www.oracle.com/technetwork/java/javase/downloads/jre8-downloads-2133155.html</u> (8u162 or newer).

- 2. Open the installer and follow the installation instructions.

- 3. Following the successful installation, restart the computer.

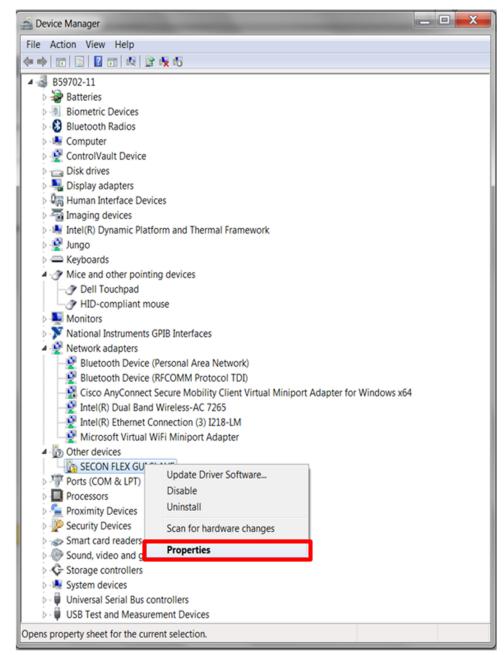

#### 5.2 Installing Windows 7 FlexGUI driver

On Windows 7 PCs, a virtual COM port installation is required. Install the Windows 7 FlexGUI driver using the following procedure.

**Note:** On Windows 10, it is not necessary to install virtual com port as Windows 10 uses a generic COM port driver.

- 1. Connect the kit to the computer as described in <u>Section 6 "Configuring the hardware</u> <u>for startup"</u>

- 2. On the Windows PC, open the Device Manager.

- 3. In the **Device Manager** window, right-click on **SECON FLEX GUI SLAVE**, and then select **Properties**.

UM11193

#### KITFS85AEEVM evaluation board

aaa-031982

4. In the SECON FLEX GUI SLAVE Properties window, click Update Driver.

## KITFS85AEEVM evaluation board

| SECON FLE | X GUI SLAVE Prop      | erties X                                                                                                       |

|-----------|-----------------------|----------------------------------------------------------------------------------------------------------------|

| General   | Driver Details        |                                                                                                                |

|           | SECON FLEX GL         | JI SLAVE                                                                                                       |

|           | Device type:          | Other devices                                                                                                  |

|           | Manufacturer:         | Unknown                                                                                                        |

|           | Location:             | Port_#0002.Hub_#0002                                                                                           |

| The The   | e is no driver select | e are not installed. (Code 28)<br>ed for the device information set or element.<br>evice, click Update Driver. |

|           |                       | Update Driver                                                                                                  |

|           |                       |                                                                                                                |

|           |                       | Close                                                                                                          |

|           |                       | aaa-03198                                                                                                      |

5. in the Update Software Driver window, select Browse my computer for driver software.

| lo | w do you want to search for driver software?                                                                                                                                                                                           |  |

|----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| •  | Search automatically for updated driver software<br>Windows will search your computer and the Internet for the latest driver<br>software for your device, unless you've disabled this feature in your device<br>installation settings. |  |

| •  | Browse my computer for driver software<br>Locate and install driver software manually.                                                                                                                                                 |  |

|    |                                                                                                                                                                                                                                        |  |

UM11193

KITFS85AEEVM evaluation board

- <complex-block>

Constant of the series of the seri

- 6. Select Let me pick from a list of device drivers on my computer, and then click Next.

7. Select Ports (COM & LPT) from the list, and then click Next.

| Select your device's type                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | ; nom the list be | low. |   |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|------|---|

| Common hardware types:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                   |      |   |

| Network Client                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                   |      |   |

| Network Protocol                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                   |      |   |

| Retwork Service                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                   |      |   |

| Non-Plug and Play Drivers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                   |      |   |

| PCMCIA adapters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                   |      |   |

| Portable Devices                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                   |      |   |

| Ports (COM & LPT)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                   |      |   |

| Reference of the second |                   |      |   |

| Processors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                   |      | = |

| Proximity Devices                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                   |      |   |

| SBP2 IEEE 1394 Devices                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                   |      |   |

| SD host adapters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                   |      |   |

| Security Devices                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                   |      | - |

8. Click Have Disk.

## KITFS85AEEVM evaluation board

|            | In the local distance                                                                                                                                                               | ligerte.                                                                                                              |      | ×             |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|------|---------------|

| $\bigcirc$ | Update Driver Software - SECON Fl                                                                                                                                                   | EX GUI SLAVE                                                                                                          |      |               |

|            | Select the manufacturer and                                                                                                                                                         | vant to install for this hardware.<br>model of your hardware device and then<br>you want to install, click Have Disk. |      | If you have a |

|            | Manufacturer<br>(Standard port types)<br>Brother<br>Compaq GSM Radio Card<br>NBC<br>Compart GSM Radio Card<br>This driver is digitally signed.<br>Tell me why driver signing is imp | Model<br>Communications Port<br>ECP Printer Port<br>Multiport Communications Port<br>Printer Port                     | Ha   | ave Disk      |

|            |                                                                                                                                                                                     |                                                                                                                       | Next | Cancel        |

aaa-031987

9. Click Browse.

| HON NO.               | nutrion tuble Properties                                                                                  | X                           |

|-----------------------|-----------------------------------------------------------------------------------------------------------|-----------------------------|

| 🕞 👖 Update D          | Priver Software - SECON FLEX GUI SLAVE                                                                    |                             |

| Select the o          | device driver you want to install for this ha                                                             | ardware.                    |

| Selec<br>Install From | t the manufacturer and model of your bardware device<br>n Disk                                            | and then click Next. If you |

| N<br>C                | Insert the manufacturer's installation disk, and then make sure that the correct drive is selected below. | OK<br>Cancel                |

| A<br>B                | Copy manufacturer's files from:                                                                           |                             |

|                       | r is digitally signed.<br><del>Iny driver signing is important</del>                                      | Have Disk                   |

|                       |                                                                                                           | Next Cancel                 |

|                       |                                                                                                           | aaa-031988                  |

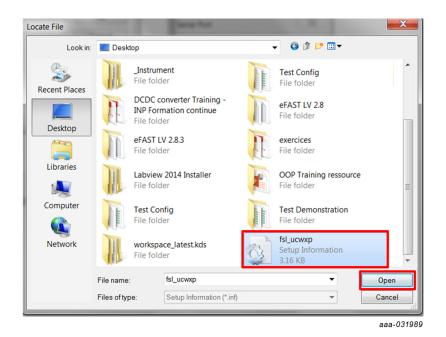

10.In the Locate File window, locate and select fsl\_ucwxp, and then click Open.

UM11193

#### KITFS85AEEVM evaluation board

11.In the Install from Disk window, click OK.

| Install Fron | n Disk                                                                                                    | X            |

|--------------|-----------------------------------------------------------------------------------------------------------|--------------|