\*scale Semiconductor

Technical Data

Document Number: MC13892

Rev. 19.0, 4/2014

# **√RoHS**

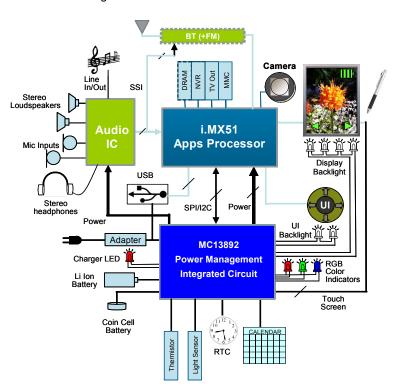

# Power Management Integrated Circuit (PMIC) for i.MX35/51

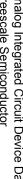

The MC13892 is a Power Management Integrated Circuit (PMIC) designed specifically for use with the Freescale i.MX35 and i.MX51 families. It is also compatible with the i.MX27, i.MX31, and i.MX37 application processors targeting netbooks, ebooks, smart mobile devices, smart phones, personal media players, and portable navigation devices. This device is powered by SMARTMOS technology.

## **Features**

- · Battery charger system for wall charging and USB charging

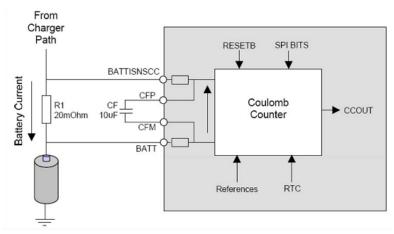

- 10-bit ADC for monitoring battery and other inputs, plus a coulomb counter support module

- Four adjustable output buck regulators for direct supply of the processor core and memory

- · 12 adjustable output LDOs with internal and external pass devices

- Boost regulator for supplying RGB LEDs

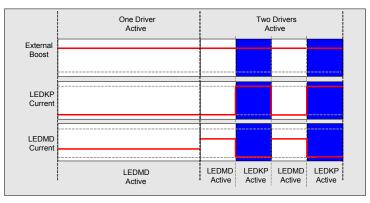

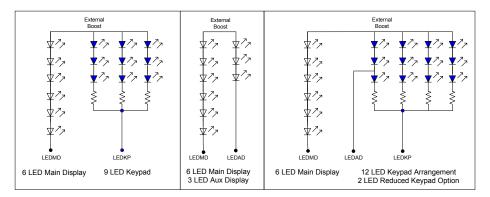

- Serial backlight drivers for displays and keypad, plus RGB LED drivers

- Power control logic with processor interface and event detection

- Real time clock and crystal oscillator circuitry, with coin cell backup and support for external secure real time clock on a companion system processor IC

- · Touch screen interface

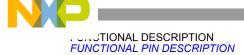

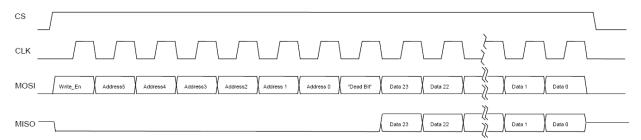

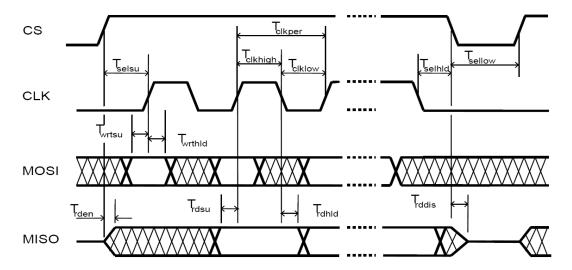

- SPI/I<sup>2</sup>C bus interface for control and register access

# 13892

## **POWER MANAGEMENT**

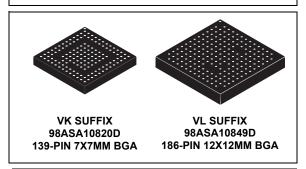

## **ORDERING INFORMATION**

See Device Variation Table on Page 2.

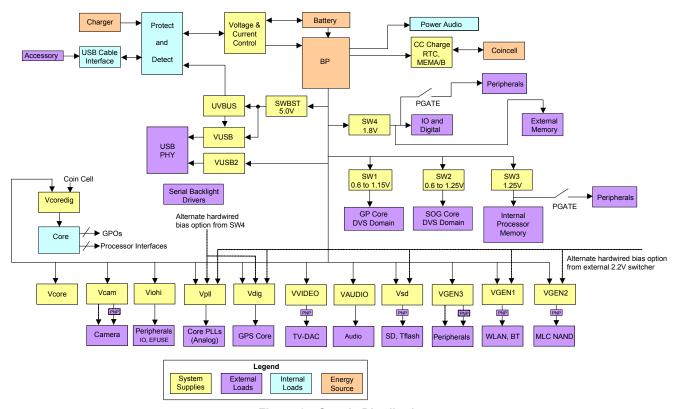

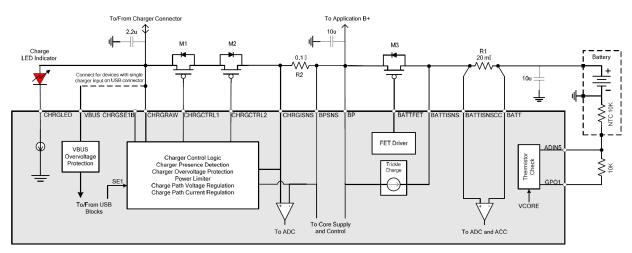

Figure 1. MC13892 Typical Operating Circuit

# **DEVICE VARIATIONS**

Table 1. MC13892 Device Variations

| Part Number <sup>(1)</sup> | Notes   | Package      | Temperature<br>Range (T <sub>A</sub> ) | Pin Map   | Description                          |  |

|----------------------------|---------|--------------|----------------------------------------|-----------|--------------------------------------|--|

| MC13892CJVK                | (2)     |              |                                        |           | Global Reset Function Default ON     |  |

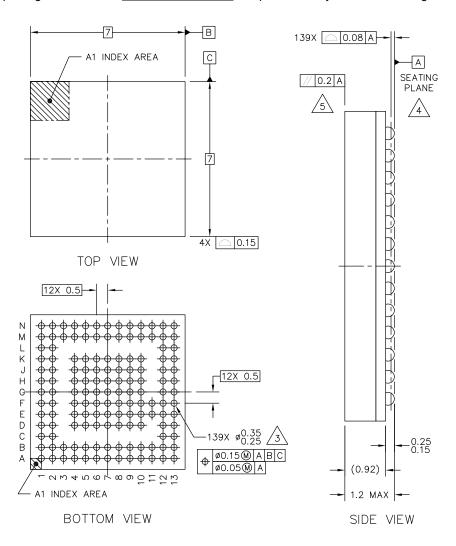

| MC13892AJVK                | (3)     |              | -40 to +85 °C -                        | Figure 3  | Global Neset Function Belaute GIV    |  |

| MC13892DJVK                | (2) (4) | 139-PIN      |                                        |           | Global Reset Function Default OFF    |  |

| MC13892BJVK                | (3)     | 7x7 mm BGA   |                                        |           | Close Nesser and Default of T        |  |

| MC13892VK                  | (3)     |              |                                        |           | No Global Reset Function             |  |

| MC13892JVK                 | (3)     |              |                                        |           | No Global Neset Fullction            |  |

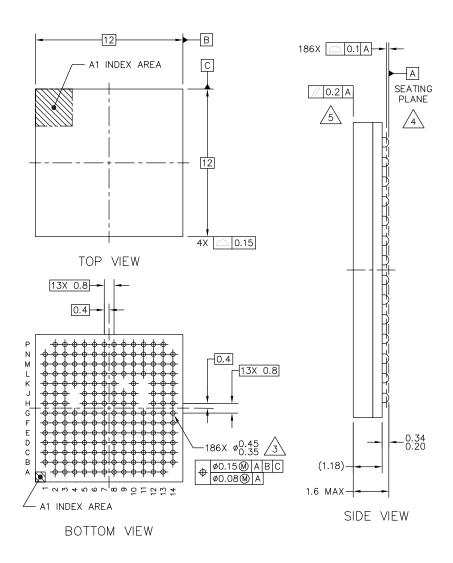

| MC13892CJVL                | (2)     |              | -40 to +65 C                           |           | Global Reset Function Default ON     |  |

| MC13892AJVL                | (3)     |              |                                        |           | Global Reset i unction belauit ON    |  |

| MC13892DJVL                | (2) (4) | 186-PIN      |                                        | Figure 4  | Global Reset Function Default OFF    |  |

| MC13892BJVL                | (3)     | 12x12 mm BGA |                                        | i igule 4 | Global Neset Full Clion Delault Of F |  |

| MC13892VL                  | (3)     |              |                                        |           | No Global Reset Function             |  |

| MC13892JVL                 | (3)     |              |                                        |           | NO Global Reset Function             |  |

# Notes

- 1. For Tape and Reel product, add an "R2" suffix to the part number.

- 2. Recommended for all new designs

- 3. Not recommended for new designs

- Backward compatible replacement part for MC13892VK, MC13892JVK, MC13892VL, MC13892JVL, MC13892BJVK, and MC13892BJVL

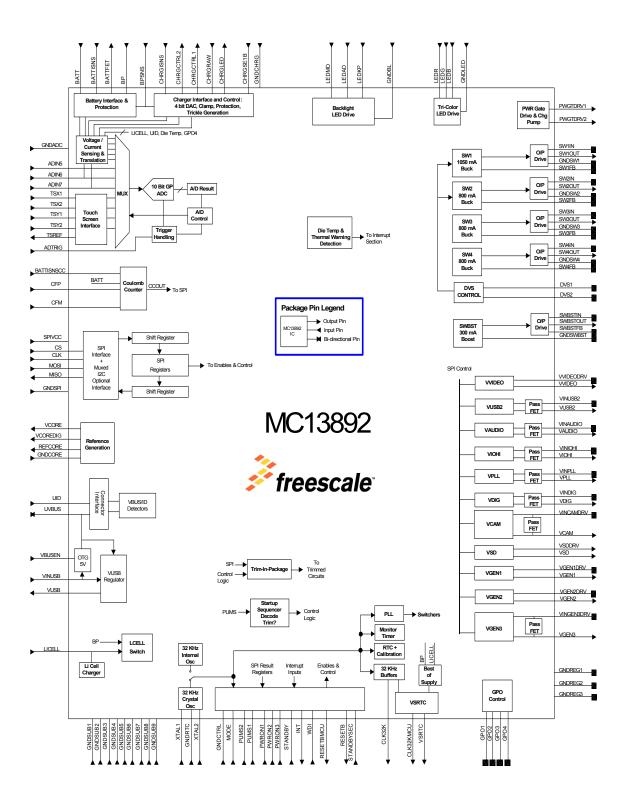

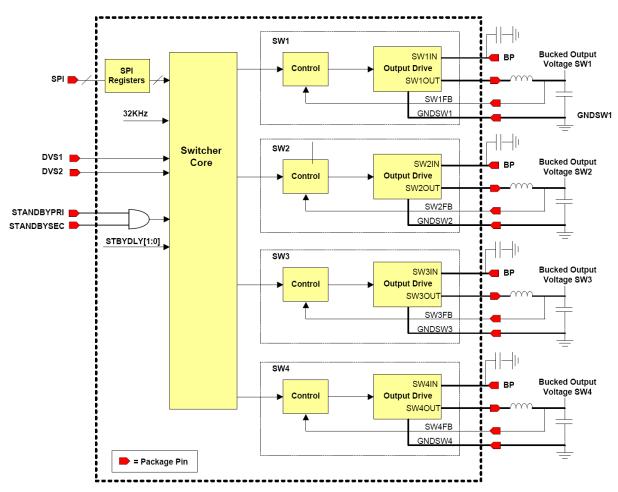

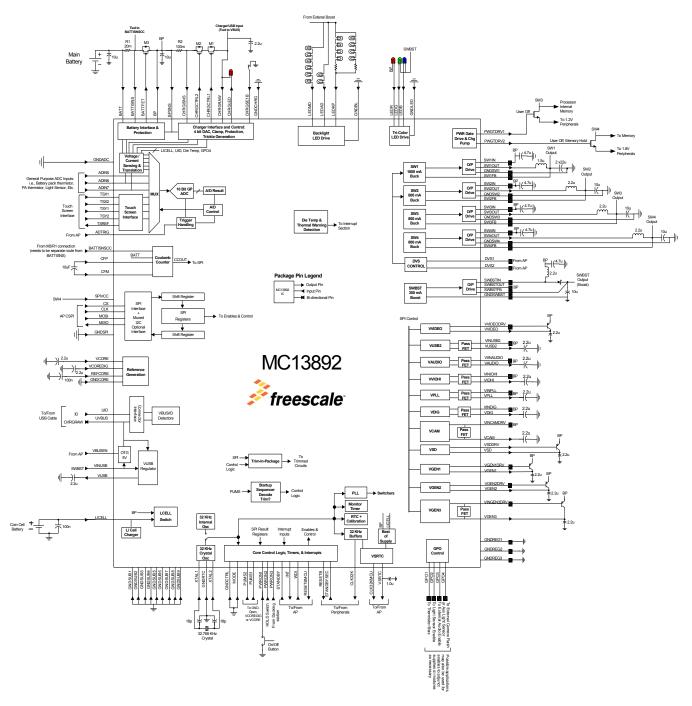

# INTERNAL BLOCK DIAGRAM

Figure 2. MC13892 Simplified Internal Block Diagram

# **PIN CONNECTIONS**

|   | 1       | 2      | 3          | 4         | 5        | 6         | 7        | 8                     | 9        | 10      | 11        | 12         | 13        |

|---|---------|--------|------------|-----------|----------|-----------|----------|-----------------------|----------|---------|-----------|------------|-----------|

| Α | VUSB2   | VUSE2  | VINUSE2    | SABSTIN   | GNDSWBST | GNDBL     | NC       | MODE                  | VOORE    | BATT    | OHRGRAW   | OHRGCTRL2  | OHRGCTRL2 |

| В | VUSB2   | GPO1   | DV\$2      | SMESTOUT  | LEDB     | EDXP      | LEDR     | GNDCCRE               | VOOREDIG | BP      | OHROCIRL1 | BATTISNSCC | O-ROCTRL2 |

| С | WNPLL   | VSDDRV |            |           |          |           |          |                       |          |         |           | O-ROSNS    | BATTISNS  |

| D | VUSB    | VSD    |            | SMBSTFB   | LEDMD    | DVS1      | REFCORE  | 0 <del>1R</del> 03E1B | NOETT    | BATTFET |           | BP9NS      | PWRONI    |

| E | UVBUS   | VRLL   |            | LEDG      | GNDLED   | UD        | PUMS2    | GNDO-RG               | OFFICE   | PWRON2  | ADTRIG    | INT        | GNDSWI    |

| F | GNDS/A3 | VBUSEN |            | SM3FB     | LEDAD    | GNDSUB    | GND8LB   | GNDSUB                | GPC3     | CPC2    | RESETBMOU | RESETB     | SW1OUT    |

| G | 9N3OUT  | VINUSB |            | SA4FB     | GNDREC2  | GNDSUB    | GND8LB   | GNDSUB                | PUMS1    | wa      |           | GP04       | SWIIN     |

| н | SMain   | MISO   |            | GND9PI    | GNDREG3  | GNDSUB    | GNDSUB   | GNDSUB                | GNDCTRL  | SWIFB   |           | STANDBYSEC | SMZIN     |

| J | SMAIN   | MOSI   |            | CIK32KWDU | STANDBY  | GNDADC    | GNDREG1  | PWRON8                | TSX1     | SWZFB   |           | TSV2       | SWZOUT    |

| К | 9/40UT  | SPIVOC |            | PWGTDRV1  | OLKSØK   | VCAM      | CFP      | СFМ                   | ADIN5    | ADIN6   |           | WIDEODRV   | GNDSW2    |

| L | GNDS/A4 | CS     |            |           |          |           |          |                       |          |         |           | TSY2       | WIDEO     |

| М | VŒN8    | ак     | VŒN2       | VSRTC     | GNDRTC   | VINCAMDRV | PWGTDRV2 | VDIG                  | MNDIG    | VŒNIDRV | ADIN7     | TSY1       | TSREF     |

| N | VŒN8    | VŒNS   | VINGENBORV | VOENZORV  | XTAL2    | XTAL1     | VINALDIO | VAUDIO                | NOH      | MNOH    | VŒNI      | TSREF      | TSPEF     |

| Regulators    |

|---------------|

| Switchers     |

| Backlights    |

| Control Logic |

| Charger       |

| RTC           |

| Grounds       |

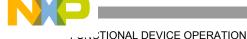

| USB           |

| ADC           |

| SPI/I2C       |

| No Connect    |

Figure 3. MC13892VK Pin Connections

GNDSUB LEDR UID DVS1 REFCORE BATTISNSCO BATTISNS LEDB LEDG LEDKP LEDAD PUMS2 VCOREDIG LICELL BATTFET BPSNS PUMS1 GNDLED CHRGLED UVBUS VINPLL PWRON2 GPO2 RESETBMC VBUSEN GNDSUB GNDSUB GNDSUB GNDSUB GNDSUB GNDSUB GNDCTRL SW10UT VINUSB WDI GNDSUB GNDSUB GNDSUB GNDSUB GNDSUB GNDSUB GNDSUB GNDSUB SW1IN GNDSUB GNDSUB GNDSUB GNDSUB GNDSUB GNDSW2 cs GNDSUB GNDSUB TSY2 STANDBYSE SW2OUT GNDSUB GNDSUB VCAM VINAUDIO VVIDEO VINCAMDRV TSREF VINIOHI ADIN5 ADIN7 GNDRTC

Figure 4. MC13892VL Pin Connections

11

12

13

14

# Table 2. MC13892 Pin Definitions

| Pin Number<br>on the<br>13982VK<br>7x7 mm | Pin Number on<br>the 13982VL<br>12x12 mm | Pin Name   | Rating<br>(V) | Pin Function | Formal Name                          | Definition                                                                                                                            |

|-------------------------------------------|------------------------------------------|------------|---------------|--------------|--------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|

| A1, A2, B1                                | A2                                       | VUSB2      | 3.6           | Output       | USB 2 Supply                         | Output regulator for USB PHY                                                                                                          |

| А3                                        | A3                                       | VINUSB2    | 5.5           | Power        | USB 2 Supply Input                   | Input regulator VUSB2                                                                                                                 |

| A4                                        | A5                                       | SWBSTIN    | 5.5           | Power        | Switcher Boost Power Input           | Switcher BST input                                                                                                                    |

| A5                                        | D5                                       | GNDSWBST   | -             | Ground       | Switcher Boost Ground                | Ground for switcher BST                                                                                                               |

| A6                                        | D8                                       | GNDBL      | -             | Ground       | Backlight LED Ground                 | Ground for serial LED drive                                                                                                           |

| A7                                        | A7                                       | NC         | -             | -            | No Connect                           | Do not connect                                                                                                                        |

| A8                                        | A8                                       | MODE       | 9.0           | Input        | Mode Configuration                   | USB LBP mode, normal mode, test mode selection,& anti-fuse bias                                                                       |

| A9                                        | A9                                       | VCORE      | 3.6           | Output       | Core Supply                          | Regulated supply output for the IC analog core circuitry                                                                              |

| A10                                       | A10                                      | BATT       | 5.5           | Input        | Battery Connection                   | Battery positive pin     Battery current sensing point 2     Battery supply voltage sense                                             |

| A11                                       | A11                                      | CHRGRAW    | 20            | I/O          | Charger Input                        | Charger input     Output to battery supplied accesories                                                                               |

| A12, A13, B13                             | A12                                      | CHRGCTRL2  | 5.5           | Output       | Charger Control 2                    | Driver output for charger path FETs M2                                                                                                |

| B2                                        | B2                                       | GPO1       | 3.6           | Output       | General Purpose<br>Output 1          | General purpose output 1                                                                                                              |

| В3                                        | C2                                       | DVS2       | 3.6           | Input        | Dynamic Voltage<br>Scaling Control 2 | Switcher 2 DVS input pin                                                                                                              |

| B4                                        | A4                                       | SWBSTOUT   | 7.5           | Power        | Switcher Boost Output                | Switcher BST BP supply                                                                                                                |

| B5                                        | C4                                       | LEDB       | 7.5           | Input        | LED Driver                           | General purpose LED current sink driver Blue                                                                                          |

| В6                                        | C6                                       | LEDKP      | 28            | Input        | LED Driver                           | Keypad lighting LED current sink driver                                                                                               |

| B7                                        | B5                                       | LEDR       | 7.5           | Input        | LED Driver                           | General purpose LED current sink driver Red                                                                                           |

| B8                                        | В9                                       | GNDCORE    | -             | Ground       | Core Ground                          | Ground for the IC core circuitry                                                                                                      |

| В9                                        | C9                                       | VCOREDIG   | 1.5           | Output       | Digital Core Supply                  | Regulated supply output for the IC digital core circuitry                                                                             |

| B10                                       | B11                                      | BP         | 5.5           | Power        | Battery Plus                         | <ol> <li>Application supply point</li> <li>Input supply to the IC core circuitry</li> <li>Application supply voltage sense</li> </ol> |

| B11                                       | D9                                       | CHRGCTRL1  | 20            | Output       | Charger Control 1                    | Driver output for charger path FETs M1                                                                                                |

| B12                                       | B13                                      | BATTISNSCC | 4.8           | Input        | Battery Current Sense                | Accumulated current counter current sensing point                                                                                     |

| C1                                        | E3                                       | VINPLL     | 5.5           | Power        | PLL Supply Input                     | Input regulator processor PLL                                                                                                         |

| C2                                        | B1                                       | VSDDRV     | 5.5           | Output       | VSD Driver                           | Drive output regulated SD card                                                                                                        |

| C12                                       | A13                                      | CHRGISNS   | 4.8           | Input        | Charger Current Sense                | Charge current sensing point 1                                                                                                        |

| C13                                       | B14                                      | BATTISNS   | 4.8           | Input        | Battery Current Sense                | Battery current sensing point 1                                                                                                       |

| 7                                         | ar accompliant of                        | A functional description of each pin can be found in the Functional Description. |               |              |                                      |                                                              |  |  |  |  |

|-------------------------------------------|------------------------------------------|----------------------------------------------------------------------------------|---------------|--------------|--------------------------------------|--------------------------------------------------------------|--|--|--|--|

| Pin Number<br>on the<br>13982VK<br>7x7 mm | Pin Number on<br>the 13982VL<br>12x12 mm | Pin Name                                                                         | Rating<br>(V) | Pin Function | Formal Name                          | Definition                                                   |  |  |  |  |

| D1                                        | D1                                       | VUSB                                                                             | 3.6           | Output       | USB Supply                           | USB transceiver regulator output                             |  |  |  |  |

| D2                                        | C1                                       | VSD                                                                              | 3.6           | Output       | SD Card Supply                       | Output regulator SD card                                     |  |  |  |  |

| D4                                        | С3                                       | SWBSTFB                                                                          | 3.6           | Input        | Switcher Boost<br>Feedback           | Switcher BST feedback                                        |  |  |  |  |

| D5                                        | D7                                       | LEDMD                                                                            | 28            | Input        | LED Driver                           | Main display backlight LED current sink driver               |  |  |  |  |

| D6                                        | В7                                       | DVS1                                                                             | 3.6           | Input        | Dynamic Voltage<br>Scaling Control 1 | Switcher 1DVS input pin                                      |  |  |  |  |

| D7                                        | B8                                       | REFCORE                                                                          | 3.6           | Output       | Core Reference                       | Main bandgap reference                                       |  |  |  |  |

| D8                                        | B10                                      | CHRGSE1B                                                                         | 3.6           | Input        | Charger Select                       | Charger forced SE1 detection input                           |  |  |  |  |

| D9                                        | C10                                      | LICELL                                                                           | 3.6           | I/O          | Coin Cell Connection                 | 1. Coin cell supply input                                    |  |  |  |  |

|                                           |                                          |                                                                                  |               |              |                                      | 2. Coin cell charger output                                  |  |  |  |  |

| D10                                       | C11                                      | BATTFET                                                                          | 4.8           | Output       | Battery FET Connection               | Driver output for battery path FET M3                        |  |  |  |  |

| D12                                       | C12                                      | BPSNS                                                                            | 4.8           | Input        | Battery Plus Sense                   | 1. BP sense point                                            |  |  |  |  |

|                                           |                                          |                                                                                  |               |              |                                      | 2. Charge current sensing point 2                            |  |  |  |  |

| D13                                       | D11                                      | PWRON1                                                                           | 3.6           | Input        | Power On 1                           | Power on/off button connection 1                             |  |  |  |  |

| E1                                        | E1                                       | UVBUS                                                                            | 20            | I/O          | USB Bus                              | USB transceiver cable interface     VBUS & OTG supply output |  |  |  |  |

| E2                                        | D2                                       | VPLL                                                                             | 3.6           | Output       | Voltage Supply for PLL               | Output regulator processor PLL                               |  |  |  |  |

| E4                                        | C5                                       | LEDG                                                                             | 7.5           | Input        | PWM Driver for Green<br>LED          | General purpose LED current sink driver Green                |  |  |  |  |

| E5                                        | D6                                       | GNDLED                                                                           | _             | Ground       | LED Ground                           | Ground for LED drivers                                       |  |  |  |  |

| E6                                        | B6                                       | UID                                                                              | 5.5           | Input        | USB ID                               | USB OTG transceiver cable ID                                 |  |  |  |  |

| E7                                        | C8                                       | PUMS2                                                                            | 3.6           | Input        | Power Up Mode Select<br>2            | Power up mode supply setting 2                               |  |  |  |  |

| E8                                        | B12                                      | GNDCHRG                                                                          | -             | Ground       | Charger Ground                       | Ground for charger interface                                 |  |  |  |  |

| E9                                        | D10                                      | CHRGLED                                                                          | 20            | Output       | Charger LED                          | Trickle LED driver output 1                                  |  |  |  |  |

| E10                                       | E11                                      | PWRON2                                                                           | 3.6           | Input        | Power On 2                           | Power on/off button connection 2                             |  |  |  |  |

| E11                                       | D13                                      | ADTRIG                                                                           | 3.6           | Input        | ADC Trigger                          | ADC trigger input                                            |  |  |  |  |

| E12                                       | E13                                      | INT                                                                              | 3.6           | Output       | Interrupt Signal                     | Interrupt to processor                                       |  |  |  |  |

| E13                                       | G13, G14                                 | GNDSW1                                                                           | -             | Ground       | Switcher 1 Ground                    | Ground for switcher 1                                        |  |  |  |  |

| F1                                        | G1, G2                                   | GNDSW3                                                                           | -             | Ground       | Switcher 3 Ground                    | Ground for switcher 3                                        |  |  |  |  |

| F2                                        | F2                                       | VBUSEN                                                                           | 3.6           | Input        | VBUS Enable                          | External VBUS enable pin for OTG supply                      |  |  |  |  |

| F4                                        | G3                                       | SW3FB                                                                            | 3.6           | Input        | Switcher 3 Feedback                  | Switcher 3 feedback                                          |  |  |  |  |

| F5                                        | C7                                       | LEDAD                                                                            | 28            | Input        | Auxiliary Display LED                | Auxiliary display backlight LED sinking current driver       |  |  |  |  |

| F6                                        | A6, B3, B4, D3,<br>D4, E4, E5, E6        | GNDSUB1                                                                          | -             | Ground       | Ground 1                             | Non critical signal ground and thermal heat sink             |  |  |  |  |

|                                           |                                           | . caon pin oan | oo louile     | and r dried  | onal Description.           |                                                   |  |

|-------------------------------------------|-------------------------------------------|----------------|---------------|--------------|-----------------------------|---------------------------------------------------|--|

| Pin Number<br>on the<br>13982VK<br>7x7 mm | Pin Number on<br>the 13982VL<br>12x12 mm  | Pin Name       | Rating<br>(V) | Pin Function | Formal Name                 | Definition                                        |  |

| F7                                        | E7, E8, E9, E10,<br>F4, F5, F6            | GNDSUB2        | -             | Ground       | Ground 2                    | Non critical signal ground and thermal heat sink  |  |

| F8                                        | F7, F8, F9, F10,<br>G4, G5, G6, G7,<br>G8 | GNDSUB3        | -             | Ground       | Ground 3                    | Non critical signal ground and thermal heat sink  |  |

| F9                                        | C13                                       | GPO3           | -             | Output       | General Purpose<br>Output 3 | General purpose output 3                          |  |

| F10                                       | E12                                       | GPO2           | 3.6           | Output       | General Purpose<br>Output 2 | General purpose output 2                          |  |

| F11                                       | E14                                       | RESETBMCU      | 3.6           | Output       | MCU Reset                   | Reset output for processor                        |  |

| F12                                       | F13                                       | RESETB         | 3.6           | Output       | Peripheral Reset            | Reset output for peripherals                      |  |

| F13                                       | F14                                       | SW1OUT         | 5.5           | Output       | Switcher 1 Output           | Switcher 1 output                                 |  |

| G1                                        | F1                                        | SW3OUT         | 5.5           | Output       | Switcher 3 Output           | Switcher 3 output                                 |  |

| G2                                        | F3                                        | VINUSB         | 7.5           | Input        | VUSB Supply Input           | Input option for UVUSB; tie to SWBST at top level |  |

| G4                                        | J3                                        | SW4FB          | 3.6           | Input        | Switcher 4 Feedback         | Switcher 4 feedback                               |  |

| G5                                        | E2                                        | GNDREG2        | -             | Ground       | Regulator 2 Ground          | Ground for regulators 2                           |  |

| G6                                        | G9, G10, G11,<br>H3, H5, H6, H7,<br>H8    | GNDSUB4        | -             | Ground       | Ground 4                    | Non critical signal ground and thermal heat sink  |  |

| G7                                        | H9, H10, H12,<br>J5, J6, J7               | GNDSUB5        | -             | Ground       | Ground 5                    | Non critical signal ground and thermal heat sink  |  |

| G8                                        | J8, J9, J10, K4,<br>K5, K6, K7            | GNDSUB6        | -             | Ground       | Ground 6                    | Non critical signal ground and thermal heat sink  |  |

| G9                                        | C14                                       | PUMS1          | 3.6           | Input        | Power Up Mode Select<br>1   | Power up mode supply setting 1                    |  |

| G10                                       | F12                                       | WDI            | 3.6           | Input        | Watchdog Input              | Watchdog input                                    |  |

| G12                                       | D14                                       | GPO4           | 3.6           | Output       | General Purpose<br>Output 4 | General purpose output 4                          |  |

| G13                                       | H13, H14                                  | SW1IN          | 5.5           | Input        | Switcher 1 Input            | Input voltage for switcher 1                      |  |

| H1                                        | H1, H2                                    | SW3IN          | 5.5           | Power        | Switcher 3 Input            | Switcher 3 input                                  |  |

| H2                                        | P2                                        | MISO           | 3.6           | I/O          | Master In Slave Out         | Primary SPI read output                           |  |

| H4                                        | L3                                        | GNDSPI         | -             | Ground       | SPI Ground                  | Ground for SPI interface                          |  |

| H5                                        | N4                                        | GNDREG3        | -             | Ground       | Regulator 3 Ground          | Ground for regulators 3                           |  |

| H6                                        | K8, K10, L4, L5,<br>L6, L10               | GNDSUB7        | -             | Ground       | Ground 7                    | Non critical signal ground and thermal heat sink  |  |

| H7                                        | P5, P7, P8, P9,<br>P10                    | GNDSUB8        | -             | Ground       | Ground 8                    | Non critical signal ground and thermal heat sink  |  |

| Н8                                        | -                                         | GNDSUB9        | -             | Ground       | Ground 9                    | Non critical signal ground and thermal heat sink  |  |

| H9                                        | F11                                       | GNDCTRL        | -             | Ground       | Logic Control Ground        | Ground for control logic                          |  |

|                                           |                                           |                |               |              |                             | •                                                 |  |

| Pin Number<br>on the<br>13982VK<br>7x7 mm | Pin Number on<br>the 13982VL<br>12x12 mm | Pin Name   | Rating<br>(V) | Pin Function | Formal Name                    | Definition                               |  |  |

|-------------------------------------------|------------------------------------------|------------|---------------|--------------|--------------------------------|------------------------------------------|--|--|

| H10                                       | G12                                      | SW1FB      | 3.6           | Input        | Switcher 1 Feedback            | Switcher 1 feedback                      |  |  |

| H12                                       | L12                                      | STANDBYSEC | 3.6           | Input        | Secondary Standby<br>Signal    | Standby input signal from peripherals    |  |  |

| H13                                       | J13, J14                                 | SW2IN      | 5.5           | Input        | Switcher 2 Input               | Input voltage for Switcher 2             |  |  |

| J1                                        | J1, J2                                   | SW4IN      | 5.5           | Power        | Switcher 4 Input               | Switcher 4 input                         |  |  |

| J2                                        | N2                                       | MOSI       | 3.6           | Input        | Master Out Slave In            | Primary SPI write input                  |  |  |

| J4                                        | M3                                       | CLK32KMCU  | 3.6           | Output       | 32 kHz Clock for MCU           | 32 kHz clock output for processor        |  |  |

| J5                                        | M6                                       | STANDBY    | 3.6           | Input        | Standby Signal                 | Standby input signal from processor      |  |  |

| J6                                        | N11                                      | GNDADC     | -             | Ground       | ADC Ground                     | Ground for A to D circuitry              |  |  |

| J7                                        | P12                                      | GNDREG1    | -             | Ground       | Regulator 1 Ground             | Ground for regulators 1                  |  |  |

| J8                                        | D12                                      | PWRON3     | 3.6           | Input        | Power On 3                     | Power on/off button connection 3         |  |  |

| J9                                        | M12                                      | TSX1       | 3.6           | Input        | Touch Screen<br>Interface X1   | Touch screen interface X1                |  |  |

| J10                                       | J12                                      | SW2FB      | 3.6           | Input        | Switcher 2 Feedback            | Switcher 2 feedback                      |  |  |

| J12                                       | M13                                      | TSX2       | 3.6           | Input        | Touch Screen<br>Interface X2   | Touch screen interface X2                |  |  |

| J13                                       | L14                                      | SW2OUT     | 5.5           | Output       | Switcher 2 Output              | Switcher 2 output                        |  |  |

| K1                                        | L1                                       | SW4OUT     | 5.5           | Output       | Switcher 4 Output              | Switcher 4 output                        |  |  |

| K2                                        | K3                                       | SPIVCC     | 3.6           | Input        | Supply Voltage for SPI         | Supply for SPI bus and audio bus         |  |  |

| K4                                        | P3                                       | PWGTDRV1   | 4.8           | Output       | Power Gate Driver 1            | Power gate driver 1                      |  |  |

| K5                                        | M4                                       | CLK32K     | 3.6           | Output       | 32 kHz Clock                   | 32 kHz clock output for peripherals      |  |  |

| K6                                        | L7                                       | VCAM       | 3.6           | Output       | Camera Supply                  | Output regulator camera                  |  |  |

| K7                                        | M8                                       | CFP        | 4.8           | Passive      | Current Filter Positive        | Accumulated current filter cap plus pin  |  |  |

| K8                                        | M9                                       | CFM        | 4.8           | Passive      | Current Filter Negative        | Accumulated current filter cap minus pin |  |  |

| K9                                        | N12                                      | ADIN5      | 4.8           | Input        | ADC Channel 5 Input            | ADC generic input channel 5              |  |  |

| K10                                       | P13                                      | ADIN6      | 4.8           | Input        | ADC Channel 6 Input            | ADC generic input channel 6              |  |  |

| K12                                       | K12                                      | VVIDEODRV  | 5.5           | Output       | VVIDEO Driver                  | Drive output regulator VVIDEO            |  |  |

| K13                                       | K13, K14                                 | GNDSW2     | -             | Ground       | Switcher 2 Ground              | Ground for switcher 2                    |  |  |

| L1                                        | K1, K2                                   | GNDSW4     | -             | Ground       | Switcher 4 Ground              | Ground for switcher 4                    |  |  |

| L2                                        | L2                                       | CS         | 3.6           | Input        | Chip Select                    | Primary SPI select input                 |  |  |

| L12                                       | L11                                      | TSY2       | 3.6           | Input        | Touch Screen<br>Interface Y2   | Touch screen interface Y2                |  |  |

| L13                                       | L13                                      | VVIDEO     | 3.6           | Output       | Video Supply                   | Output regulator TV DAC                  |  |  |

| M1, N1, N2                                | N1                                       | VGEN3      | 3.6           | Output       | General Purpose<br>Regulator 3 | Output GEN3 regulator                    |  |  |

| M2                                        | M1                                       | CLK        | 3.6           | Input        | Clock                          | Primary SPI clock input                  |  |  |

| M3                                        | N3                                       | VGEN2      | 3.6           | Output       | General Purpose<br>Regulator 2 | Output GEN2 regulator                    |  |  |

| Pin Number<br>on the<br>13982VK<br>7x7 mm | Pin Number on<br>the 13982VL<br>12x12 mm | Pin Name   | Rating<br>(V) | Pin Function | Formal Name                                           | Definition                                                                                                               |  |

|-------------------------------------------|------------------------------------------|------------|---------------|--------------|-------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|--|

| M4                                        | M5                                       | VSRTC      | 3.6           | Output       | SRTC Supply                                           | Output regulator for SRTC module on processor                                                                            |  |

| M5                                        | P6                                       | GNDRTC     | -             | Ground       | Real Time Clock<br>Ground                             | Ground for the RTC block                                                                                                 |  |

| M6                                        | M7                                       | VINCAMDRV  | 5.5           | I/O          | Camera Regulator<br>Supply Input and Driver<br>Output | Input regulator camera using internal PMOS FET.     Drive output regulator for camera voltage using external PNP device. |  |

| M7                                        | N8                                       | PWGTDRV2   | 4.8           | Output       | Power Gate Driver 2                                   | Power gate driver 2                                                                                                      |  |

| M8                                        | L9                                       | VDIG       | 3.6           | Output       | Digital Supply                                        | Output regulator digital                                                                                                 |  |

| M9                                        | P11                                      | VINDIG     | 5.5           | Input        | VDIG Supply Input                                     | Input regulator digital                                                                                                  |  |

| M10                                       | M10                                      | VGEN1DRV   | 5.5           | Output       | VGEN1 Driver                                          | Drive output GEN1 regulator                                                                                              |  |

| M11                                       | N13                                      | ADIN7      | 4.8           | Input        | ADC Channel 7 Input                                   | ADC generic input channel 7, group 1                                                                                     |  |

| M12                                       | M14                                      | TSY1       | 3.6           | Input        | Touch Screen<br>Interface Y1                          | Touch screen interface Y1                                                                                                |  |

| M13, N12,<br>N13                          | N14                                      | TSREF      | 3.6           | Output       | Touch Screen<br>Reference                             | Touch screen reference                                                                                                   |  |

| N3                                        | M2                                       | VINGEN3DRV | 5.5           | Power/Output | VGEN3 Supply Input and Driver Output                  | Input VGEN3 regulator     Drive VGEN3 output regulator                                                                   |  |

| N4                                        | P4                                       | VGEN2DRV   | 5.5           | Output       | VGEN2 Driver                                          | Drive output GEN2 regulator                                                                                              |  |

| N5                                        | N5                                       | XTAL2      | 2.5           | Input        | Crystal Connection 2                                  | 32.768 kHz oscillator crystal connection 2                                                                               |  |

| N6                                        | N6                                       | XTAL1      | 2.5           | Input        | Crystal Connection 1                                  | 32.768 kHz oscillator crystal connection 1                                                                               |  |

| N7                                        | L8                                       | VINAUDIO   | 5.5           | Power        | Audio Supply Input                                    | Input regulator VAUDIO                                                                                                   |  |

| N8                                        | N7                                       | VAUDIO     | 3.6           | Output       | Audio Supply                                          | Output regulator for audio                                                                                               |  |

| N9                                        | N9                                       | VIOHI      | 3.6           | Output       | High Voltage IO Supply                                | Output regulator high voltage IO, efuse                                                                                  |  |

| N10                                       | N10                                      | VINIOHI    | 5.5           | Input        | High Voltage IO Supply<br>Input                       | Input regulator high voltage IO                                                                                          |  |

| N11                                       | M11                                      | VGEN1      | 3.6           | Output       | General Purpose<br>Regulator 1                        | Input GEN1 regulator                                                                                                     |  |

# **ELECTRICAL CHARACTERISTICS**

# **MAXIMUM RATINGS**

## **Table 3. Maximum Ratings**

All voltages are with respect to ground unless otherwise noted. Exceeding these ratings may cause a malfunction or permanent damage to the device.

| Ratings                                                                                                           | Symbol                                                             | Value         | Unit |

|-------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|---------------|------|

| ELECTRICAL RATINGS                                                                                                |                                                                    |               |      |

| Charger and USB Input Voltage <sup>(5)</sup>                                                                      | V <sub>CHRGR</sub>                                                 | -0.3 to 20    | V    |

| MODE pin Voltage                                                                                                  | V <sub>MODE</sub>                                                  | -0.3 to 9.0   | V    |

| Main/Aux/Keypad Current Sink Voltage                                                                              | V <sub>LEDMD</sub> ,<br>V <sub>LEDAD</sub> ,<br>V <sub>LEDKP</sub> | -0.3 to 28    | V    |

| Battery Voltage                                                                                                   | V <sub>BATT</sub>                                                  | -0.3 to 4.8   | V    |

| Coin Cell Voltage                                                                                                 | V <sub>LICELL</sub>                                                | -0.3 to 3.6   | V    |

| ESD Voltage <sup>(6)</sup> Human Body Model - HBM with Mode pin excluded <sup>(9)</sup> Charge Device Model - CDM | V <sub>ESD</sub>                                                   | ±1500<br>±250 | V    |

| THERMAL RATINGS                                                                                                   |                                                                    |               | •    |

| Ambient Operating Temperature Range                                                                               | T <sub>A</sub>                                                     | -40 to +85    | °C   |

| Operating Junction Temperature Range                                                                              | TJ                                                                 | -40 to +125   | °C   |

| Storage Temperature Range                                                                                         | T <sub>STG</sub>                                                   | -65 to +150   | °C   |

| THERMAL RESISTANCE                                                                                                |                                                                    |               | •    |

| Peak Package Reflow Temperature During Reflow <sup>(7)</sup> , <sup>(8)</sup>                                     | T <sub>PPRT</sub>                                                  | Note 8        | °C   |

#### Notes

- 5. USB Input Voltage applies to UVBUS pin only

- 6. ESD testing is performed in accordance with the Human Body Model (HBM) (CZAP = 100 pF, RZAP = 1500 Ω) and the Charge Device Model (CDM), Robotic (CZAP = 4.0 pF).

- 7. Pin soldering temperature limit is for 10 seconds maximum duration. Not designed for immersion soldering. Exceeding these limits may cause malfunction or permanent damage to the device.

- 8. Freescale's Package Reflow capability meets Pb-free requirements for JEDEC standard J-STD-020C. For Peak Package Reflow Temperature and Moisture Sensitivity Levels (MSL), Go to www.freescale.com, search by part number [e.g. remove prefixes/suffixes and enter the core ID to view all orderable parts. (i.e. MC33xxxD enter 33xxx), and review parametrics.

- 9. Mode Pin is not ESD protected.

# **Table 4. Dissipation Ratings**

| Rating Parameter                       | Condition               | Symbol           | VK Package | VL Package | Unit |

|----------------------------------------|-------------------------|------------------|------------|------------|------|

| Junction to Ambient Natural Convection | Single layer board (1s) | $R_{	heta JA}$   | 104        | 65         | °C/W |

| Junction to Ambient Natural Convection | Four layer board (2s2p) | $R_{\theta JMA}$ | 54         | 42         | °C/W |

| Junction to Ambient (@200 ft/min)      | Single layer board (1s) | $R_{\theta JMA}$ | 88         | 55         | °C/W |

| Junction to Ambient (@200 ft/min)      | Four layer board (2s2p) | $R_{\theta JMA}$ | 49         | 38         | °C/W |

| Junction to Board                      |                         | $R_{\theta JB}$  | 32         | 28         | °C/W |

| Junction to Case                       |                         | $R_{	heta JC}$   | 29         | 22         | °C/W |

| Junction to Package Top                | Natural Convection      | θЈТ              | 7.0        | 5.0        | °C/W |

# STATIC ELECTRICAL CHARACTERISTICS

# **Table 5. Static Electrical Characteristics**

Characteristics noted under conditions -40 °C  $\leq$  T<sub>A</sub>  $\leq$  85 °C, GND = 0 V unless otherwise noted. Typical values noted reflect the approximate parameter means at T<sub>A</sub> = 25 °C under nominal conditions, unless otherwise noted.

| Characteristic                                                                                       | Symbol            | Min         | Тур  | Max        | Unit |

|------------------------------------------------------------------------------------------------------|-------------------|-------------|------|------------|------|

| CURRENT CONSUMPTION                                                                                  |                   | l l         |      |            |      |

| RTC Mode All blocks disabled, no main battery attached, coin cell is attached to LICELL (10)         | I <sub>RTC</sub>  |             |      |            | μΑ   |

| RTC                                                                                                  |                   | -           | 3.00 | 6.00       |      |

| OFF Mode (All blocks disabled, main battery attached) <sup>(10)</sup> MC13892 core and RTC module    | I <sub>OFF</sub>  | _           | 10   | 30         | μΑ   |

| Power Cut Mode (All blocks disabled, no main battery attached, coin cell is attached and valid) (10) | I <sub>PCUT</sub> |             |      |            | μΑ   |

| MC13892 core and RTC module                                                                          |                   | _           | 3.0  | 6.0        |      |

| ON Standby mode - Low-power mode 4 buck regulators in low-power mode, 3 regulators (11)              | I <sub>STBY</sub> | _           | 230  | 295        | μA   |

| ON Mode - Typical use case 4 buck regulators in PWMPS mode, 5 Regulators <sup>(12)</sup>             | I <sub>ON</sub>   | _           | 459  | 1500       | μA   |

| O CHARACTERISTICS (13)                                                                               |                   | "           |      | 1          |      |

| PWRON1, PWRON2, PWRON3, Pull-up (14)                                                                 |                   |             |      |            | V    |

| Input Low, 47 kOhm                                                                                   |                   | 0.0         | -    | 0.3        |      |

| Input High, 1.0 MOhm                                                                                 |                   | 1.0         | _    | VCOREDIG   |      |

| CHRGSE1B, Pull-up (15)                                                                               |                   |             |      |            | V    |

| Input Low                                                                                            |                   | 0.0         | -    | 0.3        |      |

| Input High                                                                                           |                   | 1.0         | -    | VCORE      |      |

| STANDBY, STANDBYSEC, WDI, ADTRIG, Weak Pull-down (16),(17)                                           |                   | 0.0         |      | 0.0        | V    |

| Input Low<br>Input High                                                                              |                   | 0.0<br>1.0  | _    | 0.3<br>3.6 |      |

| CLK32K, CMOS                                                                                         |                   | 1.0         |      | 3.0        | V    |

| Output Low, -100 μA                                                                                  |                   | 0.0         | _    | 0.2        | ·    |

| Output High, 100 μA                                                                                  |                   | SPIVCC -0.2 | _    | SPIVCC     |      |

| CLK32KMCU, CMOS                                                                                      |                   |             |      |            | V    |

| Output Low, -100 μA                                                                                  |                   | 0.0         | _    | 0.2        |      |

| Output High, 100 μA                                                                                  |                   | VSRTC- 0.2  | _    | VSRTC      |      |

| RESETB, RESETBMCU, Open Drain (18)                                                                   |                   |             |      |            | V    |

| Output Low, -2.0 mA                                                                                  |                   | 0.0         | _    | 0.4        |      |

| Output High, Open Drain                                                                              |                   | 0.0         | _    | 3.6        |      |

# Notes

- 10. Valid at 25 °C only.

- 11. VPLL, VIOHI, VGEN2

- 12. VPLL, VIOHI, VGEN2, VAUDIO, VVIDEO

- 13. SPIVCC is typically connected to the output of buck regulator: SW4 and set to 1.800 V

- 14. Input has internal pull-up to VCOREDIG equivalent to 200 kOhm

- 15. Input has internal pull-up to VCORE equivalent to 100 kOhm

- 16. SPIVCC needs to remain enabled for proper detection of WDI High to avoid involuntary shutdown

- 17. A weak pull-down represents a nominal internal pull down of 100 nA, unless otherwise noted

- 18. RESETB & RESETBMCU have open drain outputs, external pull-ups are required

Characteristics noted under conditions -40 °C  $\leq$  T<sub>A</sub>  $\leq$  85 °C, GND = 0 V unless otherwise noted. Typical values noted reflect the approximate parameter means at T<sub>A</sub> = 25 °C under nominal conditions, unless otherwise noted.

| Characteristic                                                                       | Symbol | Min         | Тур | Max         | Unit |

|--------------------------------------------------------------------------------------|--------|-------------|-----|-------------|------|

| I/O CHARACTERISTICS (CONTINUED) (19)                                                 |        | 1           |     |             |      |

| VSRTC, Voltage Output                                                                |        | 1.1         | -   | 1.3         | V    |

| DVS1, DVS2, Weak Pull-down (20)                                                      |        |             |     |             | V    |

| Input Low                                                                            |        | 0.0         | _   | 0.3* SPIVCC |      |

| Input High                                                                           |        | 0.7* SPIVCC | -   | 3.1         |      |

| GPO1, CMOS                                                                           |        |             |     |             | V    |

| Output Low, -400 μA                                                                  |        | 0.0         | -   | 0.2         |      |

| Output High, 400 μA                                                                  |        | VCORE- 0.2  | -   | VCORE       |      |

| To VCORE                                                                             |        | 200         | -   | 500         | Ohm  |

| GPO2, GPO3, GPO4, CMOS                                                               |        |             |     |             | V    |

| Output Low, -100 μA                                                                  |        | 0.0         | -   | 0.2         |      |

| Output High, 100 μA                                                                  |        | VIOHI - 0.2 | _   | VIOHI       |      |

| GPO4, Analog Input                                                                   |        | 0.0         | _   | VCORE+0.3   | V    |

| CS, CLK, MOSI, VBUSEN, Weak Pull-down on CS and VBUSEN (20)                          |        |             |     |             | V    |

| Input Low                                                                            |        | 0.0         | _   | 0.3* SPIVCC |      |

| Input High                                                                           |        | 0.7* SPIVCC | _   | SPIVCC+0.3  |      |

| CS, MOSI (at Booting for SPI / I <sup>2</sup> C decoding), Weak Pull-down on CS (21) |        |             |     |             | V    |

| Input Low                                                                            |        | 0.0         | -   | 0.3 * VCORE |      |

| Input High                                                                           |        | 0.7 * VCORE | _   | VCORE       |      |

| MISO, INT, CMOS (22)                                                                 |        |             |     |             | V    |

| Output Low, -100 μA                                                                  |        | 0.0         | _   | 0.2         |      |

| Output High, 100 μA                                                                  |        | SPIVCC -0.2 | -   | SPIVCC      |      |

| PUMS1, PUMS2 (22)                                                                    |        |             |     |             | V    |

| PUMSxS = 00                                                                          |        | 0.0         | -   | 0.3         |      |

| PUMSxS = 01, Load < 10 pF                                                            |        | Open        | _   | Open        |      |

| PUMSxS = 10<br>PUMSxS = 11                                                           |        | 1.3         | -   | 2.0         |      |

| POWSXS = 11                                                                          |        | 2.5         | _   | 3.1         |      |

| MODE (23)                                                                            |        |             |     |             | V    |

| Input Low                                                                            |        | 0.0         | _   | 0.4         |      |

| Input Med                                                                            |        | 1.1         | _   | 1.7         |      |

| Input High                                                                           |        | VCORE       | _   | 9.0         |      |

## Notes

- 19. SPIVCC is typically connected to the output of buck regulator: SW4 and set to 1.800  $\rm V$

- 20. A weak pull-down represents a nominal internal pull down of 100 nA unless otherwise noted

- 21. The weak pull-down on CS is disabled if a VIH is detected at startup to avoid extra consumption in I<sup>2</sup>C mode

- 22. The output drive strength is programmable

- 23. Input state is latched in first phase of cold start, refer to Power Control System for description of PUMS configuration

- 24. Input state is not latched

Characteristics noted under conditions -40 °C  $\leq$  T<sub>A</sub>  $\leq$  85 °C, GND = 0 V unless otherwise noted. Typical values noted reflect the approximate parameter means at T<sub>A</sub> = 25 °C under nominal conditions, unless otherwise noted.

| Characteristic                                                                                           | Symbol                                                               | Min                                               | Тур      | Max                                     | Unit |

|----------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|---------------------------------------------------|----------|-----------------------------------------|------|

| 32 KHZ CRYSTAL OSCILLATOR                                                                                | <b>"</b>                                                             | <u> </u>                                          |          | <u> </u>                                |      |

| Operating Voltage Oscillator and RTC Block from BP                                                       | $V_{XTAL}$                                                           | 1.2                                               | _        | 4.65                                    | V    |

| Coincell Disconnect Threshold At LICELL                                                                  | V <sub>LCD</sub>                                                     | 1.8                                               | _        | 2.0                                     | V    |

| Output Low CLK32K, CLK32KMCU<br>Output sink 100 μA                                                       | V <sub>CLKLO</sub>                                                   | 0.0                                               | _        | 0.2                                     | V    |

| Output High CLK32K Output source 100 μA CLK32KMCU Output source 100 μA                                   | V <sub>CLKHI</sub><br>V <sub>CLKMCUHI</sub>                          | SPIV <sub>CC</sub> -0.2<br>V <sub>SRTC</sub> -0.2 | -<br>-   | SPIV <sub>CC</sub><br>V <sub>SRTC</sub> | V    |

| VSRTC GENERAL                                                                                            |                                                                      |                                                   |          |                                         |      |

| Operating Input Voltage Range V <sub>INMIN</sub> to V <sub>INMAX</sub> Valid Coin Cell range Or valid BP | V <sub>LICELL</sub><br>BP                                            | 1.8<br>UVDET                                      | <u>-</u> | 3.6<br>4.65                             | V    |

| Operating Current Load Range IL <sub>MIN</sub> to IL <sub>MAX</sub>                                      | I <sub>SRTC</sub>                                                    | 0.0                                               | _        | 50                                      | μΑ   |

| Bypass Capacitor Value                                                                                   | C <sub>SRTC</sub>                                                    | _                                                 | 1.0      | _                                       | μF   |

| VSRTC ACTIVE MODE – DC                                                                                   |                                                                      | '                                                 |          | <u> </u>                                |      |

| Output Voltage $V_{OUT}$<br>$V_{INMIN} < V_{IN} < V_{INMAX}$ , $IL_{MIN} < IL < IL_{MAX}$                | V <sub>SRTC</sub>                                                    | 1.15                                              | 1.20     | 1.25                                    | V    |

| CLK AND MISO                                                                                             | <u> </u>                                                             | <del>!</del>                                      |          | <del>- !</del>                          |      |

| Input Low CS, MOSI, CLK                                                                                  | VINCSLO<br>VINMOSILO<br>VINCLKLO                                     | 0.0                                               | -        | 0.3*SPIV <sub>CC</sub>                  | V    |

| Input High CS, MOSI, CLK                                                                                 | V <sub>INCSHI</sub><br>V <sub>INMOSIHI</sub><br>V <sub>INCLKHI</sub> | 0.7*SPIV <sub>CC</sub>                            | -        | SPIV <sub>CC</sub> +0.3                 | V    |

| Output Low MISO, INT<br>Output sink 100 μA                                                               | V <sub>OMISOLO</sub><br>V <sub>OINTLO</sub>                          | 0.0                                               | _        | 0.2                                     | V    |

| Output High MISO, INT<br>Output source 100 μA                                                            | V <sub>OMISOHI</sub><br>V <sub>OINTHI</sub>                          | SPIV <sub>CC</sub> -0.2                           | -        | SPIV <sub>CC</sub>                      | V    |

| SPIVCC Operating Range                                                                                   | SPIV <sub>CC</sub>                                                   | 1.75                                              | _        | 3.1                                     | V    |

Characteristics noted under conditions -40 °C  $\leq$  T<sub>A</sub>  $\leq$  85 °C, GND = 0 V unless otherwise noted. Typical values noted reflect the approximate parameter means at T<sub>A</sub> = 25 °C under nominal conditions, unless otherwise noted.

| Characteristic                                                                                                                                                                                                                                                                                                                                           | Symbol                                                                               | Min                       | Тур                    | Max                   | Unit |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|---------------------------|------------------------|-----------------------|------|

| BUCK REGULATORS                                                                                                                                                                                                                                                                                                                                          |                                                                                      |                           |                        | •                     | •    |

| Operating Input Voltage PWM operation, 0 < IL < I <sub>MAX</sub> PFM operation, 0 < IL < I <sub>MAX</sub> Extended PWM or PFM operation <sup>(25)</sup>                                                                                                                                                                                                  | V <sub>SWIN</sub>                                                                    | 3.0<br>2.8<br>UVDET       | -<br>-<br>-            | 4.65<br>4.65<br>4.65  | V    |

| Output Voltage Range<br>Switcher 1<br>Switchers 2, 3, and 4                                                                                                                                                                                                                                                                                              | V <sub>SW1</sub>                                                                     | 0.6<br>0.6                |                        | 1.375<br>1.850        | V    |

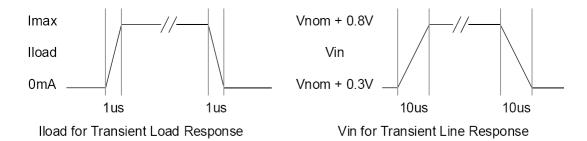

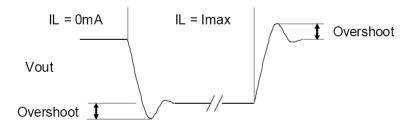

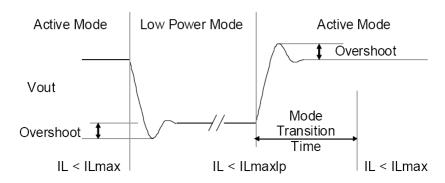

| Output Accuracy  PWM mode including ripple, load regulation, and transients (26)  PFM Mode, including ripple, load regulation, and transients                                                                                                                                                                                                            | V <sub>SWLOPP</sub><br>V <sub>SWLIPPI</sub>                                          | Nom-50<br>Nom-50          | Nom<br>Nom             | Nom+50<br>Nom+50      | mV   |

| Maximum Continuous Load Current, I <sub>MAX</sub> , V <sub>INMIN</sub> <bp<4.65 (swilimb="1," current="" in="" limit)="" limit)<sup="" max="" mode="" no="" pwm="" sw1="" v="">(27) SW2, SW3, SW4 in PWM mode (SWILIMB = 0, no max current limit) SW2, SW3, SW4 in PWM mode (SWILIMB = 1, no max current limit) SW1, SW2, SW3, SW4 in PFM mode</bp<4.65> | I <sub>SW1</sub> I <sub>SW2,3,4</sub> I <sub>SW2,3,4</sub> I <sub>SW1, 2, 3, 4</sub> | 800<br>1050<br>800<br>800 | -<br>-<br>-<br>-<br>50 | -<br>-<br>-<br>-<br>- | mA   |

| Maximum Peak Load Current, $I_{PEAK}$ , $BP \le 4.2 \text{ V}$ , SW1 in PWM Mode (SWILIMB = 1, no max current limit) <sup>(27)</sup> SW4 in PWM Mode (SWILIMB = 1, no max current limit) <sup>(27)</sup>                                                                                                                                                 | I <sub>SW1</sub>                                                                     | 1250<br>1000              | -<br>-                 | _<br>_                | mA   |

# Notes

- 25. In the extended operating range the performance may be degraded

- 26. Transient loading for load steps of ILmax/2

- 27. In this mode, current limit protection is disabled for SW1 SW4 by setting SWILIMB = 1. Therefore, the load on SW1-4 should not exceed the conditions specified in the table above. Application needs to provide current limit protection circuitry either in battery or as preregulated supply to BP.

Characteristics noted under conditions -40 °C  $\leq$  T<sub>A</sub>  $\leq$  85 °C, GND = 0 V unless otherwise noted. Typical values noted reflect the approximate parameter means at T<sub>A</sub> = 25 °C under nominal conditions, unless otherwise noted.

| Characteristic                                                                                                                                                                                                                                                                                                     | Symbol                                                                                                          | Min                                              | Тур                                       | Max                                        | Unit                                  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|--------------------------------------------------|-------------------------------------------|--------------------------------------------|---------------------------------------|

| BUCK REGULATORS (CONTINUED)                                                                                                                                                                                                                                                                                        |                                                                                                                 |                                                  |                                           |                                            |                                       |

| Automatic Mode Change Threshold, Switchover between PFM and PWM modes                                                                                                                                                                                                                                              | AMC <sub>TH</sub>                                                                                               | _                                                | 50                                        | _                                          | mA                                    |

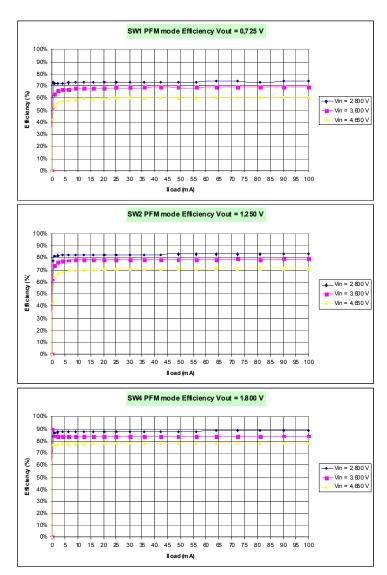

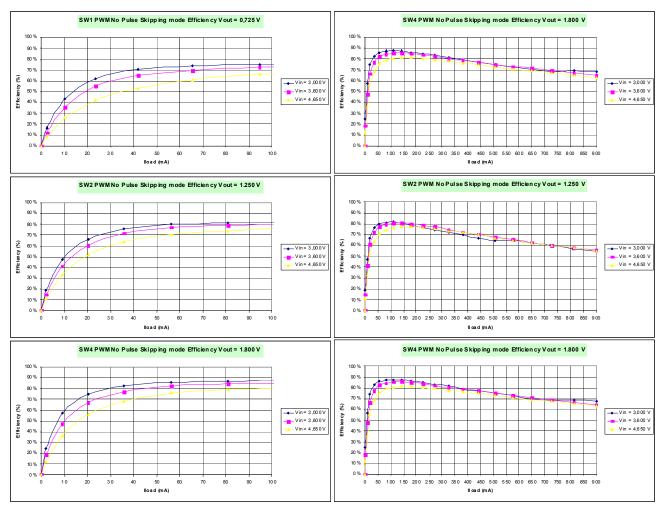

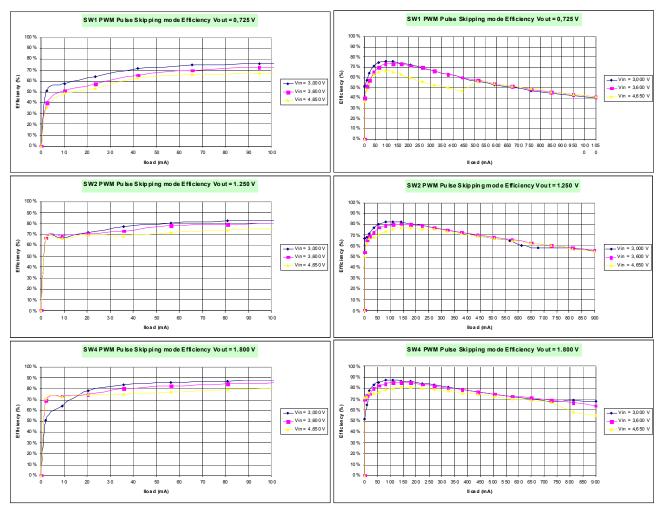

| Efficiency PFM, 0.9 V, 1.0 mA PFM, 01.8 V, 1.0 mA PWM Pulse Skipping, 1.25 V, 50 mA PWM Pulse Skipping, 1.8 V, 50 mA PWM, 1.25 V, 500 mA PWM, 1.8 V, 500 mA                                                                                                                                                        |                                                                                                                 | -<br>-<br>-<br>-                                 | 75<br>85<br>78<br>82<br>78<br>82          | -<br>-<br>-<br>-                           | η                                     |

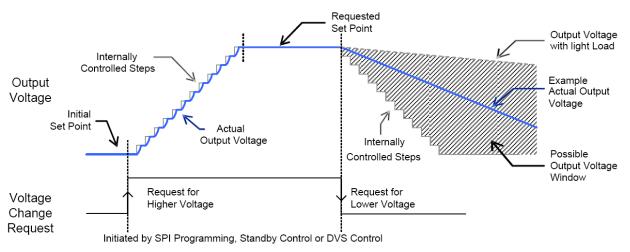

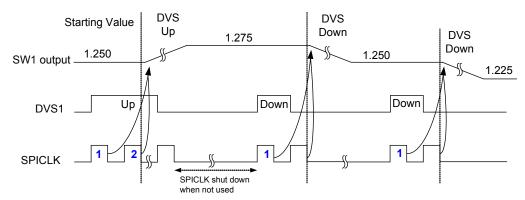

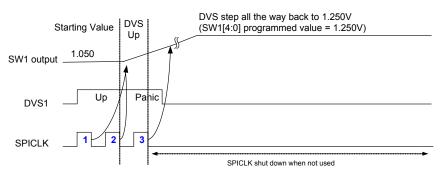

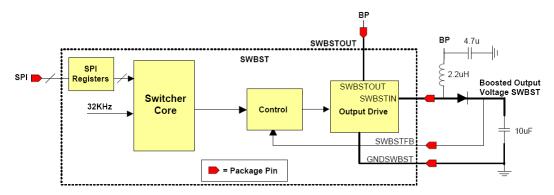

| External Components, Used as a condition for all other parameters Inductor for SW2, SW3, SW4 <sup>(28)</sup> Inductor for SW1 <sup>(28)</sup> Inductor Resistance Bypass Capacitor for SW2, SW3, SW4 <sup>(29)</sup> Bypass Capacitor for SW1 <sup>(30)</sup> Bypass Capacitor ESR Input Capacitor <sup>(31)</sup> | L <sub>SW234</sub><br>L <sub>SW1</sub><br>Rwsw<br>C <sub>OSW234</sub><br>C <sub>OSW1</sub><br>ESR <sub>SW</sub> | -20%<br>-30%<br>-<br>- 35%<br>-35%<br>5.0<br>1.0 | 2.2<br>1.5<br>-<br>10<br>2x22<br>-<br>4.7 | +20%<br>+30%<br>0.16<br>+35%<br>+35%<br>50 | μΗ<br>μΗ<br>Ω<br>μF<br>μF<br>mΩ<br>μF |