# MC33664

## Isolated network high-speed transceiver

Rev. 1.0 — 23 May 2018

Short data sheet: technical data

### 1 General description

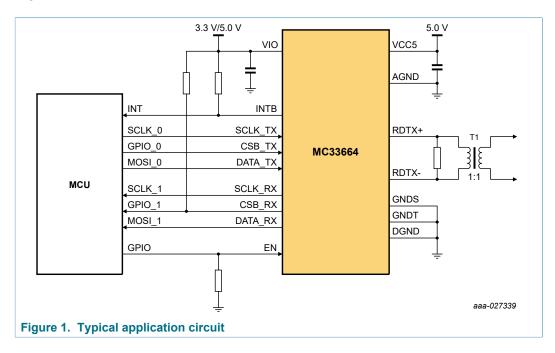

The MC33664 is a SMARTMOS transceiver physical layer transformer driver designed to interface a microcontroller conveniently to a high speed isolated communication network. MCU serial peripheral interface (SPI) data bits are directly converted to pulse bit information and transferred to the bus network.

Slave response messages use the same structure to send pulse bit information to the MC33664, which is converted and sent back to the MCU as a SPI bit stream.

#### 2 Features and benefits

- 2.0 Mbit/s isolated network communication rate

- Dual SPI architecture for message confirmation

- · Robust conducted and radiated immunity with wake-up

- 3.3 V and 5.0 V compatible logic thresholds

- · Low sleep mode current with automatic bus wake-up

- · Ultra-low radiated emissions

### Isolated network high-speed transceiver

# 3 Applications

- Automotive communication network

- · Industrial communication network

- Utility vehicle battery systems

- Forklift/mining battery systems

- · Battery backup systems

# 4 Ordering information

**Table 1. Ordering information**

| Type number                  | Package |                                                                                           |                       |          |  |  |  |

|------------------------------|---------|-------------------------------------------------------------------------------------------|-----------------------|----------|--|--|--|

|                              | Name    | Description                                                                               | T <sub>amb</sub> [°C] | Version  |  |  |  |

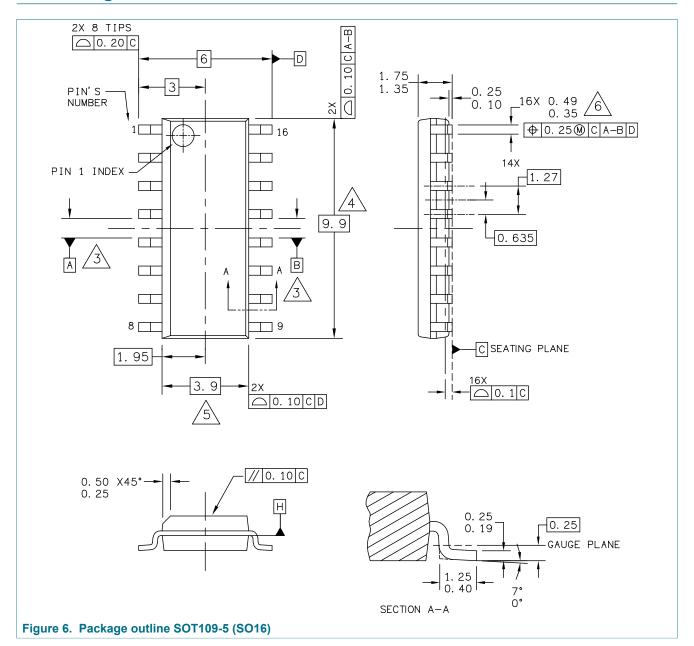

| MC33664ATL1EG <sup>[1]</sup> | SO16    | plastic small outline package; 16 leads;<br>1.27 mm pitch; body 9.9 mm × 3.9 mm × 1.75 mm | -40 to +125           | SOT109-5 |  |  |  |

<sup>[1]</sup> To order parts in tape and reel, add R2 suffix to the part number.

Isolated network high-speed transceiver

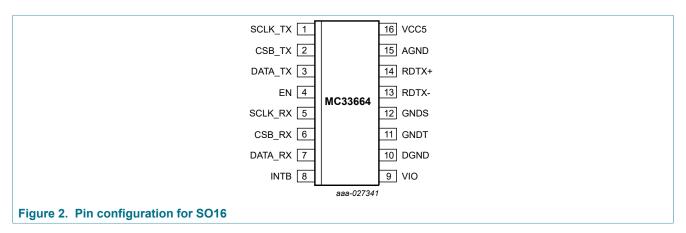

# 5 Pinning information

### 5.1 Pinning

## 5.2 Pin description

Table 2. Pin description

| Symbol  | Pin | Type   | Description                                                                        |

|---------|-----|--------|------------------------------------------------------------------------------------|

| SCLK_TX | 1   | input  | SPI transmit clock from the microcontroller to the MC33664                         |

| CSB_TX  | 2   | input  | SPI transmit chip select from the microcontroller to the MC33664                   |

| DATA_TX | 3   | input  | SPI transmit data from the microcontroller to the MC33664                          |

| EN      | 4   | input  | enable control pin for the MCU to control the MC33664 to Sleep mode or Normal mode |

| SCLK_RX | 5   | output | message receive SPI clock output to the microcontroller                            |

| CSB_RX  | 6   | output | message receive SPI chip select output to the microcontroller                      |

| DATA_RX | 7   | output | message receive SPI data output to the microcontroller                             |

| INTB    | 8   | output | digital interrupt pin used to trigger MCU wake-ups                                 |

| VIO     | 9   | power  | digital 3.3 V/5.0 V power to the IC                                                |

| DGND    | 10  | ground | digital ground                                                                     |

| GNDT    | 11  | ground | terminate to ground                                                                |

| GNDS    | 12  | ground | substrate ground; terminate to ground                                              |

| RDTX-   | 13  | I/O    | transformer communication bi-directional bus                                       |

| RDTX+   | 14  | I/O    | transformer communication bi-directional bus                                       |

| AGND    | 15  | ground | analog ground                                                                      |

| VCC5    | 16  | input  | 5.0 V input supply                                                                 |

Isolated network high-speed transceiver

## 6 Ratings and operating requirements relationship

The operating voltage range pertains to the VCC5 and VIO pins referenced to the AGND and DGND pins.

Table 3. Ratings versus operating requirements

| Fatal range                                                 | Lower limited operating range                                                                                                        | Normal operating range                                                                                                                                | Upper limited operating range                                                                                             | Fatal range                                                                  |  |  |

|-------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|--|--|

| V <sub>PWR</sub> < -0.3 V<br>Permanent failure<br>may occur | $4.5 \text{ V} \leq \text{V}_{\text{CC5}} \leq 4.75 \text{ V}$<br>no permanent failure,<br>but IC functionality is<br>not guaranteed | $4.75 \text{ V} \le \text{V}_{\text{CC5}} \le 5.5 \text{ V}$<br>$3.1 \text{ V} \le \text{V}_{\text{IO}} \le 5.5 \text{ V}$<br><b>100 % functional</b> | $5.5 \text{ V} \le \text{V}_{\text{CC5}} \le 7.0 \text{ V}$<br>$5.5 \text{ V} \le \text{V}_{\text{IO}} \le 7.0 \text{ V}$ | 7.0 V ≤ V <sub>CC5</sub> 7.0 V ≤ V <sub>IO</sub> permanent failure may occur |  |  |

|                                                             | $0 \text{ V} \le \text{V}_{CC5} \le 4.5 \text{ V}$<br>$0 \text{ V} \le \text{V}_{IO} \le 3.1 \text{ V}$<br>reset                     |                                                                                                                                                       |                                                                                                                           |                                                                              |  |  |

|                                                             | handli                                                                                                                               | handling range; no permanent failure                                                                                                                  |                                                                                                                           |                                                                              |  |  |

## 7 Limiting values

#### Table 4. Limiting values

In accordance with the Absolute Maximum Rating System (IEC 60134).

All voltages are respect to reference ground (AGND and DGND) unless otherwise noted. Exceeding these ratings may cause malfunction or permanent damage to the device.

| Symbol                                                            | Parameter                                       | Conditions                |     | Min   | Max                   | Unit |

|-------------------------------------------------------------------|-------------------------------------------------|---------------------------|-----|-------|-----------------------|------|

| V <sub>IO</sub>                                                   | supply input voltage                            |                           |     | -0.3  | +7.0                  | V    |

| V <sub>CC5</sub>                                                  | supply input voltage                            |                           |     | -0.3  | +7.0                  | V    |

| EN                                                                | digital enable pin for Sleep or<br>Normal mode  |                           |     | -0.3  | V <sub>IO</sub> + 0.3 | V    |

| RDTX+,<br>RDTX-                                                   | communication bus                               |                           |     | -10   | +10                   | V    |

| INTB                                                              | interrupt pin                                   |                           |     | -0.3  | V <sub>IO</sub> + 0.3 | V    |

| SCLK_TX,<br>SCLK_RX,<br>CSB_TX,<br>CSB_RX,<br>DATA_TX,<br>DATA_RX | serial peripheral interface communication ports |                           |     | -0.3  | V <sub>IO</sub> + 0.3 | V    |

| V <sub>ESD</sub>                                                  | electrostatic discharge                         | human body model (HBM)    | [1] | ±2000 | -                     | V    |

|                                                                   | voltage                                         | charge device model (CDM) |     | ±500  | -                     | V    |

|                                                                   |                                                 | CDM corner pins           |     | ±750  | -                     | V    |

|                                                                   |                                                 | machine model (MM)        |     | ±200  | -                     | V    |

|                                                                   |                                                 | RDTX+, RDTX-; HBM         |     | ±4000 | -                     | V    |

|                                                                   |                                                 | RDTX+, RDTX-; MM          |     | ±200  | -                     | V    |

<sup>[1]</sup> Electrostatic discharge (ESD) testing is performed in accordance with the HBM ( $C_{ZAP} = 100 \text{ pF}$ ,  $R_{ZAP} = 1500 \Omega$ ).

MC33664\_SDS

All information provided in this document is subject to legal disclaimers.

Isolated network high-speed transceiver

### 8 Thermal characteristics

#### Table 5. Thermal characteristics

|                           | Table 9. Thermal characteristics                          |                    |     |     |      |      |  |

|---------------------------|-----------------------------------------------------------|--------------------|-----|-----|------|------|--|

| Symbol                    | Parameter                                                 | Conditions         |     | Min | Max  | Unit |  |

| T <sub>amb</sub>          | ambient temperature                                       |                    |     | -40 | +125 | °C   |  |

| T <sub>j</sub>            | junction temperature                                      |                    | [1] | -40 | +150 | °C   |  |

| T <sub>stg</sub>          | storage temperature                                       |                    |     | -55 | +150 | °C   |  |

| T <sub>reflow(peak)</sub> | peak reflow temperature                                   | [2                 | [3] | -   | 260  | °C   |  |

| R <sub>th(j-a)</sub>      | thermal resistance from junction to ambient               | single layer (1s)  | [4] | -   | 125  | °C/W |  |

| R <sub>th(j-pcb)</sub>    | thermal resistance from junction to printed-circuit board | multi layer (2s2p) | [5] | -   | 62   | °C/W |  |

- [1] Junction temperature is a function of on-chip power dissipation, package thermal resistance, mounting site (board) temperature, ambient temperature, air flow, power dissipation of other components on the board, and board thermal resistance.

- [2] Pin soldering temperature limit is for 10 seconds maximum duration. Not designed for immersion soldering. Exceeding these limits may cause malfunction or permanent damage to the device.

- [3] Package reflow capability meets Pb-free requirements for JEDEC standard J-STD-020C. For peak package reflow temperature and moisture sensitivity levels (MSL), go to <a href="http://www.nxp.com">http://www.nxp.com</a>, search by part number [e.g. remove prefixes/suffixes and enter the core ID to view all orderable parts (i.e. MC33xxxD enter 33xxx)], and review parametric.

- [4] Per SEMI G38-87 and JEDEC standard JESD51-2 with the single-layer board horizontal.

- [5] Indicates the maximum thermal resistance between the die and the exposed pad surface as measured by the cold plate method (MIL SPEC-883 Method 1012.1) with the cold plate temperature used for the case temperature.

#### 9 Characteristics

#### **Table 6. Characteristics**

Characteristic noted under conditions  $4.75 \text{ V} \le V_{CC5} \le 5.5 \text{ V}$ ,  $3.1 \text{ V} \le V_{IO} \le 5.5 \text{ V}$ ,  $-40 \text{ °C} \le T_{amb} \le 125 \text{ °C}$ , unless otherwise noted. Typical values noted reflect the approximate parameter mean at  $V_{CC5} = 5.0 \text{ V}$ ,  $V_{IO} = 3.3 \text{ V}/5.0 \text{ V}$ ,  $T_{amb} = 25 \text{ °C}$  and device operating under nominal conditions unless otherwise noted.

| Symbol                   | Parameter                        | Conditions                                                       | Min  | Тур | Max  | Unit |

|--------------------------|----------------------------------|------------------------------------------------------------------|------|-----|------|------|

| Power supply VC          | C5                               |                                                                  | '    | '   |      | ·    |

| V <sub>CC5</sub>         | supply voltage                   | fully operational                                                | 4.75 | _   | 5.5  | V    |

|                          |                                  | limited operation                                                | 4.5  | _   | 4.75 | V    |

| IVCC5(NORMAL)            | supply current                   | Normal mode; EN = 1;<br>continuous transmit;<br>$50 \Omega$ load |      | 40  |      | mA   |

|                          |                                  | Normal mode; EN = 1; continuous receive                          |      | 3.0 |      | mA   |

| I <sub>VCC5(SLEEP)</sub> | supply current                   | Sleep mode; EN = 0;<br>INTB = 5.0 V                              |      | 30  |      | μΑ   |

| VCC5 <sub>UV</sub>       | VCC5 undervoltage POR threshold  |                                                                  | 4.0  | _   | 4.5  | V    |

| VCC5 <sub>UV_FLT</sub>   | VCC5 undervoltage POR filter     |                                                                  |      | 2.5 |      | μs   |

| VCC5 <sub>UVHYS</sub>    | VCC5 undervoltage POR hysteresis |                                                                  |      | 100 |      | mV   |

| Power supply VIC         | )                                |                                                                  | '    | 1   |      | '    |

| V <sub>IO</sub>          | supply voltage                   |                                                                  | 3.1  | _   | 5.5  | V    |

| VIO <sub>UV</sub>        | VIO undervoltage POR threshold   |                                                                  | 2.2  | _   | 3.1  | V    |

MC33664\_SDS

All information provided in this document is subject to legal disclaimers.

## Isolated network high-speed transceiver

| Symbol                   | Parameter                                            | Conditions                                            | Min | Тур | Max                   | Unit |

|--------------------------|------------------------------------------------------|-------------------------------------------------------|-----|-----|-----------------------|------|

| VIO <sub>UV_FLT</sub>    | VIO undervoltage POR filter                          |                                                       |     | 2.5 |                       | μs   |

| VIO <sub>UVHYS</sub>     | VIO undervoltage POR hysteresis                      |                                                       |     | 100 |                       | mV   |

| I <sub>VIO(SLEEP)</sub>  | VIO sleep current                                    | EN = 0; INTB = 1                                      | 0.1 | _   | 4.5                   | μA   |

| I <sub>VIO(NORMAL)</sub> | VIO Normal mode current                              | EN = 1;<br>continuous communication;<br>SPI_1 open    |     | 1.0 |                       | mA   |

| Logic transmit EN,       | CSB_TX, SCLK_TX, DATA_TX                             |                                                       |     |     |                       |      |

| V <sub>IH</sub>          | HIGH-level input voltage                             |                                                       | 1.7 | _   | V <sub>IO</sub> + 0.3 | V    |

| V <sub>IL</sub>          | LOW-level input voltage                              |                                                       | _   | _   | 0.95                  | V    |

| V <sub>hys</sub>         | hysteresis voltage                                   |                                                       |     | 150 |                       | mV   |

| $R_{pd}$                 | pull-down resistance                                 | EN, SCLK_TX,<br>DATA_TX                               |     | 100 |                       | kΩ   |

| R <sub>pu</sub>          | pull-up resistance                                   | CSB_TX                                                |     | 100 |                       | kΩ   |

| t <sub>READY</sub>       | Sleep mode to Normal mode                            | EN LOW to HIGH transition to device ready to transmit | _   | _   | 100                   | μs   |

| tINTB_PULSE_DELAY        | EN LOW to HIGH transition to INTB verification pulse |                                                       | _   | _   | 100                   | μs   |

| t <sub>INTB_</sub> PULSE | INTB verification pulse duration                     |                                                       | _   | 100 | _                     | μs   |

| f <sub>SCLK_TX</sub>     | SPI_0 frequency                                      | SCLK_TX                                               |     | 2.0 |                       | MHz  |

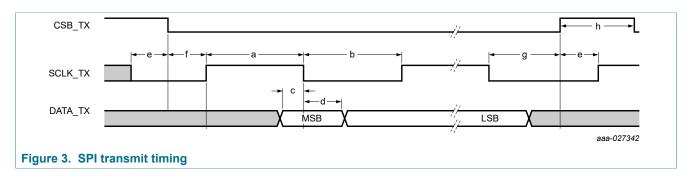

| а                        | SCLK_TX HIGH                                         | see <u>Figure 3</u>                                   |     | 250 |                       | ns   |

| b                        | SCLK_TX LOW                                          | see <u>Figure 3</u>                                   |     | 250 |                       | ns   |

| е                        | SCLK_TX to CSB_TX                                    | see <u>Figure 3</u>                                   | _   | 250 | _                     | ns   |

| L                        | CSB_TX to start of message                           |                                                       | _   | _   | 1.1                   | μs   |

## Isolated network high-speed transceiver

| Symbol                       | Parameter                                                      | Conditions                                            | Min                   | Тур | Max | Unit |

|------------------------------|----------------------------------------------------------------|-------------------------------------------------------|-----------------------|-----|-----|------|

| f                            | falling edge of CSB_TX to rising edge SCLK_TX  CSB_TX SCLK_TX  | see Figure 3                                          | 1.75                  | _   | _   | μs   |

| t <sub>rdtx_dly</sub>        | propagation delay  SCLK_TX  RDTX+ RDTX-                        | SCLK_TX LOW to sine [1] out                           | _                     | 80  | 150 | ns   |

| g                            | SCLK_TX LOW to CSB_TX<br>HIGH                                  | see Figure 3                                          | 600                   | _   | _   | ns   |

| С                            | DATA_TX to SCLK_TX setup                                       | see Figure 3                                          | 40                    | _   | _   | ns   |

| d                            | DATA_TX hold                                                   | see Figure 3                                          | 40                    | _   | _   | ns   |

| t <sub>CSB_TX_HIGH_EOM</sub> | propagation delay  CSB_TX  ——————————————————————————————————— | CSB_TX LOW to HIGH [1] to end of message              | _                     | _   | 150 | ns   |

| t <sub>1</sub>               | CSB_TX wake#up pulse                                           | CSB_TX LOW period                                     |                       | 21  |     | μs   |

| t <sub>2</sub>               | csb_tx                                                         | CSB_TX HIGH period                                    |                       | 600 |     | μs   |

| h                            | time between consecutive transmit messages                     | see Figure 3                                          | 1.0                   | 3.0 | _   | μs   |

| Logic receive pins           | (CSB_RX, SCLK_RX, DATA_R                                       | ()                                                    |                       |     |     | ,    |

| V <sub>OH</sub>              | HIGH-level output voltage                                      | I <sub>OH</sub> = -2.0 mA;<br>V <sub>IO</sub> = 3.1 V | V <sub>IO</sub> - 0.4 | _   | _   | V    |

| V <sub>OL</sub>              | LOW-level output voltage                                       | I <sub>OL</sub> = -2.0 mA;<br>V <sub>IO</sub> = 3.1 V | _                     | _   | 0.4 | V    |

| f <sub>SPI</sub>             | SPI_1 frequency                                                | SCLK_RX                                               |                       | 2.0 |     | MHz  |

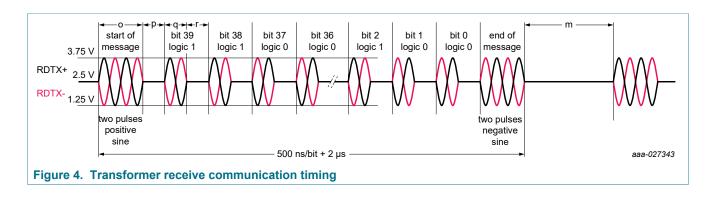

| q                            | pulse frequency                                                | see Figure 4                                          |                       | 4.0 |     | MHz  |

| О                            | start of message                                               | see Figure 4 [1]                                      |                       | 500 |     | ns   |

| а                            | SCLK_RX HIGH                                                   | [1]                                                   |                       | 250 |     | ns   |

| b                            | SCLK_RX LOW                                                    | [1]                                                   |                       | 250 |     | ns   |

## Isolated network high-speed transceiver

| Symbol                     | Parameter                                                          | Conditions                               | Min | Тур        | Max  | Unit     |

|----------------------------|--------------------------------------------------------------------|------------------------------------------|-----|------------|------|----------|

| t <sub>SOM_CSB_RX</sub>    | start of message to CSB_RX  CSB_RX  RDTX+ RDTX-                    | [1]                                      |     | 160        |      | ns       |

| t <sub>EOM_CSB_RX</sub>    | end of message to CSB_RX  CSB_RX  RDTX+ RDTX-                      | [1]                                      |     | 60         |      | ns       |

| tpdb_sclk_data_rx          | pulse data bit to DATA_RX and SCLK_RX  DATA_RX SCLK_RX RDTX+ RDTX- | [1]                                      |     | 280        |      | ns       |

| r<br>p                     | start of message to MSB (receive)                                  | see Figure 4 [1] see Figure 4            | _   | 250<br>600 | _    | ns<br>ns |

| m                          | time between consecutive messages received                         | see Figure 4                             | 1.0 | 3.0        | _    | μs       |

| Bus differential tran      | smitter/receiver                                                   |                                          | I   |            | 1    | J        |

| V <sub>RDTX(PK_DIFF)</sub> | RDTX± differential output voltage                                  | $R_L = 50 \Omega;$<br>$V_{CC5} = 4.75 V$ |     | 2.5        |      | V        |

| I <sub>RDTX</sub>          | RDTX± current limit                                                | sinking/sourcing to 2.5 V                | 65  | _          | 300  | mA       |

| V <sub>RDTX_IN(TH)</sub>   | RDTX± differential receiver                                        | rising edge                              |     | 0.74       |      | V        |

|                            | threshold voltage                                                  | falling edge                             |     | 0.61       | 0.70 | V        |

| V <sub>RDTX_IN_HYST</sub>  | RDTX± differential receiver threshold voltage hysteresis           |                                          |     | 130        |      | mV       |

| V <sub>RDTX_BIAS</sub>     | transformer bias voltage                                           | transmitter in 3-state                   |     | 2.5        |      | V        |

| f <sub>RDTX</sub>          | transmit/receive pulse frequency                                   |                                          |     | 4.0        |      | MHz      |

| Wake-up receiver           | ·                                                                  | 1                                        | 1   | 1          |      | ,        |

| V <sub>RDTXWU_TH</sub>     | RDTX± wake#up differential                                         | rising edge                              |     | 0.6        |      | V        |

| _                          | receiver threshold voltage                                         | falling edge                             |     | 0.6        |      | V        |

| V <sub>RDTXWU_TH_HYS</sub> | RDTX± wake#up differential receiver threshold hysteresis           |                                          |     | 100        |      | mV       |

MC33664\_SDS

All information provided in this document is subject to legal disclaimers.

#### Isolated network high-speed transceiver

| Symbol            | Parameter            | Conditions | Min | Тур | Max | Unit |

|-------------------|----------------------|------------|-----|-----|-----|------|

| $V_{RDTXWU\_FLT}$ | RDTX± wake#up filter |            |     | 50  |     | ns   |

<sup>[1]</sup> All bus network signals to SPI timing are referenced to 0.8 V differential threshold.

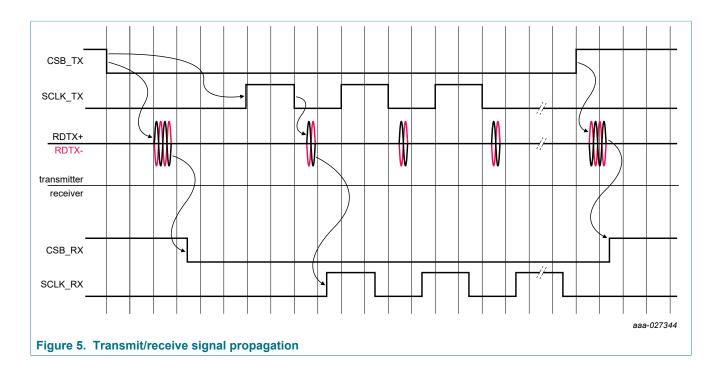

### 9.1 Timing diagrams

## Isolated network high-speed transceiver

Isolated network high-speed transceiver

# 10 Package outline

# 11 Revision history

Table 7. Revision history

| Document ID       | Release date | Data sheet status | Change notice | Supersedes |

|-------------------|--------------|-------------------|---------------|------------|

| MC33664_SDS v.1.0 | 20180523     | Technical data    | _             | _          |

#### Isolated network high-speed transceiver

## 12 Legal information

#### 12.1 Data sheet status

| Document status <sup>[1][2]</sup>       | Product status <sup>[3]</sup> | Definition                                                                                                                                                                                           |

|-----------------------------------------|-------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [short] Data sheet: product preview     | Development                   | This document contains certain information on a product under development. NXP reserves the right to change or discontinue this product without notice.                                              |

| [short] Data sheet: advance information | Qualification                 | This document contains information on a new product. Specifications and information herein are subject to change without notice.                                                                     |

| [short] Data sheet: technical data      | Production                    | This document contains the product specification. NXP Semiconductors reserves the right to change the detail specifications as may be required to permit improvements in the design of its products. |

- [1] Please consult the most recently issued document before initiating or completing a design.

- [2] The term 'short data sheet' is explained in section "Definitions".

- The product status of device(s) described in this document may have changed since this document was published and may differ in case of multiple devices. The latest product status information is available on the Internet at URL <a href="http://www.nxp.com">http://www.nxp.com</a>.

#### 12.2 Definitions

Draft — The document is a draft version only. The content is still under internal review and subject to formal approval, which may result in modifications or additions. NXP Semiconductors does not give any representations or warranties as to the accuracy or completeness of information included herein and shall have no liability for the consequences of use of such information.

Short data sheet — A short data sheet is an extract from a full data sheet with the same product type number(s) and title. A short data sheet is intended for quick reference only and should not be relied upon to contain detailed and full information. For detailed and full information see the relevant full data sheet, which is available on request via the local NXP Semiconductors sales office. In case of any inconsistency or conflict with the short data sheet, the full data sheet shall prevail.

Product specification — The information and data provided in a technical data data sheet shall define the specification of the product as agreed between NXP Semiconductors and its customer, unless NXP Semiconductors and customer have explicitly agreed otherwise in writing. In no event however, shall an agreement be valid in which the NXP Semiconductors product is deemed to offer functions and qualities beyond those described in the technical data data sheet.

#### 12.3 Disclaimers

Limited warranty and liability - Information in this document is believed to be accurate and reliable. However, NXP Semiconductors does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information. NXP Semiconductors takes no responsibility for the content in this document if provided by an information source outside of NXP Semiconductors. In no event shall NXP Semiconductors be liable for any indirect, incidental, punitive, special or consequential damages (including - without limitation - lost profits, lost savings, business interruption, costs related to the removal or replacement of any products or rework charges) whether or not such damages are based on tort (including negligence), warranty, breach of contract or any other legal theory. Notwithstanding any damages that customer might incur for any reason whatsoever, NXP Semiconductors' aggregate and cumulative liability towards customer for the products described herein shall be limited in accordance with the Terms and conditions of commercial sale of NXP Semiconductors.

Right to make changes — NXP Semiconductors reserves the right to make changes to information published in this document, including without

limitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof.

Applications — Applications that are described herein for any of these products are for illustrative purposes only. NXP Semiconductors makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification. Customers are responsible for the design and operation of their applications and products using NXP Semiconductors products, and NXP Semiconductors accepts no liability for any assistance with applications or customer product design. It is customer's sole responsibility to determine whether the NXP Semiconductors product is suitable and fit for the customer's applications and products planned, as well as for the planned application and use of customer's third party customer(s). Customers should provide appropriate design and operating safeguards to minimize the risks associated with their applications and products. NXP Semiconductors does not accept any liability related to any default, damage, costs or problem which is based on any weakness or default in the customer's applications or products, or the application or use by customer's third party customer(s). Customer is responsible for doing all necessary testing for the customer's applications and products using NXP Semiconductors products in order to avoid a default of the applications and the products or of the application or use by customer's third party customer(s). NXP does not accept any liability in this

Limiting values — Stress above one or more limiting values (as defined in the Absolute Maximum Ratings System of IEC 60134) will cause permanent damage to the device. Limiting values are stress ratings only and (proper) operation of the device at these or any other conditions above those given in the Recommended operating conditions section (if present) or the Characteristics sections of this document is not warranted. Constant or repeated exposure to limiting values will permanently and irreversibly affect the quality and reliability of the device.

Terms and conditions of commercial sale — NXP Semiconductors products are sold subject to the general terms and conditions of commercial sale, as published at http://www.nxp.com/profile/terms, unless otherwise agreed in a valid written individual agreement. In case an individual agreement is concluded only the terms and conditions of the respective agreement shall apply. NXP Semiconductors hereby expressly objects to applying the customer's general terms and conditions with regard to the purchase of NXP Semiconductors products by customer.

**No offer to sell or license** — Nothing in this document may be interpreted or construed as an offer to sell products that is open for acceptance or the grant, conveyance or implication of any license under any copyrights, patents or other industrial or intellectual property rights.

**Suitability for use in automotive applications** — This NXP Semiconductors product has been qualified for use in automotive

MC33664 SDS

All information provided in this document is subject to legal disclaimers.

#### Isolated network high-speed transceiver

applications. Unless otherwise agreed in writing, the product is not designed, authorized or warranted to be suitable for use in life support, life-critical or safety-critical systems or equipment, nor in applications where failure or malfunction of an NXP Semiconductors product can reasonably be expected to result in personal injury, death or severe property or environmental damage. NXP Semiconductors and its suppliers accept no liability for inclusion and/or use of NXP Semiconductors products in such equipment or applications and therefore such inclusion and/or use is at the customer's own risk.

**Export control** — This document as well as the item(s) described herein may be subject to export control regulations. Export might require a prior authorization from competent authorities.

**Translations** — A non-English (translated) version of a document is for reference only. The English version shall prevail in case of any discrepancy between the translated and English versions.

#### 12.4 Trademarks

Notice: All referenced brands, product names, service names and trademarks are the property of their respective owners.

$\label{eq:portion} \textbf{POR} - \text{is a trademark of NXP B.V.}$

**SMARTMOS** — is a trademark of NXP B.V.

MC33664\_SDS

All information provided in this document is subject to legal disclaimers.

## Isolated network high-speed transceiver

## **Tables**

| Tab. 1.<br>Tab. 2.<br>Tab. 3. | Ordering information2 Pin description | Tab. 6. | Thermal characteristics                  |

|-------------------------------|---------------------------------------|---------|------------------------------------------|

| Tab. 4.                       | Limiting values4                      |         |                                          |

| Figur                         | res                                   |         |                                          |

| Fig. 1.                       | Typical application circuit1          | Fig. 4. | Transformer receive communication timing |

| Fig. 2.                       | Pin configuration for SO163           | Fig. 5. | Transmit/receive signal propagation10    |

| Fig. 3.                       | SPI transmit timing9                  | Fig. 6. | Package outline SOT109-5 (SO16)1         |

### Isolated network high-speed transceiver

### **Contents**

| 1   | General description                | 1            |  |

|-----|------------------------------------|--------------|--|

| 2   | Features and benefits              | 1            |  |

| 3   | Applications                       |              |  |

| 4   | Ordering information               |              |  |

| 5   | Pinning information                |              |  |

| 5.1 | Pinning                            |              |  |

| 5.2 | Pin description                    |              |  |

| 6   | Ratings and operating requirements |              |  |

|     | relationship                       | 4            |  |

| 7   | Limiting values                    | 4            |  |

| 8   | Thermal characteristics            | 5            |  |

| 9   | Characteristics                    | <del>5</del> |  |

| 9.1 | Timing diagrams                    | g            |  |

| 10  | Package outline                    | 11           |  |

| 11  | Revision history                   | <b>1</b> 1   |  |

| 12  | Legal information                  |              |  |

Please be aware that important notices concerning this document and the product(s) described herein, have been included in section 'Legal information'.

# **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Interface - Specialised category:

Click to view products by NXP manufacturer:

Other Similar products are found below:

CY7C910-51LMB MC33689DPEWR2 MC33975ATEKR2 MEC1632-AUE NVT4555UKZ RKSAS4 HMC677G32 LPC47N207-JV FTP-637DSL633R SM712GX04LF04-BA MC33689DPEW PCA9704PWJ MCW1001A-I/SS HOA6241-001 SC74HC4066ADTR2G AS3935-BQFT NCN5120MNTWG NCN5150DR2G NCN8025MTTBG C100N50Z4A DG407AK/883B SRT2-ATT01 TDA8035HN/C1/S1J LTC1694CS5#TRMPBF TLE9221SXXUMA2 DS90UB947TRGCRQ1 NCS2300MUTAG HMC677LP5E HMC677LP5ETR LTC1756EGN#PBF LTC1955EUH#PBF LT3669EUFD-2#PBF LTC6820HMS#3ZZTRPBF MXL1543BCAI MAX3170CAI+ XL1192D TLE9221SX CP82C59AZ KTU1109EFAA-TR CH368L CH7307C-DEF LTC1694CS5#TRPBF LTC1694IS5#TRM LTS 25-NP 73S8024RN-20IMF 73S8024RN-IL/F 78P2352-IGT/F DS2406+ DS2413P+ DS2413P+T&R