Document Number: MC35XS3500

Rev. 8.0, 8/2013

# Smart Rear Corner Light Switch (Penta 35 mOhm)

The 35XS3500 is designed for low-voltage automotive and industrial lighting applications. Its five low  $R_{DS(ON)}$  MOSFETs (five 35 m $\Omega$ ) can control the high sides of five separate resistive loads (bulbs and LEDs).

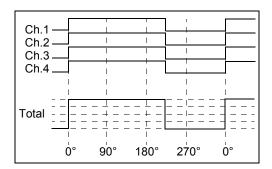

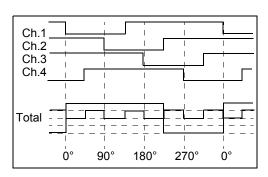

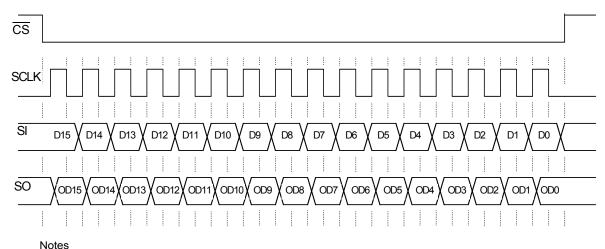

Programming, control and diagnostics are accomplished using a 16-bit SPI interface (3.3 V or 5.0 V). Each output has its own pulsewidth modulation (PWM) control via the SPI. The 35XS3500 has highly sophisticated failure mode handling to provide high availability of the outputs. Its multiphase control and output edge shaping improves electromagnetic compatibility (EMC) behavior.

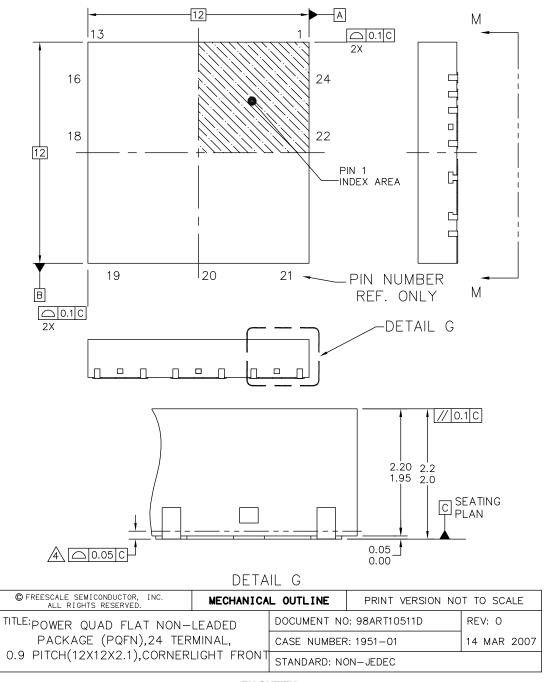

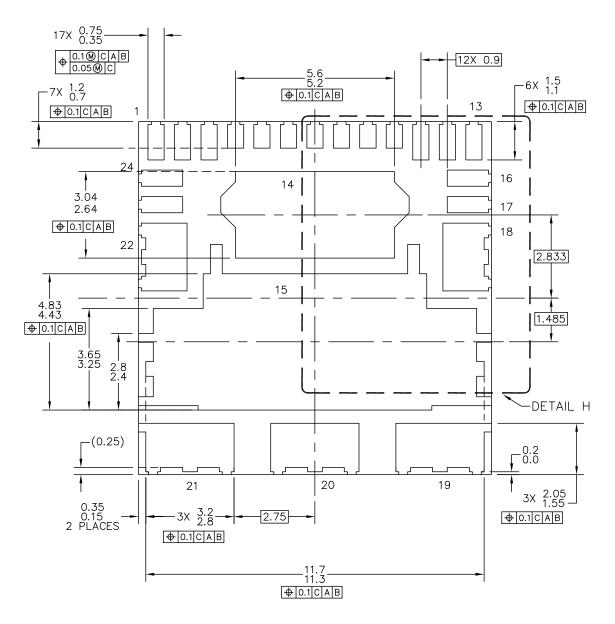

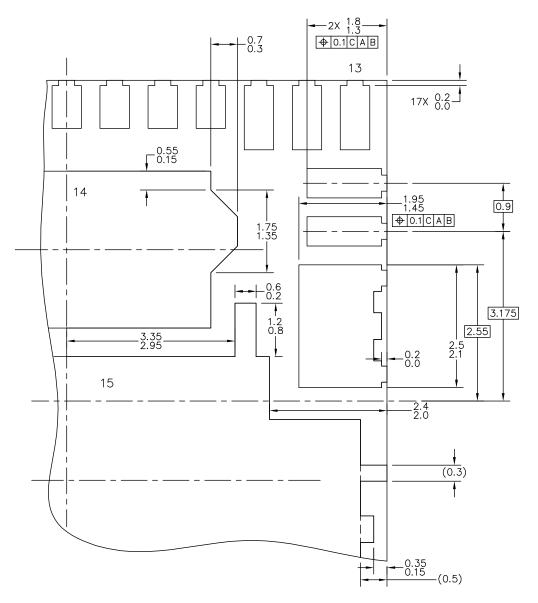

The 35XS3500 is packaged in a power-enhanced 12 x 12 mm nonleaded PQFN package with exposed tabs.

#### **Features**

- Penta 35 m $\Omega$  high side switches

- · 16-bit SPI communication interface with daisy chain capability

- Current sense output with SPI-programmable multiplex switch and board temperature feedback

- · Digital diagnosis feature

- PWM module with multiphase feature including prescaler

- LEDs control including accurate current sensing and low dutycycle capability

- · Fully protected switches

- · Over-current shutdown detection

- · Power net and reverse polarity protection

- · Low-power mode

- Fail-safe mode functions including autorestart feature

- · External smart power switch control including current recopy

## 35XS3500

#### **HIGH SIDE SWITCH**

| ORDERING INFORMATION                                   |                                        |         |  |  |  |

|--------------------------------------------------------|----------------------------------------|---------|--|--|--|

| <b>Device</b><br>(For Tape and Reel,<br>Add R2 Suffix) | Temperature<br>Range (T <sub>A</sub> ) | Package |  |  |  |

| MC35XS3500HFK                                          | -40 to 125 °C                          | 24 PQFN |  |  |  |

| * MC35XS3500DHFK                                       | -40 to 125 C                           | Z4 FQFN |  |  |  |

<sup>\*</sup> Recommended for all new designs

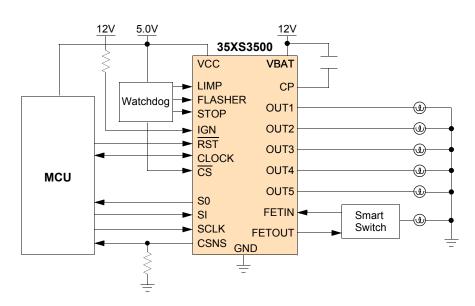

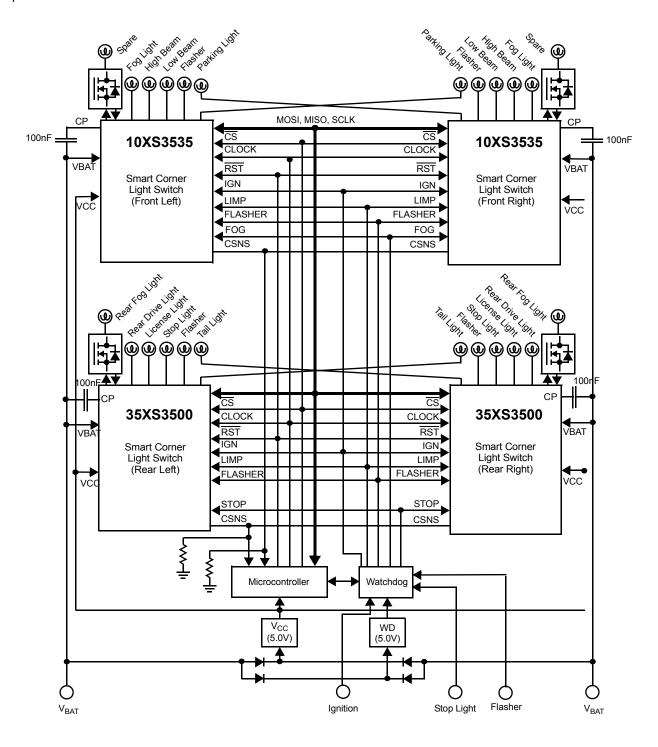

Figure 1. 35XS3500 Simplified Application Diagram

## **DEVICE VARIATIONS**

## Table 1. MC35XS3500 Device Variations

| Part Number    | Package | Temp.         | Comment                                                     |

|----------------|---------|---------------|-------------------------------------------------------------|

| MC35XS3500HFK  |         |               | Initial release                                             |

| MC35XS3500DHFK | 24 PQFN | -40 to 125 °C | D version is more robust against V <sub>BAT</sub> interrupt |

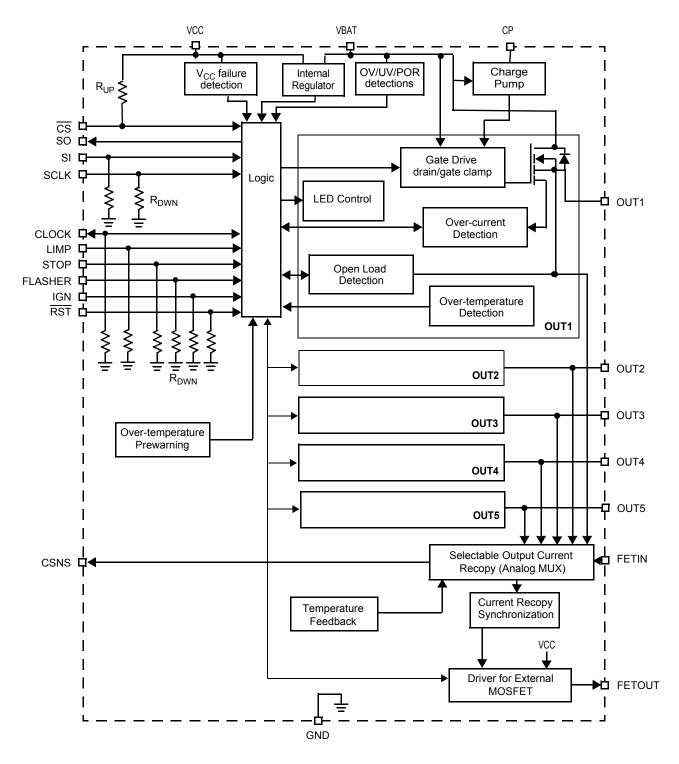

## INTERNAL BLOCK DIAGRAM

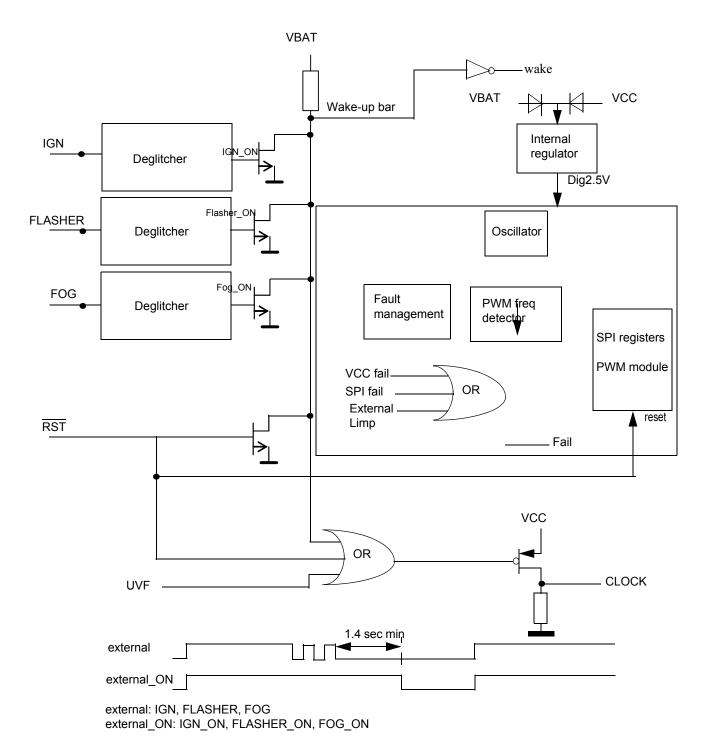

Figure 2. 35XS3500 Simplified Internal Block Diagram

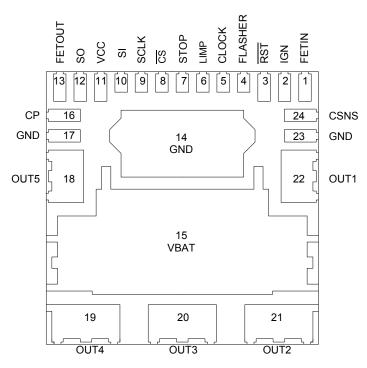

## **PIN CONNECTIONS**

Figure 3. 35XS3500 Pin Connections (Transparent Package Top View)

## Table 2. 35XS3500 Pin Definitions

Functional descriptions these pins can be found in the Functional Description section beginning on page 20.

| Pin | Pin Name | Pin Function | Formal Name                     | Definition                                                                                                                                                                                                                      |

|-----|----------|--------------|---------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | FETIN    | Input        | External FET Input              | This pin is the current sense recopy of the external MOSFET.                                                                                                                                                                    |

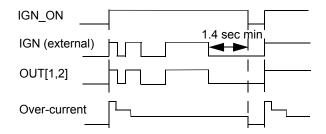

| 2   | IGN      | Input        | Ignition Input<br>(Active High) | This input wakes the device. It also controls outputs 1 and 2 in case of Fail mode activation. This pin has a passive internal pull-down.                                                                                       |

| 3   | RST      | Input        | Reset                           | This input wakes the device. It is also used to initialize the device configuration and fault registers through the SPI. This pin has a passive internal pull-down.                                                             |

| 4   | FLASHER  | Input        | Flasher Input<br>(Active High)  | This input wakes the device. This pin has a passive internal pull-down.                                                                                                                                                         |

| 5   | CLOCK    | Input        | Clock Input                     | This pin state depends on RST logic level.                                                                                                                                                                                      |

|     |          |              |                                 | As long as RST input pin is set to logic [0], this pin is pulled up in order to report wake event. Otherwise, the PWM frequency and timing are generated from this digital clock input by the PWM module.                       |

|     |          |              |                                 | This pin has a passive internal pull-down.                                                                                                                                                                                      |

| 6   | LIMP     | Input        | Limp Home Input (Active High)   | The Fail mode can be activated by this digital input. This pin has an active internal pull-down current source.                                                                                                                 |

| 7   | STOP     | Input        | Stop Light Input (Active High)  | This input wakes the device. This pin has a passive internal pull-down.                                                                                                                                                         |

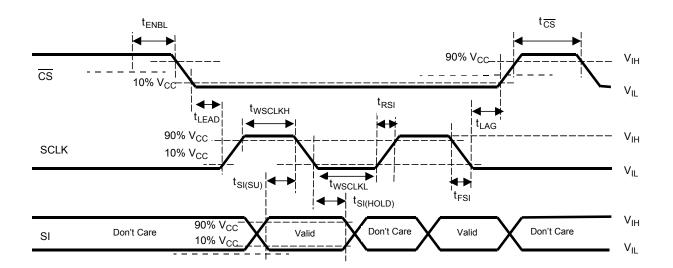

| 8   | CS       | Input        | Chip Select<br>(Active Low)     | When this signal is high, SPI signals are ignored. Asserting this pin low starts a SPI transaction. The transaction is signaled as completed when this signal returns high. This pin has a passive internal pull-up resistance. |

| 9   | SCLK     | Input        | SPI Clock Input                 | This input pin is connected to the master microcontroller providing the required bit shift clock for SPI communication. This pin has a passive internal pull-down resistance.                                                   |

## Table 2. 35XS3500 Pin Definitions (continued)

Functional descriptions these pins can be found in the Functional Description section beginning on page 20.

| Pin                        | Pin Name                             | Pin Function                                   | Formal Name                                              | Definition                                                                                                                                                                                                                                                                                                                                                                          |

|----------------------------|--------------------------------------|------------------------------------------------|----------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 10                         | SI                                   | Input                                          | Master-Out Slave-In                                      | This data input is sampled on the positive edge of the SCLK. This pin has a passive internal pull-down resistance.                                                                                                                                                                                                                                                                  |

| 11                         | VCC                                  | Input                                          | Logic Supply                                             | SPI Logic power supply.                                                                                                                                                                                                                                                                                                                                                             |

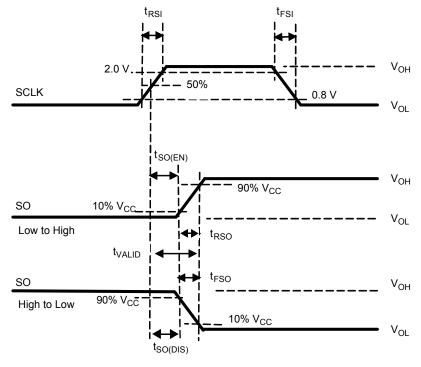

| 12                         | SO                                   | Output                                         | Master-In Slave-Out                                      | SPI data sent to the MCU by this $\underline{\text{pin.}}$ . This data output changes on the negative edge of SCLK, and when $\overline{\text{CS}}$ is high. This $\underline{\text{pin}}$ is high-impedance.                                                                                                                                                                       |

| 13                         | FETOUT                               | Output                                         | External FET Gate                                        | This pin controls an external SMART MOSFET by logic level. This output called OUT6.                                                                                                                                                                                                                                                                                                 |

|                            |                                      |                                                |                                                          | If OUT6 is not used in the application, this output pin is set to logic high when the current sense output becomes valid when CSNS sync SPI bit is set to logic [1].                                                                                                                                                                                                                |

| 14, 17, 23                 | GND                                  | Ground                                         | Ground                                                   | This pin is the ground for the logic and analog circuitry of the device. (1)                                                                                                                                                                                                                                                                                                        |

| 15                         | VBAT                                 | Input                                          | Battery Input                                            | Power supply pin.                                                                                                                                                                                                                                                                                                                                                                   |

| 16                         | CP                                   | Output                                         | Charge Pump                                              | This pin is the connection for an external tank capacitor (for internal use only).                                                                                                                                                                                                                                                                                                  |

| 18<br>19<br>20<br>21<br>22 | OUT5<br>OUT4<br>OUT3<br>OUT2<br>OUT1 | Output<br>Output<br>Output<br>Output<br>Output | Output 5<br>Output 4<br>Output 3<br>Output 2<br>Output 1 | Protected 35 m $\Omega$ high side power output to the load.                                                                                                                                                                                                                                                                                                                         |

| 24                         | CSNS                                 | Output                                         | Current Sense Output                                     | This pin is used to output a current proportional to OUT1:OUT5, FETin current, and it is used externally to generate a ground-referenced voltage for the microcontroller to monitor output current. Moreover, this pin can report a voltage proportional to the temperature on the GND flag.  OUT1:OUT5, FETin current sensing and Temperature feedback choice is SPI programmable. |

#### Notes

1. The pins 14, 17, and 23 must be shorted on the board.

## **ELECTRICAL CHARACTERISTICS**

## **MAXIMUM RATINGS**

#### **Table 3. Maximum Ratings**

All voltages are with respect to ground unless otherwise noted. Exceeding these ratings may cause a malfunction or permanent damage to the device.

| Rating                                                                                                                                                               | Symbol             | Value                          | Unit |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|--------------------------------|------|

| ELECTRICAL RATINGS                                                                                                                                                   | <u> </u>           |                                |      |

| Over-voltage Test Range Maximum Operation Voltage Load Dump (400 ms) at 25 °C                                                                                        | V <sub>BAT</sub>   | 28<br>40                       | V    |

| Reverse Polarity Voltage Range 2.0 Min at 25 °C                                                                                                                      | V <sub>BAT</sub>   | -18                            | V    |

| VCC Supply Voltage                                                                                                                                                   | V <sub>CC</sub>    | -0.3 to 5.5                    | V    |

| Output Voltage Positive Negative (ground disconnected)                                                                                                               | V <sub>OUT</sub>   | 40<br>-16                      | V    |

| Digital Input Current in Clamping Mode (SI, SCLK, CS, IGN, FLASHER, STOP, LIMP)                                                                                      | I <sub>IN</sub>    | ±1.0                           | mA   |

| FETIN Input Current                                                                                                                                                  | I <sub>FETIN</sub> | +10<br>-1.0                    | mA   |

| SO and FETOUT Output Voltage                                                                                                                                         | V <sub>SO</sub>    | -0.3 to V <sub>CC</sub> +0.3   | V    |

| Outputs clamp energy using single pulse method (L = 2.0 mH; R = 0 $\Omega$ ; VBAT = 14 V at 150 °C initial)                                                          | E                  | 30                             | mJ   |

| ESD Voltage <sup>(2)</sup> Human Body Model (HBM) OUT[1:5], VPWR, and GND Charge Device Model (CDM) Corner Pins (1,13,19,21) All Other Pins (2-12, 14-18, 20, 22-24) | V <sub>ESD</sub>   | ±2000<br>±8000<br>±750<br>±500 | V    |

| THERMAL RATINGS                                                                                                                                                      | ·                  |                                | •    |

| Operating Temperature Ambient Junction                                                                                                                               | T <sub>A</sub>     | -40 to 125<br>-40 to 150       | °C   |

| Peak Package Reflow Temperature During Reflow <sup>(3), (4)</sup>                                                                                                    | T <sub>PPRT</sub>  | Note 4                         | °C   |

| Storage Temperature                                                                                                                                                  | T <sub>STG</sub>   | -55 to 150                     | °C   |

| THERMAL RESISTANCE                                                                                                                                                   | l .                |                                | l    |

| Thermal Resistance, Junction to Case <sup>(5)</sup>                                                                                                                  | $R_{	heta JC}$     | 1.0                            | °C/W |

|                                                                                                                                                                      |                    |                                |      |

#### Notes

- 2. ESD testing is performed in accordance with the Human Body Model (HBM) (C<sub>ZAP</sub> = 100 pF, R<sub>ZAP</sub> = 1500 Ω) and the Charge Device Model

- 3. Pin soldering temperature limit is for 40 seconds maximum duration. Not designed for immersion soldering. Exceeding these limits may cause malfunction or permanent damage to the device.

- 4. Freescale's Package Reflow capability meets Pb-free requirements for JEDEC standard J-STD-020C. For Peak Package Reflow Temperature and Moisture Sensitivity Levels (MSL), Go to www.freescale.com, search by part number [e.g. remove prefixes/suffixes and enter the core ID to view all orderable parts. (i.e. MC33xxxD enter 33xxx), and review parametrics.

- 5. Typical value is guaranteed per design.

## STATIC ELECTRICAL CHARACTERISTICS

## **Table 4. Static Electrical Characteristics**

Characteristics noted under conditions 3.0 V  $\leq$  V<sub>CC</sub>  $\leq$  5.5 V, 7.0 V  $\leq$  V<sub>BAT</sub>  $\leq$  20 V, -40 °C  $\leq$  T<sub>A</sub>  $\leq$  125 °C, unless otherwise noted. Typical values noted reflect the approximate parameter mean at T<sub>A</sub> = 25 °C under nominal conditions, unless otherwise noted.

| Characteristic                                                                      | Symbol                   | Min  | Тур | Max  | Unit |

|-------------------------------------------------------------------------------------|--------------------------|------|-----|------|------|

| POWER INPUT (VBAT, VCC)                                                             |                          |      |     |      |      |

| Battery Supply Voltage Range                                                        | $V_{BAT}$                |      |     |      | V    |

| Full Performance and Short-circuit                                                  |                          | 7.0  | -   | 20   |      |

| Extended Voltage Range <sup>(6)</sup>                                               |                          | 6.0  | _   | 28   |      |

| Battery Supply Under-voltage (UV flag is set ON)                                    | V <sub>BATUV</sub>       | 5.0  | 5.5 | 6.0  | V    |

| Battery Voltage Clamp (OV flag is set ON)                                           | V <sub>BATCLAMP_OV</sub> | 27.5 | 30  | 32.5 | V    |

| Battery Voltage Clamp                                                               | V <sub>BATCLAMP</sub>    | 40   | _   | 48   | V    |

| Battery Supply Power on Reset <sup>(9)</sup>                                        |                          |      |     |      | V    |

| If $V_{BAT}$ < 5.5 V, $V_{BAT}$ = $V_{CC}$                                          | V <sub>BATPOR1</sub>     | 2.0  | _   | 3.0  |      |

| If $V_{BAT} < 5.5 V$ , $V_{BAT} = 0$                                                | V <sub>BATPOR2</sub>     | 2.0  | _   | 4.0  |      |

| VBAT Supply Current at 25 °C and V <sub>BAT</sub> =12 V and V <sub>CC</sub> = 5.0 V |                          |      |     |      |      |

| Sleep State Current, Outputs Open                                                   | I <sub>BATSLEEP1</sub>   | _    | 0.5 | 5.0  | μА   |

| Sleep State Current, Outputs Grounded                                               | I <sub>BATSLEEP2</sub>   | -    | 0.5 | 5.0  | μΑ   |

| Normal Mode, IGN = 5.0 V, RST = 5.0 V, Outputs Open                                 | I <sub>BAT</sub>         | _    | 10  | 20   | mA   |

| Digital Voltage Range, Full Performance                                             | V <sub>CC</sub>          | 3.0  | _   | 5.5  | V    |

| Digital Supply Under-voltage (V <sub>CC</sub> Failure)                              | V <sub>CCUV</sub>        | 2.2  | 2.5 | 2.8  | V    |

| Sleep Current Consumption on V <sub>CC</sub> at 25 °C and V <sub>BAT</sub> = 12 V   | I <sub>CCSLEEP</sub>     |      |     |      | μА   |

| Output OFF                                                                          |                          | _    | 0.2 | 5.0  |      |

| Supply Current Consumption on V <sub>CC</sub> and V <sub>BAT</sub> = 12 V           | I <sub>CC</sub>          |      |     |      | mA   |

| No SPI                                                                              |                          | _    | _   | 2.6  |      |

| 3.0 MHz SPI Communication                                                           |                          |      | _   | 5.0  |      |

## LOGIC INPUT/OUTPUT (IGN, CS, CSNS, SI, SCLK, CLOCK, SO, FLASHER, RST, LIMP, STOP)

| Input High Logic Level <sup>(7)</sup>                                                                                     | V <sub>IH</sub>     | 2.0  | _    | _    | V               |

|---------------------------------------------------------------------------------------------------------------------------|---------------------|------|------|------|-----------------|

| Input Low Logic Level <sup>(7)</sup>                                                                                      | V <sub>IL</sub>     | _    | _    | 0.8  | V               |

| Ignition Threshold Level (IGN, FLASHER, STOP and RST)                                                                     | V <sub>IGNTH</sub>  | 1.0  |      | 2.2  | V               |

| Input Clamp Voltage (IGN, FLASHER, LIMP, STOP, $\overline{\text{CS}}$ , SCLK, SI, $\overline{\text{RST}}$ )  I = 1.0 mA   | V <sub>CL_POS</sub> | 7.5  | _    | 13   | V               |

| Input Forward Voltage (IGN, FLASHER, LIMP, STOP, $\overline{\text{CS}}$ , SCLK, SI, $\overline{\text{RST}}$ )  I = 1.0 mA | V <sub>CL_NEG</sub> | -2.0 | _    | -0.3 | V               |

| Input Passive Pull-up Resistance on $\overline{\text{CS}}$ pin <sup>(8)</sup>                                             | R <sub>UP</sub>     | 100  | 200  | 400  | kΩ              |

| Input Passive Pull-down Resistance on SI, SCLK, FLASHER, IGN, FOG, CLOCK, LIMP and RST pins <sup>(8)</sup>                | R <sub>DWN</sub>    | 100  | 200  | 500  | kΩ              |

| SO High-state Output Voltage                                                                                              | V <sub>SOH</sub>    |      |      |      | V <sub>CC</sub> |

| I <sub>OH</sub> = 1.0 mA                                                                                                  |                     | 8.0  | 0.95 | ı    |                 |

| CLOCK Output Voltage reporting wake-up event (I <sub>CLOCK</sub> =1.0 mA)                                                 | V <sub>CLOCKH</sub> | 0.8  | 0.95 | _    | V <sub>CC</sub> |

#### Notes

- 6. In extended mode, the functionality is guaranteed but not the electrical parameters.

- 7. Valid for RST, SI, SCLK, CLOCK, FLASHER, STOP, and LIMP pins.

- 8. Valid for the following input voltage range: VCC = -0.3 to +0.3 V.

- 9. Please refer to Loss of VBAT section for more details.

Characteristics noted under conditions 3.0 V  $\leq$  V<sub>CC</sub>  $\leq$  5.5 V, 7.0 V  $\leq$  V<sub>BAT</sub>  $\leq$  20 V, -40 °C  $\leq$  T<sub>A</sub>  $\leq$  125 °C, unless otherwise noted. Typical values noted reflect the approximate parameter mean at T<sub>A</sub> = 25 °C under nominal conditions, unless otherwise noted.

| Characteristic                                                                                | Symbol                            | Min        | Тур   | Max      | Unit |

|-----------------------------------------------------------------------------------------------|-----------------------------------|------------|-------|----------|------|

| LOGIC INPUT/OUTPUT (IGN, CS, CSNS, SI, SCLK, CLOCK, SO, FLASHEI                               | R, RST, LIMP, ST                  | OP) (CONTI | NUED) |          | •    |

| SO Low-state Output Voltage                                                                   | $V_{SOL}$                         |            |       |          | V    |

| $I_{OL} = -1.6 \text{ mA}$                                                                    |                                   | _          | 0.2   | 0.4      |      |

| SO Tri-state Leakage Current                                                                  | I <sub>SOLEAK</sub>               |            |       |          | μΑ   |

| CS ≥ 0.7 V <sub>CC</sub>                                                                      |                                   | -1.0       | 0.0   | 1.0      |      |

| CSNS Tri-state Leakage Current                                                                | I <sub>CSNSLEAK</sub>             |            |       |          | μΑ   |

| VCC = 5.5 V, CSNS = 4.5 V                                                                     |                                   | -5.0       | 0.0   | 1.0      |      |

| VCC = 5.0 V, CSNS = 5.5 V                                                                     |                                   | -10        | 0.0   | 1.0      |      |

| VCC = 5.0 V, CSNS = 3.0 V                                                                     |                                   | -1.0       | 0.0   | 1.0      |      |

| Current Sense Output Clamp Voltage                                                            | V <sub>CSNS</sub>                 | 5.0        | 6.0   | 7.0      | V    |

| I <sub>CSNS</sub> < 10.0 mA                                                                   |                                   |            |       |          |      |

| OUTPUT (OUT 1:5)                                                                              |                                   | 1          |       |          |      |

| Output Leakage Current in OFF state                                                           | I <sub>OUTLEAK</sub>              |            |       |          | μА   |

| Sleep mode, Outputs Grounded                                                                  |                                   | _          | 0     | 2.0      |      |

| Normal mode, Outputs Grounded                                                                 |                                   | _          | 20    | 25       |      |

| Output Negative Clamp Voltage                                                                 | V <sub>OUT</sub>                  |            |       |          | V    |

| I <sub>OUT</sub> = -500 mA, Outputs OFF                                                       |                                   | -22        | _     | -16      |      |

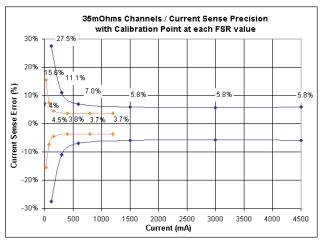

| Current Sense Output Precision <sup>(10)</sup>                                                | δl <sub>CS</sub> /l <sub>CS</sub> |            |       |          | %    |

| Full-Scale Range (FSR) for LED Control bit = 0                                                |                                   |            |       |          |      |

| 0.75 FSR                                                                                      |                                   | -14        | -     | 14       |      |

| 0.50 FSR                                                                                      |                                   | -15<br>-17 | -     | 15       |      |

| 0.25 FSR<br>0.10 FSR                                                                          |                                   | -17<br>-22 | _     | 17<br>22 |      |

| Full-Scale Range (FSR) for LED Control bit = 1                                                |                                   |            |       |          |      |

| 0.187 FSR = 0.75 FSR <sub>I FD</sub>                                                          |                                   | -13        | _     | 13       |      |

| 0.125 FSR = 0.50 FSR <sub>LED</sub>                                                           |                                   | -13        | _     | 13       |      |

| 0.062 FSR = 0.25 FSR <sub>LED</sub>                                                           |                                   | -20        | -     | 20       |      |

| 0.025 FSR = 0.10 FSR <sub>LED</sub>                                                           |                                   | -30        | -     | 30       |      |

| Current Sense Output Precision                                                                |                                   |            |       |          | %    |

| Over-temperature Range [-40;125 °C], V <sub>BAT</sub> Range [10 V-16 V] and FSR               |                                   | -6.0       | -     | 6.0      |      |

| Range [25%-100%], calculated with one calibration point (Taken at 25 °C,                      |                                   |            |       |          |      |

| VBAT = 13.5 V and 50% FSR) <sup>(12)</sup>                                                    |                                   |            |       |          |      |

| Current Sense Output Precision with one calibration point (50% FSR <sub>LED</sub> ,           |                                   | -6.0       | _     | 6.0      | %    |

| $V_{BAT} = 13.5 \text{ at } 25 ^{\circ}\text{C}^{(12)}$                                       |                                   |            |       |          |      |

| Temperature Drift of Current Sense Output <sup>(11)</sup>                                     | ΔI <sub>CS</sub> /ΔΤ              |            |       |          | ppm/ |

| V <sub>BAT</sub> = 13.5 V, I <sub>OUT</sub> = 2.8 A reference taken at T <sub>A</sub> = 25 °C |                                   | _          | ±280  | ±400     | °C   |

#### Notes

- 10. 10 V <  $V_{BAT}$  < 16 V. ( $\delta I_{CS}/I_{CS}$  = (measured  $I_{CS}$  targeted  $I_{CS}$ )/ targeted  $I_{CS}$  with targeted  $I_{CS}$  = 5.0 mA

- 11. Based on statistical data. Not production tested.  $\Delta I_{CS}/\Delta T = [(measured at I_{CS} at T_1 measured at I_{CS} at T_2) measured at I_{CS} at room]/(T_1 T_2)$

- 12. Based on statistical analysis covering 99.74% of parts.

Characteristics noted under conditions 3.0 V  $\leq$  V<sub>CC</sub>  $\leq$  5.5 V, 7.0 V  $\leq$  V<sub>BAT</sub>  $\leq$  20 V, -40 °C  $\leq$  T<sub>A</sub>  $\leq$  125 °C, unless otherwise noted. Typical values noted reflect the approximate parameter mean at T<sub>A</sub> = 25 °C under nominal conditions, unless otherwise noted.

| ,, ,, ,, ,, ,, ,, ,, ,, ,, ,, ,, ,, ,,                                                                                                                                             |                               |                              |                              |                              |           |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|------------------------------|------------------------------|------------------------------|-----------|--|

| Characteristic                                                                                                                                                                     | Symbol                        | Min                          | Тур                          | Max                          | Unit      |  |

| OUTPUT (OUT 1:5) (CONTINUED)                                                                                                                                                       |                               |                              |                              |                              |           |  |

| Minimum Output Current Reported in CSNS for OUT[1-5] <sup>(13)</sup><br>10 V $\leq$ VBAT $\leq$ 16 V                                                                               | I <sub>35MIN(CSNS)</sub>      | 65                           | -                            | _                            | mA        |  |

| Minimum Output Current Reported in CSNS for OUT[1-5] in LED Mode $^{(13)}$ 10 V $\leq$ VBAT $\leq$ 16 V                                                                            | I <sub>35MIN</sub> (CSNS) LED | 40                           | _                            | _                            | mA        |  |

| Over-temperature Shutdown                                                                                                                                                          | T <sub>OTS</sub>              | 155                          | 175                          | 195                          | °C        |  |

| Thermal Prewarning <sup>(14)</sup>                                                                                                                                                 | T <sub>OTSWARN</sub>          | 110                          | 125                          | 140                          | °C        |  |

| Output Voltage Threshold                                                                                                                                                           | V <sub>OUT_TH</sub>           | 0.475                        | 0.5                          | 0.525                        | $V_{BAT}$ |  |

| TAIL LIGHT (OUT1)                                                                                                                                                                  |                               |                              |                              |                              |           |  |

| Output Drain-to-Source ON Resistance ( $I_{OUT}$ = 2.8 A, $T_A$ = 25 °C) $V_{BAT}$ = 13.5 V $V_{BAT}$ = 7.0 V                                                                      | R <sub>DS(ON)</sub>           | -<br>-                       | -<br>-                       |                              | mΩ        |  |

| Output Drain-to-Source ON Resistance ( $I_{OUT}$ = 2.8 A, $V_{BAT}$ = 13.5 V, $T_A$ = 150 °C) <sup>(14)</sup>                                                                      | R <sub>DS(ON)</sub>           | _                            | -                            | 59.5                         | mΩ        |  |

| Reverse Output ON Resistance (I <sub>OUT</sub> = -2.8 A, V <sub>BAT</sub> = -12 V, T <sub>A</sub> = 25 °C) <sup>(15)</sup>                                                         | R <sub>SD(ON)</sub>           | -                            | _                            | 70                           | mΩ        |  |

| TAIL LIGHT (OUT1)                                                                                                                                                                  |                               |                              |                              | L                            |           |  |

| Output Drain-to-Source ON Resistance ( $I_{OUT}$ = 1.5 A, $T_A$ = 25 °C) for LED Control = 1 $V_{BAT}$ = 13.5 V $V_{BAT}$ = 7.0 V                                                  | R <sub>DS(ON)25</sub> _LED    | -<br>-                       | -<br>-                       | -                            | mΩ        |  |

| Output Drain-to-Source ON Resistance ( $I_{OUT} = 1.5 \text{ A}$ , $V_{BAT} = 13.5 \text{ V}$ , $T_A = 150  ^{\circ}\text{C}$ ) for LED Control = 1                                | R <sub>DS(ON)150_LED</sub>    | -                            | -                            | 119                          | mΩ        |  |

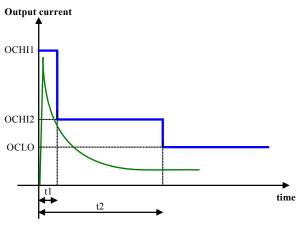

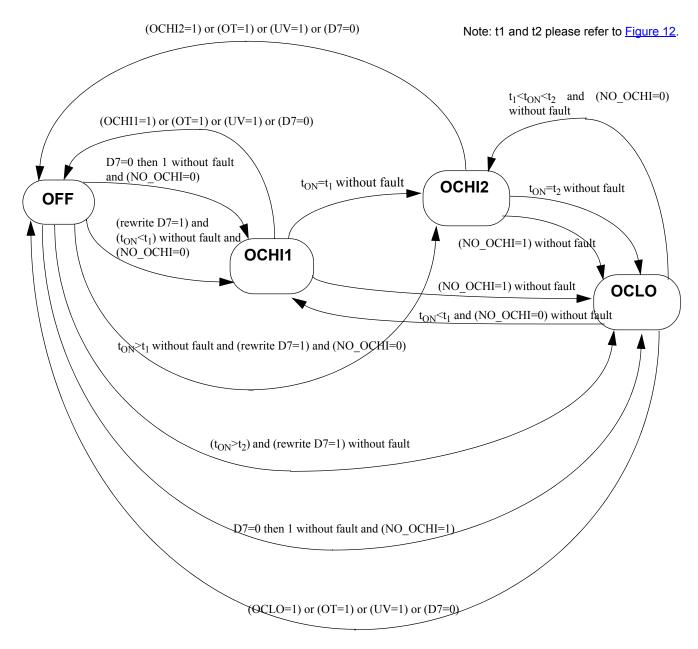

| High Over-current Shutdown Threshold 1 $V_{BAT} = 16 \text{ V}, T_A = -40 \text{ °C}$ $V_{BAT} = 16 \text{ V}, T_A = 25 \text{ °C}$ $V_{BAT} = 16 \text{ V}, T_A = 125 \text{ °C}$ | I <sub>OCHI1</sub>            | 28.0<br>30.2<br>29.4<br>28.3 | 35.0<br>36.0<br>35.0<br>33.8 | 43.5<br>41.8<br>40.6<br>39.3 | А         |  |

| High Over-current Shutdown Threshold 2                                                                                                                                             | I <sub>OCHI2</sub>            | 12.3                         | 15.4                         | 18.5                         | Α         |  |

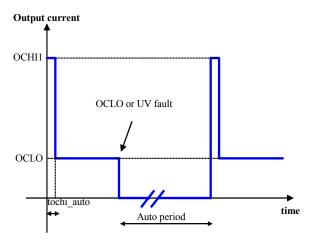

| Low Over-current Shutdown Threshold                                                                                                                                                | l <sub>OCLO</sub>             | 5.7                          | 7.2                          | 8.9                          | Α         |  |

| Open Load Current Threshold in ON State <sup>(16)</sup>                                                                                                                            | I <sub>OL</sub>               | 0.05                         | 0.2                          | 0.5                          | Α         |  |

| Open Load Current Threshold in ON State with LED <sup>(17)</sup> $V_{OL} = V_{BAT} - 0.5 \text{ V}$                                                                                | IOLLED                        | 4.0                          | 10                           | 20                           | mA        |  |

| Current Sense Full-scale Range <sup>(18)</sup>                                                                                                                                     | I <sub>CS FSR</sub>           | _                            | 6.0                          | -                            | Α         |  |

#### Notes

- 13. Output current value computed after leakage current removal (open load condition)

- 14. Parameter guaranteed by design; however it is not production tested.

- 15. Source-to-Drain ON Resistance (Reverse Drain-to-Source ON Resistance) with negative polarity V<sub>BAT</sub>.

- 16. OLLED1, bit D0 in SI data is set to [0]

- 17. OLLED1, bit D0 in SI data is set to [1]

- 18. For a typical value of I<sub>CS FSR,</sub> I<sub>CSNS</sub> = 5.0 mA. If the range is exceeded, no current clamp and the precision is not guaranteed.

Characteristics noted under conditions 3.0 V  $\leq$  V<sub>CC</sub>  $\leq$  5.5 V, 7.0 V  $\leq$  V<sub>BAT</sub>  $\leq$  20 V, -40 °C  $\leq$  T<sub>A</sub>  $\leq$  125 °C, unless otherwise noted. Typical values noted reflect the approximate parameter mean at T<sub>A</sub> = 25 °C under nominal conditions, unless otherwise noted.

| Characteristic                                                                                                            | Symbol                     | Min  | Тур  | Max  | Unit |

|---------------------------------------------------------------------------------------------------------------------------|----------------------------|------|------|------|------|

| TAIL LIGHT (OUT1) (CONTINUED)                                                                                             |                            |      |      |      |      |

| Current Sense Full-scale Range (19) depending on LED Control = 1                                                          | I <sub>CS FSR_LED</sub>    | _    | 1.6  | _    | Α    |

| Severe Short-circuit Impedance Range (19)                                                                                 | R <sub>SC1(OUT1)</sub>     | 350  | _    | _    | mΩ   |

| LICENSE LIGHT (OUT2)                                                                                                      |                            |      |      |      | •    |

| Output Drain-to-Source ON Resistance (I <sub>OUT</sub> = 2.8 A, T <sub>A</sub> = 25 °C)                                   | R <sub>DS(ON)</sub>        |      |      |      | mΩ   |

| V <sub>BAT</sub> = 13.5 V                                                                                                 |                            | -    | _    | 35   |      |

| V <sub>BAT</sub> = 7.0 V                                                                                                  |                            | _    | _    | 55   |      |

| Output Drain-to-Source ON Resistance (I <sub>OUT</sub> = -2.8 A, V <sub>BAT</sub> = -13.5 V,                              | R <sub>DS(ON)</sub>        |      |      |      | mΩ   |

| $T_A = 25 ^{\circ}\text{C})^{(20)}$                                                                                       |                            | -    | _    | 59.5 |      |

| Reverse Output ON Resistance (I <sub>OUT</sub> = 2.8 A, V <sub>BAT</sub> = 12 V, T <sub>A</sub> = 150 °C) <sup>(21)</sup> | R <sub>SD(ON)</sub>        | -    | _    | 70   | mΩ   |

| Output Drain-to-Source ON Resistance (I <sub>OUT</sub> =1.5 A, T <sub>A</sub> = 25 °C) for LED                            | R <sub>DS(ON)25_LED</sub>  |      |      |      | mΩ   |

| Control = 1                                                                                                               |                            | -    | _    | 70   |      |

| $V_{BAT}$ = 13.5 V                                                                                                        |                            | _    | _    | 110  |      |

| $V_{BAT} = 7.0 \text{ V}$                                                                                                 |                            |      |      |      |      |

| Output Drain-to-Source ON Resistance (I <sub>OUT</sub> = 1.5 A, V <sub>BAT</sub> = 13.5 V,                                | R <sub>DS(ON)150_LED</sub> |      |      |      | mΩ   |

| T <sub>A</sub> = 150 °C) for LED Control = 1                                                                              |                            | -    | _    | 119  |      |

| High Over-current Shutdown Threshold 1                                                                                    | I <sub>OCHI1</sub>         | 28.0 | 35.0 | 43.5 | Α    |

| $V_{BAT} = 16 \text{ V}, T_A = -40 ^{\circ}\text{C}$                                                                      |                            | 30.2 | 36.0 | 41.8 |      |

| $V_{BAT} = 16 \text{ V}, T_A = 25 \text{ °C}$                                                                             |                            | 29.4 | 35.0 | 40.6 |      |

| V <sub>BAT =</sub> 16 V, T <sub>A</sub> = 125 °C                                                                          |                            | 28.3 | 33.8 | 39.3 |      |

| High Over-current Shutdown Threshold 2                                                                                    | I <sub>OCHI2</sub>         | 12.3 | 15.4 | 18.5 | Α    |

| Low Over-current Shutdown Threshold                                                                                       | l <sub>OCLO</sub>          | 5.7  | 7.2  | 8.9  | Α    |

| Open Load Current Threshold in ON State <sup>(22)</sup>                                                                   | l <sub>OL</sub>            | 0.05 | 0.2  | 0.5  | Α    |

| Open Load Current Threshold in ON State with LED <sup>(23)</sup>                                                          | I <sub>OLLED</sub>         |      |      |      | mA   |

| $V_{OL} = V_{BAT} - 0.5 V$                                                                                                |                            | 4.0  | 10   | 20   |      |

| Current Sense Full-Scale Range <sup>(24)</sup>                                                                            | I <sub>CS FSR</sub>        | -    | 6.0  | _    | Α    |

| Current Sense Full-Scale Range <sup>(20)</sup> depending on LED Control = 1                                               | I <sub>CS FSR_LED</sub>    | -    | 1.6  | _    | Α    |

| Severe short-circuit impedance range <sup>(20)</sup>                                                                      | R <sub>SC1(OUT2)</sub>     | 350  | _    | -    | mΩ   |

|                                                                                                                           |                            |      |      |      | •    |

- 19. Output current value computed after leakage current removal (open load condition)

- 20. Parameter guaranteed by design; however, it is not production tested.

- $21. \quad \text{Source-to-Drain ON Resistance (Reverse Drain-to-Source ON Resistance) with negative polarity $V_{BAT}$. }$

- 22. OLLED2, bit D0 in SI data is set to [0]

- 23. OLLED2, bit D0 in SI data is set to [1]

- 24. For typical value of  $I_{CS\ FSR}$ ,  $I_{CSNS}$  = 5.0 mA. If the range is exceeded, no current clamp and the precision is not guaranteed.

Characteristics noted under conditions 3.0 V  $\leq$  V<sub>CC</sub>  $\leq$  5.5 V, 7.0 V  $\leq$  V<sub>BAT</sub>  $\leq$  20 V, -40 °C  $\leq$  T<sub>A</sub>  $\leq$  125 °C, unless otherwise noted. Typical values noted reflect the approximate parameter mean at T<sub>A</sub> = 25 °C under nominal conditions, unless otherwise noted.

| Characteristic                                                                                                | Symbol                     | Min          | Тур          | Max          | Unit |

|---------------------------------------------------------------------------------------------------------------|----------------------------|--------------|--------------|--------------|------|

| TAIL LIGHT (OUT3)                                                                                             |                            |              |              |              |      |

| Output Drain-to-Source ON Resistance (I <sub>OUT</sub> = 2.8 A, T <sub>A</sub> = 25 °C)                       | R <sub>DS(ON)25</sub>      |              |              |              | mΩ   |

| V <sub>BAT</sub> = 13.5 V                                                                                     |                            | _            | _            | 35           |      |

| V <sub>BAT</sub> = 7.0 V                                                                                      |                            | _            | _            | 55           |      |

| Output Drain-to-Source ON Resistance ( $I_{OUT}$ = 2.8 A, $V_{BAT}$ = 13.5 V, $T_A$ = 150 °C) <sup>(25)</sup> | R <sub>DS(ON)150</sub>     | _            | _            | 59.5         | mΩ   |

| Reverse Source-to-Drain ON Resistance ( $I_{OUT}$ = -2.8 A, $V_{BAT}$ = -12 V, $T_A$ = 25 °C) <sup>(26)</sup> | R <sub>SD(ON)25</sub>      | _            | _            | 70           | mΩ   |

| Output Drain-to-Source ON Resistance (I <sub>OUT</sub> = 1.5 A, T <sub>A</sub> = 25 °C) for LED               | R <sub>DS(ON)25_LED</sub>  |              |              |              | mΩ   |

| Control = 1                                                                                                   |                            | _            | _            | 70           |      |

| V <sub>BAT</sub> = 13.5 V                                                                                     |                            | -            | _            | 110          |      |

| V <sub>BAT</sub> = 7.0 V                                                                                      | _                          |              |              |              |      |

| Output Drain-to-Source ON Resistance ( $I_{OUT} = 1.5 \text{ A}$ , $V_{BAT} = 13.5 \text{ V}$ ,               | R <sub>DS(ON)150_LED</sub> |              |              | 119          | mΩ   |

| T <sub>A</sub> = 150 °C) for LED Control = 1                                                                  |                            |              | _            | 119          |      |

| High Over Current Shutdown Threshold 1                                                                        | I <sub>OCHI1</sub>         | 28.0         | 35.0         | 43.5         | Α    |

| $V_{BAT} = 16 \text{ V}, T_A = -40 ^{\circ}\text{C}$                                                          |                            | 30.2<br>29.4 | 36.0<br>35.0 | 41.8<br>40.6 |      |

| $V_{BAT} = 16 \text{ V}, T_A = 25 \text{ °C}$<br>$V_{BAT} = 16 \text{ V}, T_A = 125 \text{ °C}$               |                            | 29.4         | 33.8         | 39.3         |      |

| High Over-current Shutdown Threshold 2                                                                        | I <sub>OCHI2</sub>         | 12.3         | 15.4         | 18.5         | Α    |

| <u> </u>                                                                                                      |                            |              |              |              |      |

| Low Over-current Shutdown Threshold                                                                           | locto                      | 5.7          | 7.2          | 8.9          | Α    |

| Open Load Current Threshold in ON State <sup>(27)</sup>                                                       | I <sub>OL</sub>            | 0.05         | 0.2          | 0.5          | Α    |

| Open Load Current Threshold in ON State with LED <sup>(28)</sup>                                              | I <sub>OLLED</sub>         |              |              |              | mA   |

| $V_{OL} = V_{BAT} - 0.5 V$                                                                                    |                            | 4.0          | 10           | 20           |      |

| Current Sense Full-scale Range <sup>(29)</sup>                                                                | I <sub>CS FSR</sub>        | _            | 6.0          | -            | Α    |

| Current Sense Full-scale Range <sup>(25)</sup> depending on LED Control = 1                                   | I <sub>CS FSR_LED</sub>    | 1            | 1.6          | -            | Α    |

| Severe short-circuit impedance range <sup>(25)</sup>                                                          | R <sub>SC1(OUT3)</sub>     | 350          | -            | _            | mΩ   |

- 25. Parameter guaranteed by design; however, it is not production tested.

- 26. Source-to-Drain ON Resistance (Reverse Drain-to-Source ON Resistance) with negative polarity V<sub>BAT</sub>.

- 27. OLLED3, bit D2 in SI data is set to [0]

- 28. OLLED3, bit D2 in SI data is set to [1]

- 29. For a typical value of I<sub>CS FSR,</sub> I<sub>CSNS</sub> = 5.0 mA. If the range is exceeded, no current clamp and the precision is not guaranteed.

Characteristics noted under conditions 3.0 V  $\leq$  V<sub>CC</sub>  $\leq$  5.5 V, 7.0 V  $\leq$  V<sub>BAT</sub>  $\leq$  20 V, -40 °C  $\leq$  T<sub>A</sub>  $\leq$  125 °C, unless otherwise noted. Typical values noted reflect the approximate parameter mean at T<sub>A</sub> = 25 °C under nominal conditions, unless otherwise noted.

| Characteristic                                                                                                | Symbol                     | Min          | Тур          | Max          | Unit     |

|---------------------------------------------------------------------------------------------------------------|----------------------------|--------------|--------------|--------------|----------|

| STOP LIGHT (OUT4)                                                                                             |                            |              |              |              | <b>.</b> |

| Output Drain-to-Source ON Resistance (I <sub>OUT</sub> = 2.8 A, T <sub>A</sub> = 25 °C)                       | R <sub>DS(ON)25</sub>      |              |              |              | mΩ       |

| V <sub>BAT</sub> = 13.5 V                                                                                     |                            | -            | _            | 35           |          |

| V <sub>BAT</sub> = 7.0 V                                                                                      |                            | -            | _            | 55           |          |

| Output Drain-to-Source ON Resistance ( $I_{OUT}$ = 2.8 A, $V_{BAT}$ = 13.5 V, $T_A$ = 150 °C) <sup>(30)</sup> | R <sub>DS(ON)150</sub>     | _            | _            | 59.5         | mΩ       |

| Output Drain-to-Source ON Resistance ( $I_{OUT}$ = 1.5 A, $T_{A}$ = 25 °C) for LED Control = 1                | R <sub>DS(ON)25_LED</sub>  |              |              |              | mΩ       |

| V <sub>BAT</sub> = 13.5 V                                                                                     |                            | -            | -            | 70           |          |

| V <sub>BAT</sub> = 7.0 V                                                                                      |                            | _            | _            | 110          |          |

| Output Drain-to-Source ON Resistance (I <sub>OUT</sub> =1.5 A, V <sub>BAT</sub> = 13.5 V,                     | R <sub>DS(ON)150_LED</sub> |              |              |              | mΩ       |

| $T_A = 150 ^{\circ}\text{C}$ ) for LED Control = 1                                                            |                            | -            | _            | 119          |          |

| Reverse Source-to-Drain ON Resistance ( $I_{OUT}$ = -2.8 A, $V_{BAT}$ = -12 V, $T_A$ = 25 °C) <sup>(31)</sup> | R <sub>DS(ON)25</sub>      | -            | _            | 70           | mΩ       |

| High Over-current Shutdown Threshold 1                                                                        | I <sub>OCHI1</sub>         | 28.0         | 35.0         | 43.5         | Α        |

| $V_{BAT} = 16 \text{ V}, T_A = -40 ^{\circ}\text{C}$                                                          |                            | 30.2         | 36.0         | 41.8         |          |

| $V_{BAT} = 16 \text{ V}, T_A = 25 \text{ °C}$<br>$V_{BAT} = 16 \text{ V}, T_A = 125 \text{ °C}$               |                            | 29.4<br>28.3 | 35.0<br>33.8 | 40.6<br>39.3 |          |

| High Over-current Shutdown Threshold 2                                                                        | I <sub>OCHI2</sub>         | 12.3         | 15.4         | 18.5         | A        |

| Low Over-current Shutdown Threshold                                                                           |                            | 5.7          | 7.2          | 8.9          | A        |

|                                                                                                               | l <sub>octo</sub>          | 0.05         | 0.2          |              |          |

| Open Load Current Threshold in ON State <sup>(32)</sup>                                                       | I <sub>OL</sub>            | 0.05         | 0.2          | 0.5          | A        |

| Open Load Current Threshold in ON State with LED <sup>(33)</sup>                                              | I <sub>OLLED</sub>         |              |              |              | mA       |

| $V_{OL} = V_{BAT} - 0.5 V$                                                                                    |                            | 4.0          | 10           | 20           |          |

| Current Sense Full-scale Range <sup>(34)</sup>                                                                | I <sub>CS FSR</sub>        |              | 6.0          | _            | Α        |

| Current Sense Full-scale Range <sup>(30)</sup> depending on LED Control = 1                                   | I <sub>CS FSR_LED</sub>    | -            | 1.6          | -            | Α        |

| Severe Short-circuit Impedance Range <sup>(30)</sup>                                                          | R <sub>SC1(OUT4)</sub>     | 350          |              |              | mΩ       |

- 30. Parameter guaranteed by design; however, it is not production tested.

- 31. Source-to-Drain ON Resistance (Reverse Drain-to-Source ON Resistance) with negative polarity V<sub>BAT</sub>.

- 32. OLLED3, bit D2 in SI data is set to [0]

- 33. OLLED3, bit D2 in SI data is set to [1]

- 34. For a typical value of I<sub>CS FSR,</sub> I<sub>CSNS</sub> = 5.0 mA. If the range is exceeded, no current clamp and the precision is not guaranteed.

Characteristics noted under conditions 3.0 V  $\leq$  V<sub>CC</sub>  $\leq$  5.5 V, 7.0 V  $\leq$  V<sub>BAT</sub>  $\leq$  20 V, -40 °C  $\leq$  T<sub>A</sub>  $\leq$  125 °C, unless otherwise noted. Typical values noted reflect the approximate parameter mean at T<sub>A</sub> = 25 °C under nominal conditions, unless otherwise noted.

| Characteristic                                                                                                | Symbol                     | Min  | Тур  | Max  | Unit |

|---------------------------------------------------------------------------------------------------------------|----------------------------|------|------|------|------|

| FLASHER (OUT5)                                                                                                |                            |      |      |      |      |

| Output Drain-to-Source ON Resistance (I <sub>OUT</sub> = 2.8 A, T <sub>A</sub> = 25 °C)                       | R <sub>DS(ON)25</sub>      |      |      |      | mΩ   |

| V <sub>BAT</sub> = 13.5 V                                                                                     |                            | _    | _    | 35   |      |

| V <sub>BAT</sub> = 7.0 V                                                                                      |                            | -    | _    | 55   |      |

| Output Drain-to-Source ON Resistance ( $I_{OUT}$ = 2.8 A, $V_{BAT}$ = 13.5 V, $T_A$ = 150 °C) <sup>(35)</sup> | R <sub>DS(ON)150</sub>     | _    | _    | 59.5 | mΩ   |

| Reverse Source-to-Drain ON Resistance ( $I_{OUT}$ = -2.8 A, $V_{BAT}$ = -12 V, $T_A$ = 25 °C) <sup>(36)</sup> | R <sub>SD(ON)25</sub>      | -    | _    | 70   | mΩ   |

| Output Drain-to-Source ON Resistance (I <sub>OUT</sub> =1.5 A, T <sub>A</sub> = 25 °C) for LED Control = 1    | R <sub>DS(ON)25_LED</sub>  |      |      |      | mΩ   |

| V <sub>BAT</sub> = 13.5 V                                                                                     |                            | -    | _    | 70   |      |

| V <sub>BAT</sub> = 7.0 V                                                                                      |                            | _    | _    | 110  |      |

| Output Drain-to-Source ON Resistance (I <sub>OUT</sub> = 1.5 A, V <sub>BAT</sub> = 13.5 V,                    | R <sub>DS(ON)150_LED</sub> |      |      |      | mΩ   |

| T <sub>A</sub> = 150 °C) for LED Control = 1                                                                  |                            | -    | _    | 119  |      |

| High Over-current Shutdown Threshold 1                                                                        | I <sub>OCHI1</sub>         | 28.0 | 35.0 | 43.5 | Α    |

| $V_{BAT} = 16 \text{ V}, T_A = -40 ^{\circ}\text{C}$                                                          |                            | 30.2 | 36.0 | 41.8 |      |

| $V_{BAT} = 16 \text{ V}, T_A = 25 ^{\circ}\text{C}$                                                           |                            | 29.4 | 35.0 | 40.6 |      |

| V <sub>BAT</sub> = 16 V, T <sub>A</sub> = 125 °C                                                              |                            | 28.3 | 33.8 | 39.3 |      |

| High Over-current Shutdown Threshold 2                                                                        | I <sub>OCHI2</sub>         | 12.3 | 15.4 | 18.5 | Α    |

| Low Over-current Shutdown Threshold                                                                           | I <sub>OCLO</sub>          | 5.7  | 7.2  | 8.9  | Α    |

| Open Load Current Threshold in ON State <sup>(37)</sup>                                                       | I <sub>OL</sub>            | 0.05 | 0.2  | 0.5  | Α    |

| Open Load Current Threshold in ON State with LED <sup>(38)</sup>                                              | I <sub>OLLED</sub>         |      |      |      | mA   |

| $V_{OL} = V_{BAT} - 0.5 V$                                                                                    |                            | 4.0  | 10   | 20   |      |

| Current Sense Full-scale Range <sup>(39)</sup>                                                                | I <sub>CS FSR</sub>        | _    | 6.0  | -    | Α    |

| Current Sense Full-scale Range <sup>(35)</sup> depending on LED Control = 1                                   | I <sub>CS FSR_LED</sub>    | -    | 1.6  | _    | Α    |

| Severe Short-circuit Impedance Range <sup>(35)</sup>                                                          | R <sub>SC1(OUT5)</sub>     | 350  | _    | _    | mΩ   |

- 35. Parameter guaranteed by design; however, it is not production tested.

- 36. Source-to-Drain ON Resistance (Reverse Drain-to-Source ON Resistance) with negative polarity  $V_{BAT}$ .

- 37. OLLED3, bit D2 in SI data is set to [0]

- 38. OLLED3, bit D2 in SI data is set to [1]

- 39. For a typical value of  $I_{CS FSR}$ ,  $I_{CSNS} = 5.0$  mA. If the range is exceeded, no current clamp and the precision is not guaranteed.

$Characteristics \ noted \ under \ conditions \ 3.0 \ V \leq V_{CC} \leq 5.5 \ V, \ 7.0 \ V \leq V_{BAT} \leq 20 \ V, \ -40 \ ^{\circ}C \leq T_{A} \leq 125 \ ^{\circ}C, \ unless \ otherwise \ noted.$ Typical values noted reflect the approximate parameter mean at  $T_A$  = 25 °C under nominal conditions, unless otherwise noted.

| Characteristic                                                                                                                                                                                    | Symbol                  | Min          | Тур    | Max        | Unit            |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|--------------|--------|------------|-----------------|

| SPARE (FETOUT, FETIN)                                                                                                                                                                             |                         |              |        |            |                 |

| FETOUT Output High Level at I = 1.0 mA                                                                                                                                                            | V <sub>H MAX</sub>      | 0.8          | _      | _          | V <sub>CC</sub> |

| FETOUT Output Low Level at I = 1.0 mA                                                                                                                                                             | V <sub>H MIN</sub>      | -            | 0.2    | 0.4        | V               |

| FETIN Input Full Scale Range Current                                                                                                                                                              | I <sub>FETIN</sub>      | -            | 5.0    | -          | mA              |

| FETIN Input Clamp Voltage                                                                                                                                                                         | V <sub>CLIN</sub>       | 5.3          | -      | 7.0        | V               |

| Drop Voltage between FETIN and CSNS for MUX[2:0] = 110 I <sub>FETIN</sub> = 5 mA, 5.5 V > CSNS > 0.0 V                                                                                            | V <sub>DRIN</sub>       | 0.0          | _      | 0.4        | V               |

| FETIN Leakage Current when external current switch sense is enabled 4.5 V > V <sub>FETIN</sub> > 0 V, 5.5 V > VCC > 4.5 V, CSNS open 3.0 V > V <sub>FETIN</sub> > 0 V, 4.5 V > VCC > 0, CSNS open | I <sub>FETINLEAK</sub>  | -1.0<br>-1.0 | _<br>_ | 5.0<br>1.0 | μА              |

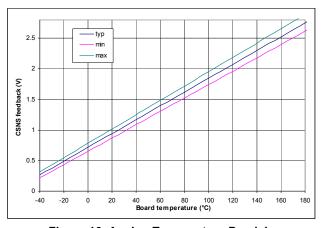

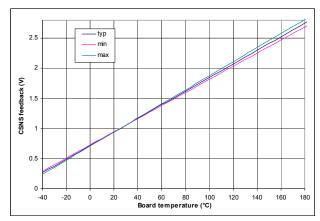

| TEMPERATURE OF GND FLAG                                                                                                                                                                           |                         |              |        |            |                 |

| Analog Temperature Feedback at T <sub>A</sub> = 25 °C with 5.0 k $\Omega$ > R <sub>CSNS</sub> > 500 $\Omega$                                                                                      | V <sub>T_FEED</sub>     | 920          | 1025   | 1140       | mV              |

| Analog Temperature Feedback Derating with 5.0 k $\Omega$ > R <sub>CSNS</sub> > 500 $\Omega^{(40)}$                                                                                                | V <sub>DT_FEED</sub>    | 10.9         | 11.3   | 11.7       | mV/ °C          |

| Analog Temperature Feedback Precision <sup>(40)</sup>                                                                                                                                             | V <sub>DT_ACC</sub>     | -15          | -      | 15         | °C              |

| Analog Temperature Feedback Precision with calibration point at 25 °C <sup>(40)</sup>                                                                                                             | V <sub>DT_ACC_CAL</sub> | -5.0         | -      | 5.0        | °C              |

#### Notes

<sup>40.</sup> Parameter guaranteed by design; however, it is not production tested.

## **DYNAMIC ELECTRICAL CHARACTERISTICS**

## **Table 5. Dynamic Electrical Characteristics**

Characteristics noted under conditions 4.5 V  $\leq$  V<sub>CC</sub>  $\leq$  5.5 V, 7.0 V  $\leq$  V<sub>BAT</sub>  $\leq$  20 V, -40 °C  $\leq$  T<sub>A</sub>  $\leq$  125 °C, unless otherwise noted. Typical values noted reflect the approximate parameter mean at T<sub>A</sub> = 25 °C under nominal conditions, unless otherwise noted.

| Characteristic                                                                                                                                                     | Symbol                  | Min  | Тур  | Max  | Unit |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|------|------|------|------|

| POWER OUTPUTS TIMING (OUT1:5)                                                                                                                                      |                         |      |      |      | •    |

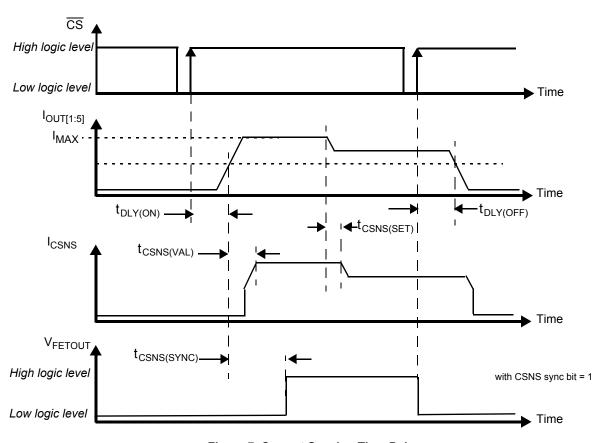

| Current Sense Valid Time on resistive load only <sup>(41)</sup>                                                                                                    | t <sub>CSNS(VAL)</sub>  |      |      |      | μS   |

| SR bit = 0                                                                                                                                                         |                         | _    | 90   | 150  |      |

| SR bit = 1                                                                                                                                                         |                         | _    | 45   | 75   |      |

| Current Sense Synchronization Time on FETOUT                                                                                                                       | t <sub>CSNS(SYNC)</sub> |      |      |      | μS   |

| SR bit = 0                                                                                                                                                         |                         | _    | 130  | 185  |      |

| SR bit = 1                                                                                                                                                         |                         | _    | 70   | 110  |      |

| Current Sense Settling Time on resistive load only <sup>(41)</sup>                                                                                                 | t <sub>CSNS(SET)</sub>  | -    | 10   | 30   | μS   |

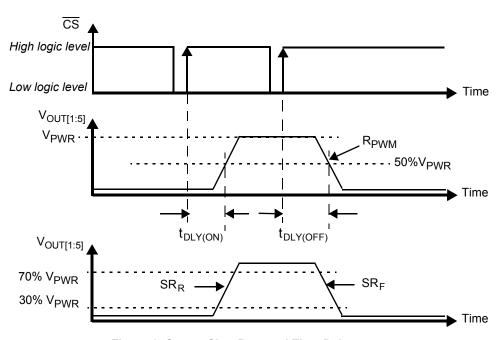

| Driver Output Positive Slew Rate (30% to 70% at V <sub>BAT</sub> = 14 V)                                                                                           | SR <sub>R</sub>         |      |      |      | V/μs |

| SR bit = 0, I <sub>OUT</sub> = 2.8 A                                                                                                                               |                         | 0.10 | 0.25 | 0.56 |      |

| SR bit = 1, I <sub>OUT</sub> = 0.7 A                                                                                                                               |                         | 0.20 | 0.40 | 0.80 |      |

| Driver Output Negative Slew Rate (70% to 30% at V <sub>BAT</sub> = 14 V)                                                                                           | SR <sub>F</sub>         |      |      |      | V/µs |

| SR bit = 0, I <sub>OUT</sub> = 2.8 A                                                                                                                               |                         | 0.10 | 0.25 | 0.56 |      |

| SR bit = 1, I <sub>OUT</sub> = 0.7 A                                                                                                                               |                         | 0.20 | 0.40 | 0.80 |      |

| Driver Output Matching Slew Rate $(SR_R/SR_F)(70\% \text{ to } 30\% \text{ at } V_{BAT} = 14 \text{ V}$                                                            | ΔSR                     |      |      |      |      |

| at 25 °C)                                                                                                                                                          |                         | 0.8  | 1.0  | 1.2  |      |

| Driver Output Turn-ON Delay (SPI ON Command [No PWM, $\overline{\text{CS}}$ Positive Edge] to Output = 50% $V_{\text{BAT}}$ at $V_{\text{BAT}}$ = 14 V)            | t <sub>DLYON</sub>      |      |      |      | μS   |

| SR bit = 0, I <sub>OUT</sub> = 2.8 A                                                                                                                               |                         | 50   | -    | 120  |      |

| SR bit = 1, I <sub>OUT</sub> = 0.7 A                                                                                                                               |                         | 25   | -    | 65   |      |

| Driver Output Turn-OFF Delay (SPI OFF command $\overline{[CS]}$ Positive Edge] to Output = 50% $V_{BAT}$ at $V_{BAT}$ = 14 V)                                      | t <sub>DLYOFF</sub>     |      |      |      | μS   |

| SR bit = 0, I <sub>OUT</sub> = 2.8 A                                                                                                                               |                         | 50   | -    | 120  |      |

| SR bit = 1, I <sub>OUT</sub> = 0.7 A                                                                                                                               |                         | 25   | -    | 65   |      |

| Driver Output Matching Time ( $t_{DLY(ON)}$ - $t_{DLY(OFF)}$ ) at Output = 50% $V_{BAT}$ with $V_{BAT}$ = 14 V, $f_{PWM}$ = 240 Hz, $\delta_{PWM}$ = 50%, at 25 °C | Δt <sub>RF</sub>        |      |      |      | μS   |

| SR bit = 0, I <sub>OUT</sub> = 2.8 A for OUT1/2/3/4/5                                                                                                              |                         | -40  | _    | 20   |      |

| SR bit = 1, I <sub>OUT</sub> = 0.7 A for OUT1/2/3/4/5                                                                                                              |                         | -23  | _    | 7.0  |      |

#### Notes

41. Not production tested.

Characteristics noted under conditions 4.5 V  $\leq$  V<sub>CC</sub>  $\leq$  5.5 V, 7.0 V  $\leq$  V<sub>BAT</sub>  $\leq$  20 V, -40 °C  $\leq$  T<sub>A</sub>  $\leq$  125 °C, unless otherwise noted. Typical values noted reflect the approximate parameter mean at T<sub>A</sub> = 25 °C under nominal conditions, unless otherwise noted.

| Characteristic                                                                                                                                                          | Symbol                 | Min       | Тур    | Max      | Unit |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|-----------|--------|----------|------|

| PWM MODULE                                                                                                                                                              |                        |           |        |          | •    |

| Nominal PWM Frequency Range <sup>(44)</sup>                                                                                                                             | f <sub>PWM</sub>       | 30        | _      | 400      | Hz   |

| Clock Input Frequency Range                                                                                                                                             | f <sub>CLK</sub>       | 7.68      | -      | 51.2     | kHz  |

| Output PWM Duty Cycle maximum range for 11 V <v<sub>BAT&lt;18 V<sup>(42), (44)</sup></v<sub>                                                                            | PWM_MAX                | 4.0       | _      | 96       | %    |

| Output PWM Duty Cycle linear range for 11 V <v<sub>BAT&lt;18 V<sup>(43), (44)</sup></v<sub>                                                                             | PWM_LIN                | 5.5       | -      | 96       | %    |

| Output PWM Duty Cycle range for full diagnostic for 11 V <vbat<18 v<sup="">(45) 200 Hz Output PWM frequency 400 Hz Output PWM frequency</vbat<18>                       | PWM_DIAG               | 5.5<br>11 | -<br>- | 96<br>90 | %    |

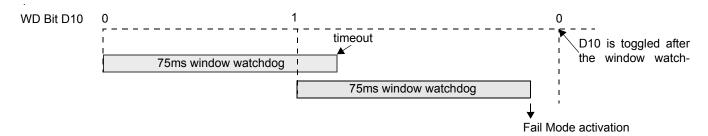

| WATCHDOG TIMING                                                                                                                                                         |                        |           | l      |          |      |

| Watchdog Timeout (SPI Failure)                                                                                                                                          | t <sub>WDTO</sub>      | 50        | 75     | 100      | ms   |

| I/O PLAUSIBILITY CHECK TIMING                                                                                                                                           |                        |           | l      |          |      |

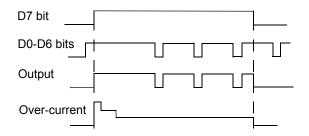

| Fault Shutdown Delay Time (from Over-temperature or OCHI1 or OHCI2 or OCLO Fault Detection to Output = 50% V <sub>BAT</sub> without round shaping feature for turn off) | t <sub>SD</sub>        | -         | 7.0    | 30       | μS   |

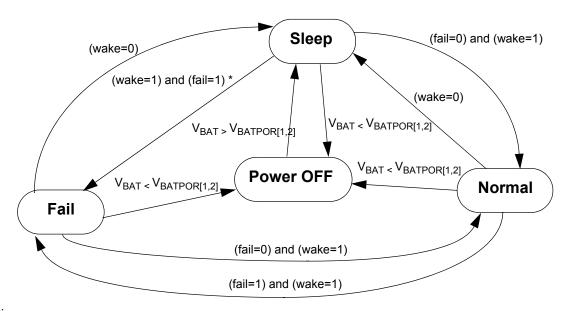

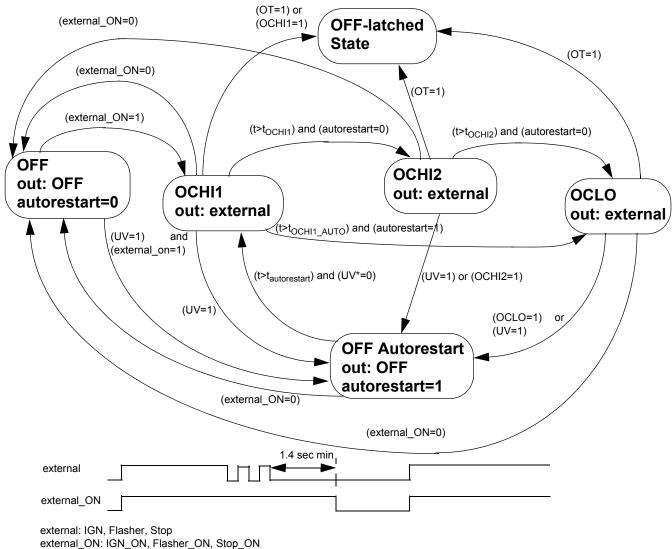

| Under-voltage Deglitch Time <sup>(46)</sup>                                                                                                                             | t <sub>UV</sub>        | 0.8       | 1.25   | 2.0      | μS   |