# MC68HC812A4

**Data Sheet**

M68HC12 Microcontrollers

MC68HC812A4 Rev. 7 05/2006

freescale.com

# MC68HC812A4

#### **Data Sheet**

To provide the most up-to-date information, the revision of our documents on the World Wide Web will be the most current. Your printed copy may be an earlier revision. To verify you have the latest information available, refer to:

http://freescale.com

The following revision history table summarizes changes contained in this document. For your convenience, the page number designators have been linked to the appropriate location.

# **Revision History**

| Date                          | Revision<br>Level                                                                                                                                                                                  | Description                                                                                                                                              | Page<br>Number(s) |

|-------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

|                               |                                                                                                                                                                                                    | <b>Figure 1-3. Expanded Wide Mode SRAM Expansion Schematic</b> — Figure title changed from FLASH EEPROM to SRAM and address line designators corrected   | 40                |

| August,                       |                                                                                                                                                                                                    | <b>Figure 1-4. Expanded Narrow Mode SRAM Expansion Schematic</b> — Figure title changed from FLASH EEPROM to SRAM and address line designators corrected | 42                |

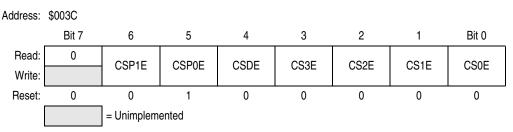

| 2001<br>(Continued<br>on next | value for CSPOE (bit 5)  Figure 10-1. Clock Module Block Diagram — Corrected E- and generator options  Figure 11-1. PLL Block Diagram — Revised diagram to show coplacement of divide-by-two block | Figure 8-16. Chip-Select Control Register 0 (CSCTL0) — Corrected reset value for CSPOE (bit 5)                                                           | 138               |

| page)                         |                                                                                                                                                                                                    | Figure 10-1. Clock Module Block Diagram — Corrected E- and P-clock generator options                                                                     | 156               |

|                               |                                                                                                                                                                                                    | Figure 11-1. PLL Block Diagram — Revised diagram to show correct placement of divide-by-two block                                                        | 170               |

|                               |                                                                                                                                                                                                    | 12.11.2 Timer Port Data Direction Register — Descriptive paragraph added for clarity                                                                     | 209               |

Freescale™ and the Freescale logo are trademarks of Freescale Semiconductor, Inc.

© Freescale Semiconductor, Inc., 2006. All rights reserved.

MC68HC812A4 Data Sheet, Rev. 7

# **Revision History**

# **Revision History**

| Date            | Revision<br>Level | Description                                                                                                                         | Page<br>Number(s) |

|-----------------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| August,         |                   | 12.11.3 Data Direction Register for Timer Port — Repetitive information removed. See 12.11.2 Timer Port Data Direction Register     | 209               |

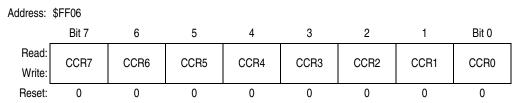

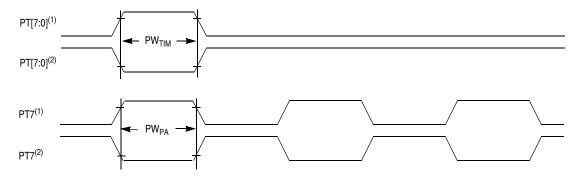

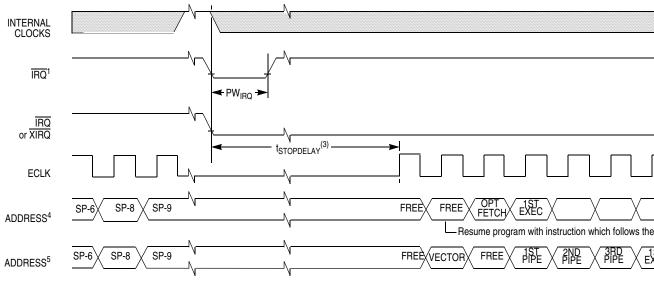

| 2001            | 4                 | <b>18.12 Control Timing</b> — Minimum values added for PW <sub>IRQ</sub> and PW <sub>TIM</sub>                                      | 329               |

| (Continued)     |                   | <b>18.14 Non-Multiplexed Expansion Bus Timing</b> — Table heading changed to reflect minimum and maximum values at 8 MHz            | 334               |

| September,      | 5                 | <b>Table 12-3. Prescaler Selection</b> — Added value column and updated prescale factors                                            | 197               |

| 2001            | 5                 | <b>18.11 EEPROM Characteristics</b> — Corrected minimum and maximum values for programming and erase times                          | 328               |

|                 |                   | Figure 1-3. Expanded Wide Mode SRAM Expansion Schematic — On sheet 1 of this schematic removed reference to resistor R2             | 40                |

| August,<br>2002 | 6                 | Figure 1-4. Expanded Narrow Mode SRAM Expansion Schematic — On sheet 1 of this schematic removed reference to resistor R2           | 42                |

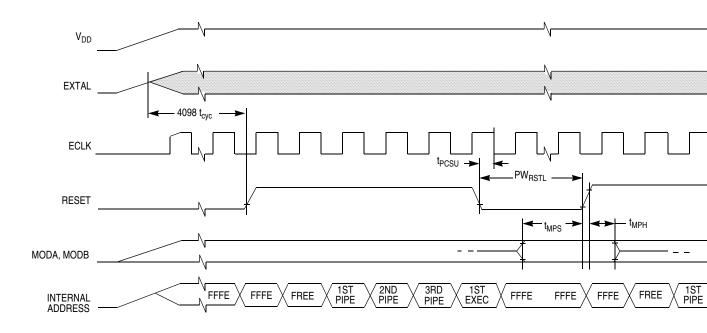

|                 |                   | 4.6.2 External Reset — Corrected reference to eight E-clock cycles to nine E-clock cycles                                           | 77                |

|                 |                   | Updated to meet Freescale identity guidelines.                                                                                      | Throughout        |

|                 |                   | 1.3 Ordering Information — Updated Table 1-1. Ordering Information and added Figure 1-1. Device Numbering System.                   | 18                |

|                 |                   | Figure 1-4. Expanded Wide Mode SRAM Expansion Schematic (Sheet 1 of 3)  — Updated sheet 1 and corrected title for sheets 2 and 3.   | 24                |

|                 |                   | Figure 1-5. Expanded Narrow Mode SRAM Expansion Schematic (Sheet 1 of 3)  — Updated sheet 1 and corrected title for sheets 2 and 3. | 26                |

|                 |                   | Figure 3-9. Condition Code Register (CCR) — Corrected reset state for bit 7.                                                        | 46                |

|                 |                   | Table 4-1. Interrupt Vector Map — Corrected reference to clock monitor reset.                                                       | 50                |

|                 |                   | 4.5 Resets — Reworked paragraph for clarity.                                                                                        | 52                |

|                 |                   | Figure 5-1. Mode Register (MODE) — Changed reset state designator from Peripheral to Special peripheral.                            | 58                |

| May,<br>2006    | 7                 | Figure 10-3. Clock Function Register Map — Removed reference to Special Reset for the COP Control Register.                         | 102               |

|                 |                   | Figure 10-9. COP Control Register (COPCTL) — Corrected reset states.                                                                | 107               |

|                 |                   | 12.4.1 Prescaler — Corrected number of prescaler divides.                                                                           | 122               |

|                 |                   | Figure 12-17. Timer Mask 2 Register (TMSK2) — Corrected reset state for bit 4.                                                      | 131               |

|                 |                   | Table 16-5. ATD Interrupt Sources — Corrected table title.                                                                          | 207               |

|                 |                   | 18.2 Functional Operating Range — Corrected operating temperature range entries.                                                    | 222               |

|                 |                   | 18.10 EEPROM Characteristics — Corrected minimum value for minimum programming clock frequency.                                     | 226               |

|                 |                   | 18.11 Control Timing — Corrected maximum value for frequency of operation.                                                          | 227               |

|                 |                   | 18.12 Peripheral Port Timing — Corrected table heading.                                                                             | 231               |

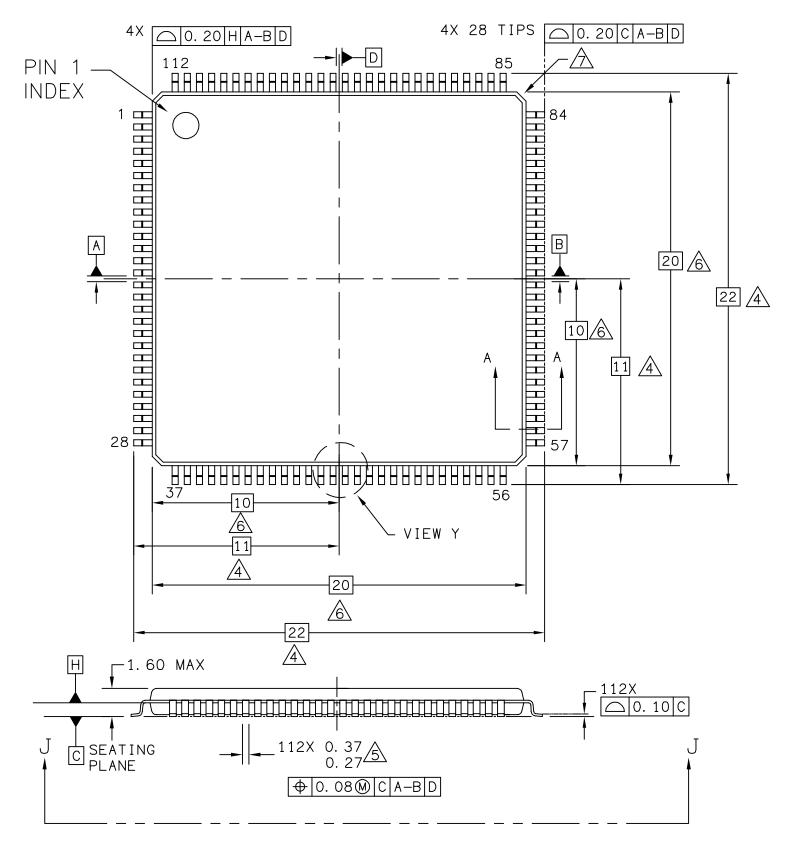

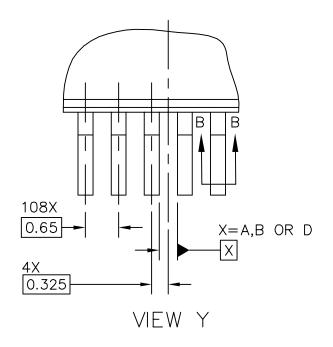

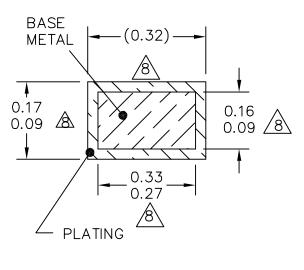

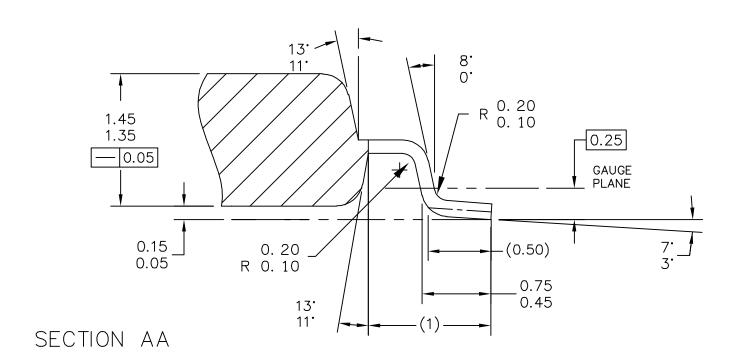

|                 |                   | 19.2 Package Dimensions — Replaced package dimension drawing with the latest available.                                             | 237               |

# **List of Chapters**

| Chapter 1 General Description                           |                 |

|---------------------------------------------------------|-----------------|

| Chapter 2 Register Block                                | 29              |

| Chapter 3 Central Processor Unit (CPU12)                | 43              |

| Chapter 4 Resets and Interrupts                         | 49              |

| Chapter 5 Operating Modes and Resource Mapping          |                 |

| Chapter 6 Bus Control and Input/Output (I/O)            |                 |

| Chapter 7 EEPROM                                        |                 |

| Chapter 8 Memory Expansion and Chip-Select              | 79              |

| Chapter 9 Key Wakeups                                   |                 |

| Chapter 10 Clock Module                                 | 10 <sup>-</sup> |

| Chapter 11 Phase-Lock Loop (PLL)                        | 11°             |

| Chapter 12 Standard Timer Module                        | 117             |

| Chapter 13 Multiple Serial Interface (MSI)              |                 |

| Chapter 14 Serial Communications Interface Module (SCI) | 15              |

| Chapter 15 Serial Peripheral Interface (SPI)            | 179             |

| Chapter 16 Analog-to-Digital Converter (ATD)            |                 |

| Chapter 17 Development Support                          | 21 <sup>-</sup> |

| Chapter 18 Electrical Characteristics                   | 22 <sup>-</sup> |

| Chanter 19 Mechanical Specifications                    | 237             |

**List of Chapters**

# **Table of Contents**

# Chapter 1 General Description

|                | Goneral Booonpaon                     |    |

|----------------|---------------------------------------|----|

| 1.1            | Introduction                          |    |

| 1.2            | Features                              | 17 |

| 1.3            | Ordering Information                  |    |

| 1.4            | Block Diagram                         | 19 |

| 1.5            | Signal Descriptions                   | 20 |

|                | Chapter 2                             |    |

|                | Register Block                        |    |

| 2.1            | Overview                              | 29 |

| 2.2            | Register Map                          |    |

| 2.3            | Modes of Operation                    |    |

|                |                                       |    |

|                | Chapter 3                             |    |

|                | Central Processor Unit (CPU12)        |    |

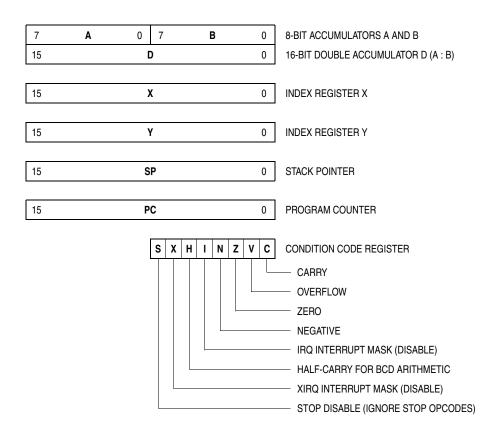

| 3.1            | Overview                              |    |

| 3.2            | Programming Model                     |    |

| 3.3            | CPU Registers                         |    |

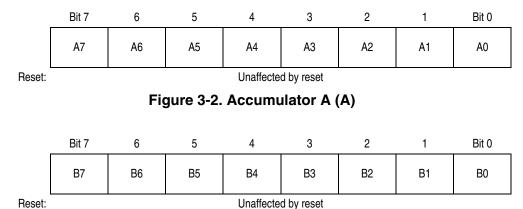

| 3.3.1          | Accumulators A and B                  |    |

| 3.3.2<br>3.3.3 | Accumulator D                         |    |

| 3.3.4          | Stack Pointer                         |    |

| 3.3.5          | Program Counter                       |    |

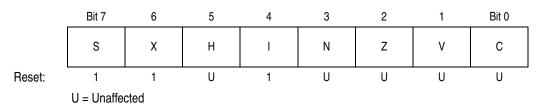

| 3.3.6          | Condition Code Register               |    |

| 3.4            | Data Types                            | 46 |

| 3.5            | Addressing Modes                      | 47 |

| 3.6            | Indexed Addressing Modes              | 48 |

| 3.7            | Opcodes and Operands                  | 48 |

|                | Chapter 4                             |    |

|                | Resets and Interrupts                 |    |

| 4.1            | Introduction                          | 49 |

| 4.2            | Exception Priority                    |    |

| 4.3            | Maskable Interrupts                   |    |

| 4.3<br>4.4     | Interrupt Registers                   |    |

| 4.4<br>4.4.1   | Interrupt Control Register.           |    |

| 4.4.2          | Highest Priority I Interrupt Register |    |

|                |                                       |    |

| -  |   |   |    | <u> </u> |

|----|---|---|----|----------|

| ıа | n | А | OΤ | Contents |

| 4.5     | Resets                                      | 52 |

|---------|---------------------------------------------|----|

| 4.5.1   | Power-On Reset                              | 52 |

| 4.5.2   | External Reset                              | 52 |

| 4.5.3   | COP Reset                                   |    |

| 4.5.4   | Clock Monitor Reset                         | 52 |

| 4.6     | Effects of Reset                            |    |

| 4.6.1   | Operating Mode and Memory Map               |    |

| 4.6.2   | Clock and Watchdog Control Logic            |    |

| 4.6.3   | Interrupts                                  |    |

| 4.6.4   | Parallel I/O                                |    |

| 4.6.5   | Central Processor Unit                      |    |

| 4.6.6   | Memory                                      |    |

| 4.6.7   | Other Resources                             |    |

| 4.7     | Interrupt Recognition                       | 54 |

|         | Chapter 5                                   |    |

|         | Operating Modes and Resource Mapping        |    |

| 5.1     | Introduction                                | 55 |

| 5.2     | Operating Modes                             |    |

| 5.2.1   | Normal Operating Modes                      |    |

| 5.2.1.1 |                                             |    |

| 5.2.1.2 | ·                                           |    |

| 5.2.1.3 | ·                                           |    |

| 5.2.2   | Special Operating Modes                     |    |

| 5.2.2.1 |                                             |    |

| 5.2.2.2 |                                             |    |

| 5.2.2.3 |                                             |    |

| 5.2.2.4 | Special Peripheral Mode                     | 56 |

| 5.2.3   | Background Debug Mode                       | 56 |

| 5.3     | Internal Resource Mapping                   | 57 |

| 5.4     | Mode and Resource Mapping Registers         |    |

| 5.4.1   | Mode Register                               |    |

| 5.4.2   | Register Initialization Register            |    |

| 5.4.3   | RAM Initialization Register                 | 60 |

| 5.4.4   | EEPROM Initialization Register              |    |

| 5.4.5   | Miscellaneous Mapping Control Register      | 61 |

| 5.5     | Memory Map                                  | 62 |

|         | Oh autau C                                  |    |

|         | Chapter 6                                   |    |

| 0.4     | Bus Control and Input/Output (I/O)          |    |

| 6.1     | Introduction                                |    |

| 6.2     | Detecting Access Type from External Signals |    |

| 6.3     | Registers                                   |    |

| 6.3.1   | Port A Data Register                        |    |

| 6.3.2   | Port A Data Direction Register              |    |

| 6.3.3   | Port B Data Register                        |    |

| 6.3.4   | Port B Data Direction Register              | 65 |

MC68HC812A4 Data Sheet, Rev. 7

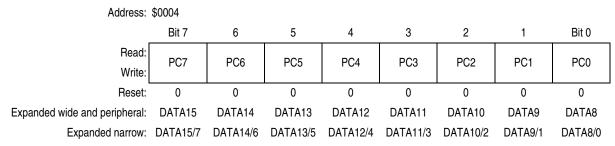

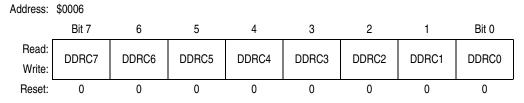

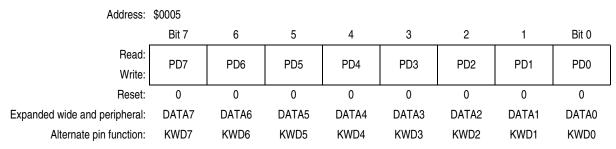

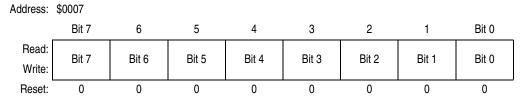

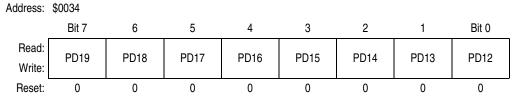

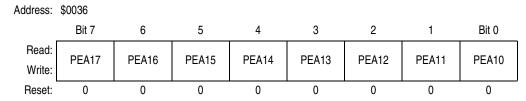

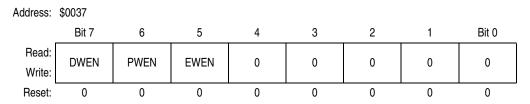

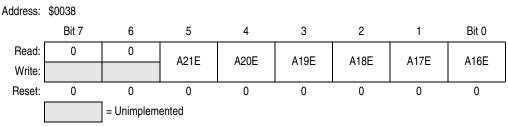

| 6.3.5<br>6.3.6<br>6.3.7<br>6.3.8<br>6.3.9<br>6.3.10<br>6.3.11<br>6.3.12 | Port C Data Register Port C Data Direction Register Port D Data Register Port D Data Direction Register Port E Data Register Port E Data Register Port E Data Direction Register Port E Assignment Register Pullup Control Register | 66<br>67<br>67<br>68<br>68<br>69 |

|-------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| 6.3.13                                                                  | Reduced Drive Register                                                                                                                                                                                                              |                                  |

|                                                                         | Chapter 7 EEPROM                                                                                                                                                                                                                    |                                  |

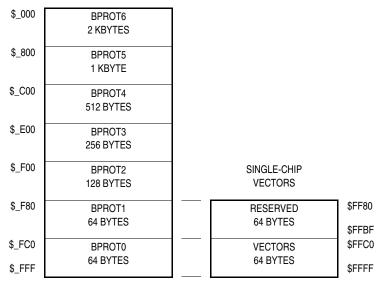

| 7.1                                                                     | Introduction                                                                                                                                                                                                                        | 73                               |

| 7.2                                                                     | EEPROM Programmer's Model                                                                                                                                                                                                           |                                  |

| 7.3                                                                     | EEPROM Control Registers                                                                                                                                                                                                            |                                  |

| 7.3.1                                                                   | EEPROM Module Configuration Register                                                                                                                                                                                                |                                  |

| 7.3.2                                                                   | EEPROM Block Protect Register                                                                                                                                                                                                       |                                  |

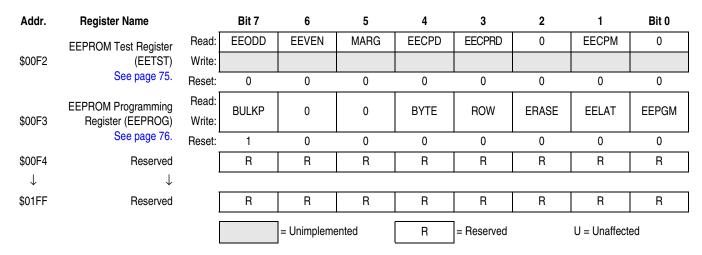

| 7.3.3                                                                   | EEPROM Test Register                                                                                                                                                                                                                |                                  |

| 7.3.4                                                                   | EEPROM Programming Register                                                                                                                                                                                                         | 76                               |

|                                                                         | Chapter 8                                                                                                                                                                                                                           |                                  |

|                                                                         | Memory Expansion and Chip-Select                                                                                                                                                                                                    |                                  |

| 8.1                                                                     | Introduction                                                                                                                                                                                                                        |                                  |

| 8.2                                                                     | Generation of Chip-Selects                                                                                                                                                                                                          |                                  |

| 8.2.1<br>8.2.2                                                          | Chip-Selects Independent of Memory Expansion                                                                                                                                                                                        |                                  |

|                                                                         | Chip-Selects Used in Conjunction with Memory Expansion                                                                                                                                                                              |                                  |

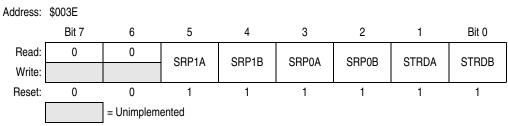

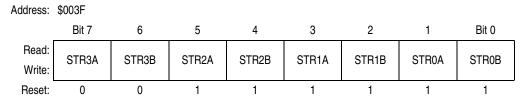

| 8.3                                                                     | Chip-Select Stretch                                                                                                                                                                                                                 |                                  |

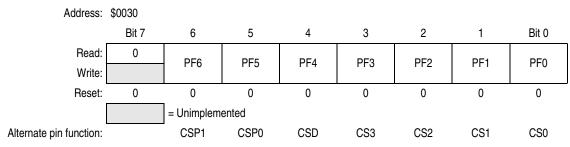

| 8.4<br>8.4.1                                                            | Memory Expansion Registers                                                                                                                                                                                                          |                                  |

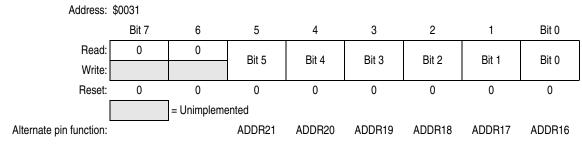

| 8.4.2                                                                   | Port G Data Register                                                                                                                                                                                                                |                                  |

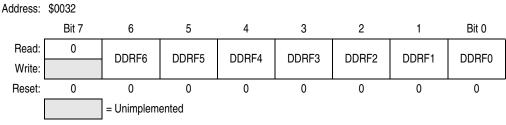

| 8.4.3                                                                   | Port F Data Direction Register                                                                                                                                                                                                      |                                  |

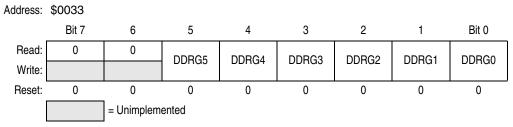

| 8.4.4                                                                   | Port G Data Direction Register.                                                                                                                                                                                                     |                                  |

| 8.4.5                                                                   | Data Page Register                                                                                                                                                                                                                  |                                  |

| 8.4.6                                                                   | Program Page Register                                                                                                                                                                                                               | 87                               |

| 8.4.7                                                                   | Extra Page Register                                                                                                                                                                                                                 |                                  |

| 8.4.8                                                                   | Window Definition Register                                                                                                                                                                                                          |                                  |

| 8.4.9                                                                   | Memory Expansion Assignment Register                                                                                                                                                                                                |                                  |

| 8.5                                                                     | Chip-Selects                                                                                                                                                                                                                        |                                  |

| 8.6                                                                     | Chip-Select Registers                                                                                                                                                                                                               |                                  |

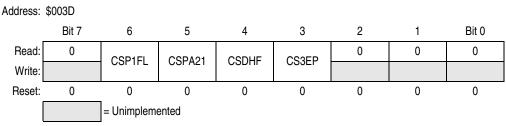

| 8.6.1                                                                   | Chip-Select Control Register 0                                                                                                                                                                                                      |                                  |

| 8.6.2<br>8.6.3                                                          | Chip-Select Control Register 1                                                                                                                                                                                                      |                                  |

| 8.7                                                                     | Priority                                                                                                                                                                                                                            | 92                               |

### **Table of Contents**

# Chapter 9 Key Wakeups

| 9.1    | Introduction                                | 93   |

|--------|---------------------------------------------|------|

| 9.2    | Key Wakeup Registers                        | 93   |

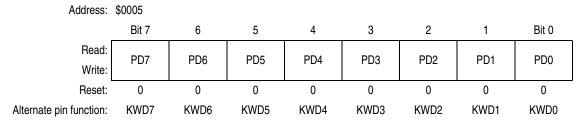

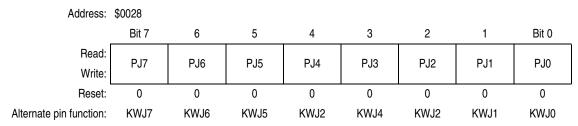

| 9.2.1  | Port D Data Register                        | 93   |

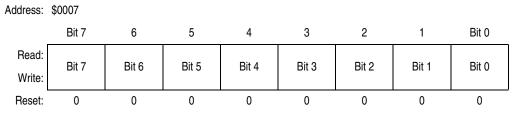

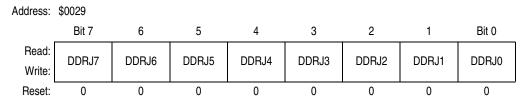

| 9.2.2  | Port D Data Direction Register              | 94   |

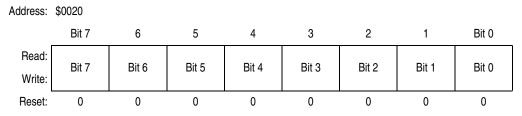

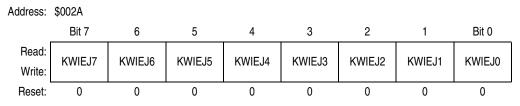

| 9.2.3  | Port D Key Wakeup Interrupt Enable Register | 94   |

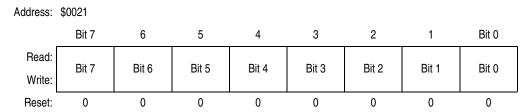

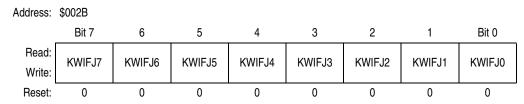

| 9.2.4  | Port D Key Wakeup Flag Register             | 95   |

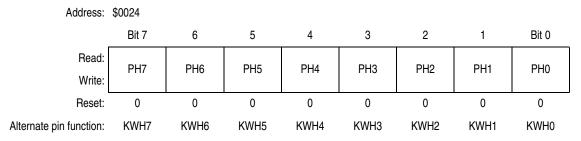

| 9.2.5  | Port H Data Register                        |      |

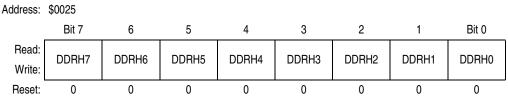

| 9.2.6  | Port H Data Direction Register              |      |

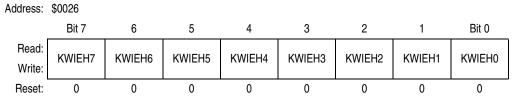

| 9.2.7  | Port H Key Wakeup Interrupt Enable Register |      |

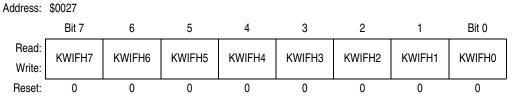

| 9.2.8  | Port H Key Wakeup Flag Register             |      |

| 9.2.9  | Port J Data Register                        |      |

| 9.2.10 | Port J Data Direction Register              |      |

| 9.2.11 | Port J Key Wakeup Interrupt Enable Register |      |

| 9.2.12 | Port J Key Wakeup Flag Register             |      |

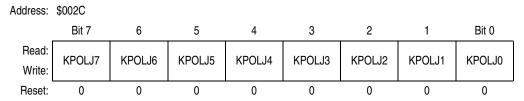

| 9.2.13 | Port J Key Wakeup Polarity Register         |      |

| 9.2.14 | Port J Pullup/Pulldown Select Register      |      |

| 9.2.15 | Port J Pullup/Pulldown Enable Register      | . 99 |

|        | Chapter 10                                  |      |

|        | Clock Module                                |      |

| 404    |                                             | 404  |

| 10.1   | Introduction                                |      |

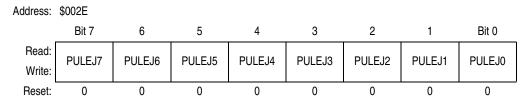

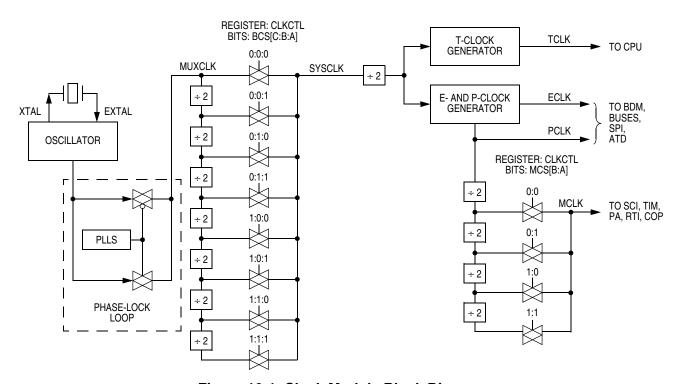

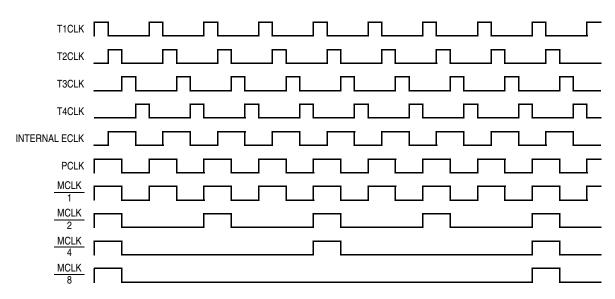

| 10.2   | Block Diagram                               |      |

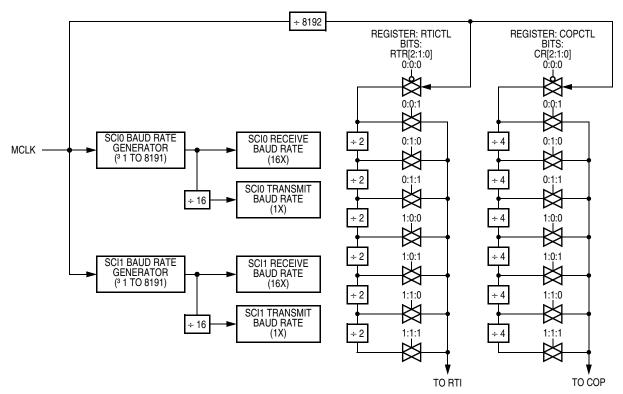

| 10.2.1 | Clock Generators                            |      |

| 10.3   | Register Map                                | 102  |

| 10.4   | Functional Description                      |      |

| 10.4.1 | Computer Operating Properly (COP)           |      |

| 10.4.2 | Real-Time Interrupt                         |      |

| 10.4.3 | Clock Monitor                               |      |

| 10.4.4 | Peripheral Clock Divider Chains             |      |

| 10.5   | Registers and Reset Initialization.         |      |

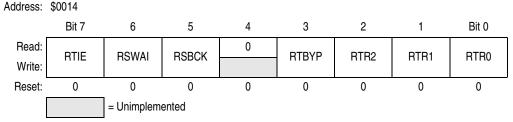

| 10.5.1 | Real-Time Interrupt Control Register        |      |

| 10.5.2 | Real-Time Interrupt Flag Register           |      |

| 10.5.3 | COP Control Register                        |      |

| 10.5.4 | Arm/Reset COP Timer Register                | 109  |

|        | Chapter 11                                  |      |

|        | Phase-Lock Loop (PLL)                       |      |

|        | ,                                           |      |

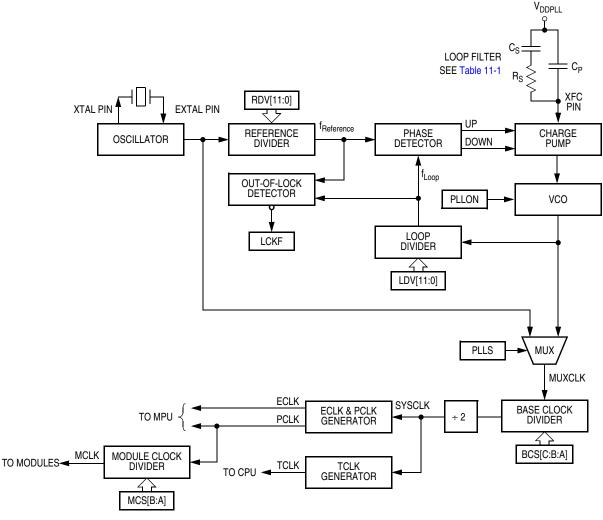

| 11.1   | Introduction                                |      |

| 11.2   | Block Diagram                               |      |

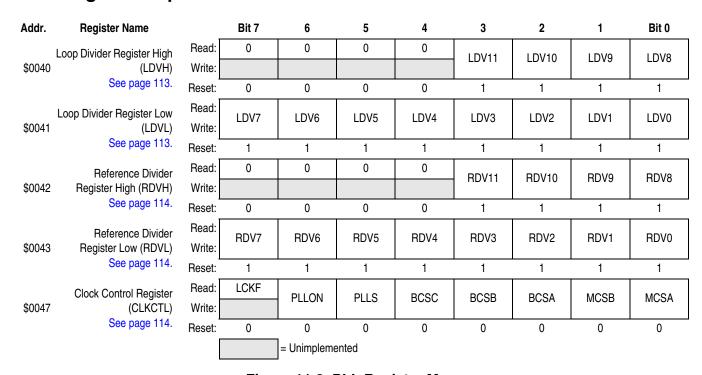

| 11.3   | Register Map                                | 112  |

| 11.4   | Functional Description                      | 113  |

| 11.5   | Registers and Reset Initialization          |      |

| 11.5.1 | Loop Divider Registers                      |      |

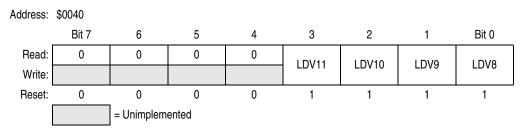

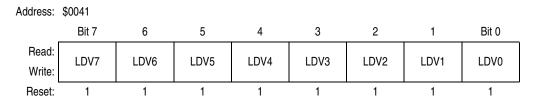

| 11.5.2 | Reference Divider Registers                 |      |

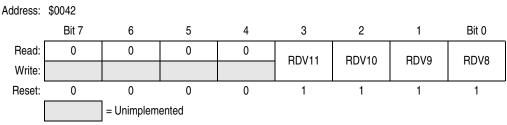

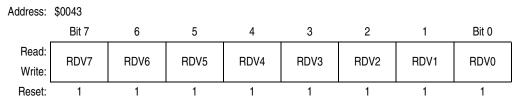

| 11.5.3 | Clock Control Register                      |      |

| _      | •                                           |      |

# Chapter 12 Standard Timer Module

| 12.1 I   | ntroduction                                                 | 117 |

|----------|-------------------------------------------------------------|-----|

| 12.2 I   | Register Map                                                | 117 |

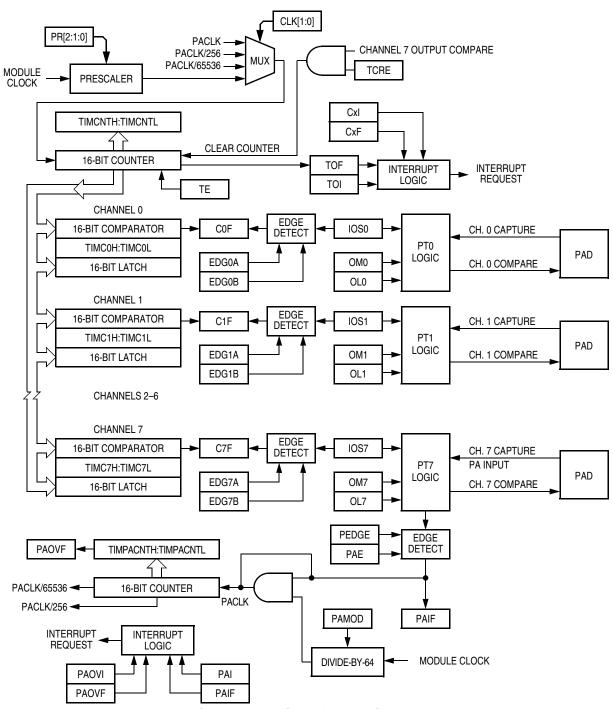

| 12.3 I   | Block Diagram                                               | 118 |

|          | Functional Description                                      |     |

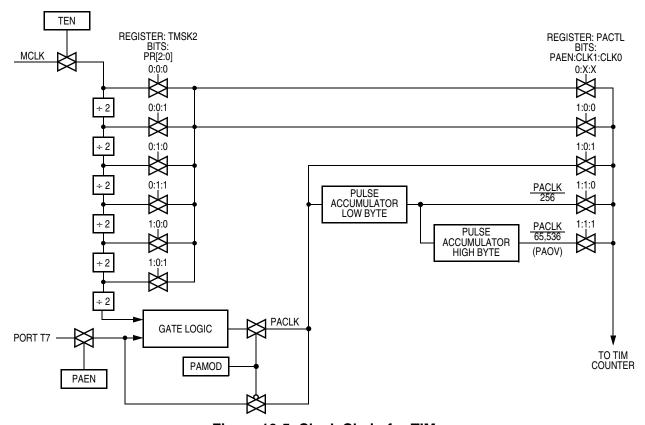

| 12.4.1   | Prescaler                                                   |     |

| 12.4.2   | Input Capture                                               |     |

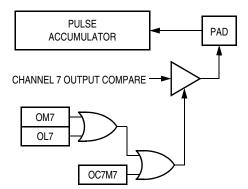

| 12.4.3   | Output Compare                                              |     |

| 12.4.4   | Pulse Accumulator                                           |     |

| 12.4.4.1 |                                                             |     |

| 12.4.4.2 | Gated Time Accumulation Mode                                | 124 |

| 12.5 I   | Registers and Reset Initialization                          | 125 |

| 12.5.1   | Timer IC/OC Select Register                                 | 125 |

| 12.5.2   | Timer Compare Force Register                                |     |

| 12.5.3   | Timer Output Compare 7 Mask Register                        | 126 |

| 12.5.4   | Timer Output Compare 7 Data Register                        | 126 |

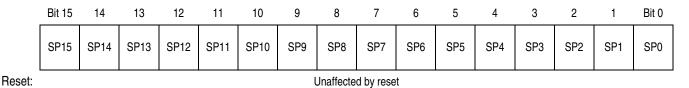

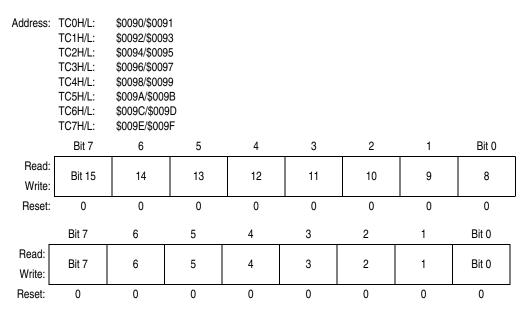

| 12.5.5   | Timer Counter Registers                                     |     |

| 12.5.6   | Timer System Control Register                               |     |

| 12.5.7   | Timer Control Registers 1 and 2                             |     |

| 12.5.8   | Timer Control Registers 3 and 4                             |     |

| 12.5.9   | Timer Mask Register 1                                       |     |

| 12.5.10  | $oldsymbol{\circ}$                                          |     |

| 12.5.11  | Timer Flag Register 1                                       |     |

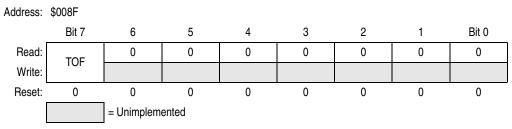

| 12.5.12  | Timer Flag Register 2                                       |     |

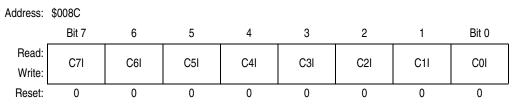

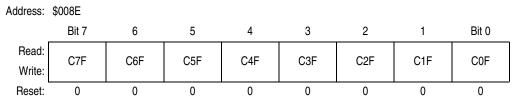

| 12.5.13  | Timer Channel Registers                                     |     |

| 12.5.14  | Pulse Accumulator Control Register                          |     |

| 12.5.15  | Pulse Accumulator Flag Register                             |     |

| 12.5.16  | Pulse Accumulator Counter Registers                         |     |

| 12.5.17  | Timer Test Register                                         |     |

|          | External Pins                                               |     |

| 12.6.1   | Input Capture/Output Compare Pins                           |     |

| 12.6.2   | Pulse Accumulator Pin                                       |     |

|          | Background Debug Mode                                       |     |

| 12.8 l   | Low-Power Options                                           |     |

| 12.8.1   | Run Mode 1                                                  | 138 |

| 12.8.2   | Wait Mode                                                   |     |

| 12.8.3   | Stop Mode                                                   | 138 |

| 12.9 I   | nterrupt Sources                                            | 139 |

| 12.10    | General-Purpose I/O Ports 1                                 | 139 |

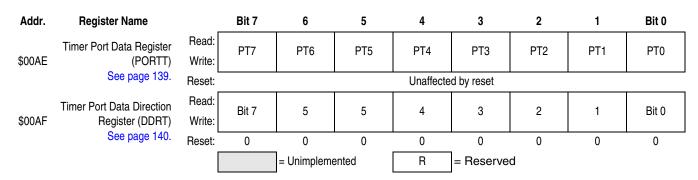

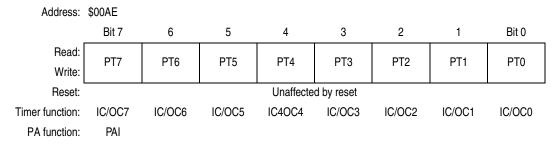

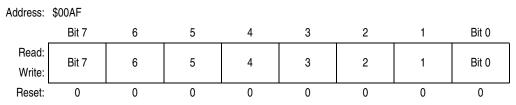

| 12.10.1  | Timer Port Data Register                                    | 139 |

| 12.10.2  |                                                             |     |

| 12.11 l  | Using the Output Compare Function to Generate a Square Wave |     |

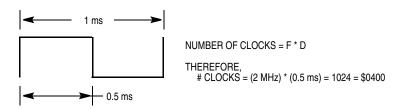

| 12.11.1  | Sample Calculation to Obtain Period Counts                  |     |

| 12.11.2  | · · · · · · · · · · · · · · · · · · ·                       |     |

| 12.11.3  |                                                             |     |

### **Table of Contents**

# Chapter 13 Multiple Serial Interface (MSI)

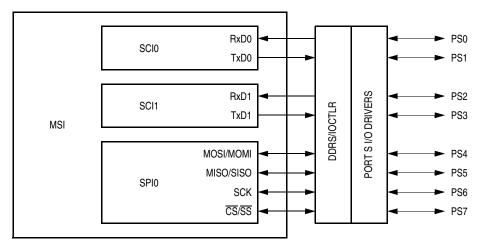

| 13.1           | Introduction                                   | 143 |

|----------------|------------------------------------------------|-----|

| 13.2           | SCI Features                                   | 143 |

| 13.3           | SPI Features                                   |     |

| 13.4           | MSI Block Diagram                              |     |

| 13.5           | MSI Register Map                               |     |

|                |                                                |     |

| 13.6<br>13.6.1 | General-Purpose I/O Ports                      |     |

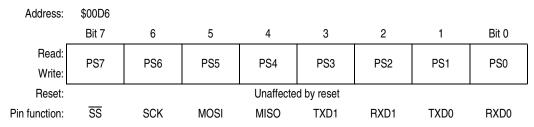

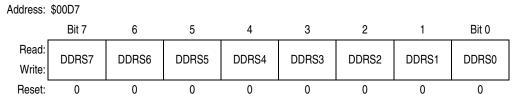

| 13.6.2         | Port S Data Register                           |     |

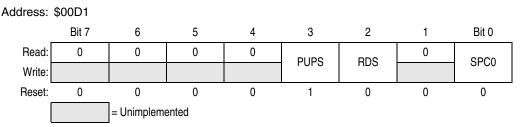

| 13.6.2         | Port S Pullup and Reduced Drive Control        |     |

| 13.6.4         | Port S Wired-OR Mode Control                   |     |

| 10.0.4         | Totto Wilca-Off Mode Control                   | 143 |

|                | Chapter 14                                     |     |

|                | Serial Communications Interface Module (SCI)   |     |

| 14.1           | Introduction                                   | 151 |

| 14.2           | Features                                       |     |

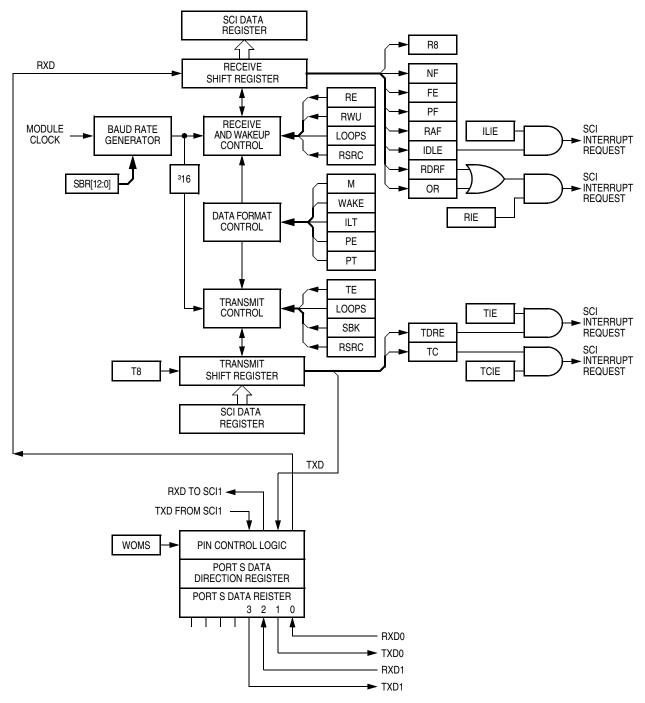

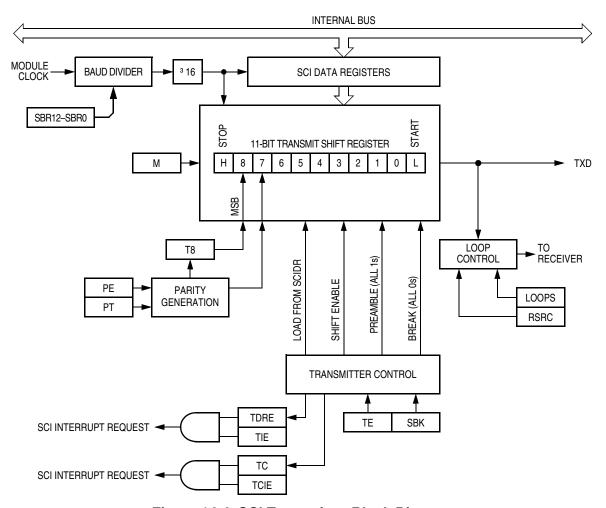

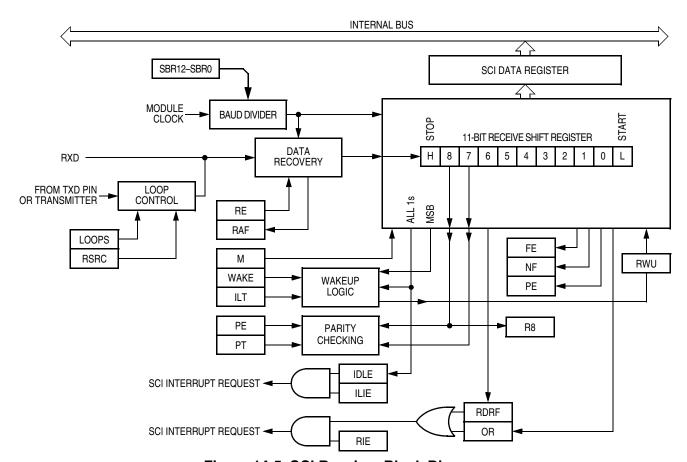

| 14.3           | Block Diagram                                  |     |

| 14.4           | Register Map                                   |     |

| 14.5           | Functional Description                         |     |

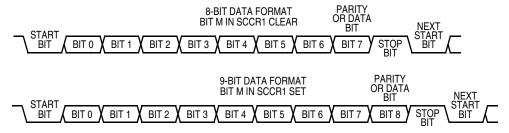

| 14.5.1         | Data Format                                    |     |

| 14.5.1         | Baud Rate Generation                           |     |

| 14.5.2         | Transmitter                                    |     |

| 14.5.3.        |                                                |     |

| 14.5.3.        |                                                |     |

| 14.5.3.        |                                                |     |

| 14.5.3.        |                                                |     |

| 14.5.4         | Receiver                                       |     |

| 14.5.4.        |                                                |     |

| 14.5.4.        |                                                |     |

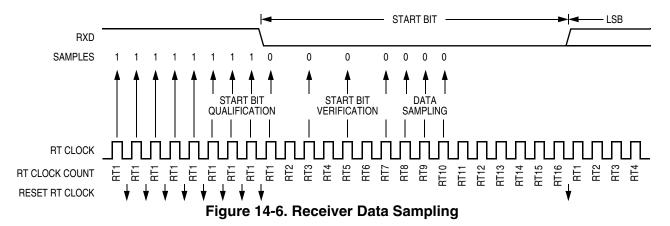

| 14.5.4.        | 3 Data Sampling                                | 160 |

| 14.5.4.        | 4 Framing Errors                               | 164 |

| 14.5.4.        |                                                | 164 |

| 14.5.4.        | · · · · · · · · · · · · · · · · · · ·          |     |

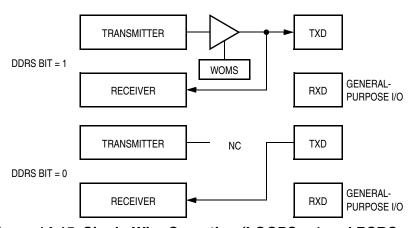

| 14.5.5         | Single-Wire Operation                          |     |

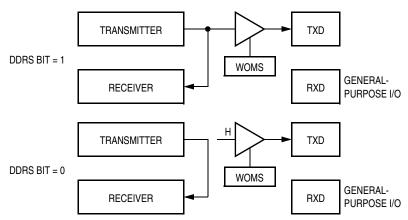

| 14.5.6         | Loop Operation                                 |     |

| 14.6           | Register Descriptions and Reset Initialization |     |

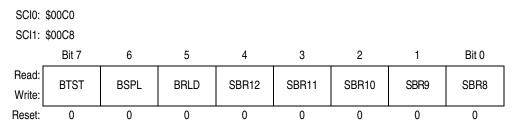

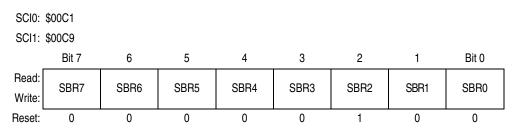

| 14.6.1         | SCI Baud Rate Registers                        |     |

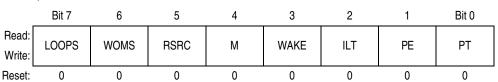

| 14.6.2         | SCI Control Register 1                         |     |

| 14.6.3         | SCI Control Register 2                         |     |

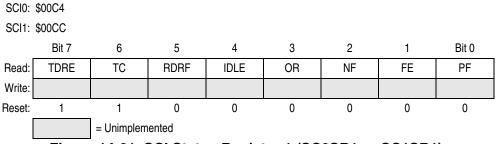

| 14.6.4         | SCI Status Register 1                          |     |

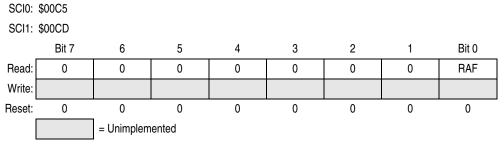

| 14.6.5         | SCI Status Register 2                          |     |

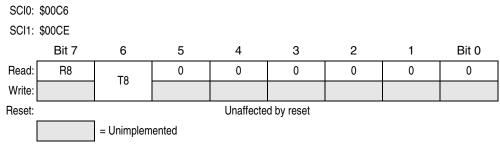

| 14.6.6         | SCI Data Registers                             |     |

| 14.7           | External Pin Descriptions                      |     |

| 14.7.1         | TXD Pin                                        |     |

| 14.7.2         | RXD Pin                                        | 1/5 |

| 14.8 Modes of Operation                                 | 175 |

|---------------------------------------------------------|-----|

| 14.9 Low-Power Options                                  | 175 |

| 14.9.1 Run Mode                                         |     |

| 14.9.2 Wait Mode                                        | 175 |

| 14.9.3 Stop Mode                                        | 175 |

| 14.10 Interrupt Sources                                 | 176 |

| 14.11 General-Purpose I/O Ports                         |     |

| 14.12 Serial Character Transmission Using the SCI       |     |

| 14.12.1 Equipment                                       |     |

| 14.12.2 Code Listing                                    |     |

|                                                         |     |

| Chapter 15                                              |     |

| Serial Peripheral Interface (SPI)                       |     |

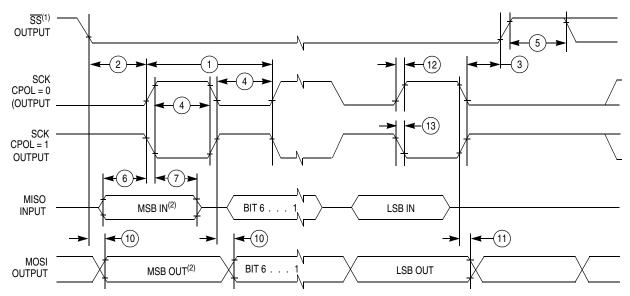

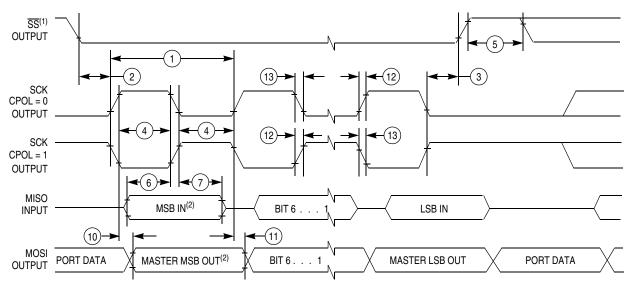

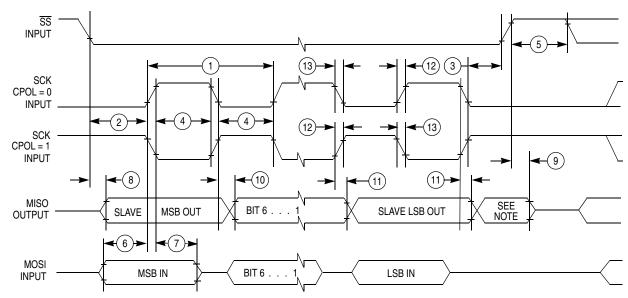

| 15.1 Introduction                                       | 179 |

| 15.2 Features                                           | 179 |

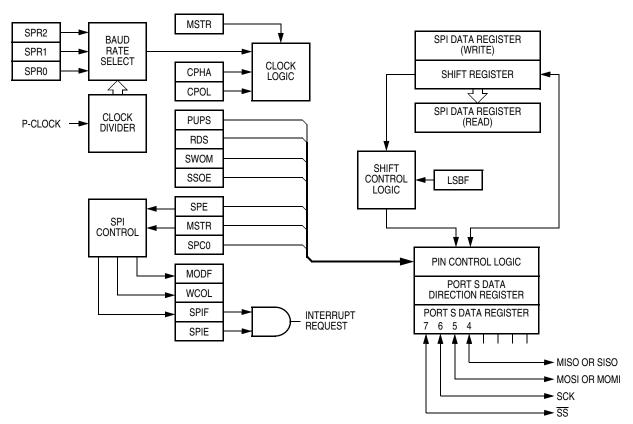

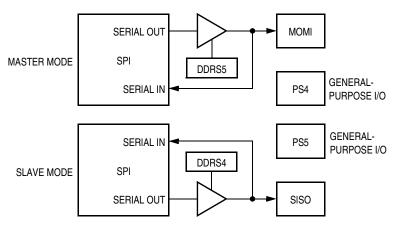

| 15.3 Block Diagram                                      | 180 |

| 15.4 Register Map                                       | 181 |

| 15.5 Functional Description                             | 182 |

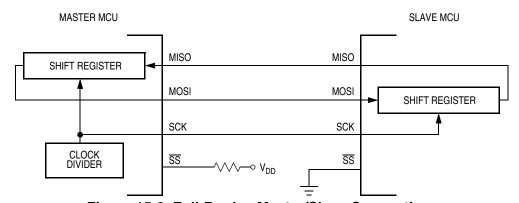

| 15.5.1 Master Mode                                      |     |

| 15.5.2 Slave Mode                                       | 182 |

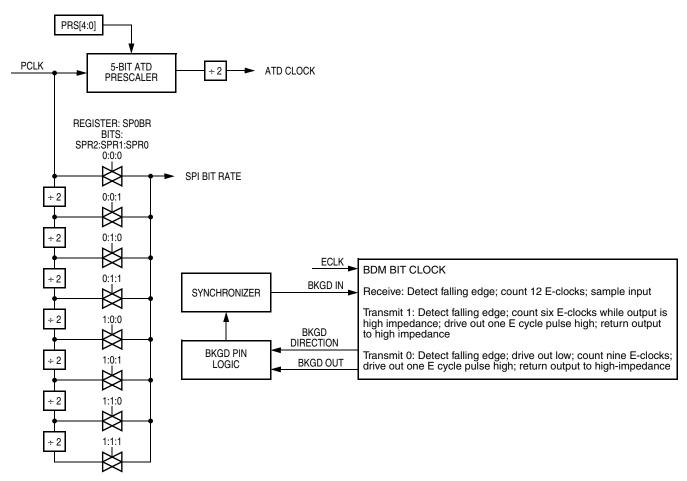

| 15.5.3 Baud Rate Generation                             | 183 |

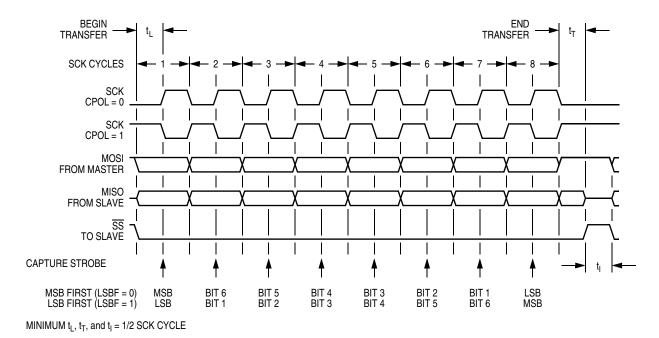

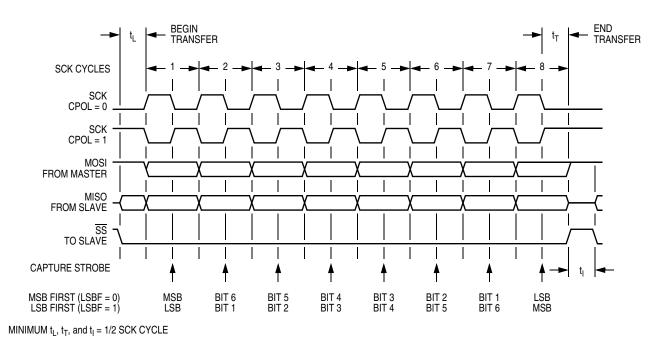

| 15.5.4 Clock Phase and Polarity                         | 183 |

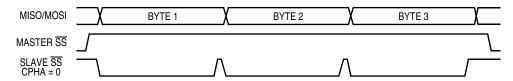

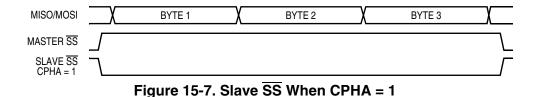

| 15.5.5 SS Output                                        |     |

| 15.5.6 Single-Wire Operation                            |     |

| 15.6 SPI Register Descriptions and Reset Initialization |     |

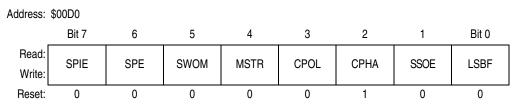

| 15.6.1 SPI Control Register 1                           |     |

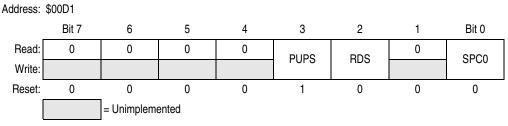

| 15.6.2 SPI Control Register 2                           |     |

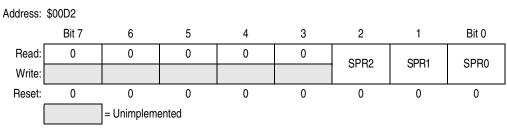

| 15.6.3 SPI Baud Rate Register                           |     |

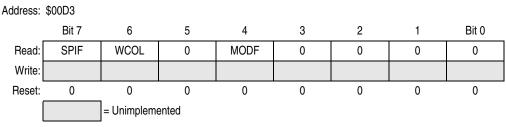

| 15.6.4 SPI Status Register                              |     |

| 15.6.5 SPI Data Register                                |     |

| 15.7 External Pins                                      |     |

| 15.7.1 MISO (Master In, Slave Out)                      |     |

| 15.7.2 MOSI (Master Out, Slave In)                      |     |

| 15.7.4 SS (Slave Select)                                |     |

| 15.8 Low-Power Options                                  |     |

| 15.8.1 Run Mode                                         |     |

| 15.8.2 Wait Mode                                        |     |

| 15.8.3 Stop Mode                                        |     |

| 15.9 Interrupt Sources                                  |     |

| 15.10 General-Purpose I/O Ports                         |     |

| 15.11 Synchronous Character Transmission Using the SPI  |     |

| 15.11.1 Equipment                                       |     |

| 15.11.2 Code Listing                                    |     |

| 15.11.2                                                 | 194 |

### **Table of Contents**

# Chapter 16 Analog-to-Digital Converter (ATD)

| 16.1             | Introduction                                    | 195 |

|------------------|-------------------------------------------------|-----|

| 16.2             | Features                                        | 195 |

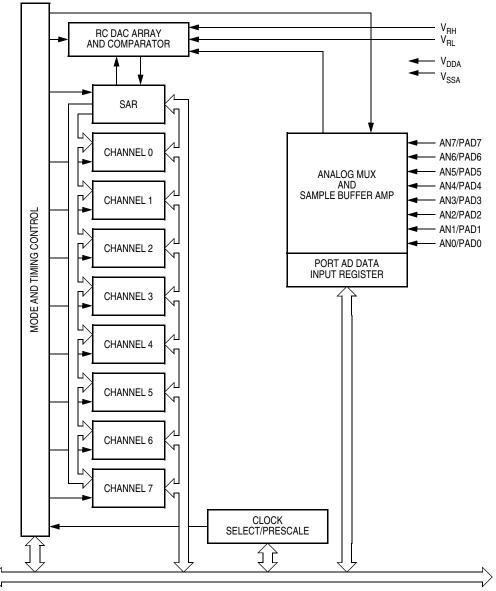

| 16.3             | Block Diagram                                   | 196 |

| 16.4             | Register Map                                    | 197 |

| 16.5             | Functional Description                          | 198 |

| 16.6             | Registers and Reset Initialization              | 199 |

| 16.6.1           | ATD Control Register 0                          |     |

| 16.6.2           | ATD Control Register 1                          |     |

| 16.6.3           | ATD Control Register 2                          |     |

| 16.6.4           | ADT Control Register 3                          |     |

| 16.6.5           | ATD Control Register 4                          |     |

| 16.6.6<br>16.6.7 | ATD Status Registers                            |     |

| 16.6.8           | ATD Status RegistersATD Test Registers          |     |

| 16.6.9           | ATD Result Registers                            |     |

| 16.7             | Low-Power Options                               |     |

| 16.7.1           | Run Mode.                                       |     |

| 16.7.2           | Wait Mode                                       |     |

| 16.7.3           | Stop Mode                                       |     |

| 16.8             | Interrupt Sources                               | 207 |

| 16.9             | General-Purpose Ports                           | 207 |

| 16.10            | Port AD Data Register                           |     |

| 16.11            | Using the ATD to Measure a Potentiometer Signal |     |

| 16.11.1          |                                                 |     |

| 16.11.2          |                                                 |     |

|                  | Observator 47                                   |     |

|                  | Chapter 17 Development Support                  |     |

| 17.1             | Introduction                                    | 211 |

| 17.1<br>17.2     | Instruction Queue.                              |     |

| 17.2<br>17.3     | Background Debug Mode (BDM)                     |     |

| 17.3<br>17.3.1   | BDM Serial Interface                            |     |

| 17.3.1           | Enabling BDM Firmware Commands                  |     |

| 17.3.3           | BDM Commands                                    |     |

| 17.4             | BDM Registers                                   |     |

| 17.4.1           | BDM Instruction Register                        |     |

| 17.4.1.          |                                                 |     |

| 17.4.1.          |                                                 |     |

| 17.4.2           | BDM Status Register                             |     |

| 17.4.3           | BDM Shift Register.                             |     |

| 17.4.4           | BDM Address Register                            |     |

| 17.4.5           | BDM CCR Holding Register                        |     |

| 17.5             | Instruction Tagging                             | 220 |

# Chapter 18 Electrical Characteristics

| 18.1  | Maximum Ratings                            | 221 |

|-------|--------------------------------------------|-----|

| 18.2  | Functional Operating Range                 | 222 |

| 18.3  | Thermal Characteristics                    | 222 |

| 18.4  | DC Electrical Characteristics              | 223 |

| 18.5  | Supply Current                             | 224 |

| 18.6  | ATD Maximum Ratings                        | 224 |

| 18.7  | ATD DC Electrical Characteristcs           | 225 |

| 18.8  | Analog Converter Operating Characteristics | 225 |

| 18.9  | ATD AC Operating Characteristics           | 226 |

| 18.10 | EEPROM Characteristics                     | 226 |

| 18.11 | Control Timing                             | 227 |

| 18.12 | Peripheral Port Timing                     | 231 |

|       | Non-Multiplexed Expansion Bus Timing       |     |

| 18.14 | SPI Timing                                 | 234 |

|       | Chapter 19                                 |     |

| 19.1  | Mechanical Specifications  Introduction    | 007 |

| _     |                                            |     |

| 19.2  | Package Dimensions                         | 23/ |

**Table of Contents**

# Chapter 1 General Description

### 1.1 Introduction

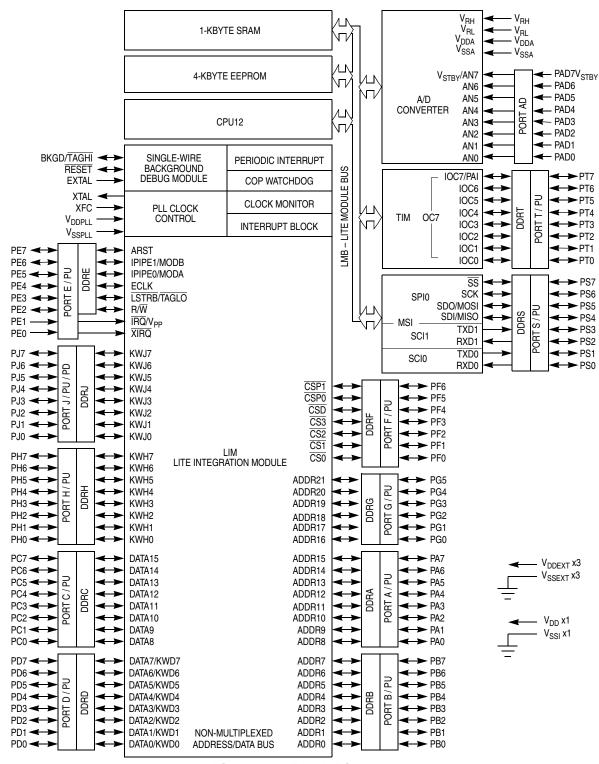

The MC68HC812A4 microcontroller unit (MCU) is a 16-bit device composed of standard on-chip peripheral modules connected by an intermodule bus. Modules include:

- 16-bit central processor unit (CPU12)

- Lite integration module (LIM)

- Two asynchronous serial communications interfaces (SCI0 and SCI1)

- Serial peripheral interface (SPI)

- Timer and pulse accumulator module

- 8-bit analog-to-digital converter (ATD)

- 1-Kbyte random-access memory (RAM)

- 4-Kbyte electrically erasable, programmable read-only memory (EEPROM)

- Memory expansion logic with chip selects, key wakeup ports, and a phase-locked loop (PLL)

# 1.2 Features

Features of the MC68HC812A4 include:

- Low-power, high-speed M68HC12 CPU

- · Power-saving stop and wait modes

- Memory:

- 1024-byte RAM

- 4096-byte EEPROM

- On-chip memory mapping allows expansion to more than 5-Mbyte address space

- Single-wire background debug mode

- Non-multiplexed address and data buses

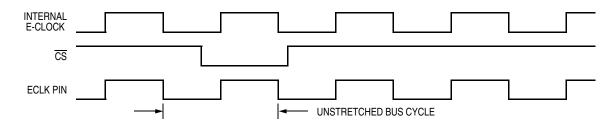

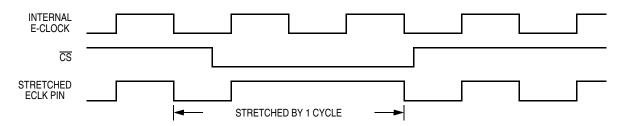

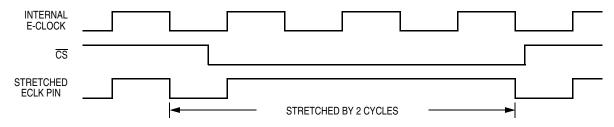

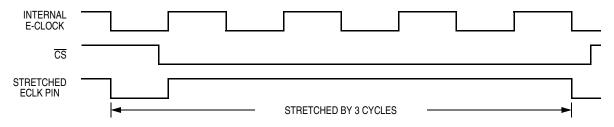

- Seven programmable chip-selects with clock stretching (expanded modes)

- 8-channel, enhanced 16-bit timer with programmable prescaler:

- All channels configurable as input capture or output compare

- Flexible choice of clock source

- 16-bit pulse accumulator

- Real-time interrupt circuit

- Computer operating properly (COP) watchdog

- Clock monitor

- Phase-locked loop (PLL)

- Two enhanced asynchronous non-return-to-zero (NRZ) serial communication interfaces (SCI)

- Enhanced synchronous serial peripheral interface (SPI)

- 8-channel, 8-bit analog-to-digital converter (ATD)

- Up to 24 key wakeup lines with interrupt capability

- Available in 112-lead low-profile quad flat pack (LQFP) packaging

# 1.3 Ordering Information

The MC68HC812A4 is available in 112-lead low-profile quad flat pack (LQFP) packaging.

Operating temperature range and voltage requirements are specified when ordering the MC68HC812A4 device. Refer to Table 1-1 for part numbers and to Figure 1-1 for details of the device numbering system.

Table 1-1. Ordering Information

| Order Number    | Temp         | erature    | Voltage | Frequency |

|-----------------|--------------|------------|---------|-----------|

| Order Number    | Range        | Designator | Voltage | (MHz)     |

| MC68HC812A4CPV8 | -40 to +85°C | С          | 5.0     | 8.0       |

| XC68HC812A4PV5  | 0 to +70°C   | _          | 3.3     | 5.0       |

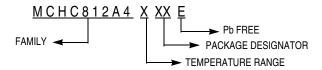

Figure 1-1. Device Numbering System

Evaluation boards, assemblers, compilers, and debuggers are available from Freescale and from third-party suppliers. An up-to-date list of products that support the M68HC12 Family of microcontrollers can be found on the World Wide Web at this URL:

http://freescale.com

Documents to assist in product selection are available from the Freescale Literature Distribution Center or local Freescale sales offices.

# 1.4 Block Diagram

Figure 1-2. Block Diagram

# 1.5 Signal Descriptions

#### NOTE

A line over a signal name indicates an active low signal. For example, RESET is active high and  $\overline{RESET}$  is active low.

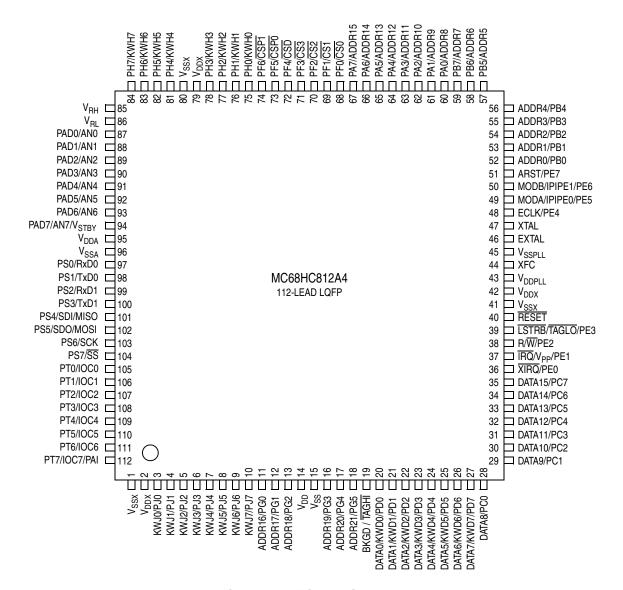

The MC68HC812A4 is available in a 112-lead low-profile quad flat pack (LQFP). The pin assignments are shown in Figure 1-3. Most pins perform two or more functions, as described in Table 1-2. Individual ports are cross referenced in Table 1-3 and Table 1-4.

Figure 1-3. Pin Assignments

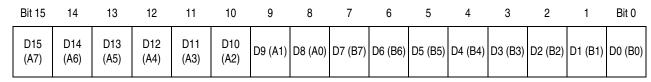

# **Table 1-2. Pin Descriptions**

| Pin                                     | Port       | Description                                                                                                                            |

|-----------------------------------------|------------|----------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>DD</sub> , V <sub>SS</sub>       | _          | Operating voltage and ground for the MCU <sup>(1)</sup>                                                                                |

| V <sub>RH</sub> , V <sub>RL</sub>       | _          | Reference voltages for the ADC                                                                                                         |

| AV <sub>DD</sub> , AV <sub>SS</sub>     | _          | Operating voltage and ground for the ADC <sup>(2)</sup>                                                                                |

| V <sub>DDPLL</sub> , V <sub>SSPLL</sub> | _          | Power and ground for PLL clock control                                                                                                 |

| V <sub>STBY</sub>                       | Port<br>AD | RAM standby power input                                                                                                                |

| XTAL, EXTAL                             | _          | Input pins for either a crystal or a CMOS compatible clock <sup>(3)</sup>                                                              |

| XIRQ                                    | PE0        | Asynchronous, non-maskable external interrupt request input                                                                            |

| ĪRQ                                     | PE1        | Asynchronous, maskable external interrupt request input with selectable falling-edge triggering or low-level triggering                |

| R/W                                     | PE2        | Expansion bus data direction indicator General-purpose I/O; read/write in expanded modes                                               |

| LSTRB                                   | PE3        | Low byte strobe (0 = low byte valid) <sup>(4)</sup> General-purpose I/O                                                                |

| ECLK                                    | PE4        | Timing reference output for external bus clock (normally, half the crystal frequency) General-purpose I/O                              |

| BKGD                                    | _          | Mode-select pin determines initial operating mode of the MCU after reset                                                               |

| MODA                                    | PE5        | Mode-select input determines initial operating mode of the MCU after reset <sup>(5)</sup>                                              |

| MODB                                    | PE6        | Mode-select input determines initial operating mode of the MCU after reset <sup>(5)</sup>                                              |

| IPIPE0                                  | PE5        | Instruction queue tracking signals for development systems                                                                             |

| IPIPE1                                  | PE6        | instruction queue tracking signals for development systems                                                                             |

| ARST                                    | PE7        | Alternate active-high reset input<br>General-purpose I/O                                                                               |

| XFC                                     | _          | Loop filter pin for controlled damping of PLL VCO loop                                                                                 |

| RESET                                   | _          | Active-low bidirectional control signal; input initializes MCU to known startup state; output when COP or clock monitor causes a reset |

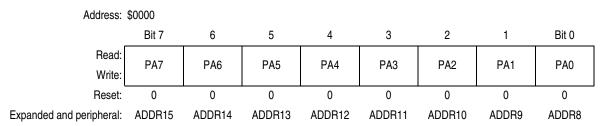

| ADDR15-ADDR8                            | Port A     |                                                                                                                                        |

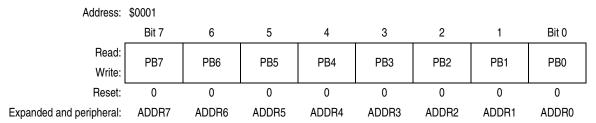

| ADDR7-ADDR0                             | Port B     | Single-chip modes: general-purpose I/O Expanded modes: external bus pins                                                               |

| DATA15-DATA8                            | Port C     | Port D in narrow data bus mode: general-purpose I/O or key wakeup port                                                                 |

| DATA7-DATA0                             | Port D     |                                                                                                                                        |

| ADDR21-ADDR16                           | Port G     | Memory expansion and general-purpose I/O                                                                                               |

| CS3–CS0,CSD,<br>CSP1, CSP0              | Port F     | Chip selects General-purpose I/O                                                                                                       |

| BKGD                                    | _          | Single-wire background debug pin Mode-select pin that determines special or normal operating mode after reset                          |

| KWD7–KWD0                               | Port D     | Key wakeup pins that can generate interrupt requests on high-to-low transitions                                                        |

| KWH7–KWH0                               | Port H     | General-purpose I/O                                                                                                                    |

| KWJ7–KWJ0                               | Port J     | Key wakeup pins that can generate interrupt requests on any transition<br>General-purpose I/O                                          |

| RxD0                                    | PS0        | Receive pin for SCI0                                                                                                                   |

| TxD0                                    | PS1        | Transmit pin for SCI0                                                                                                                  |

# MC68HC812A4 Data Sheet, Rev. 7

# **Table 1-2. Pin Descriptions (Continued)**

| Pin       | Port   | Description                                                                  |

|-----------|--------|------------------------------------------------------------------------------|

| RxD1      | PS2    | Receive pin for SCI1                                                         |

| TxD1      | PS3    | Transmit pin for SCI1                                                        |

| SDI/MISO  | PS4    | Master in/slave out pin for SPI                                              |

| SDO/MOSI  | PS5    | Master out/slave in pin for SPI                                              |

| SCK       | PS6    | Serial clock for SPI                                                         |

| SS        | PS7    | Slave select output for SPI in master mode; slave select input in slave mode |

| IOC7-IOC0 | Port T | Input capture or output compare channels and pulse accumulator input         |

- 1. The MCU operates from a single power supply. Use the customary bypass techniques as very fast signal transitions occur on MCU pins.

- 2. Separate power supply pins allow the ADC power supply to be bypassed independently of the MCU power supply.

- 3. Out of reset the frequency applied to EXTAL is twice the desired E-clock rate. On reset all device clocks are derived from the EXTAL input frequency. XTAL is the crystal output.

- 4. LSTRB is the exclusive-NOR of A0 and the internal SZ8 signal. SZ8 indicates the size 16/8 access.

- 5. After reset, MODA and MODB can be configured as instruction queue tracking signals IPIPE0 and IPIPE1 or as general-purpose I/O pins.

# **Table 1-3. Port Descriptions**

| Port    | Direction                | Function                                                                                                                                                     |

|---------|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Port A  | I/O                      | Single-chip modes: general-purpose I/O Expanded modes: external address bus ADDR15–ADDR8                                                                     |

| Port B  | I/O                      | Single-chip modes: general-purpose I/O Expanded modes: external address bus ADDR7–ADDR0                                                                      |

| Port C  | I/O                      | Single-chip modes: general-purpose I/O Expanded wide modes: external data bus DATA15-DATA8 Expanded narrow modes: external data bus DATA15-DATA8/DATA7-DATA0 |

| Port D  | I/O                      | Single-chip and expanded narrow modes: general-purpose I/O External data bus DATA7-DATA0 in expanded wide mode <sup>(1)</sup>                                |

| Port E  | I/O and I <sup>(2)</sup> | External interrupt request inputs, mode select inputs, bus control signals General-purpose I/O                                                               |

| Port F  | I/O                      | Chip select General-purpose I/O                                                                                                                              |

| Port G  | I/O                      | Memory expansion General-purpose I/O                                                                                                                         |

| Port H  | I/O                      | Key wakeup <sup>(3)</sup> General-purpose I/O                                                                                                                |

| Port J  | I/O                      | Key wakeup <sup>(4)</sup> General-purpose I/O                                                                                                                |

| Port S  | I/O                      | SCI and SPI ports<br>General-purpose I/O                                                                                                                     |

| Port T  | I/O                      | Timer port General-purpose I/O                                                                                                                               |

| Port AD | I                        | ADC port General-purpose input                                                                                                                               |

- 1. Key wakeup interrupt request can occur when an input goes from high to low.

- 2. PE1 and PE0 are input-only pins.

- 3. Key wakeup interrupt request can occur when an input goes from high to low.

- 4. Key wakeup interrupt request can occur when an input goes from high to low or from low to high.

#### MC68HC812A4 Data Sheet, Rev. 7

Table 1-4. Port Pullup, Pulldown, and Reduced Drive Summary

|                                  |                            | En                    | able Bit       |                | Reduced Dri                   | ve Contro   | l Bit          |  |

|----------------------------------|----------------------------|-----------------------|----------------|----------------|-------------------------------|-------------|----------------|--|

| Port<br>Name                     | Resistive<br>Input Loads   | Register<br>(Address) | Bit Name       | Reset<br>State | Register<br>(Address)         | Bit<br>Name | Reset<br>State |  |

| Port A                           | Pullup                     | PUCR (\$000C)         | PUPA           | Enabled        | RDRIV (\$000D)                | RDPAB       | Full drive     |  |

| Port B                           | Pullup                     | PUCR (\$000C)         | PUPB           | Enabled        | RDRIV (\$000D)                | RDPAB       | Full drive     |  |

| Port C                           | Pullup                     | PUCR (\$000C)         | PUPC           | Enabled        | RDRIV (\$000D)                | RDPC        | Full drive     |  |

| Port D                           | Pullup                     | PUCR (\$000C)         | PUPD           | Enabled        | RDRIV (\$000D)                | Full drive  |                |  |

| Port E:<br>PE7, PE3,<br>PE2, PE0 | Pullup                     | PUCR (\$000C)         | C) PUPE Enab   |                | RDRIV (\$000D)                | RDPE        | Full drive     |  |

| Port E:<br>PE1                   | Pullup                     | Alway                 | s enabled      |                | RDRIV (\$000D)                | RDPE        | Full drive     |  |

| Port E:<br>PE4                   | None                       |                       | _              |                | RDRIV (\$000D)                | RDPE        | Full drive     |  |

| Port E:<br>PE6 and PE5           | Pulldown                   | Enabled               | I during reset |                | _                             | _           | -              |  |

| Port F                           | Pullup                     | PUCR (\$000C)         | PUPF           | Enabled        | RDRIV (\$000D)                | RDPF        | Full drive     |  |

| Port G                           | Pullup                     | PUCR (\$000C)         | PUPG           | Enabled        | RDRIV (\$000D)                | RDPG        | Full drive     |  |

| Port H                           | Pullup                     | PUCR (\$000C)         | PUPH           | Enabled        | RDRIV (\$000D)                | RDPH        | Full drive     |  |

| Port J                           | Pullup/down <sup>(1)</sup> | PULEJ (\$002E)        | PULEJ[7:0]     | Disabled       | RDRIV (\$000D)                | RDPJ        | Full drive     |  |

| Port S                           | Pullup                     | SP0CR2 (\$00D1)       | PUPS           | Enabled        | SP0CR2 (\$00D1)               | RDS         | Full drive     |  |

| Port T                           | Pullup                     | TMSK2 (\$008D)        | PUPT           | Enabled        | TMSK2 (\$008D) RDPT Full driv |             |                |  |

| Port AD                          | None                       |                       |                |                |                               |             |                |  |

| BKGD                             | Pullup                     | _                     | — Enabled —    |                | _                             | Full drive  |                |  |

<sup>1.</sup> Pullup or pulldown devices for each port J pin can be selected with the PUPSJ register (\$002D). After reset, pulldowns are selected for all port J pins but must be enabled with PULEJ register.

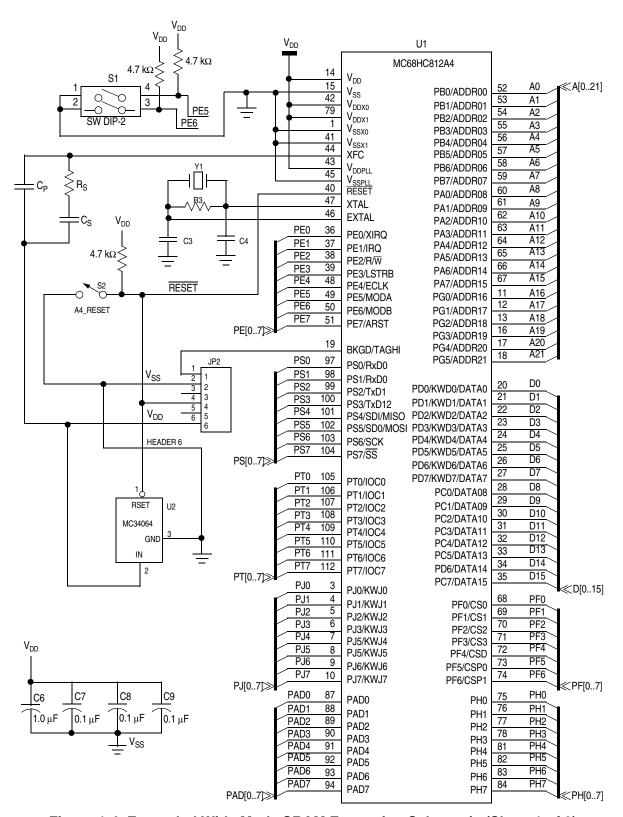

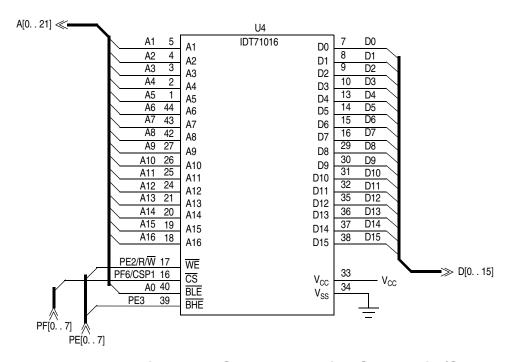

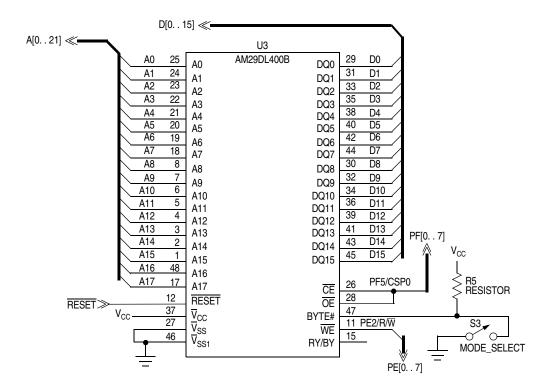

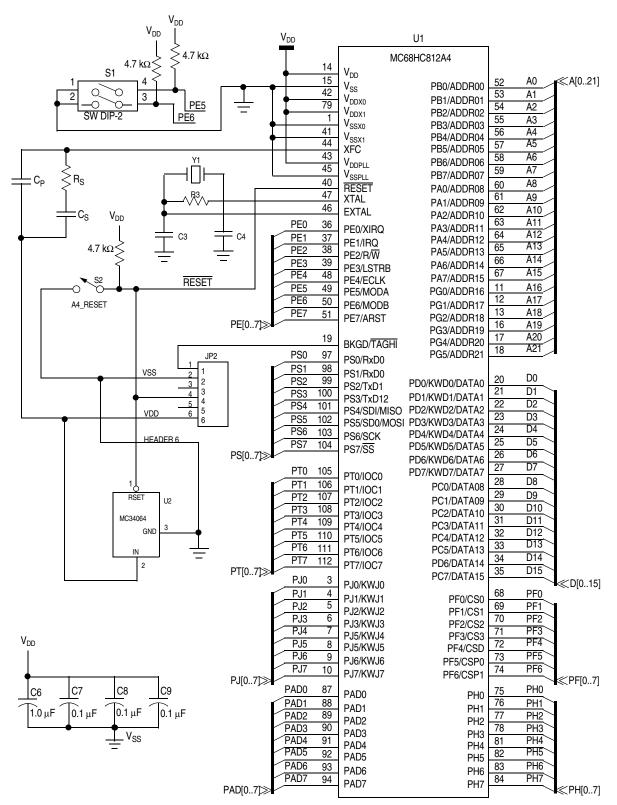

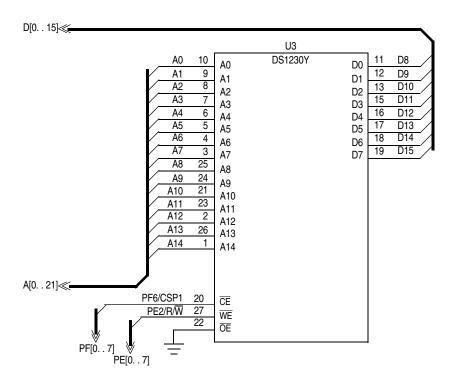

Figure 1-4. Expanded Wide Mode SRAM Expansion Schematic (Sheet 1 of 3)

Figure 1-4. Expanded Wide Mode SRAM Expansion Schematic (Sheet 2 of 3)

Figure 1-4. Expanded Wide Mode SRAM Expansion Schematic (Sheet 3 of 3)

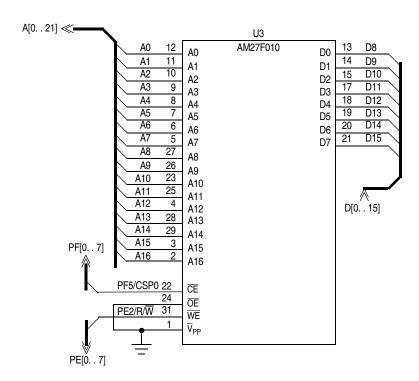

Figure 1-5. Expanded Narrow Mode SRAM Expansion Schematic (Sheet 1 of 3)

Figure 1-5. Expanded Narrow Mode SRAM Expansion Schematic (Sheet 2 of 3)

Figure 1-5. Expanded Narrow Mode SRAM Expansion Schematic (Sheet 3 of 3)

# Chapter 2 Register Block

# 2.1 Overview

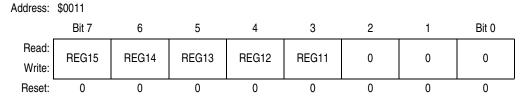

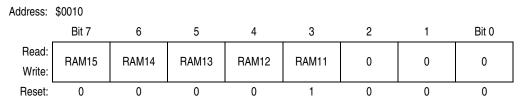

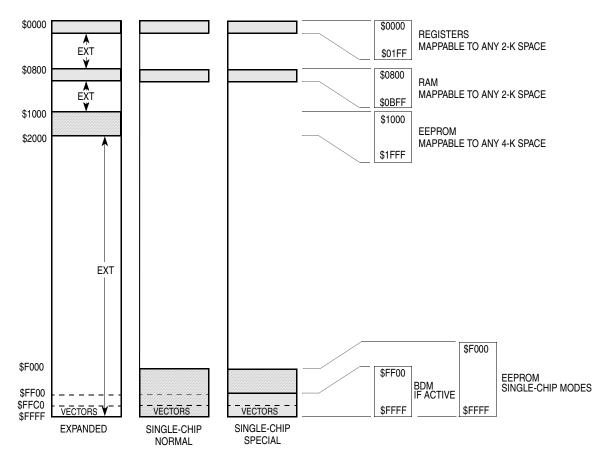

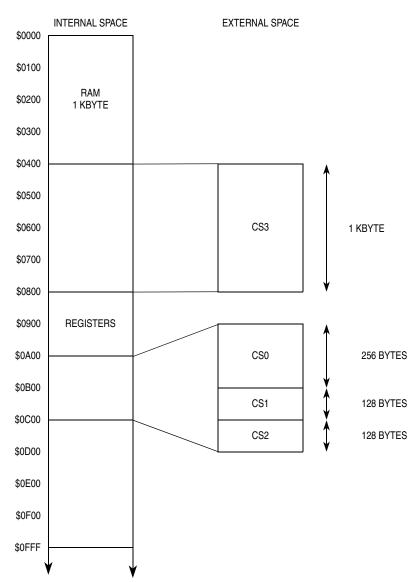

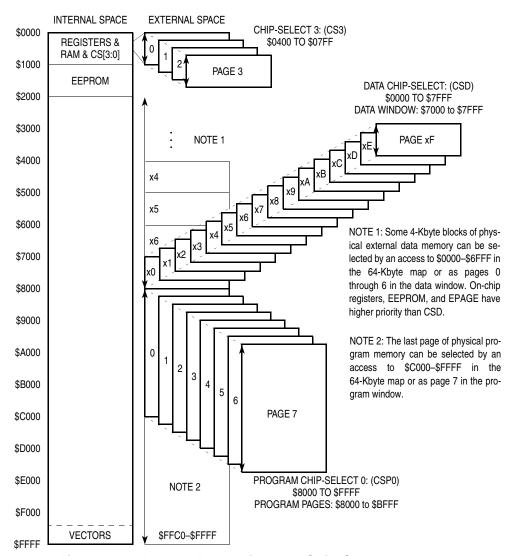

The register block can be mapped to any 2-Kbyte boundary within the standard 64-Kbyte address space by manipulating bits REG15–REG11 in the INITRG register. INITRG establishes the upper five bits of the register block's 16-bit address.

The register block occupies the first 512 bytes of the 2-Kbyte block. Figure 2-1 shows the default addressing.

# 2.2 Register Map

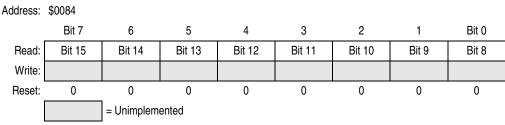

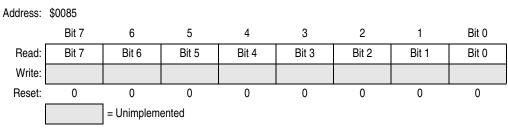

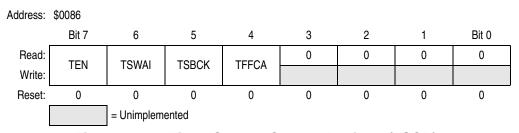

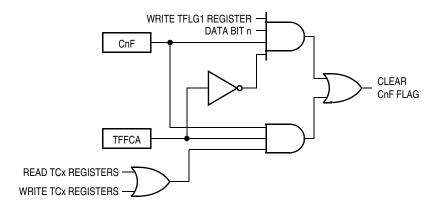

| Addr.  | Register Name                            |                 | Bit 7 | 6           | 5     | 4                      | 3     | 2     | 1            | Bit 0 |

|--------|------------------------------------------|-----------------|-------|-------------|-------|------------------------|-------|-------|--------------|-------|

| \$0000 | Port A Data Register<br>(PORTA)          | Read:<br>Write: | PA7   | PA6         | PA5   | PA4                    | PA3   | PA2   | PA1          | PA0   |

|        | See page 64.                             | Reset:          | 0     | 0           | 0     | 0                      | 0     | 0     | 0            | 0     |

| \$0001 | Port B Data Register (PORTB)             | Read:<br>Write: | PB7   | PB6         | PB5   | PB4                    | PB3   | PB2   | PB1          | PB0   |

|        | See page 65.                             | Reset:          | 0     | 0           | 0     | 0                      | 0     | 0     | 0            | 0     |

| \$0002 | Port A Data Direction<br>Register (DDRA) | Read:<br>Write: | DDRA7 | DDRA6       | DDRA5 | DDRA4                  | DDRA3 | DDRA2 | DDRA1        | DDRA0 |

|        | See page 64.                             | Reset:          | 0     | 0           | 0     | 0                      | 0     | 0     | 0            | 0     |

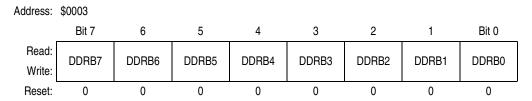

| \$0003 | Port B Data Direction<br>Register (DDRB) | Read:<br>Write: | DDRB7 | DDRB6       | DDRB5 | DDRB4                  | DDRB3 | DDRB2 | DDRB1        | DDRB0 |

|        | See page 65.                             | Reset:          | 0     | 0           | 0     | 0                      | 0     | 0     | 0            | 0     |

| \$0004 | Port C Data Register (PORTC)             | Read:<br>Write: | PC7   | PC6         | PC5   | PC4                    | PC3   | PC2   | PC1          | PC0   |

|        | See page 66.                             | Reset:          | 0     | 0           | 0     | 0                      | 0     | 0     | 0            | 0     |

| \$0005 | Port D Data Register<br>(PORTD)          | Read:<br>Write: | PD7   | PD6         | PD5   | PD4                    | PD3   | PD2   | PD1          | PD0   |

|        | See page 67.                             | Reset:          | 0     | 0           | 0     | 0                      | 0     | 0     | 0            | 0     |

| \$0006 | Port C Data Direction<br>Register (DDRC) | Read:<br>Write: | DDRC7 | DDRC6       | DDRC5 | DDRC4                  | DDRC3 | DDRC2 | DDRC1        | DDRC0 |

|        | See page 66.                             | Reset:          | 0     | 0           | 0     | 0                      | 0     | 0     | 0            | 0     |

|        |                                          |                 |       | = Unimpleme | ented | R = Reserved U = Unaff |       |       | U = Unaffect | ed    |

Figure 2-1. Register Map (Sheet 1 of 14)

# **Register Block**

| Addr.  | Register Name                                    | _               | Bit 7 | 6           | 5               | 4     | 3            | 2     | 1              | Bit 0 |  |

|--------|--------------------------------------------------|-----------------|-------|-------------|-----------------|-------|--------------|-------|----------------|-------|--|

| \$0007 | Port D Data Direction<br>Register (DDRD)         | Read:<br>Write: | Bit 7 | Bit 6       | Bit 5           | Bit 4 | Bit 3        | Bit 2 | Bit 1          | Bit 0 |  |

|        | See page 67.                                     | Reset:          | 0     | 0           | 0               | 0     | 0            | 0     | 0              | 0     |  |

| \$0008 | Port E Data Register<br>(PORTE)                  | Read:<br>Write: | PE7   | PE6         | PE5             | PD4   | PD3          | PD2   | PD1            | PD0   |  |

|        | See page 68.                                     | Reset:          | 0     | 0           | 0               | 0     | 1            | 0     | 0              | 0     |  |

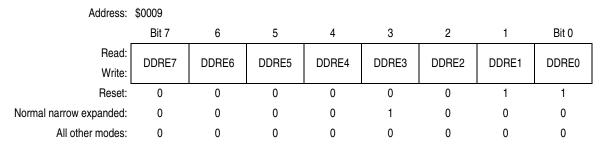

| \$0009 | Port E Data Direction<br>Register (DDRE)         | Read:<br>Write: | DDRE7 | DDRE6       | DDRE5           | DDRE4 | DDRE3        | DDRE2 | DDRE1          | DDRE0 |  |

|        | See page 68.                                     | Reset:          | 0     | 0           | 0               | 0     | 0            | 0     | 1              | 1     |  |

| \$000A | Port E Assignment<br>Register (PEAR)             | Read:<br>Write: | ARSIE | PLLTE       | PIPOE           | NECLK | LSTRE        | RDWE  | 0              | 0     |  |

|        | See page 69.                                     | Reset:          | 0     | 0           | 1               | 0     | 1            | 1     | 0              | 0     |  |

| \$000B | Mode Register (MODE)                             | Read:<br>Write: | SMODN | MODB        | MODA            | ESTR  | IVIS         | 0     | EMD            | EME   |  |

|        | See page 58.                                     | Reset:          | 0     | 0           | 0               | 1     | 1            | 0     | 1              | 1     |  |

| \$000C | Pullup Control<br>Register (PUCR)                | Read:<br>Write: | PUPH  | PUPG        | PUPF            | PUPE  | PUPD         | PUC   | PUPB           | PUPA  |  |

|        | See page 71.                                     | Reset:          | 1     | 1           | 1               | 1     | 1            | 1     | 1              | 1     |  |

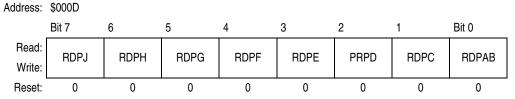

| \$000D | Reduced Drive<br>Register (RDRIV)                | Read:<br>Write: | RDPJ  | RDPH        | RDPG            | RDPF  | RDPE         | PRPD  | RDPC           | RDPAB |  |

|        | See page 72.                                     | Reset:          | 0     | 0           | 0               | 0     | 0            | 0     | 0              | 0     |  |

| \$000E | Reserved                                         |                 | R     | R           | R               | R     | R            | R     | R              | R     |  |

| \$000F | Reserved                                         |                 | R     | R           | R               | R     | R            | R     | R              | R     |  |

| \$0010 | RAM Initialization Register (INITRM)             | Read:<br>Write: | RAM15 | RAM14       | RAM13           | RAM12 | RAM11        | 0     | 0              | 0     |  |

|        | See page 60.                                     | Reset:          | 0     | 0           | 0               | 0     | 1            | 0     | 0              | 0     |  |

| \$0011 | Register Initialization<br>Register (INITRG)     | Read:<br>Write: | REG15 | REG14       | REG13           | REG12 | REG11        | 0     | 0              | 0     |  |

|        | See page 59.                                     | Reset:          | 0     | 0           | 0               | 0     | 0            | 0     | 0              | 0     |  |

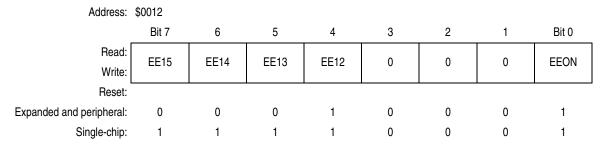

| \$0012 | EEPROM Initialization<br>Register (INITEE)       | Read:<br>Write: | EE15  | EE14        | EE13            | EE12  | 0            | 0     | 0              | EEON  |  |

|        | See page 60.                                     | Reset:          | 0     | 0           | 0               | 1     | 0            | 0     | 0              | 1     |  |

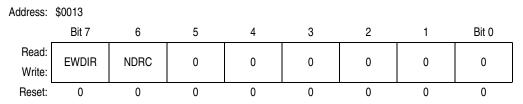

| \$0013 | Miscellaneous Mapping<br>Control Register (MISC) | Read:<br>Write: | EWDIR | NDRC        | 0               | 0     | 0            | 0     | 0              | 0     |  |

|        | See page 61.                                     | Reset:          | 0     | 0           | 0               | 0     | 0            | 0     | 0              | 0     |  |

|        |                                                  |                 |       | = Unimpleme | = Unimplemented |       | R = Reserved |       | U = Unaffected |       |  |

Figure 2-1. Register Map (Sheet 2 of 14)

| Addr.    | Register Name                                     |                 | Bit 7 | 6           | 5     | 4     | 3          | 2      | 1            | Bit 0 |  |

|----------|---------------------------------------------------|-----------------|-------|-------------|-------|-------|------------|--------|--------------|-------|--|

| \$0014   | Real-Tme Interrupt Control<br>Register (RTICTL)   | Read:<br>Write: | RTIE  | RSWAI       | RSBCK | 0     | RTBYP      | RTR2   | RTR1         | RTR0  |  |

|          | See page 105.                                     | Reset:          | 0     | 0           | 0     | 0     | 0          | 0      | 0            | 0     |  |

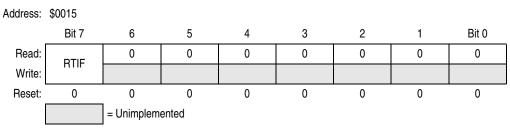

|          | Real-Time Interrupt Flag                          | Read:           | RTIF  | 0           | 0     | 0     | 0          | 0      | 0            | 0     |  |

| \$0015   | Register (RTIFLG) See page 107.                   | Write:          | niir  |             |       |       |            |        |              |       |  |

|          | 200 pago 1011                                     | Reset:          | 0     | 0           | 0     | 0     | 0          | 0      | 0            | 0     |  |

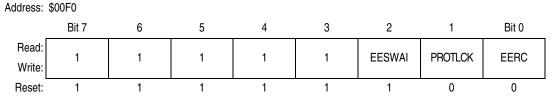

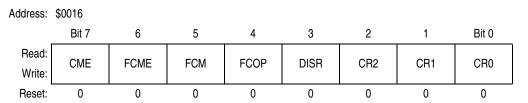

| \$0016   | COP Control Register<br>(COPCTL)<br>See page 107. | Read:<br>Write: | CME   | FCME        | FCM   | FCOP  | DISR       | CR2    | CR1          | CR0   |  |

|          | 200 pago 107.                                     | Reset:          | 0     | 0           | 0     | 0     | 0          | 1      | 1            | 1     |  |

|          | Arm/Reset COP Register                            | Read:           | 0     | 0           | 0     | 0     | 0          | 0      | 0            | 0     |  |

| \$0017   | (COPRST)                                          | Write:          | Bit 7 | Bit 6       | Bit 5 | Bit 4 | Bit 3      | Bit 2  | Bit 1        | Bit 0 |  |

|          | See page 109.                                     | Reset:          | 0     | 0           | 0     | 0     | 0          | 0      | 0            | 0     |  |

| \$0018   | Reserved                                          |                 | R     | R           | R     | R     | R          | R      | R            | R     |  |

| <b>↓</b> | <b>+</b>                                          | Г               |       |             |       |       |            |        |              |       |  |

| \$001D   | Reserved                                          | L               | R     | R           | R     | R     | R          | R      | R            | R     |  |

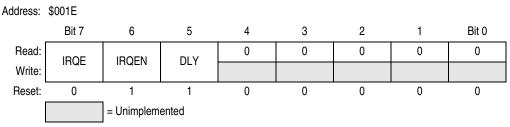

| \$001E   | Interrupt Control Register (INTCR)                | Read:<br>Write: | IRQE  | IRQEN       | DLY   | 0     | 0          | 0      | 0            | 0     |  |

|          | See page 51.                                      | Reset:          | 0     | 1           | 1     | 0     | 0          | 0      | 0            | 0     |  |

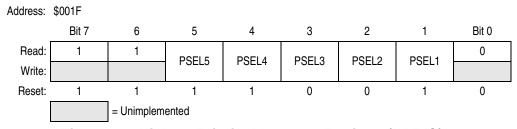

|          | Highest Priority I Interrupt                      | Read:           | 1     | 1           | DOELE | PSEL4 | DCEL 2     | DCEL 0 | DOEL 1       | 0     |  |

| \$001F   | Register (HPRIO)                                  | Write:          |       |             | PSEL5 | PSEL4 | PSEL3      | PSEL2  | PSEL1        |       |  |

|          | See page 51.                                      | Reset:          | 1     | 1           | 1     | 1     | 0          | 0      | 1            | 0     |  |

| \$0020   | Port D Key Wakeup<br>Interrupt Enable Register    | Read:<br>Write: | Bit 7 | Bit 6       | Bit 5 | Bit 4 | Bit 3      | Bit 2  | Bit 1        | Bit 0 |  |

|          | (KWIED) See page 94.                              | Reset:          | 0     | 0           | 0     | 0     | 0          | 0      | 0            | 0     |  |

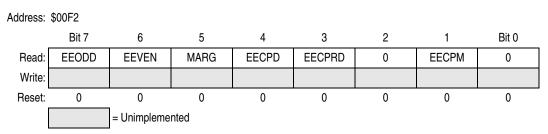

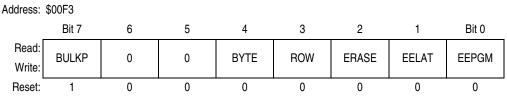

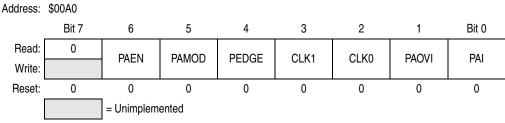

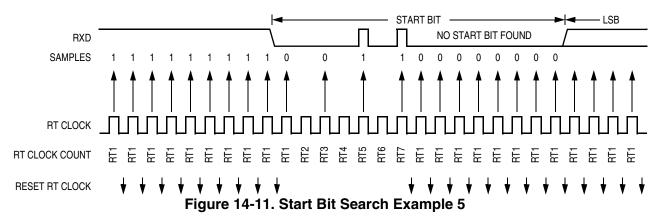

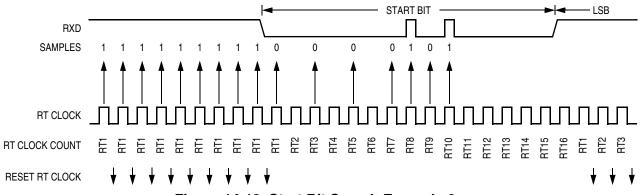

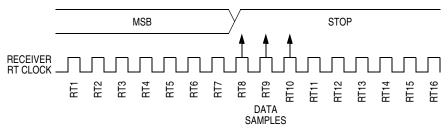

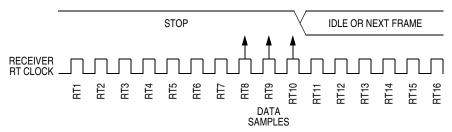

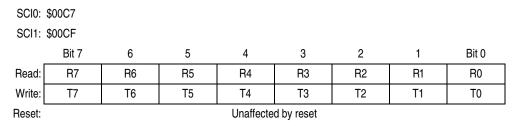

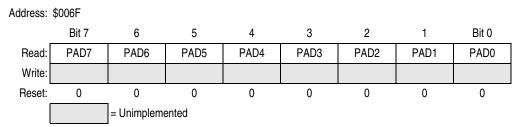

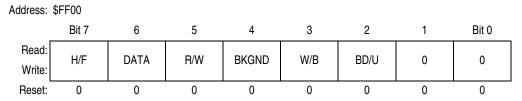

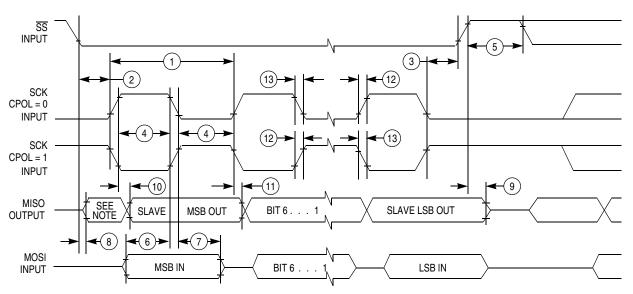

| \$0021   | Port D Key Wakeup Flag<br>Register (KWIFD)        | Read:<br>Write: | Bit 7 | Bit 6       | Bit 5 | Bit 4 | Bit 3      | Bit 2  | Bit 1        | Bit 0 |  |