# **GD3162\_SDS**

## Advanced IGBT/SiC gate driver with dynamic gate strength adjust

Rev. 2 — 12 January 2024

Product short data sheet

## 1 General description

The GD3162 is an advanced, galvanically isolated, single-channel gate driver designed to drive the latest SiC and IGBT modules for xEV traction inverters. The device does this while enabling space savings and performance improvements through advanced gate-drive functionality.

The GD3162 offers integrated galvanic isolation, a programmable interface via SPI, and advanced programmable protection features, such as overtemperature, desaturation, and current sense protection. GD3162 with integrated boost capability, can drive most SiC MOSFET and IGBT/SiC module gates directly and is able to shape the gate drive capability in order to improve the power device's switching performance and reduce voltage stress.

The control of the gate strength can be done using either SPI commands or the GS Enable Pins. GS\_ENH logic controls the drive strength of the turn on, and GS\_ENL controls the drive strength of the turn off. To further improve performance, these functions are designed to operate independent of each other. Three separate pullup drive strengths and three pulldown drive strengths are made available via trilevel functions on the input pins or commands in SPI.

The GD3162 autonomously manages faults and reports power device and gate driver status via the INTB pin. VCE/VDS monitoring, as well as VGE monitoring, can be selected to be output on the INTA/RTRPT pin.

The GD3162 includes self-test and control protection functions for design of high functional safety integrity level systems (ASIL C/D) and meets the stringent requirements of automotive applications, being fully AEC-Q100 grade 1 qualified.

#### 2 Features and benefits

This section summarizes the key features, safety features, and regulatory approvals for the GD3162.

#### 2.1 Key features

- Integrated galvanic signal isolation (up to 8 kV)

- Integrated boost capability for increased drive strength: Up to 10 A/ 20 A/ 30 A source/sink current available by gate strength selection

- SPI or 3-state enabled GS\_ENH and GS\_ENL low-voltage domain pins to dynamically control gate drive strength. Adjustment of gate strength up to 20 KHz supported

- Dual gate pullup pins and dual gate pulldown pins for enhanced drive capability, synchronous adjustment of gate strength, reduced thermal loading during weak drive, and independent verification of each drive state operation

- SPI programmable ISEN/COMP setpoint, to allow the gate driver to automatically control gate drive strength based on high-voltage domain inputs.

- Temperature sense pins compatible with NTC and PTC thermistors allow for local control of temperaturebased gate-drive strength, as well as power device temperature monitoring via AOUT pin or SPI.

- Programmable ADC delay Up to 8 μs sampling delay from rising or falling edge of PWM.

- Active Bus Discharge Functionality (MGD3162AM551EK and MGD3162AM581EK only) Provides either MCU controlled or Safety Logic Controlled Gate drive to actively discharge the DC Link Capacitor.

- VDS measurement capability for RDSon and junction temperature estimation

- SPI interface for safety monitoring, configuration, and diagnostic reporting

- VCE power device monitoring via the low-voltage domain INTA/RTRPT pin

- Supports high PWM switching frequencies: PWM up to 100 kHz, thermally limited

- Fail-safe state management from LV and HV domain for user-selectable safe state

- Configurable desaturation and current sense optimized for protecting SiC and IGBTs against short circuit in less than 1 µs

- INTA/RTRPT and INTB Interrupt pins for current and voltage Fault Reporting and, if selected, VCE or VGE real-time reporting.

- Advanced two-level turn-off (2LTO) in combination with soft shutdown gate current to reduce current and voltage stress associated with rapid turnoff.

- CMTI > 100 V/ns

#### 2.2 Safety features

- · Certified compliant with ISO 26262, supporting ASIL D level functional safety

- · Error checking of SPI and configuration data with 8-bit CRC

- Autonomously manages severe faults and reports status via configurable INTB and/or INTA/RTRPT pins, and SPI interface

- VCE/VGE real-time cycle-by-cycle monitoring and reporting for feedback of power device status.

- · Built-in self-test (BIST) of all analog and digital circuits

- · Continuous watchdog of communications across isolation barrier

- · Deadtime enforcement

- Overvoltage and undervoltage supervision of 5 V bias supply for LV circuitry

- Overvoltage and undervoltage supervision of VCC supply for HV circuitry

- Dedicated fail-safe state management pins on both low-voltage and high-voltage sides

GD3162\_SDS

GD3162\_SDS

Advanced IGBT/SiC gate driver with dynamic gate strength adjust

## 2.3 Safety and regulatory approvals

- Reinforced isolation per DIN V VDE V 0884-10

- Withstand 5000 V rms (1 minute) isolation per UL 1577

- AEC-Q100 grade 1 automotive qualified

## 3 Ordering information

Table 1. Orderable part variations

| Part number <sup>[1]</sup>                         | VDD (V) | External clearance and creepage distance (mm) | Material<br>(isolation)<br>group | Temperature (T <sub>J</sub> ) (°C) | Package                                    |

|----------------------------------------------------|---------|-----------------------------------------------|----------------------------------|------------------------------------|--------------------------------------------|

| MGD3162AM550EK (without DC Link Discharge Mode)    | 5.0     | >7.72 <sup>[2]</sup>                          | II <sup>[3]</sup>                | -40 to 150                         | 32-pin wide<br>body SOIC,<br>0.65 mm pitch |

| MGD3162AM551EK (with DC<br>Link Discharge Mode)    | 5.0     | >7.72 <sup>[2]</sup>                          | II <sup>[3]</sup>                | -40 to 150                         | 32-pin wide<br>body SOIC,<br>0.65 mm pitch |

| MGD3162AM580EK (without<br>DC Link Discharge Mode) | 5.0     | >8.00 <sup>[2]</sup>                          | l <sup>[3]</sup>                 | -40 to 150                         | 32-pin wide<br>body SOIC,<br>0.65 mm pitch |

| MGD3162AM581EK (with DC<br>Link Discharge Mode)    | 5.0     | >8.00 <sup>[2]</sup>                          | I <sub>[3]</sub>                 | -40 to 150                         | 32-pin wide<br>body SOIC,<br>0.65 mm pitch |

<sup>[1]</sup> To order parts in tape and reel, add the R2 suffix to the part number. To order parts in tray packing, add the T suffix to the part number.

<sup>[2]</sup> per IEC 60950-1 Tables 2K and 2N

<sup>[3]</sup> per IEC 60664-1

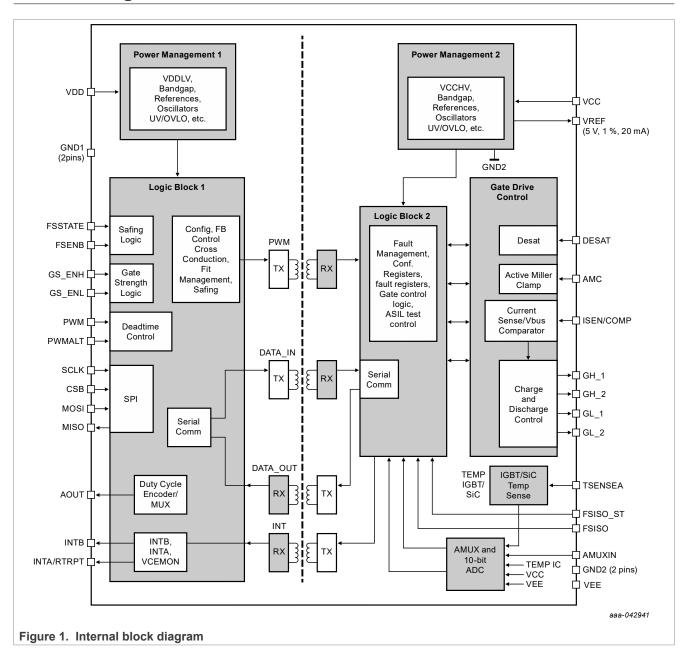

## 4 Block diagram

## 5 Limiting values

#### Table 2. Absolute maximum ratings

All voltages referenced to GND1 (LV domain) or GND2 (HV domain). T<sub>J</sub> = -40 to 150 °C, unless otherwise specified. Currents are positive into and negative out of the specified pins.

| Symbol                  | Description (Rating)                                                                   |            | Min                    | Max                      | Unit |

|-------------------------|----------------------------------------------------------------------------------------|------------|------------------------|--------------------------|------|

| Power supplies ar       | nd current references                                                                  |            |                        |                          |      |

| V <sub>VDD</sub>        | Low-voltage domain logic supply voltage, 5.0 V                                         | [1]        | -0.5                   | 6.0                      | V    |

| V <sub>VCC</sub>        | High-voltage domain positive supply voltage                                            | [2]        | -0.3                   | 25                       | V    |

| V <sub>VEE</sub>        | High-voltage domain negative supply voltage                                            | [2]        | -12                    | 0.3                      | V    |

| V <sub>VCC-VEE</sub>    | High-voltage domain positive/negative supply                                           |            | -0.3                   | 35                       | V    |

| V <sub>VREF</sub>       | VREF voltage                                                                           | [2]        | -0.3                   | 6.0                      | V    |

| I <sub>VREF</sub>       | VREF output current                                                                    |            | _                      | -20                      | mA   |

| Logic pins              |                                                                                        |            |                        |                          |      |

| V <sub>IN</sub>         | Logic input pin voltage (FSSTATE, FSENB, PWM, PWMALT, GS_ENH, GS_ENL, SCLK, CSB, MOSI) | [1]        | -0.3                   | 18                       | V    |

| V <sub>OUT</sub>        | Logic output pin voltage (MISO, INTB, INTA/RTRPT, AOUT)                                | [1]        | -0.3                   | V <sub>VDD</sub> + 0.3   | V    |

| V <sub>FSISO</sub>      | Logic input pin voltage (FSISO)                                                        | [2]        | -0.3                   | 12                       | V    |

| V <sub>FSISO_ST</sub>   | Logic input pin voltage (FSISO_ST)                                                     | [2]        | -0.3                   | 12                       | V    |

| Gage drive output       | t stage                                                                                |            |                        |                          |      |

| V <sub>GH_1,2</sub>     | GH_1,2 voltage                                                                         | [2]        | V <sub>VEE</sub> - 0.3 | V <sub>VCC</sub> + 0.3   | V    |

| V <sub>GL_1,2</sub>     | GL_1,2 voltage                                                                         | [2]        | V <sub>VEE</sub> - 0.3 | V <sub>VCC</sub> + 0.3   | V    |

| V <sub>AMC</sub>        | AMC voltage                                                                            | [2]        | V <sub>VEE</sub> - 0.3 | V <sub>VCC</sub> + 0.3   | V    |

| Temperature sens        | e pin                                                                                  |            |                        |                          |      |

| V <sub>TSENSEA</sub>    | TSENSEA voltage                                                                        | [2]        | -0.3                   | 6.0                      | V    |

| Interrupt pins          | ·                                                                                      |            |                        | •                        |      |

| I <sub>INTA/RTRPT</sub> | Open drain DC output current                                                           | [3]        | -                      | -20                      | mA   |

| I <sub>INTB</sub>       | Open drain DC output current                                                           | [3]        | _                      | -20                      | mA   |

| ISENSE sense pin        | 1                                                                                      |            |                        |                          |      |

| V <sub>ISEN/COMP</sub>  | ISEN/COMP voltage                                                                      | [2]        | -2.0                   | V <sub>VCC</sub> + 0.3 V | V    |

| AMUXIN pin              |                                                                                        |            |                        |                          |      |

| V <sub>AMUXIN</sub>     | AMUXIN voltage                                                                         | [2]<br>[4] | -0.3                   | 6.0                      | V    |

| ESD ratings             |                                                                                        |            |                        |                          |      |

| V <sub>ESDHBM</sub>     | ESD voltage (HBM) All pins                                                             | [5]        | -2.0                   | 2.0                      | kV   |

| V <sub>ESDCDM</sub>     | ESD voltage (CDM) Corner pins Other pins                                               | [6]        | -750<br>-500           | 750<br>500               | V    |

| V <sub>ESDModule</sub>  | ESD voltage (module level)<br>GND1, GND2 pins                                          | [7]        | -8.0                   | 8.0                      | kV   |

| IMMUNITY                |                                                                                        |            |                        |                          |      |

| dV <sub>ISO</sub> /dt   | Common mode transient immunity                                                         | [8]        | _                      | 100                      | V/ns |

- [1] Ref = GND1

- [2] Ref = GND2

- 3] V<sub>INTB</sub>, V<sub>INTA/RTRPT</sub> < 1.0 V

- [4] ADC performance is guaranteed by design up to 500 μA injected current in AMUXIN pin.

- 5] Human Body Model (HBM) at device level

ANSI/ESDA/JEDEC JS-001: 2010 Model HBM (human body model)

Electrostatic Discharge (ESD) Sensitivity Testing Human Body Model (HBM)

Test points: pin to GND1 and pin to GND2

[6] Charged Device Model (CDM)

ANSI/ESD S5.3.1-2009

ESD Association Standard for Electrostatic Discharge Sensitivity Testing - Charged Device Model (CDM) - Component Level

7] Module Level ESD Tests

ISO 10605:2008/Cor. 1:2010(E)

Road vehicles - Test methods for electrical disturbances from electrostatic discharge

[8] Pulse width = 10 ns

GD3162\_SDS

All information provided in this document is subject to legal disclaimers.

© 2024 NXP B.V. All rights reserved.

## 6 Revision history

#### Table 3. Revision history

| Document ID         | Release date                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Data sheet status | Change notice | Supersedes |  |

|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|---------------|------------|--|

| GD3162_SDS<br>v.2.0 | 20240112                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Product           | _             | v.1.1      |  |

| Modifications       | <ul> <li>Updated document title</li> <li>Status changed to Product from Objective</li> <li>Section 2.1: Changed eighth bullet item to "(MGD3162AM551EK and MGD3162AM581EK only)" from "(PGD3162 AM551EK and PGD3162AM581EK only)"</li> <li>Updated Table 1; part numbers changed to "MGD3162AM550EK", "MGD3162AM551EK", "MGD3162AM580 EK", and "MGD3162AM581EK" from "PGD3162AM550EK", "PGD3162AM551EK", "PGD3162AM580EK", and "PGD3162AM581EK"</li> <li>Revision history was updated to conform with NXP's document content hierarchy.</li> </ul> |                   |               |            |  |

| GD3162_SDS<br>v.1.1 | 20230510                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Objective         | _             | v.1.0      |  |

| Modifications       | <ul> <li>Corrected status on cover.</li> <li>Section 2.1: Added bullet item: "VDS measurement capability for RDSon and junction temperature estimation."</li> <li>Section 3: Added "To order parts in tray packing, add the T suffix to the part number." to the first footnote.</li> <li>Section 5         <ul> <li>Updated section title from "Absolute maximum ratings" to "Limiting values".</li> <li>Table 2: Removed last four rows under "Gage drive output state" subtitle.</li> </ul> </li> </ul>                                         |                   |               |            |  |

| GD3162_SDS<br>v.1.0 | 20221129                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Objective         | _             | _          |  |

| Modifications       | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 1                 | 1             | J          |  |

## **Legal information**

#### Data sheet status

| Document status <sup>[1][2]</sup> | Product status <sup>[3]</sup> | Definition                                                                            |

|-----------------------------------|-------------------------------|---------------------------------------------------------------------------------------|

| Objective [short] data sheet      | Development                   | This document contains data from the objective specification for product development. |

| Preliminary [short] data sheet    | Qualification                 | This document contains data from the preliminary specification.                       |

| Product [short] data sheet        | Production                    | This document contains the product specification.                                     |

- [1] Please consult the most recently issued document before initiating or completing a design.

- [2] The term 'short data sheet' is explained in section "Definitions".

- The product status of device(s) described in this document may have changed since this document was published and may differ in case of multiple devices. The latest product status information is available on the Internet at URL <a href="https://www.nxp.com">https://www.nxp.com</a>.

#### **Definitions**

**Draft** — A draft status on a document indicates that the content is still under internal review and subject to formal approval, which may result in modifications or additions. NXP Semiconductors does not give any representations or warranties as to the accuracy or completeness of information included in a draft version of a document and shall have no liability for the consequences of use of such information.

Short data sheet — A short data sheet is an extract from a full data sheet with the same product type number(s) and title. A short data sheet is intended for quick reference only and should not be relied upon to contain detailed and full information. For detailed and full information see the relevant full data sheet, which is available on request via the local NXP Semiconductors sales office. In case of any inconsistency or conflict with the short data sheet, the full data sheet shall prevail.

Product specification — The information and data provided in a Product data sheet shall define the specification of the product as agreed between NXP Semiconductors and its customer, unless NXP Semiconductors and customer have explicitly agreed otherwise in writing. In no event however, shall an agreement be valid in which the NXP Semiconductors product is deemed to offer functions and qualities beyond those described in the Product data sheet.

#### **Disclaimers**

Limited warranty and liability — Information in this document is believed to be accurate and reliable. However, NXP Semiconductors does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information. NXP Semiconductors takes no responsibility for the content in this document if provided by an information source outside of NXP Semiconductors.

In no event shall NXP Semiconductors be liable for any indirect, incidental, punitive, special or consequential damages (including - without limitation - lost profits, lost savings, business interruption, costs related to the removal or replacement of any products or rework charges) whether or not such damages are based on tort (including negligence), warranty, breach of contract or any other legal theory.

Notwithstanding any damages that customer might incur for any reason whatsoever, NXP Semiconductors' aggregate and cumulative liability towards customer for the products described herein shall be limited in accordance with the Terms and conditions of commercial sale of NXP Semiconductors.

Right to make changes — NXP Semiconductors reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof.

**Applications** — Applications that are described herein for any of these products are for illustrative purposes only. NXP Semiconductors makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

Customers are responsible for the design and operation of their applications and products using NXP Semiconductors products, and NXP Semiconductors accepts no liability for any assistance with applications or customer product design. It is customer's sole responsibility to determine whether the NXP Semiconductors product is suitable and fit for the customer's applications and products planned, as well as for the planned application and use of customer's third party customer(s). Customers should provide appropriate design and operating safeguards to minimize the risks associated with their applications and products.

NXP Semiconductors does not accept any liability related to any default, damage, costs or problem which is based on any weakness or default in the customer's applications or products, or the application or use by customer's third party customer(s). Customer is responsible for doing all necessary testing for the customer's applications and products using NXP Semiconductors products in order to avoid a default of the applications and the products or of the application or use by customer's third party customer(s). NXP does not accept any liability in this respect.

Limiting values — Stress above one or more limiting values (as defined in the Absolute Maximum Ratings System of IEC 60134) will cause permanent damage to the device. Limiting values are stress ratings only and (proper) operation of the device at these or any other conditions above those given in the Recommended operating conditions section (if present) or the Characteristics sections of this document is not warranted. Constant or repeated exposure to limiting values will permanently and irreversibly affect the quality and reliability of the device.

Terms and conditions of commercial sale — NXP Semiconductors products are sold subject to the general terms and conditions of commercial sale, as published at https://www.nxp.com/profile/terms, unless otherwise agreed in a valid written individual agreement. In case an individual agreement is concluded only the terms and conditions of the respective agreement shall apply. NXP Semiconductors hereby expressly objects to applying the customer's general terms and conditions with regard to the purchase of NXP Semiconductors products by customer.

GD3162\_SDS

All information provided in this document is subject to legal disclaimers.

© 2024 NXP B.V. All rights reserved.

Suitability for use in automotive applications — This NXP product has been qualified for use in automotive applications. If this product is used by customer in the development of, or for incorporation into, products or services (a) used in safety critical applications or (b) in which failure could lead to death, personal injury, or severe physical or environmental damage (such products and services hereinafter referred to as "Critical Applications"), then customer makes the ultimate design decisions regarding its products and is solely responsible for compliance with all legal, regulatory, safety, and security related requirements concerning its products, regardless of any information or support that may be provided by NXP. As such, customer assumes all risk related to use of any products in Critical Applications and NXP and its suppliers shall not be liable for any such use by customer. Accordingly, customer will indemnify and hold NXP harmless from any claims, liabilities, damages and associated costs and expenses (including attorneys' fees) that NXP may incur related to customer's incorporation of any product in a Critical Application.

**Export control** — This document as well as the item(s) described herein may be subject to export control regulations. Export might require a prior authorization from competent authorities.

**Translations** — A non-English (translated) version of a document, including the legal information in that document, is for reference only. The English version shall prevail in case of any discrepancy between the translated and English versions.

**NXP B.V.** — NXP B.V. is not an operating company and it does not distribute or sell products.

#### **Trademarks**

Notice: All referenced brands, product names, service names, and trademarks are the property of their respective owners.

NXP — wordmark and logo are trademarks of NXP B.V.

SafeAssure — is a trademark of NXP B.V.

### **NXP Semiconductors**

GD3162\_SDS

## Advanced IGBT/SiC gate driver with dynamic gate strength adjust

### **Tables**

| Tab. 1. | Orderable part variations4 | Tab. 3. | Revision history . |  |

|---------|----------------------------|---------|--------------------|--|

| Tab. 2. | Absolute maximum ratings6  |         |                    |  |

GD3162\_SDS

Advanced IGBT/SiC gate driver with dynamic gate strength adjust

| F | ig | u | re | S |

|---|----|---|----|---|

|   |    |   |    |   |

Fig. 1. Internal block diagram .....5

### **Contents**

| 1   | General description             | 1 |

|-----|---------------------------------|---|

| 2   | Features and benefits           |   |

| 2.1 | Key features                    | 2 |

| 2.2 | Safety features                 |   |

| 2.3 | Safety and regulatory approvals |   |

| 3   | Ordering information            |   |

| 4   | Block diagram                   |   |

| 5   | Limiting values                 |   |

| 6   | Revision history                |   |

|     | Legal information               |   |

Please be aware that important notices concerning this document and the product(s) described herein, have been included in section 'Legal information'.

## **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Galvanically Isolated Gate Drivers category:

Click to view products by NXP manufacturer:

Other Similar products are found below:

NCP51561DADWR2G

TPSI3052QDWZRQ1

SI82521AD-AS3

ADUM4135BRWZ-RL

ADUM4146BRWZ-RL

AHV85110KNHTR

1ED3140MU12FXUMA1

1ED3141MU12FXUMA1

1ED3142MU12FXUMA1

2EDL8033G4BXTMA1

2EDL8033G4CXTMA1

2EDL8033G4CXTMA1

2EDL8033G3CXTMA1

MGD3162AM550EKT

MGD3162AM551EKT

NCP51560BBDWR2G

NCD57530DWKR2G

NCD57540DWKR2G

NCP51560ABDWR2G

NCV51563CADWR2G

NCV57530DWKR2G

NCV57540DWKR2G

NCV51561BBDWR2G

NCD57101DWR2G

NCP51563BBDWR2G

NCV51563BBDWR2G

NCV5707BDR2G

R2A25110KSP#U50

BM61M22BFJ-CE2

TPSI3050DWZR

TPSI3052SQDWZRQ1

TPSI3050SDWZR

TPSI3050SQDWZRQ1

UCC21717QDWRQ1

UCC21737QDWRQ1

UCC21755QDWRQ1

UCC5871QDWJRQ1