**3-Axis Multifunction Digital Accelerometer** Rev. 2.1 — 26 April 2016 Dat

Data sheet: Technical data **COMPANY PUBLIC**

#### **General description** 1

The MMA8491Q is a low voltage, 3-axis low-g accelerometer housed in a 3 mm x 3 mm QFN package. The device can accommodate two accelerometer configurations, acting as either a 45° tilt sensor or a digital output accelerometer with I<sup>2</sup>C bus.

- As a 45° tilt sensor, the MMA8491Q device offers extreme ease of implementation by using a single line output per axis.

- As a digital output accelerometer, the 14-bit ±8 g accelerometer data can be read from the device with a 1 mg/LSB sensitivity.

The extreme low power capabilities of the MMA8491Q will reduce the low data rate current consumption to less than 400 nA per Hz.

#### Features and benefits 2

- Extreme low power, 400 nA per Hz

- Ultra-fast data output time, ~700 μs

- V<sub>DD</sub> supply range of 1.95 V to 3.6 V

- 3 mm x 3 mm, 0.65 mm pitch with visual solder joint inspection

- ±8 g full-scale range

- 14-bit digital output, 1 mg/LSB sensitivity

- Output Data Rate (ODR), implementation based from < 1 Hz to 800 Hz<sup>1</sup>

- I<sup>2</sup>C digital interface

- 3-axis, 45° tilt outputs

#### **Typical applications** 3

- Smart grid: tamper detect

- Anti-theft

- White goods tilt

- Remote controls

<sup>1</sup> The ODR for this device is user defined by the period of the Enable pulsed signal. The maximum recommended frequency of the Enable signal or the ODR that can be achieved for this device is 800 Hz.

## 4 Ordering information

| Table 1. Ordering informatic           Part Number | Temperature Range | Package | Shipping              |

|----------------------------------------------------|-------------------|---------|-----------------------|

| MMA8491QT                                          | –40 to +85 °C     | QFN 12  | Tray                  |

| MMA8491QR1                                         | –40 to +85 °C     | QFN 12  | 1000 pc / Tape & Reel |

| MMA8491QR2                                         | –40 to +85 °C     | QFN 12  | 5000 pc / Tape & Reel |

## 5 Related documentation

The MMA8491Q device features and operations are described in a variety of reference manuals, user guides, and application notes. To find the most current versions of these documents:

- 1. Go to the NXP homepage at: <u>http://www.nxp.com/</u>

- In the Keyword search box at the top of the page, enter the device number MMA8491Q. In the Refine Your Result pane on the left, click on the Documentation link.

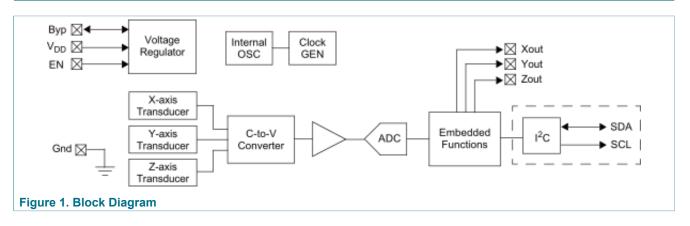

## 6 Block diagram

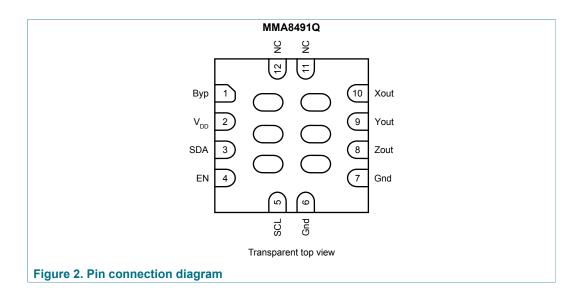

## 7 Pinout

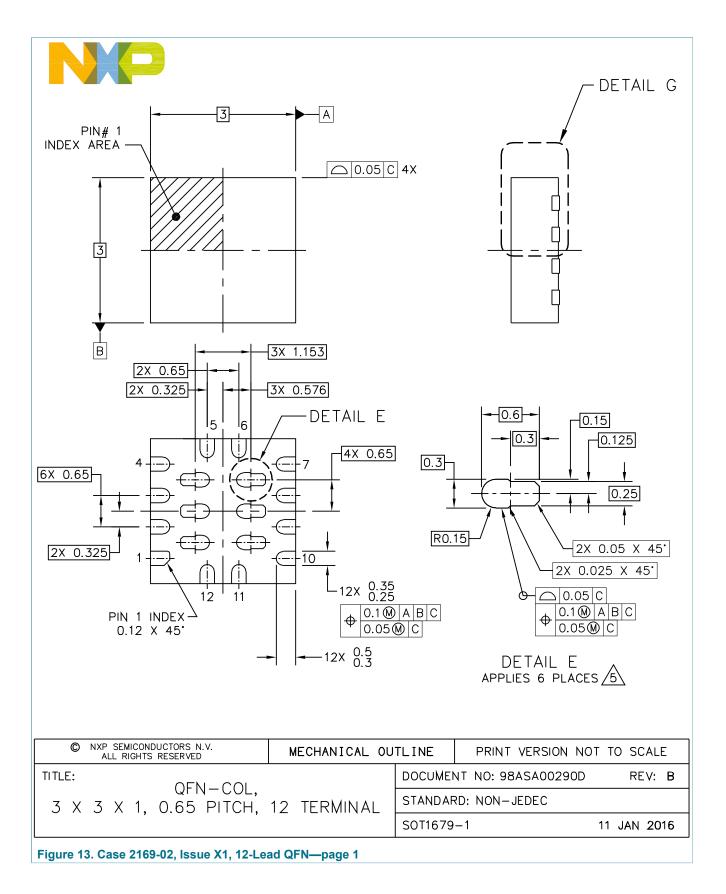

MMA8491Q is hosted in a 12-pin 3 mm x 3 mm QFN package. Ten pins are used for functions; two pins are unconnected. Refer to <u>Table 2</u> for complete pin descriptions and functions.

### **3-Axis Multifunction Digital Accelerometer**

| Pin | Symbol          | Function                                             | Description                                                                                                                                                                                                                              | Pin status   |

|-----|-----------------|------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

| 1   | Вур             | Internal regulator<br>output capacitor<br>connection | The internal regulator voltage of 1.8 V is present on this pin. Connect to external 0.1 $\mu F$ bypass capacitor.                                                                                                                        | Output       |

| 2   | V <sub>DD</sub> | Power Supply                                         | Device power is supplied through the $V_{DD}$ line. Power supply decoupling capacitors should be placed as near as possible to pin 1 of the device.                                                                                      | Input        |

| 3   | SDA             | I <sup>2</sup> C Data                                | <ul> <li>I<sup>2</sup>C Slave Data Line, open drain</li> <li>7-bit I<sup>2</sup>C device address is 0x55</li> <li>The SDA and SCL I<sup>2</sup>C connections are open drain, and therefore usually require a pull-up resistor</li> </ul> | Input/Output |

| 4   | EN              | Enable pin                                           | The Enable pin fully turns on the accelerometer system when it is pulled up to logic high. The accelerometer system is turned off when the Enable pin is logic low.                                                                      | Input        |

| 5   | SCL             | I <sup>2</sup> C Clock                               | I <sup>2</sup> C Slave Clock Line, open drain                                                                                                                                                                                            | Input        |

| 6   | Gnd             | Ground                                               | Ground                                                                                                                                                                                                                                   | Ground       |

| 7   | Gnd             | Ground                                               | Ground                                                                                                                                                                                                                                   | Ground       |

| 8   | Zout            | Push-pull Z-Axis<br>Tilt Detection<br>Output         | <ul> <li>Output is high when acceleration is &gt; 0.688 g (axis is   φ  &gt; 45°).</li> <li>Output is low when acceleration is ≤ 0.688 g (axis is  φ </li> </ul>                                                                         | Output       |

| 9   | Yout            | Push-pull Y-Axis<br>Tilt Detection<br>Output         | <ul> <li>≤ 45°).</li> <li>These pins are push-pull output pins.</li> </ul>                                                                                                                                                               | Output       |

| 10  | Xout            | Push-pull X-Axis<br>Tilt Detection<br>Output         |                                                                                                                                                                                                                                          | Output       |

| 11  | NC              | No internal connection                               | No internal connection                                                                                                                                                                                                                   |              |

| 12  | NC              | No internal connection                               | No internal connection                                                                                                                                                                                                                   |              |

#### **3-Axis Multifunction Digital Accelerometer**

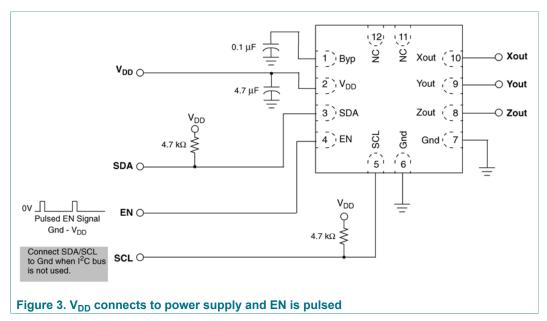

## 8 Recommended application diagram

To ensure the accelerometer is fully functional, connect the MMA8491Q as suggested in Figure 3.

- A capacitor must be connected to the Bypass pin (pin 1) to assist the internal voltage regulator. It is recommended to use a 0.1 µF capacitor. The capacitor should be placed as near as possible to the Bypass pin.

- The device power is supplied through the  $V_{\text{DD}}$  line. The power supply decoupling capacitor should be placed as close as possible to the  $V_{\text{DD}}$  pin.

- Use a 1.0 or 4.7  $\mu$ F capacitor when the V<sub>DD</sub> and EN are not tied together.

- When V<sub>DD</sub> and EN are tied together, use a 0.1  $\mu$ F capacitor. The 0.1  $\mu$ F capacitor value has been chosen to minimize the average current consumption while still maintaining an acceptable level of power supply high frequency filtering.

- Both ground pins (pins 6 and 7) must be connected to ground.

- When the I<sup>2</sup>C communication line is used, use a pull-up resistor to connect to line SDA and SCL. The SCL line can be driven by a push-pull driver, in which case, no pull-up resistor is necessary. If SDA and SCL pins are not used, then they should be tied to ground.

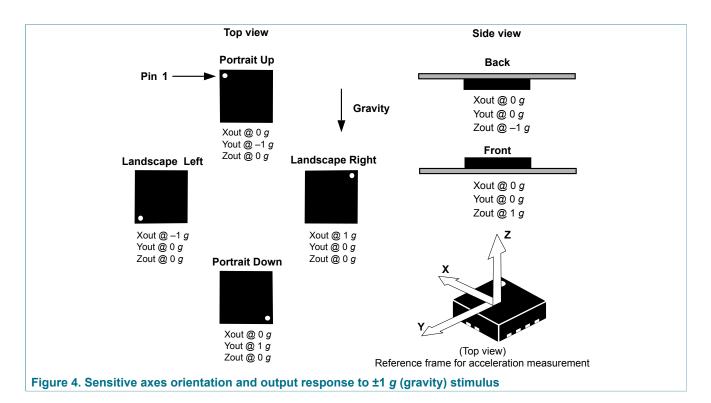

## **9** Sensing direction and output response

The MMA8491Q has three tilt detection outputs: Xout, Yout, and Zout. The following figure shows the output results at the six different orientation positions.

MMA8491Q

© NXP B.V. 2016. All rights reserved

### **NXP Semiconductors**

## **MMA8491Q**

#### **3-Axis Multifunction Digital Accelerometer**

## **10** Mechanical and electrical specifications

### 10.1 Absolute maximum ratings

Absolute maximum ratings are the limits the device can be exposed to without damage. Functional operation at absolute maximum rating is not guaranteed.

Although this device contains circuitry to protect against damage due to high static voltage or electrostatic fields, it is advised that normal precautions be taken to avoid application of any voltage higher than the maximum-rated voltage.

#### Table 3. Absolute maximum ratings

| Symbol                  | Rating                                  | Min  | Max    | Unit |

|-------------------------|-----------------------------------------|------|--------|------|

| <b>g</b> <sub>max</sub> | Maximum acceleration (all axes, 100 µs) |      | 10 000 | V    |

| V <sub>DD</sub>         | Analog supply voltage                   | -0.3 | 3.6    | V    |

| D <sub>drop</sub>       | Drop test                               |      | 1.8    | m    |

| T <sub>AGOC</sub>       | Operating temperature                   | -40  | +85    | °C   |

| T <sub>STG</sub>        | Storage temperature                     | -40  | +125   | °C   |

#### Table 4. ESD and latch-up protection characteristics

| Symbol           | Rating                 |       | Unit |

|------------------|------------------------|-------|------|

| V <sub>HBM</sub> | Human body model (HBM) | ±2000 | V    |

| V <sub>MM</sub>  | Machine model (MM)     | ±200  | V    |

**3-Axis Multifunction Digital Accelerometer**

| Symbol           | Rating                                     |      | Unit |

|------------------|--------------------------------------------|------|------|

| V <sub>CDM</sub> | Charge device model (CDM)                  | ±500 | V    |

| I <sub>LU</sub>  | Latch-up current at $T_A = 85 \ ^{\circ}C$ | ±100 | mA   |

#### 10.2 **Mechanical characteristics**

#### Table 5. Accelerometer mechanical characteristics

$V_{DD}$  = 2.8 V, T = 25 °C, unless otherwise noted.

Typical number is the target number, unless otherwise specified.

All numbers are based on  $V_{DD}$  cap = 4.7  $\mu$ F.

| Parameter                             | Symbol                           | Conditions            | Min    | Тур   | Мах   | Unit           |

|---------------------------------------|----------------------------------|-----------------------|--------|-------|-------|----------------|

| Full-scale measurement range          | FS <sup>[1]</sup>                |                       |        | ±8    |       | g              |

| Sensitivity                           | So <sup>[2]</sup>                |                       | 973    | 1024  | 1075  | counts/g       |

| Calibrated sensitivity error          | CSE <sup>[2]</sup>               | All axes, all ranges  | -5     |       | 5     | %              |

| Cross-axis sensitivity                | CX <sub>SEN</sub> <sup>[1]</sup> | Die rotation included | -4.2   |       | 4.2   | %              |

| Sensitivity temperature variation     | TCS <sup>[1]</sup>               | –40 °C to +85 °C      | -0.014 |       | 0.014 | %/°C           |

| Zero-g level temperature variation    | TCO <sup>[1]</sup>               | –40 °C to +85 °C      | -0.98  |       | 0.98  | m <i>g</i> /°C |

| Zero-g level offset accuracy          | TyOff <sup>[2][3]</sup>          |                       | -100   |       | 100   | m <i>g</i>     |

| Zero-g level after board mount        | TyOffPBM <sup>[1][4]</sup>       |                       | -120   |       | 120   | m <i>g</i>     |

| Noise                                 | RMS <sup>[1]</sup>               | —                     |        | 11.5  | 18    | mg-rms         |

| Nonlinearity                          | NL <sup>[1]</sup>                | —                     |        |       | 1     | %FS            |

| Threshold / g-value <sup>[5]</sup>    | TDL <sup>[6]</sup>               | 25 °C                 | 0.583  | 0.688 | 0.780 | g              |

|                                       | TDL <sup>[1][4][6]</sup>         | –40 °C to +85 °C      | 0.577  | 0.688 | 0.784 |                |

| Threshold / Tilt angle <sup>[7]</sup> | T <sub>AGOC</sub> <sup>[1]</sup> | 25 °C                 | 35.6   | 43.5  | 51.3  | degrees        |

|                                       |                                  | –40 °C to +85 °C      | 35.2   | 43.5  | 51.7  | 1              |

| Temperature range                     |                                  |                       | -40    | 25    | 85    | °C             |

Verified by characterization; not tested in production. Parameters tested 100% at final test at room temperature.

Before board mount.

Post-board mount offset specifications are based on a 4-layer PCB, relative to 25 °C.

[1] [2] [3] [4] [5] [6]

Internal threshold of output level change (from 0 g reference), g values are calculated from trip angles. All angles are based on the trip angle from static 0 g to 1 g; the g-values are calculated from the trip angle. Internal threshold of output level change (from 0 g reference).

[7]

### **10.3 Electrical characteristics**

#### **Table 6. Electrical characteristics**

$V_{DD}$  = 2.8 V, T = 25 °C, unless otherwise noted.

Typical values represent mean or mean  $\pm 1 \sigma$  values, depending on the specific parameter.

Typical number is the target number unless otherwise specified.

All numbers are based on  $V_{DD}$  cap = 4.7  $\mu$ F.

| Symbol                                                  | Parameter                                                                       | Conditions                                                                       | Min                       | Тур                      | Max                      | Unit  |

|---------------------------------------------------------|---------------------------------------------------------------------------------|----------------------------------------------------------------------------------|---------------------------|--------------------------|--------------------------|-------|

| V <sub>DD</sub>                                         | Supply voltage <sup>[1]</sup>                                                   | _                                                                                | 1.71                      | 1.8                      | 3.6                      | V     |

| I <sub>DD</sub>                                         | Supply current in one-shot mode                                                 | $V_{DD}$ = 2.8 V, EN is pulsed to $V_{DD}$ for 1 ms                              | -                         | 400 <sup>[2][3][4]</sup> | 980 <sup>[1][5][6]</sup> | nA/Hz |

| I <sub>SD</sub>                                         | Supply current in shutdown mode                                                 | V <sub>DD</sub> = 2.8 V, EN = 0                                                  | _                         | 1.8 <sup>[2][3]</sup>    | 68 <sup>[1][6]</sup>     | nA    |

| C <sub>BYP</sub> <sup>[2]</sup>                         | Bypass capacitor at Byp pin                                                     | _                                                                                | 70                        | 100                      | 470                      | nF    |

| V <sub>OH</sub> <sup>[1]</sup>                          | High level output voltage Xout,<br>Yout, Zout                                   | I <sub>O</sub> = 500 μA                                                          | 0.85<br>* V <sub>DD</sub> | —                        | _                        | V     |

| V <sub>OL</sub> <sup>[1]</sup>                          | Low level output voltage Xout,<br>Yout, Zout                                    | I <sub>O</sub> = 500 μA                                                          | —                         | —                        | 0.15 * V <sub>DD</sub>   | V     |

| V <sub>IH</sub> <sup>[1]</sup>                          | High level input voltage EN                                                     | V <sub>DD</sub> = 2.8 V                                                          | 0.85<br>* V <sub>DD</sub> | —                        | _                        | V     |

| V <sub>IL</sub> <sup>[1]</sup>                          | Low level input voltage EN                                                      | V <sub>DD</sub> = 2.8 V                                                          | _                         | —                        | 0.15 * V <sub>DD</sub>   | V     |

| V <sub>OLS</sub> <sup>[7]</sup>                         | Low level output voltage SDA                                                    | I <sub>O</sub> = 3 mA                                                            | _                         | _                        | 0.4                      | V     |

| V <sub>IH</sub> <sup>[7]</sup>                          | High level input voltage SDA, SCL                                               | V <sub>DD</sub> = 2.8 V                                                          | 0.7 * V <sub>DD</sub>     | -                        | _                        | V     |

| V <sub>IL</sub> <sup>[7]</sup>                          | Low level input voltage SDA, SCL                                                | V <sub>DD</sub> = 2.8 V                                                          | —                         | —                        | 0.3 * V <sub>DD</sub>    | V     |

| I <sub>SOURCE</sub> <sup>[1]</sup>                      | Output source current Xout,<br>Yout, Zout                                       | Voltage high level<br>Vout = 0.85 x<br>V <sub>DD</sub> , V <sub>DD</sub> = 2.8 V | _                         | _                        | 7.3                      | mA    |

| I <sub>SINK</sub> <sup>[1]</sup>                        | Output sink current Xout, Yout,<br>Zout                                         | Voltage low level<br>Vout = 0.15 x<br>V <sub>DD</sub> , V <sub>DD</sub> = 2.8 V  | _                         | —                        | 8.9                      | mA    |

| T <sub>ON</sub> /<br>T <sub>ACTIVE</sub> <sup>[8]</sup> | Turn-on time<br>Measured from the time EN =<br>1.95 V to valid outputs          | _                                                                                | _                         | 720 <sup>[2][3][4]</sup> | 900 <sup>[1][5][6]</sup> | μs    |

| T <sub>RST</sub> <sup>[7]</sup>                         | Reset Time<br>The time between falling edge of<br>EN and next rising edge of EN | V <sub>DD</sub> = 2.8 V                                                          | 1000                      | -                        |                          | μs    |

Verified by characterization; not tested in production. Evaluation data: not tested in production. Typical number is mean data. [1]

Typical number is mean data. Data is based on typical bypass cap = 100 nF. Data is based on max bypass cap = 470 nF. Over temperature -40 °C to 85 °C. Guaranteed by design. For application connection, see Figure 3

[2] [3] [4] [5] [6]

[7] [8]

# **11** I<sup>2</sup>C Interface

Acceleration data may be accessed through an  $I^2C$  interface, thus making the device particularly suitable for direct interfacing with a microcontroller. The MMA8491Q features three interrupt signals that indicate the tilt-sensing results on X, Y, Z axis respectively. The raw accelerometer data are readable via  $I^2C$  at the same time when an interrupt signal is available.

The registers embedded inside the MMA8491Q are accessible through the  $I^2C$  serial interface, <u>Table 7</u>. To enable the  $I^2C$  interface, the EN pin must be HIGH. If either EN or V<sub>DD</sub> are absent, the MMA8491Q  $I^2C$  interface reads invalid data. The  $I^2C$  interface may be used for communications along with other  $I^2C$  devices. Removing power from the V<sub>DD</sub> pin of the MMA8491Q does not affect the  $I^2C$  bus.

#### Table 7. Serial interface pins

| Pin | Description                   |

|-----|-------------------------------|

| SCL | I <sup>2</sup> C Serial Clock |

| SDA | I <sup>2</sup> C Serial Data  |

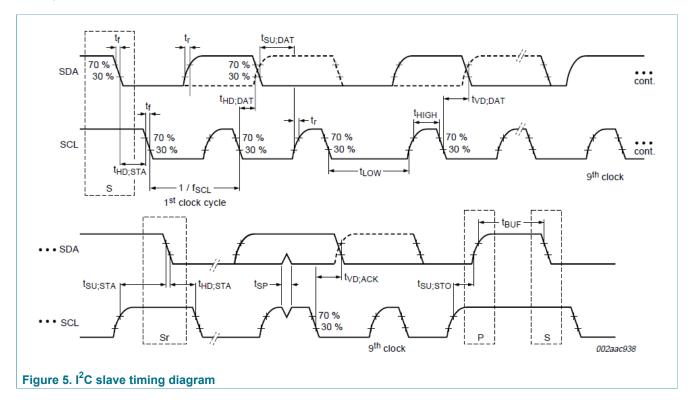

There are two signals associated with the  $I^2C$  bus; the Serial Clock Line (SCL) and the Serial Data Line (SDA). The SDA is a bidirectional line used for sending and receiving the data to/from the interface. External pull-up resistors connected to  $V_{DD}$  are expected for SDA and SCL. When the bus is free both the lines are HIGH. The  $I^2C$  interface is compliant with Fast mode (400 kHz, <u>Table 8</u>).

| Parameter                                                                             | Symbol              | I2C Fast                               | Mode <sup>[1]</sup> | Unit |

|---------------------------------------------------------------------------------------|---------------------|----------------------------------------|---------------------|------|

|                                                                                       |                     | Min                                    | Max                 | -    |

| SCL clock frequency                                                                   | f <sub>SCL</sub>    | 0                                      | 400                 | kHz  |

| Bus-free time between STOP and START condition                                        | t <sub>BUF</sub>    | 1.3                                    |                     | μs   |

| (Repeated) START hold time                                                            | t <sub>HD;STA</sub> | 0.6                                    |                     | μs   |

| Repeated START setup time                                                             | t <sub>SU;STA</sub> | 0.6                                    |                     | μs   |

| STOP condition setup time                                                             | t <sub>SU;STO</sub> | 0.6                                    |                     | μs   |

| SDA data hold time                                                                    | t <sub>HD;DAT</sub> | 0.05                                   | 0.9 <sup>[2]</sup>  | μs   |

| SDA setup time                                                                        | t <sub>SU;DAT</sub> | 100                                    |                     | μs   |

| SCL clock low time                                                                    | t <sub>LOW</sub>    | 1.3                                    | _                   | μs   |

| SCL clock high time                                                                   | t <sub>HIGH</sub>   | 0.6                                    |                     | μs   |

| SDA and SCL rise time                                                                 | t <sub>r</sub>      | 20 + 0.1 C <sub>b</sub> <sup>[3]</sup> | 300                 | μs   |

| SDA and SCL fall time                                                                 | t <sub>f</sub>      | 20 + 0.1 C <sub>b</sub> <sup>[3]</sup> | 300                 | μs   |

| SDA valid time <sup>[4]</sup>                                                         | t <sub>VD;DAT</sub> | _                                      | 0.9 <sup>[2]</sup>  | μs   |

| SDA valid acknowledge time <sup>[5]</sup>                                             | t <sub>VD;ACK</sub> | _                                      | 0.9 <sup>[2]</sup>  | μs   |

| Pulse width of spikes on SDA and SCL that must be suppressed by internal input filter | t <sub>SP</sub>     | 0                                      | 50                  | μs   |

| Capacitive load for each bus line                                                     | Cb                  |                                        | 400                 | pF   |

### Table 8. I<sup>2</sup>C slave timing values

[1] All values referred to VIH(min) (0.3V\_{DD}) and V\_{IL}(max) (0.7V\_{DD}) levels.

#### **3-Axis Multifunction Digital Accelerometer**

- [2] This device does not stretch the LOW period (t<sub>LOW</sub>) of the SCL signal.

- [3] Cb = total capacitance of one bus line in pF.

- [4] t<sub>VD:DAT</sub> = time for data signal from SCL LOW to SDA output (HIGH or LOW, depending on which one is worse).

- [5] t<sub>VD:ACK</sub> = time for Acknowledgement signal from SCL LOW to SDA output (HIGH or LOW, depending on which one is worse).

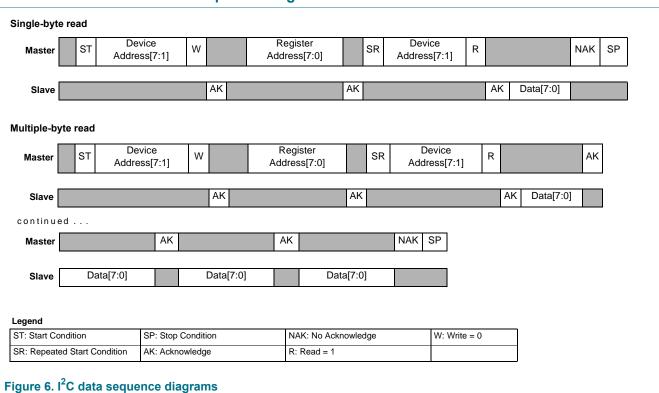

## **11.1** I<sup>2</sup>C read operations

The transaction on the bus is started through a start condition (START) signal. A START condition is defined as a HIGH-to-LOW transition on the data line while the SCL line is held HIGH.

After START has been transmitted by the Master, the bus is considered busy. The next byte of data transmitted after START contains the slave address in the first seven bits, and the eighth bit tells whether the Master is receiving data from the slave or transmitting data to the slave. When an address is sent, each device in the system compares the first seven bits after a start condition with its address. If they match, then the device considers itself addressed by the Master.

The ninth clock pulse, following the slave address byte, and each subsequent byte, is the acknowledge (ACK). The transmitter must release the SDA line during the ACK period. The receiver must then pull the data line LOW so that it remains stable low during the high period of the acknowledge clock period.

A LOW-to-HIGH transition on SDA while SCL is HIGH is defined as a stop condition (STOP). A data transfer is always terminated by a STOP.

A Master may also issue a repeated START during a data transfer. The MMA8491Q expects repeated STARTs to be used to randomly read from specific registers.

The MMA8491Q accelerometer standard 7-bit slave address is 01010101(0x55).

MMA8491Q

© NXP B.V. 2016. All rights reserved

| Table 9.1 C device add | less sequence           |                         |         |                            |

|------------------------|-------------------------|-------------------------|---------|----------------------------|

| Command                | [7:1] Device<br>Address | [7:1] Device<br>Address | [0] R/W | [7:0] 8-bit<br>Final Value |

| Read                   | 01010101                | 0x55                    | 1       | 0xAB                       |

| Write                  | 01010101                | 0x55                    | 0       | 0xAA                       |

### Table 9. I<sup>2</sup>C device address sequence

### 11.1.1 Single-byte read

The transmission of an 8-bit command begins on the falling edge of SCL. After the 8 clock cycles are used to send the command, note that the data returned is sent with the MSB first after the data is received. Figure 6 shows the timing diagram for the accelerometer 8-bit  $I^2C$  read operation.

- 1. The Master (or MCU) transmits a start condition (ST) to the MMA8491Q, slave address (0x55), with the R/W bit set to "0" for a write, and the MMA8491Q sends an acknowledgement.

- 2. Then the Master (or MCU) transmits the address of the register to read and the MMA8491Q sends an acknowledgement.

- 3. The Master (or MCU) transmits a repeated start condition (SR) and then addresses the MMA8491Q (0x1D) with the R/ W bit set to 1 for a read from the previously selected register.

- 4. The Slave then acknowledges and transmits the data from the requested register.

- 5. The Master does not acknowledge (NAK) the transmitted data, but transmits a stop condition to end the data transfer.

### 11.1.2 Multiple-byte read

When performing a multiple-byte read or *burst read*, the MMA8491Q automatically increments the received register address commands after a read command is received. Therefore, after following the steps of a single-byte read, multiple bytes of data can be read from sequential registers after each MMA8491Q acknowledgment (AK) is received, until a no acknowledge (NAK) occurs from the Master, followed by a stop condition (SP) signaling an end of transmission.

**3-Axis Multifunction Digital Accelerometer**

### 11.1.3 I2C data sequence diagrams

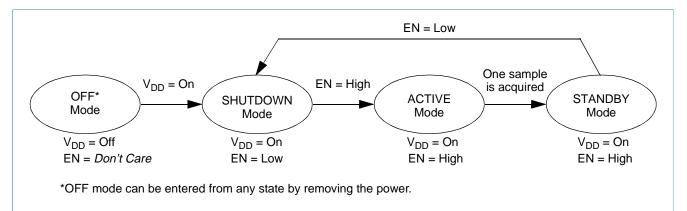

## **12 Modes of operation**

#### Figure 7. MMA8491Q operating modes

| Mode     | Conditions                                      | Function description      | Digital output state |

|----------|-------------------------------------------------|---------------------------|----------------------|

| OFF      | V <sub>DD</sub> = OFF<br>EN = <i>Don't Care</i> | Device is powered off.    | Hi-Z                 |

| SHUTDOWN | V <sub>DD</sub> = ON<br>EN = Low                | All blocks are shut down. | Hi-Z                 |

| Mode    | Conditions                        | Function description                                                                            | Digital output state                          |

|---------|-----------------------------------|-------------------------------------------------------------------------------------------------|-----------------------------------------------|

| ACTIVE  | V <sub>DD</sub> = ON<br>EN = High | All blocks are enabled.<br>Device enters Standby mode automatically<br>after data conversion.   | Deasserted, Xout = 0, Yout= 0, Zout = 0       |

| STANDBY | V <sub>DD</sub> = ON<br>EN = High | Only digital output subsystem is enabled.<br>Data is valid and available only in this<br>stage. | Active, I <sup>2</sup> C outputs become valid |

## 12.1 ACTIVE mode

The accelerometer subsystem is turned on at the rising edge of the EN pin, and acquires one sample for each of the three axes. Note that EN should not be asserted before  $V_{DD}$  reaches 1.95 V. Samples are acquired, converted, and compensated for zero-g offset and gain errors, and then compared to an internal threshold value of 0.688 *g* and stored.

- If any of the X, Y, Z axes sample's **absolute value > this threshold**, then the corresponding outputs on these axes drive logic highs.

- If any of the X, Y, Z axes sample's **absolute value** ≤ **this threshold**, then the corresponding outputs on these axes drive logic lows.

Read register 00h in this stage to determine whether the sample data is ready to be read.

### 12.2 STANDBY mode

The device enters STANDBY mode automatically after the previously described function (powers into SHUTDOWN mode, ACTIVE mode) is accomplished. The digital output system outputs valid data, which can also be read via the  $I^2C$  communication bus. This is the appropriate phase to read the measured data, either from the three push-pull logic outputs or through the  $I^2C$  transaction. All other subsystems are turned off.

These outputs are held until the MMA8491Q operation mode changes. For lower power consumption, deassert the EN pin as soon as data is read (to enter SHUTDOWN mode).

## 12.3 Next sample acquisition

The MMA8491Q needs to be brought back to the ACTIVE mode again by pulling EN pin up to a Logic 1. Another option is to power down the device and start from OFF mode as illustrated in Figure 7.

For applications where sampling intervals are greater than 30 seconds, the host can shut off the tilt sensor power after acquisition of tilt sensor output data to conserve energy and prolong battery life.

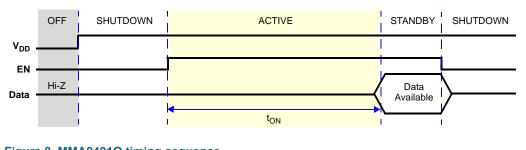

### 12.4 Power-up timing sequences

The power-up timing sequence for MMA84591Q is shown in the following figure, where  $V_{DD}$  is powered and the EN pin is activated to acquire a single sample. Additional samples can be acquired by repeating the EN pulse.

**3-Axis Multifunction Digital Accelerometer**

$t_{\text{ON}}$  is the time between EN to the end of ACTIVE stage, after which the newly acquired sample data is available.

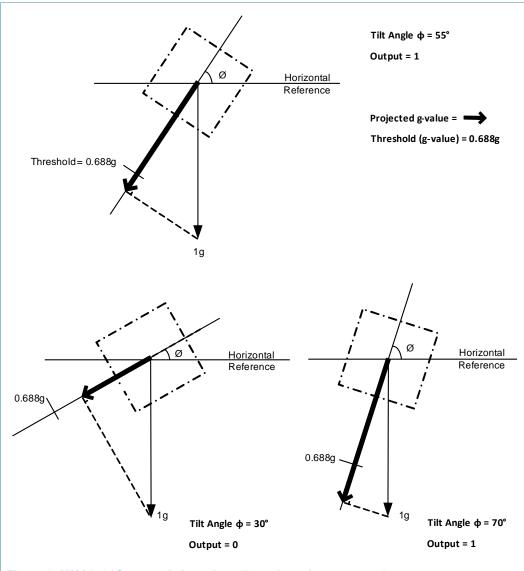

### 12.5 45° tilt detection

The output value changes according to the **absolute value** of the acceleration of the MMA8491Q compared to the threshold:

- When the acceleration's **absolute value** > the threshold 0.688 g, the output = 1.

- When the acceleration's **absolute value** ≤ the threshold, the output = 0.

$$Output = \begin{cases} 1, when (|g-value| > 0.688g) \\ 0, when (|g-value| \le 0.688g) \end{cases}$$

For example,

- When the MMA8491Q is set on a table, it senses 1 *g* acceleration on Z-axis and senses 0 *g* on X- and Y-axes.

- When the MMA8491Q is flipped upside down on the table, it senses –1 *g* acceleration on Z-axis and senses 0 *g* on X- and Y-axes.

In both cases Xout = 0, Yout = 0, and Zout = 1.

### 12.6 Tilt angle

Tilt angles can be calculated from the *g*-value threshold using the equation below. The tilt threshold is 0.688 *g*, which corresponds to  $43.5^{\circ}$ . Figure 9 illustrates the tilt angle threshold.

Tilt Angle =

$$asin\left(\frac{g-value}{1g}\right)$$

- When 0 g acceleration is present on an axis, the tilt angle = 0°; when 1 g acceleration is present on an axis, the tilt angle = 90°.

- When the tilt angle > the tilt threshold, the output for the axis is HIGH; when the tilt angle ≤ the tilt threshold, the output for the axis is LOW.

### **3-Axis Multifunction Digital Accelerometer**

Figure 9. MMA8491Q output is based on tilt angle and sensor g-value

## **13 Register descriptions**

#### Table 11. Register address map

| Name      | Туре | Register<br>Address | Auto-<br>increment<br>Address <sup>[1]</sup> | Reset  | Comment                                   |

|-----------|------|---------------------|----------------------------------------------|--------|-------------------------------------------|

| STATUS    | R    | 0x00                | 0x01                                         | 0x00   | Read time status                          |

| OUT_X_MSB | R    | 0x01                | 0x02                                         | Output | [7:0] are the 8 MSBs of the 14-bit sample |

| OUT_X_LSB | R    | 0x02                | 0x03                                         | Output | [7:2] are the 6 LSBs of the 14-bit sample |

| OUT_Y_MSB | R    | 0x03                | 0x04                                         | Output | [7:0] are the 8 MSBs of the 14-bit sample |

| OUT_Y_LSB | R    | 0x04                | 0x05                                         | Output | [7:2] are the 6 LSBs of the 14-bit sample |

| OUT_Z_MSB | R    | 0x05                | 0x06                                         | Output | [7:0] are the 8 MSBs of the 14-bit sample |

| OUT_Z_LSB | R    | 0x06                | 0x00                                         | Output | [7:2] are the 6 LSBs of the 14-bit sample |

[1] Auto-increment is the I<sup>2</sup>C feature that the I<sup>2</sup>C read address is automatically updated after each read. Auto-increment addresses that are not a simple increment are highlighted in bold. The auto-increment addressing is only enabled when device registers are read using I<sup>2</sup>C burst read mode. Therefore the internal storage of the auto-increment address is cleared whenever a stop-bit is detected.

#### Notes:

- Register contents are preserved when EN pin is set high after sampling.

- Register contents are reset when EN pin is set low.

### 13.1 STATUS - Status register (address 00h)

Register 0x00 reflects the real-time status information of the X, Y, and Z sample data. The data read bits (ZYXDR, ZDR, YDR, XDR) are set when samples are taken and ready to be read.

#### Table 12. STATUS - Status register (address 00h) bit allocation

| Bit    | 7 | 6 | 5 | 4 | 3     | 2   | 1   | 0   |

|--------|---|---|---|---|-------|-----|-----|-----|

| Symbol |   | - |   |   | ZYXDR | ZDR | YDR | XDR |

| Reset  | 0 | 0 | 0 | 0 | 0     | 0   | 0   | 0   |

| Access | R | R | R | R | R     | R   | R   | R   |

### Table 13. STATUS - Status register (address 00h) field descriptions

| Field      | Description                                                                                                                                                                                                                                                                                                                                                                                            |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3<br>ZYXDR | <ul> <li>X-, Y-, Z-axis new Data Ready (and available)</li> <li>ZYXDR signals that a new sample for all channels is available.</li> <li>ZYXDR is cleared when the high-bytes of the acceleration data (OUT_X_MSB, OUT_Y_MSB, OUT_Z_MSB) of all channels are read</li> <li>No new set of data ready (default value)</li> <li>A new set of XYZ acceleration and temperature data is available</li> </ul> |

| 2<br>ZDR   | <ul> <li>Z-axis new Data Ready (and available)</li> <li>ZDR is set whenever a new acceleration sample related to the Z-axis is generated.</li> <li>ZDR is cleared anytime OUT_Z_MSB register is read.</li> <li>0: No new Z-axis data is ready (default value)</li> <li>1: A new Z-axis data is ready</li> </ul>                                                                                        |

#### **3-Axis Multifunction Digital Accelerometer**

| Field    | Description                                                                                                                                                                                                                                                                                                  |

|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1<br>YDR | <ul> <li>Y-axis new Data Ready (and available)</li> <li>YDR is set whenever a new acceleration sample related to the Y-axis is generated.</li> <li>YDR is cleared anytime OUT_Y_MSB register is read.</li> <li>0: No new Y-axis data ready (default value)</li> <li>1: A new Y-axis data is ready</li> </ul> |

| 0<br>XDR | <ul> <li>X-axis new Data Ready (and available)</li> <li>XDR is set whenever a new acceleration sample related to the X-axis is generated.</li> <li>XDR is cleared anytime OUT_X_MSB register is read.</li> <li>0: No new X-axis data ready (default value)</li> <li>1: A new X-axis data is ready</li> </ul> |

### 13.2 Output data registers (addresses 01h to 06h)

These registers contain the X-axis, Y-axis, and Z-axis14-bit output sample data (expressed as 2's complement numbers).

- OUT\_X\_MSB, OUT\_X\_LSB, OUT\_Y\_MSB, OUT\_Y\_LSB, OUT\_Z\_MSB, and OUT\_Z\_LSB are stored in the autoincrementing address range of 0x01 0x06.

- The LSB registers can only be read immediately following the read access of the corresponding MSB register. A random read access to the LSB registers is not possible.

- Reading the MSB register and then the LSB register in sequence ensures that both bytes (LSB and MSB) belong to the same data sample, even if a new data sample arrives between reading the MSB and the LSB byte.

- The accelerometer data registers should be read only after the status register has confirmed that new data on all axes is available.

|        |   |   | g |      |       |   |   |   |  |

|--------|---|---|---|------|-------|---|---|---|--|

| Bit    | 7 | 6 | 5 | 4    | 3     | 2 | 1 | 0 |  |

| Symbol |   |   |   | XD[1 | 13:6] |   |   |   |  |

| Reset  | 0 | 0 | 0 | 0    | 0     | 0 | 0 | 0 |  |

| Access | R | R | R | R    | R     | R | R | R |  |

#### Table 14. OUT\_X\_MSB - Output data register (address 01h) bit allocation

#### Table 15. OUT\_X\_LSB - Output data register (address 02h) bit allocation

| Bit    | 7       | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|--------|---------|---|---|---|---|---|---|---|

| Symbol | XD[5:0] |   |   |   |   |   |   |   |

| Reset  | 0       | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| Access | R       | R | R | R | R | R | R | R |

### **3-Axis Multifunction Digital Accelerometer**

| Bit    | 7 | 6        | 5 | 4 | 3 | 2 | 1 | 0 |

|--------|---|----------|---|---|---|---|---|---|

| Symbol |   | YD[13:6] |   |   |   |   |   |   |

| Reset  | 0 | 0        | 0 | 0 | 0 | 0 | 0 | 0 |

| Access | R | R        | R | R | R | R | R | R |

#### Table 16. OUT\_Y\_MSB - Output data register (address 03h) bit allocation

#### Table 17. OUT\_Y\_LSB - Output data register (address 04h) bit allocation

| Bit    | 7        | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|--------|----------|---|---|---|---|---|---|---|

| Symbol | YD[13:6] |   |   |   |   |   | _ | — |

| Reset  | 0        | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| Access | R        | R | R | R | R | R | R | R |

#### Table 18. OUT\_Z\_MSB - Output data register (address 05h) bit allocation

| Bit    | 7          | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|--------|------------|---|---|---|---|---|---|---|

| Symbol | OUT_Z[7:0] |   |   |   |   |   |   |   |

| Reset  | 0          | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| Access | R          | R | R | R | R | R | R | R |

#### Table 19. OUT\_Z\_LSB - Output data register (address 06h) bit allocation

| Bit    | 7       | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|--------|---------|---|---|---|---|---|---|---|

| Symbol | ZD[5:0] |   |   |   |   |   |   |   |

| Reset  | 0       | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| Access | R       | R | R | R | R | R | R | R |

## 13.3 Accelerometer output conversion

| Table 20. Accelerometer output data |                         |  |  |  |  |  |  |

|-------------------------------------|-------------------------|--|--|--|--|--|--|

| 14-bit Data                         | Range ±8 g (1 mg/count) |  |  |  |  |  |  |

| 01 1111 1111 1111                   | +8.000 g                |  |  |  |  |  |  |

| 01 1111 1111 1110                   | +7.998 g                |  |  |  |  |  |  |

|                                     |                         |  |  |  |  |  |  |

| 00 0000 0000 0000                   | 0.000 g                 |  |  |  |  |  |  |

| 11 1111 1111 1111                   | –0.001 g                |  |  |  |  |  |  |

|                                     |                         |  |  |  |  |  |  |

| 10 0000 0000 0001                   | –7.998 g                |  |  |  |  |  |  |

| 10 0000 0000 0000                   | -8.000 g                |  |  |  |  |  |  |

## **14 Mounting guidelines**

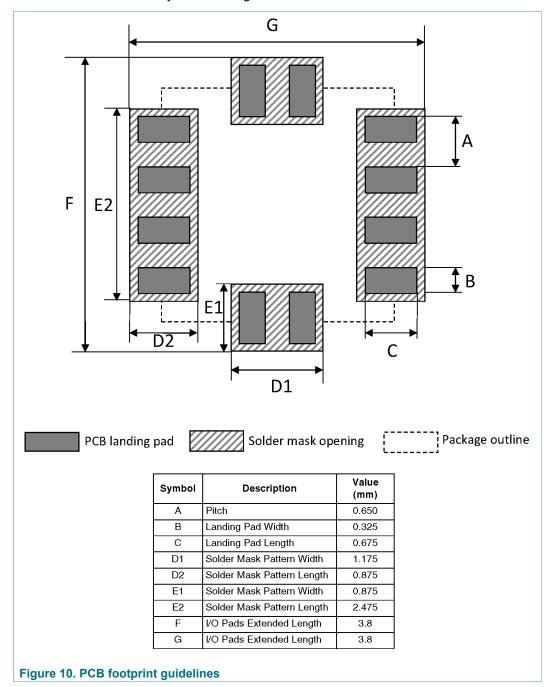

Surface-mount printed circuit board (PCB) layout is a critical portion of the total design. The footprint for the surface mount package must be the correct size to ensure proper solder connection interface between the PCB and the package. With the correct footprint, the package will self-align when subjected to a solder reflow process. The purpose is to minimize the stress on the package after board mounting. The MMA8491Q accelerometers use the QFN package. This section describes suggested methods of soldering and mounting these devices to the PCB for consumer applications.

### 14.1 Overview of soldering considerations

The information provided here is based on experiments executed on QFN devices. They do not represent exact conditions present at a customer site. Therefore, information herein should be used as guidance only, and process and design optimizations are recommended to develop an application specific solution. It should be noted that with the proper PCB footprint and solder stencil designs, the package will self-align during the solder reflow process.

### 14.2 Halogen content

This package is designed to be Halogen Free, exceeding most industry and customer standards. Halogen Free means that no homogeneous material within the assembly package shall contain chlorine (CI) in excess of 700 ppm or 0.07% weight/weight or bromine (Br) in excess of 900 ppm or 0.09% weight/weight.

### 14.3 PCB mounting recommendations

- Do not solder down the six exposed pads under the package, thus minimizing boardmounting stress impact to product performance.

- PCB landing pad is 0.675 mm x 0.325 mm as shown in Figure 10.

- Solder mask opening = PCB land pad edge + 0.2 mm larger all around.

- Stencil opening size is 0.625 mm x 0.3 mm.

- Stencil thickness is 100 μm or 125 μm.

- The solder mask should not cover any of the PCB landing pads, as shown in Figure 10.

- No additional via nor metal pattern underneath package on the top of the PCB layer.

- Do not place any components or vias within 2 mm of the package land area. This may cause additional package stress if it is too close to the package land area.

- Signal traces connected to pads should be as symmetric as possible. Put dummy traces on NC pads, to have the same length of exposed trace for all pads.

- Use a standard pick-and-place process and equipment. Do not use a hand soldering process.

- Customers are advised to be cautious about the proximity of screw-down holes to the sensor, and the location of any press fit to the assembled PCB when in an enclosure. It is important that the assembled PCB remain flat after assembly to keep electronic operation of the device optimal.

- The PCB should be rated for the multiple lead-free reflow condition with a maximum 260 °C temperature.

- NXP sensors are compliant with Restrictions on Hazardous Substances (RoHS), having halide-free molding compound (green) and lead-free terminations. These

### **3-Axis Multifunction Digital Accelerometer**

terminations are compatible with tin-lead (Sn-Pb) as well as tin-silver-copper (Sn-Ag-Cu) solder paste soldering processes. Reflow profiles applicable to those processes can be used successfully for soldering the devices.

## **15 Package Information**

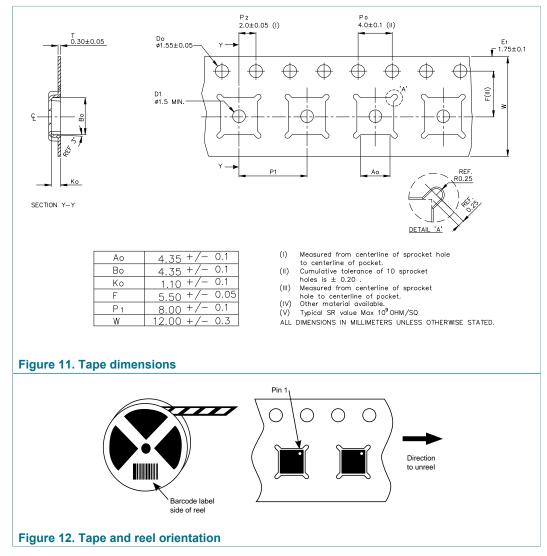

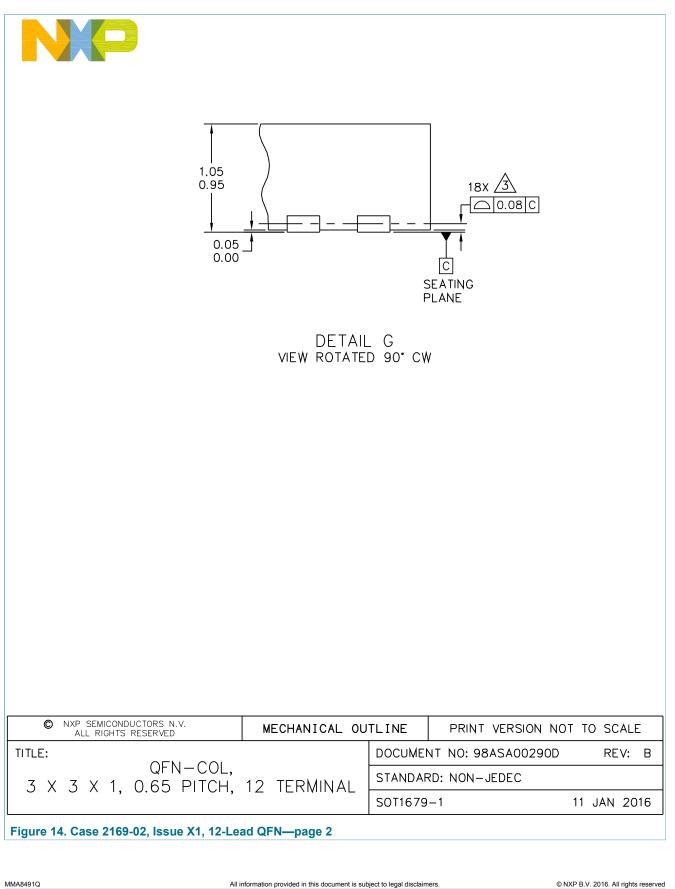

The MMA8491Q uses a 12-lead QFN package, case number 98ASA00290D.

### 15.1 Tape and reel information

### 15.2 Package description

This drawing is available for download at <u>http://www.nxp.com/files/shared/doc/</u> <u>package\_info/98ASA00290D.pdf</u>. Please consult the most recently issued drawing before initiating or completing a design.

**3-Axis Multifunction Digital Accelerometer**

**3-Axis Multifunction Digital Accelerometer**

| NOTES:<br>1. ALL DIMENSIONS ARE IN MILLIMETERS.<br>2. DIMENSIONING AND TOLERANCING PER ASME Y<br>3. COPLANARITY APPLIES TO LEADS.<br>4. MIN. METAL GAP SHOULD BE 0.2 MM.<br>5. LEADS 13 TO 18 ARE NOT SOLDERABLE. | 14.5M—1994.                     |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

|                                                                                                                                                                                                                   |                                 |

| NXP SEMICONDUCTORS N.V.                                                                                                                                                                                           |                                 |

| ALL RIGHTS RESERVED MECHANICAL OU                                                                                                                                                                                 |                                 |

| TITLE:<br>QFN-COL,                                                                                                                                                                                                | DOCUMENT NO: 98ASA00290D REV: B |

| 3 X 3 X 1, 0.65 PITCH, 12 TERMINAL                                                                                                                                                                                | STANDARD: NON-JEDEC             |

|                                                                                                                                                                                                                   | SOT1679-1 11 JAN 2016           |

| Figure 15. Case 2169-02, Issue X1, 12-Lead QFN—page 3                                                                                                                                                             |                                 |

## **16 Revision history**

| Revision number | Revision date | Description                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-----------------|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.0             | 10/2012       | Initial release                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 2.0             | 11/2012       | Characterization data verified to be complete and final                                                                                                                                                                                                                                                                                                                                                                            |

| 2.1             | 4/2016        | <ul> <li>Added MMA8491QR2 to Ordering information table</li> <li>Added paragraphs describing absolute maximum ratings</li> <li>Revised package dimensions drawings to the NXP format, no technical changes</li> <li>The format of this data sheet has been redesigned to comply with the new identity guidelines of NXP Semiconductors</li> <li>Legal texts have been adapted to the new company name where appropriate</li> </ul> |

## **17 Legal information**

#### Data sheet status

| Document status <sup>[1]</sup>  | Product status <sup>[2]</sup> | Definition                                                                                                                                                           |

|---------------------------------|-------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Data sheet: Product preview     | Development                   | This document contains information on a product<br>under development. NXP reserves the right to change<br>or discontinue this product without notice.                |

| Data sheet: Advance information | Qualification                 | This document contains information on a pre-<br>production product. Specifications and pre-production<br>information herein are subject to change without<br>notice. |

| Data sheet: Technical data      | Production                    | NXP reserves the right to change the production detail specifications as may be required to permit improvements in the design of its products.                       |

[1] Please consult the most recently issued document before initiating or completing a design.

[2] The product status of device(s) described in this document may have changed since this document was published and may differ in case of multiple devices. The latest product status information is available on the Internet at URL nxp.com.

#### Definitions

**Draft** — The document is a draft version only. The content is still under internal review and subject to formal approval, which may result in modifications or additions. NXP Semiconductors does not give any representations or warranties as to the accuracy or completeness of information included herein and shall have no liability for the consequences of use of such information.

#### Disclaimers

Information in this document is provided solely to enable system and software implementers to use NXP products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits based on the information in this document. NXP reserves the right to make changes without further notice to any products herein. NXP makes no warranty, representation, or guarantee regarding the suitability of its products for any particular purpose, nor does NXP assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in NXP data sheets and/ or specifications can and do vary in different applications, and actual performance may vary over time. All operating parameters, including "typicals," must be validated for each customer application by customer's technical experts. NXP does not convey any license under its patent rights nor the rights of others. NXP sells products pursuant to standard terms and conditions of sale, which can be found at the following address: nxp.com/salestermsandconditions. Trademarks

Trademarks

NXP, the NXP logo, Freescale, the Freescale logo and SMARTMOS are trademarks of NXP B.V. All other product or service names are the property of their respective owners.

## **NXP Semiconductors**

# **MMA8491Q**

**3-Axis Multifunction Digital Accelerometer**

## Tables

| Tab. 1.  | Ordering information                         | 2    |

|----------|----------------------------------------------|------|

| Tab. 2.  | Pin descriptions                             | 3    |

| Tab. 3.  | Absolute maximum ratings                     | 5    |

| Tab. 4.  | ESD and latch-up protection characteristics  | 5    |

| Tab. 5.  | Accelerometer mechanical characteristics     | 6    |

| Tab. 6.  | Electrical characteristics                   | 7    |

| Tab. 7.  | Serial interface pins                        | 8    |

| Tab. 8.  | I2C slave timing values                      | 8    |

| Tab. 9.  | I2C device address sequence                  | .10  |

| Tab. 10. | MMA8491Q operating modes                     | 11   |

| Tab. 11. | Register address map                         | . 15 |

| Tab. 12. | STATUS - Status register (address 00h) bit   |      |

|          | allocation                                   | 15   |

| Tab. 13. | STATUS - Status register (address 00h) field |      |

|          | descriptions                                 | 15   |

| Tab. 14. | OUT_X_MSB - Output data register          |

|----------|-------------------------------------------|

|          | (address 01h) bit allocation16            |

| Tab. 15. | OUT_X_LSB - Output data register (address |

|          | 02h) bit allocation16                     |

| Tab. 16. | OUT_Y_MSB - Output data register          |

|          | (address 03h) bit allocation17            |

| Tab. 17. | OUT_Y_LSB - Output data register (address |

|          | 04h) bit allocation17                     |

| Tab. 18. | OUT_Z_MSB - Output data register          |

|          | (address 05h) bit allocation17            |

| Tab. 19. | OUT_Z_LSB - Output data register (address |

|          | 06h) bit allocation17                     |

| Tab. 20. | Accelerometer output data17               |

|          |                                           |

## **NXP Semiconductors**

# **MMA8491Q**

**3-Axis Multifunction Digital Accelerometer**

## **Figures**

| Fig. 1. | Block Diagram                                 | 2   |

|---------|-----------------------------------------------|-----|

| Fig. 2. | Pin connection diagram                        | 3   |

| Fig. 3. | VDD connects to power supply and EN is pulsed | 4   |

| Fig. 4. | Sensitive axes orientation and output         | 4   |

| 5       | response to ±1 g (gravity) stimulus           | 5   |

| Fig. 5. | I2C slave timing diagram                      | 9   |

| Fig. 6. | I2C data sequence diagrams                    | 11  |

| Fig. 7. | MMA8491Q operating modes                      | 11  |

| Fig. 8. | MMA8491Q timing sequence                      | .13 |

| Fig. 9.  | MMA8491Q output is based on tilt angle and |      |

|----------|--------------------------------------------|------|

|          | sensor g-value                             | 14   |

| Fig. 10. | PCB footprint guidelines                   | 19   |

| Fig. 11. | Tape dimensions                            | 20   |

| Fig. 12. | Tape and reel orientation                  |      |

| Fig. 13. | Case 2169-02, Issue X1, 12-Lead QFN-       |      |

|          | page 1                                     | .21  |

| Fig. 14. | Case 2169-02, Issue X1, 12-Lead QFN-       |      |

| -        | page 2                                     | . 22 |

| Fig. 15. | Case 2169-02, Issue X1, 12-Lead QFN-       |      |

| -        | page 3                                     | . 23 |

|          |                                            |      |

### **3-Axis Multifunction Digital Accelerometer**

## Contents

| 1      | General description                            | 1    |

|--------|------------------------------------------------|------|

| 2      | Features and benefits                          | 1    |

| 3      | Typical applications                           |      |

| 4      | Ordering information                           | 2    |

| 5      | Related documentation                          |      |

| 6      | Block diagram                                  |      |

| 7      | Pinout                                         | 2    |

| 8      | Recommended application diagram                | 4    |

| 9      | Sensing direction and output response          |      |

| 10     | Mechanical and electrical specifications       |      |

| 10.1   | Absolute maximum ratings                       |      |

| 10.2   | Mechanical characteristics                     |      |

| 10.3   | Electrical characteristics                     | 7    |

| 11     | I2C Interface                                  |      |

| 11.1   | I2C read operations                            | 9    |

| 11.1.1 | Single-byte read                               |      |

| 11.1.2 | Multiple-byte read                             |      |

| 11.1.3 | I2C data sequence diagrams                     |      |

| 12     | Modes of operation                             |      |

| 12.1   | ACTIVE mode                                    | 12   |

| 12.2   | STANDBY mode                                   | .12  |

| 12.3   | Next sample acquisition                        | 12   |

| 12.4   | Power-up timing sequences                      |      |

| 12.5   | 45° tilt detection                             | .13  |

| 12.6   | Tilt angle                                     | . 13 |

| 13     | Register descriptions                          | . 15 |

| 13.1   | STATUS - Status register (address 00h)         | . 15 |

| 13.2   | Output data registers (addresses 01h to 06h) . | . 16 |

| 13.3   | Accelerometer output conversion                |      |

| 14     | Mounting guidelines                            | . 18 |

| 14.1   | Overview of soldering considerations           | . 18 |

| 14.2   | Halogen content                                | . 18 |

| 14.3   | PCB mounting recommendations                   |      |

| 15     | Package Information                            | .20  |

| 15.1   | Tape and reel information                      |      |

| 15.2   | Package description                            | . 20 |

| 16     | Revision history                               |      |

| 17     | Legal information                              | . 25 |

|        |                                                |      |

#### © NXP B.V. 2016. All rights reserved

For more information, please visit: http://www.nxp.com For sales office addresses, please send an email to: salesaddresses@nxp.com Released on 26 April 2016

# **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Accelerometers category:

Click to view products by NXP manufacturer:

Other Similar products are found below :

AD22372Z-RL7 ADXL313WACPZ-RL 805M1-0050-01 MXC6655XA MMA7455LT 805M1-0200-01 810M1-0025X AIS328DQTR 832M1-0050 805-0050 AD22301 ADXL354BEZ SCA620-EF8H1A-1 MC3413 MXC6244AU 3038-0500 ACH-01-04/10 4692 ADXL372BCCZ-RL7 735T 787-500 787AM8 793-6 793L 997-M4 HV101 HV102 HV200 PC420VP-50 PC420VR-10 786A 786A-IS 787A 787A-IS HT786A HT787A PC420VP-10 ADCMXL1021-1BMLZ ADIS16003CCCZ ADIS16006CCCZ ADIS16228CMLZ ADXL700WBRWZ-RL ADXL1003BCPZ ADXL103CE-REEL ADXL203CE-REEL ADXL206HDZ ADXL213AE ADXL213AE-REEL ADXL288WBRDZ-RL ADXL295WBRDZ-RL