# **Freescale Semiconductor**

Data Sheet: Technical Data

Document Number: MPC5554

Rev. 4, May 2012

# MPC5554 Microcontroller Data Sheet

by: Microcontroller Division

This document provides electrical specifications, pin assignments, and package diagrams for the MPC5554 microcontroller device. For functional characteristics, refer to the MPC5553/MPC5554 Microcontroller Reference Manual.

# 1 Overview

The MPC5554 microcontroller (MCU) is a member of the MPC5500 family of microcontrollers built on the Power Architecture embedded technology. This family of parts has many new features coupled with high performance CMOS technology to provide substantial reduction of cost per feature and significant performance improvement over the MPC500 family.

The host processor core of this device complies with the Power Architecture embedded category that is 100% user-mode compatible (including floating point library) with the original PowerPC instruction set. The embedded architecture enhancements improve the performance in embedded applications. The core also has additional instructions, including digital signal processing (DSP) instructions, beyond the original PowerPC instruction set.

#### **Contents**

| Ove  | rview                                                                                     |

|------|-------------------------------------------------------------------------------------------|

| Orde | ering Information                                                                         |

| Elec | trical Characteristics                                                                    |

| 3.1  | Maximum Ratings 4                                                                         |

| 3.2  | Thermal Characteristics 5                                                                 |

| 3.3  | Package 8                                                                                 |

| 3.4  | EMI (Electromagnetic Interference) Characteristics 8                                      |

| 3.5  | ESD (Electromagnetic Static Discharge) Characteristics9                                   |

| 3.6  | Voltage Regulator Controller (VRC) and<br>Power-On Reset (POR) Electrical Specifications9 |

| 3.7  | Power-Up/Down Sequencing                                                                  |

| 3.8  | DC Electrical Specifications                                                              |

| 3.9  | Oscillator and FMPLL Electrical Characteristics 20                                        |

| 3.10 | eQADC Electrical Characteristics                                                          |

| 3.11 | H7Fa Flash Memory Electrical Characteristics 23                                           |

| 3.12 | AC Specifications                                                                         |

| 3.13 | AC Timing                                                                                 |

| Mec  | hanicals                                                                                  |

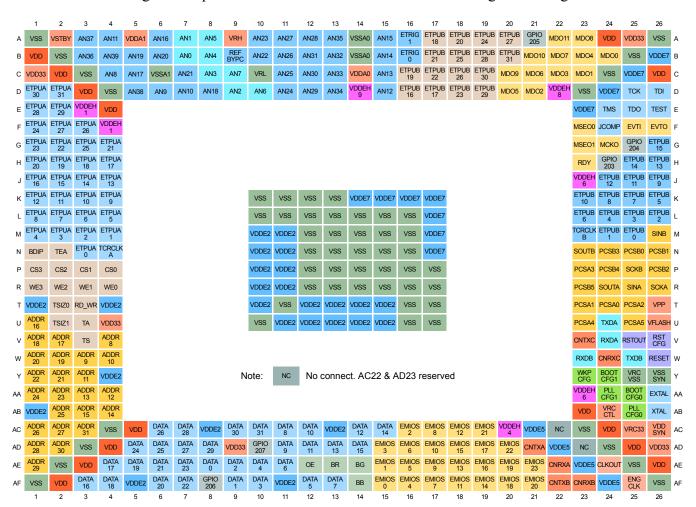

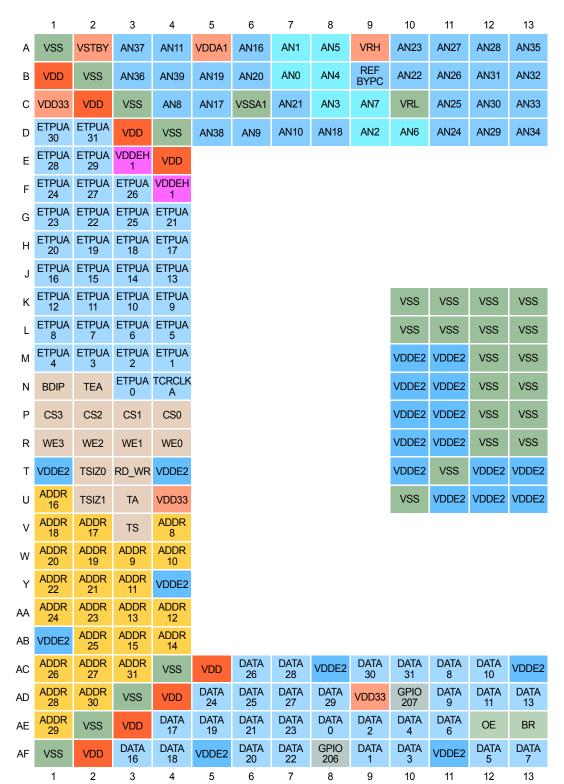

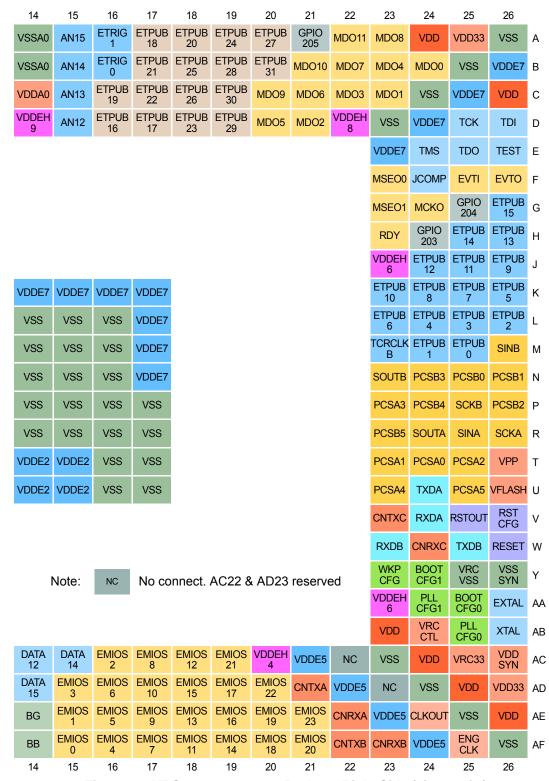

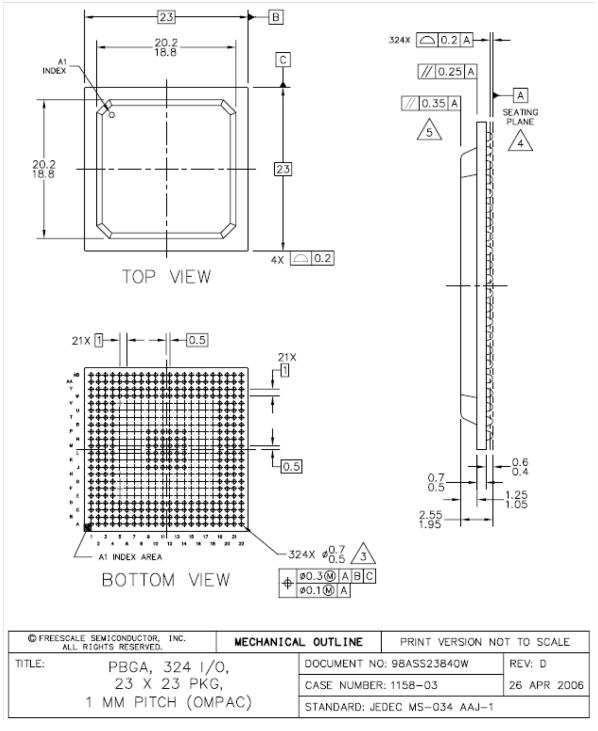

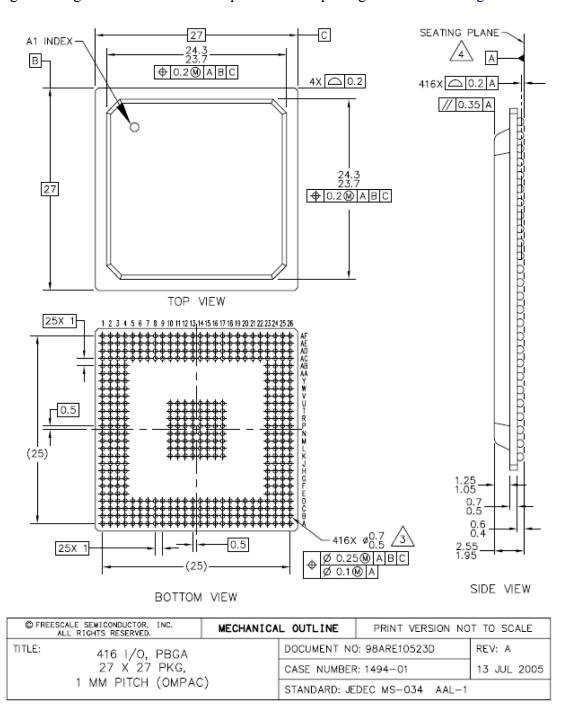

| 4.1  | MPC5553546667 416 PBGA Pinout 45                                                          |

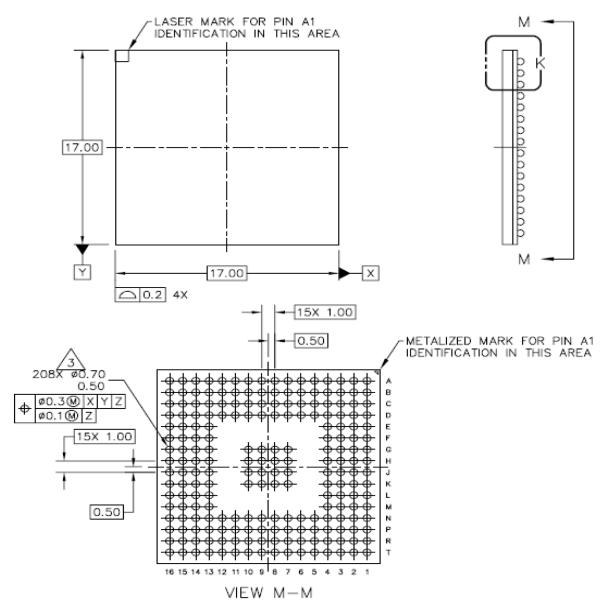

| 4.2  | MPC5554 416-Pin Package Dimensions 52                                                     |

| Revi | sion History for the MPC5554 Data Sheet 54                                                |

| 5.1  | Changes between Revision 3 and Revision 4 54                                              |

| 5.2  | Changes between Revision 2 and Revision 3 54                                              |

#### Overview

The MPC5500 family of parts contains many new features coupled with high performance CMOS technology to provide significant performance improvement over the MPC565.

The MPC5554 has two levels of memory hierarchy. The fastest accesses are to the 32-kilobytes (KB) unified cache. The next level in the hierarchy contains the 64-KB on-chip internal SRAM and two-megabytes (MB) internal flash memory. The internal SRAM and flash memory hold instructions and data. The external bus interface is designed to support most of the standard memories used with the MPC5xx family.

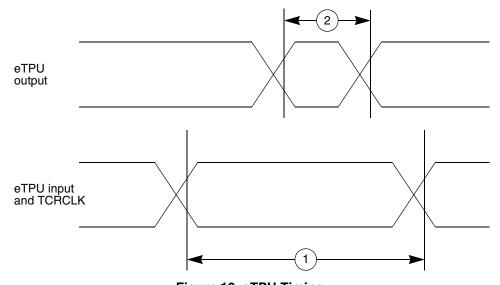

The complex input/output timer functions of the MPC5554 are performed by two enhanced time processor unit (eTPU) engines. Each eTPU engine controls 32 hardware channels, providing a total of 64 hardware channels. The eTPU has been enhanced over the TPU by providing: 24-bit timers, double-action hardware channels, variable number of parameters per channel, angle clock hardware, and additional control and arithmetic instructions. The eTPU is programmed using a high-level programming language.

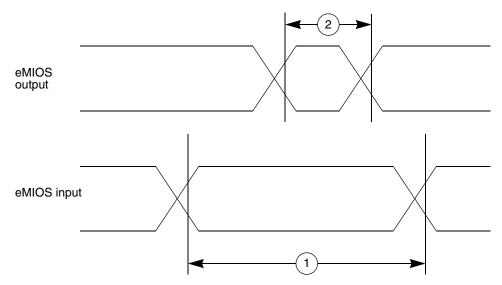

The less complex timer functions of the MPC5554 are performed by the enhanced modular input/output system (eMIOS). The eMIOS' 24 hardware channels are capable of single-action, double-action, pulse-width modulation (PWM), and modulus-counter operations. Motor control capabilities include edge-aligned and center-aligned PWM.

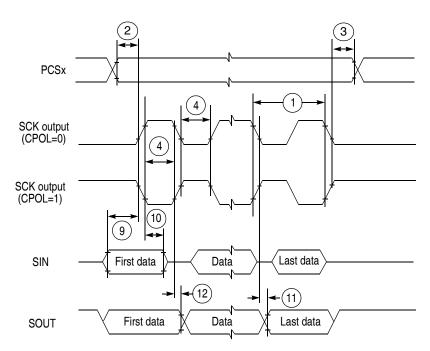

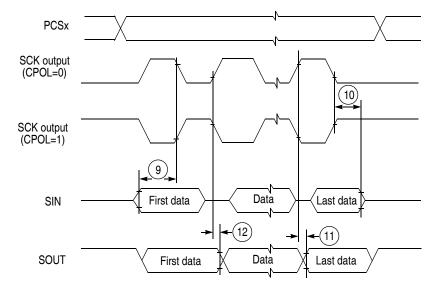

Off-chip communication is performed by a suite of serial protocols including controller area networks (FlexCANs), enhanced deserial/serial peripheral interfaces (DSPIs), and enhanced serial communications interfaces (eSCIs). The DSPIs support pin reduction through hardware serialization and deserialization of timer channels and general-purpose input/output (GPIOs) signals.

The MCU has an on-chip enhanced queued dual analog-to-digital converter (eQADC). 324 s40-channels.

The system integration unit (SIU) performs several chip-wide configuration functions. Pad configuration and general-purpose input and output (GPIO) are controlled from the SIU. External interrupts and reset control are also determined by the SIU. The internal multiplexer submodule provides multiplexing of eQADC trigger sources, daisy chaining the DSPIs, and external interrupt signal multiplexing.

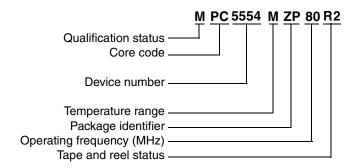

# 2 Ordering Information

Temperature Range  $M = -40^{\circ} C$  to  $125^{\circ} C$   $A = -55^{\circ} C$  to  $125^{\circ} C$

Package Identifier

ZP = 416PBGA SnPb

VR = 416PBGA Pb-free

**Operating Frequency** 80 = 80 MHz 112 = 112 MHz 132 = 132 MHz **Tape and Reel Status** R2 = Tape and reel (blank) = Trays

Qualification Status

P = Pre qualification

M = Fully spec. qualified

Note: Not all options are available on all devices. Refer to Table 1.

Figure 1. MPC5500 Family Part Number Example

Unless noted in this data sheet, all specifications apply from  $T_L$  to  $T_H$ .

**Table 1. Orderable Part Numbers**

| Freescale Part Number <sup>1</sup> | Package Description                       | Speed (MHz) Operating |                                       |                        | Temperature <sup>2</sup> |  |

|------------------------------------|-------------------------------------------|-----------------------|---------------------------------------|------------------------|--------------------------|--|

| Treescale Fait Number              | Fackage Description                       | Nominal               | Max. <sup>3</sup> (f <sub>MAX</sub> ) | Min. (T <sub>L</sub> ) | Max. (T <sub>H</sub> )   |  |

| MPC5554MVR132                      |                                           | 132                   | 132                                   |                        |                          |  |

| MPC5554MVR112                      | MPC5554 416 package<br>Lead-free (PbFree) | 112                   | 114                                   | −40° C                 | 125° C                   |  |

| MPC5554MVR80                       |                                           | 80                    | 82                                    |                        |                          |  |

| MPC5554AVR132                      |                                           | 132                   | 132                                   | −55° C                 | 125° C                   |  |

| MPC5554MZP132                      |                                           | 132                   | 132                                   |                        |                          |  |

| MPC5554MZP112                      | MPC5554 416 package                       | 112                   | 114                                   | −40° C                 | 125° C                   |  |

| MPC5554MZP80                       | Leaded (SnPb)                             | 80                    | 82                                    |                        |                          |  |

| MPC5554AZP132                      |                                           | 132                   | 132                                   | −55° C                 | 125° C                   |  |

All devices are PPC5554, rather than MPC5554, until product qualifications are complete. Not all configurations are available in the PPC parts.

<sup>&</sup>lt;sup>2</sup> The lowest ambient operating temperature is referenced by T<sub>L</sub>; the highest ambient operating temperature is referenced by T<sub>H</sub>.

Speed is the nominal maximum frequency. Max. speed is the maximum speed allowed including frequency modulation (FM).

82 MHz parts allow for 80 MHz system clock + 2% FM; 114 MHz parts allow for 112 MHz system clock + 2% FM; and132 MHz parts allow for 128 MHz system clock + 2% FM.

# 3 Electrical Characteristics

This section contains detailed information on power considerations, DC/AC electrical characteristics, and AC timing specifications for the MCU.

# 3.1 Maximum Ratings

Table 2. Absolute Maximum Ratings <sup>1</sup>

| Spec |                                                                                                     |                                      | Min.                                | Max.                                 | Unit |

|------|-----------------------------------------------------------------------------------------------------|--------------------------------------|-------------------------------------|--------------------------------------|------|

| 1    | 1.5 V core supply voltage <sup>2</sup>                                                              | $V_{DD}$                             | -0.3                                | 1.7                                  | V    |

| 2    | Flash program/erase voltage                                                                         | $V_{PP}$                             | -0.3                                | 6.5                                  | V    |

| 4    | Flash read voltage                                                                                  | V <sub>FLASH</sub>                   | -0.3                                | 4.6                                  | V    |

| 5    | SRAM standby voltage                                                                                | V <sub>STBY</sub>                    | -0.3                                | 1.7                                  | V    |

| 6    | Clock synthesizer voltage                                                                           | V <sub>DDSYN</sub>                   | -0.3                                | 4.6                                  | V    |

| 7    | 3.3 V I/O buffer voltage                                                                            | V <sub>DD33</sub>                    | -0.3                                | 4.6                                  | V    |

| 8    | Voltage regulator control input voltage                                                             | V <sub>RC33</sub>                    | -0.3                                | 4.6                                  | V    |

| 9    | Analog supply voltage (reference to V <sub>SSA</sub> )                                              | $V_{DDA}$                            | -0.3                                | 5.5                                  | V    |

| 10   | I/O supply voltage (fast I/O pads) <sup>3</sup>                                                     | $V_{DDE}$                            | -0.3                                | 4.6                                  | V    |

| 11   | I/O supply voltage (slow and medium I/O pads) <sup>3</sup>                                          | $V_{DDEH}$                           | -0.3                                | 6.5                                  | V    |

| 12   | DC input voltage <sup>4</sup> V <sub>DDEH</sub> powered I/O pads  V <sub>DDE</sub> powered I/O pads | V <sub>IN</sub>                      | -1.0 <sup>5</sup> -1.0 <sup>5</sup> | 6.5 <sup>6</sup><br>4.6 <sup>7</sup> | V    |

| 13   | Analog reference high voltage (reference to V <sub>RL</sub> )                                       | V <sub>RH</sub>                      | -0.3                                | 5.5                                  | V    |

| 14   | V <sub>SS</sub> to V <sub>SSA</sub> differential voltage                                            | V <sub>SS</sub> – V <sub>SSA</sub>   | -0.1                                | 0.1                                  | V    |

| 15   | V <sub>DD</sub> to V <sub>DDA</sub> differential voltage                                            | $V_{DD} - V_{DDA}$                   | -V <sub>DDA</sub>                   | $V_{DD}$                             | V    |

| 16   | V <sub>REF</sub> differential voltage                                                               | $V_{RH} - V_{RL}$                    | -0.3                                | 5.5                                  | V    |

| 17   | V <sub>RH</sub> to V <sub>DDA</sub> differential voltage                                            | V <sub>RH</sub> – V <sub>DDA</sub>   | -5.5                                | 5.5                                  | V    |

| 18   | V <sub>RL</sub> to V <sub>SSA</sub> differential voltage                                            | V <sub>RL</sub> – V <sub>SSA</sub>   | -0.3                                | 0.3                                  | V    |

| 19   | V <sub>DDEH</sub> to V <sub>DDA</sub> differential voltage                                          | V <sub>DDEH</sub> – V <sub>DDA</sub> | $-V_{DDA}$                          | $V_{DDEH}$                           | V    |

| 20   | V <sub>DDF</sub> to V <sub>DD</sub> differential voltage                                            | $V_{\rm DDF} - V_{\rm DD}$           | -0.3                                | 0.3                                  | V    |

| 21   | $V_{RC33}$ to $V_{DDSYN}$ differential voltage spec has been moved to                               | Table 9 DC Electric                  | al Specification                    | ons, Spec 43a                        |      |

| 22   | V <sub>SSSYN</sub> to V <sub>SS</sub> differential voltage                                          | V <sub>SSSYN</sub> – V <sub>SS</sub> | -0.1                                | 0.1                                  | V    |

| 23   | V <sub>RCVSS</sub> to V <sub>SS</sub> differential voltage                                          | V <sub>RCVSS</sub> – V <sub>SS</sub> | -0.1                                | 0.1                                  | V    |

| 24   | Maximum DC digital input current <sup>8</sup> (per pin, applies to all digital pins) <sup>4</sup>   | I <sub>MAXD</sub>                    | -2                                  | 2                                    | mA   |

| 25   | Maximum DC analog input current <sup>9</sup> (per pin, applies to all analog pins)                  | I <sub>MAXA</sub>                    | -3                                  | 3                                    | mA   |

| 26   | Maximum operating temperature range <sup>10</sup> Die junction temperature                          | TJ                                   | T <sub>L</sub>                      | 150.0                                | °C   |

| 27   | Storage temperature range                                                                           | T <sub>STG</sub>                     | -55.0                               | 150.0                                | °C   |

| Table 2. Absolute | Maximum | Ratings | 1 | (continued) |

|-------------------|---------|---------|---|-------------|

|-------------------|---------|---------|---|-------------|

| Spec | Characteristic                                                             | Symbol           | Min. | Max.           | Unit |

|------|----------------------------------------------------------------------------|------------------|------|----------------|------|

| 28   | Maximum solder temperature <sup>11</sup> Lead free (Pb-free) Leaded (SnPb) | T <sub>SDR</sub> |      | 260.0<br>245.0 | °C   |

| 29   | Moisture sensitivity level <sup>12</sup>                                   | MSL              | _    | 3              |      |

Functional operating conditions are given in the DC electrical specifications. Absolute maximum ratings are stress ratings only, and functional operation at the maxima is not guaranteed. Stress beyond any of the listed maxima can affect device reliability or cause permanent damage to the device.

- $^2$  1.5 V  $\pm$  10% for proper operation. This parameter is specified at a maximum junction temperature of 150 °C.

- <sup>3</sup> All functional non-supply I/O pins are clamped to V<sub>SS</sub> and V<sub>DDE</sub>, or V<sub>DDEH</sub>.

- <sup>4</sup> AC signal overshoot and undershoot of up to ± 2.0 V of the input voltages is permitted for an accumulative duration of 60 hours over the complete lifetime of the device (injection current not limited for this duration).

- <sup>5</sup> Internal structures hold the voltage greater than -1.0 V if the injection current limit of 2 mA is met. Keep the negative DC voltage greater than -0.6 V on eTPUB[15] and SINB during the internal power-on reset (POR) state.

- Internal structures hold the input voltage less than the maximum voltage on all pads powered by V<sub>DDEH</sub> supplies, if the maximum injection current specification is met (2 mA for all pins) and V<sub>DDEH</sub> is within the operating voltage specifications.

- Internal structures hold the input voltage less than the maximum voltage on all pads powered by V<sub>DDE</sub> supplies, if the maximum injection current specification is met (2 mA for all pins) and V<sub>DDE</sub> is within the operating voltage specifications.

- <sup>8</sup> Total injection current for all pins (including both digital and analog) must not exceed 25 mA.

- 9 Total injection current for all analog input pins must not exceed 15 mA.

- <sup>10</sup> Lifetime operation at these specification limits is not guaranteed.

- <sup>11</sup> Moisture sensitivity profile per IPC/JEDEC J-STD-020D.

- <sup>12</sup> Moisture sensitivity per JEDEC test method A112.

## 3.2 Thermal Characteristics

The shaded rows in the following table indicate information specific to a four-layer board.

Table 3. MPC5554 Thermal Characteristics

| Spec | MPC5554 Thermal Characteristic                                                   | Symbol           | 416 PBGA | Unit |

|------|----------------------------------------------------------------------------------|------------------|----------|------|

| 1    | Junction to ambient <sup>1, 2</sup> , natural convection (one-layer board)       | $R_{	heta JA}$   | 24       | °C/W |

| 2    | Junction to ambient <sup>1, 3</sup> , natural convection (four-layer board 2s2p) | $R_{\theta JA}$  | 18       | °C/W |

| 3    | Junction to ambient <sup>1, 3</sup> (@200 ft./min., one-layer board)             | $R_{\theta JMA}$ | 19       | °C/W |

| 4    | Junction to ambient <sup>1, 3</sup> (@200 ft./min., four-layer board 2s2p)       | $R_{\theta JMA}$ | 15       | °C/W |

| 5    | Junction to board <sup>4</sup> (four-layer board 2s2p)                           | $R_{\theta JB}$  | 9        | °C/W |

| 6    | Junction to case <sup>5</sup>                                                    | $R_{	heta JC}$   | 5        | °C/W |

| 7    | Junction to package top <sup>6</sup> , natural convection                        | $\Psi_{JT}$      | 2        | °C/W |

Junction temperature is a function of on-chip power dissipation, package thermal resistance, mounting site (board) temperature, ambient temperature, air flow, power dissipation of other components on the board, and board thermal resistance.

<sup>&</sup>lt;sup>2</sup> Per SEMI G38-87 and JEDEC JESD51-2 with the single-layer board horizontal.

<sup>&</sup>lt;sup>3</sup> Per JEDEC JESD51-6 with the board horizontal.

Thermal resistance between the die and the printed circuit board per JEDEC JESD51-8. Board temperature is measured on the top surface of the board near the package.

<sup>&</sup>lt;sup>5</sup> Indicates the average thermal resistance between the die and the case top surface as measured by the cold plate method (MIL SPEC-883 Method 1012.1) with the cold plate temperature used for the case temperature.

<sup>&</sup>lt;sup>6</sup> Thermal characterization parameter indicating the temperature difference between package top and the junction temperature per JEDEC JESD51-2.

# 3.2.1 General Notes for Specifications at Maximum Junction Temperature

An estimation of the device junction temperature, T<sub>1</sub>, can be obtained from the equation:

$$T_{J} = T_{A} + (R_{\theta JA} \times P_{D})$$

where:

$T_A$  = ambient temperature for the package ( ${}^{o}C$ )

$R_{\theta JA}$  = junction to ambient thermal resistance (°C/W)

$P_D$  = power dissipation in the package (W)

The thermal resistance values used are based on the JEDEC JESD51 series of standards to provide consistent values for estimations and comparisons. The difference between the values determined for the single-layer (1s) board compared to a four-layer board that has two signal layers, a power and a ground plane (2s2p), demonstrate that the effective thermal resistance is not a constant. The thermal resistance depends on the:

- Construction of the application board (number of planes)

- Effective size of the board which cools the component

- Quality of the thermal and electrical connections to the planes

- Power dissipated by adjacent components

Connect all the ground and power balls to the respective planes with one via per ball. Using fewer vias to connect the package to the planes reduces the thermal performance. Thinner planes also reduce the thermal performance. When the clearance between the vias leave the planes virtually disconnected, the thermal performance is also greatly reduced.

As a general rule, the value obtained on a single-layer board is within the normal range for the tightly packed printed circuit board. The value obtained on a board with the internal planes is usually within the normal range if the application board has:

- One oz. (35 micron nominal thickness) internal planes

- Components are well separated

- Overall power dissipation on the board is less than 0.02 W/cm<sup>2</sup>

The thermal performance of any component depends on the power dissipation of the surrounding components. In addition, the ambient temperature varies widely within the application. For many natural convection and especially closed box applications, the board temperature at the perimeter (edge) of the package is approximately the same as the local air temperature near the device. Specifying the local ambient conditions explicitly as the board temperature provides a more precise description of the local ambient conditions that determine the temperature of the device.

At a known board temperature, the junction temperature is estimated using the following equation:

$$T_J = T_B + (R_{\theta JB} \times P_D)$$

where:

$T_J = \text{junction temperature (}^{\circ}\text{C}\text{)}$

$T_B = \text{board temperature at the package perimeter (}^{\circ}\text{C/W}\text{)}$

$R_{\theta JB} = \text{junction-to-board thermal resistance (}^{\circ}\text{C/W}\text{)}$  per JESD51-8

$P_D = \text{power dissipation in the package (W)}$

When the heat loss from the package case to the air does not factor into the calculation, an acceptable value for the junction temperature is predictable. Ensure the application board is similar to the thermal test condition, with the component soldered to a board with internal planes.

The thermal resistance is expressed as the sum of a junction-to-case thermal resistance plus a case-to-ambient thermal resistance:

$$\begin{split} R_{\theta JA} &= R_{\theta JC} + R_{\theta CA} \\ \text{where:} \\ R_{\theta JA} &= \text{junction-to-ambient thermal resistance (°C/W)} \\ R_{\theta JC} &= \text{junction-to-case thermal resistance (°C/W)} \\ R_{\theta CA} &= \text{case-to-ambient thermal resistance (°C/W)} \end{split}$$

$R_{\theta JC}$  is device related and is not affected by other factors. The thermal environment can be controlled to change the case-to-ambient thermal resistance,  $R_{\theta CA}$ . For example, change the air flow around the device, add a heat sink, change the mounting arrangement on the printed circuit board, or change the thermal dissipation on the printed circuit board surrounding the device. This description is most useful for packages with heat sinks where 90% of the heat flow is through the case to heat sink to ambient. For most packages, a better model is required.

A more accurate two-resistor thermal model can be constructed from the junction-to-board thermal resistance and the junction-to-case thermal resistance. The junction-to-case thermal resistance describes when using a heat sink or where a substantial amount of heat is dissipated from the top of the package. The junction-to-board thermal resistance describes the thermal performance when most of the heat is conducted to the printed circuit board. This model can be used to generate simple estimations and for computational fluid dynamics (CFD) thermal models.

To determine the junction temperature of the device in the application on a prototype board, use the thermal characterization parameter  $(\Psi_{JT})$  to determine the junction temperature by measuring the temperature at the top center of the package case using the following equation:

$$T_{J} = T_{T} + (\Psi_{JT} \times P_{D})$$

where:

$$T_{T} = \text{thermocouple temperature on top of the package (°C)}$$

$$\Psi_{JT} = \text{thermal characterization parameter (°C/W)}$$

$$P_{D} = \text{power dissipation in the package (W)}$$

The thermal characterization parameter is measured in compliance with the JESD51-2 specification using a 40-gauge type T thermocouple epoxied to the top center of the package case. Position the thermocouple so that the thermocouple junction rests on the package. Place a small amount of epoxy on the thermocouple junction and approximately 1 mm of wire extending from the junction. Place the thermocouple wire flat against the package case to avoid measurement errors caused by the cooling effects of the thermocouple wire

#### References:

Semiconductor Equipment and Materials International 3081 Zanker Rd.

San Jose, CA., 95134

(408) 943-6900

MIL-SPEC and EIA/JESD (JEDEC) specifications are available from Global Engineering Documents at 800-854-7179 or 303-397-7956.

JEDEC specifications are available on the web at http://www.jedec.org.

- 1. C.E. Triplett and B. Joiner, "An Experimental Characterization of a 272 PBGA Within an Automotive Engine Controller Module," Proceedings of SemiTherm, San Diego, 1998, pp. 47–54.

- 2. G. Kromann, S. Shidore, and S. Addison, "Thermal Modeling of a PBGA for Air-Cooled Applications," Electronic Packaging and Production, pp. 53–58, March 1998.

- 3. B. Joiner and V. Adams, "Measurement and Simulation of Junction to Board Thermal Resistance and Its Application in Thermal Modeling," Proceedings of SemiTherm, San Diego, 1999, pp. 212–220.

# 3.3 Package

The MPC5554 is available in packaged form. Read the package options in Section 2, "Ordering Information." Refer to Section 4, "Mechanicals," for pinouts and package drawings.

# 3.4 EMI (Electromagnetic Interference) Characteristics

Table 4. EMI Testing Specifications <sup>1</sup>

| Spec | Characteristic                                                          | Minimum | Typical | Maximum                            | Unit |

|------|-------------------------------------------------------------------------|---------|---------|------------------------------------|------|

| 1    | Scan range                                                              | 0.15    | _       | 1000                               | MHz  |

| 2    | Operating frequency                                                     | _       | _       | f <sub>MAX</sub>                   | MHz  |

| 3    | V <sub>DD</sub> operating voltages                                      | _       | 1.5     | _                                  | V    |

| 4    | $V_{DDSYN}, V_{RC33}, V_{DD33}, V_{FLASH}, V_{DDE}$ operating voltages  | _       | 3.3     | _                                  | V    |

| 5    | V <sub>PP</sub> V <sub>DDEH</sub> , V <sub>DDA</sub> operating voltages | _       | 5.0     | _                                  | V    |

| 6    | Maximum amplitude                                                       |         | _       | 14 <sup>2</sup><br>32 <sup>3</sup> | dBuV |

| 7    | Operating temperature                                                   | _       | _       | 25                                 | °C   |

<sup>&</sup>lt;sup>1</sup> EMI testing and I/O port waveforms per SAE J1752/3 issued 1995-03. Qualification testing was performed on the MPC5554 and applied to the MPC5500 family as generic EMI performance data.

<sup>&</sup>lt;sup>2</sup> Measured with the single-chip EMI program.

<sup>&</sup>lt;sup>3</sup> Measured with the expanded EMI program.

# 3.5 ESD (Electromagnetic Static Discharge) Characteristics

Table 5. ESD Ratings <sup>1, 2</sup>

| Characteristic                                                        | Symbol | Value             | Unit   |

|-----------------------------------------------------------------------|--------|-------------------|--------|

| ESD for human body model (HBM)                                        |        | 2000              | V      |

| LIDM aircuit description                                              | R1     | 1500              | Ω      |

| HBM circuit description                                               | С      | 100               | pF     |

| ESD for field induced charge model (FDCM)                             |        | 500 (all pins)    |        |

| ESD for field induced charge moder (FDCM)                             |        | 750 (corner pins) | V      |

| Number of pulses per pin: Positive pulses (HBM) Negative pulses (HBM) |        | 1 1               |        |

| Interval of pulses                                                    | _      | 1                 | second |

<sup>&</sup>lt;sup>1</sup> All ESD testing conforms to CDF-AEC-Q100 Stress Test Qualification for Automotive Grade Integrated Circuits.

# 3.6 Voltage Regulator Controller (V<sub>RC</sub>) and Power-On Reset (POR) Electrical Specifications

The following table lists the V<sub>RC</sub> and POR electrical specifications:

Table 6. V<sub>RC</sub> and POR Electrical Specifications

| Spec | Charac                                                                                            | teristic                                                                                                         | Symbol                   | Min.                     | Max.                         | Units |

|------|---------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|--------------------------|--------------------------|------------------------------|-------|

| 1    | 1.5 V (V <sub>DD</sub> ) POR <sup>1</sup> Negated (ramp up) Asserted (ramp down)                  |                                                                                                                  | V <sub>POR15</sub>       | 1.1<br>1.1               | 1.35<br>1.35                 | V     |

| 2    | 3.3 V (V <sub>DDSYN</sub> ) POR <sup>1</sup>                                                      | Asserted (ramp up) Negated (ramp up) Asserted (ramp down) Negated (ramp down)                                    | V <sub>POR33</sub>       | 0.0<br>2.0<br>2.0<br>0.0 | 0.30<br>2.85<br>2.85<br>0.30 | V     |

| 3    | RESET pin supply (V <sub>DDEH6</sub> ) POR <sup>1, 2</sup> Negated (ramp up) Asserted (ramp down) |                                                                                                                  | V <sub>POR5</sub>        | 2.0<br>2.0               | 2.85<br>2.85                 | V     |

| 4    |                                                                                                   | Before V <sub>RC</sub> allows the pass transistor to start turning on                                            | V <sub>TRANS_START</sub> | 1.0                      | 2.0                          | V     |

| 5    | V <sub>RC33</sub> voltage                                                                         | When V <sub>RC</sub> allows the pass transistor to completely turn on <sup>3, 4</sup>                            | V <sub>TRANS_ON</sub>    | 2.0                      | 2.85                         | V     |

| 6    |                                                                                                   | When the voltage is greater than the voltage at which the $V_{RC}$ keeps the 1.5 V supply in regulation $^{5,6}$ | V <sub>VRC33REG</sub>    | 3.0                      | _                            | ٧     |

|      |                                                                                                   | – 55° C <sup>7</sup>                                                                                             |                          | 11.0                     |                              | mA    |

|      | Current can be sourced                                                                            | -40° C                                                                                                           |                          | 11.0                     | _                            | mA    |

| 7    | by V <sub>RCCTL</sub> at Tj:                                                                      | 25° C                                                                                                            | I <sub>VRCCTL</sub> 8    | 9.0                      | _                            | mA    |

|      |                                                                                                   | 150° C                                                                                                           |                          | 7.5                      | _                            | mA    |

Device failure is defined as: 'If after exposure to ESD pulses, the device does not meet the device specification requirements, which includes the complete DC parametric and functional testing at room temperature and hot temperature.

## Table 6. V<sub>RC</sub> and POR Electrical Specifications (continued)

| Spec | Characte                                                                                                                                 | Symbol                          | Min.               | Max.                                  | Units    |        |

|------|------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|--------------------|---------------------------------------|----------|--------|

| 8    | Voltage differential during power up su $V_{DD33}$ can lag $V_{DDSYN}$ or $V_{DDEH6}$ before $V_{POR33}$ and $V_{POR5}$ minimums respect | V <sub>DD33_LAG</sub>           | _                  | 1.0                                   | V        |        |

| 9    | Absolute value of slew rate on power s                                                                                                   | _                               | _                  | 50                                    | V/ms     |        |

| 10   | Required gain at Tj:<br>$I_{DD} \div I_{VRCCTL}$ (@ $f_{sys} = f_{MAX}$ ) <sup>6, 8, 9, 10</sup>                                         | – 55° C <sup>7</sup><br>– 40° C | DETA 11            | 70<br>70                              | _        | _<br>_ |

| 10   |                                                                                                                                          | 25° C<br>150° C                 | BETA <sup>11</sup> | 85 <sup>11</sup><br>105 <sup>11</sup> | —<br>500 | _      |

The internal POR signals are V<sub>POR15</sub>, V<sub>POR33</sub>, and V<sub>POR5</sub>. On power up, assert RESET before the internal POR negates. RESET must remain asserted until the power supplies are within the operating conditions as specified in Table 9 DC Electrical Specifications. On power down, assert RESET before any power supplies fall outside the operating conditions and until the internal POR asserts.

# 3.7 Power-Up/Down Sequencing

Power sequencing between the 1.5 V power supply and  $V_{DDSYN}$  or the  $\overline{RESET}$  power supplies is required if using an external 1.5 V power supply with  $V_{RC33}$  tied to ground (GND). To avoid power-sequencing,  $V_{RC33}$  must be powered up within the specified operating range, even if the on-chip voltage regulator controller is not used. Refer to Section 3.7.2, "Power-Up Sequence (VRC33 Grounded)," and Section 3.7.3, "Power-Down Sequence (VRC33 Grounded)."

Power sequencing requires that  $V_{DD33}$  must reach a certain voltage where the values are read as ones before the POR signal negates. Refer to Section 3.7.1, "Input Value of Pins During POR Dependent on VDD33."

Although power sequencing is not required between  $V_{RC33}$  and  $V_{DDSYN}$  during power up,  $V_{RC33}$  must not lead  $V_{DDSYN}$  by more than 600 mV or lag by more than 100 mV for the  $V_{RC}$  stage turn-on to operate within specification. Higher spikes in the emitter current of the pass transistor occur if  $V_{RC33}$  leads or lags  $V_{DDSYN}$  by more than these amounts. The value of that higher spike in current depends on the board power supply circuitry and the amount of board level capacitance.

$<sup>^{2}</sup>$  V<sub>IL S</sub> (Table 9, Spec15) is guaranteed to scale with V<sub>DDEH6</sub> down to V<sub>POR5</sub>.

Supply full operating current for the 1.5 V supply when the 3.3 V supply reaches this range.

<sup>&</sup>lt;sup>4</sup> It is possible to reach the current limit during ramp up—do not treat this event as short circuit current.

<sup>5</sup> At peak current for device.

Requires compliance with Freescale's recommended board requirements and transistor recommendations. Board signal traces/routing from the V<sub>RCCTL</sub> package signal to the base of the external pass transistor and between the emitter of the pass transistor to the V<sub>DD</sub> package signals must have a maximum of 100 nH inductance and minimal resistance (less than 1 Ω). V<sub>RCCTL</sub> must have a nominal 1 μF phase compensation capacitor to ground. V<sub>DD</sub> must have a 20 μF (nominal) bulk capacitor (greater than 4 μF over all conditions, including lifetime). Place high-frequency bypass capacitors consisting of eight 0.01 μF, two 0.1 μF, and one 1 μF capacitors around the package on the V<sub>DD</sub> supply signals.

<sup>&</sup>lt;sup>7</sup> Only available on devices that support -55° C.

$<sup>^{8}</sup>$  I<sub>VRCCTL</sub> is measured at the following conditions: V<sub>DD</sub> = 1.35 V, V<sub>RC33</sub> = 3.1 V, V<sub>VRCCTL</sub> = 2.2 V.

<sup>&</sup>lt;sup>9</sup> Refer to Table 1 for the maximum operating frequency.

<sup>&</sup>lt;sup>10</sup> Values are based on I<sub>DD</sub> from high-use applications as explained in the I<sub>DD</sub> Electrical Specification.

<sup>&</sup>lt;sup>11</sup> BETA represents the worst-case external transistor. It is measured on a per-part basis and calculated as ( $I_{DD}

div I_{VBCCTI}$ ).

Furthermore, when all of the PORs negate, the system clock starts to toggle, adding another large increase of the current consumed by V<sub>RC33</sub>. If V<sub>RC33</sub> lags V<sub>DDSYN</sub> by more than 100 mV, the increase in current consumed can drop V<sub>DD</sub> low enough to assert the 1.5 V POR again. Oscillations are possible when the  $1.5~\mathrm{V}$  POR asserts and stops the system clock, causing the voltage on  $V_{DD}$  to rise until the  $1.5~\mathrm{V}$  POR negates again. All oscillations stop when V<sub>RC33</sub> is powered sufficiently.

When powering down, V<sub>RC33</sub> and V<sub>DDSYN</sub> have no delta requirement to each other, because the bypass capacitors internal and external to the device are already charged. When not powering up or down, no delta between  $V_{RC33}$  and  $V_{DDSYN}$  is required for the  $V_{RC}$  to operate within specification.

There are no power up/down sequencing requirements to prevent issues such as latch-up, excessive current spikes, and so on. Therefore, the state of the I/O pins during power up and power down varies depending on which supplies are powered.

Table 7 gives the pin state for the sequence cases for all pins with pad type pad fc (fast type).

| V <sub>DDE</sub> | V <sub>DD33</sub> | V <sub>DD</sub> | POR      | Pin Status for Fast Pad Output Driver pad_fc (fast) |

|------------------|-------------------|-----------------|----------|-----------------------------------------------------|

| Low              | _                 | _               | Asserted | Low                                                 |

| $V_{DDE}$        | Low               | Low             | Asserted | High                                                |

| $V_{DDE}$        | Low               | $V_{DD}$        | Asserted | High                                                |

| $V_{DDE}$        | V <sub>DD33</sub> | Low             | Asserted | High impedance (Hi-Z)                               |

| $V_{DDE}$        | $V_{DD33}$        | $V_{DD}$        | Asserted | Hi-Z                                                |

| $V_{DDE}$        | V <sub>DD33</sub> | $V_{DD}$        | Negated  | Functional                                          |

Table 7. Pin Status for Fast Pads During the Power Sequence

Table 8 gives the pin state for the sequence cases for all pins with pad type pad mh (medium type) and pad sh (slow type).

| V <sub>DDEH</sub> | V <sub>DD</sub> | POR      | Pin Status for Medium and Slow Pad Output Driver pad_mh (medium) pad_sh (slow) |

|-------------------|-----------------|----------|--------------------------------------------------------------------------------|

| Low               | _               | Asserted | Low                                                                            |

| V <sub>DDEH</sub> | Low             | Asserted | High impedance (Hi-Z)                                                          |

| V <sub>DDEH</sub> | V <sub>DD</sub> | Asserted | Hi-Z                                                                           |

| V <sub>DDEH</sub> | $V_{DD}$        | Negated  | Functional                                                                     |

Table 8. Pin Status for Medium and Slow Pads During the Power Sequence

The values in Table 7 and Table 8 do not include the effect of the weak-pull devices on the output pins during power up.

Before exiting the internal POR state, the voltage on the pins go to a high-impedance state until POR negates. When the internal POR negates, the functional state of the signal during reset applies and the weak-pull devices

(up or down) are enabled as defined in the device reference manual. If V<sub>DD</sub> is too low to correctly propagate the logic signals, the weak-pull devices can pull the signals to V<sub>DDE</sub> and V<sub>DDEH</sub>.

To avoid this condition, minimize the ramp time of the V<sub>DD</sub> supply to a time period less than the time required to enable the external circuitry connected to the device outputs.

During initial power ramp-up, when Vstby is 0.6v or above. a typical current of 1-3mA and maximum of 4mA may be seen until  $V_{DD}$  is applied. This current will not reoccur until  $V_{stbv}$  is lowered below  $V_{stbv}$ min. specification.

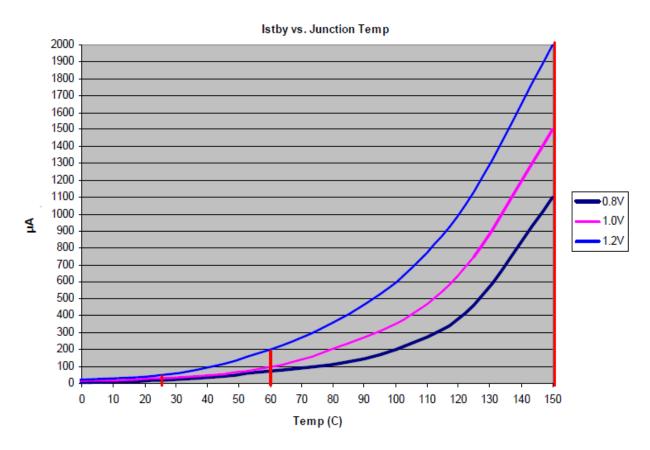

Figure 2 shows an approximate interpolation of the I<sub>STBY</sub> worst-case specification to estimate values at different voltages and temperatures. The vertical lines shown at 25 °C, 60 °C, and 150 °C in Figure 2 are the actual I<sub>DD STBY</sub> specifications (27d) listed in Table 9.

Figure 2. fISTBY Worst-case Specifications

MPC5554 Microcontroller Data Sheet, Rev. 4 12 Freescale Semiconductor

# 3.7.1 Input Value of Pins During POR Dependent on V<sub>DD33</sub>

When powering up the device,  $V_{DD33}$  must not lag the latest  $V_{DDSYN}$  or  $\overline{RESET}$  power pin ( $V_{DDEH6}$ ) by more than the  $V_{DD33}$  lag specification listed in Table 6, spec 8. This avoids accidentally selecting the bypass clock mode because the internal versions of PLLCFG[0:1] and  $\overline{RSTCFG}$  are not powered and therefore cannot read the default state when POR negates.  $V_{DD33}$  can lag  $V_{DDSYN}$  or the  $\overline{RESET}$  power pin ( $V_{DDEH6}$ ), but cannot lag both by more than the  $V_{DD33}$  lag specification. This  $V_{DD33}$  lag specification applies during power up only.  $V_{DD33}$  has no lead or lag requirements when powering down.

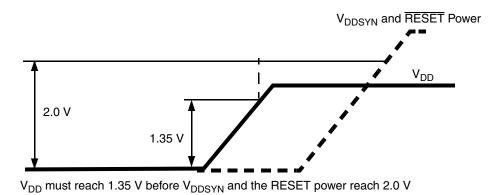

# 3.7.2 Power-Up Sequence (V<sub>RC33</sub> Grounded)

The 1.5 V  $V_{DD}$  power supply must rise to 1.35 V before the 3.3 V  $V_{DDSYN}$  power supply and the  $\overline{RESET}$  power supply rises above 2.0 V. This ensures that digital logic in the PLL for the 1.5 V power supply does not begin to operate below the specified operation range lower limit of 1.35 V. Because the internal 1.5 V POR is disabled, the internal 3.3 V POR or the  $\overline{RESET}$  power POR must hold the device in reset. Since they can negate as low as 2.0 V,  $V_{DD}$  must be within specification before the 3.3 V POR and the  $\overline{RESET}$  POR negate.

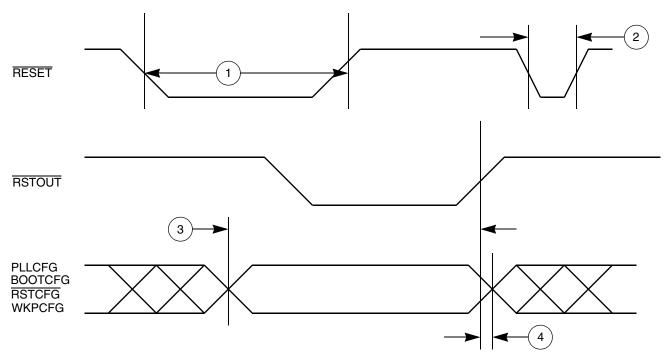

Figure 3. Power-Up Sequence (V<sub>RC33</sub> Grounded)

# 3.7.3 Power-Down Sequence (V<sub>RC33</sub> Grounded)

The only requirement for the power-down sequence with  $V_{RC33}$  grounded is if  $V_{DD}$  decreases to less than its operating range,  $V_{DDSYN}$  or the  $\overline{RESET}$  power must decrease to less than 2.0 V before the  $V_{DD}$  power increases to its operating range. This ensures that the digital 1.5 V logic, which is reset only by an ORed POR and can cause the 1.5 V supply to decrease less than its specification value, resets correctly. See Table 6, footnote 1.

# 3.8 DC Electrical Specifications

Table 9. DC Electrical Specifications ( $T_A = T_L \text{ to } T_H$ )

| Spec | Characteristic                                                                                                           | Symbol             | Min                                              | Max.                                             | Unit                 |

|------|--------------------------------------------------------------------------------------------------------------------------|--------------------|--------------------------------------------------|--------------------------------------------------|----------------------|

| 1    | Core supply voltage (average DC RMS voltage)                                                                             | V <sub>DD</sub>    | 1.35                                             | 1.65                                             | V                    |

| 2    | Input/output supply voltage (fast input/output) 1                                                                        | V <sub>DDE</sub>   | 1.62                                             | 3.6                                              | V                    |

| 3    | Input/output supply voltage (slow and medium input/output)                                                               | V <sub>DDEH</sub>  | 3.0                                              | 5.25                                             | V                    |

| 4    | 3.3 V input/output buffer voltage                                                                                        | V <sub>DD33</sub>  | 3.0                                              | 3.6                                              | V                    |

| 5    | Voltage regulator control input voltage                                                                                  | V <sub>RC33</sub>  | 3.0                                              | 3.6                                              | V                    |

| 6    | Analog supply voltage <sup>2</sup>                                                                                       | $V_{\mathrm{DDA}}$ | 4.5                                              | 5.25                                             | V                    |

| 8    | Flash programming voltage <sup>3</sup>                                                                                   | V <sub>PP</sub>    | 4.5                                              | 5.25                                             | V                    |

| 9    | Flash read voltage                                                                                                       | V <sub>FLASH</sub> | 3.0                                              | 3.6                                              | V                    |

| 10   | SRAM standby voltage <sup>4</sup>                                                                                        | V <sub>STBY</sub>  | 0.8                                              | 1.2                                              | V                    |

| 11   | Clock synthesizer operating voltage                                                                                      | V <sub>DDSYN</sub> | 3.0                                              | 3.6                                              | V                    |

| 12   | Fast I/O input high voltage                                                                                              | V <sub>IH_F</sub>  | 0.65 × V <sub>DDE</sub>                          | V <sub>DDE</sub> + 0.3                           | V                    |

| 13   | Fast I/O input low voltage                                                                                               | V <sub>IL_F</sub>  | V <sub>SS</sub> - 0.3                            | $0.35 \times V_{DDE}$                            | V                    |

| 14   | Medium and slow I/O input high voltage                                                                                   | V <sub>IH_S</sub>  | 0.65 × V <sub>DDEH</sub>                         | V <sub>DDEH</sub> + 0.3                          | V                    |

| 15   | Medium and slow I/O input low voltage                                                                                    | V <sub>IL_S</sub>  | V <sub>SS</sub> - 0.3                            | $0.35 \times V_{DDEH}$                           | V                    |

| 16   | Fast input hysteresis                                                                                                    | V <sub>HYS_F</sub> | 0.1 × V <sub>DDE</sub>                           |                                                  | V                    |

| 17   | Medium and slow I/O input hysteresis                                                                                     | V <sub>HYS_S</sub> | 0.1 ×                                            | V <sub>DDEH</sub>                                | V                    |

| 18   | Analog input voltage                                                                                                     | V <sub>INDC</sub>  | V <sub>SSA</sub> - 0.3                           | V <sub>DDA</sub> + 0.3                           | V                    |

| 19   | Fast output high voltage ( $I_{OH\_F} = -2.0 \text{ mA}$ )                                                               | V <sub>OH_F</sub>  | $0.8 \times V_{DDE}$                             | _                                                | V                    |

| 20   | Slow and medium output high voltage $I_{OH\_S} = -2.0 \text{ mA}$ $I_{OH\_S} = -1.0 \text{ mA}$                          | V <sub>OH_S</sub>  | $0.80 \times V_{DDEH}$<br>$0.85 \times V_{DDEH}$ | _                                                | V                    |

| 21   | Fast output low voltage (I <sub>OL_F</sub> = 2.0 mA)                                                                     | V <sub>OL_F</sub>  | _                                                | $0.2 \times V_{DDE}$                             | V                    |

| 22   | Slow and medium output low voltage $I_{OL\_S} = 2.0 \text{ mA}$ $I_{OL\_S} = 1.0 \text{ mA}$                             | V <sub>OL_S</sub>  | _                                                | $0.20 \times V_{DDEH}$<br>$0.15 \times V_{DDEH}$ | V                    |

| 23   | Load capacitance (fast I/O) <sup>5</sup> DSC (SIU_PCR[8:9]) = 0b00 = 0b01 = 0b10 = 0b11                                  | C <sub>L</sub>     | _<br>_<br>_<br>_                                 | 10<br>20<br>30<br>50                             | pF<br>pF<br>pF<br>pF |

| 24   | Input capacitance (digital pins)                                                                                         | C <sub>IN</sub>    | _                                                | 7                                                | pF                   |

| 25   | Input capacitance (analog pins)                                                                                          | C <sub>IN_A</sub>  | _                                                | 10                                               | pF                   |

| 26   | Input capacitance: (Shared digital and analog pins AN[12]_MA[0]_SDS, AN[13]_MA[1]_SDO, AN[14]_MA[2]_SDI, and AN[15]_FCK) | C <sub>IN_M</sub>  | _                                                | 12                                               | pF                   |

# Table 9. DC Electrical Specifications ( $T_A = T_L \text{ to } T_H$ ) (continued)

| Spec | Characteristic                                                                                                                                                                                                                                                                                | Symbol                                                                   | Min              | Max.                                                                    | Unit                 |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|------------------|-------------------------------------------------------------------------|----------------------|

| 27a  | Operating Current 1.5 V Supplies @ 132 MHz: <sup>6</sup>                                                                                                                                                                                                                                      |                                                                          |                  |                                                                         |                      |

|      | $V_{DD}$ (including $V_{DDF}$ max current) @ 1.65 V typical use $^{7,8}$ $V_{DD}$ (including $V_{DDF}$ max current) @ 1.4 V typical use $^{7,8}$ $V_{DD}$ (including $V_{DDF}$ max current) @ 1.65 V high use $^{8,9}$ $V_{DD}$ (including $V_{DDF}$ max current) @ 1.4 V high use $^{8,9}$   | I <sub>DD</sub><br>I <sub>DD</sub><br>I <sub>DD</sub>                    | _<br>_<br>_      | 700<br>600<br>875<br>740                                                | mA<br>mA<br>mA<br>mA |

| 27b  | Operating Current 1.5 V Supplies @ 114 MHz: <sup>6</sup>                                                                                                                                                                                                                                      |                                                                          |                  |                                                                         |                      |

|      | $V_{DD}$ (including $V_{DDF}$ max current) @ 1.65 V typical use $^{7,8}$ $V_{DD}$ (including $V_{DDF}$ max current) @ 1.4 V typical use $^{7,8}$ $V_{DD}$ (including $V_{DDF}$ max current) @ 1.65 V high use $^{8,9}$ $V_{DD}$ (including $V_{DDF}$ max current) @ 1.4 V high use $^{8,9}$   | I <sub>DD</sub><br>I <sub>DD</sub><br>I <sub>DD</sub>                    | _<br>_<br>_<br>_ | 609<br>522<br>760<br>643                                                | mA<br>mA<br>mA<br>mA |

| 27c  | Operating Current 1.5 V Supplies @ 82 MHz: <sup>6</sup>                                                                                                                                                                                                                                       |                                                                          |                  |                                                                         |                      |

|      | $V_{DD}$ (including $V_{DDF}$ max current) @ 1.65 V typical use $^{7,8}$ $V_{DD}$ (including $V_{DDF}$ max current) @ 1.40 V typical use $^{7,8}$ $V_{DD}$ (including $V_{DDF}$ max current) @ 1.65 V high use $^{8,9}$ $V_{DD}$ (including $V_{DDF}$ max current) @ 1.40 V high use $^{8,9}$ | I <sub>DD</sub><br>I <sub>DD</sub><br>I <sub>DD</sub><br>I <sub>DD</sub> | _<br>_<br>_<br>_ | 446<br>384<br>555<br>471                                                | mA<br>mA<br>mA<br>mA |

| 27d  | RAM standby current. <sup>10</sup> I <sub>DD_STBY</sub> @ 25° C V <sub>STBY</sub> @ 0.8 V V <sub>STBY</sub> @ 1.0 V V <sub>STBY</sub> @ 1.2 V                                                                                                                                                 | I <sub>DD_STBY</sub><br>I <sub>DD_STBY</sub><br>I <sub>DD_STBY</sub>     | _<br>_<br>_      | 20<br>30<br>50                                                          | μΑ<br>μΑ<br>μΑ       |

|      | I <sub>DD_STBY</sub> @ 60° C<br>V <sub>STBY</sub> @ 0.8 V<br>V <sub>STBY</sub> @ 1.0 V<br>V <sub>STBY</sub> @ 1.2 V                                                                                                                                                                           | I <sub>DD_STBY</sub><br>I <sub>DD_STBY</sub><br>I <sub>DD_STBY</sub>     | _<br>_<br>_      | 70<br>100<br>200                                                        | μΑ<br>μΑ<br>μΑ       |

|      | I <sub>DD_STBY</sub> @ 150° C (Tj)<br>V <sub>STBY</sub> @ 0.8 V<br>V <sub>STBY</sub> @ 1.0 V<br>V <sub>STBY</sub> @ 1.2 V                                                                                                                                                                     | I <sub>DD_STBY</sub><br>I <sub>DD_STBY</sub><br>I <sub>DD_STBY</sub>     | _<br>_<br>_      | 1200<br>1500<br>2000                                                    | μΑ<br>μΑ<br>μΑ       |

| 28   | Operating current 3.3 V supplies @ f <sub>MAX</sub> MHz $V_{DD33}^{-11}$                                                                                                                                                                                                                      | I <sub>DD_33</sub>                                                       | _                | 2 + (values<br>derived from<br>procedure of<br>footnote <sup>11</sup> ) | mA                   |

|      | V <sub>FLASH</sub>                                                                                                                                                                                                                                                                            | I <sub>VFLASH</sub>                                                      | _                | 10                                                                      | mA                   |

|      | V <sub>DDSYN</sub>                                                                                                                                                                                                                                                                            | I <sub>DDSYN</sub>                                                       | _                | 15                                                                      | mA                   |

| 29   | Operating current 5.0 V supplies (12 MHz ADCLK):  V <sub>DDA</sub> (V <sub>DDA0</sub> + V <sub>DDA1</sub> )  Analog reference supply current (V <sub>RH</sub> , V <sub>RL</sub> )  V <sub>PP</sub>                                                                                            | I <sub>DD_</sub> A<br>Iref<br>I <sub>PP</sub>                            | _<br>_<br>_      | 20.0<br>1.0<br>25.0                                                     | mA<br>mA<br>mA       |

Table 9. DC Electrical Specifications ( $T_A = T_L \text{ to } T_H$ ) (continued)

| Spec | Characteristic                                                                                                                                                                                                          | Symbol                                                                                                                                                   | Min                                  | Max.                                   | Unit                                   |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|----------------------------------------|----------------------------------------|

| 30   | Operating current V <sub>DDE</sub> supplies: 12  V <sub>DDEH1</sub> V <sub>DDE2</sub> V <sub>DDE3</sub> V <sub>DDEH4</sub> V <sub>DDE5</sub> V <sub>DDEH6</sub> V <sub>DDE7</sub> V <sub>DDEH8</sub> V <sub>DDEH9</sub> | I <sub>DD1</sub> I <sub>DD2</sub> I <sub>DD3</sub> I <sub>DD4</sub> I <sub>DD5</sub> I <sub>DD6</sub> I <sub>DD7</sub> I <sub>DD8</sub> I <sub>DD9</sub> | -<br>-<br>-<br>-<br>-<br>-<br>-<br>- | Refer to footnote 12                   | mA<br>mA<br>mA<br>mA<br>mA<br>mA<br>mA |

|      | Fast I/O weak pullup current <sup>13</sup> 1.62–1.98 V 2.25–2.75 V 3.00–3.60 V  Fast I/O weak pulldown current <sup>13</sup> 1.62–1.98 V 2.25–2.75 V 3.00–3.60 V                                                        | - I <sub>ACT_</sub> F                                                                                                                                    | 10<br>20<br>20<br>10<br>20<br>20     | 110<br>130<br>170<br>100<br>130<br>170 | μΑ<br>μΑ<br>μΑ<br>μΑ<br>μΑ             |

| 32   | Slow and medium I/O weak pullup/down current <sup>13</sup> 3.0–3.6 V 4.5–5.5 V                                                                                                                                          | I <sub>ACT_</sub> S                                                                                                                                      | 10<br>20                             | 150<br>170                             | μ <b>Α</b><br>μ <b>Α</b>               |

| 33   | I/O input leakage current <sup>14</sup>                                                                                                                                                                                 | I <sub>INACT_D</sub>                                                                                                                                     | -2.5                                 | 2.5                                    | μΑ                                     |

| 34   | DC injection current (per pin)                                                                                                                                                                                          | I <sub>IC</sub>                                                                                                                                          | -2.0                                 | 2.0                                    | mA                                     |

| 35   | Analog input current, channel off <sup>15</sup>                                                                                                                                                                         | I <sub>INACT_A</sub>                                                                                                                                     | -150                                 | 150                                    | nA                                     |

| 35a  | Analog input current, shared analog / digital pins (AN[12], AN[13], AN[14], AN[15])                                                                                                                                     | I <sub>INACT_AD</sub>                                                                                                                                    | -2.5                                 | 2.5                                    | μА                                     |

| 36   | V <sub>SS</sub> to V <sub>SSA</sub> differential voltage <sup>16</sup>                                                                                                                                                  | V <sub>SS</sub> – V <sub>SSA</sub>                                                                                                                       | -100                                 | 100                                    | mV                                     |

| 37   | Analog reference low voltage                                                                                                                                                                                            | V <sub>RL</sub>                                                                                                                                          | V <sub>SSA</sub> - 0.1               | V <sub>SSA</sub> + 0.1                 | V                                      |

| 38   | V <sub>RL</sub> differential voltage                                                                                                                                                                                    | V <sub>RL</sub> – V <sub>SSA</sub>                                                                                                                       | -100                                 | 100                                    | mV                                     |

| 39   | Analog reference high voltage                                                                                                                                                                                           | $V_{RH}$                                                                                                                                                 | V <sub>DDA</sub> – 0.1               | V <sub>DDA</sub> + 0.1                 | V                                      |

| 40   | V <sub>REF</sub> differential voltage                                                                                                                                                                                   | $V_{RH} - V_{RL}$                                                                                                                                        | 4.5                                  | 5.25                                   | V                                      |

| 41   | V <sub>SSSYN</sub> to V <sub>SS</sub> differential voltage                                                                                                                                                              | V <sub>SSSYN</sub> - V <sub>SS</sub>                                                                                                                     | -50                                  | 50                                     | mV                                     |

| 42   | V <sub>RCVSS</sub> to V <sub>SS</sub> differential voltage                                                                                                                                                              | V <sub>RCVSS</sub> – V <sub>SS</sub>                                                                                                                     | -50                                  | 50                                     | mV                                     |

| 43   | V <sub>DDF</sub> to V <sub>DD</sub> differential voltage                                                                                                                                                                | $V_{DDF} - V_{DD}$                                                                                                                                       | -100                                 | 100                                    | mV                                     |

| 43a  | V <sub>RC33</sub> to V <sub>DDSYN</sub> differential voltage                                                                                                                                                            | V <sub>RC33</sub> – V <sub>DDSYN</sub>                                                                                                                   | -0.1                                 | 0.1 <sup>17</sup>                      | V                                      |

| 44   | Analog input differential signal range (with common mode 2.5 V)                                                                                                                                                         | V <sub>IDIFF</sub>                                                                                                                                       | -2.5                                 | 2.5                                    | V                                      |

| 45   | Operating temperature range, ambient (packaged)                                                                                                                                                                         | $T_A = (T_L \text{ to } T_H)$                                                                                                                            | T <sub>L</sub>                       | T <sub>H</sub>                         | °C                                     |

| 46   | Slew rate on power-supply pins                                                                                                                                                                                          | _                                                                                                                                                        | _                                    | 50                                     | V/ms                                   |

<sup>1</sup> V<sub>DDE2</sub> and V<sub>DDE3</sub> are limited to 2.25–3.6 V only if SIU\_ECCR[EBTS] = 0; V<sub>DDE2</sub> and V<sub>DDE3</sub> have a range of 1.6–3.6 V if SIU\_ECCR[EBTS] = 1.

## MPC5554 Microcontroller Data Sheet, Rev. 4

- $^{2}$  |  $V_{DDA0} V_{DDA1}$  | must be < 0.1 V.

- <sup>3</sup> V<sub>PP</sub> can drop to 3.0 V during read operations.

- <sup>4</sup> If standby operation is not required, connect V<sub>STBY</sub> to ground.

- <sup>5</sup> Applies to CLKOUT, external bus pins, and Nexus pins.

- <sup>6</sup> Maximum average RMS DC current.

- Average current measured on automotive benchmark.

- <sup>8</sup> Peak currents can be higher on specialized code.

- High use current measured while running optimized SPE assembly code with all code and data 100% locked in cache (0% miss rate) with all channels of the eMIOS and eTPU running autonomously, plus the eDMA transferring data continuously from SRAM to SRAM. Higher currents are possible if an "idle" loop that crosses cache lines is run from cache. Write code that avoids this condition.

- <sup>10</sup> The current specification relates to average standby operation after SRAM has been loaded with data. For power up current see Section 3.7, "Power-Up/Down Sequencing", Figure 2.

- <sup>11</sup> Power requirements for the V<sub>DD33</sub> supply depend on the frequency of operation, load of all I/O pins, and the voltages on the I/O segments. Refer to Table 11 for values to calculate the power dissipation for a specific operation.

- <sup>12</sup> Power requirements for each I/O segment are dependent on the frequency of operation and load of the I/O pins on a particular I/O segment, and the voltage of the I/O segment. Refer to Table 10 for values to calculate power dissipation for specific operation. The total power consumption of an I/O segment is the sum of the individual power consumptions for each pin on the segment.

- $^{13}$  Absolute value of current, measured at  $V_{IL}$  and  $V_{IH}$ .

- <sup>14</sup> Weak pullup/down inactive. Measured at V<sub>DDE</sub> = 3.6 V and V<sub>DDEH</sub> = 5.25 V. Applies to pad types: pad\_fc, pad\_sh, and pad\_mh.

- <sup>15</sup> Maximum leakage occurs at maximum operating temperature. Leakage current decreases by approximately one-half for each 8 °C to 12 °C, in the ambient temperature range of 50 °C to 125 °C. Applies to pad types: pad\_a and pad\_ae.

- $^{16}\,\rm V_{SSA}$  refers to both  $\rm V_{SSA0}$  and  $\rm V_{SSA1}.$  |  $\rm V_{SSA0}$   $\rm V_{SSA1}$  | must be < 0.1 V.

- <sup>17</sup> Up to 0.6 V during power up and power down.

# 3.8.1 I/O Pad Current Specifications

The power consumption of an I/O segment depends on the usage of the pins on a particular segment. The power consumption is the sum of all output pin currents for a segment. The output pin current can be calculated from Table 10 based on the voltage, frequency, and load on the pin. Use linear scaling to calculate pin currents for voltage, frequency, and load parameters that fall outside the values given in Table 10.

Table 10. I/O Pad Average DC Current  $(T_A = T_L \text{ to } T_H)^1$

| VA E III |              |                       |                    |                        |             |                                                |              |

|----------|--------------|-----------------------|--------------------|------------------------|-------------|------------------------------------------------|--------------|

| Spec     | Pad Type     | Symbol                | Frequency<br>(MHz) | Load <sup>2</sup> (pF) | Voltage (V) | Drive Select /<br>Slew Rate<br>Control Setting | Current (mA) |

| 1        |              |                       | 25                 | 50                     | 5.25        | 11                                             | 8.0          |

| 2        | Slow         |                       | 10                 | 50                     | 5.25        | 01                                             | 3.2          |

| 3        | Slow         | I <sub>DRV_SH</sub>   | 2                  | 50                     | 5.25        | 00                                             | 0.7          |

| 4        |              |                       | 2                  | 200                    | 5.25        | 00                                             | 2.4          |

| 5        |              |                       | 50                 | 50                     | 5.25        | 11                                             | 17.3         |

| 6        | Medium       |                       | 20                 | 50                     | 5.25        | 01                                             | 6.5          |

| 7        | Medium       | 1 I <sub>DRV_MH</sub> | 3.33               | 50                     | 5.25        | 00                                             | 1.1          |

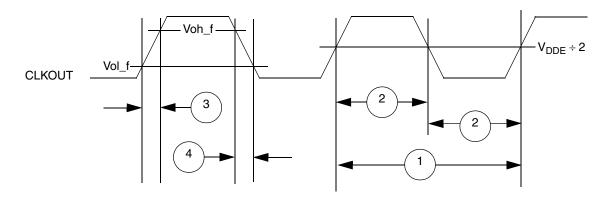

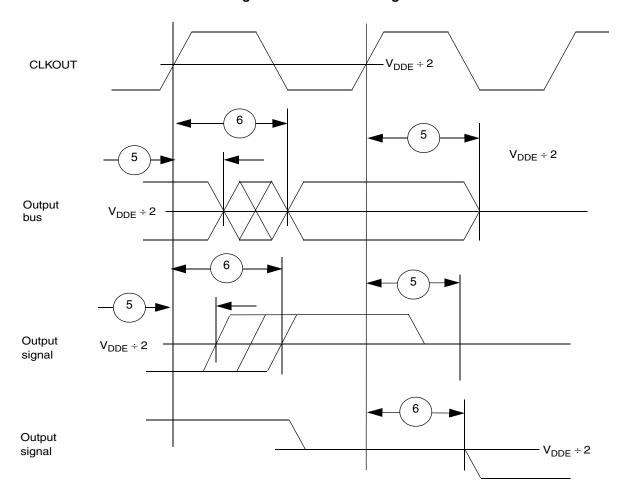

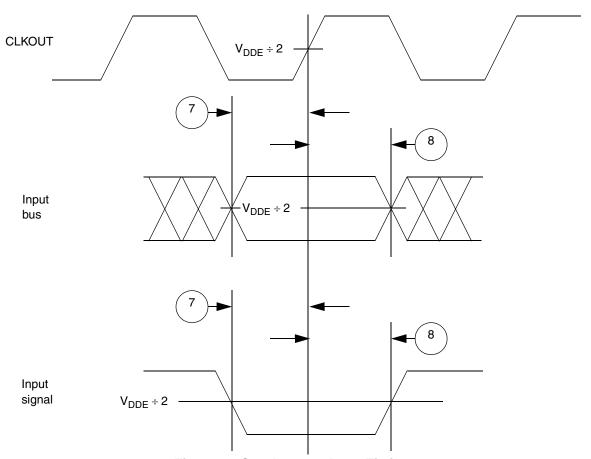

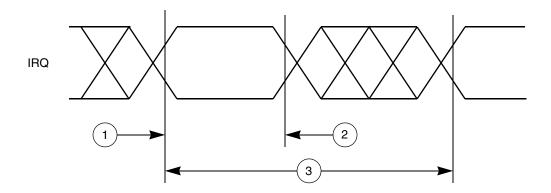

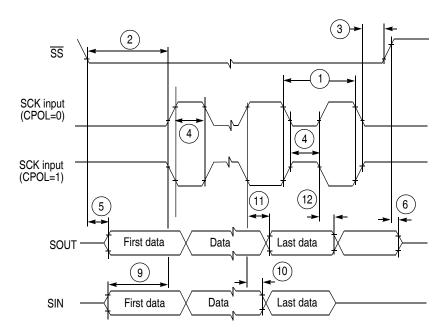

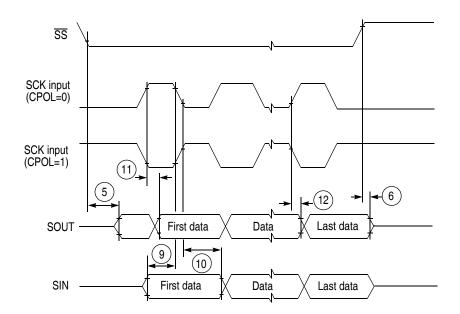

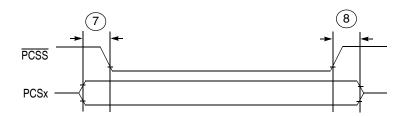

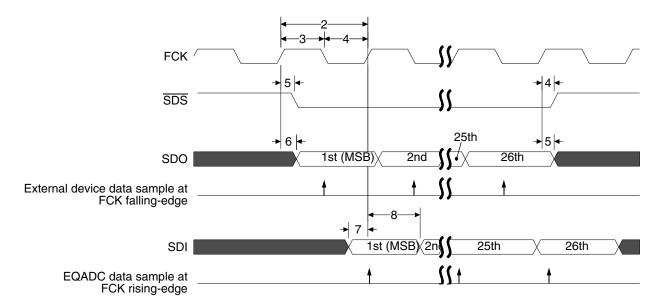

| 8        |              |                       | 3.33               | 200                    | 5.25        | 00                                             | 3.9          |