# P87C51MB2/P87C51MC2

80C51 8-bit microcontroller family with extended memory; 64 kB/96 kB OTP with 2 kB/3 kB RAM

Rev. 03 — 13 November 2003

**Product data**

### 1. General description

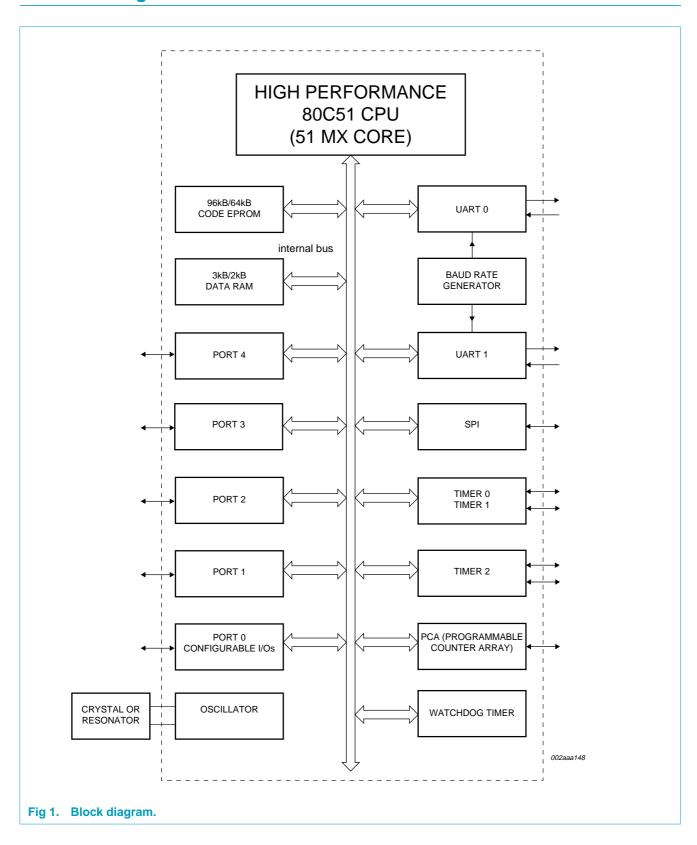

The P87C51Mx2 represents the first microcontroller based on Philips Semiconductors' new 51MX core. The P87C51MC2 features 96 kbytes of OTP program memory and 3 kbytes of data SRAM, while the P87C51MB2 has 64 kbytes of OTP and 2 kbytes of RAM. In addition, both devices are equipped with a Programmable Counter Array (PCA), a watchdog timer that can be configured to different time ranges through SFR bits, as well as two enhanced UARTs and Serial Peripheral Interface (SPI).

Philips Semiconductors' 51MX (Memory eXtension) core is an accelerated 80C51 architecture that executes instructions at twice the rate of standard 80C51 devices. The linear address range of the 51MX has been expanded to support up to 8 Mbytes of program memory and 8 Mbytes of data memory. It retains full program code compatibility to enable design engineers to re-use 80C51 development tools, eliminating the need to move to a new, unfamiliar architecture. The 51MX core also retains 80C51 bus compatibility to allow for the continued use of 80C51-interfaced peripherals and Application Specific Integrated Circuits (ASICs).

The P87C51Mx2 provides greater functionality, increased performance and overall lower system cost. By offering an embedded memory solution combined with the enhancements to manage the memory extension, the P87C51Mx2 eliminates the need for software work-around. The increased program memory enables design engineers to develop more complex programs in a high-level language like C, for example, without struggling to contain the program within the traditional 64 kbytes of program memory. These enhancements also greatly improve C Language efficiency for code size below 64 kbytes.

The 51MX core is described in more detail in the 51MX Architecture Reference.

#### 2. Features

#### 2.1 Key features

- Extended features of the 51MX Core:

- 23-bit program memory space and 23-bit data memory space

- Linear program and data address range expanded to support up to 8 Mbytes each

- Program counter expanded to 23 bits

- Stack pointer extended to 16 bits enabling stack space beyond the 80C51 limitation

- New 23-bit extended data pointer and two 24-bit universal pointers greatly improve C compiler code efficiency in using pointers to access variables in different spaces

- 100% binary compatibility with the classic 80C51 so that existing code is completely reusable

- Up to 24 MHz CPU clock with 6 clock cycles per machine cycle

- 96 kbytes (MC2) or 64 kbytes (MB2) of on-chip OTP

- 3 kbytes (MC2) or 2 kbytes (MB2) of on-chip RAM

- Programmable Counter Array (PCA)

- Two full-duplex enhanced UARTs and Serial Peripheral Interface (SPI) communication modules

#### 2.2 Key benefits

- Increases program/data address range to 8 Mbytes each

- Enhances performance and efficiency for C programs

- Fully 80C51-compatible microcontroller

- Provides seamless and compelling upgrade path from classic 80C51

- Preserves 80C51 code base, investment/knowledge, and peripherals & ASICs

- Supported by wide range of 80C51 development systems and programming tools vendors

- The P87C51Mx2 makes it possible to develop applications at lower cost and with a reduced time-to-market

#### 2.3 Complete features

- Fully static

- Up to 24 MHz CPU clock with 6 clock cycles per machine cycle

- 96 kbytes or 64 kbytes of on-chip OTP

- 3 kbytes or 2 kbytes of on-chip RAM

- 23-bit program memory space and 23-bit data memory space

- Four-level interrupt priority

- 34 I/O lines (5 ports)

- Three Timers: Timer0, Timer1 and Timer2

- Two full-duplex enhanced UARTs with baud rate generator

- Framing error detection

- Automatic address recognition

- Supports industry-standard Serial Peripheral Interface (SPI) with a baud rate up to 6 Mbits/s

- Power control modes

- Clock can be stopped and resumed

- Idle mode

- Power down mode with advanced clock control

- Second DPTR register

- Asynchronous port reset

- Programmable Counter Array (PCA) (compatible with 8xC51Rx+) with five Capture/Compare modules

9397 750 12302

- Low EMI (inhibit ALE)

- Watchdog timer with programmable prescaler for different time ranges (compatible with 8xC66x with added prescaler)

# 3. Differences between P87C51MX2/02 part and previous revisions of P87C51MX2

The P87C51MX2/02 offers several advantages over the previous generation of P87C51MX2 parts. Right now, SPI module is available, two more general purpose digital pins on P4 are present and additional power control features are implemented (advanced peripheral clock control). New memory interface mode and code size optimization options are available with the use of MXCON register.

No changes are necessary when porting and loading code written for existing P87C51MX2 to the new P87C51MX2/02.

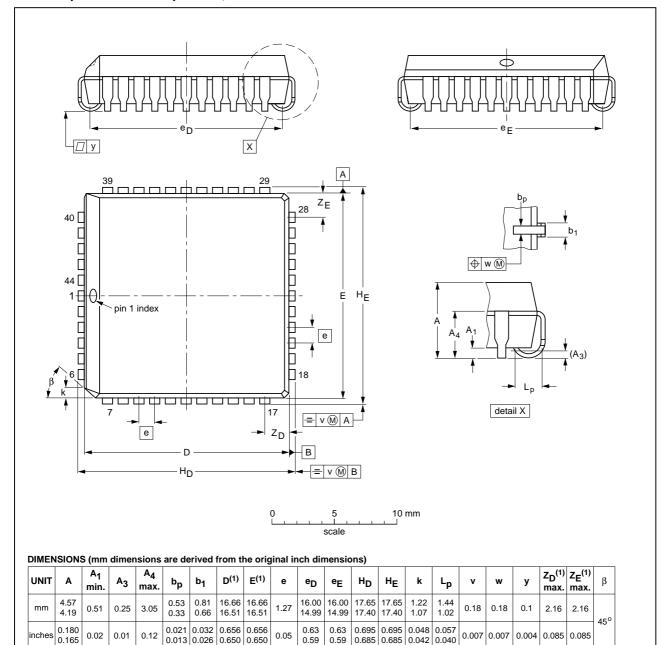

### 4. Ordering information

**Table 1: Ordering information**

| Type number    | Memory |        | Temp          | V <sub>DD</sub> voltage | Frequency                         | Frequency                         |        | Package                                     |          |  |  |

|----------------|--------|--------|---------------|-------------------------|-----------------------------------|-----------------------------------|--------|---------------------------------------------|----------|--|--|

|                | ОТР    | RAM    | Range<br>(°C) | range                   | V <sub>DD</sub> = 2.7<br>to 5.5 V | V <sub>DD</sub> = 4.5<br>to 5.5 V | Name   | Description                                 | Version  |  |  |

| P87C51MB2BA/02 | 64 kB  | 2048 B | 0 to +70      | 2.7 to 5.5 V            | 0 to<br>12 MHz                    | 0 to<br>24 MHz                    | PLCC44 | plastic leaded<br>chip carrier;<br>44 leads | SOT187-2 |  |  |

| P87C51MC2BA/02 | 96 kB  | 3072 B | 0 to +70      | 2.7 to 5.5 V            | 0 to<br>12 MHz                    | 0 to<br>24 MHz                    | PLCC44 | plastic leaded<br>chip carrier;<br>44 leads | SOT187-2 |  |  |

# 5. Block diagram

9397 750 12302

© Koninklijke Philips Electronics N.V. 2003. All rights reserved.

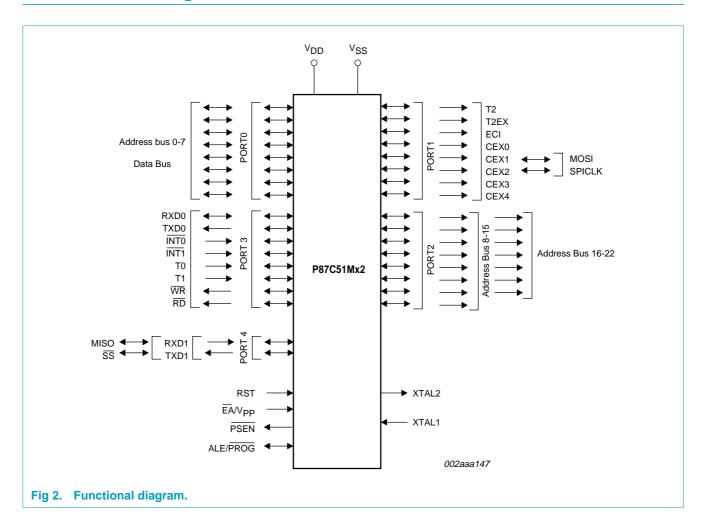

# 6. Functional diagram

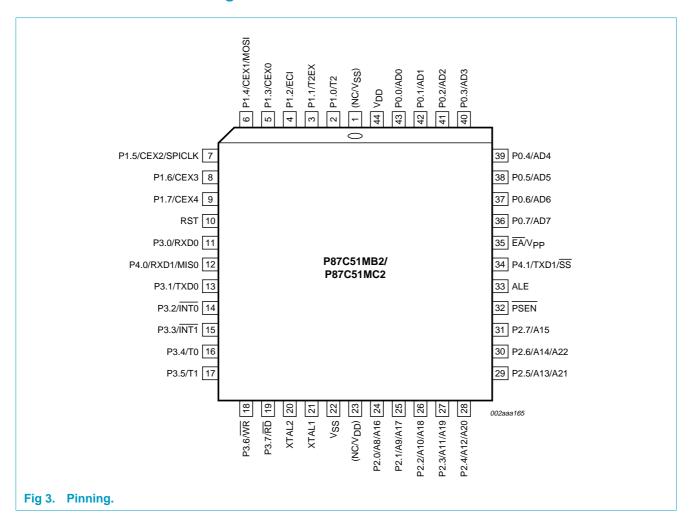

# 7. Pinning information

#### 7.1 Pinning

# 7.2 Pin description

Table 2: Pin description

| Symbol      | Pin     | Type | Description                                                                                                                                                                                                                                                                                                                                         |

|-------------|---------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P0.0 - P0.7 | 43 - 36 | I/O  | <b>Port 0:</b> Port 0 is an open drain, bidirectional I/O port. Port 0 pins that have 1s written to them float and can be used as high-impedance inputs. Port 0 is also the multiplexed low-order address and data bus during accesses to external program and data memory. In this application, it uses strong internal pull-ups when emitting 1s. |

| P1.0 - P1.7 | 2 - 9   | I/O  | <b>Port 1:</b> Port 1 is an 8-bit bidirectional I/O port with internal pull-ups on all pins. Port 1 pins that have 1s written to them are pulled HIGH by the internal pull-ups and can be used as inputs. As inputs, port 1 pins that are externally pulled LOW will source current because of the internal pull-ups.                               |

|             | 2       | I/O  | • P1.0, T2                                                                                                                                                                                                                                                                                                                                          |

|             |         |      | <ul> <li>Timer/Counter 2 external count input/Clock out</li> </ul>                                                                                                                                                                                                                                                                                  |

|             | 3       | 1    | • P1.1, T2EX                                                                                                                                                                                                                                                                                                                                        |

|             |         |      | <ul> <li>Timer/Counter 2 Reload/Capture/Direction Control</li> </ul>                                                                                                                                                                                                                                                                                |

|             | 4       | 1    | • P1.2, ECI                                                                                                                                                                                                                                                                                                                                         |

|             |         |      | <ul> <li>External Clock Input to the PCA</li> </ul>                                                                                                                                                                                                                                                                                                 |

|             | 5       | I/O  | • P1.3, CEX0                                                                                                                                                                                                                                                                                                                                        |

|             |         |      | <ul> <li>Capture/Compare External I/O for PCA module 0</li> </ul>                                                                                                                                                                                                                                                                                   |

|             | 6       | I/O  | • P1.4, CEX1                                                                                                                                                                                                                                                                                                                                        |

|             |         |      | <ul> <li>Capture/Compare External I/O for PCA module 1 (with pull-up on pin)</li> </ul>                                                                                                                                                                                                                                                             |

|             |         | I/O  | • MOSI                                                                                                                                                                                                                                                                                                                                              |

|             |         |      | <ul> <li>SPI Master Out/Slave In (Selected when SPEN (SPCTL.6) is '1', in which<br/>case the pull-up for this pin is disabled)</li> </ul>                                                                                                                                                                                                           |

|             | 7       | I/O  | ● P1.5, CEX2                                                                                                                                                                                                                                                                                                                                        |

|             |         |      | <ul> <li>Capture/Compare External I/O for PCA module 2 (with pull-up on pin)</li> </ul>                                                                                                                                                                                                                                                             |

|             |         | I/O  | • SPICLK                                                                                                                                                                                                                                                                                                                                            |

|             |         |      | <ul> <li>SPI Clock (Selected when SPEN (SPCTL.6) is '1', in which case the<br/>pull-up for this pin is disabled)</li> </ul>                                                                                                                                                                                                                         |

|             | 8       | I/O  | • P1.6, CEX3                                                                                                                                                                                                                                                                                                                                        |

|             |         |      | <ul> <li>Capture/Compare External I/O for PCA module 3</li> </ul>                                                                                                                                                                                                                                                                                   |

|             | 9       | I/O  | ● P1.7, CEX4                                                                                                                                                                                                                                                                                                                                        |

|             |         |      | <ul> <li>Capture/Compare External I/O for PCA module</li> </ul>                                                                                                                                                                                                                                                                                     |

Table 2:

Pin description...continued

| Table 2:    | Pin description. | continuea |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-------------|------------------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Symbol      | Pin              | Туре      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

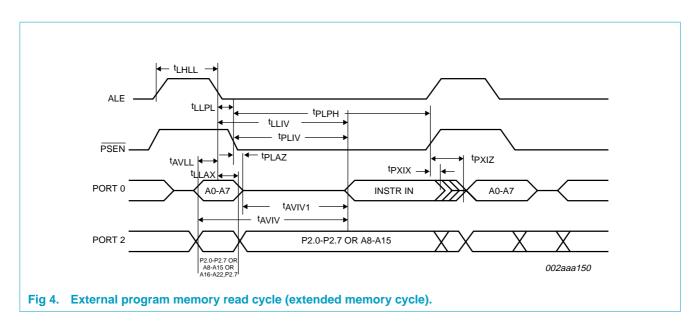

| P2.0 - P2.7 | 24 - 31          | I/O       | Port 2: Port 2 is a 8-bit bidirectional I/O port with internal pull-ups on all pins. Port 2 pins that have 1s written to them are pulled HIGH by the internal pull-ups and can be used as inputs. As inputs, port 2 pins that are externally being pulled LOW will source current because of the internal pull-ups. (See Section 10 "Static characteristics", I <sub>IL</sub> ). Port 2 emits the high-order address byte during fetches from external program memory and during accesses to external data memory that use 16-bit addresses (MOVX @ DPTR) or 23-bit addresses (MOVX @EPTR, EMOV). In this application, it uses strong internal pull-ups when emitting 1s. During accesses to external data memory that use 8-bit addresses (MOV @ Ri), port 2 emits the contents of the P2 Special Function Register.  Note that when 23-bit address is used, address bits A16-A22 will be outputted to P2.0-P2.6 when ALE is HIGH, and address bits A8-A14 are outputted to P2.0-P2.6 when ALE is LOW. Address bit A15 is outputted on P2.7 regardless |

|             |                  |           | of ALE.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| P3.0 - P3.7 | 11,13 -19        | I/O       | <b>Port 3:</b> Port 3 is an 8-bit bidirectional I/O port with internal pull-ups. Port 3 pins that have 1s written to them are pulled HIGH by the internal pull-ups and can be used as inputs. As inputs, port 3 pins that are externally pulled LOW will source current because of the internal pull-ups.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|             | 11               | 1         | • P3.0, RXD0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|             |                  |           | <ul><li>Serial input port 0</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|             | 13               | 0         | • P3.1, TXD0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|             |                  |           | <ul> <li>Serial output port 0</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|             | 14               | I         | • P3.2, INT0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|             |                  |           | <ul><li>External interrupt 0</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|             | 15               | I         | • P3.3, INT1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|             |                  |           | <ul><li>External interrupt 1</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|             | 16               | I         | • P3.4, T0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|             |                  |           | <ul> <li>Timer0 external input</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|             | 17               | I         | • P3.5, T1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|             |                  |           | - Timer1 external input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|             | 18               | 0         | • P3.6, WR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|             |                  |           | <ul> <li>External data memory write strobe</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|             | 19               | 0         | • P3.7, RD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|             |                  |           | External data memory read strobe                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| P4.0 - P4.1 | 12,34            | I/O       | <b>Port 4:</b> Port 4 is an 2-bit bidirectional I/O port with internal pull-ups on all pins. Port 4 pins that have 1s written to them are pulled HIGH by the internal pull-ups and can be used as inputs. As inputs, port 4 pins that are externally pulled LOW will source current because of the internal pull-ups. As inputs, port 4 pins that are externally pulled LOW will source current because of the internal pull-ups. (Note: When SPEN, i.e.,SPCTL.6, is '1', the pull-ups at these port pins are disabled.)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|             | 12               | I         | • P4.0, RXD1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|             |                  |           | <ul> <li>Serial input port 1 (with pull-up on pin)</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|             |                  | I/O       | • MISO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|             |                  |           | <ul> <li>SPI Master In/Slave Out (Selected when SFR bit SPEN (SPCTL.6) is '1',<br/>in which case the pull-up for this pin is disabled)</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

9397 750 12302

**Product data**

© Koninklijke Philips Electronics N.V. 2003. All rights reserved.

Table 2:

Pin description...continued

| Symbol                | Pin | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-----------------------|-----|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                       | 34  | 0    | • P4.1, TXD1                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                       |     |      | <ul> <li>Serial output port 1 (with pull-up on pin)</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                       |     | I/O  | • <del>SS</del>                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                       |     |      | <ul> <li>SPI Slave Select (Selected when SPEN (SPCTL.6) is '1', in which case<br/>the pull-up for this pin is disabled)</li> </ul>                                                                                                                                                                                                                                                                                                                                                      |

| RST                   | 10  | I    | <b>Reset:</b> A HIGH on this pin for two machine cycles, while the oscillator is running, resets the device. An internal diffused resistor to $V_{SS}$ permits a power-on reset using only an external capacitor to $V_{DD}$ .                                                                                                                                                                                                                                                          |

| ALE                   | 33  | 0    | <b>Address Latch Enable:</b> Output pulse for latching the LOW byte of the address during an access to external memory. In normal operation, ALE is emitted at a constant rate of $\frac{1}{6}$ the oscillator frequency, and can be used for external timing or clocking. Note that one ALE pulse is skipped during each access to external data memory. ALE can be disabled by setting SFR AUXR.0. With this bit is set, ALE will be active only during a MOVX/EMOV/MOVC instruction. |

| PSEN                  | 32  | 0    | <b>Program Store Enable:</b> The read strobe to external program memory. When executing code from the external program memory, $\overline{PSEN}$ is activated twice each machine cycle, except that two $\overline{PSEN}$ activations are skipped during each access to external data memory. $\overline{PSEN}$ is not activated during fetches from internal program memory.                                                                                                           |

| ĒĀ/V <sub>PP</sub>    | 35  | I    | External Access Enable/Programming Supply Voltage: $\overline{EA}$ must be externally held LOW to enable the device to fetch code from external program memory locations. If $\overline{EA}$ is held HIGH, the device executes from internal program memory. The value on the $\overline{EA}$ pin is latched when RST is released and any subsequent changes have no effect.                                                                                                            |

| XTAL1                 | 21  | I    | <b>Crystal 1:</b> Input to the inverting oscillator amplifier and input to the internal clock generator circuits.                                                                                                                                                                                                                                                                                                                                                                       |

| XTAL2                 | 20  | 0    | Crystal 2: Output from the inverting oscillator amplifier.                                                                                                                                                                                                                                                                                                                                                                                                                              |

| V <sub>SS</sub>       | 22  | I    | Ground: 0 V reference.                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| $V_{DD}$              | 44  | I    | <b>Power Supply:</b> This is the power supply voltage for normal operation as well as Idle and Power Down modes.                                                                                                                                                                                                                                                                                                                                                                        |

| (NC/V <sub>SS</sub> ) | 1   | I    | <b>No Connect/Ground:</b> This pin is internally connected to $V_{SS}$ on the P87C51MB2/MC2. If connected externally, this pin must only be connected to the same $V_{SS}$ as at pin 22. (Note: Connecting the second pair of $V_{SS}$ and $V_{DD}$ pins is not required. However, they may be connected in addition to the primary $V_{SS}$ and $V_{DD}$ pins to improve power distribution, reduce noise in output signals, and improve system-level EMI characteristics.)            |

| (NC/V <sub>DD</sub> ) | 23  | I    | <b>No Connect/Power Supply:</b> This pin is internally connected to $V_{DD}$ on the P87C51MB2/MC2. If connected externally, this pin must only be connected to the same $V_{DD}$ as at pin 44. (Note: Connecting the second pair of $V_{SS}$ and $V_{DD}$ pins is not required. However, they may be connected in addition to the primary $V_{SS}$ and $V_{DD}$ pins to improve power distribution, reduce noise in output signals, and improve system-level EMI characteristics.)      |

### 8. Functional description

#### 8.1 Memory arrangement

P87C51MB2 has 64 kbytes of OTP (MX universal map range: 80:0000-80:FFFF), while P87C51MC2 has 96 kbytes of OTP (MX universal map range: 80:0000-81:7FFF).

The P87C51MB2 and P87C51MC2 have 2 kbytes and 3 kbytes of on-chip RAM respectively:

Table 3: Memory arrangement

| Data me | emory                                                                                                                                          | Size (bytes) and MX universal memory map range |                           |  |  |  |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|---------------------------|--|--|--|

| Туре    | Description                                                                                                                                    | P87C51MB2                                      | P87C51MC2                 |  |  |  |

| DATA    | memory that can be addressed both directly and indirectly; can be used as stack                                                                | 128<br>(7F:0000-7F:007F)                       | 128<br>(7F:0000-7F:001F)  |  |  |  |

| IDATA   | superset of DATA; memory that can<br>be addressed indirectly (where direct<br>address for upper half is for SFR<br>only); can be used as stack | 256<br>(7F:0000-7F:00FF)                       | 256<br>(7F:0000-7F:00FF)  |  |  |  |

| EDATA   | superset of DATA/IDATA; memory that<br>can be addressed indirectly using<br>Universal Pointers (PR0,1); can be<br>used as stack                | 512<br>(7F:0000-7F:01FF)                       | 512<br>(7F:0000-7F:01FF)  |  |  |  |

| XDATA   | memory (on-chip 'External Data') that is accessed via the MOVX/EMOV instructions using DPTR/EPTR                                               | 1536<br>(00:0000-00:05FF)                      | 2560<br>(00:0000-00:09FF) |  |  |  |

For more detailed information, please refer to the *P87C51Mx2 User Manual* or the *51MX Architecture Specification*.

#### 8.2 Special Function Registers

Special Function Register (SFR) accesses are restricted in the following ways:

- User must **not** attempt to access any SFR locations not defined.

- Accesses to any defined SFR locations must be strictly for the functions for the SFRs.

- SFR bits labeled '-', '0', or '1' can **only** be written and read as follows:

- '-' MUST be written with '0', but can return any value when read (even if it was written with '0'). It is a reserved bit and may be used in future derivatives.

- '0' MUST be written with '0', and will return a '0' when read.

- '1' MUST be written with '1', and will return a '1' when read.

9397 750 12302

Table 4:

Name

**Special Function Registers**

Module 1 Capture LOW

Module 2 Capture LOW

Module 3 Capture LOW

Module 4 Capture LOW

Module 0 Mode

Module 1 Mode

Module 2 Mode

Module 3 Mode

Module 4 Mode

**PCA Counter Control**

PCA Counter HIGH

PCA Counter LOW

PCA Counter Mode

Description

CCAP1L<sup>[2]</sup>

CCAP2L[2]

CCAP3L[2]

CCAP4L[2]

CCAPM0[2]

CCAPM1[2]

CCAPM2[2]

CCAPM3<sup>[2]</sup>

CCAPM4[2]

CCON[1][2]

CMOD<sup>[2]</sup>

CH[2]

CL[2]

© Koninklijke Philips Electronics N.V. 2003. All rights reserved

| ACC <sup>[1]</sup>      | Accumulator                      | E0H                |    |    |    |      |     |    |   |

|-------------------------|----------------------------------|--------------------|----|----|----|------|-----|----|---|

| AUXR <sup>[2]</sup>     | Auxiliary Function Register      | 8EH                | -  | -  | -  | -    | -   | -  | Е |

| AUXR1 <sup>[2]</sup>    | Auxiliary Function Register 1    | A2H                | -  | -  | -  | LPEP | GF2 | 0  | - |

|                         | Bit                              | address            | F7 | F6 | F5 | F4   | F3  | F2 | F |

| B[1]                    | B Register                       | F0H                |    |    |    |      |     |    |   |

| BRGCON[2]               | Baud Rate Generator Control      | 85H <sup>[3]</sup> | -  | -  | -  | -    | -   | -  | S |

| BRGR0 <sup>[2][5]</sup> | Baud Rate Generator Rate LOW     | 86H <sup>[3]</sup> |    |    |    |      |     |    |   |

| BRGR1 <sup>[2][5]</sup> | Baud Rate Generator Rate<br>HIGH | 87H <sup>[3]</sup> |    |    |    |      |     |    |   |

| CCAP0H <sup>[2]</sup>   | Module 0 Capture HIGH            | FAH                |    |    |    |      |     |    |   |

| CCAP1H <sup>[2]</sup>   | Module 1 Capture HIGH            | FBH                |    |    |    |      |     |    |   |

| CCAP2H <sup>[2]</sup>   | Module 2 Capture HIGH            | FCH                |    |    |    |      |     |    |   |

| CCAP3H <sup>[2]</sup>   | Module 3 Capture HIGH            | FDH                |    |    |    |      |     |    |   |

| CCAP4H <sup>[2]</sup>   | Module 4 Capture HIGH            | FEH                |    |    |    |      |     |    |   |

| CCAP0L <sup>[2]</sup>   | Module 0 Capture LOW             | EAH                |    |    |    |      |     |    |   |

**MSB**

Bit functions and addresses

**E6**

ECOM\_0

ECOM\_1

ECOM\_2

ECOM\_3

ECOM\_4

DE

CR

WDTE

**E**5

**E**4

CAPP\_0 CAPN\_0 MAT\_0

CAPN\_1

CAPN\_2

CAPN\_3

CAPN\_4

DC

CCF4

MAT\_1

MAT\_2

MAT\_3

MAT\_4

CCF3

DB

CAPP\_1

CAPP\_2

CAPP\_3

CAPP\_4

DD

**E**3

**E2**

TOG\_0

TOG\_1

TOG\_2

TOG\_3

TOG\_4

DA

CCF2

CPS1

P

P'

P

P

D

С

С

Ē

**SFR**

Addr.

EBH

**ECH**

EDH

EEH

DAH

DBH

DCH

DDH

DEH

D8H

F9H

E9H

D9H

Bit address DF

CF

CIDL

Bit address E7

P0<sup>[1]</sup>

P1<sup>[1]</sup>

Port 0

Port 1

| 9397                  | Table 4:             | Special Function Registerscom  | ntinued            |            |             |         |       |       |       |     |

|-----------------------|----------------------|--------------------------------|--------------------|------------|-------------|---------|-------|-------|-------|-----|

| 9397 750 12302        | Name                 | Description                    | SFR                | Bit functi | ons and add | dresses |       |       |       |     |

| 2302                  |                      |                                | Addr.              | MSB        |             |         |       |       |       |     |

|                       | DPTR                 | Data Pointer (2 bytes)         | '                  |            |             |         |       |       |       |     |

|                       | DPH                  | Data Pointer HIGH              | 83H                |            |             |         |       |       |       |     |

|                       | DPL                  | Data Pointer LOW               | 82H                |            |             |         |       |       |       |     |

|                       | EPTR                 | Extended Data Pointer (3 bytes | s)                 |            |             |         |       |       |       |     |

|                       | EPL <sup>[2]</sup>   | Extended Data Pointer LOW      | FCH <sup>[3]</sup> |            |             |         |       |       |       |     |

|                       | EPM <sup>[2]</sup>   | Extended Data Pointer Middle   | FDH <sup>[3]</sup> |            |             |         |       |       |       |     |

|                       | EPH <sup>[2]</sup>   | Extended Data Pointer HIGH     | FEH <sup>[3]</sup> |            |             |         |       |       |       |     |

|                       |                      | I                              | Bit address        | AF         | AE          | AD      | AC    | AB    | AA    | A   |

|                       | IEN0[1]              | Interrupt Enable 0             | A8H                | ĒΑ         | EC          | ET2     | ES0/  | ET1   | EX1   | E.  |

|                       |                      |                                |                    |            |             |         | ES0R  |       |       |     |

|                       |                      | I                              | Bit address        | EF         | EE          | ED      | EC    | EB    | EA    | E   |

| 3                     | IEN1 [1]             | Interrupt Enable 1             | E8H                | -          | -           | -       | -     | ESPI  | ES1T  | E   |

| 2                     |                      |                                | Direct Library     | DE         | DE.         |         |       |       |       |     |

| 2                     | . <b></b> [4]        |                                | Bit address        | BF         | BE          | BD      | BC    | BB    | BA    | B   |

|                       | IP0 <sup>[1]</sup>   | Interrupt Priority             | B8H                | -          | PPC         | PT2     | PS0/  | PT1   | PX1   | P.  |

| 5                     | IDOLL                |                                | D=1.1              |            | DDOLL       | DTOLL   | PS0R  | DT    | DV411 |     |

|                       | IP0H                 | Interrupt<br>Priority 0 HIGH   | В7Н                | -          | PPCH        | PT2H    | PS0H/ | PT1H  | PX1H  | P.  |

|                       |                      | •                              | Direct Disease     |            |             | ED      | PS0RH |       |       |     |

|                       | [4]                  |                                | Bit address        | FF         | FE          | FD      | FC    | FB    | FA    | F   |

|                       | IP1 <sup>[1]</sup>   | Interrupt Priority 1           | F8H                | -          | -           | -       | -     | PSPI  | PS1T  | P   |

| 0                     | IP1H                 | Interrupt Priority 1 HIGH      | F7H                | -          |             | _       | -     | PSPIH | PS1TH | P   |

| Koninklij             |                      | sp                             |                    |            |             |         |       | ···   |       | - ' |

| © Koninklijke Philips | MXCON <sup>[2]</sup> | MX Control Register            | FFH[3]             | -          | -           | -       | ECRM  | EAM1  | EAM0  | E   |

| 8                     |                      |                                |                    |            |             |         |       |       |       |     |

86

96

CEX3

AD6

85

95

AD5

CEX2/

SPICLK

84

94

AD4

CEX1/

MOSI

83

93

AD3

CEX0

82

AD2

92

ECI

8

Α

9

Ŧ

Bit address 87

AD7

CEX4

97

80H

90H

9397 750 12302

Table 4:

Name

**Special Function Registers**...continued

Serial Port 0 Data Buffer

Serial Port 0 Status

Serial Port 1 Control

Serial Port 1 Data buffer

Serial Port 1 Address Register

Serial Port 1 Address Enable

Serial Port 0 Address Register

Serial Port 0 Address Enable

Register

Register

Description

S0BUF

S0ADDR

**SOADEN**

SOSTAT[2]

S1CON[1][2]

S1BUF[2]

S1ADDR<sup>[2]</sup>

S1ADEN[2]

© Koninklijke Philips Electronics N.V. 2003. All rights res

P2<sup>[1]</sup> Port 2 A0H AD15 AD14/ ADA13/ AD12/ AD11/ AD10/ Α AD22 AD21 AD20 AD19 AD18 Α **B2** Bit address **B7 B6 B5 B4 B3** В P3<sup>[1]</sup>  $\overline{\mathsf{RD}}$  $\overline{\mathsf{WR}}$ ĪNT0 Port 3 B0H T1 T0 INT1  $\mathsf{T}$ C6[3] C3[3] **Bit address C7**[3] C5[3] C4[3] C<sub>2</sub>[3] C P4[1][2] C0H[3] Port 4  $\mathsf{T}$ S PCON<sup>[2]</sup> Power Control Register 87H SMOD1 SMOD0 POF GF1 GF0 Ρ S PCONA<sup>[2]</sup> Power Control Register A B5H **PCAPD SPIPD BRGPD** T2PD D2 Bit address D7 **D6 D5 D4 D3** D PSW<sup>[1]</sup> CY F Program Status Word D0H AC F0 RS1 RS0 OV RCAP2H<sup>[2]</sup> CBH Timer2 Capture HIGH RCAP2L[2] Timer2 Capture LOW CAH 9C 9B 9A Bit address 9F **9E** 9D 99 S0CON[1] Serial Port 0 Control 98H SM0\_0/ SM1\_0 SM2\_0 REN\_0 TB8\_0 RB8\_0 T

FE\_0

DBMOD\_0

**87**[3]

FE\_1

SM0\_1/

INTLO\_0

**86**[3]

SM1\_1

99H

A9H

В9Н

8CH[3]

Bit address

80H[3]

81H<sup>[3]</sup>

82H[3]

83H[3]

**MSB**

**A7**

Bit functions and addresses

**A6**

**A5**

**A4**

CIDIS\_0 DBISEL\_ FE\_0

84[3]

REN\_1

**83**[3]

TB8\_1

0

**85**[3]

SM2\_1

**A3**

**A2**

BR\_0

**82**[3]

RB8\_1

0

8

T

Α

SFR

Addr.

**Bit address**

Table 4: **Special Function Registers**...continued

| 9397           | Table 4: Sp           | pecial Function Registerscont                                        | inued              |              |            |         |         |        |        |    |

|----------------|-----------------------|----------------------------------------------------------------------|--------------------|--------------|------------|---------|---------|--------|--------|----|

| 9397 750 12302 | Name                  | Description                                                          | SFR                | Bit function | s and addr | esses   |         |        |        |    |

| 2302           |                       |                                                                      | Addr.              | MSB          |            |         |         |        |        |    |

|                | S1STAT <sup>[2]</sup> | Serial Port 1 Status                                                 | 84H <sup>[3]</sup> | DBMOD_1      | INTLO_1    | CIDIS_1 | DBISEL1 | FE_1   | BR_1   | 0  |

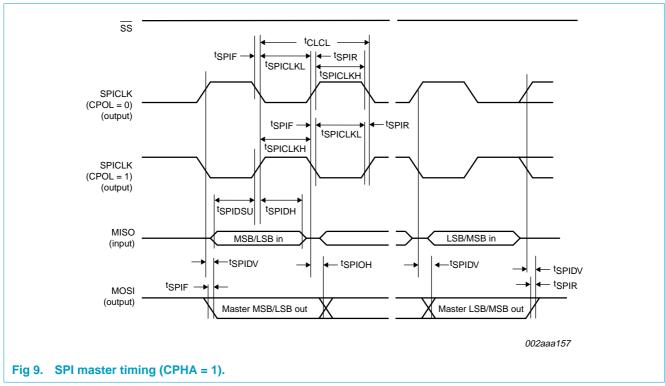

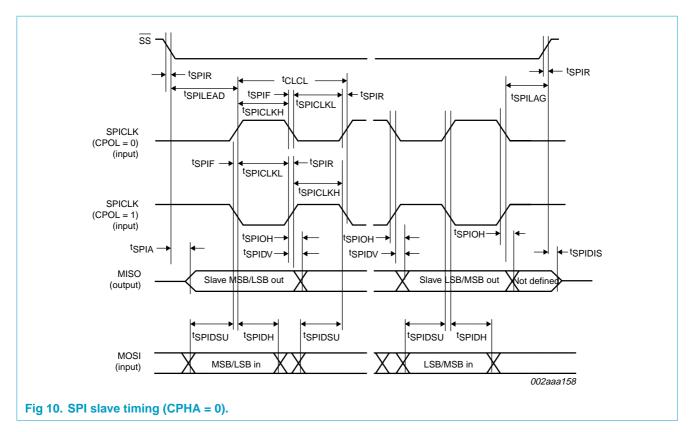

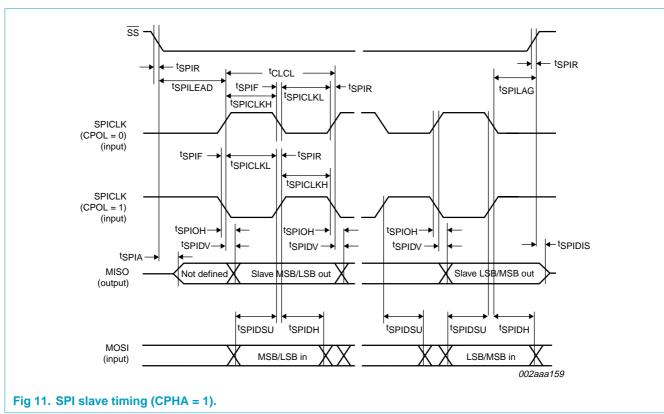

|                | SPCTL <sup>[2]</sup>  | SPI Control Register                                                 | E2H                | SSIG         | SPEN       | DORD    | MSTR    | CPOL   | CPHA   | P  |

|                | SPCFG <sup>[2]</sup>  | SPI Configuration Register                                           | E1H                | SPIF         | SPWCOL     | -       | -       | -      | -      | -  |

|                | SPDAT <sup>[2]</sup>  | SPI Data                                                             | E3H                |              |            |         |         |        |        |    |

|                | SP                    | Stack Pointer (or Stack Pointer<br>LOW Byte When EDATA<br>Supported) | 81H                |              |            |         |         |        |        |    |

|                | SPE <sup>[2]</sup>    | Stack Pointer HIGH                                                   | FBH <sup>[3]</sup> |              |            |         |         |        |        |    |

|                |                       | В                                                                    | it address         | 8F           | 8E         | 8D      | 8C      | 8B     | 8A     | 89 |

|                | TCON <sup>[1]</sup>   | Timer Control Register                                               | 88H                | TF1          | TR1        | TF0     | TR0     | IE1    | IT1    | ΙE |

| ,              |                       |                                                                      |                    | CF           | CE         | CD      | CC      | СВ     | CA     | C  |

|                | T2CON[1][2]           | Timer2 Control Register                                              | C8H                | TF2          | EXF2       | RCLK    | TCLK    | EXEN2  | TR2    | C  |

|                | T2MOD <sup>[2]</sup>  | Timer2 Mode Control                                                  | C9H                | -            | -          | ENT2    | TF2DE   | T2GATE | T2PWME | T2 |

|                | TH0                   | Timer 0 HIGH                                                         | 8CH                |              |            |         |         |        |        |    |

|                | TH1                   | Timer 1 HIGH                                                         | 8DH                |              |            |         |         |        |        |    |

|                | TH2                   | Timer 2 HIGH                                                         | CDH                |              |            |         |         |        |        |    |

| ,              | TL0                   | Timer 0 LOW                                                          | 8AH                |              |            |         |         |        |        |    |

|                | TL1                   | Timer 1 LOW                                                          | 8BH                |              |            |         |         |        |        |    |

|                | TL2                   | Timer 2 LOW                                                          | CCH                |              |            |         |         |        |        |    |

|                | TMOD                  | Timer 0 and 1 Mode                                                   | 89H                | GATE         | C/T        | M1      | MO      | GATE   | C/T    | M  |

|                | WDTRST[2]             | Watchdog Timer Reset                                                 | A6H                |              |            |         |         |        |        |    |

| © Konin        | WDCON <sup>[2]</sup>  | Watchdog Timer Control                                               | 8FH <sup>[3]</sup> | -            | -          | -       | -       | -      | WDPRE2 | W  |

<sup>[1]</sup> SFRs are bit addressable.

<sup>[2]</sup> SFRs are modified from or added to the 80C51 SFRs.

<sup>[3]</sup> Extended SFRs accessed by preceding the instruction with MX escape (opcode A5h).

<sup>[4]</sup> Power on reset is 10H. Other reset is 00H.

BRGR1 and BRGR0 must only be written if BRGEN in BRGCON SFR is '0'. If any of them is written if BRGEN = 1, result is unpredictable.

The unimplemented bits (labeled '-') in the SFRs are X's (unknown) at all times. '1's should not be written to these bits, as they may be used for derivatives. The reset values shown for these bits are '0's although they are unknown when read.

#### 8.3 Security bits

The P87C51Mx2 has security bits to protect users' firmware codes. With none of the security bits programmed, the code in the program memory can be verified. When only security bit 1 (see Table 5) is programmed, MOVC instructions executed from external program memory are disabled from fetching code bytes from the internal memory.  $\overline{EA}$  is latched on Reset and all further programming of EPROM is disabled. When security bits 1 and 2 are programmed, in addition to the above, verify mode is disabled. When all three security bits are programmed, all of the conditions above apply and all external program memory execution is disabled.

Table 5: EPROM security bits

| Securit | y Bits <sup>[1][2</sup> | 2]    |       |                                                                                                                                                                                                                        |

|---------|-------------------------|-------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | Bit 1                   | Bit 2 | Bit 3 | Protection description                                                                                                                                                                                                 |

| 1       | U                       | U     | U     | No program security features enabled. EEPROM is programmable and verifiable.                                                                                                                                           |

| 2       | Р                       | U     | U     | MOVC instructions executed from external program memory are disabled from fetching code bytes from internal memory, $\overline{EA}$ is sampled and latched on Reset, and further programming of the EPROM is disabled. |

| 3       | Р                       | Р     | U     | Same as 2, also verification is disabled.                                                                                                                                                                              |

| 4       | Р                       | Р     | Р     | Same as 3, external execution is disabled.                                                                                                                                                                             |

<sup>[1]</sup> P - programmed. U - unprogrammed.

# 9. Limiting values

**Table 6: Limiting values**

In accordance with the Absolute Maximum Rating System (IEC 60134).

| Symbol                          | Parameter                                                                                  | Conditions                                                   | Min  | Max                     | Unit    |

|---------------------------------|--------------------------------------------------------------------------------------------|--------------------------------------------------------------|------|-------------------------|---------|

| T <sub>amb</sub>                | operating temperature                                                                      | under bias                                                   | 0    | +70                     | °C      |

| T <sub>stg</sub>                | storage temperature range                                                                  |                                                              | -65  | +150                    | °C      |

| VI                              | input voltage on $\overline{\text{EA}}/\text{V}_{\text{PP}}$ pin to $\text{V}_{\text{SS}}$ |                                                              | 0    | +13                     | V       |

|                                 | input voltage on any other pin to $V_{\mbox{\footnotesize SS}}$                            | 3                                                            | -0.5 | V <sub>DD</sub> + 0.5 V | °C<br>V |

| I <sub>I</sub> , I <sub>O</sub> | maximum I <sub>OL</sub> per I/O pin                                                        |                                                              | -    | 20                      | mA      |

| P                               | power dissipation                                                                          | based on package heat transfer, not device power consumption | -    | 1.5                     | W       |

<sup>[1]</sup> The following applies to the Limiting values:

- a) Stresses above those listed under Limiting values may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any conditions other than those described in Section 10 "Static characteristics" and Section 11 "Dynamic characteristics" of this specification is not implied.

- b) This product includes circuitry specifically designed for the protection of its internal devices from the damaging effects of excessive static charge. Nonetheless, it is suggested that conventional precautions be taken to avoid applying greater than the rated maxima.

- Parameters are valid over operating temperature range unless otherwise specified. All voltages are with respect to V<sub>SS</sub> unless otherwise noted.

<sup>[2]</sup> Any other combination of security bits is not defined.

#### 10. Static characteristics

**Table 7: Static characteristics**

$T_{amb} = 0$  °C to +70 °C for commercial, unless otherwise specified;  $V_{DD} = 2.7$  V to 5.5 V unless otherwise specified.

| Symbol           | Parameter                                                               | Conditions                                           |     | Min                     | Typ <sup>[1]</sup> | Max                                    | Unit |

|------------------|-------------------------------------------------------------------------|------------------------------------------------------|-----|-------------------------|--------------------|----------------------------------------|------|

| V <sub>IL</sub>  | Input low voltage                                                       |                                                      |     | -0.5                    |                    | 0.2V <sub>DD</sub> -0.1                | V    |

| V <sub>IH</sub>  | Input high voltage (ports 0, 1, 2, 3, 4, $\overline{EA}$ )              |                                                      |     | 0.2V <sub>DD</sub> +0.9 |                    | V <sub>DD</sub> +0.5                   | V    |

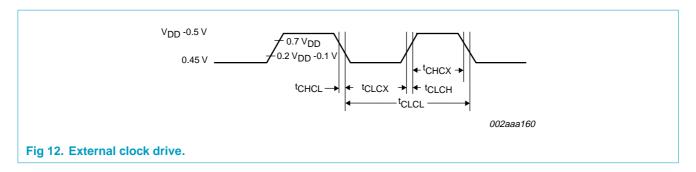

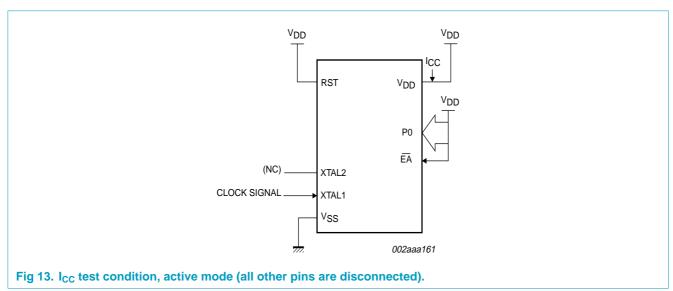

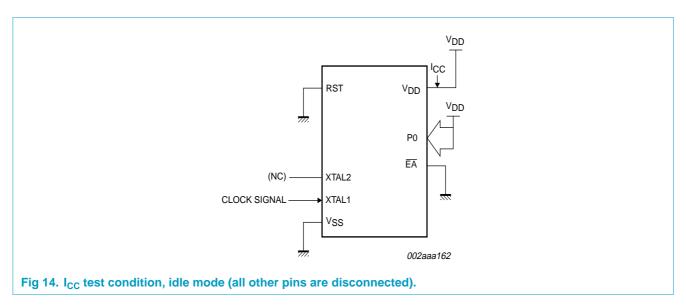

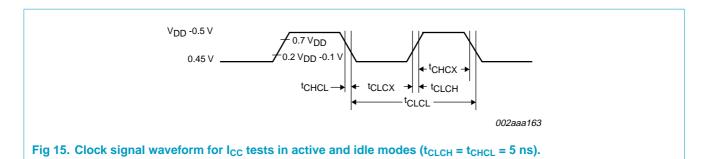

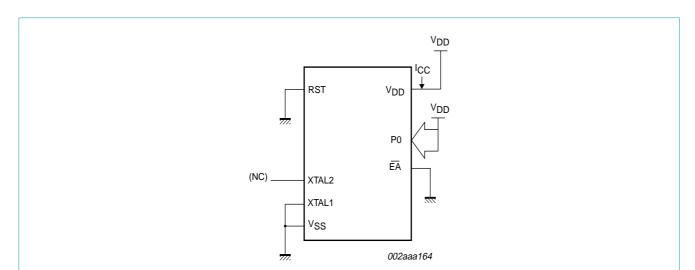

| V <sub>IH1</sub> | Input high voltage, XTAL1, RST                                          |                                                      |     | 0.7V <sub>DD</sub>      |                    | V <sub>DD</sub> +0.5                   | V    |