# PCA9539; PCA9539R

16-bit I<sup>2</sup>C-bus and SMBus low power I/O port with interrupt and reset

Rev. 9 — 8 November 2017

Product data sheet

## 1. General description

The PCA9539; PCA9539R is a 24-pin CMOS device that provides 16 bits of General Purpose parallel Input/Output (GPIO) expansion with interrupt and reset for I<sup>2</sup>C-bus/SMBus applications and was developed to enhance the NXP Semiconductors family of I<sup>2</sup>C-bus I/O expanders. I/O expanders provide a simple solution when additional I/O is needed for ACPI power switches, sensors, push buttons, LEDs, fans, etc.

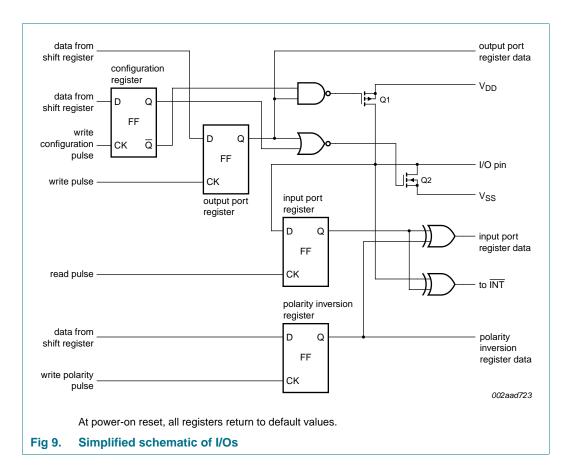

The PCA9539; PCA9539R consists of two 8-bit configuration (input or output selection), input, output and polarity inversion (active HIGH or active LOW operation) registers. The system master can enable the I/Os as either inputs or outputs by writing to the I/O configuration bits. The data for each input or output is kept in the corresponding Input or Output register. The polarity of the read register can be inverted with the Polarity inversion register. All registers can be read by the system master.

The PCA9539; PCA9539R is identical to the PCA9555 except for the removal of the internal I/O pull-up resistor which greatly reduces power consumption when the I/Os are held LOW, replacement of A2 with RESET and a different address range.

The PCA9539; PCA9539R open-drain interrupt output is activated when any input state differs from its corresponding input port register state and is used to indicate to the system master that an input state has changed.

The power-on reset sets the registers to their default values and initializes the device state machine. In the PCA9539, the RESET pin causes the same reset/default I/O input configuration to occur without de-powering the device, holding the registers and I $^2$ C-bus state machine in their default state until the RESET input is once again HIGH. This input requires a pull-up to  $V_{DD}$ . In the PCA9539R however, only the device state machine is initialized by the RESET pin and the internal general-purpose registers remain unchanged. Using the PCA9539R RESET pin will only reset the I $^2$ C-bus interface should it be stuck LOW to regain access to the I $^2$ C-bus. This allows the I/O pins to retain their last configured state so that they can keep any lines in their previously defined state and not cause system errors while the I $^2$ C-bus is being restored.

Two hardware pins (A0, A1) vary the fixed I<sup>2</sup>C-bus address and allow up to four devices to share the same I<sup>2</sup>C-bus/SMBus.

#### 2. Features and benefits

- 16-bit I<sup>2</sup>C-bus GPIO with interrupt and reset

- Operating power supply voltage range of 2.3 V to 5.5 V (3.0 V to 5.5 V for PCA9539PW/Q900 and PCA9539RPW/Q900)

- 5 V tolerant I/Os

- Polarity inversion register

- Active LOW interrupt output

- Active LOW reset input

- Low standby current

- Noise filter on SCL/SDA inputs

- No glitch on power-up

- Internal power-on reset

- 16 I/O pins which default to 16 inputs

- 0 Hz to 400 kHz clock frequency

- ESD protection exceeds 2000 V HBM per JESD22-A114 and 1000 V CDM per JESD22-C101

- Latch-up testing is done to JEDEC Standard JESD78 which exceeds 100 mA

- Offered in three different packages: SO24, TSSOP24, and HVQFN24

## 3. Ordering information

Table 1. Ordering information

| Type number        | Topside   | Package |                                                                                                                  |          |

|--------------------|-----------|---------|------------------------------------------------------------------------------------------------------------------|----------|

|                    | marking   | Name    | Description                                                                                                      | Version  |

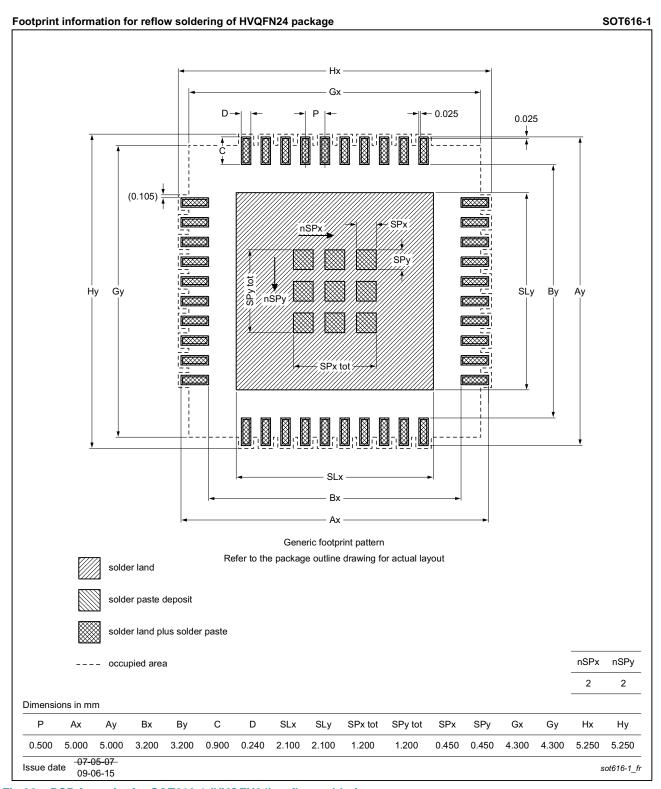

| PCA9539BS          | 9539      | HVQFN24 | plastic thermal enhanced very thin quad flat package; no leads; 24 terminals; body 4 $\times$ 4 $\times$ 0.85 mm | SOT616-1 |

| PCA9539RBS         | 539R      | HVQFN24 | plastic thermal enhanced very thin quad flat package; no leads; 24 terminals; body $4 \times 4 \times 0.85$ mm   | SOT616-1 |

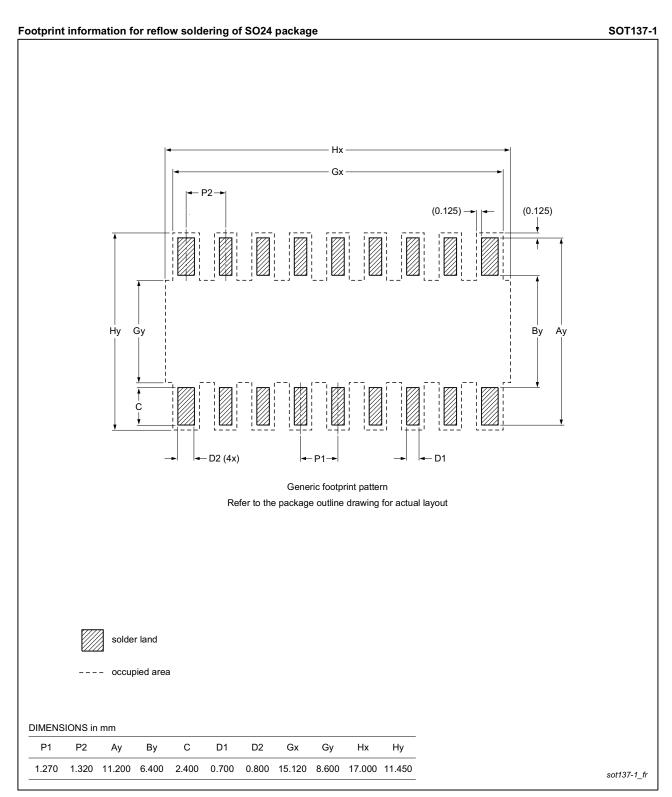

| PCA9539D           | PCA9539D  | SO24    | plastic small outline package; 24 leads;<br>body width 7.5 mm                                                    | SOT137-1 |

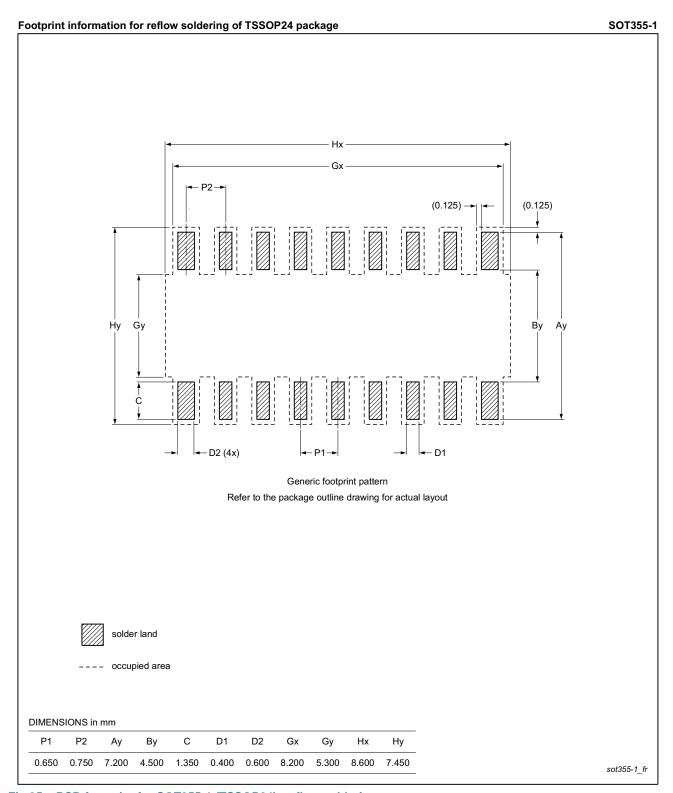

| PCA9539PW          | PCA9539PW | TSSOP24 | plastic thin shrink small outline package; 24 leads; body width 4.4 mm                                           | SOT355-1 |

| PCA9539PW/Q900[1]  | PCA9539PW | TSSOP24 | plastic thin shrink small outline package; 24 leads; body width 4.4 mm                                           | SOT355-1 |

| PCA9539RPW         | PA9539RPW | TSSOP24 | plastic thin shrink small outline package; 24 leads; body width 4.4 mm                                           | SOT355-1 |

| PCA9539RPW/Q900[1] | PA9539RPW | TSSOP24 | plastic thin shrink small outline package; 24 leads; body width 4.4 mm                                           | SOT355-1 |

<sup>[1]</sup> PCA9539PW/Q900 and PCA9539RPW/Q900 are AEC-Q100 compliant. Contact I2C.support@nxp.com for PPAP.

#### 3.1 Ordering options

Table 2. Ordering options

| Type number | Orderable part number | Package | Packing method                       | Minimum order quantity | Temperature                                                         |

|-------------|-----------------------|---------|--------------------------------------|------------------------|---------------------------------------------------------------------|

| PCA9539BS   | PCA9539BS,115         | HVQFN24 | Reel 7" Q1/T1 *standard mark SMD[1]  | 1500                   | $T_{amb} = -40  ^{\circ}\text{C} \text{ to } +85  ^{\circ}\text{C}$ |

|             | PCA9539BS,118         | HVQFN24 | Reel 13" Q1/T1 *standard mark SMD[1] | 6000                   | $T_{amb} = -40  ^{\circ}\text{C} \text{ to } +85  ^{\circ}\text{C}$ |

|             | PCA9539BSHP           | HVQFN24 | Reel 13" Q2/T3 *standard mark SMD[2] | 6000                   | $T_{amb} = -40  ^{\circ}\text{C} \text{ to } +85  ^{\circ}\text{C}$ |

Table 2.

Ordering options ...continued

| Type number     | Orderable part number | Package | Packing method                               | Minimum order quantity | Temperature                                                          |

|-----------------|-----------------------|---------|----------------------------------------------|------------------------|----------------------------------------------------------------------|

| PCA9539RBS      | PCA9539RBS,118        | HVQFN24 | Reel 13" Q1/T1 *standard mark SMD[1]         | 6000                   | $T_{amb} = -40  ^{\circ}\text{C} \text{ to } +85  ^{\circ}\text{C}$  |

| PCA9539D        | PCA9539D,112          | SO24    | Standard marking * IC's tube - DSC bulk pack | 1200                   | $T_{amb} = -40  ^{\circ}\text{C} \text{ to } +85  ^{\circ}\text{C}$  |

|                 | PCA9539D,118          | SO24    | Reel 13" Q1/T1 *standard mark SMD[1]         | 1000                   | $T_{amb} = -40  ^{\circ}\text{C} \text{ to } +85  ^{\circ}\text{C}$  |

| PCA9539PW       | PCA9539PW,112         | TSSOP24 | Standard marking * IC's tube - DSC bulk pack | 1575                   | $T_{amb} = -40  ^{\circ}\text{C} \text{ to } +85  ^{\circ}\text{C}$  |

|                 | PCA9539PW,118         | TSSOP24 | Reel 13" Q1/T1 *standard mark SMD[1]         | 2500                   | $T_{amb} = -40  ^{\circ}\text{C} \text{ to } +85  ^{\circ}\text{C}$  |

| PCA9539PW/Q900  | PCA9539PW/Q900,118    | TSSOP24 | Reel 13" Q1/T1 *standard mark SMD[1]         | 2500                   | $T_{amb} = -40  ^{\circ}\text{C} \text{ to } +125  ^{\circ}\text{C}$ |

| PCA9539RPW      | PCA9539RPW,118        | TSSOP24 | Reel 13" Q1/T1 *standard mark SMD[1]         | 2500                   | $T_{amb} = -40  ^{\circ}\text{C} \text{ to } +85  ^{\circ}\text{C}$  |

| PCA9539RPW/Q900 | PCA9539RPWJ           | TSSOP24 | Reel 13" Q1/T1 *standard mark SMD[1]         | 2500                   | $T_{amb} = -40  ^{\circ}\text{C} \text{ to } +125  ^{\circ}\text{C}$ |

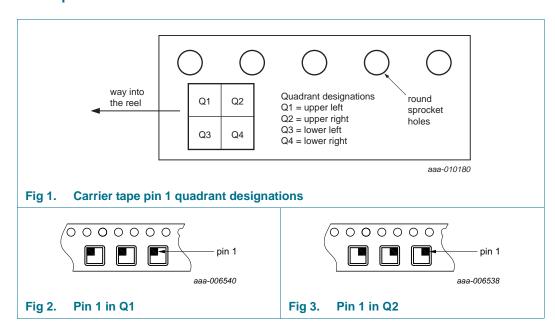

[1] Pin 1 in Quadrant 1; see Figure 2.

[2] Pin 1 in Quadrant 2; see Figure 3.

#### 3.1.1 Pin 1 quadrant indication

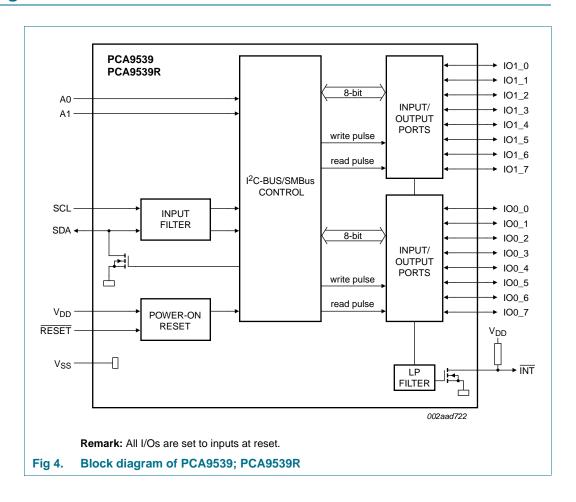

## 4. Block diagram

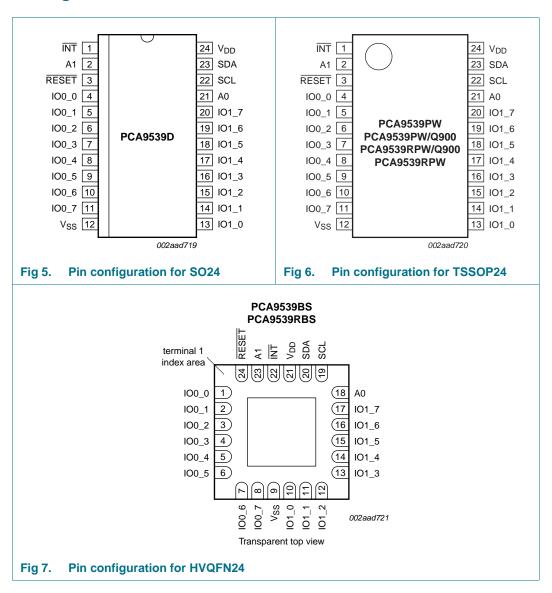

## 5. Pinning information

## 5.1 Pinning

## 5.2 Pin description

Table 3. Pin description

| Symbol   | Pin           |         | Description                                                                                                                                                                     |

|----------|---------------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          | SO24, TSSOP24 | HVQFN24 |                                                                                                                                                                                 |

| ĪNT      | 1             | 22      | interrupt output (open-drain)                                                                                                                                                   |

| A1       | 2             | 23      | address input 1                                                                                                                                                                 |

| RESET    | 3             | 24      | active LOW reset input. Driving this pin LOW causes:  PCA9539 to reset its state machine and registers  PCA9539R to reset its state machine, but has no effect on its registers |

| IO0_0    | 4             | 1       | port 0 input/output 0                                                                                                                                                           |

| IO0_1    | 5             | 2       | port 0 input/output 1                                                                                                                                                           |

| IO0_2    | 6             | 3       | port 0 input/output 2                                                                                                                                                           |

| IO0_3    | 7             | 4       | port 0 input/output 3                                                                                                                                                           |

| IO0_4    | 8             | 5       | port 0 input/output 4                                                                                                                                                           |

| IO0_5    | 9             | 6       | port 0 input/output 5                                                                                                                                                           |

| IO0_6    | 10            | 7       | port 0 input/output 6                                                                                                                                                           |

| IO0_7    | 11            | 8       | port 0 input/output 7                                                                                                                                                           |

| $V_{SS}$ | 12            | 9[1]    | supply ground                                                                                                                                                                   |

| IO1_0    | 13            | 10      | port 1 input/output 0                                                                                                                                                           |

| IO1_1    | 14            | 11      | port 1 input/output 1                                                                                                                                                           |

| IO1_2    | 15            | 12      | port 1 input/output 2                                                                                                                                                           |

| IO1_3    | 16            | 13      | port 1 input/output 3                                                                                                                                                           |

| IO1_4    | 17            | 14      | port 1 input/output 4                                                                                                                                                           |

| IO1_5    | 18            | 15      | port 1 input/output 5                                                                                                                                                           |

| IO1_6    | 19            | 16      | port 1 input/output 6                                                                                                                                                           |

| IO1_7    | 20            | 17      | port 1 input/output 7                                                                                                                                                           |

| A0       | 21            | 18      | address input 0                                                                                                                                                                 |

| SCL      | 22            | 19      | serial clock line input                                                                                                                                                         |

| SDA      | 23            | 20      | serial data line open-drain input/output                                                                                                                                        |

| $V_{DD}$ | 24            | 21      | supply voltage                                                                                                                                                                  |

|          |               |         | 1                                                                                                                                                                               |

<sup>[1]</sup> HVQFN24 package die supply ground is connected to both  $V_{SS}$  pin and exposed center pad.  $V_{SS}$  pin must be connected to supply ground for proper device operation. For enhanced thermal, electrical, and board level performance, the exposed pad needs to be soldered to the board using a corresponding thermal pad on the board and for proper heat conduction through the board, thermal vias need to be incorporated in the PCB in the thermal pad region.

## 6. Functional description

Refer to Figure 4 "Block diagram of PCA9539; PCA9539R".

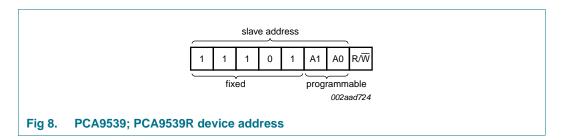

#### 6.1 Device address

## 6.2 Registers

#### 6.2.1 Command byte

The command byte is the first byte to follow the address byte during a write transmission. It is used as a pointer to determine which of the following registers will be written or read.

Table 4. Command byte

| Command | Register                  |

|---------|---------------------------|

| 0       | Input port 0              |

| 1       | Input port 1              |

| 2       | Output port 0             |

| 3       | Output port 1             |

| 4       | Polarity inversion port 0 |

| 5       | Polarity inversion port 1 |

| 6       | Configuration port 0      |

| 7       | Configuration port 1      |

#### 6.2.2 Registers 0 and 1: Input port registers

This register is an input-only port. It reflects the incoming logic levels of the pins, regardless of whether the pin is defined as an input or an output by Register 3. Writes to this register have no effect.

The default value 'X' is determined by the externally applied logic level.

Table 5. Input port 0 register

| Bit     | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|---------|------|------|------|------|------|------|------|------|

| Symbol  | 10.7 | 10.6 | 10.5 | 10.4 | 10.3 | 10.2 | 10.1 | 10.0 |

| Default | Х    | Х    | Х    | Х    | Х    | Х    | Х    | Х    |

Table 6. Input port 1 register

| Bit     | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|---------|------|------|------|------|------|------|------|------|

| Symbol  | l1.7 | I1.6 | l1.5 | l1.4 | I1.3 | l1.2 | l1.1 | I1.0 |

| Default | Х    | Х    | Х    | Х    | Х    | Х    | Х    | Х    |

#### 6.2.3 Registers 2 and 3: Output port registers

This register is an output-only port. It reflects the outgoing logic levels of the pins defined as outputs by Registers 6 and 7. Bit values in this register have no effect on pins defined as inputs. In turn, reads from this register reflect the value that is in the flip-flop controlling the output selection, **not** the actual pin value.

Table 7. Output port 0 register

| Bit     | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|---------|------|------|------|------|------|------|------|------|

| Symbol  | O0.7 | O0.6 | O0.5 | O0.4 | O0.3 | O0.2 | O0.1 | O0.0 |

| Default | 1    | 1    | 1    | 1    | 1    | 1    | 1    | 1    |

Table 8. Output port 1 register

| Bit     | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|---------|------|------|------|------|------|------|------|------|

| Symbol  | O1.7 | O1.6 | O1.5 | O1.4 | O1.3 | 01.2 | O1.1 | O1.0 |

| Default | 1    | 1    | 1    | 1    | 1    | 1    | 1    | 1    |

#### 6.2.4 Registers 4 and 5: Polarity inversion registers

This register allows the user to invert the polarity of the Input port register data. If a bit in this register is set (written with '1'), the Input port data polarity is inverted. If a bit in this register is cleared (written with a '0'), the Input port data polarity is retained.

Table 9. Polarity inversion port 0 register

| Bit     | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|---------|------|------|------|------|------|------|------|------|

| Symbol  | N0.7 | N0.6 | N0.5 | N0.4 | N0.3 | N0.2 | N0.1 | N0.0 |

| Default | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    |

Table 10. Polarity inversion port 1 register

| Bit     | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|---------|------|------|------|------|------|------|------|------|

| Symbol  | N1.7 | N1.6 | N1.5 | N1.4 | N1.3 | N1.2 | N1.1 | N1.0 |

| Default | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    |

#### 6.2.5 Registers 6 and 7: Configuration registers

This register configures the directions of the I/O pins. If a bit in this register is set (written with '1'), the corresponding port pin is enabled as an input with high-impedance output driver. If a bit in this register is cleared (written with '0'), the corresponding port pin is enabled as an output. At reset, the device's ports are inputs.

Table 11. Configuration port 0 register

| Bit     | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|---------|------|------|------|------|------|------|------|------|

| Symbol  | C0.7 | C0.6 | C0.5 | C0.4 | C0.3 | C0.2 | C0.1 | C0.0 |

| Default | 1    | 1    | 1    | 1    | 1    | 1    | 1    | 1    |

Table 12. Configuration port 1 register

| Bit     | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|---------|------|------|------|------|------|------|------|------|

| Symbol  | C1.7 | C1.6 | C1.5 | C1.4 | C1.3 | C1.2 | C1.1 | C1.0 |

| Default | 1    | 1    | 1    | 1    | 1    | 1    | 1    | 1    |

#### 6.3 Power-on reset

When power is applied to  $V_{DD}$ , an internal power-on reset holds the PCA9539; PCA9539R in a reset condition until  $V_{DD}$  has reached  $V_{POR}$ . At that point, the reset condition is released and the PCA9539; PCA9539R registers and SMBus state machine will initialize to their default states. Thereafter,  $V_{DD}$  must be lowered below 0.2 V to reset the device.

For a power reset cycle,  $V_{DD}$  must be lowered below 0.2 V and then restored to the operating voltage.

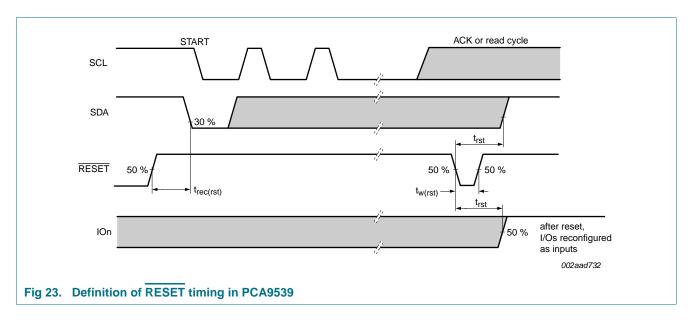

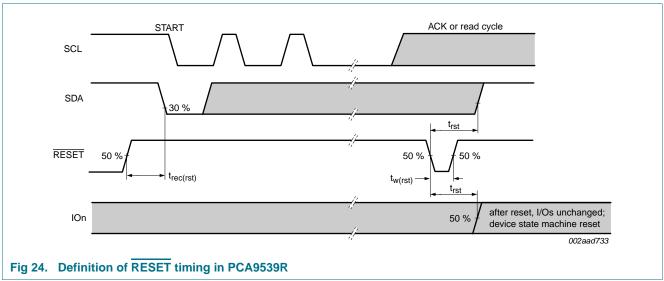

## 6.4 RESET input

A reset can be accomplished by holding the RESET pin LOW for a minimum of  $t_{w(rst)}$ . In the PCA9539 the registers and SMBus/I²C-bus state machine will be held in their default state until the RESET input is once again HIGH. This input typically requires a pull-up to  $V_{DD}$ . In the PCA9539R, only the device state machine is initialized. The internal general-purpose registers remain unchanged. Using the PCA9539R hardware reset pin will only reset the I²C-bus interface should it be stuck LOW to regain access to the I²C-bus. This allows the I/O pins to retain their last configured state so that they can keep any lines in their previously defined state and not cause system errors while the I²C-bus is being restored.

#### 6.5 I/O port

When an I/O is configured as an input, FETs Q1 and Q2 are off, creating a high-impedance input. The input voltage may be raised above V<sub>DD</sub> to a maximum of 5.5 V.

If the I/O is configured as an output, then either Q1 or Q2 is on, depending on the state of the Output port register. Care should be exercised if an external voltage is applied to an I/O configured as an output because of the low-impedance path that exists between the pin and either  $V_{DD}$  or  $V_{SS}$ .

#### 6.6 Bus transactions

#### 6.6.1 Writing to the port registers

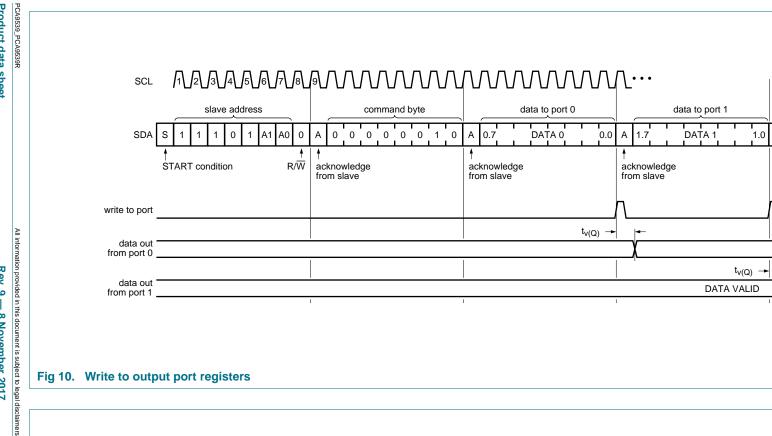

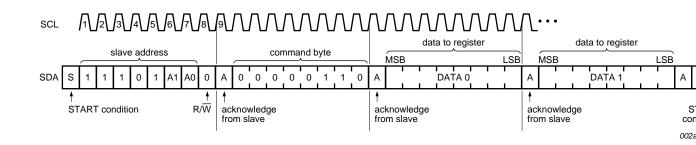

Data is transmitted to the PCA9539; PCA9539R by sending the device address and setting the least significant bit to a logic 0 (see <u>Figure 8 "PCA9539; PCA9539R device</u> <u>address"</u>). The command byte is sent after the address and determines which register will receive the data following the command byte.

The eight registers within the PCA9539; PCA9539R are configured to operate as four register pairs. The four pairs are Input ports, Output ports, Polarity inversion ports, and Configuration ports. After sending data to one register, the next data byte will be sent to the other register in the pair (see <a href="Figure 10">Figure 10</a> and <a href="Figure 11">Figure 11</a>). For example, if the first byte is sent to Output port 1 (register 3), then the next byte will be stored in Output port 0 (register 2). There is no limitation on the number of data bytes sent in one write transmission. In this way, each 8-bit register may be updated independently of the other registers.

Fig 11. Write to configuration registers

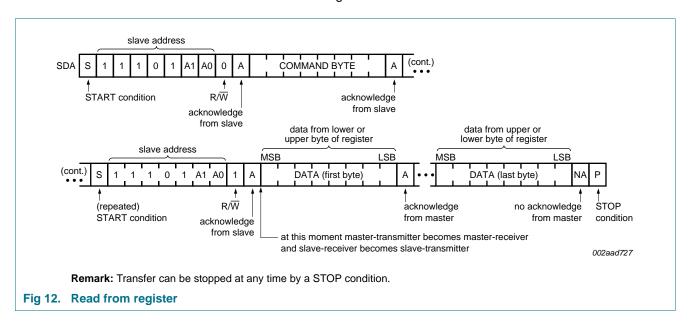

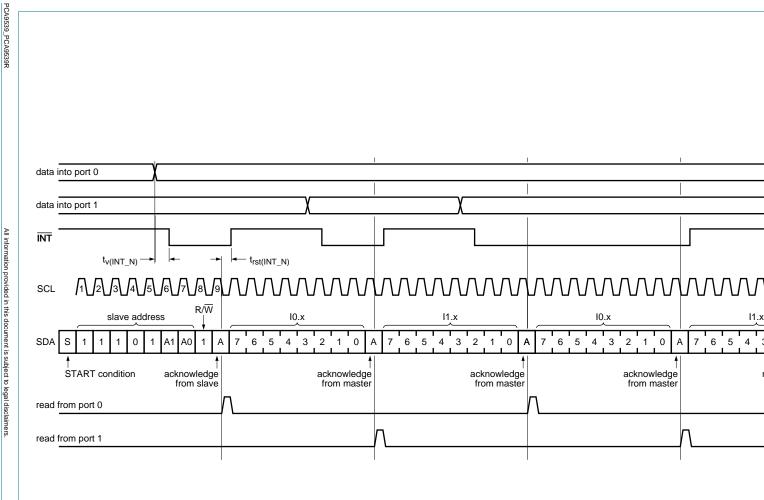

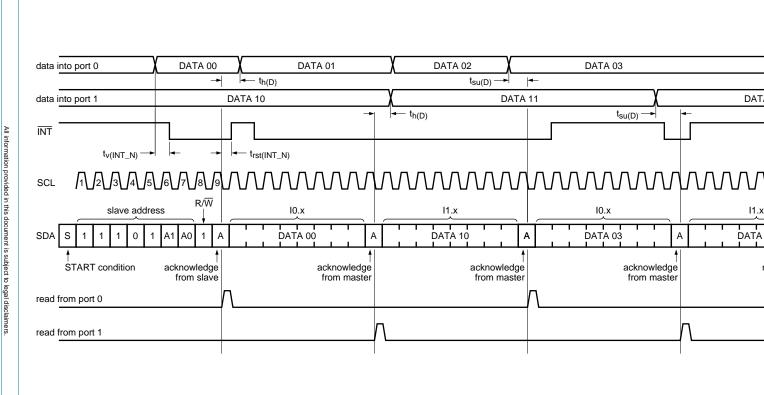

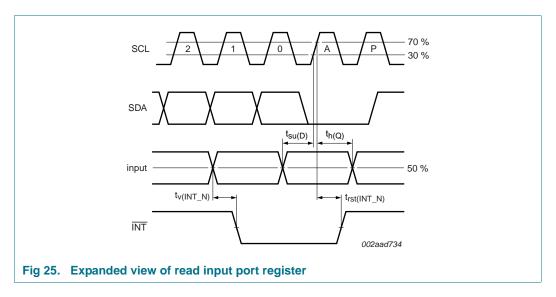

#### 6.6.2 Reading the port registers

In order to read data from the PCA9539; PCA9539R, the bus master must first send the PCA9539; PCA9539R address with the least significant bit set to a logic 0 (see Figure 8 "PCA9539; PCA9539R device address"). The command byte is sent after the address and determines which register will be accessed. After a restart, the device address is sent again, but this time the least significant bit is set to a logic 1. Data from the register defined by the command byte will then be sent by the PCA9539; PCA9539R (see Figure 12, Figure 13 and Figure 14). Data is clocked into the register on the falling edge of the acknowledge clock pulse. After the first byte is read, additional bytes may be read but the data will now reflect the information in the other register in the pair. For example, if you read Input port 1, then the next byte read would be Input port 0. There is no limitation on the number of data bytes received in one read transmission but the final byte received, the bus master must not acknowledge the data.

**Remark:** Transfer of data can be stopped at any moment by a STOP condition. When this occurs, data present at the latest acknowledge phase is is assumed that the command byte has previously been set to '00' (read input port register).

Fig 13. Read input port register, scenario 1

PCA9539\_PCA9539R

**Remark:** Transfer of data can be stopped at any moment by a STOP condition. When this occurs, data present at the latest acknowledge phase is is assumed that the command byte has previously been set to '00' (read input port register).

Fig 14. Read input port register, scenario 2

#### 6.6.3 Interrupt output

The open-drain interrupt output is activated when one of the port pins changes state and the pin is configured as an input. The interrupt is deactivated when the input returns to its previous state or the Input port register is read (see <u>Figure 13</u>). A pin configured as an output cannot cause an interrupt. Since each 8-bit port is read independently, the interrupt caused by Port 0 will not be cleared by a read of Port 1 or the other way around.

**Remark:** Changing an I/O from an output to an input may cause a false interrupt to occur if the state of the pin does not match the contents of the Input port register.

#### 7. Characteristics of the I<sup>2</sup>C-bus

The I<sup>2</sup>C-bus is for 2-way, 2-line communication between different ICs or modules. The two lines are a serial data line (SDA) and a serial clock line (SCL). Both lines must be connected to a positive supply via a pull-up resistor when connected to the output stages of a device. Data transfer may be initiated only when the bus is not busy.

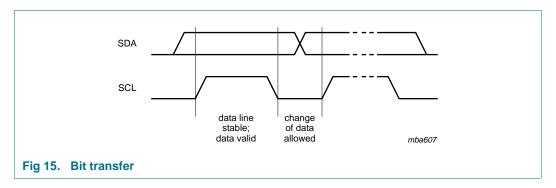

#### 7.1 Bit transfer

One data bit is transferred during each clock pulse. The data on the SDA line must remain stable during the HIGH period of the clock pulse as changes in the data line at this time will be interpreted as control signals (see Figure 15).

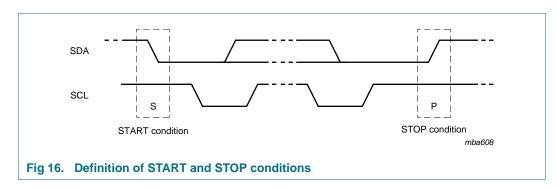

#### 7.1.1 START and STOP conditions

Both data and clock lines remain HIGH when the bus is not busy. A HIGH-to-LOW transition of the data line while the clock is HIGH is defined as the START condition (S). A LOW-to-HIGH transition of the data line while the clock is HIGH is defined as the STOP condition (P) (see Figure 16).

#### 7.2 System configuration

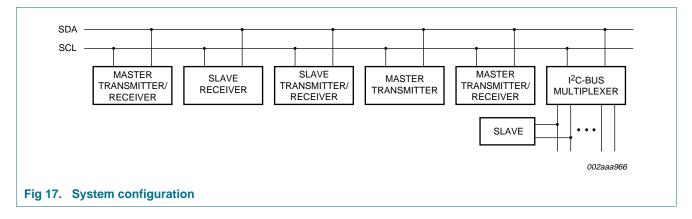

A device generating a message is a 'transmitter'; a device receiving is the 'receiver'. The device that controls the message is the 'master' and the devices which are controlled by the master are the 'slaves' (see Figure 17).

#### 7.3 Acknowledge

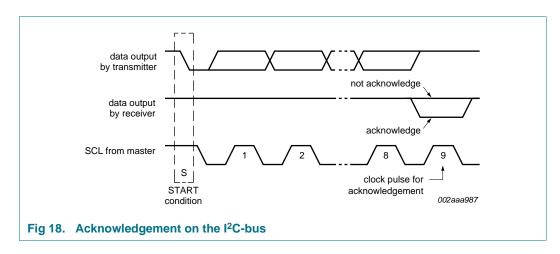

The number of data bytes transferred between the START and the STOP conditions from transmitter to receiver is not limited. Each byte of eight bits is followed by one acknowledge bit. The acknowledge bit is a HIGH level put on the bus by the transmitter, whereas the master generates an extra acknowledge related clock pulse.

A slave receiver which is addressed must generate an acknowledge after the reception of each byte. Also a master must generate an acknowledge after the reception of each byte that has been clocked out of the slave transmitter. The device that acknowledges has to pull down the SDA line during the acknowledge clock pulse, so that the SDA line is stable LOW during the HIGH period of the acknowledge related clock pulse; set-up time and hold time must be taken into account.

A master receiver must signal an end of data to the transmitter by not generating an acknowledge on the last byte that has been clocked out of the slave. In this event, the transmitter must leave the data line HIGH to enable the master to generate a STOP condition.

## 8. Application design-in information

#### 8.1 Minimizing I<sub>DD</sub> when the I/Os are used to control LEDs

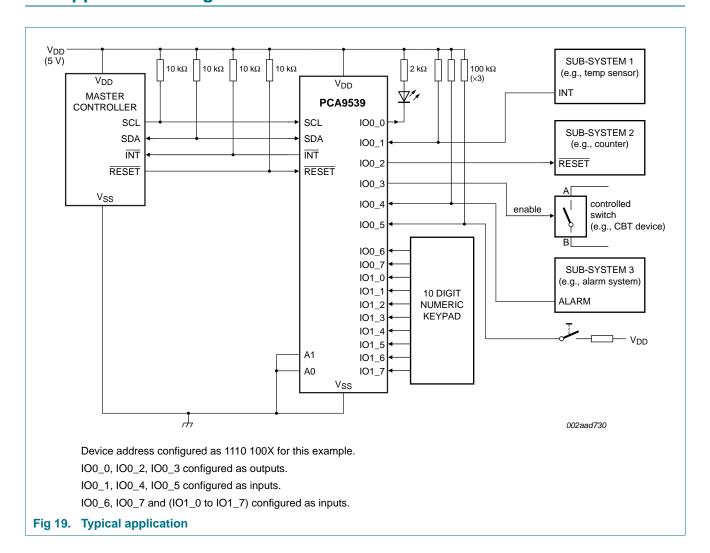

When the I/Os are used to control LEDs, they are normally connected to  $V_{DD}$  through a resistor as shown in <u>Figure 19</u>. Since the LED acts as a diode, when the LED is off the I/O  $V_{I}$  is about 1.2 V less than  $V_{DD}$ . The supply current,  $I_{DD}$ , increases as  $V_{I}$  becomes lower than  $V_{DD}$ .

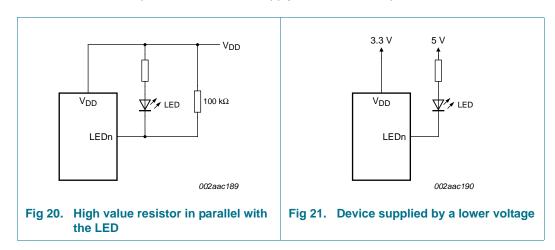

Designs needing to minimize current consumption, such as battery power applications, should consider maintaining the I/O pins greater than or equal to  $V_{DD}$  when the LED is off. Figure 20 shows a high value resistor in parallel with the LED. Figure 21 shows  $V_{DD}$  less than the LED supply voltage by at least 1.2 V. Both of these methods maintain the I/O  $V_{I}$  at or above  $V_{DD}$  and prevents additional supply current consumption when the LED is off.

## 9. Limiting values

#### Table 13. Limiting values

In accordance with the Absolute Maximum Rating System (IEC 60134).

| Symbol              | Parameter                      | Conditions                                               | Min                   | Max  | Unit |

|---------------------|--------------------------------|----------------------------------------------------------|-----------------------|------|------|

| $V_{DD}$            | supply voltage                 |                                                          | -0.5                  | +6.0 | V    |

| V <sub>I/O</sub>    | voltage on an input/output pin |                                                          | V <sub>SS</sub> - 0.5 | 6    | V    |

| Io                  | output current                 | on an I/O pin                                            | -                     | ±50  | mA   |

| l <sub>l</sub>      | input current                  |                                                          | -                     | ±20  | mA   |

| I <sub>DD</sub>     | supply current                 |                                                          | -                     | 160  | mA   |

| I <sub>SS</sub>     | ground supply current          |                                                          | -                     | 200  | mA   |

| P <sub>tot</sub>    | total power dissipation        |                                                          | -                     | 200  | mW   |

| T <sub>stg</sub>    | storage temperature            |                                                          | -65                   | +150 | °C   |

| T <sub>amb</sub>    | ambient temperature            | operating                                                |                       |      | '    |

|                     |                                | all devices except PCA9539PW/Q900<br>and PCA9539RPW/Q900 | -40                   | +85  | °C   |

|                     |                                | PCA9539PW/Q900 and<br>PCA9539RPW/Q900                    | -40                   | +125 | °C   |

| T <sub>j(max)</sub> | maximum junction temperature   |                                                          | -                     | 125  | °C   |

#### 10. Static characteristics

Table 14. Static characteristics for all devices except PCA9539PW/Q900 and PCA9539RPW/Q900

$V_{DD}$  = 2.3 V to 5.5 V;  $V_{SS}$  = 0 V;  $T_{amb}$  = -40 °C to +85 °C; unless otherwise specified.

| Symbol           | Parameter                        | Conditions                                                                                                             | М               | in               | Тур  | Max                 | Unit |

|------------------|----------------------------------|------------------------------------------------------------------------------------------------------------------------|-----------------|------------------|------|---------------------|------|

| Supplie          | es                               |                                                                                                                        |                 |                  |      |                     |      |

| $V_{DD}$         | supply voltage                   |                                                                                                                        | 2.              | 3                | -    | 5.5                 | V    |

| I <sub>DD</sub>  | supply current                   | Operating mode; $V_{DD} = 5.5 \text{ V}$ ; no load; $f_{SCL} = 100 \text{ kHz}$ ; I/O = inputs                         | -               |                  | 135  | 200                 | μА   |

| I <sub>stb</sub> | standby current                  | Standby mode; $V_{DD} = 5.5 \text{ V}$ ; no load; $V_{I} = V_{SS}$ ; $f_{SCL} = 0 \text{ kHz}$ ; $I/O = \text{inputs}$ | -               |                  | 0.25 | 1                   | μА   |

|                  |                                  | Standby mode; $V_{DD}$ = 5.5 V; no load; $V_{I}$ = $V_{DD}$ ; $f_{SCL}$ = 0 kHz; I/O = inputs                          | -               |                  | 0.25 | 1                   | μА   |

| $V_{POR}$        | power-on reset voltage[1]        | no load; V <sub>I</sub> = V <sub>DD</sub> or V <sub>SS</sub>                                                           | -               |                  | 1.7  | 2.2                 | V    |

| Input S          | CL; input/output SDA             |                                                                                                                        |                 |                  |      |                     |      |

| $V_{IL}$         | LOW-level input voltage          |                                                                                                                        | _(              | ).5              | -    | +0.3V <sub>DD</sub> | V    |

| $V_{IH}$         | HIGH-level input voltage         |                                                                                                                        | 0.              | $7V_{DD}$        | -    | 5.5                 | V    |

| I <sub>OL</sub>  | LOW-level output current         | V <sub>OL</sub> = 0.4 V                                                                                                | 3               |                  | -    | -                   | mA   |

| IL               | leakage current                  | $V_{I} = V_{DD} = V_{SS}$                                                                                              |                 | 1                | -    | +1                  | μА   |

| Ci               | input capacitance                | $V_{I} = V_{SS}$                                                                                                       | -               |                  | 6    | 10                  | pF   |

| I/Os             |                                  |                                                                                                                        |                 |                  |      |                     |      |

| $V_{IL}$         | LOW-level input voltage          |                                                                                                                        | -(              | ).5              | -    | +0.3V <sub>DD</sub> | V    |

| V <sub>IH</sub>  | HIGH-level input voltage         |                                                                                                                        | 0.              | 7V <sub>DD</sub> | -    | 5.5                 | V    |

| I <sub>OL</sub>  | LOW-level output current         | $V_{DD} = 2.3 \text{ V to } 5.5 \text{ V; } V_{OL} = 0.5 \text{ V}$                                                    | [2] 8           |                  | 9    | -                   | mA   |

|                  |                                  | $V_{DD} = 2.3 \text{ V to } 5.5 \text{ V; } V_{OL} = 0.7 \text{ V}$                                                    | [ <u>2</u> ] 1( | )                | 11   | -                   | mA   |

| V <sub>OH</sub>  | HIGH-level output voltage        | $I_{OH} = -8 \text{ mA}; V_{DD} = 2.3 \text{ V}$                                                                       | [ <u>3</u> ] 1. | 8                | -    | -                   | V    |

|                  |                                  | $I_{OH} = -10 \text{ mA}; V_{DD} = 2.3 \text{ V}$                                                                      | [ <u>3</u> ] 1. | 7                | -    | -                   | V    |

|                  |                                  | $I_{OH} = -8 \text{ mA}; V_{DD} = 3.0 \text{ V}$                                                                       | [ <u>3</u> ] 2. | 6                | -    | -                   | V    |

|                  |                                  | $I_{OH} = -10 \text{ mA}; V_{DD} = 3.0 \text{ V}$                                                                      | [ <u>3</u> ] 2. | 5                | -    | -                   | V    |

|                  |                                  | $I_{OH} = -8 \text{ mA}; V_{DD} = 4.75 \text{ V}$                                                                      | [ <u>3</u> ] 4. | 1                | -    | -                   | V    |

|                  |                                  | $I_{OH} = -10 \text{ mA}; V_{DD} = 4.75 \text{ V}$                                                                     | [ <u>3</u> ] 4. | 0                | -    | -                   | V    |

| I <sub>LIH</sub> | HIGH-level input leakage current | $V_{DD} = 5.5 \text{ V}; V_{I} = V_{DD}$                                                                               | -               |                  | -    | 1                   | μА   |

| I <sub>LIL</sub> | LOW-level input leakage current  | $V_{DD} = 5.5 \text{ V}; V_{I} = V_{SS}$                                                                               | -               |                  | -    | -1                  | μА   |

| Ci               | input capacitance                |                                                                                                                        | -               |                  | 3.7  | 5                   | pF   |

| Co               | output capacitance               |                                                                                                                        | -               |                  | 3.7  | 5                   | pF   |

| Interrup         | ot INT                           |                                                                                                                        |                 |                  | 1    | 1                   | 1    |

| I <sub>OL</sub>  | LOW-level output current         | V <sub>OL</sub> = 0.4 V                                                                                                | 3               |                  | -    | -                   | mA   |

|                  | nputs A0, A1 and RESET           |                                                                                                                        |                 |                  | 1    | 1                   | 1    |

| V <sub>IL</sub>  | LOW-level input voltage          |                                                                                                                        | -(              | 0.5              | -    | +0.3V <sub>DD</sub> | V    |

| V <sub>IH</sub>  | HIGH-level input voltage         |                                                                                                                        | 0.              | 7V <sub>DD</sub> | -    | 5.5                 | V    |

| I <sub>LI</sub>  | input leakage current            |                                                                                                                        |                 | 1                | -    | +1                  | μА   |

<sup>[1]</sup>  $V_{DD}$  must be lowered to 0.2 V for at least 5  $\mu s$  in order to reset part.

<sup>[2]</sup> Each I/O must be externally limited to a maximum of 25 mA and each octal (IOO\_0 to IOO\_7 and IO1\_0 to IO1\_7) must be limited to a maximum current of 100 mA for a device total of 200 mA.

[3] The total current sourced by all I/Os must be limited to 160 mA (80 mA for IO0\_0 through IO0\_7 and 80 mA for IO1\_0 through IO1\_7).

Table 15. Static characteristics for PCA9539PW/Q900 and PCA9539RPW/Q900

$V_{DD} = 3.0 \text{ V to } 5.5 \text{ V; } V_{SS} = 0 \text{ V; } T_{amb} = -40 ^{\circ}\text{C} \text{ to } +125 ^{\circ}\text{C; } unless \text{ otherwise specified.}$

| Symbol           | Parameter                             | Conditions                                                                                                                   | Min         | Тур  | Max                 | Unit |

|------------------|---------------------------------------|------------------------------------------------------------------------------------------------------------------------------|-------------|------|---------------------|------|

| Supplies         | S                                     |                                                                                                                              |             |      |                     | _    |

| $V_{DD}$         | supply voltage                        |                                                                                                                              | 3.0         | -    | 5.5                 | V    |

| I <sub>DD</sub>  | supply current                        | Operating mode; $V_{DD} = 5.5 \text{ V}$ ; no load; $f_{SCL} = 100 \text{ kHz}$ ; I/O = inputs                               | -           | 135  | 200                 | μΑ   |

| I <sub>stb</sub> | standby current                       | Standby mode; V <sub>DD</sub> = 5.5 V; no load;<br>V <sub>I</sub> = V <sub>SS</sub> ; f <sub>SCL</sub> = 0 kHz; I/O = inputs | -           | 0.25 | 1                   | μА   |

|                  |                                       | Standby mode; $V_{DD} = 5.5 \text{ V}$ ; no load; $V_{I} = V_{DD}$ ; $f_{SCL} = 0 \text{ kHz}$ ; $I/O = \text{inputs}$       | -           | 0.25 | 1                   | μА   |

| $V_{POR}$        | power-on reset voltage <sup>[1]</sup> | no load; $V_I = V_{DD}$ or $V_{SS}$                                                                                          | -           | 1.7  | 2.2                 | V    |

| Input SC         | CL; input/output SDA                  |                                                                                                                              |             |      |                     |      |

| $V_{IL}$         | LOW-level input voltage               |                                                                                                                              | -0.5        | -    | +0.3V <sub>DD</sub> | V    |

| $V_{IH}$         | HIGH-level input voltage              |                                                                                                                              | $0.7V_{DD}$ | -    | 5.5                 | V    |

| $I_{OL}$         | LOW-level output current, SDA         | $V_{OL} = 0.4 V$                                                                                                             |             |      |                     |      |

|                  |                                       | $V_{DD} = 5.5 \text{ V}$                                                                                                     | 3           | -    | -                   | mA   |

|                  |                                       | $V_{DD} = 3.0 \text{ V}$                                                                                                     | 2.5         | -    | -                   | mA   |

| IL               | leakage current                       | $V_I = V_{DD} = V_{SS}$                                                                                                      | -1          | -    | +1                  | μΑ   |

| Ci               | input capacitance                     | $V_I = V_{SS}$                                                                                                               | -           | 6    | 10                  | pF   |

| I/Os             |                                       |                                                                                                                              |             |      | ·                   |      |

| $V_{IL}$         | LOW-level input voltage               |                                                                                                                              | -0.5        | -    | +0.3V <sub>DD</sub> | V    |

| $V_{IH}$         | HIGH-level input voltage              |                                                                                                                              | $0.7V_{DD}$ | -    | 5.5                 | V    |

| $I_{OL}$         | LOW-level output current              | $V_{OL} = 0.5 \text{ V}$                                                                                                     |             |      |                     |      |

|                  |                                       | $V_{DD} = 4.5 \text{ V}$ [2]                                                                                                 | 8           | 9    | -                   | mA   |

|                  |                                       | $V_{DD} = 3.0 \text{ V}$ [2]                                                                                                 | 7.5         | -    | -                   | mA   |

|                  |                                       | V <sub>OL</sub> = 0.7 V                                                                                                      |             |      |                     |      |

|                  |                                       | V <sub>DD</sub> = 4.5 V                                                                                                      | 10          | 11   | -                   | mA   |

|                  |                                       | V <sub>DD</sub> = 3.0 V                                                                                                      | 9.5         | -    | -                   | mA   |

| V <sub>OH</sub>  | HIGH-level output voltage             | $I_{OH} = -8 \text{ mA}$                                                                                                     |             |      |                     |      |

|                  |                                       | V <sub>DD</sub> = 4.5 V                                                                                                      | 4.1         | -    | -                   | V    |

|                  |                                       | V <sub>DD</sub> = 3.0 V                                                                                                      | 2.5         | -    | -                   | V    |

|                  |                                       | $I_{OH} = -10 \text{ mA}$                                                                                                    |             |      |                     |      |

|                  |                                       | V <sub>DD</sub> = 4.5 V                                                                                                      | 4.0         | -    | -                   | V    |

|                  |                                       | V <sub>DD</sub> = 3.0 V                                                                                                      | 2.4         | -    | -                   | V    |

| I <sub>LIH</sub> | HIGH-level input leakage current      | $V_{DD} = 5.5 \text{ V}; V_{I} = V_{DD}$                                                                                     | -           | -    | 1                   | μΑ   |

| I <sub>LIL</sub> | LOW-level input leakage current       | $V_{DD} = 5.5 \text{ V}; V_{I} = V_{SS}$                                                                                     | -           | -    | -1                  | μΑ   |

| Ci               | input capacitance                     |                                                                                                                              | -           | 3.7  | 5                   | pF   |

| Co               | output capacitance                    |                                                                                                                              | -           | 3.7  | 5                   | pF   |

| Interrup         | INT                                   |                                                                                                                              | 1           | 1    |                     | -1   |

| I <sub>OL</sub>  | LOW-level output current              | V <sub>OL</sub> = 0.4 V                                                                                                      | 3           | -    | -                   | mA   |

Table 15. Static characteristics for PCA9539PW/Q900 and PCA9539RPW/Q900 ...continued

$V_{DD} = 3.0 \text{ V to } 5.5 \text{ V; } V_{SS} = 0 \text{ V; } T_{amb} = -40 \text{ °C to } +125 \text{ °C; } unless otherwise specified.}$

| Symbol          | Parameter                | Conditions | Min         | Тур | Max                 | Unit |

|-----------------|--------------------------|------------|-------------|-----|---------------------|------|

| Select in       | puts A0, A1 and RESET    |            |             |     |                     |      |

| V <sub>IL</sub> | LOW-level input voltage  |            | -0.5        | -   | +0.3V <sub>DD</sub> | V    |

| V <sub>IH</sub> | HIGH-level input voltage |            | $0.7V_{DD}$ | -   | 5.5                 | V    |

| ILI             | input leakage current    |            | -1          | -   | +1                  | μΑ   |

<sup>[1]</sup>  $V_{DD}$  must be lowered to 0.2 V for at least 5  $\mu s$  in order to reset part.

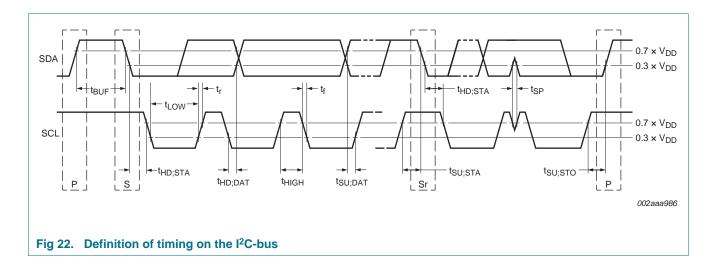

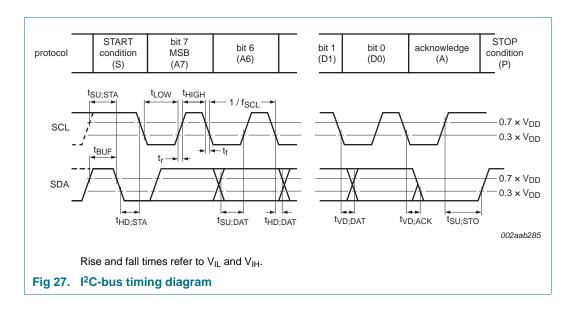

## 11. Dynamic characteristics

Table 16. Dynamic characteristics

| Symbol              | Parameter                                                               | Conditions |     | rd-mode<br>-bus | Fast-mode              | Unit |     |

|---------------------|-------------------------------------------------------------------------|------------|-----|-----------------|------------------------|------|-----|

|                     |                                                                         |            | Min | Max             | Min                    | Max  |     |

| f <sub>SCL</sub>    | SCL clock frequency                                                     |            | 0   | 100             | 0                      | 400  | kHz |

| t <sub>BUF</sub>    | bus free time between a STOP and START condition                        |            | 4.7 | -               | 1.3                    | -    | μS  |

| t <sub>HD;STA</sub> | hold time (repeated) START condition                                    |            | 4.0 | -               | 0.6                    | -    | μS  |

| t <sub>SU;STA</sub> | set-up time for a repeated START condition                              |            | 4.7 | -               | 0.6                    | -    | μS  |

| t <sub>SU;STO</sub> | set-up time for STOP condition                                          |            | 4.0 | -               | 0.6                    | -    | μS  |

| t <sub>VD;ACK</sub> | data valid acknowledge time                                             | [1         | 0.3 | 3.45            | 0.1                    | 0.9  | μS  |

| t <sub>HD;DAT</sub> | data hold time                                                          |            | 0   | -               | 0                      | -    | ns  |

| t <sub>VD;DAT</sub> | data valid time                                                         | [2         | 300 | -               | 50                     | -    | ns  |

| t <sub>SU;DAT</sub> | data set-up time                                                        |            | 250 | -               | 100                    | -    | ns  |

| t <sub>LOW</sub>    | LOW period of the SCL clock                                             |            | 4.7 | -               | 1.3                    | -    | μS  |

| t <sub>HIGH</sub>   | HIGH period of the SCL clock                                            |            | 4.0 | -               | 0.6                    | -    | μS  |

| t <sub>f</sub>      | fall time of both SDA and SCL signals                                   | [3         | -   | 300             | 20 + 0.1C <sub>b</sub> | 300  | ns  |

| t <sub>r</sub>      | rise time of both SDA and SCL signals                                   | [3         | -   | 1000            | 20 + 0.1C <sub>b</sub> | 300  | ns  |

| t <sub>SP</sub>     | pulse width of spikes that<br>must be suppressed by the<br>input filter |            | -   | 50              | -                      | 50   | ns  |

| Port timi           | ng                                                                      |            |     |                 | •                      |      |     |

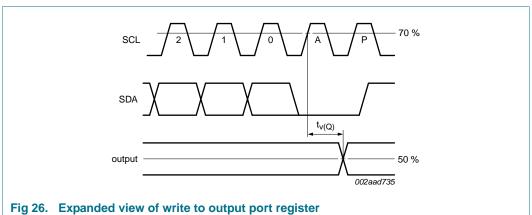

| t <sub>v(Q)</sub>   | data output valid time                                                  | <u>[4</u>  | -   | 200             | -                      | 200  | ns  |

| t <sub>su(D)</sub>  | data input set-up time                                                  |            | 150 | -               | 150                    | -    | ns  |

| t <sub>h(D)</sub>   | data input hold time                                                    |            | 1   | -               | 1                      | -    | μS  |

<sup>[2]</sup> Each I/O must be externally limited to a maximum of 25 mA and each octal (IO0\_0 to IO0\_7 and IO1\_0 to IO1\_7) must be limited to a maximum current of 100 mA for a device total of 200 mA.

<sup>[3]</sup> The total current sourced by all I/Os must be limited to 160 mA (80 mA for IOO\_0 through IOO\_7 and 80 mA for IO1\_0 through IO1\_7).

Table 16. Dynamic characteristics ...continued

| Symbol                  | Parameter             | Conditions                            |                | ard-mode<br>C-bus | Fast-mode | Unit |    |

|-------------------------|-----------------------|---------------------------------------|----------------|-------------------|-----------|------|----|

|                         |                       |                                       | Min            | Max               | Min       | Max  |    |

| Interrupt               | timing                |                                       | ,              |                   |           |      |    |

| t <sub>v(INT_N)</sub>   | valid time on pin INT |                                       | -              | 4                 | -         | 4    | μS |

| t <sub>rst(INT_N)</sub> | reset time on pin INT |                                       | -              | 4                 | -         | 4    | μS |

| RESET til               | ming                  |                                       |                |                   |           |      |    |

| t <sub>w(rst)</sub>     | reset pulse width     | all devices except<br>PCA9539RPW/Q900 | 4              | -                 | 4         | -    | ns |

|                         |                       | PCA9539RPW/Q900                       | 6              | -                 | 6         | -    | ns |

| t <sub>rec(rst)</sub>   | reset recovery time   |                                       | 0              | -                 | 0         | -    | ns |

| t <sub>rst</sub>        | reset time            | [5]                                   | <u>[6]</u> 400 | -                 | 400       | -    | ns |

- [1]  $t_{VD;ACK}$  = time for acknowledgement signal from SCL LOW to SDA (out) LOW.

- [2] t<sub>VD:DAT</sub> = minimum time for SDA data out to be valid following SCL LOW.

- [3]  $C_b = total$  capacitance of one bus line in pF.

- [4]  $t_{V(Q)}$  measured from 0.7V<sub>DD</sub> on SCL to 50 % I/O output.

- [5] Resetting the device while actively communicating on the bus may cause glitches or errant STOP conditions.

- [6] Upon reset, the full delay will be the sum of  $t_{rst}$  and the RC time constant of the SDA bus.

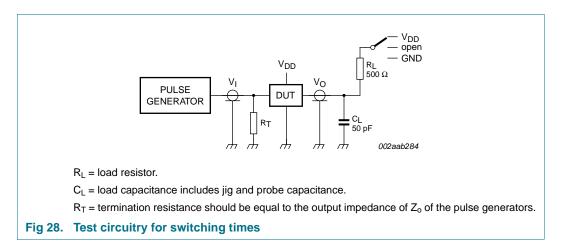

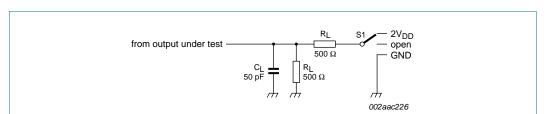

### 12. Test information

Fig 29. Load circuit

Table 17. Test data

| Test       | Load  | Switch |                   |

|------------|-------|--------|-------------------|

|            | CL    |        |                   |

| $t_{V(Q)}$ | 50 pF | 500 Ω  | $2 \times V_{DD}$ |

## 13. Package outline

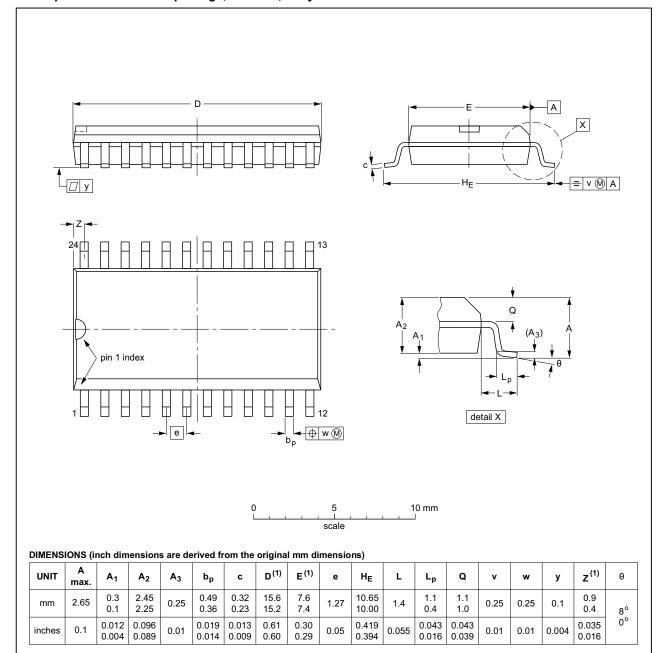

#### SO24: plastic small outline package; 24 leads; body width 7.5 mm

SOT137-1

#### Note

1. Plastic or metal protrusions of 0.15 mm (0.006 inch) maximum per side are not included.

| OUTLINE  |        | EUROPEAN | ISSUE DATE |  |            |                                 |

|----------|--------|----------|------------|--|------------|---------------------------------|

| VERSION  | IEC    | JEDEC    | JEITA      |  | PROJECTION | ISSUE DATE                      |

| SOT137-1 | 075E05 | MS-013   |            |  |            | <del>99-12-27</del><br>03-02-19 |

Fig 30. Package outline SOT137-1 (SO24)

PCA9539\_PCA9539R

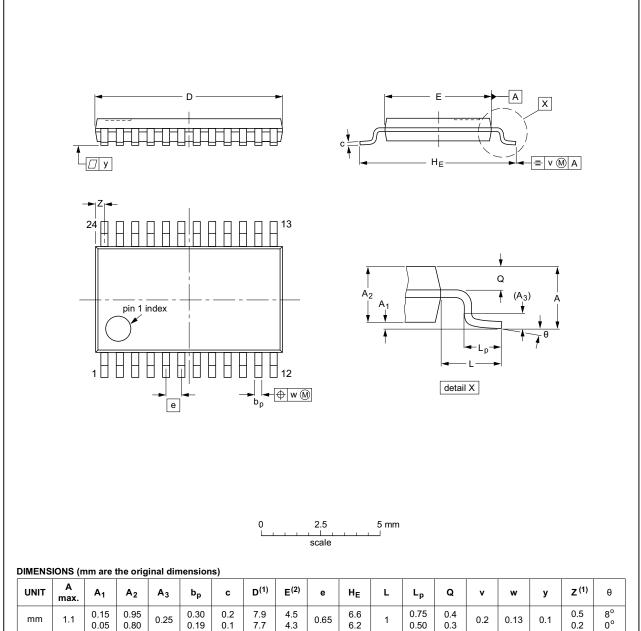

TSSOP24: plastic thin shrink small outline package; 24 leads; body width 4.4 mm

SOT355-1

| UNIT | A<br>max. | A <sub>1</sub> | A <sub>2</sub> | <b>A</b> <sub>3</sub> | bp           | C          | D <sup>(1)</sup> | E <sup>(2)</sup> | е    | HE         | L | Lp           | Q          | v   | w    | у   | Z <sup>(1)</sup> | θ        |

|------|-----------|----------------|----------------|-----------------------|--------------|------------|------------------|------------------|------|------------|---|--------------|------------|-----|------|-----|------------------|----------|

| mm   | 1.1       | 0.15<br>0.05   | 0.95<br>0.80   | 0.25                  | 0.30<br>0.19 | 0.2<br>0.1 | 7.9<br>7.7       | 4.5<br>4.3       | 0.65 | 6.6<br>6.2 | 1 | 0.75<br>0.50 | 0.4<br>0.3 | 0.2 | 0.13 | 0.1 | 0.5<br>0.2       | 8°<br>0° |

#### Notes

- 1. Plastic or metal protrusions of 0.15 mm maximum per side are not included.

- 2. Plastic interlead protrusions of 0.25 mm maximum per side are not included.

| OUTLINE  |     | REFER  | EUROPEAN | ISSUE DATE |            |                                 |

|----------|-----|--------|----------|------------|------------|---------------------------------|

| VERSION  | IEC | JEDEC  | JEITA    |            | PROJECTION | ISSUE DATE                      |

| SOT355-1 |     | MO-153 |          |            |            | <del>99-12-27</del><br>03-02-19 |

Fig 31. Package outline SOT355-1 (TSSOP24)

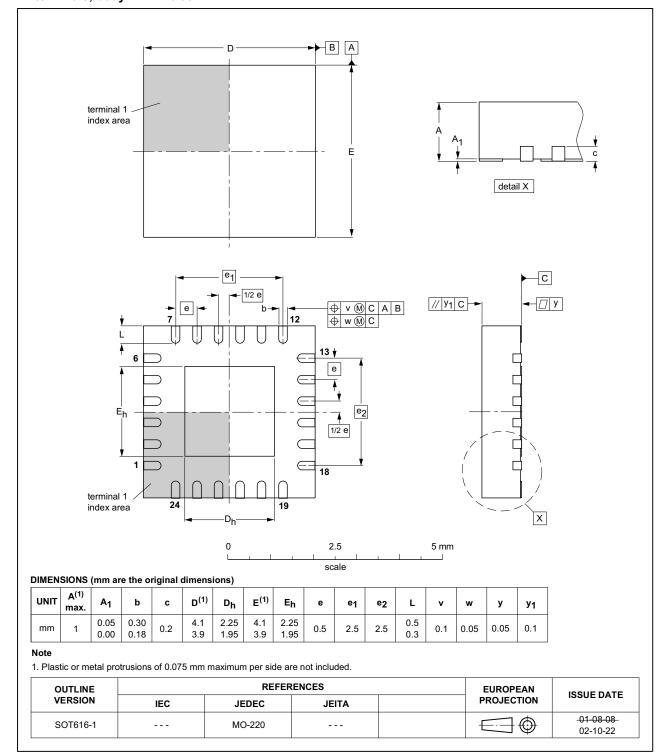

HVQFN24: plastic thermal enhanced very thin quad flat package; no leads; 24 terminals; body  $4 \times 4 \times 0.85$  mm

SOT616-1

Fig 32. Package outline SOT616-1 (HVQFN24)

## 14. Handling information

All input and output pins are protected against ElectroStatic Discharge (ESD) under normal handling. When handling ensure that the appropriate precautions are taken as described in *JESD625-A* or equivalent standards.

## 15. Soldering of SMD packages

This text provides a very brief insight into a complex technology. A more in-depth account of soldering ICs can be found in Application Note *AN10365* "Surface mount reflow soldering description".

#### 15.1 Introduction to soldering

Soldering is one of the most common methods through which packages are attached to Printed Circuit Boards (PCBs), to form electrical circuits. The soldered joint provides both the mechanical and the electrical connection. There is no single soldering method that is ideal for all IC packages. Wave soldering is often preferred when through-hole and Surface Mount Devices (SMDs) are mixed on one printed wiring board; however, it is not suitable for fine pitch SMDs. Reflow soldering is ideal for the small pitches and high densities that come with increased miniaturization.

#### 15.2 Wave and reflow soldering

Wave soldering is a joining technology in which the joints are made by solder coming from a standing wave of liquid solder. The wave soldering process is suitable for the following:

- Through-hole components

- Leaded or leadless SMDs, which are glued to the surface of the printed circuit board

Not all SMDs can be wave soldered. Packages with solder balls, and some leadless packages which have solder lands underneath the body, cannot be wave soldered. Also, leaded SMDs with leads having a pitch smaller than ~0.6 mm cannot be wave soldered, due to an increased probability of bridging.

The reflow soldering process involves applying solder paste to a board, followed by component placement and exposure to a temperature profile. Leaded packages, packages with solder balls, and leadless packages are all reflow solderable.

Key characteristics in both wave and reflow soldering are:

- Board specifications, including the board finish, solder masks and vias

- Package footprints, including solder thieves and orientation

- · The moisture sensitivity level of the packages

- Package placement

- Inspection and repair

- Lead-free soldering versus SnPb soldering

#### 15.3 Wave soldering

Key characteristics in wave soldering are:

- Process issues, such as application of adhesive and flux, clinching of leads, board transport, the solder wave parameters, and the time during which components are exposed to the wave

- Solder bath specifications, including temperature and impurities

#### 15.4 Reflow soldering

Key characteristics in reflow soldering are:

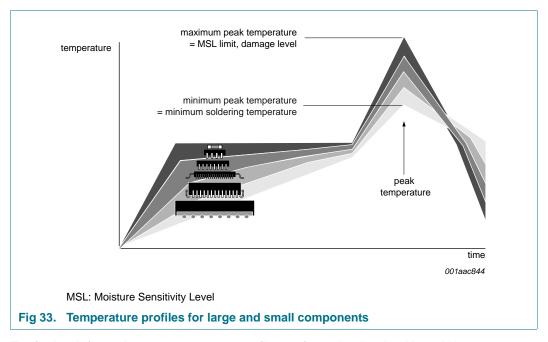

- Lead-free versus SnPb soldering; note that a lead-free reflow process usually leads to higher minimum peak temperatures (see <u>Figure 33</u>) than a SnPb process, thus reducing the process window

- Solder paste printing issues including smearing, release, and adjusting the process window for a mix of large and small components on one board

- Reflow temperature profile; this profile includes preheat, reflow (in which the board is heated to the peak temperature) and cooling down. It is imperative that the peak temperature is high enough for the solder to make reliable solder joints (a solder paste characteristic). In addition, the peak temperature must be low enough that the packages and/or boards are not damaged. The peak temperature of the package depends on package thickness and volume and is classified in accordance with Table 18 and 19

Table 18. SnPb eutectic process (from J-STD-020D)

| Package thickness (mm) | Package reflow temperature (°C) |       |  |  |  |  |  |

|------------------------|---------------------------------|-------|--|--|--|--|--|

|                        | Volume (mm³)                    |       |  |  |  |  |  |

|                        | < 350                           | ≥ 350 |  |  |  |  |  |

| < 2.5                  | 235                             | 220   |  |  |  |  |  |

| ≥ 2.5                  | 220                             | 220   |  |  |  |  |  |

Table 19. Lead-free process (from J-STD-020D)

| Package thickness (mm) | Package reflow temperature (°C)  Volume (mm³) |             |        |

|------------------------|-----------------------------------------------|-------------|--------|

|                        |                                               |             |        |

|                        | < 350                                         | 350 to 2000 | > 2000 |

| < 1.6                  | 260                                           | 260         | 260    |

| 1.6 to 2.5             | 260                                           | 250         | 245    |

| > 2.5                  | 250                                           | 245         | 245    |

Moisture sensitivity precautions, as indicated on the packing, must be respected at all times.

Studies have shown that small packages reach higher temperatures during reflow soldering, see Figure 33.

For further information on temperature profiles, refer to Application Note *AN10365* "Surface mount reflow soldering description".

## 16. Soldering: PCB footprints

Fig 34. PCB footprint for SOT137-1 (SO24); reflow soldering

Fig 35. PCB footprint for SOT355-1 (TSSOP24); reflow soldering

Fig 36. PCB footprint for SOT616-1 (HVQFN24); reflow soldering

## 17. Abbreviations

Table 20. Abbreviations

| Acronym              | Description                                |

|----------------------|--------------------------------------------|

| ACPI                 | Advanced Configuration and Power Interface |

| CBT                  | Cross-Bar Technology                       |

| CDM                  | Charged-Device Model                       |

| CMOS                 | Complementary Metal-Oxide Semiconductor    |

| ESD                  | ElectroStatic Discharge                    |

| FET                  | Field-Effect Transistor                    |

| FF                   | Flip-Flop                                  |

| GPIO                 | General Purpose Input/Output               |

| НВМ                  | Human Body Model                           |

| I <sup>2</sup> C-bus | Inter-Integrated Circuit bus               |

| I/O                  | Input/Output                               |

| LED                  | Light Emitting Diode                       |

| SMBus                | System Management Bus                      |

## 18. Revision history

Table 21. Revision history

| Document ID                     | Release date                                        | Data sheet status                                                                                           | Change notice      | Supersedes                                            |

|---------------------------------|-----------------------------------------------------|-------------------------------------------------------------------------------------------------------------|--------------------|-------------------------------------------------------|

| PCA9539_PCA9539R v.9            | 20171108                                            | Product data sheet                                                                                          | 2017100021         | PCA9539_PCA9539R v.8.2                                |

| Modifications:                  | PCA9539R                                            | Static characteristics for all de<br>PW/Q900", Table 15 "Static (<br>PW/Q900", : Corrected V <sub>POF</sub> | characteristics fo | r PCA9539PW/Q900 and                                  |

| PCA9539_PCA9539R v.8.2          | 20161123                                            | Product data sheet                                                                                          | -                  | PCA9539_PCA9539R v.8.1                                |

| Modifications:                  | Added PCA                                           | A9539RPW/Q900 to Figure 6                                                                                   | "Pin configuration | on for TSSOP24"                                       |

|                                 | <ul> <li><u>Table 16 "E</u><br/>PCA9539R</li> </ul> | Oynamic characteristics", t <sub>w(rs</sub><br>PW/Q900                                                      | t): added AC para  | ameters for                                           |

| PCA9539_PCA9539R v.8.1          | 20161123                                            | Product data sheet                                                                                          | -                  | PCA9539_PCA9539R v.8                                  |

| Modifications:                  | Added PCA                                           | A9539RPW/Q900                                                                                               |                    |                                                       |

| PCA9539_PCA9539R v.8            | 20141126                                            | Product data sheet                                                                                          | -                  | PCA9539_PCA9539R v.7                                  |

| Modifications:                  | updated I <sub>O</sub>                              | Static characteristics for PCAS<br>L and V <sub>OH</sub> ; changed operatin<br>V to 5.5 V" for PCA9539PW/0  | g power supply v   | nd PCA9539RPW/Q900":<br>oltage range from "5.0 V ± 10 |

| PCA9539_PCA9539R v.7            | 20140415                                            | Product data sheet                                                                                          | -                  | PCA9539_PCA9539R v.6                                  |

| PCA9539_PCA9539R v.6            | 20130206                                            | Product data sheet                                                                                          | -                  | PCA9539_PCA9539R v.5                                  |

| PCA9539_PCA9539R v.5            | 20080728                                            | Product data sheet                                                                                          | -                  | PCA9539_PCA9539R v.4                                  |

| PCA9539_PCA9539R v.4            | 20080519                                            | Product data sheet                                                                                          | -                  | PCA9539 v.3                                           |

| PCA9539 v.3                     | 20060921                                            | Product data sheet                                                                                          | -                  | PCA9539 v.2                                           |

| PCA9539 v.2<br>(9397 750 14048) | 20040930                                            | Product data sheet                                                                                          | -                  | PCA9539 v.1                                           |

#### Table 21. Revision history ... continued

| Document ID                     | Release date |                    | Change notice | Supersedes |

|---------------------------------|--------------|--------------------|---------------|------------|

| PCA9539 v.1<br>(9397 750 12898) | 20040827     | Product data sheet | -             | -          |

### 19. Legal information

#### 19.1 Data sheet status

| Document status[1][2]          | Product status[3] | Definition                                                                            |

|--------------------------------|-------------------|---------------------------------------------------------------------------------------|

| Objective [short] data sheet   | Development       | This document contains data from the objective specification for product development. |

| Preliminary [short] data sheet | Qualification     | This document contains data from the preliminary specification.                       |

| Product [short] data sheet     | Production        | This document contains the product specification.                                     |

- [1] Please consult the most recently issued document before initiating or completing a design.

- [2] The term 'short data sheet' is explained in section "Definitions"

- [3] The product status of device(s) described in this document may have changed since this document was published and may differ in case of multiple devices. The latest product status information is available on the Internet at URL <a href="http://www.nxp.com">http://www.nxp.com</a>.

#### 19.2 Definitions

**Draft** — The document is a draft version only. The content is still under internal review and subject to formal approval, which may result in modifications or additions. NXP Semiconductors does not give any representations or warranties as to the accuracy or completeness of information included herein and shall have no liability for the consequences of use of such information.

Short data sheet — A short data sheet is an extract from a full data sheet with the same product type number(s) and title. A short data sheet is intended for quick reference only and should not be relied upon to contain detailed and full information. For detailed and full information see the relevant full data sheet, which is available on request via the local NXP Semiconductors sales office. In case of any inconsistency or conflict with the short data sheet, the full data sheet shall prevail.

**Product specification** — The information and data provided in a Product data sheet shall define the specification of the product as agreed between NXP Semiconductors and its customer, unless NXP Semiconductors and customer have explicitly agreed otherwise in writing. In no event however, shall an agreement be valid in which the NXP Semiconductors product is deemed to offer functions and qualities beyond those described in the Product data sheet.

#### 19.3 Disclaimers

Limited warranty and liability — Information in this document is believed to be accurate and reliable. However, NXP Semiconductors does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information. NXP Semiconductors takes no responsibility for the content in this document if provided by an information source outside of NXP Semiconductors.

In no event shall NXP Semiconductors be liable for any indirect, incidental, punitive, special or consequential damages (including - without limitation - lost profits, lost savings, business interruption, costs related to the removal or replacement of any products or rework charges) whether or not such damages are based on tort (including negligence), warranty, breach of contract or any other legal theory.

Notwithstanding any damages that customer might incur for any reason whatsoever, NXP Semiconductors' aggregate and cumulative liability towards customer for the products described herein shall be limited in accordance with the *Terms and conditions of commercial sale* of NXP Semiconductors.

Right to make changes — NXP Semiconductors reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof.

Suitability for use — NXP Semiconductors products are not designed, authorized or warranted to be suitable for use in life support, life-critical or safety-critical systems or equipment, nor in applications where failure or malfunction of an NXP Semiconductors product can reasonably be expected to result in personal injury, death or severe property or environmental damage. NXP Semiconductors and its suppliers accept no liability for inclusion and/or use of NXP Semiconductors products in such equipment or applications and therefore such inclusion and/or use is at the customer's own risk.

**Applications** — Applications that are described herein for any of these products are for illustrative purposes only. NXP Semiconductors makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

Customers are responsible for the design and operation of their applications and products using NXP Semiconductors products, and NXP Semiconductors accepts no liability for any assistance with applications or customer product design. It is customer's sole responsibility to determine whether the NXP Semiconductors product is suitable and fit for the customer's applications and products planned, as well as for the planned application and use of customer's third party customer(s). Customers should provide appropriate design and operating safeguards to minimize the risks associated with their applications and products.

NXP Semiconductors does not accept any liability related to any default, damage, costs or problem which is based on any weakness or default in the customer's applications or products, or the application or use by customer's third party customer(s). Customer is responsible for doing all necessary testing for the customer's applications and products using NXP Semiconductors products in order to avoid a default of the applications and the products or of the application or use by customer's third party customer(s). NXP does not accept any liability in this respect.

Limiting values — Stress above one or more limiting values (as defined in the Absolute Maximum Ratings System of IEC 60134) will cause permanent damage to the device. Limiting values are stress ratings only and (proper) operation of the device at these or any other conditions above those given in the Recommended operating conditions section (if present) or the Characteristics sections of this document is not warranted. Constant or repeated exposure to limiting values will permanently and irreversibly affect the quality and reliability of the device.