INTEGRATED CIRCUITS

Product Specification (Rev. 1998 Apr 20)

printed 1998 Apr 20

### **PCF7991AT**

### CONTENTS

| 1            | FEATURES                                 |

|--------------|------------------------------------------|

| 2            | GENERAL DESCRIPTION                      |

| 3            | ORDERING INFORMATION                     |

| 4            | BLOCK DIAGRAM                            |

| 5            | QUICK REFERENCE DATA                     |

| 6            | PINNING INFORMATION                      |

| 6.1          | Pinning Diagram                          |

| 6.2          | Pin Description                          |

| 7            | MINIMUM APPLICATION CIRCUITRY            |

| 8            | FUNCTIONAL DESCRIPTION                   |

| 8.1          | Power Supply                             |

| 8.2          | Antenna driver                           |

| 8.3          | Modulator                                |

| 8.4<br>8.5   | Oscillator<br>Receiver                   |

| 8.5.1        | Synchron Demodulator                     |

| 8.5.2        | Bandpass Filter, Amplifier and Digitizer |

| 8.5.3        | Phase Measurement                        |

| 8.5.4        | Determining the Sampling Time            |

| 8.5.5        | Data Amplitude Comparison                |

| 8.5.6<br>8.6 | System Diagnostics<br>Power-on reset     |

| 8.7          | Power-down modes                         |

| 8.8          | Serial Interface                         |

| 8.8.1        | Serial Interface Mode                    |

| 9            | COMMAND SET                              |

| 9.1          | READ_TAG                                 |

| 9.2          | WRITE_TAG_N                              |

| 9.3<br>9.4   | WRITE_TAG<br>READ_PHASE                  |

| 9.4<br>9.5   | SET_SAMPLING_TIME                        |

| 9.6          | GET_SAMPLING_TIME                        |

| 9.7          | SET_CONFIG_PAGE                          |

| 9.8          | GET_CONFIG_PAGE                          |

| 10           | LIMITING VALUES                          |

| 11           | DC CHARACTERISTICS                       |

| 12           | AC CHARACTERISTICS                       |

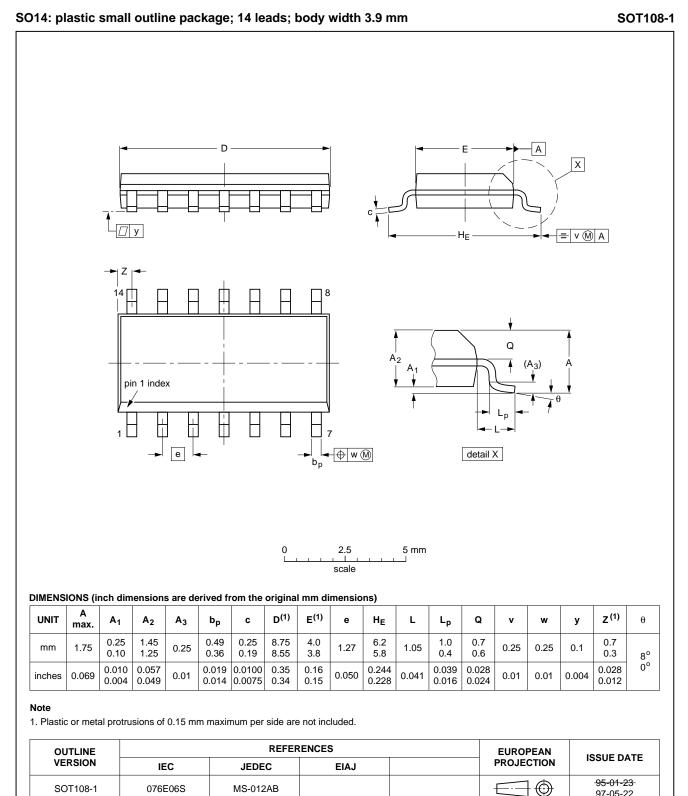

| 13           | PACKAGE                                  |

| 14           | DEFINITIONS                              |

| 15           | LIFE SUPPORT APPLICATIONS                |

### PCF7991AT

### 1 FEATURES

- Fully integrated single chip basestation

- Compatible with PCF79xx transponder family

- Robust antenna coil power driver stage with modulator

- High performance adaptive sampling time AM/PM demodulator (patent pending)

- · Read and write function

- · Programmable modulator/demodulator characteristics

- On-chip clock oscillator and divider in the case of external clock reference

- Antenna rupture and short circuit detection

- Low power consumption

- Very low power stand-by mode

- Low external component count

- Small package (SO14).

### 2 GENERAL DESCRIPTION

The PCF7991AT is a fully integrated Advanced Basestation IC, ABIC, designed for car immobilizer systems providing read and write access to an identification transponder. The device is intended for use with the Philips transponder family (PCF79xx) as well as other transponder types operating at 125 kHz and employing ASK, Amplitude Shift Keying for write and AM/PM for the read operation. The receiver characteristics (amplifier gain, filter cutoff frequencies) can be optimized to system and transponder requirements. The PCF7991AT IC is designed for easy integration into immobilizer read/write and read-only systems featuring a high degree of integration and very low external component count. The device integrates a powerful antenna driver/modulator, a low-noise adaptive sampling time demodulator, programmable filters/amplifier and digitizer, required to design high-performance basestations. A three wire microcontroller interface is provided for programming the PCF7991AT as well as for the bidirectional communication with the transponder. The three-wire interface can be configured for two wire operation by connecting the data input and the data output.

The device employs a unique Adaptive Sampling Time (AST) demodulation technique, that extends the system operation range and eliminates the effect of a zero amplitude modulation response from the transponder, as a result of resonance frequency tolerances.

### **3 ORDERING INFORMATION**

| EXTENDED       |      | PACKAGE                                 |          | TEMPERATURE |

|----------------|------|-----------------------------------------|----------|-------------|

| TYPE NUMBER    | NAME | DESCRIPTION                             | VERSION  | RANGE (°C)  |

| PCF7991AT/1081 | SO14 | plastic small outline package; 14 leads | SOT108-1 | -40 to +85  |

# PCF7991AT

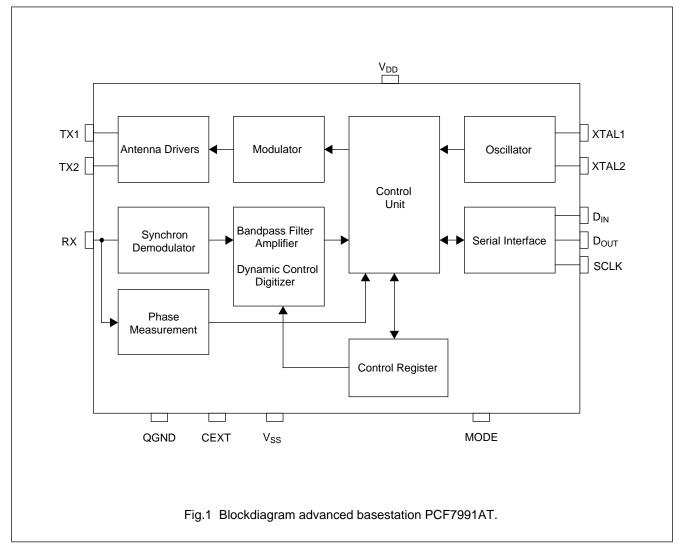

### 4 BLOCK DIAGRAM

### 5 QUICK REFERENCE DATA

| DADAMETER                                                         |                 | VALUE            |                  |  |  |  |

|-------------------------------------------------------------------|-----------------|------------------|------------------|--|--|--|

| PARAMETER                                                         | MIN.            | MAX.             | UNIT             |  |  |  |

| Supply voltage                                                    | 4.5             | 5.5              | V                |  |  |  |

| Power-down current                                                |                 | 20               | μA               |  |  |  |

| Clock/Oscillator frequency<br>(antenna carrier frequency 125 kHz) | 4               | 16               | MHz              |  |  |  |

| Antenna driver current                                            |                 | 400              | mA <sub>p</sub>  |  |  |  |

| Receiver sensitivity                                              | 2               |                  | mV <sub>pp</sub> |  |  |  |

| Serial interface                                                  | CMOS compatible |                  |                  |  |  |  |

| Package                                                           | SO14            |                  |                  |  |  |  |

| Operation temperature range                                       |                 | –40 °C to +85 °C |                  |  |  |  |

# PCF7991AT

### 6 PINNING INFORMATION

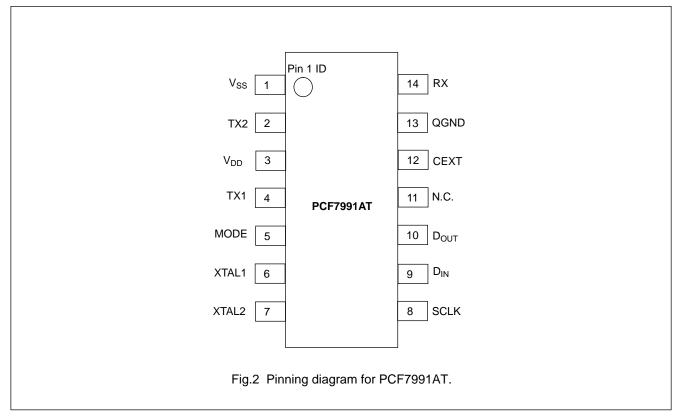

### 6.1 Pinning Diagram

### 6.2 Pin Description

Table 1

Pin description for PCF7991AT

| SYMBOL           | PIN | DESCRIPTION                                           |

|------------------|-----|-------------------------------------------------------|

| V <sub>SS</sub>  | 1   | Common ground, GND.                                   |

| TX2              | 2   | Antenna driver output.                                |

| V <sub>DD</sub>  | 3   | Supply voltage input, stabilized.                     |

| TX1              | 4   | Antenna driver output.                                |

| MODE             | 5   | Microcontroller interface mode select.                |

| XTAL1            | 6   | Oscillator interface, external clock reference input. |

| XTAL2            | 7   | Oscillator interface.                                 |

| SCLK             | 8   | Microcontroller interface: serial clock input.        |

| D <sub>IN</sub>  | 9   | Microcontroller interface: serial data in.            |

| D <sub>OUT</sub> | 10  | Microcontroller interface: serial data out.           |

| N.C.             | 11  | Not connected.                                        |

| CEXT             | 12  | High pass filter decoupling.                          |

| QGND             | 13  | Analog ground bias.                                   |

| RX               | 14  | Receiver input.                                       |

PCF7991AT

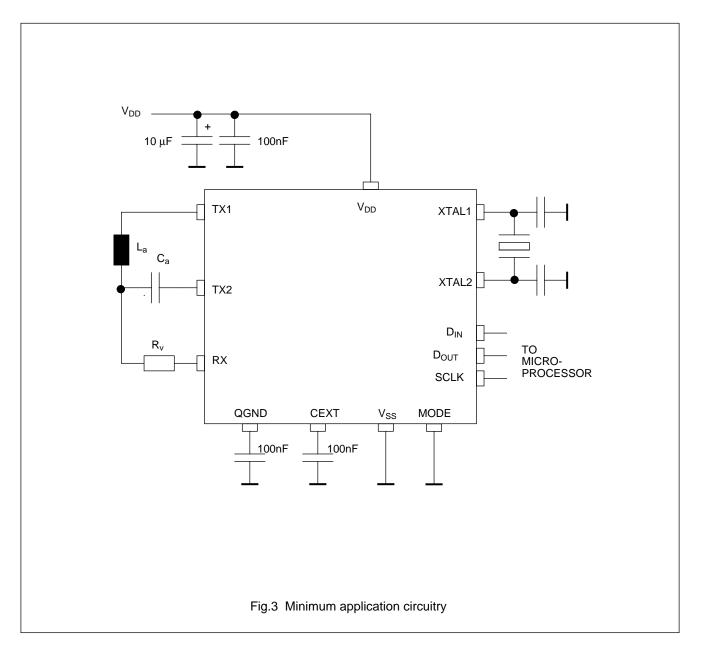

### 7 MINIMUM APPLICATION CIRCUITRY

The following figure shows a minimal application circuitry for the PCF7991AT. The antenna coil  $L_a$  together with the capacitor  $C_a$  form a series resonant LC circuit (f = 125 kHz). The antenna tap voltage is attenuated by  $R_V$  and the input impedance of the RX-pin. The capacitors at XTAL1 and XTAL2 are selected according to the crystal or ceramic resonator specification. In the case of an external clock reference they may be omitted. The capacitors at QGND and CEXT are for device internal biasing and decoupling purposes.

### PCF7991AT

#### 8 FUNCTIONAL DESCRIPTION

#### 8.1 Power Supply

The PCF7991AT operates from an external 5 V power supply. For optimum performance a stabilized supply voltage should be applied.

#### 8.2 Antenna driver

The antenna drivers are configured as a full bridge capable to deliver a square wave shaped voltage to the series resonant antenna circuit, which is connected between TX1 and TX2. The full bridge drivers are characterized by a low output impedance featuring a large drive voltage to the resonant antenna circuit. The antenna carrier frequency is 125 kHz typically.

#### 8.3 Modulator

The modulator enables ASK (Amplitude Shift Keying) modulation of the antenna RF signal after switching the device into transparent mode (WRITE\_TAG mode) by a WRITE\_TAG or WRITE\_TAG\_N command (see Table 2). ASK modulation is achieved by blanking the antenna drive signal under control of the data input ( $D_{IN}$ ). The modulator features a timer circuitry that supports carrier blanking with a programmable duration (see Table 2).

### 8.4 Oscillator

The on-chip oscillator operates either with a crystal or ceramic resonator connected to XTAL1/2. Alternatively, an external clock source (CMOS compatible) may be applied at XTAL1. The oscillator frequency feeds a programmable divider in order to derive the system clock and the antenna carrier frequency of 125 kHz. The programmable divider supports an oscillator frequency of 4, 8, 12 and 16 MHz (see Table 11).

### 8.5 Receiver

The receiver senses and demodulates the absorption modulation applied by a transponder that is inside the antenna RF field. The demodulated and digitized signal is available at the data output ( $D_{OUT}$ ) after switching the device into transparent mode (READ\_TAG mode) by a READ\_TAG command (see Table 2).

The receiver features a high sensitivity and an extended input voltage range to ensure a large receiver dynamic range. The antenna tap signal is fed to the receiver input (RX) after attenuation by means of an external series resistor ( $R_V$ ) and the receiver input impedance ( $R_{IRX}$ ) in

order to match the receiver input voltage specification. The receive signal passes an on-chip second order low pass filter and is further attenuated before it is fed to the synchron demodulator and phase measurement circuitry.

#### 8.5.1 SYNCHRON DEMODULATOR

The antenna current and therefore the tap voltage is modulated by the transponder in amplitude and/or phase depending on various system parameters. By employing a unique Adaptive Sampling Time (AST) demodulation technique, amplitude and phase modulation of the receive signal is detected featuring an extended system operation range. The receive sampling time is set by the SET\_SAMPLING\_TIME command (see Table 2). The appropriate sampling time can be derived from an on-chip phase measurement and an offset that accounts for the external antenna interface component values.

Receive signal sampling is inhibited when a WRITE\_TAG or WRITE\_TAG\_N command is issued in order to avoid that write pulses de-sensitize the amplifier and digitizer circuitry. Signal sampling is resumed when the WRITE\_TAG mode is terminated. For better receiver setting a short delay after the last write pulse has to be provided before the WRITE\_TAG mode is terminated.

#### 8.5.2 BANDPASS FILTER, AMPLIFIER AND DIGITIZER

After demodulation the receive signal passes a baseband filter and amplifier prior to digitization. The amplifier gain and bandpass filter cutoff frequencies are adjustable by the SET\_CONFIG\_PAGE 0 command, in order to adapt the receiver path to the system coupling factor and transponder data rate.

For fast receiver settling after device power-up, sampling time shift or when switching from WRITE\_TAG mode to READ\_TAG mode the bandpass filter, amplifier and digitizer circuit biasing condition can be initialized and restored by a set of control bits accessible via the SET\_CONFIG\_PAGE commands.

#### 8.5.3 PHASE MEASUREMENT

The optimum receive signal sampling time depends on the actual tuning condition of the resonant antenna circuitry. The actual tuning condition of the resonance antenna is determined by measuring the phase relationship between the exciting signal at the antenna driver output and the antenna tap voltage applied to the receiver input. In case of perfect tuning, the phase should be 90 degree plus an offset that accounts for the receiver input attenuation and

### PCF7991AT

low pass filter. Miss-tuning of the resonance antenna circuit by component spreads or due to ambient temperature changes results in a change of the phase relationship. The actual phase relationship is determined by a READ\_PHASE command (see Table 6) and used to calculate the optimum receive signal sampling time with support of an external microcontroller.

#### 8.5.4 DETERMINING THE SAMPLING TIME

Measurement, calculation and setting of the sampling time is typically implemented during system power-up initialization when the transponder is also in its power-up sequence not sending any data. As soon as the oscillator and resonance antenna circuit are settled a phase measurement is initiated and the sampling time determined according to the following relation:

$T_S = 2 * T_{ANT} + T_{OFFSET}$

| T <sub>S</sub> | Receive signal sampling time |

|----------------|------------------------------|

| 0              |                              |

T<sub>ANT</sub> Actual phase measurement

T<sub>OFFSET</sub> Offset that accounts for the phase shift due to the antenna tap voltage attenuation and low pass filtering

After setting the sampling time the receiver has to settle before data can be demodulated and digitized properly.

#### 8.5.5 DATA AMPLITUDE COMPARISON

For advanced receiver sampling time optimization the demodulated data signal strength can be weighted by amplitude comparison and the result reported in the status bit AMPCOMP (see Table 13).

When the ACQAMP control bit (see Table 10) is set by a SET\_CONFIG\_PAGE command, the actual demodulated data signal amplitude is stored as reference. After resetting the ACQAMP control bit the status bit AMPCOMP is set, when the actual data signal amplitude is larger than the stored reference otherwise it is cleared.

### 8.5.6 SYSTEM DIAGNOSTICS

In order to detect an antenna short or open condition the receiver input voltage at the RX-pin is monitored and an antenna fail condition is reported in the status bit ANTFAIL, (see Table 13). If the receiver input voltage does not exceed the diagnostic threshold level  $V_{DTH}$  (see Chapter 11), the status bit ANTFAIL is set, otherwise it is cleared. The status bit is updated once per antenna carrier period and can be read by a GET\_CONFIG\_Page 2 or 3 command (see Table 13). The status bit is undefined in Power-down or Idle mode, during the oscillator start-up

time and when the antenna drivers are disabled. Advanced system diagnostics are feasible by considering the phase measurement information also.

#### 8.6 Power-on reset

The device generates an internal power-on reset to initialize the chip after power-on or power fail condition. As a result the control register is initialized according to Table 11.

#### 8.7 Power-down modes

After a power-on reset condition the device operates in ACTIVE mode. The PCF7991AT supports an Idle and Power-down mode for power saving means. The mode of operation is determined by control bits addressed by an SET\_CONFIG\_PAGE 1 command (see Table 10).

In Idle mode only the oscillator and a minimum of other circuitry is active. In Power-down mode the device is in OFF state completely. The serial interface is operational in any case in order to provide access to the control register.

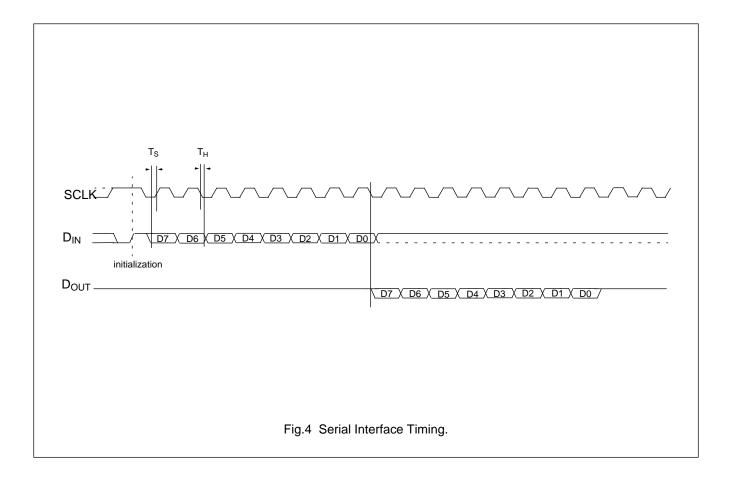

#### 8.8 Serial Interface

The communication between the PCF7991AT and the microcontroller is done via a three wire digital interface. The interface is used to issue commands for writing and reading of device configuration data and for writing and reading to the transponder in one of the transparent modes (READ\_TAG, WRITE\_TAG). Device configuration is stored in a control register with read back feature.

The interface is operated by the following signals:

| SCLK             | Clock       |

|------------------|-------------|

| D <sub>IN</sub>  | Data Input  |

| D <sub>OUT</sub> | Data Output |

SCLK and  $\mathsf{D}_{\mathsf{IN}}$  are realized as Schmitt-Trigger inputs.  $\mathsf{D}_{\mathsf{OUT}}$  is an open drain output with internal pullup resistor.

Any communication between the PCF7991AT and the microcontroller begins with an initialization of the serial interface before the desired command can be issued. The interface initialization condition is a low-to-high transition of the signal  $D_{IN}$  while SCLK is high (see Fig.4).

All commands are transmitted to the PCF7991AT serial interface starting with Most Significant Bit (MSB).  $D_{IN}$  is latched with a high state at SCLK.  $D_{OUT}$  is valid during the high state of SCLK (MODE pin connected to  $V_{SS}$ ).

$\mathsf{D}_{\mathsf{OUT}}$  and  $\mathsf{D}_{\mathsf{IN}}$  may be connected to each other in order to form a two wire communication link with the microcontroller.

### PCF7991AT

#### 8.8.1 SERIAL INTERFACE MODE

The serial interfaces supports two modes of operation, filtered and non-filtered communication.

If MODE is connected to  $V_{SS}$  no filtering is applied and the state of the interface signals is directly available at the internal circuitry. The maximum data rate of the serial interface is limited by the set-up and hold time as specified (see Chapter 12).

If MODE is connected to V<sub>DD</sub>, digital filtering of SCLK and D<sub>IN</sub> is performed offering improved immunity against glitches on these interface signals. This mode of operation is intended for use for so called 'Active Antenna Applications', where the PCF7991AT and the microcontroller have to communicate via long interface wires. The digital filtering is provided by sampling the SCLK and D<sub>IN</sub> inputs at a rate of 1/f<sub>TX</sub>, 8  $\mu$ s typically. The

internal state of these signals is updated only, if two successive samples are equal. Due to the sampling operation a state change at the SCLK or D<sub>IN</sub> input is delayed at least by 16  $\mu$ s before it is recognized by the internal circuitry. If D<sub>IN</sub> and D<sub>OUT</sub> are connected to each other to form a two wire communication link, the filtering delay between D<sub>IN</sub> and D<sub>OUT</sub> must be considered. Due to the digital filtering, the maximum serial interface data rate is limited to approximately 30 kbit/sec.

If digital filtering of SCLK and  $D_{IN}$  is enabled and the device has been forced into Power-down mode, this mode can be terminated by setting SCLK to LOW and  $D_{IN}$  unequal to the status bit TXDIS (see Table 10). As a result the XTAL oscillator is restarted and the configuration bit PD\_MODE is cleared, which causes the device to enter Idle mode.

### PCF7991AT

#### 9 COMMAND SET

Table 2Command set summary

| COMMAND NAME      | MSB |   |    | BIT | NO. | LSB | RESPONSE |    |                                                      |

|-------------------|-----|---|----|-----|-----|-----|----------|----|------------------------------------------------------|

|                   | 7   | 6 | 5  | 4   | 3   | 2   | 1        | 0  | RESPONSE                                             |

| GET_SAMPLING_TIME | 0   | 0 | 0  | 0   | 0   | 0   | 1        | 0  | 8 bit (0 0 D5-D0)                                    |

| GET_CONFIG_PAGE   | 0   | 0 | 0  | 0   | 0   | 1   | P1       | P0 | 8 bit (X3 X2 X1 X0 D3-D0)                            |

| READ_PHASE        | 0   | 0 | 0  | 0   | 1   | 0   | 0        | 0  | 8 bit (0 0 D5 - D0)                                  |

| READ_TAG          | 1   | 1 | 1  | _   | _   | _   | _        | _  | enter READ_TAG-mode                                  |

| WRITE_TAG_N       | 0   | 0 | 0  | 1   | N3  | N2  | N1       | N0 | enter WRITE_TAG-mode with pulse<br>width programming |

| WRITE_TAG         | 1   | 1 | 0  | _   | _   | _   | _        | _  | enter WRITE_TAG-mode                                 |

| SET_CONFIG_PAGE   | 0   | 1 | P1 | P0  | D3  | D2  | D1       | D0 | 4 bit per config page addressed                      |

| SET_SAMPLING_TIME | 1   | 0 | D5 | D4  | D3  | D2  | D1       | D0 | 8 bit (00 D5 - D0)                                   |

#### 9.1 READ\_TAG

This command is used to read the demodulated bit stream from a transponder: After the assertion of the three command bits the PCF7991AT instantaneously switches to READ\_TAG-mode and the demodulated, filtered and digitized data from the transponder is available at the data output  $D_{OUT}$  for decoding by the microcontroller.

READ\_TAG-mode is terminated immediately by a low to high transition at SCLK.

Table 3

READ\_TAG command sequence

| BIT NO. | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | REMARK                               |

|---------|---|---|---|---|---|---|---|---|--------------------------------------|

| Command | 1 | 1 | 1 | — | - | - | - | - | received data available at $D_{OUT}$ |

### 9.2 WRITE\_TAG\_N

This command is used to write data to a transponder and to set the modulator blanking characteristics.

If N3-N0 are set to zero, the signal from  $D_{IN}$  is transparently switched to the drivers. A high level at  $D_{IN}$  corresponds to antenna drivers switched off, a low level corresponds to antenna drivers switched on.

If any binary number between 1 and 1111 is loaded into N3-N0, the drivers are switched off at the next positive transition of  $D_{IN}$ . The driver off state is maintained for a time interval equal to N \* T0 (T0=8  $\mu$ s) regardless the state of  $D_{IN}$ . This method relaxes the timing resolution requirements to the microcontroller and to the software implementation while providing an exact, selectable write pulse timing.

WRITE\_TAG-mode is terminated immediately by a low to high transition at SCLK. As a result, the driver resume their initial state, regardless the actual state of the modulation pulse timer.

Table 4

WRITE\_TAG\_N command sequence

| BIT NO. | 7 | 6 | 5 | 4 | 3  | 2  | 1  | 0  | REMARK      |

|---------|---|---|---|---|----|----|----|----|-------------|

| Command | 0 | 0 | 0 | 1 | N3 | N2 | N1 | N0 | no response |

### PCF7991AT

#### 9.3 WRITE\_TAG

This is the 3 bit short form of the command WRITE\_TAG\_N. It allows to switch into WRITE\_TAG-mode with a minimum communication time.

The behaviour of the WRITE\_TAG command is identical to WRITE\_TAG\_N with two exceptions:

WRITE\_TAG-mode is entered after assertion of the 3rd command bit.

No N parameter is specified with this command; instead the N value which has been programmed with the most recent WRITE\_TAG\_N command is used. If no WRITE\_TAG\_N was issued so far, a default N=0 (transparent mode) will be assumed.

WRITE\_TAG-mode is terminated immediately by a low to high transition at SCLK. As a result, the driver resume their initial state, regardless the actual state of the modulation pulse timer.

Table 5

WRITE\_TAG command sequence

| BIT NO. | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | REMARK      |

|---------|---|---|---|---|---|---|---|---|-------------|

| Command | 1 | 1 | 0 |   | _ | _ |   | _ | no response |

#### 9.4 READ\_PHASE

This command is used to read the antenna's phase T<sub>ANT</sub>, which is measured at every carrier cycle. The phase is coded binary in D5-D0.

| Table 6 | READ_PHASE command sequence |

|---------|-----------------------------|

|---------|-----------------------------|

| BIT NO.  | 7 | 6 | 5  | 4  | 3  | 2  | 1  | 0  | REMARK |

|----------|---|---|----|----|----|----|----|----|--------|

| Command  | 0 | 0 | 0  | 0  | 1  | 0  | 0  | 0  |        |

| Response | 0 | 0 | D5 | D4 | D3 | D2 | D1 | D0 |        |

#### 9.5 SET\_SAMPLING\_TIME

This command specifies the demodulator sampling time Ts. The sampling time is coded binary in D5-D0.

Table 7

SET\_SAMPLING\_TIME command sequence

| BIT NO. | 7 | 6 | 5  | 4  | 3  | 2  | 1  | 0  | REMARK      |

|---------|---|---|----|----|----|----|----|----|-------------|

| Command | 1 | 0 | D5 | D4 | D3 | D2 | D1 | D0 | no response |

### PCF7991AT

#### 9.6 GET\_SAMPLING\_TIME

This command is used to read back the sampling time Ts set with SET\_SAMPLING\_TIME. The sampling time is coded binary in D5-D0.

| Table 8 | GET_SAMPLING_TIME command sequence |

|---------|------------------------------------|

|---------|------------------------------------|

| BIT NO.  | 7 | 6 | 5  | 4  | 3  | 2  | 1  | 0  | REMARK |

|----------|---|---|----|----|----|----|----|----|--------|

| Command  | 0 | 0 | 0  | 0  | 0  | 0  | 1  | 0  |        |

| Response | 0 | 0 | D5 | D4 | D3 | D2 | D1 | D0 |        |

#### 9.7 SET\_CONFIG\_PAGE

This command is used to configure the receiver characteristics (cutoff frequencies, gain factors) and the different operation modes. P1 and P0 select one of four configuration pages.

| Table 9 | SET_CONFIG | _PAGE command sequence |

|---------|------------|------------------------|

|---------|------------|------------------------|

| BIT NO. | 7 | 6 | 5  | 4  | 3  | 2  | 1  | 0  | REMARK      |

|---------|---|---|----|----|----|----|----|----|-------------|

| Command | 0 | 1 | P1 | P0 | D3 | D2 | D1 | D0 | no response |

### Table 10 SET\_CONFIG\_PAGE mapping

|                   | BIT NO. | P1 | P0 | D3      | D2               | D1         | D0      |

|-------------------|---------|----|----|---------|------------------|------------|---------|

| COMMAND/PAGE NO.  |         |    |    |         |                  |            |         |

| SET_CONFIG_PAGE 0 |         | 0  | 0  | GAIN1   | GAIN0            | FILTERH    | FILTERL |

| SET_CONFIG_PAGE 1 |         | 0  | 1  | PD_MODE | PD               | HYSTERESIS | TXDIS   |

| SET_CONFIG_PAGE 2 |         | 1  | 0  | THRESET | ACQAMP           | FREEZE1    | FREEZE0 |

| SET_CONFIG_PAGE 3 |         | 1  | 1  | DISLP1  | DISSMART<br>COMP | FSEL1      | FSEL0   |

PCF7991AT

| BIT NAME     | DESCRIPTION                                                        | RESET<br>CONDITION |                                                          |

|--------------|--------------------------------------------------------------------|--------------------|----------------------------------------------------------|

| FILTERH      | main low pass cutoff frequency                                     | 0                  | 0: f <sub>L</sub> = 3 kHz; 1: f <sub>L</sub> = 6 kHz     |

| FILTERL      | main high pass cutoff frequency                                    | 0                  | 0: f <sub>H</sub> = 40 Hz; 1: f <sub>H</sub> = 160 Hz    |

| GAIN0        | amplifier_0 gain factor                                            | 0                  | 0: $gain_0 = 16$ ; 1: $gain_0 = 32$                      |

| GAIN1        | amplifier_1 gain factor                                            | 1                  | 0: gain <sub>1</sub> = 6.22; 1: gain <sub>1</sub> = 31.5 |

| TXDIS        | disable antenna driver                                             | 0                  | 0: driver active; 1: driver inactive                     |

| HYSTERESIS   | data comparator hysteresis                                         | 0                  | 0: hysteresis OFF; 1: hysteresis ON                      |

| PD           | Power-down mode enable                                             | 0                  | 0: device active; 1: Power-down mode                     |

| PD_MODE      | select Power-down mode, if PD = 1                                  | 0                  | 0: Idle mode; 1: Power-down mode                         |

| FREEZE0      | receiver characteristics override                                  | 0                  | see Note 1                                               |

| FREEZE1      | receiver characteristics override                                  | 0                  | see Note 1                                               |

| ACQAMP       | store signal amplitude as reference for later amplitude comparison | 0                  | see Section 8.5.5                                        |

| THRESET      | reset threshold generation of digitizer                            | 0                  | see Note 3                                               |

| FSEL0        | clock frequency select LSB                                         | 0                  | see Note 2                                               |

| FSEL1        | clock frequency select MSB                                         | 0                  |                                                          |

| DISSMARTCOMP | disable smart comparator                                           | 0                  | 0: comparator = ON, 1: comparator = OFF                  |

| DISLP1       | disable main low pass                                              | 0                  | 0: low pass = ON, 1: low pass = OFF                      |

#### Table 11 Configuration bit description

#### Note

1. In order to achieve fast receiver settling the amplifier and filter characteristics can temporarily be overridden:

| FREEZE 1 | FREEZE 0 | REMARK                                                                                                                                                            |

|----------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0        | 0        | normal operation according to configuration page 0                                                                                                                |

| 0        | 1        | main low pass is frozen and main high pass is initialized to QGND                                                                                                 |

| 1        | 0        | main low pass is frozen and the time constant of the main high pass is reduced by a factor of 16 for FILTERH = 0 and by a factor of 8 for FILTERH = 1             |

| 1        | 1        | time constant of the main high pass is reduced by a factor of 16 for FILTERH = 0<br>and by a factor of 8 for FILTERH = 1. Second high pass is initialized to QGND |

2. In order to derive an antenna carrier frequency f<sub>TX</sub> of 125 kHz; the clock divider has to be programmed as follows:

| FSEL0 | FSEL1 | OSCILLATOR FREQUENCY |

|-------|-------|----------------------|

| 0     | 0     | 4 MHz                |

| 0     | 1     | 8 MHz                |

| 1     | 0     | 12 MHz               |

| 0     | 1     | 16 MHz               |

3. If the THRESET is set, the threshold generator is disabled and initialized according to the receive signal conditions.

### PCF7991AT

### 9.8 GET\_CONFIG\_PAGE

This command has three functions:

- 1. Reading back the configuration parameters set by SET\_CONFIG\_PAGE command

- 2. Reading back the transmit pulse width programmed with WRITE\_TAG\_N

- 3. Reading the system status information

P1 and P0 select one of four configuration pages. The response (X3 X2 X1 X0 D3 D2 D1 D0) contains the contents of the selected configuration page in its lower nibble. For P = 0 or P = 1 the higher nibble reflects the current setting of N (the transmit pulse width). For P = 2 or P = 3 the system status information is returned in the higher nibble.

Table 12 GET\_CONFIG\_PAGE command sequence

| BIT NO.  | 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0  | REMARK |

|----------|----|----|----|----|----|----|----|----|--------|

| Command  | 0  | 0  | 0  | 0  | 0  | 1  | P1 | P0 |        |

| Response | X3 | X2 | X1 | X0 | D3 | D2 | D1 | D0 |        |

### Table 13 GET\_CONFIG\_PAGE mapping

| COMMAND / PAGE NO.  |    |    | BIT N   | UMBER   |    |    |    |    |

|---------------------|----|----|---------|---------|----|----|----|----|

| COMIMAND / PAGE NO. | 7  | 6  | 5       | 4       | 3  | 2  | 2  | 0  |

| GET_CONFIG_PAGE 0   | N3 | N2 | N1      | N0      | D3 | D2 | D1 | D0 |

| GET_CONFIG_PAGE 1   | N3 | N2 | N1      | N0      | D3 | D2 | D1 | D0 |

| GET_CONFIG_PAGE 2   | 0  | 0  | AMPCOMP | ANTFAIL | D3 | D2 | D1 | D0 |

| GET_CONFIG_PAGE 3   | 0  | 0  | AMPCOMP | ANTFAIL | D3 | D2 | D1 | D0 |

#### Table 14 Status Bit description

| BIT NAME | DESCRIPTION                 |                   |

|----------|-----------------------------|-------------------|

| ANTFAIL  | antenna failure             | see Section 8.5.6 |

| AMPCOMP  | amplitude comparison result | see Section 8.5.5 |

### 10 LIMITING VALUES

Stress above one or more of the limiting values may cause permanent damage to the device. These are stress ratings only and operation of the device at these or at any other conditions above those given in the characteristics sections of this specification is not implied. Exposure to limiting values for extended periods may affect device reliability.

| SYMBOL             | PARAMETER                          | MIN. | MAX.                 | UNIT |

|--------------------|------------------------------------|------|----------------------|------|

| VI                 | input voltage at any PIN except RX | -0.3 | +6.5                 | V    |

| VI                 | input voltage at any PIN except RX | -0.3 | V <sub>DD</sub> +0.3 | V    |

| V <sub>IRX</sub>   | input voltage at RX pin            | -10  | +12                  | V    |

| Tj                 | maximum junction temperature       |      | 140                  | °C   |

| T <sub>store</sub> | storage temperature range          | -65  | +125                 | °C   |

### PCF7991AT

### 11 DC CHARACTERISTICS

All voltages are measured to V<sub>SS</sub>,  $T_{amb} = -40$  to +85°C,  $f_{TX} = 125$  kHz; unless otherwise specified.

| SYMBOL               | PARAMETER                                 | CONDITIONS                                                      | MIN.                 | TYP.                 | MAX.                   | UNIT            |

|----------------------|-------------------------------------------|-----------------------------------------------------------------|----------------------|----------------------|------------------------|-----------------|

| Supply               |                                           |                                                                 |                      | •                    | -                      |                 |

| V <sub>DD</sub>      | supply voltage                            | $V_{DD}$ with respect to $V_{SS}$                               | 4.5                  | 5.0                  | 5.5                    | V               |

| I <sub>ON</sub>      | operating supply current                  | $V_{DD} = 5.5 \text{ V}, \text{ I}_{TX1} = \text{ I}_{TX2} = 0$ |                      | 4.0                  | 10                     | mA              |

| I <sub>ID</sub>      | current in Idle mode                      | V <sub>DD</sub> = 5.5 V; see Note 1                             |                      | 0.2                  | 0.4                    | mA              |

| I <sub>PD</sub>      | current in Power-down mode                | V <sub>DD</sub> = 5.5 V; see Note 1                             |                      | 7.0                  | 20                     | μA              |

| Antenna [            | Driver (TX1, TX2)                         |                                                                 |                      | •                    |                        |                 |

| I <sub>TXCW</sub>    | output peak-current                       | continuous wave                                                 |                      |                      | 200                    | mA <sub>p</sub> |

| I <sub>TXpulse</sub> | output peak-current                       | On/Off-ratio = 1:4<br>t <sub>on</sub> < 400 ms                  |                      |                      | 400                    | mA <sub>p</sub> |

| R <sub>OTX</sub>     | output resistance                         | full bridge, $R_{OTX} = R_{OTX1} + R_{OTX2}$                    |                      | 2.5                  | 7.0                    | Ω               |

| Receiver i           | input (RX)                                |                                                                 |                      | -                    |                        |                 |

| V <sub>IRX</sub>     | input voltage range                       | VIRX with respect to QGND                                       | -8                   |                      | +8                     | Vp              |

| V <sub>QGND</sub>    | analog ground                             |                                                                 | 0.35 V <sub>DD</sub> | 0.42 V <sub>DD</sub> | 0.5 V <sub>DD</sub>    | V               |

| R <sub>IRX</sub>     | impedance input                           |                                                                 | 17                   | 25                   | 33                     | kΩ              |

| V <sub>DTH</sub>     | diagnostic threshold level                | V <sub>DTH</sub> with respect to QGND                           | -1.5                 | -1.15                | -0.8                   | V               |

|                      | out (D <sub>IN</sub> , S <sub>CLK</sub> ) | VDIH with respect to QGIND                                      | -1.5                 |                      | -0.8                   | V               |

| V <sub>IH</sub>      | data input voltage HIGH                   |                                                                 | 0.7 V <sub>DD</sub>  |                      | V <sub>DD</sub> +0.3 V |                 |

| V <sub>IL</sub>      | data input voltage LOW                    |                                                                 | -0.3 V               |                      | 0.3 V <sub>DD</sub>    |                 |

| Digital ou           | tput (D <sub>OUT</sub> )                  |                                                                 |                      |                      |                        |                 |

| V <sub>OL</sub>      | output voltage LOW                        | I <sub>OL max</sub> = +1 mA                                     |                      |                      | 0.4                    | V               |

| I <sub>OL</sub>      | output drive capability                   | $V_{OL} \le 0.4 \text{ V}$                                      | 1                    |                      |                        | mA              |

#### Note

1. Does not include power consumption of XTAL or other external components.

### PCF7991AT

### **12 AC CHARACTERISTICS**

$T_{amb}$  = -40 to +85°C,  $f_{TX}$  = 125 kHz; unless otherwise specified.

| SYMBOL             | PARAMETER                            | CONDITIONS                                  | MIN. | TYP. | MAX.  | UNIT             |

|--------------------|--------------------------------------|---------------------------------------------|------|------|-------|------------------|

| XTAL Osc           | illator (XTAL1, XTAL2)               |                                             | -    |      | -     |                  |

| f <sub>OSC</sub>   | frequency range                      | depending on FSEL                           | 4    |      | 16    | MHz              |

| T <sub>SUP</sub>   | start-up time                        |                                             |      | 4    | 10    | ms               |

| R <sub>FB</sub>    | feedback resistance                  | XTAL1 to XTAL 2                             | 0.5  | 1.3  | 3     | MΩ               |

| External C         | Clock Input (XTAL1)                  |                                             |      |      |       |                  |

| f <sub>EXT</sub>   | frequency range                      | depending on FSEL                           | 4    |      | 16    | MHz              |

|                    | duty cycle                           |                                             | 40   |      | 60    | %                |

| C <sub>XTAL1</sub> | input capacitance                    | XTAL1                                       |      | 5    |       | pF               |

| Serial Inte        | rface                                |                                             |      |      |       |                  |

| T <sub>S</sub>     | set-up time                          | MODE pin at V <sub>SS</sub>                 | 50   |      |       | ns               |

| T <sub>H</sub>     | hold time                            | MODE pin at V <sub>SS</sub>                 | 50   |      |       | ns               |

| Receiver           |                                      |                                             | •    |      |       |                  |

| V <sub>RX</sub>    | receiver sensitivity                 | V <sub>RX</sub> with respect to QGND        | 2    | 1    |       | mV <sub>pp</sub> |

| T <sub>RCV0</sub>  | receiver delay                       | FILTERL = 0                                 | 290  | 310  | 340   | μs               |

| T <sub>RCV1</sub>  | receiver delay                       | FILTERL = 1                                 | 160  | 175  | 190   | μs               |

|                    | phase measurement error              |                                             |      |      | ± 5.7 | 0                |

| Recovery           | from clock stable to demodulato      | r valid                                     |      |      |       |                  |

| T <sub>RPD</sub>   | recovery time demodulator            | see Note 1                                  |      |      | 5     | ms               |

| Recovery           | from WRITE-pulse                     |                                             |      | •    |       |                  |

| T <sub>RWD</sub>   | recovery of demodulator              | see Note 1                                  |      |      | 500   | μs               |

| Recovery           | from AST-step                        |                                             |      |      |       |                  |

| T <sub>RAST</sub>  | recovery of demodulator              | see Note 1                                  |      | 0.7  | 1.5   | ms               |

| Response           | delay data input to antenna drive    | er                                          |      |      |       |                  |

| T <sub>DITX</sub>  | response delay D <sub>IN</sub> to TX | MODE pin at V <sub>SS</sub> ;<br>see Note 2 |      |      | 10    | μs               |

#### Note

1. Specific command sequence required.

Applicable for WRITE\_TAG and WRITE\_TAG\_N commands. Due to device internal signal synchronization measures, T<sub>DITX</sub> is the response delay between a change at D<sub>IN</sub> and the resulting change at the antenna drivers. In the case of N is zero, T<sub>DITX</sub> applies for both the rising and failing transition at D<sub>IN</sub>, while for N unequal zero it applies for the rising transition at D<sub>IN</sub> only.

### **PCF7991AT**

97-05-22

### 13 PACKAGE

$V_{pp}, I_{pp}$  $V_p, I_p$

### Advanced Basestation IC

### PCF7991AT

#### 14 DEFINITIONS

| Peak-to-peak of arbitrary shaped signals: |

|-------------------------------------------|

|-------------------------------------------|

Zero-to peak of arbitrary shaped signals:

| Data sheet status            |                                                                                       |  |

|------------------------------|---------------------------------------------------------------------------------------|--|

| Objective specification      | This data sheet contains target or goal specifications for product development.       |  |

| Preliminary specification    | This data sheet contains preliminary data; supplementary data may be published later. |  |

| Product specification        | This data sheet contains final product specifications.                                |  |

| Limiting values              |                                                                                       |  |

| Limiting values given are in | accordance with the Absolute Maximum Rating System (IEC 134). Stress above one or     |  |

more of the limiting values may cause permanent damage to the device. These are stress ratings only and operation of the device at these or at any other conditions above those given in the Characteristics sections of the specification is not implied. Exposure to limiting values for extended periods may affect device reliability.

#### **Application information**

Where application information is given, it is advisory and does not form part of the specification.

#### 15 LIFE SUPPORT APPLICATIONS

These products are not designed for use in life support appliances, devices, or systems where malfunction of these products can reasonably be expected to result in personal injury. Philips customers using or selling these products for use in such applications do so at their own risk and agree to fully indemnify Philips for any damages resulting from such improper use or sale.

# Philips Semiconductors – a worldwide company

Argentina: see South America Australia: 34 Waterloo Road, NORTH RYDE, NSW 2113, Tel. +61 2 9805 4455, Fax. +61 2 9805 4466 Austria: Computerstr. 6, A-1101 WIEN, P.O. Box 213, Tel. +43 160 1010, Fax. +43 160 101 1210 Belarus: Hotel Minsk Business Center, Bld. 3, r. 1211, Volodarski Str. 6, 220050 MINSK, Tel. +375 172 200 733, Fax. +375 172 200 773 Belgium: see The Netherlands Brazil: see South America Bulgaria: Philips Bulgaria Ltd., Energoproject, 15th floor, 51 James Bourchier Blvd., 1407 SOFIA Tel. +359 2 689 211, Fax. +359 2 689 102 Canada: PHILIPS SEMICONDUCTORS/COMPONENTS. Tel. +1 800 234 7381 China/Hong Kong: 501 Hong Kong Industrial Technology Centre, 72 Tat Chee Avenue, Kowloon Tong, HONG KONG, Tel. +852 2319 7888, Fax. +852 2319 7700 Colombia: see South America Czech Republic: see Austria Denmark: Prags Boulevard 80, PB 1919, DK-2300 COPENHAGEN S, Tel. +45 32 88 2636, Fax. +45 31 57 0044 Finland: Sinikalliontie 3, FIN-02630 ESPOO, Tel. +358 9 615800, Fax. +358 9 61580920 France: 4 Rue du Port-aux-Vins, BP317, 92156 SURESNES Cedex, Tel. +33 1 40 99 6161, Fax. +33 1 40 99 6427 Germany: Hammerbrookstraße 69, D-20097 HAMBURG, Tel. +49 40 23 53 60, Fax. +49 40 23 536 300 Greece: No 15 25th March Street GR 17778 TAVROS/ATHENS Tel. +30 1 4894 339/239, Fax. +30 1 4814 240 Hungary: see Austria India: Philips INDIA Ltd, Band Box Building, 2nd floor, 254-D, Dr. Annie Besant Road, Worli, MUMBAI 400 025, Tel. +91 22 493 8541, Fax. +91 22 493 0966 Indonesia: see Singapore Ireland: Newstead, Clonskeagh, DUBLIN 14. Tel. +353 1 7640 000. Fax. +353 1 7640 200 Israel: RAPAC Electronics, 7 Kehilat Saloniki St, PO Box 18053, TEL AVIV 61180, Tel. +972 3 645 0444, Fax. +972 3 649 1007 Italy: PHILIPS SEMICONDUCTORS, Piazza IV Novembre 3,

20124 MILANO, Tel. +39 2 6752 2531, Fax. +39 2 6752 2557 **Japan:** Philips Bldg 13-37, Kohnan 2-chome, Minato-ku, TOKYO 108, Tel. +81 3 3740 5130, Fax. +81 3 3740 5077

Korea: Philips House, 260-199 Itaewon-dong, Yongsan-ku, SEOUL, Tel. +82 2 709 1412, Fax. +82 2 709 1415

Malaysia: No. 76 Jalan Universiti, 46200 PETALING JAYA, SELANGOR, Tel. +60 3 750 5214, Fax. +60 3 757 4880

Mexico: 5900 Gateway East, Suite 200, EL PASO, TEXAS 79905, Tel. +9-5 800 234 7381

Middle East: see Italy

Netherlands: Postbus 90050, 5600 PB EINDHOVEN, Bldg. VB, Tel. +31 40 27 82785, Fax. +31 40 27 88399 New Zealand: 2 Wagener Place, C.P.O. Box 1041, AUCKLAND,

Tel. +64 9 849 4160, Fax. +64 9 849 7811

Norway: Box 1, Manglerud 0612, OSLO, Tel. +47 22 74 8000, Fax. +47 22 74 8341

Philippines: Philips Semiconductors Philippines Inc., 106 Valero St. Salcedo Village, P.O. Box 2108 MCC, MAKATI, Metro MANILA, Tel. +63 2 816 6380, Fax. +63 2 817 3474 Poland: Ul. Lukiska 10, PL 04-123 WARSZAWA,

Tel. +48 22 612 2831, Fax. +48 22 612 2327

#### Portugal: see Spain

Romania: see Italy

Russia: Philips Russia, UI. Usatcheva 35A, 119048 MOSCOW, Tel. +7 095 755 6918, Fax. +7 095 755 6919

Singapore: Lorong 1, Toa Payoh, SINGAPORE 1231,

Tel. +65 350 2538, Fax. +65 251 6500

Slovakia: see Austria Slovenia: see Italv

South Africa: S.A. PHILIPS Pty Ltd., 195-215 Main Road Martindale, 2092 JOHANNESBURG, P.O. Box 7430 Johannesburg 2000, Tel. +27 11 470 5911, Fax. +27 11 470 5494

South America: Rua do Rocio 220, 5th floor, Suite 51, 04552-903 São Paulo, SÃO PAULO - SP, Brazil,

Tel. +55 11 821 2333, Fax. +55 11 829 1849 **Spain:** Balmes 22, 08007 BARCELONA,

Tel. +34 3 301 6312, Fax. +34 3 301 4107

Sweden: Kottbygatan 7, Akalla, S-16485 STOCKHOLM, Tel. +46 8 632 2000, Fax. +46 8 632 2745

Switzerland: Allmendstrasse 140, CH-8027 ZÜRICH,

Tel. +41 1 488 2686, Fax. +41 1 481 7730

Taiwan: Philips Semiconductors, 6F, No. 96, Chien Kuo N. Rd., Sec. 1, TAIPEI, Taiwan Tel. +886 2 2134 2865, Fax. +886 2 2134 2874

Thailand: PHILIPS ELECTRONICS (THAILAND) Ltd., 209/2 Sanpavuth-Bangna Road Prakanong, BANGKOK 10260, Tel. +66 2 745 4090, Fax. +66 2 398 0793

Turkey: Talatpasa Cad. No. 5, 80640 GÜLTEPE/ISTANBUL, Tel. +90 212 279 2770, Fax. +90 212 282 6707

Ukraine: PHILIPS UKRAINE, 4 Patrice Lumumba str., Building B, Floor 7, 252042 KIEV, Tel. +380 44 264 2776, Fax. +380 44 268 0461

United Kingdom: Philips Semiconductors Ltd., 276 Bath Road, Hayes, MIDDLESEX UB3 5BX, Tel. +44 181 730 5000, Fax. +44 181 754 8421 United States: 811 East Arques Avenue, SUNNYVALE, CA 94088-3409,

Tel. +1 800 234 7381

Uruguay: see South America

Vietnam: see Singapore

Yugoslavia: PHILIPS, Trg N. Pasica 5/v, 11000 BEOGRAD, Tel. +381 11 625 344, Fax.+381 11 635 777

For all other countries apply to: Philips Semiconductors, Marketing & Sales Communications, Building BE-p, P.O. Box 218, 5600 MD EINDHOVEN, The Netherlands, Fax. +31 40 27 24825

SCA55

© Philips Electronics N.V. 1997

All rights are reserved. Reproduction in whole or in part is prohibited without the prior written consent of the copyright owner.

The information presented in this document does not form part of any quotation or contract, is believed to be accurate and reliable and may be changed without notice. No liability will be accepted by the publisher for any consequence of its use. Publication thereof does not convey nor imply any license under patent- or other industrial or intellectual property rights.

Let's make things better.

Internet: http://www.semiconductors.philips.com

# **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for RF Receiver category:

Click to view products by NXP manufacturer:

Other Similar products are found below :

TDA5240 TDA5225 PQJ7911AHN/C0C,515 ATA8205P6C-TKQW SI4732-A10-GS FM17580-QNA-T-G PCF7991AT/1081/M WS1830S SI522 SI522A Ci522 U3741BM-P3FLG3 MICRF229YQS ATA8202C-PXQW-1 STA8088FGTR SI4362-C2A-GM Si4836-A10-GS SI4825-A10-CS SI4730-D60-GUR MICRF219AAYQS SI4831-B30-GUR SI4844-B20-GUR AW13412DNR SI4705-D60-GM SI4734-D60-GU T5743P3-TGQ AS3932-BQFT AD6643BCPZ-250 AD9864BCPZ FM12AG16M01 B82450A1084C CMX994AQ4 CMX994EQ4 CMX994GQ4 BGT24MR2E6327XUMA1 TDA5210 TDA5210XUMA1 TDA5211 TDA7200 TDA5240XUMA1 MICRF011YM MAX1473EUI+T MAX1473EUI+ MAX1470EUI+ MAX7034AUI+ MLX71122RLQ-BAA-000-SP MICRF002YM MICRF022YM-FS48 MICRF220AYQS-TR SI4355-B1A-FMR