# Ultra Low-Power Bluetooth Smart 5.0 SIP Rev. 1.0 — 5 December 2018

**Objective data sheet**

## **General description**

The QN9080-001-M17 is a fully certified device supporting BLE and NFC. It has ultra-low power consumption, highly integrated with rich feature sets, fully FCC/CE/IC/MIC certified. The QN9080-001-M17 supports Bluetooth 5, and it is intended for ultra-small, portable connected wireless applications.

This ultra-small device is based on QN9080 die and NT3H2211 die. QN9080 is powered by an Arm® Cortex®-M4F, and has a dedicated fusion sensor co-processor (FSP) to further reduce power consumption by off-loading complex math computations to the hardware. 512 KB of on-board flash and 128 KB SRAM provide enough room and flexibility for complex applications. NT3H2211 is NFC Forum Type 2 Tag compliant IC with I2C interface, which supplies the fastest, least expensive way to add tap-and-go connectivity to just about any electronic applications.

The QN9080-001-M17 also integrates 32 MHz and 32.768 kHz crystals, a 2.4 GHz optimized antenna, and necessary components for QN9080 system to run. It offers a complete solution for applications requiring BLE wireless connectivity and fast pairing with NTAG as an option. Its low external component count reduces overall system size, complexity and shortens development time.

#### **Features and benefits** 2.

- Key features:

- Bluetooth 5.0 certified

- Integrated antenna

- Integrated 32 MHz and 32.768 kHz crystals

- 32-bit Arm Cortex-M4F core at 32 MHz

- ♦ 512 KB flash

- 128 KB RAM

- ◆ TX power: up to +2 dBm

- RX sensitivity: -92.7 dBm in 1 Mbps mode and -89 dBm in 2 Mbps mode

- True single-chip Bluetooth Low Energy (v5.0) SoC solution:

- Integrated Bluetooth LE radio, protocol stack and application profiles

- Support central and peripherals roles

- Support master/slave concurrency

- Support 16 simultaneous links

- Support secure connections

- Support data packet length extension

- 48-bit unique BD address

- ◆ -92.7 dBm in 1 Mbps mode and -89 dBm in 2 Mbps mode

- ◆ TX output power from -20 dBm to +2 dBm

- Very low power consumption:

- ◆ Single 1.67 V ~3.6 V power supply

- 1 μA power-down mode, to wake up by GPIO

- 2 μA power-down mode, to wake up by 32 kHz sleep timer, RTC and GPIO

- 4 mA RX current at 3 V supply in 1 Mbps

- ◆ Ultra Low power Bluetooth Low Energy 5.0 module

- ♦ 3.5 mA TX current at 0 dBm TX power at 3 V supply in 1 Mbps mode

- Interface:

- 32 General-Purpose Input/Output (GPIO) pins, with configurable pull-up/pull-down resistors

- 8 external ADC inputs (shared with GPIO pins)

- 2 Analog Comparator input pins (share with GPIO pins)

- Single power supply 1.67 V to 3.6 V

- Operating temperature range -40 °C to +85 °C

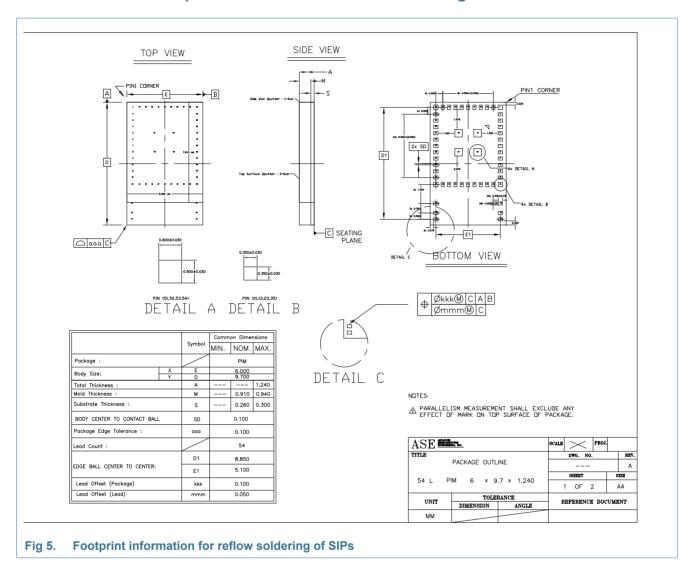

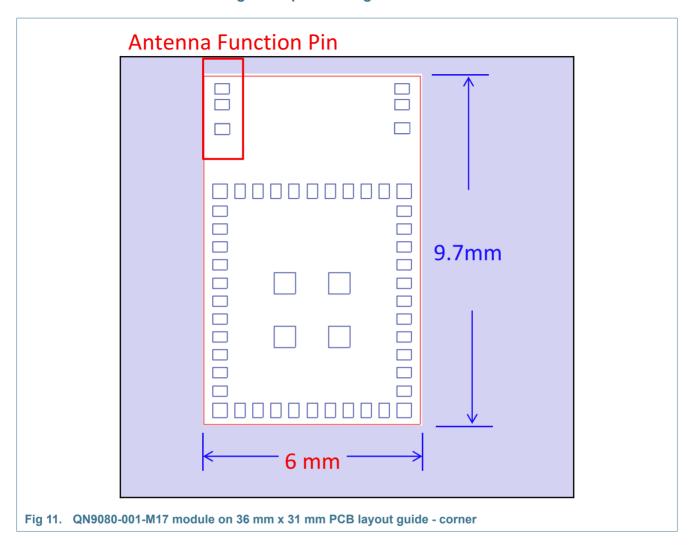

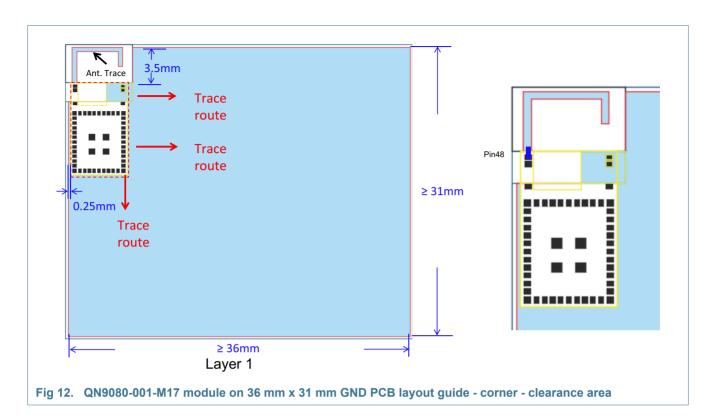

- 6 x9.7x1.17 mm LFLGA package

#### 2.1 Feature of QN9080

- True single-chip Bluetooth Low Energy (v5.0) SoC solution

- ◆ Integrated Bluetooth LE radio, protocol stack and application profiles

- Supports central and peripherals roles

- Supports master/slave concurrency

- Supports 16 simultaneous links

- Supports secure connections

- Supports data packet length extension

- ♦ Wifi/Bluetooth LE coexistence interface

- 48-bit unique bluetooth device address

- RF

- ◆ Fast and reliable RSSI in 1 dB step

- ◆ TX output power from –20 dBm to 2 dBm

- Single-ended RF port with integrated balun

- Generic FSK modulation with programmed data rate from 250 Kbps to 2 Mbps

- Compatible with worldwide radio frequency regulations

- Very low power consumption

- ◆ Single 1.67 V to 3.6 V power supply

- ◆ Integrated DC-to-DC buck converter and LDO

- 1.0 μA power-down 1 mode, to wake up by GPIO

- 2.5 μA power-down 0 mode, to wake up by 32 kHz sleep timer, RTC and GPIO

- 3.5 mA RX current with DC-to-DC convertor enabled at 3 V supply in 1Mbps mode

- 4 mA TX current at 0 dBm TX power with DC-to-DC converter enabled at 3 V supply in 1 Mbps mode

- Arm Cortex-M4 core (version r0p1)

- ◆ Arm Cortex-M4 processor, running at a frequency of up to 32 MHz

- ◆ Floating Point Unit (FPU) and Memory Protection Unit (MPU)

- ◆ Arm Cortex-M4 built-in Nested Vectored Interrupt Controller (NVIC)

- Serial Wire Debug (SWD) with six instruction breakpoints, two literal comparators, and four watch points, including serial wire output for enhanced debug capabilities

- System tick timer

- On-chip memory

- ◆ 512 KB on-chip flash program memory and 2 KB page erase and write

- ◆ 128 KB SRAM

- ◆ 256 KB ROM

- ROM API support

- Flash In-System Programming (ISP)

- Serial interfaces

- ◆ Four Flexcomm serial peripherals

- ◆ USART protocol supported by Flexcomm0, USART and I<sup>2</sup>C by Flexcomm1, SPI and I2C by Flexcomm2, and SPI by Flexcomm3

- Each Flexcomm includes a FIFO

- I<sup>2</sup>C-bus interfaces support fast mode and with multiple address recognition and monitor mode

- USB 2.0 (full speed) device interface

- Two quadrature decoders

- SPI Flash Interface (SPIFI) uses a SPI bus superset with four data lines to access off-chip quad SPI flash memory at a much higher rate than is possible using standard SPI or SSP interfaces

- Supports SPI memories with 1 or 4 data lines

- Digital peripherals

- DMA controller with 20 channels, able to access memories and DMA capable peripherals

- Up to 35 General Purpose Input Output (GPIO) pins, with configurable pull-up or pull-down resistors

- GPIO registers are located on the AHB for fast access

- 32 GPIOs can be selected as Pin INTerrupts (PINT), triggered by rising, or falling input edges

- ◆ AES-128 security coprocessor

- Random Number Generator (RNG)

- CRC engine

- Fusion Signal Processor (FSP) for data fusion and machine learning algorithms resulting in low power consumption compared to software processing

#### Analog peripherals

- ◆ 16-bit ADC with 8 external input channels, with sample rates of up to 32k sample per second, and with multiple internal and external trigger inputs

- ◆ Integrated temperature sensor, connected to one internal dedicated ADC channel

- ◆ Integrated battery monitor connected to one internal dedicated ADC channel

- General-purpose 8-bit 1M sample per second DAC

- Integrated capacitive sense up to 8 channels, able to wake up the MCU from low power states.

- Two ultra low-power analog comparators, able to wake up the MCU from low power states.

#### Timers

- ◆ Four 32-bit general-purpose timers or counters, support capture inputs and compare outputs, PWM mode, and external count input

- ◆ Sleep timer, which can work in power-down mode and wake up MCU

- 32-bit Real Time Clock (RTC) with 1 second resolution running in the always-on power domain; can be used for wake-up from all low power modes including power-down

- Watchdog Timer.

- SC Timer or PWM.

- Clock generation

- ◆ 32 MHz internal RC oscillator, which can be used as a system clock

- 16 MHz or 32 MHz crystal oscillator, which can be used as a system and RF reference

- 32 kHz on-chip RC oscillator

- ◆ 32.768 kHz crystal oscillator

- Power control

- Programmable Power Management Unit (PMU) to minimize power consumption

- Reduced power modes: sleep, and power-down

- Power-On Reset (POR)

- Brown-Out Detection (BOD) with separate thresholds for interrupt and forced reset

- Single power supply 1.67 V to 3.6 V

- Operating temperature range –40 °C to +85 °C

See QN908x data sheet for more details.

#### 2.2 Features of NTAG

- Interoperability

- ◆ ISO/IEC 14443 Part 2 and 3 compliant

- NTAG I2C plus development board is certified as NFC Forum Type 2 Tag (Certification ID: 58514)

- Unique 7-byte UID

- GET\_VERSION command for easy identification of chip type and supported features

- ◆ Input capacitance of 50 pF

- Host interface

- ◆ I<sup>2</sup>C slave

All information provided in this document is subject to legal disclaimers.

© NXP Semiconductors B.V. 2018. All rights reserved.

- ◆ Configurable event detection pin to signal NFC or pass-through data events

- Memory

- ◆ 1912 bytes of EEPROM-based user memory

- ◆ 64 bytes SRAM buffer for transfer of data between NFC and I<sup>2</sup>C interfaces with memory mirror or pass-through mode

- Clear arbitration between NFC and I<sup>2</sup>C memory access

- Data transfer

- ◆ Pass-through mode with 64-byte SRAM buffer

- ◆ FAST WRITE and FAST READ NFC commands for higher data throughput

- Security and memory-access management

- Full, read-only, or no memory access from NFC interface, based on 32-bit password

- ◆ Full, read-only, or no memory access from I<sup>2</sup>C interface

- ◆ NFC silence feature to disable the NFC interface

- Originality signature based on Elliptic Curve Cryptography (ECC) for simple, genuine authentication

- Power Management

- Configurable field-detection output signal for data-transfer synchronization and device wake-up

- Energy harvesting from NFC field, so as to power external devices (e.g. connected microcontroller)

See NT3H2111 2211 Product Data Sheet for more details.

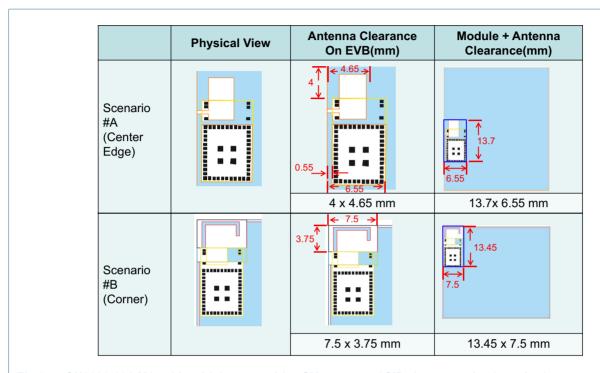

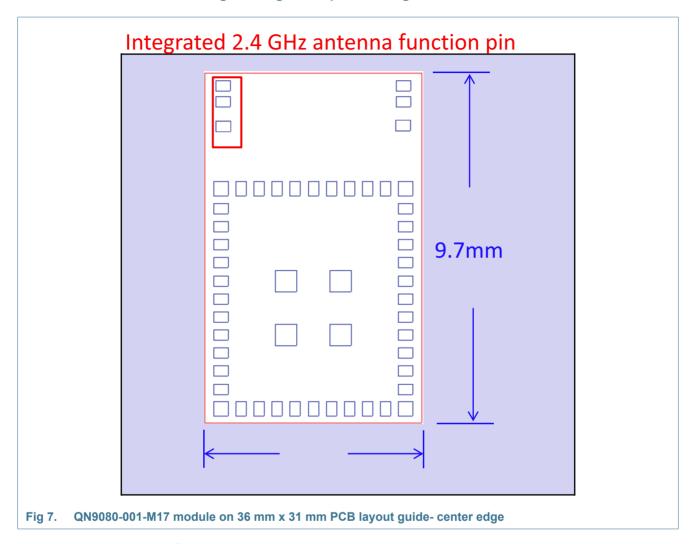

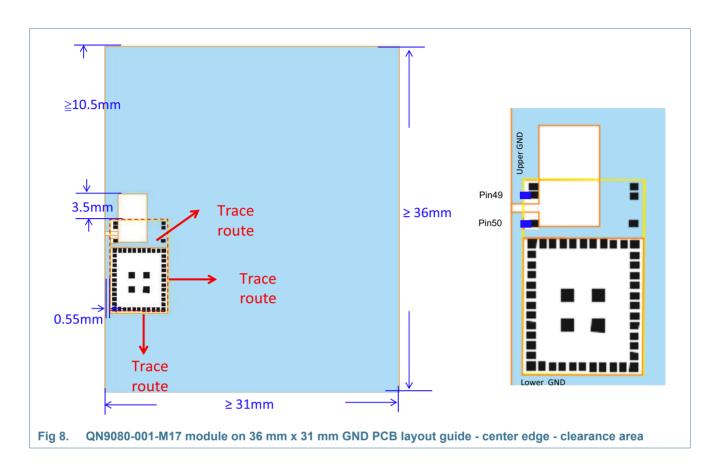

#### 2.3 Features of integrated 2.4 GHz antenna

- Monolithic SMD with small, low-profile and light-weight type.

- Wide bandwidth

- RoHS compliant

Note: When NFC function is required, the NFC tag antenna need to be connected externally.

## 3. Applications

- Health and medical devices

- Sports and fitness trackers

- Building and home automation

- Retail and advertising beacons

## 4. Ordering information

Table 1. Ordering information

| Type number    | Package |                                                               |             |  |  |

|----------------|---------|---------------------------------------------------------------|-------------|--|--|

|                | Name    | Description                                                   | Version     |  |  |

| QN9080-001-M17 | LFLGA54 | SIP module in LGA package; body $6 \times 9.7 \times 1.17$ mm | SOT1910 AA1 |  |  |

QN9080-001-M17

All information provided in this document is subject to legal disclaimers.

© NXP Semiconductors B.V. 2018. All rights reserved.

Table 2. Ordering options

| Type number    | Package<br>number | Flash (KB) | Total SRAM<br>(KB) | Cortex-M4 with FPU | FSP | USB FS | GPIO |

|----------------|-------------------|------------|--------------------|--------------------|-----|--------|------|

| QN9080-001-M17 | 3322 960 18570    | 512        | 128                | 1                  | 1   | 1      | 32   |

## 5. Marking

Fig 1. QN9080-001-M17 package marking

Table 3. Marking codes

| Line<br>number | Content      | Descriptions                                         |  |  |  |

|----------------|--------------|------------------------------------------------------|--|--|--|

| 1              | NXP          | Logo                                                 |  |  |  |

| 2              | QN9080-1-M17 | Product identifier                                   |  |  |  |

| 3              | XXXXX        | STR number request. It will be removed on production |  |  |  |

| 4              | XXXXXXXXXXX  | QN batch number                                      |  |  |  |

| 5              | E            | TSMC                                                 |  |  |  |

|                | t            | ASE-K                                                |  |  |  |

|                | D            | RoHS indicator (Dark green)                          |  |  |  |

|                | YY           | year; last two digits of year code of assembly       |  |  |  |

|                | WW           | week code of assembly                                |  |  |  |

|                | X            | mask version                                         |  |  |  |

|                | X            | for SIP before CQS; it will be removed after         |  |  |  |

QN9080-001-M17 has the following top-side marking:

Table 4. Device revision table

| Revision identifier (R) | Revision description        |  |  |

|-------------------------|-----------------------------|--|--|

| 001                     | Initial SIP module revision |  |  |

QN9080-001-M17 device has received FCC "Modular Approval", in compliance with CFR 47 FCC part 15 regulations and in accordance to FCC public notice DA00-1407. The modular approvals notice and test reports are available on request.

**Remark:** FCC, IC & Japan ID are not mentioned on the package due to the small device size.

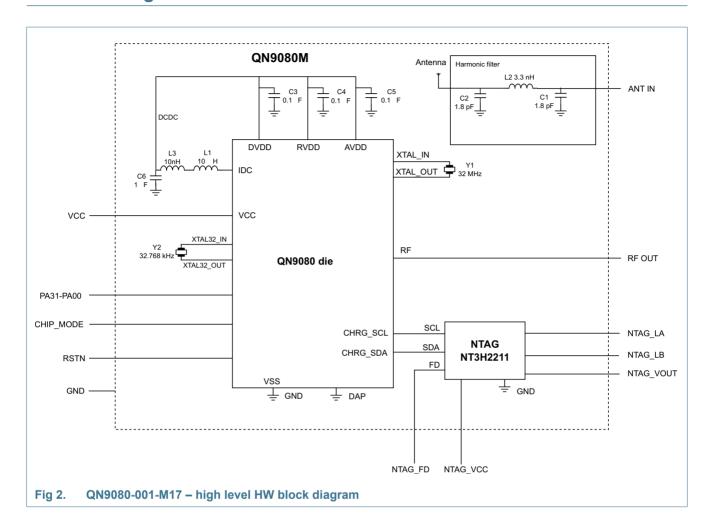

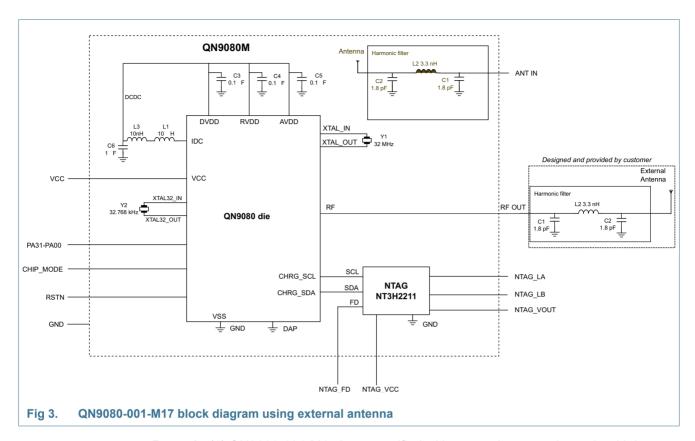

## 6. Block diagram

**Remark:** (1) QN9080-001-M17 is not certified with external antenna but only with its internal antenna. Customer using external antenna has to do new certification. (2) Harmonic filter is in adequacy with board.

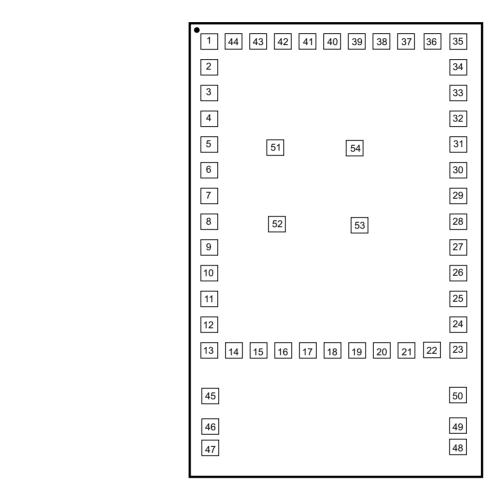

## 7. Pinning information

## 7.1 Pinning

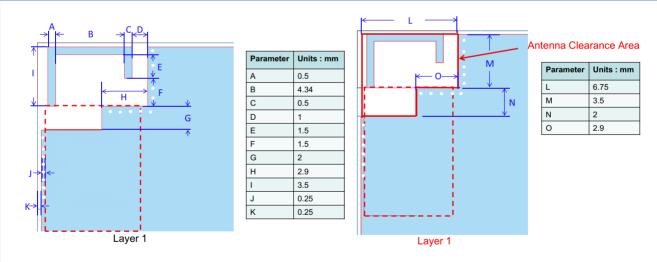

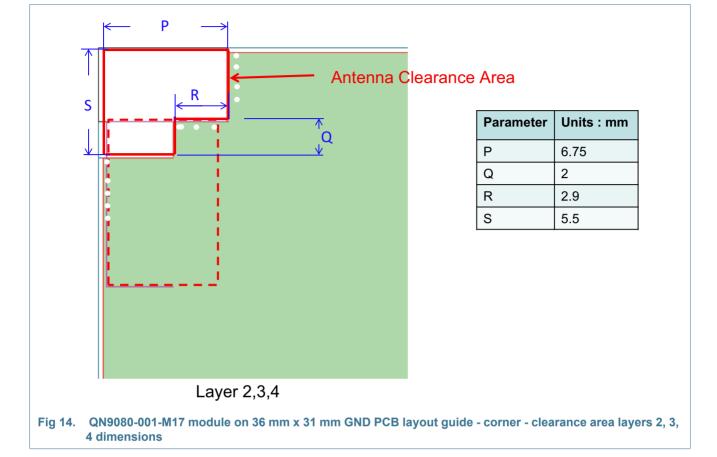

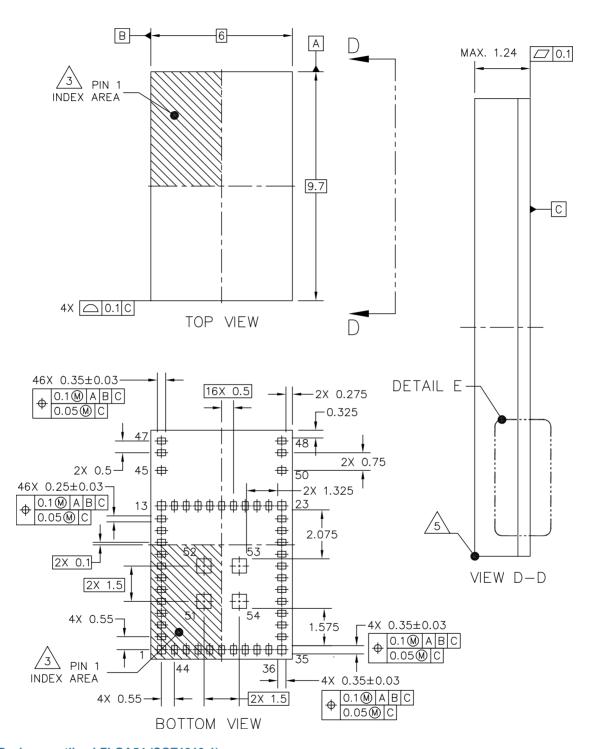

Fig 4. QN9080-001-M17 pinout diagram

## 7.2 Pin description

Table 5. Pin description

| Symbol | LFLGA54 | Reset state[1] | Alternate function | Туре                 | Description                              |

|--------|---------|----------------|--------------------|----------------------|------------------------------------------|

| PA30   | 1       | PU             | GPIOA30            | I/O                  | general-purpose digital input output pin |

|        |         |                | ACMP1P             | Al                   | analog comparator 1 positive input       |

|        |         |                | ETM_TRACEDAT3      | 0                    | ETM trace data output bit 3              |

|        |         |                | CTIMER3_MAT1       | 0                    | timer 3 match output 1                   |

|        |         |                | FC2_SCK            | I/O                  | flexcomm 2: SPI clock                    |

|        |         | FC3_MOSI       | I/O                | flexcomm 3: SPI MOSI |                                          |

|        |         |                | SPIFI_IO3          | I/O                  | data bit 3 for the SPI flash interface   |

Table 5. Pin description ...continued

| Symbol | LFLGA54 | Reset state <sup>[1]</sup> | Alternate function | Туре | Description                                                                  |

|--------|---------|----------------------------|--------------------|------|------------------------------------------------------------------------------|

| PA29   | 2       | PU                         | GPIOA29            | I/O  | general-purpose digital input output pin                                     |

|        |         |                            | ACMP1N             | Al   | analog comparator 1 negative input                                           |

|        |         |                            | ETM_TRACEDAT2      | 0    | ETM trace data output bit 2                                                  |

|        |         |                            | CTIMER3_MAT0       | 0    | timer 3 match output 0                                                       |

|        |         |                            | FC2_SCK            | I/O  | flexcomm 2: SPI clock                                                        |

|        |         |                            | FC3_MISO           | I/O  | flexcomm 3: SPI MISO                                                         |

|        |         |                            | SPIFI_IO2          | I/O  | data bit 2 for the SPI flash interface                                       |

| PA28   | 3       | PU                         | GPIOA28            | I/O  | general-purpose digital input output pin                                     |

|        |         |                            | CLK_AHB            | 0    | AHB clock output                                                             |

|        |         |                            | ETM_TRACECLK       | 0    | ETM trace clock output                                                       |

|        |         |                            | RTC_CAP            | I    | RTC capture input                                                            |

|        |         |                            | FC1_SCK            | I/O  | flexcomm 1: USART clock                                                      |

|        |         |                            | SD_DAC             | 0    | sigma-delta modulator DAC output                                             |

|        |         |                            | SPIFI_CSN          | 0    | active low chip select output for the SPI flash interface                    |

| PA27   | 4       | PU                         | GPIOA27            | I/O  | general-purpose digital input output pin                                     |

|        |         |                            | USB_DM             | I/O  | USB0 bidirectional D- line                                                   |

|        |         |                            | SCT0_IN1           | I    | SCTimer input 1                                                              |

|        |         |                            | CTIMER1_MAT2       | 0    | 32-bit CTimer 1 match output 2                                               |

|        |         |                            | FC2_SCL_MISO       | I/O  | flexcomm 2: I2C SCL, SPI MISO                                                |

|        |         |                            | QDEC0_B            | I    | quadrature decoder 0 input channel B                                         |

|        |         |                            | BLE_IN_PROC        | 0    | BLE event in process indicator for coexistence                               |

| PA26   | 5       | PU                         | GPIOA26            | I/O  | general-purpose digital input output pin                                     |

|        |         |                            | USB_DP             | I/O  | USB0 bidirectional D+ line                                                   |

|        |         |                            | SCT0_IN0           | I    | SCTimer input 0                                                              |

|        |         |                            | CTIMER1_MAT0       | 0    | 32-bit CTimer 1 match output 0                                               |

|        |         |                            | FC2_SDA_MOSI       | I/O  | flexcomm 2: I2C SDA, SPI MOSI                                                |

|        |         |                            | QDEC0_A            | I    | quadrature decoder 0 input channel A                                         |

|        |         |                            | BLE_SYNC           | 0    | BLE sync pulse                                                               |

| LB     | 6       | _                          | _                  | RF   | NTAG antenna/coil terminal B                                                 |

| LA     | 7       | _                          | _                  | RF   | NTAG antenna/coil terminal A                                                 |

| PA25   | 8       | PU                         | GPIOA25            | I/O  | general-purpose digital input output pin                                     |

|        |         |                            | ACMP0P/CS7         | Al   | analog comparator 0 positive input, or capacitive touch sense button input 7 |

|        |         |                            | ETM_TRACEDAT1      | 0    | ETM trace data output bit 1                                                  |

|        |         |                            | CTIMER3_CAP1       | I    | timer 3 input capture 1                                                      |

|        |         |                            | RFE_TX_EN          | 0    | TX enable for external RF front-end                                          |

|        |         |                            | FC3_SSEL0          | I/O  | flexcomm 3: SPI SSEL0                                                        |

|        |         |                            | SPIFI_IO1          | I/O  | data bit 1 for the SPI flash interface                                       |

Table 5. Pin description ...continued

| Symbol | LFLGA54 | Reset state[1] | Alternate function | Туре | Description                                                                  |

|--------|---------|----------------|--------------------|------|------------------------------------------------------------------------------|

| PA24   | 9       | PU             | GPIOA24            | I/O  | general-purpose digital input output pin                                     |

|        |         |                | ACMP0N/CS6         | AI   | analog comparator 0 negative input, or capacitive touch sense button input 6 |

|        |         |                | ETM_TRACEDAT0      | 0    | ETM trace data output bit 0                                                  |

|        |         |                | CTIMER3_CAP0       | I    | timer 3 input capture 0                                                      |

|        |         |                | RFE_RX_EN          | 0    | RX enable for external RF front-end                                          |

|        |         |                | FC3_SSEL1          | I/O  | flexcomm 3: SPI SSEL1                                                        |

|        |         |                | SPIFI_IO0          | I/O  | data bit 0 for the SPI flash interface                                       |

| SWDIO/ | 10      | PU             | SWDIO              | I/O  | serial wire debug I/O; it is the default function after booting              |

| PA23   |         |                | GPIOA23            | I/O  | general-purpose digital input output pin                                     |

|        |         |                | SCT0_IN3           | I    | SCTimer input 3                                                              |

|        |         |                | CTIMER3_MAT1       | 0    | 32-bit CTimer 3 match output 1                                               |

|        |         |                | FC2_SCL_SSEL1      | I/O  | flexcomm 2: I2C SCL, SPI SSEL1                                               |

|        |         |                | FC3_SSEL2          | I/O  | flexcomm 3: SPI SSEL2                                                        |

|        |         |                | QDEC1_B            | I    | quadrature decoder 1 input channel B                                         |

| SWCLK  | 11      | PU             | SWCLK              | I/O  | serial wire clock; it is the default function after reset                    |

| /PA22  |         |                | GPIOA22            | I/O  | general-purpose digital input output pin                                     |

|        |         |                | SCT0_IN2           | I    | SCTimer input 2                                                              |

|        |         |                | CTIMER3_MAT0       | 0    | 32-bit CTimer 3 match output 0                                               |

|        |         |                | FC2_SDA_SSEL0      | I/O  | flexcomm 2: I2C SDA, SPI SSEL0                                               |

|        |         |                | FC3_SSEL3          | I/O  | flexcomm 3: SPI SSEL3                                                        |

|        |         |                | QDEC1_A            | I    | quadrature decoder 1 input channel A                                         |

| PA21   | 12      | PU             | GPIOA21            | I/O  | general-purpose digital input output pin                                     |

|        |         |                | QDEC1_B            | I    | quadrature decoder 1 input channel B                                         |

|        |         |                | SCT0_OUT0          | 0    | SCTimer output 0, PWM output 0                                               |

|        |         |                | CTIMER2_MAT1       | 0    | 32-bit CTimer 2 match output 1                                               |

|        |         |                | FC2_SSEL3          | I/O  | flexcomm 2: SPI SSEL3                                                        |

|        |         |                | FC1_CTS_SDA        | I/O  | flexcomm 1: USART CTS, I2C SDA                                               |

|        |         |                | SPIFI_CSN          | 0    | active low chip select output for the SPI flash interface                    |

| PA20   | 13      | PU             | GPIOA20            | I/O  | general-purpose digital input output pin                                     |

|        |         |                | QDEC1_A            | I    | quadrature decoder 1 input channel A                                         |

|        |         |                | SCT0_OUT1          | 0    | SCTimer output 1, PWM output 1                                               |

|        |         |                | CTIMER2_MAT0       | 0    | 32-bit CTimer 2 match output 0                                               |

|        |         |                | SWO                | I/O  | serial wire trace output                                                     |

|        |         |                | FC1_RTS_SCL        | I/O  | flexcomm 1: USART RTS, I2C SCL                                               |

|        |         |                | SPIFI_CLK          | 0    | clock output for the SPI flash interface                                     |

Table 5. Pin description ...continued

| Symbol | LFLGA54 | Reset state <sup>[1]</sup> | Alternate function | Туре | Description                                    |

|--------|---------|----------------------------|--------------------|------|------------------------------------------------|

| PA19   | 14      | PU                         | GPIOA19            | I/O  | general-purpose digital input output pin       |

|        |         |                            | CS5                | Al   | capacitive touch sense button input 5          |

|        |         |                            | SCT0_OUT2          | 0    | SCTimer output 2, PWM output 2                 |

|        |         |                            | RFE_EN             | 0    | enable for external RF front-end               |

|        |         |                            | FC0_SCK            | I/O  | flexcomm 0: USART clock                        |

|        |         |                            | FC3_SSEL3          | I/O  | flexcomm 3: SPI SSEL3                          |

|        |         |                            | BLE_IN_PROC        | 0    | BLE event in process indicator for coexistence |

| PA18   | 15      | PU                         | GPIOA18            | I/O  | general-purpose digital input output pin       |

|        |         |                            | CS4                | Al   | capacitive touch sense button input 4          |

|        |         |                            | SCT0_OUT3          | 0    | SCTimer output 3, PWM output 3                 |

|        |         |                            | CTIMER2_MAT2       | 0    | 32-bit CTimer 2 match output 2                 |

|        |         |                            | FC0_SCK            | I/O  | flexcomm 0: USART clock                        |

|        |         |                            | FC3_SSEL2          | I/O  | flexcomm 3: SPI SSEL2                          |

|        |         |                            | BLE_SYNC           | 0    | BLE sync pulse                                 |

| PA17   | 16      | PU                         | GPIOA17            | I/O  | general-purpose digital input output pin       |

|        |         |                            | CS3                | Al   | capacitive touch sense button input 3          |

|        |         |                            | SD_DAC             | 0    | sigma-delta modulator DAC output               |

|        |         |                            | CTIMER2_MAT1       | 0    | 32-bit CTimer 2 match output 1                 |

|        |         |                            | FC0_RXD            | I/O  | flexcomm 0: USART RXD                          |

|        |         |                            | FC3_MISO           | I/O  | flexcomm 3: SPI MISO                           |

|        |         |                            | QDEC0_B            | I    | quadrature decoder 0 input channel B           |

| PA16   | 17      | PU                         | GPIOA16            | I/O  | general-purpose digital input output pin       |

|        |         |                            | CS2                | Al   | capacitive touch sense button input 2          |

|        |         |                            | SCT0_OUT1          | 0    | SCTimer output 1, PWM output 1                 |

|        |         |                            | CTIMER2_MAT0       | 0    | 32-bit CTimer 2 match output 0                 |

|        |         |                            | FC0_TXD            | I/O  | flexcomm 0: USART TXD                          |

|        |         |                            | FC3_MOSI           | I/O  | flexcomm 3: SPI MOSI                           |

|        |         |                            | QDEC0_A            | I    | quadrature decoder 0 input channel A           |

| PA15   | 18      | PU                         | GPIOA15            | I/O  | general-purpose digital input output pin       |

|        |         |                            | CS1                | Al   | capacitive touch sense button input 1          |

|        |         |                            | SCT0_OUT0          | 0    | SCTimer output 0, PWM output 0                 |

|        |         |                            | CTIMER2_CAP1       | I    | timer 2 input capture 1                        |

|        |         |                            | FC0_CTS            | I/O  | flexcomm 0: USART CTS                          |

|        |         |                            | FC3_SCK            | I/O  | flexcomm 3: SPI clock                          |

|        |         |                            | QDEC1_B            | I    | quadrature decoder 1 input channel B           |

Table 5. Pin description ...continued

| Symbol                    | LFLGA54 | Reset state <sup>[1]</sup> | Alternate function | Туре | Description                                                                                                                                                                                   |

|---------------------------|---------|----------------------------|--------------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PA14                      | 19      | PU                         | GPIOA14            | I/O  | general-purpose digital input output pin                                                                                                                                                      |

|                           |         |                            | CS0                | Al   | capacitive touch sense button input 0                                                                                                                                                         |

|                           |         |                            | ANT_SW             | 0    | external antenna switch for diversity                                                                                                                                                         |

|                           |         |                            | CTIMER2_CAP0       | I    | timer 2 input capture 0                                                                                                                                                                       |

|                           |         |                            | FC0_RTS            | I/O  | flexcomm 0: USART RTS                                                                                                                                                                         |

|                           |         |                            | FC3_SSEL0          | I/O  | flexcomm 3: SPI SSEL0                                                                                                                                                                         |

|                           |         |                            | QDEC1_A            | I    | quadrature decoder 1 input channel A                                                                                                                                                          |

| PA13                      | 20      | PU                         | GPIOA13            | I/O  | general-purpose digital input output pin                                                                                                                                                      |

|                           |         |                            | R                  | I/O  | reserved                                                                                                                                                                                      |

|                           |         |                            | SCT0_OUT4          | 0    | SCTimer output 4                                                                                                                                                                              |

|                           |         |                            | ACMP1_OUT          | 0    | analog comparator 1 output                                                                                                                                                                    |

|                           |         |                            | FC1_RXD_SDA        | I/O  | flexcomm 1: USART RXD, I2C SDA                                                                                                                                                                |

|                           |         |                            | FC3_SSEL1          | I/O  | flexcomm 3: SPI SSEL1                                                                                                                                                                         |

|                           |         |                            | RFE_EN             | 0    | enable for external RF front-end                                                                                                                                                              |

| CHIP_M 21<br>ODE/PB<br>02 | 21      | PU                         | CHIP_MODE          | I    | boot selection with pull-up by default; it should be pulled low<br>to go through the normal ISP process for firmware<br>programming, otherwise the ISP process is escaped to jump<br>to flash |

|                           |         |                            | GPIOB02            | I/O  | general-purpose digital input output pin                                                                                                                                                      |

|                           |         |                            | ANT_SW             | 0    | external antenna switch for diversity                                                                                                                                                         |

| RSTN                      | 22      | PU                         | _                  | I    | active low reset input                                                                                                                                                                        |

| ANT_IN                    | 23      | _                          | _                  | RF   | Internal antenna                                                                                                                                                                              |

| RF_OU<br>T                | 24      | _                          | _                  | RF   | RF input output port with Tx or Rx switch integrated on chip                                                                                                                                  |

| GND                       | 25      | _                          | _                  |      | ground                                                                                                                                                                                        |

| PA12                      | 26      | PU                         | GPIOA12            | I/O  | general-purpose digital input output pin                                                                                                                                                      |

|                           |         |                            | R                  | 0    | reserved                                                                                                                                                                                      |

|                           |         |                            | SCT0_OUT5          | 0    | SCTimer output 5                                                                                                                                                                              |

|                           |         |                            | ACMP0_OUT          | 0    | analog comparator 0 output                                                                                                                                                                    |

|                           |         |                            | FC1_TXD_SCL        | I/O  | flexcomm 1: USART TXD, I2C SCL                                                                                                                                                                |

|                           |         |                            | SD_DAC             | 0    | sigma-delta modulator DAC output                                                                                                                                                              |

|                           |         |                            | ANT_SW             | 0    | external antenna switch for diversity                                                                                                                                                         |

| PA11                      | 27      | PU                         | GPIOA11            | I/O  | general-purpose digital input output pin                                                                                                                                                      |

|                           |         |                            | ADC7               | Al   | ADC external input 7                                                                                                                                                                          |

|                           |         |                            | SCT0_IN3           | I    | SCTimer input 3                                                                                                                                                                               |

|                           |         |                            | CTIMER1_MAT2       | 0    | 32-bit CTimer 1 match output 2                                                                                                                                                                |

|                           |         |                            | FC2_SSEL2          | I/O  | flexcomm 2: SPI SSEL2                                                                                                                                                                         |

|                           |         |                            | ACMP1_OUT          | 0    | analog comparator 1 output                                                                                                                                                                    |

|                           |         |                            | BLE_RX             | 0    | BLE reception indicator for coexistence                                                                                                                                                       |

Table 5. Pin description ...continued

| Symbol | LFLGA54 | Reset state <sup>[1]</sup> | Alternate function | Туре | Description                                               |

|--------|---------|----------------------------|--------------------|------|-----------------------------------------------------------|

| PA10   | 28      | PU                         | GPIOA10            | I/O  | general-purpose digital input output pin                  |

|        |         |                            | ADC6               | Al   | ADC external input 6                                      |

|        |         |                            | SCT0_IN2           | I    | SCTimer input 2                                           |

|        |         |                            | CTIMER1_MAT1       | 0    | 32-bit CTimer 1 match output 1                            |

|        |         |                            | FC1_SCK            | I/O  | flexcomm 1: USART clock                                   |

|        |         |                            | ACMP0_OUT          | 0    | analog comparator 0 output                                |

|        |         |                            | BLE_TX             | 0    | BLE transmit indicator for coexistence                    |

| PA09   | 29      | PU                         | GPIOA9             | I/O  | general-purpose digital input output pin                  |

|        |         |                            | ADC5               | Al   | ADC external input 5                                      |

|        |         |                            | SCT0_IN1           | I    | SCTimer input 1                                           |

|        |         |                            | CTIMER1_MAT0       | 0    | 32-bit CTimer 1 match output 0                            |

|        |         |                            | FC1_RXD_SDA        | I/O  | flexcomm 1: USART RXD, I2C SDA                            |

|        |         |                            | BLE_PTI3           | 0    | BLE packet traffic information bit 3                      |

|        |         |                            | SPIFI_IO3          | I/O  | data bit 3 for the SPI flash interface                    |

| PA08   | 30      | PU                         | GPIOA8             | I/O  | general-purpose digital input output pin                  |

|        |         |                            | ADC4               | Al   | ADC external input 4                                      |

|        |         |                            | SCT0_IN0           | I    | SCTimer input 0                                           |

|        |         |                            | CTIMER1_CAP1       | I    | timer 1 input capture 1                                   |

|        |         |                            | FC1_TXD_SCL        | I/O  | flexcomm 1: USART TXD, I2C SCL                            |

|        |         |                            | BLE_PTI2           | 0    | BLE packet traffic information 2                          |

|        |         |                            | SPIFI_IO2          | I/O  | data bit 2 for the SPI flash interface                    |

| PA07   | 31      | PU                         | GPIOA7             | I/O  | general-purpose digital input output pin                  |

|        |         |                            | ADC_VREFI          | Al   | ADC external reference voltage input                      |

|        |         |                            | SCT0_OUT2          | 0    | SCTimer output 2                                          |

|        |         |                            | CTIMER1_CAP0       | I    | timer 1 input capture 0                                   |

|        |         |                            | FC1_CTS_SDA        | I/O  | flexcomm 1: USART CTS, I2C SDA                            |

|        |         |                            | BLE_PTI1           | 0    | BLE packet traffic information 1                          |

|        |         |                            | SPIFI_CSN          | 0    | active low chip select output for the SPI flash interface |

| PA06   | 32      | PU                         | GPIOA6             | I/O  | general-purpose digital input output pin                  |

|        |         |                            | ADC_EX_CAP         | Α    | connected with ADC external capacitor                     |

|        |         |                            | SCT0_OUT3          | 0    | SCTimer output 3                                          |

|        |         |                            | CTIMER0_MAT2       | 0    | 32-bit CTimer 0 match output 2                            |

|        |         |                            | FC1_RTS_SCL        | I/O  | flexcomm 1: USART RTS, I2C SCL                            |

|        |         |                            | BLE_PTI0           | 0    | BLE packet traffic information bit 0                      |

|        |         |                            | SPIFI_CLK          | 0    | clock output for the SPI flash interface                  |

Table 5. Pin description ...continued

| Symbol       | LFLGA54 | Reset state[1] | Alternate function | Туре | Description                              |

|--------------|---------|----------------|--------------------|------|------------------------------------------|

| PA05         | 33      | PU             | GPIOA5             | I/O  | general-purpose digital input output pin |

|              |         |                | ADC3               | Al   | ADC external input 3                     |

|              |         |                | SCT0_OUT5          | 0    | SCTimer output 5                         |

|              |         |                | CTIMER0_MAT1       | 0    | 32-bit CTimer 0 match output 1           |

|              |         |                | FC0_RXD            | I/O  | flexcomm 0: USART RXD                    |

|              |         |                | FC2_SCL_MISO       | I/O  | flexcomm 2: SCL, SPI MISO                |

|              |         |                | SPIF_IO1           | I/O  | data bit 1 for the SPI flash interface   |

| PA04         | 34      | PU             | GPIOA4             | I/O  | general-purpose digital input output pin |

|              |         |                | ADC2               | Al   | ADC external input 2                     |

|              |         |                | SCT0_OUT4          | 0    | SCTimer output 4                         |

|              |         |                | CTIMER0_MAT0       | 0    | 32-bit CTimer 0 match output 0           |

|              |         |                | FC0_TXD            | I/O  | flexcomm 0: USART TXD                    |

|              |         |                | FC2_SDA_MOSI       | I/O  | flexcomm 2: I2C SDA, SPI MOSI            |

|              |         |                | SPIF_IO0           | I/O  | data bit 0 for the SPI flash interface   |

| PA03         | 35      | PU             | GPIOA3             | I/O  | general-purpose digital input output pin |

|              |         |                | QDEC0_B            | I    | quadrature decoder 0 input channel B     |

|              |         |                | SCT0_OUT3          | 0    | SCTimer output 3                         |

|              |         |                | CTIMER0_MAT1       | 0    | 32-bit CTimer 0 match output 1           |

|              |         |                | R                  | 0    | reserved                                 |

|              |         |                | FC2_SDA_SSEL0      | I/O  | flexcomm 2: I2C SDA, SPI SSEL0           |

|              |         |                | RFE_TX_EN          | 0    | TX enable for external RF front-end      |

| PA02         | 36      | PU             | GPIOA2             | I/O  | general-purpose digital input output pin |

|              |         |                | QDEC0_A            | I    | quadrature decoder 0 input channel A     |

|              |         |                | SCT0_OUT2          | 0    | SCTimer output 2                         |

|              |         |                | CTIMER0_MAT0       | 0    | 32-bit CTimer 0 match output 0           |

|              |         |                | R                  | I/O  | reserved                                 |

|              |         |                | FC2_SCL_SSEL1      | I/O  | flexcomm 2: I2C SCL, SPI SSEL1           |

|              |         |                | RFE_RX_EN          | 0    | RX enable for external RF front-end      |

| NTAG_<br>FD  | 37      | _              | _                  | 0    | field detection                          |

| VCC          | 38      | _              | _                  | _    | power supply                             |

| NTAG_<br>VCC | 39      | _              | _                  | _    | NTAG power supply                        |

| VOUT         | 40      | _              | _                  | _    | output supply voltage(energy harvesting) |

| VSS1         | 41      |                | _                  | _    | ground                                   |

Table 5. Pin description ... continued

| Symbol       | LFLGA54 | Reset state <sup>[1]</sup> | Alternate function | Type | Description                                          |

|--------------|---------|----------------------------|--------------------|------|------------------------------------------------------|

| PA01         | PA01 42 | PU                         | GPIOA1             | I/O  | general-purpose digital input output pin             |

|              |         |                            | ADC1               | Al   | ADC external input 1                                 |

|              |         |                            | SCT0_OUT1          | 0    | SCTimer output 1                                     |

|              |         |                            | CTIMER0_CAP1       | I    | 32-bit CTimer 0 capture input 1                      |

|              |         |                            | FC0_CTS            | I/O  | flexcomm 0: USART CTS                                |

|              |         |                            | FC2_SSEL2          | I/O  | flexcomm 2: SPI SSEL2                                |

|              |         |                            | WLAN_RX            | I    | WLAN active high RX active indicator for coexistence |

| PA00         | 43      | PU                         | GPIOA0             | I/O  | general-purpose digital input output pin             |

|              |         |                            | ADC0               | Al   | ADC external input 0                                 |

|              |         |                            | SCT0_OUT0          | 0    | SCTimer output 0                                     |

|              |         |                            | CTIMER0_CAP0       | I    | 32-bit CTimer 0 capture input 0                      |

|              |         |                            | FC0_RTS            | I/O  | flexcomm 0: USART RTS                                |

|              |         |                            | FC2_SSEL3          | I/O  | flexcomm 2: SPI SSEL3                                |

|              |         |                            | WLAN_TX            | I    | WLAN active high TX active indicator for coexistence |

| PA31         | 44      | PU                         | GPIOA31            | I/O  | general-purpose digital input output pin             |

|              |         |                            | DAC                | AO   | DAC analog output                                    |

|              |         |                            | RTC_CAP            | I    | RTC capture input                                    |

|              |         |                            | CTIMER3_MAT2       | 0    | Timer 3 match output 2                               |

|              |         |                            | SWO                | I/O  | serial wire trace output                             |

|              |         |                            | FC3_SCK            | I/O  | flexcomm 3: SPI clock                                |

|              |         |                            | SPIFI_CLK          | 0    | clock output for the SPI flash interface             |

| GND          | 45      | _                          | _                  | _    | ground                                               |

| GND          | 46      | _                          | _                  |      | ground                                               |

| GND          | 47      | _                          | _                  |      | ground                                               |

| ANT_Pi<br>n3 | 48      |                            |                    |      | Internal antenna ground                              |

| ANT_Pi<br>n2 | 49      |                            | _                  |      | Internal antenna ground                              |

| ANT_Pi<br>n1 | 50      | _                          | _                  | _    | Internal antenna ground                              |

| GND          | 51      | _                          | _                  | _    | ground                                               |

| GND          | 52      | _                          | _                  | _    | ground                                               |

| GND          | 53      | _                          | _                  | _    | ground                                               |

| GND          | 54      | _                          | _                  | _    | ground                                               |

<sup>[1]</sup> PU = input mode, pull-up enabled (pull-up resistor pulls up pin to V<sub>CC</sub>). Z = high impedance; pull-up or pull-down disabled, AI = analog input, AO = analog output, I = input, O = output, F = floating. Reset state reflects the pin state at reset without boot code operation.

#### 7.2.1 Termination of unused pins

<u>Table 6</u> shows how to terminate pins that are not used in the application. In many cases, unused pins should be connected externally or configured correctly by software to minimize the overall power consumption of the part.

Unused pins with GPIO function should be configured as outputs LOW with their internal pull-up disabled. To configure a GPIO pin as output and drive it LOW, select the GPIO function in the IOCON register, select output in the GPIO DIR register, and write a 0 to the GPIO PORT register for that pin. Disable the pull-up in the pin's IOCON register.

In addition, it is recommended to configure all GPIO pins that are not bonded out on smaller packages as outputs driven LOW with their internal pull-up disabled.

Table 6. Termination of unused pins

| ·         |                                 |                                                                                                       |  |  |  |  |

|-----------|---------------------------------|-------------------------------------------------------------------------------------------------------|--|--|--|--|

| Pin       | Default<br>state <sup>[1]</sup> | Recommended termination of unused pins                                                                |  |  |  |  |

| RSTN      | I; PU                           | the RSTN pin can be left unconnected if the application does not use it.                              |  |  |  |  |

| all PAnm  | I; PU                           | can be left unconnected if driven LOW and configured as GPIO output with pull-up disabled by software |  |  |  |  |

| CHIP_MODE | I; PU                           | can be left unconnected if driven LOW and configured as GPIO output with pull-up disabled by software |  |  |  |  |

<sup>[1]</sup> I = Input, IA = Inactive (no pull-up/pull-down enabled), PU = Pull-Up enabled.

#### 7.2.2 Pin states in different power modes

Table 7. Pin states in different power modes

| Pin      | Active - Sleep - Power Down modes                                  |

|----------|--------------------------------------------------------------------|

| all PAnm | As configured in the SYSCON[1]. Default: internal pull-up enabled. |

| RSTN     | Reset function enabled. Default: input, internal pull-up enabled   |

<sup>[1]</sup> Default and programmed pin states are retained in sleep, and power-down mode.

## 8. Compliance statements and documentation

- The FCC ID number of the QN9080-001-M17 is XXMQN9080M17

- The IC ID number of the QN9080-001-M17 is 8764A-QN9080M17

- The Japan ID number of the QN9080-001-M17 is

#### 8.1 FCC Statements and documentation

This section contains the Federal Communication Commission (FCC) statements and documents.

#### 8.1.1 FCC interference Statements

• This equipment has been tested and found to comply with the limits for a Class B digital device, pursuant to Part 15 of the FCC Rules. These limits are designed to provide reasonable protection against harmful interference in a residential installation. This equipment generates, uses, and can radiate radio frequency energy and, if not installed and used in accordance with the instructions, may cause harmful interference to radio communications. However, there is no guarantee that interference will not occur in a particular installation. If this equipment does cause harmful interference to radio or television reception, which can be determined by turning the equipment off and on, the user is encouraged to try to correct the interference by one of the following measures:

- Reorient or relocate the receiving antenna

- Increase the separation between the equipment and receiver

- Connect the equipment into an outlet on a circuit different from that to which the receiver is connected

- Consult the dealer or an experienced radio/TV technician for help

- · OEM integrators instructions

- The OEM integrators are responsible for ensuring that the end-user has no manual instructions to remove or install SIP

- The SIP is limited to installation in mobile or fixed applications, according to CFR 47 Part 2.1091(b)

- Separate approval is required for all other operating configurations, including portable configurations with respect to CFR 47 Part 2.1093 and different antenna configurations

- User guide mandatory statements

User's instructions of the host device must contain the following statements in addition to operation instructions:

- \* "This device complies with part 15 of the FCC Rules. Operation is subject to the following two conditions:

- (1) This device may not cause harmful interference, and

- (2) This device must accept any interference received, including interference that may cause undesired operation"

- \* "Changes or modifications not expressly approved by the party responsible for compliance could void the user's authority to operate the equipment"

- FCC RF Exposure requirements

User's instructions of the host device must contain the following instructions in addition to operation instructions:

Avoid direct contact to the antenna, or keep it to a 20cm minimum distance while using this equipment. This device must not be collocated or operating in conjunction with another antenna or transmitter.

This SIP has been designed to operate etheir with internal antenna or with external antennas having a maximum gain of 2 dBi. Antennas having a gain greater than 2 dBi are strictly prohibited for use with this device. The required antenna impedance is 50 ohms

#### 8.1.2 FCC end product labelling

The final 'end product' should be labelled in a visible area with the following: "Contains TX FCC ID: XXMQN9080M17 to reflect the SIP being used inside the product.

#### 8.2 Industry Canada Statement

This device complies with Industry Canada licence-exempt RSS standard(s). Operation is subject to the following two conditions: (1) this device may not cause interference, and (2) this device must accept any interference, including interference that may cause undesired operation of the device.

This device complies with Industry Canada RF radiation exposure limits set forth for general population (uncontrolled exposure). This device must be installed to provide a separation distance of at least 20 cm from all persons and must not be collocated or operating in conjunction with any other antenna or transmitter.

Le présent appareil est conforme aux CNR d'Industrie Canada applicables aux appareils radio exempts de licence.

L'exploitation est autorisée aux deux conditions suivantes : (1) il ne doit pas produire de brouillage, et (2) l'utilisateur du dispositif doit être prêt à accepter tout brouillage radioélectrique re?u, même si ce brouillage est susceptible de compromettre le fonctionnement du dispositif.

Le présent appareil est conforme aux niveaux limites d'exigences d'exposition RF aux personnes définies par Industrie Canada. Cet appareil doit être installé afin d'offrir une distance de séparation d'au moins 20 cm avec l'utilisateur, et ne doit pas être installé à proximité ou être utilisé en conjonction avec une autre antenne ou un autre émetteur.

To reduce potential radio interference to other users, the antenna type and its gain should be so chosen that the equivalent isotropic radiated power (e.i.r.p.) is not more than that permitted for successful communication.

The Gain of SIP with internal antenna is -3dBi.

If customer wants, he can also use the SIP with external antenna with maximum gain of 2dbi. This feature is not certified by NXP and need to be done by the customer. Antennas having a gain greater than 2 dBi are strictly prohibited for use with this device. The required antenna impedance is 50 ohms.

As long as the above condition is met, further transmitter testing will not be required.

However, the OEM integrator is still responsible for testing their end-product for any additional compliance requirements required with this SIP installed (for example, digital device emissions, PC peripheral requirements, etc.).

#### 8.2.1 Industry of Canada end product labelling

For Industry Canada purposes the following should be used: "Contains Industry Canada ID IC: 8764A-QN9080M17

#### 8.3 Japanese Radio Certification Statement

This equipment has been tested and found to comply with the Japanese Radio Certification Rules

#### 8.3.1 Radio Certification end product labelling

For Japanese Radio Certification purposes, the following should be used:

"Contains Japanese Radio certificate product: Japan ID number is 😂 207-990010

#### 9. Static characteristics

#### 9.1 General operating conditions

Table 8. General operating conditions

$T_{amb}$  = -40 °C to +85 °C, unless otherwise specified.

| Symbol           | Parameter                      | Conditions                    | Min  | Typ[1] | Max | Unit |

|------------------|--------------------------------|-------------------------------|------|--------|-----|------|

| f <sub>clk</sub> | Clock frequency                | _                             |      | _      | 32  | MHz  |

| V <sub>CC</sub>  | Supply voltage                 | _                             | 1.67 | 3      | 3.6 | V    |

| V <sub>ESD</sub> | Electrostatic discharge        | Human body model[2]; all pins |      | _      | 2   | kV   |

| voltage          | Charged device model; all pins |                               | _    | 300    | V   |      |

| $T_{J(max)}$     | Maximum junction temperature   | _                             | _    |        | 85  | °C   |

- [1] Typical ratings are not guaranteed. The values listed are for room temperature (25 °C), nominal supply voltages.

- [2] Human body model: equivalent to discharging a 100 pF capacitor through a 1.5 k $\Omega$  series resistor.

#### 9.2 Power consumption

Power measurements in active, sleep, power down modes were performed under the following conditions:

- · All peripherals disabled

- Analog peripherals (ADC/DAC/ACMP/Capacitive Sense) powered down

- RF off

- Internal 32 MHz HFRCO powered down

Table 9. Static characteristics: Power consumption in active modes

$T_{amb}$  = -40 °C to +85 °C, unless otherwise specified.

| Symbol                                                 | Parameter      | Conditions                        |     | Min | Typ[1] | Max | Unit |

|--------------------------------------------------------|----------------|-----------------------------------|-----|-----|--------|-----|------|

| 32 MHz HFXO; DC-DC converter enabled, $V_{CC}$ = 3.0 V |                |                                   |     |     |        |     |      |

| I <sub>CC</sub>                                        | Supply current | CoreMark code executed from flash |     |     |        |     |      |

|                                                        |                | CLK_AHB = 16 MHz                  | [2] | _   | 920    | _   | μΑ   |

- [1] Typical ratings are not guaranteed. Typical values listed are at room temperature (25  $^{\circ}$ C).

- [2] Characterized through bench measurements using typical samples.

Table 10. Static characteristics: Bluetooth LE power consumption in active modes

$T_{amb}$  = -40 °C to +85 °C, unless otherwise specified.

| Symbol          | Parameter                                                                                             | Conditions                                        |        | Min          | Typ[1][2] | Max <sup>[3]</sup> | Unit |

|-----------------|-------------------------------------------------------------------------------------------------------|---------------------------------------------------|--------|--------------|-----------|--------------------|------|

| 32 MHz crystal  | 32 MHz crystal oscillator, CLK_AHB = 16 MHz, transmitter mode: f <sub>c</sub> = 2440 MHz, 1 Mbps mode |                                                   |        |              |           |                    |      |

| I <sub>CC</sub> | supply current                                                                                        | DC-to-DC converter enabled, V <sub>cc</sub> = 3 V |        |              |           |                    |      |

|                 |                                                                                                       | Tx power = 0 dBm                                  |        | _            | 3.5       | _                  | mA   |

| 32 MHz crystal  | oscillator, CLK_AHB = 1                                                                               | 6 MHz, transmitter mode: f <sub>c</sub> = 2       | 440 MH | lz, 1 Mbps i | mode      |                    |      |

| I <sub>CC</sub> | supply current                                                                                        | DC-to-DC converter enabled, V <sub>cc</sub> = 3 V |        |              |           |                    |      |

|                 |                                                                                                       | -92.7 dBm RX sensitivity                          |        | _            | 4         | _                  | mA   |

[1] Typical ratings are not guaranteed. Typical values listed are at room temperature (25  $^{\circ}$ C).

QN9080-001-M17

All information provided in this document is subject to legal disclaimers.

© NXP Semiconductors B.V. 2018. All rights reserved.

- [2] Characterized through bench measurements using typical samples, with 50  $\Omega$  loading on RF port.

- [3] Guaranteed by characterization, not tested in production.

Table 11. Static characteristics: Power consumption in sleep, and power-down modes

$T_{amb}$  = -40 °C to +85 °C; unless otherwise specified.

| Symbol          | Parameter                                                                                                  | Conditions                                                                | Min                                                                                         | Typ[1][2]                | Max[3] | Unit |  |  |  |

|-----------------|------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|--------------------------|--------|------|--|--|--|

| I <sub>CC</sub> | Supply current                                                                                             | Sleep mode: all SRAM on. Flash in standby mode. DC                        | Sleep mode: all SRAM on. Flash in standby mode. DC-to-DC converter enabled, $V_{cc}$ = 3 V. |                          |        |      |  |  |  |

|                 |                                                                                                            | 32 MHz crystal oscillator                                                 |                                                                                             |                          |        |      |  |  |  |

|                 |                                                                                                            | CLK_AHB = 16 MHz                                                          | _                                                                                           | 470                      | _      | μΑ   |  |  |  |

|                 | Power down mode; all clocks off. Flash is powered down. DC-DC disabled, $V_{cc}$ = 3 V. $T_{amb}$ = 25 °C. |                                                                           |                                                                                             |                          |        |      |  |  |  |

|                 |                                                                                                            | 8 KB SRAM powered                                                         | _                                                                                           | 1.0                      | _      | μΑ   |  |  |  |

|                 |                                                                                                            | Power down mode; 32.768 kHz LFXO on Flash is powered down. DC-DC disabled |                                                                                             | T <sub>amb</sub> = 25 °C | D.     |      |  |  |  |

|                 |                                                                                                            | 8 KB SRAM powered                                                         | _                                                                                           | 2.5                      | _      | μΑ   |  |  |  |

- [1] Typical ratings are not guaranteed. Typical values listed are at room temperature (25 °C).

- [2] Characterized through bench measurements using typical samples.

- [3] Guaranteed by characterization, not tested in production.

#### 9.3 Clock source

Table 12. 32 MHz clock source characteristics

| Symbol           | Parameter             | Conditions | Min | Тур | Max | Unit |

|------------------|-----------------------|------------|-----|-----|-----|------|

| f <sub>nom</sub> | Nominal frequency     | _          | _   | 32  | _   | MHz  |

|                  | Frequency tolerance   | at +25°C   | -10 | _   | +10 | ppm  |

| C <sub>L</sub>   | Load capacitance      | _          | _   | 10  | _   | pF   |

| R <sub>r</sub>   | Equivalent resistance | _          | _   | _   | 60  | Ω    |

Table 13. 32.768 kHz clock source characteristics

| Symbol           | Parameter             | Conditions                    | Min | Тур    | Max | Unit |

|------------------|-----------------------|-------------------------------|-----|--------|-----|------|

| f <sub>nom</sub> | Nominal frequency     | _                             | _   | 32.768 | _   | kHz  |

|                  | Frequency tolerance   | at +25±3°C, Not include aging | -20 |        | +20 | ppm  |

| C <sub>L</sub>   | Load capacitance      | _                             | _   | 12.5   | _   | pF   |

| R <sub>r</sub>   | Equivalent resistance | _                             | _   | _      | 120 | kΩ   |

#### 10. RF characteristics

#### 10.1 Receiver

#### Table 14. Receiver characteristics

$T_{amb}$  = 25 °C; based on characterization; not tested in production.  $V_{CC}$  = 3 V;  $f_c$  = 2440 MHz; BER < 0.1 %, 1 Mbps mod

| Symbol                         | Parameter            | Conditions                             | Min | Тур   | Max | Unit |

|--------------------------------|----------------------|----------------------------------------|-----|-------|-----|------|

| S <sub>RX</sub>                | RX sensitivity       | low power mode with DC-to-DC converter | _   | -92.7 |     | dBm  |

| P <sub>i(max)</sub>            | maximum input power  |                                        |     | 0     | _   | dBm  |

| C/I[1]                         | carrier-to-interfere | co-channel                             | _   | 6     | _   | dB   |

|                                |                      | adjacent channel at ±1 MHz             | _   | -4    | _   | dB   |

|                                | noc ratio            | alternate channel at ±2 MHz            | _   | -41   | _   | dB   |

| α <sub>image</sub> [1]         | image rejection      |                                        | _   | -41   | _   | dB   |

| $\alpha_{\text{sup(oob)}}$ [1] |                      | 30 MHz to 2000 MHz                     | -1  | _     | _   | dBm  |

|                                | out-of-band          | 2003 MHz to 2399 MHz                   | -10 | _     | _   | dBm  |

|                                | suppression          | 2484 MHz to 2997 MHz                   | -10 | _     | _   | dBm  |

|                                |                      | 3 GHz to 12.75 GHz                     | -10 | _     | _   | dBm  |

<sup>[1]</sup> The values of these parameters are from QN9080 data sheet

#### 10.2 Transmitter

#### Table 15. Transmitter characteristics

$T_{amb}$  = 25 °C; based on QN9080 characterization; not tested in production.  $V_{CC}$  = 3 V;  $f_c$  = 2440 MHz

| Symbol                 | Parameter            | Conditions | Min  | Тур | Max    | Unit |

|------------------------|----------------------|------------|------|-----|--------|------|

| f <sub>o(RF)</sub>     | RF output frequency  |            | 2400 |     | 2483.5 | MHz  |

| αCS                    | channel separation   |            |      | 2   | _      | MHz  |

| Po                     | output power         | TX power   | -20  | _   | +2     | dBm  |

| P <sub>o(RF)step</sub> | RF output power step |            | _    | 1   |        | dB   |

| P <sub>o(acc)</sub>    | TX power accuracy    | _          | -2   | _   | +2     | dB   |

**Remark:** The QN9080-001-M17 is a fully certified device supporting Bluetooth 5.0. There is a marginality (5% drift compare to the Min value of 185 kHz) on frequency deviation df2 99.9% at -40°C.

## 11. Internal antenna characteristic

#### Table 16. BOD static characteristics

T<sub>amb</sub> = 25 °C; based on characterization; not tested in production.

| Parameter       | Min  | Тур | Max  | Unit |

|-----------------|------|-----|------|------|

| Frequency range | 2400 | _   | 2480 | MHz  |