# Intelligent battery sensor with CAN and LIN

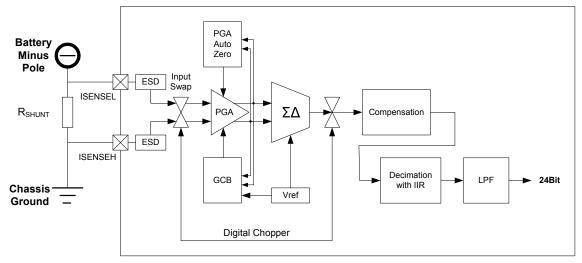

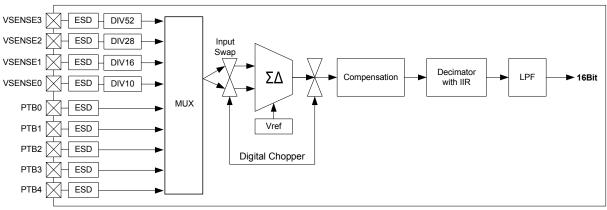

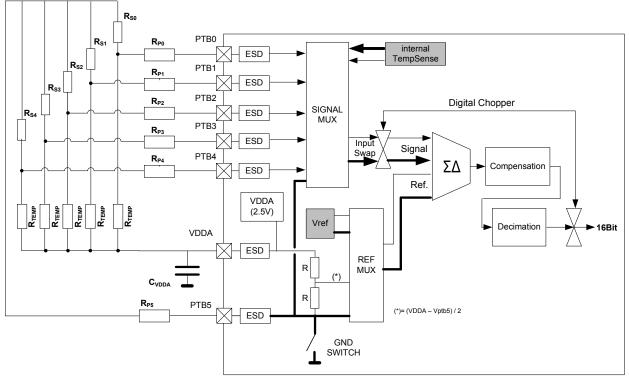

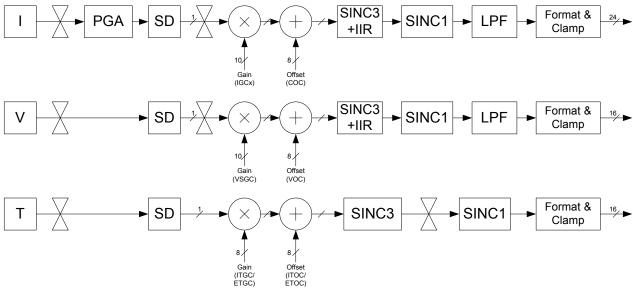

The MM9Z1\_638 is a fully integrated intelligent battery monitoring system. The device supports precise current measurement via an external shunt resistor. It features four voltage measurements via internal calibrated resistor dividers or external dividers. It includes an internal temperature sensor, allowing close proximity battery temperature measurements, plus four external temperature sensor inputs.

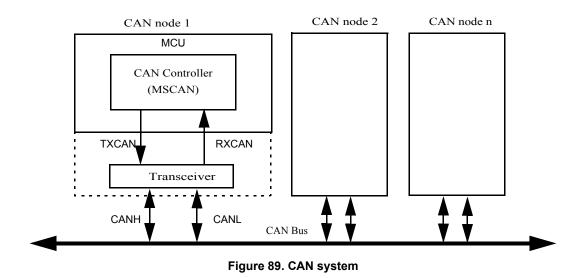

The MM9Z1\_638 features the LIN 2.2 protocol and physical interface, as well as an msCAN protocol controller, for interfacing to automotive buses. The MM9Z1\_638 is able to supply and control external CAN interfaces.

This device is powered by SMARTMOS technology.

#### Features

- Wide range battery current measurement; On-chip temperature measurement

- Four battery voltage measurements with internal resistor dividers, and up to five direct voltage measurements for use with an external resistor divider

- Measurement synchronization between voltage channels and current channels

- Five external temperature sensor inputs with internal supply for external sensors

- · Low-power modes with low-current operation

- Multiple wake-up sources: LIN, timer, high-voltage input, external CAN interface, and current threshold and integration

- Precision internal oscillator and connections for external crystal

- · LIN 2.2/ 2.1/ 2.0 protocol and physical interface

- msCAN protocol controller, and supply capability for 8 and 14 pin CAN interfaces

- MM9Z1\_638: S12Z microcontroller with 96/128 kByte Flash, 8.0 kByte RAM, 4.0 kByte EEPROM

# MM9Z1\_638

#### **BATTERY MONITORING SYSTEM**

#### Applications

- 12 V lead-acid battery monitoring

- · Multi-cell battery (Li-ion) monitoring

- · HV battery pack sensor

- Truck battery monitoring

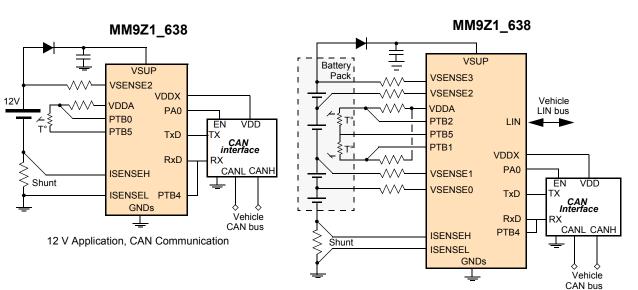

Multiple Cell Monitoring, CAN & LIN Communication,

Figure 1. 12 V simplified application diagrams

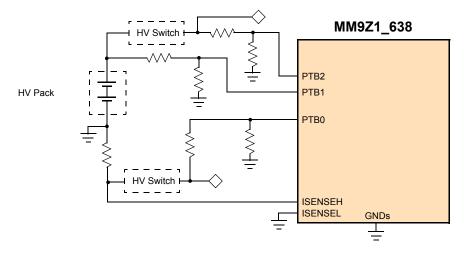

Figure 2. Simplified application diagram for HV pack monitoring - Use of an external divider principle schematic

# Table of contents

| 1 |       | ring information                                             |     |

|---|-------|--------------------------------------------------------------|-----|

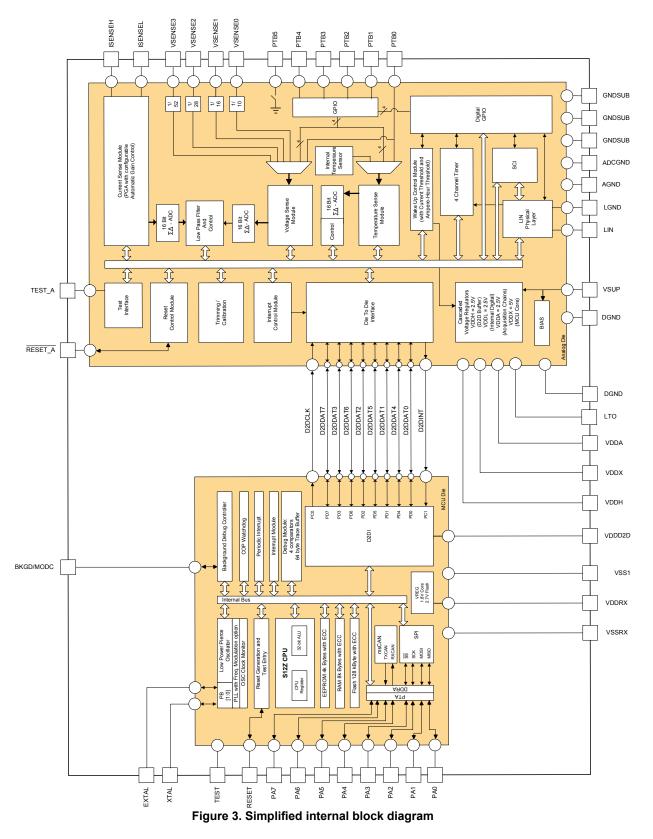

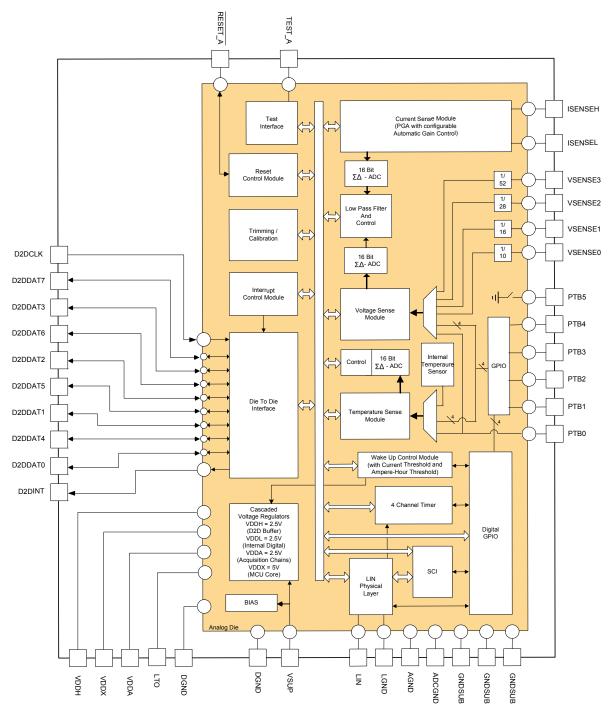

| 2 |       | nal block diagram                                            |     |

| 3 | Pin a | ssignment                                                    | . 8 |

|   | 3.1   | MM9Z1_638 pin description                                    | . 8 |

|   | 3.2   | Typical applications                                         | 10  |

| 4 |       | rical characteristics                                        |     |

|   |       | General                                                      |     |

|   |       | Absolute maximum ratings                                     |     |

|   |       | Operating conditions                                         |     |

|   |       | Supply currents                                              |     |

|   |       | 4.4.1 Measurement conditions                                 |     |

|   | 45    | Analog die electrical characteristics                        |     |

|   | 4.0   | 4.5.1 Static electrical characteristics                      |     |

|   |       | 4.5.2 Dynamic electrical characteristics                     |     |

|   | 16    | S12ZI128 electrical characteristics                          |     |

|   | 4.0   |                                                              |     |

|   |       | 4.6.1 Electrical Characteristics                             |     |

|   |       | 4.6.2 NVM electrical parameters                              |     |

|   |       | 4.6.3 Electrical specification for voltage regulator         |     |

|   |       | 4.6.4 OSCLCPcr electrical specifications                     |     |

|   |       | 4.6.5 PLL electrical specifications                          |     |

|   |       | 4.6.6 IRC electrical specifications                          |     |

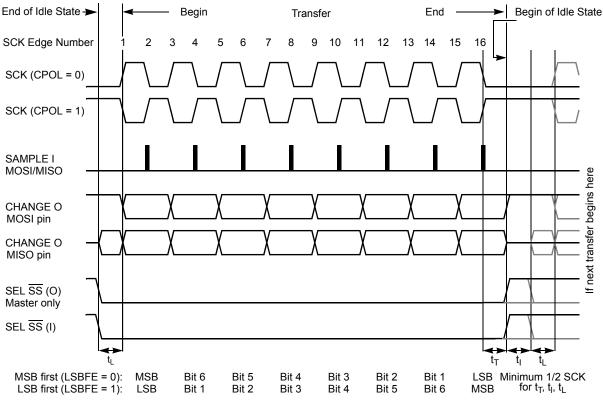

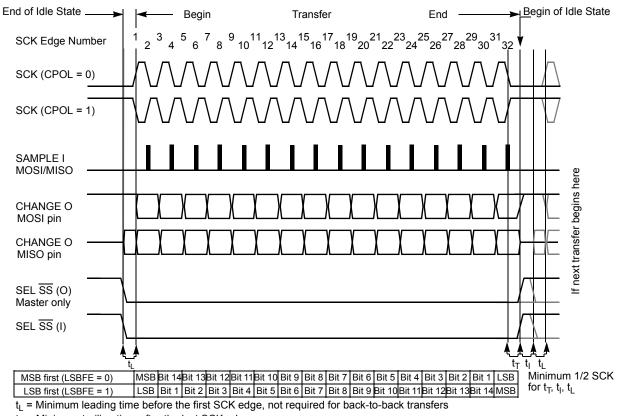

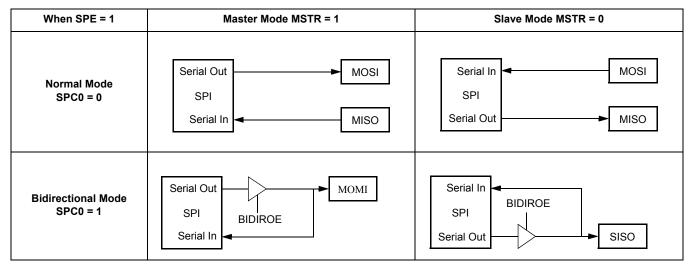

|   |       | 4.6.7 SPI electrical specifications                          |     |

|   |       | Thermal protection characteristics                           |     |

|   |       | Electromagnetic compatibility (EMC)                          |     |

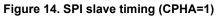

| 5 | MM9   | Z1_638 overview                                              |     |

|   | 5.1   | MM9Z1_638 analog die overview                                |     |

|   |       | 5.1.1 Introduction                                           | 42  |

|   |       | 5.1.2 Features                                               | 43  |

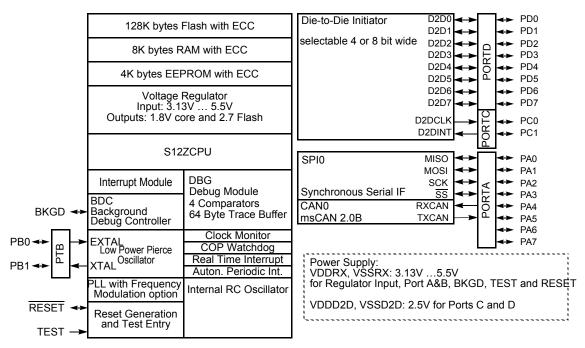

|   | 5.2   | MC9S12ZI128 overview                                         | 44  |

|   |       | 5.2.1 Introduction                                           |     |

|   |       | 5.2.2 Features                                               |     |

|   |       | 5.2.3 Module features                                        |     |

|   |       | 5.2.4 Block diagram                                          |     |

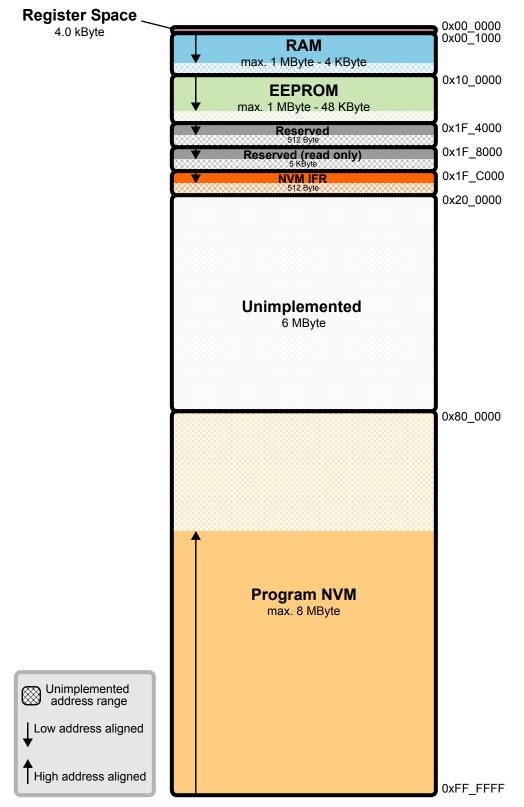

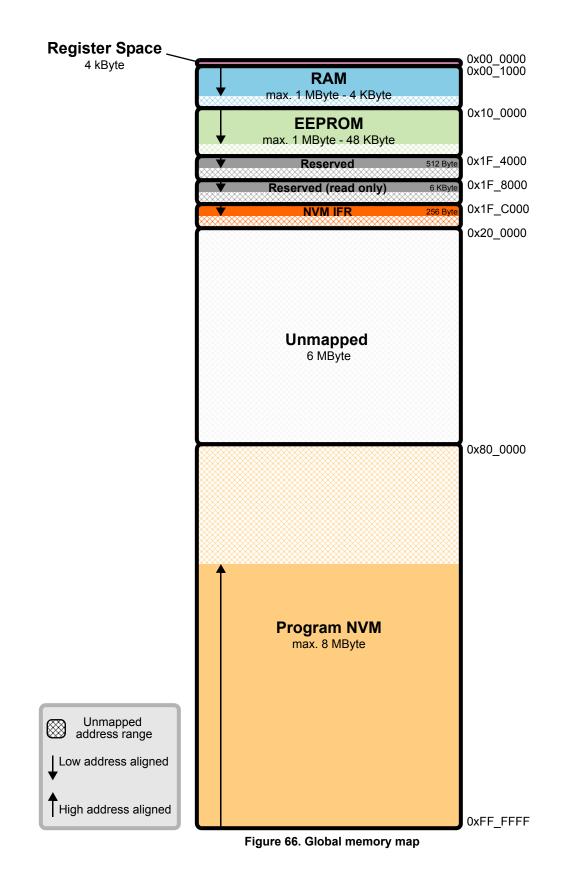

|   |       | 5.2.5 Device memory map                                      |     |

|   |       | 5.2.6 Modes of operation                                     |     |

|   |       | 5.2.7 Security                                               |     |

|   |       | 5.2.8 Resets and interrupts                                  |     |

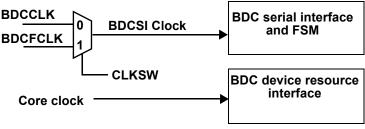

|   |       | 5.2.9 BDC clock source connectivity                          |     |

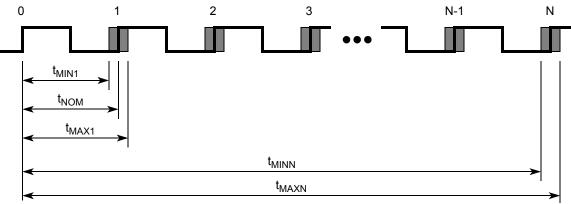

|   |       | 5.2.10COP configuration                                      |     |

| 6 | Euro  | tional description and application information               |     |

| 0 |       |                                                              |     |

|   | 0.1   | Device register map                                          |     |

|   | 6.0   | 6.1.1 Detailed module register map                           |     |

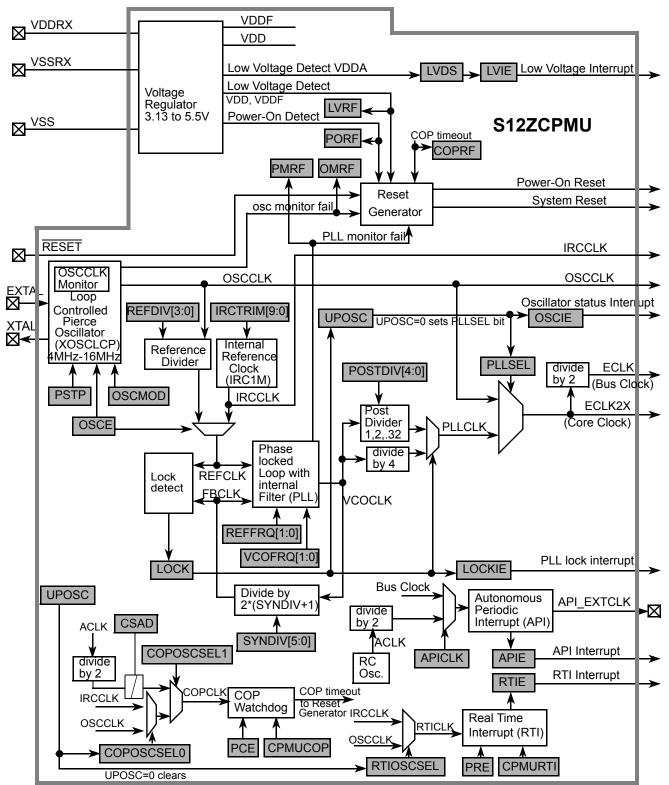

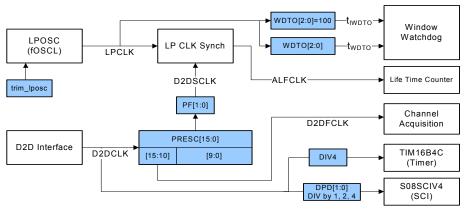

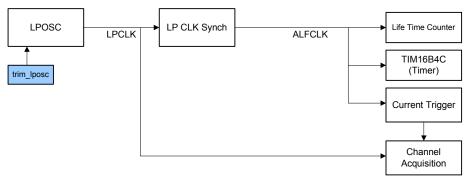

|   | 0.2   | Clock, reset, and power management unit (S12ZCPMU + PCR)     |     |

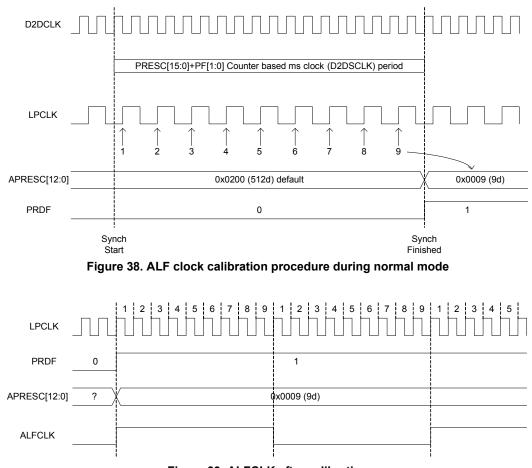

|   |       | 6.2.1 S12Z clock, reset and power management unit (S12ZCPMU) |     |

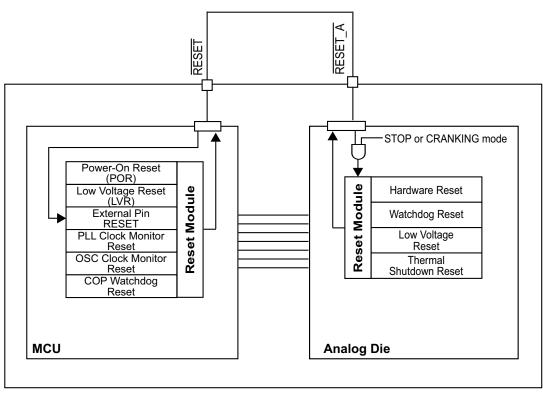

|   |       | 6.2.2 Analog die - power, clock and resets - PCR             |     |

|   |       | 6.2.3 Window watchdog                                        |     |

|   | 6.3   |                                                              | 133 |

|   |       |                                                              | 133 |

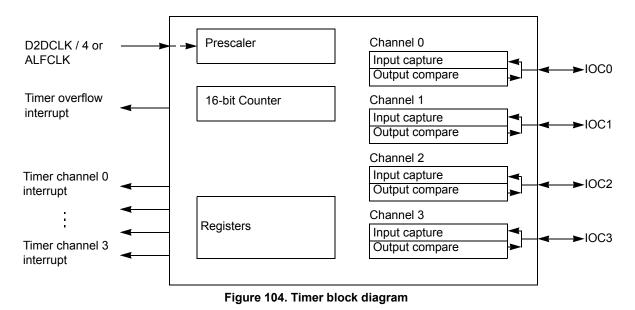

|   |       | 6.3.2 Block diagrams                                         |     |

|   |       |                                                              | 136 |

|   | 6.4   | General purpose I/O - GPIO                                   |     |

|   |       | 6.4.1 Introduction                                           | 174 |

|   |       | 6.4.2 Features                                               | 174 |

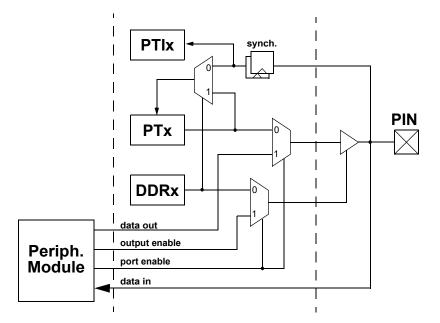

|   |       | 6.4.3 Block diagram                                          | 175 |

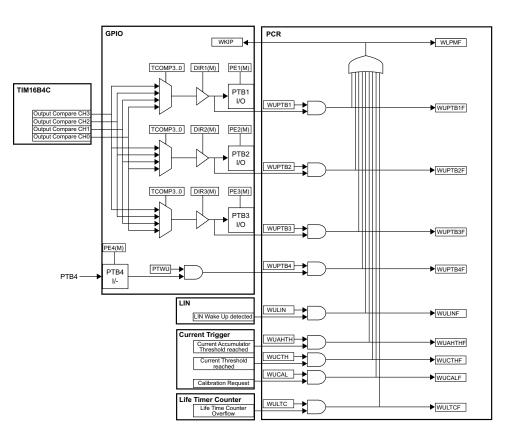

|   |       | 6.4.4 Modes of operation                                     | 176 |

|   |       | 6.4.5 Memory map and registers                               | 176 |

|   |       |                                                              |     |

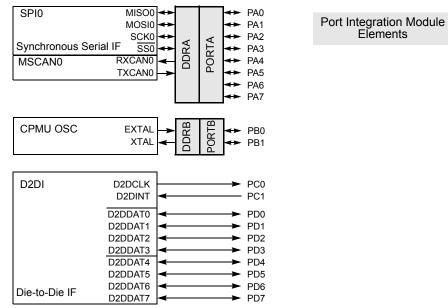

| 6.5  | Port integration module (S12ZIPIMV1)                |     |

|------|-----------------------------------------------------|-----|

|      | 6.5.1 Introduction                                  |     |

|      | 6.5.2 External signal description                   |     |

|      | 6.3.3 Channel acquisition                           |     |

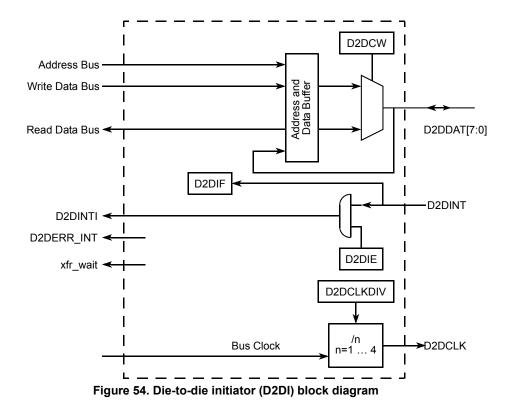

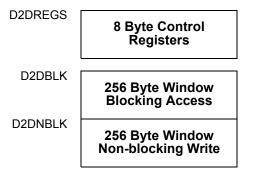

| 6.6  | Die to die interface                                |     |

|      | 6.6.1 Die-to-die initiator (D2DIV2)                 |     |

|      | 6.6.2 Die to die interface - target                 | 205 |

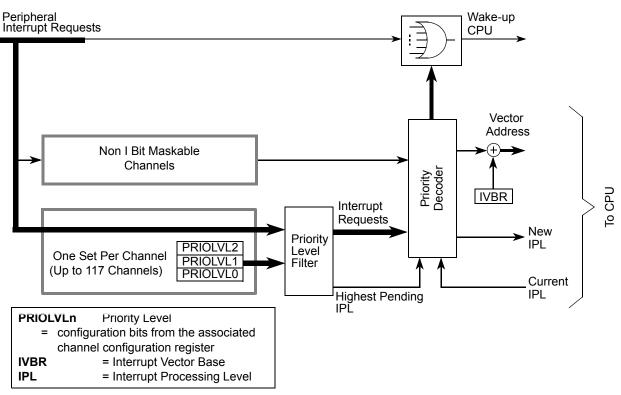

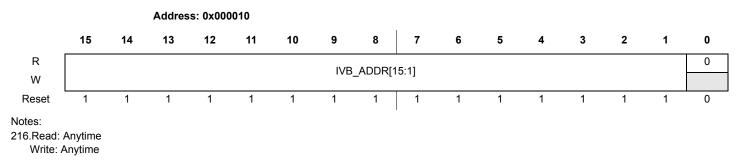

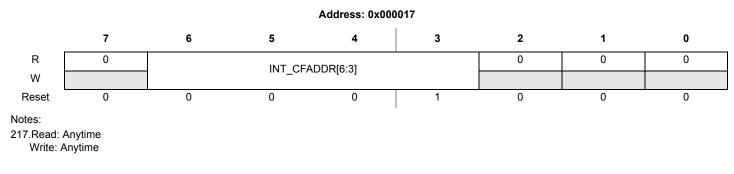

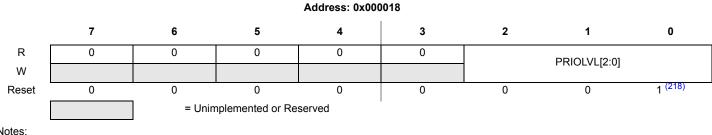

| 6.7  | Interrupt module (S12ZINTV0 + IRQ)                  | 207 |

|      | 6.7.1 Interrupt (S12ZINTV0)                         |     |

|      | 6.7.2 Interrupt module - IRQ                        | 217 |

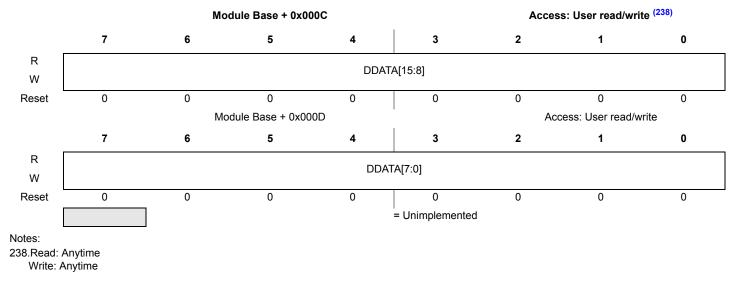

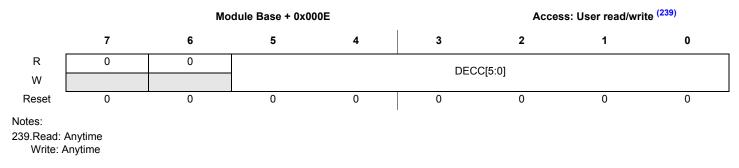

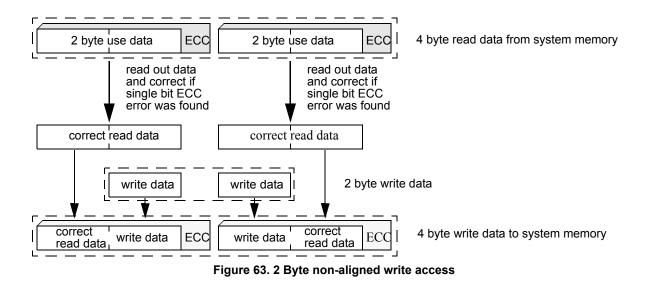

| 6.8  | ECC generation module (SRAM_ECCV1)                  |     |

|      | 6.8.1 Introduction                                  |     |

|      | 6.8.2 Memory map and register definition            |     |

|      | 6.8.3 Functional description                        |     |

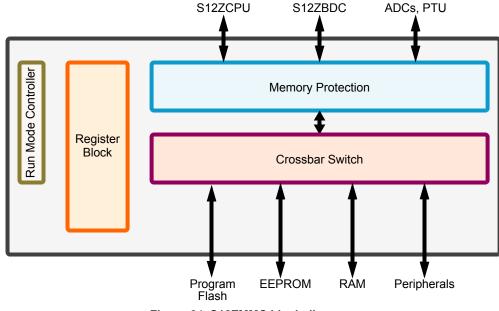

| 6.9  | Memory mapping control (S12ZMMCV1)                  |     |

|      | 6.9.1 Introduction                                  |     |

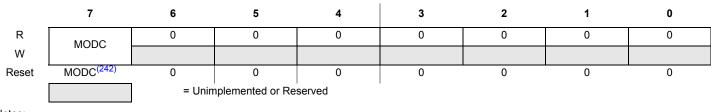

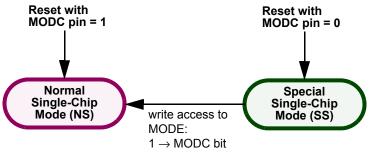

|      | 6.9.2 External signal description                   | 233 |

|      | 6.9.3 Memory map and register definition            |     |

|      | 6.9.4 Functional description                        |     |

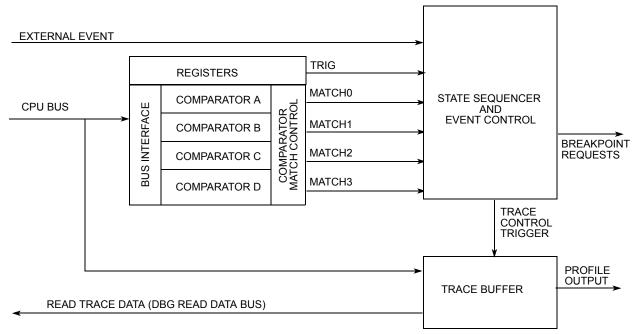

| 6.10 | S12Z debug module (S12ZDBGV2)                       | 240 |

|      | 6.10.1 Introduction                                 |     |

|      | 6.10.2External signal description                   | 242 |

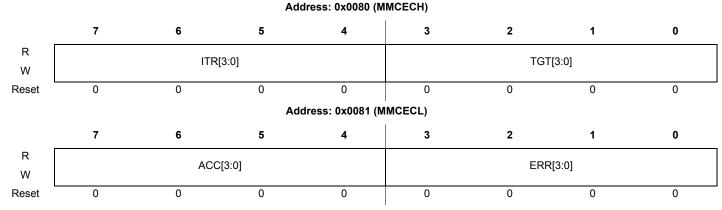

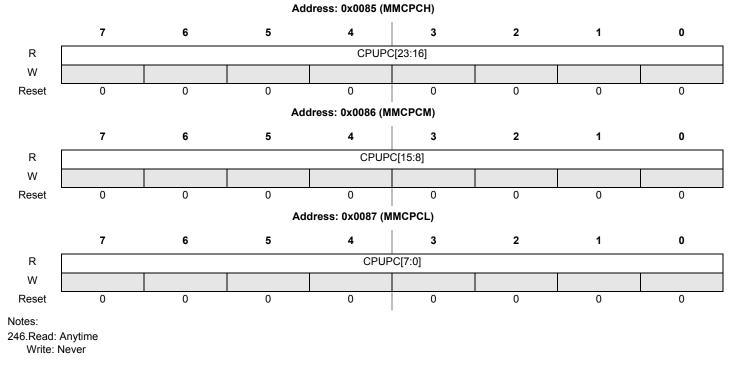

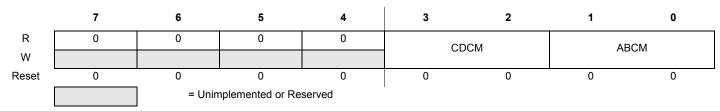

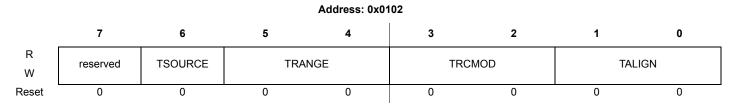

|      | 6.10.3Memory map and registers                      |     |

|      | 6.10.4Functional description                        |     |

|      | 6.10.5Application information                       | 279 |

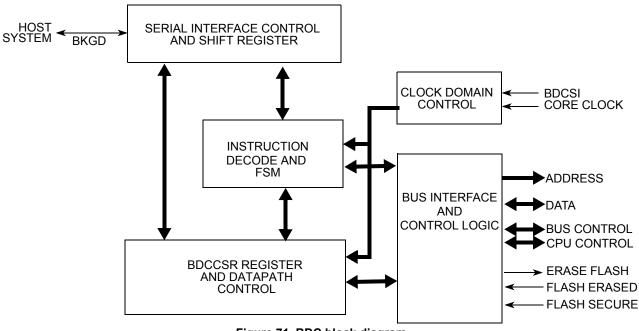

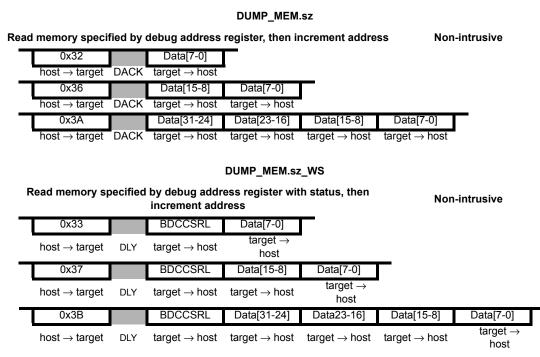

| 6.11 | Background debug controller (S12ZBDCV1)             | 280 |

|      | 6.11.1 Introduction                                 |     |

|      | 6.11.2 External signal description                  |     |

|      | 6.11.3 Memory map and register definition           | 283 |

|      | 6.11.4 Functional description                       |     |

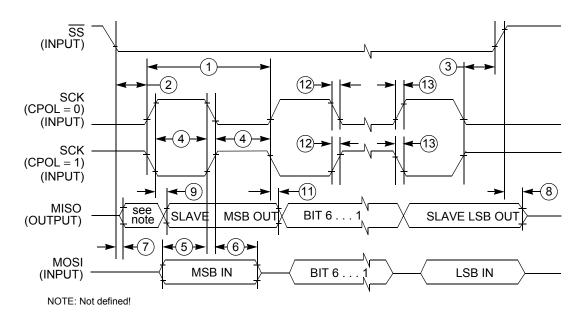

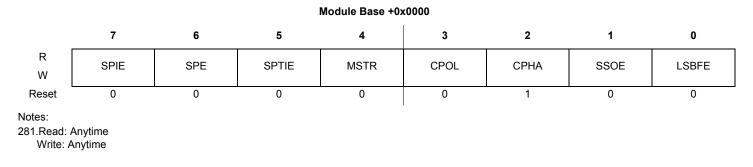

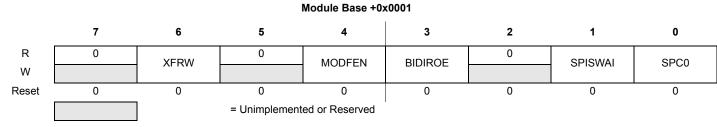

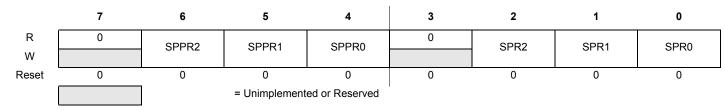

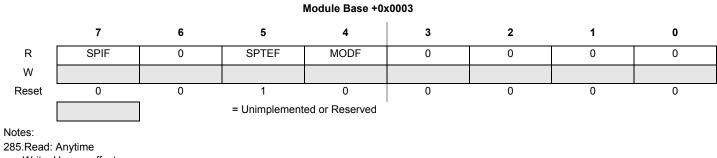

| 6.12 | Serial peripheral interface (S12SPIV5)              |     |

|      | 6.12.1 Introduction                                 |     |

|      | 6.12.2External signal description                   |     |

|      | 6.12.3Memory map and register definition            |     |

|      | 6.12.4Functional description                        | 315 |

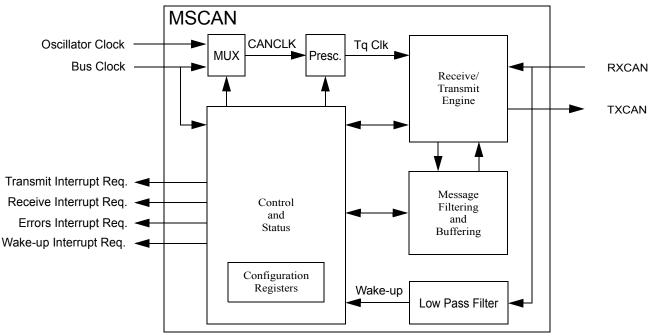

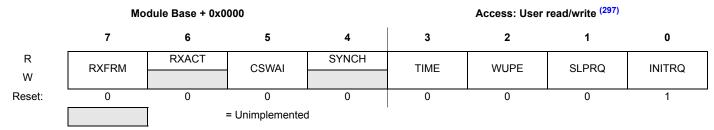

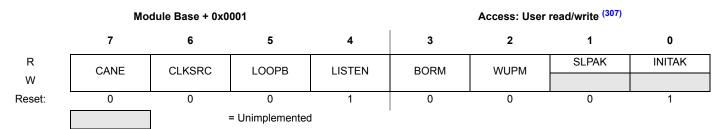

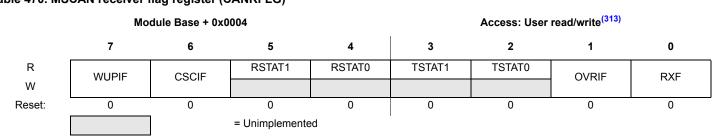

| 6.13 | NXP's scalable controller area network (S12MSCANV3) |     |

|      | 6.13.1 Introduction                                 |     |

|      | 6.13.2External signal description                   |     |

|      | 6.13.3Memory map and register definition            |     |

|      | 6.13.4Functional Description                        |     |

|      | 6.13.5Initialization/application information        |     |

| 6.14 |                                                     | 365 |

|      |                                                     | 365 |

|      | 6.14.2External signal description                   |     |

|      | 6.14.3Memory map and registers                      | 367 |

|      | 6.14.4Functional description                        | 385 |

|      | 6.14.5Security                                      | 403 |

|      | 6.14.6Initialization                                |     |

| 6.15 |                                                     | 405 |

|      | 6.15.1 Introduction                                 |     |

|      | 6.15.2Signal description                            |     |

|      | 6.15.3Memory map and registers                      | 406 |

|      | 6.15.4Functional description                        |     |

|      | 6.15.5Resets                                        |     |

|      |                                                     | 418 |

| 6.16 | Life time counter (LTC)                             |     |

|      | 6.16.1Introduction                                  |     |

|      | 6.16.2Memory map and registers                      | 419 |

|   | 6.17 Serial communication interface (S08SCIV4) | 422 |

|---|------------------------------------------------|-----|

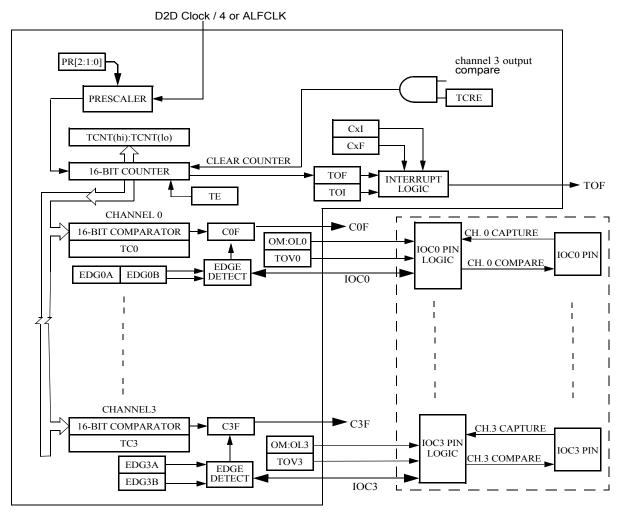

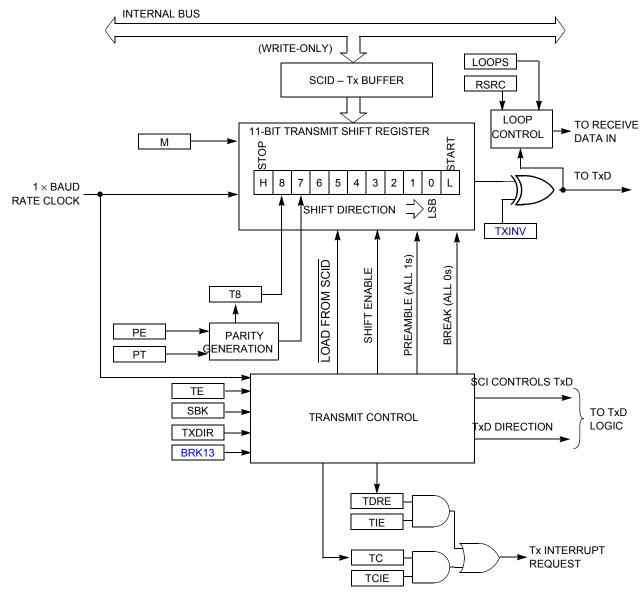

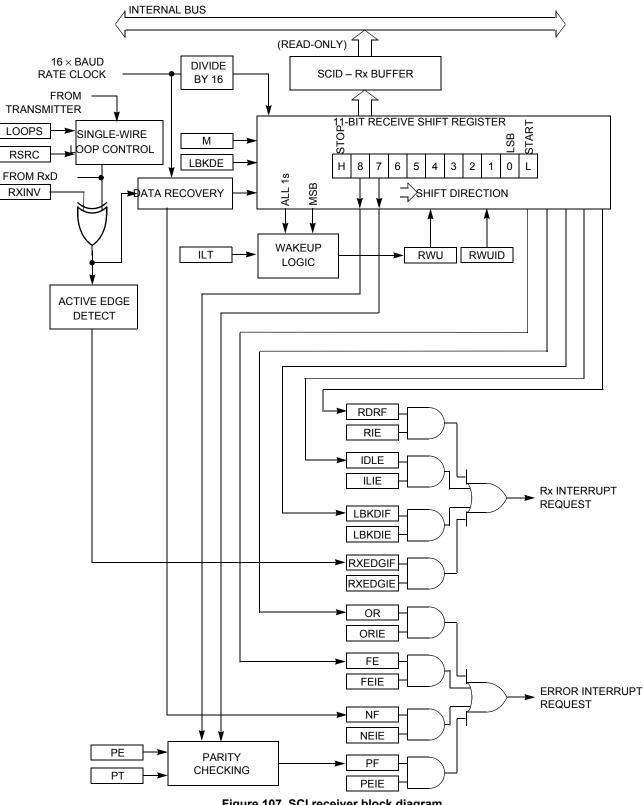

|   | 6.17.1 Introduction                            | 422 |

|   | 6.17.2Memory map and registers                 | 425 |

|   | 6.17.3Functional description                   | 432 |

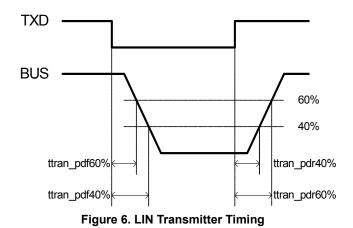

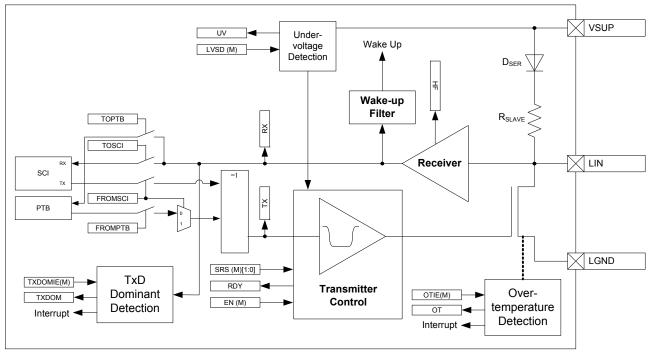

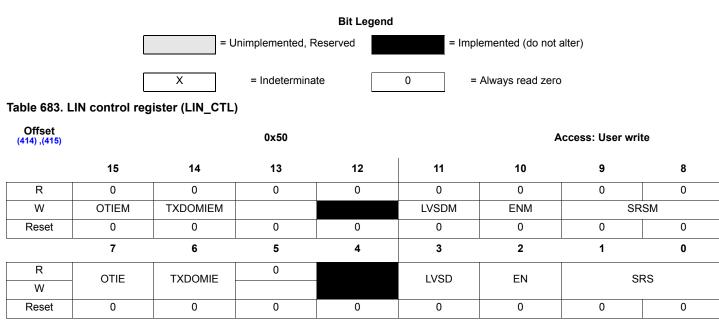

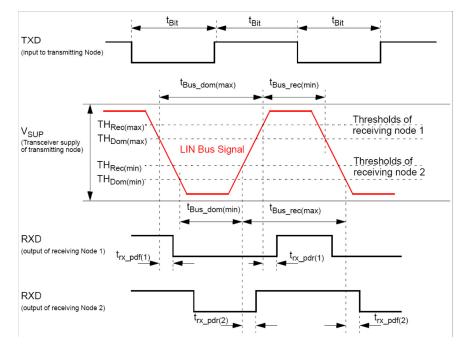

|   | 6.18 LIN                                       | 436 |

|   | 6.18.1Introduction                             | 436 |

|   | 6.18.20verview                                 | 436 |

|   | 6.18.3Memory map and registers                 | 438 |

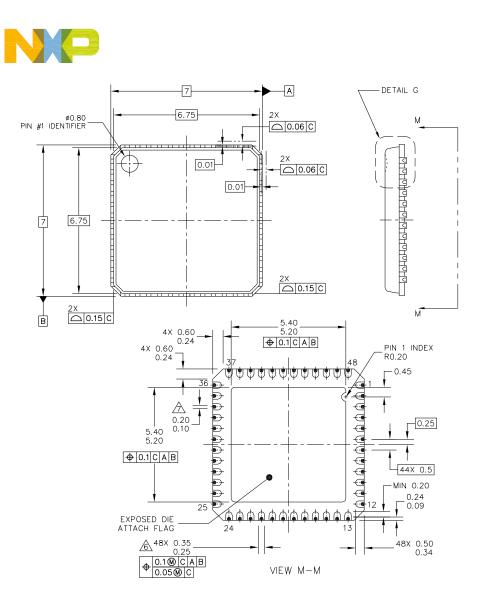

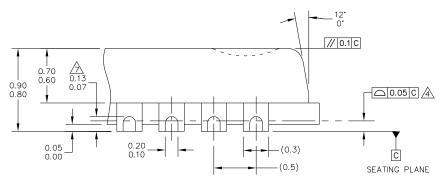

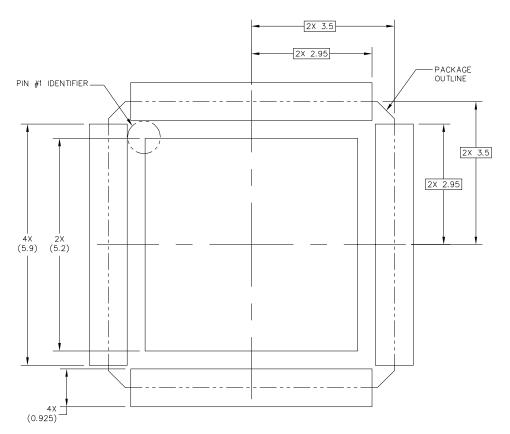

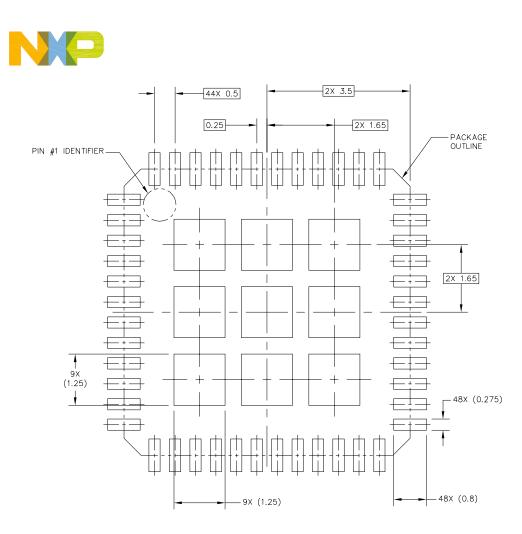

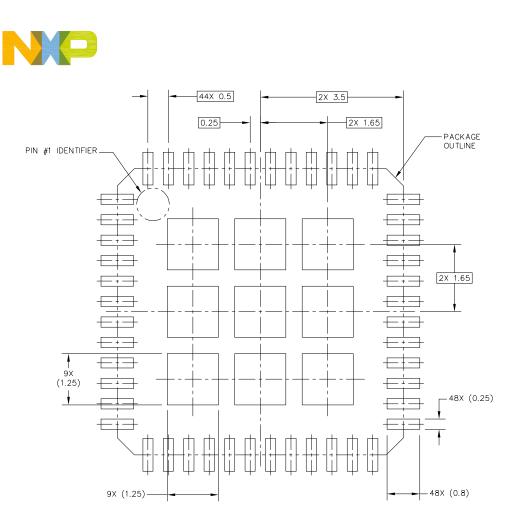

| 7 | Packaging                                      | 444 |

|   | 7.1 Package dimensions                         | 444 |

| 8 | Revision history                               | 450 |

# 1 Ordering information

#### Table 1. Ordering information

| Device<br>(Add an R2 suffix for tape and reel orders) | Temperature range (T <sub>A</sub> ) | Package   | Flash (kB) | RAM (kB) | EEPROM (kB) |

|-------------------------------------------------------|-------------------------------------|-----------|------------|----------|-------------|

| MM9Z1J638BM2EP                                        | -40 °C to 125 °C                    | 48 QFN-EP | 128        | 8.0      | 4.0         |

| MM9Z1I638BM2EP                                        | -40 010 123 0                       |           | 96         | 0.0      | 4.0         |

# 2 Internal block diagram

**PIN ASSIGNMENT**

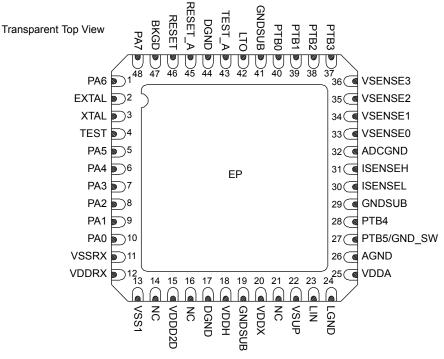

# 3 Pin assignment

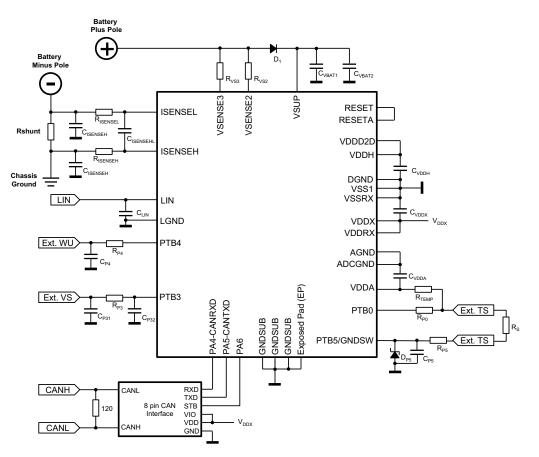

Figure 4. MM9Z1\_638 pin connections

# 3.1 MM9Z1\_638 pin description

The following table gives a brief description of all available pins on the MM9Z1\_638 device. Refer to the highlighted chapter for detailed information

| Pin # | Pin name | Formal name     | Description                                                                                                                                                                                                                                                                       |  |  |

|-------|----------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 1     | PA6      | MCU PA6         | General purpose port A input or output pin 6. See Port integration module (S12ZIPIMV1).                                                                                                                                                                                           |  |  |

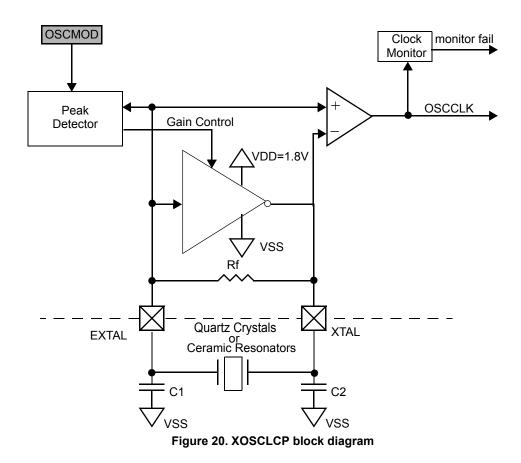

| 2     | EXTAL    | MCU Oscillator  | EXTAL is one of the optional crystal/resonator drivers and external clock pins, and the PB0 port may be used as a general purpose I/O. On reset, all the device clocks are derived from the internal reference clock. See S12Z clock, reset and power management unit (S12ZCPMU). |  |  |

| 3     | XTAL     | MCU Oscillator  | XTAL is one of the optional crystal/resonator drivers and external clock pins, and the PB1 port may be used as a general purpose I/O. On reset all the device clocks are derived from the internal reference clock. See S12Z clock, reset and power management unit (S12ZCPMU).   |  |  |

| 4     | TEST     | MCU Test        | This input only pin is reserved for test. This pin has a pull-down device. The TEST pin mube tied to VSSRX in user mode.                                                                                                                                                          |  |  |

| 5     | PA5      | MCU PA5/CAN TXD | General purpose port A input or output pin 5. This pin is shared with the TXDCAN of the integrated msCAN module. See Port integration module (S12ZIPIMV1).                                                                                                                        |  |  |

| 6     | PA4      | MCU PA4/CAN RXD | General purpose port A input or output pin 4. This pin is shared with the RXDCAN of the integrated msCAN module. See Port integration module (S12ZIPIMV1).                                                                                                                        |  |  |

| 7     | PA3      | MCU PA3 / SS    | General purpose port A input or output pin 3, shared with the SS signal of the integrated SPI interface. See Port integration module (S12ZIPIMV1).                                                                                                                                |  |  |

| 8     | PA2      | MCU PA2 / SCK   | General purpose port A input or output pin 2, shared with the SCLK signal of the integrated SPI interface. See Port integration module (S12ZIPIMV1).                                                                                                                              |  |  |

#### MM9Z1\_638

#### Table 2. MM9Z1\_638 pin description (continued)

| Pin # | Pin name        | Formal name                               | Description                                                                                                                                                                                                                                                                                                                                                         |  |  |

|-------|-----------------|-------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 9     | PA1             | MCU PA1 / MOSI                            | General purpose port A input or output pin 1, shared with the MOSI signal of the integrated SPI interface. See Port integration module (S12ZIPIMV1).                                                                                                                                                                                                                |  |  |

| 10    | PA0             | MCU PA0 / MISO                            | General purpose port A input or output pin 0, shared with the MISO signal of the integrated SPI interface. See Port integration module (S12ZIPIMV1).                                                                                                                                                                                                                |  |  |

| 11    | VSSRX           | MCU 5.0 V Ground                          | External ground for the MCU - VDDRX return path.                                                                                                                                                                                                                                                                                                                    |  |  |

| 12    | VDDRX           | MCU 5.0 V Supply                          | 5.0 V MCU input power supply. This pin must be connected to VDDX.                                                                                                                                                                                                                                                                                                   |  |  |

| 13    | VSS1            | MCU 2.5 V Ground                          | External ground for the MCU - VDDD2D return path.                                                                                                                                                                                                                                                                                                                   |  |  |

| 14    | NC              | Not connected                             | This pin must be grounded in the application.                                                                                                                                                                                                                                                                                                                       |  |  |

| 15    | VDDD2D          | MCU 2.5 V Supply                          | 2.5 V MCU input power supply for the die to die interface. This pin must be connected to VDDH.                                                                                                                                                                                                                                                                      |  |  |

| 16    | NC              | Not connected                             | This pin must be grounded in the application.                                                                                                                                                                                                                                                                                                                       |  |  |

| 17    | DGND            | Digital Ground                            | This pin is the device digital ground connection.                                                                                                                                                                                                                                                                                                                   |  |  |

| 18    | VDDH            | Voltage Regulator Output<br>2.5 V         | 2.5 V output voltage. This pin must be connected to the VDDD2D. An external capacitor ( $C_{VDDH}$ ) is needed.                                                                                                                                                                                                                                                     |  |  |

| 19    | GNDSUB          | Substrate Ground                          | Substrate ground connection.                                                                                                                                                                                                                                                                                                                                        |  |  |

| 20    | VDDX            | MCU 5.0 V and External<br>CAN Supply      | 5.0 V output power supply for the internal MCU die and an external 8 or 14 pin CAN interface. This pin must be connected to VDDRX. An external capacitor ( $C_{VDDX}$ ) is needed.                                                                                                                                                                                  |  |  |

| 21    | NC              | Not connected                             | This pin is not connected to the die. Within the application, it could be connected or left open.                                                                                                                                                                                                                                                                   |  |  |

| 22    | VSUP            | Power Supply                              | This pin is the device power supply pin. A reverse battery protection diode is required. External capacitor(s) needed.                                                                                                                                                                                                                                              |  |  |

| 23    | LIN             | LIN Bus                                   | This pin is the single-wire LIN bus.                                                                                                                                                                                                                                                                                                                                |  |  |

| 24    | LGND            | LIN Ground                                | This pin is the device LIN ground connection.                                                                                                                                                                                                                                                                                                                       |  |  |

| 25    | VDDA            | Analog Voltage Regulator<br>Output        | Voltage regulator output pin, to supply the analog front end, and the external temperature sensor circuitry. An external capacitor ( $C_{VDDA}$ ) is needed.                                                                                                                                                                                                        |  |  |

| 26    | AGND            | Analog Ground                             | This pin is the device analog voltage regulator and LP oscillator ground connection.                                                                                                                                                                                                                                                                                |  |  |

| 27    | PTB5/<br>GND_SW | GND Switch Temp                           | This pin is a switch to GND for connection of the external temperature sensors circuitry.                                                                                                                                                                                                                                                                           |  |  |

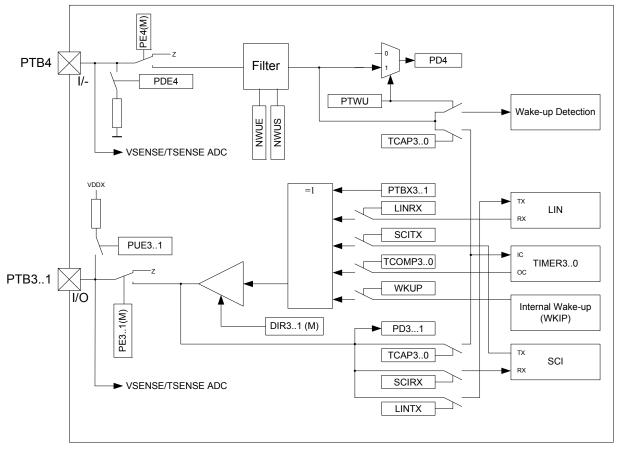

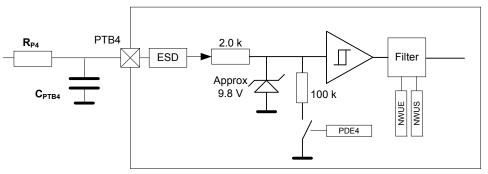

| 28    | PTB4            | Analog Input & General<br>Purpose Input 4 | General purpose 5.0 V Input (connection to timer and selectable pull-down). This pin<br>shares several functions:<br>Temperature sensor input.<br>Direct voltage sense, used with an external resistor divider<br>Wake-up input.<br>General purpose 5.0 V input                                                                                                     |  |  |

| 29    | GNDSUB          | Substrate Ground                          | Substrate ground connection.                                                                                                                                                                                                                                                                                                                                        |  |  |

| 30    | ISENSEL         | Current Sense L                           | Current sense input "Low". This pin is used in combination with ISENSEH to measure the voltage drop across a shunt resistor.                                                                                                                                                                                                                                        |  |  |

| 31    | ISENSEH         | Current Sense H                           | Current sense input "high". This pin is used in combination with ISENSEL to measure the voltage drop across a shunt resistor.                                                                                                                                                                                                                                       |  |  |

| 32    | ADCGND          | Analog Digital Converter<br>Ground        | Analog digital converter ground connection.                                                                                                                                                                                                                                                                                                                         |  |  |

| 33    | VSENSE0         | Voltage Sense 0                           | Precision battery voltage measurement input. This pin can be connected directly to the battery line for voltage measurements. The voltage preset at this input is scaled down by an internal voltage divider. The pin is self protected against reverse battery connections. An external resistor (R <sub>VSENSE</sub> ) is needed for protection.                  |  |  |

| 34    | VSENSE1         | Voltage Sense 1                           | <ul> <li>Precision battery voltage measurement input. This pin can be connected directly to the battery line for voltage measurements. The voltage preset at this input is scaled down by an internal voltage divider. The pin is self-protected against reverse battery connections. A external resistor (R<sub>VSENSE</sub>) is needed for protection.</li> </ul> |  |  |

#### **PIN ASSIGNMENT**

| Table 2. MM9Z1 | _638 pin | description | (continued) |

|----------------|----------|-------------|-------------|

|----------------|----------|-------------|-------------|

| Pin # | Pin name | Formal name                             | Description                                                                                                                                                                                                                                                                                                                                        |  |  |

|-------|----------|-----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 35    | VSENSE2  | Voltage Sense 2                         | Precision battery voltage measurement input. This pin can be connected directly to the battery line for voltage measurements. The voltage preset at this input is scaled down by an internal voltage divider. The pin is self-protected against reverse battery connections. An external resistor ( $R_{VSENSE}$ ) is needed for protection.       |  |  |

| 36    | VSENSE3  | Voltage Sense 3                         | Precision battery voltage measurement input. This pin can be connected directly to the battery line for voltage measurements. The voltage preset at this input is scaled down by an internal voltage divider. The pin is self-protected against reverse battery connections. An external resistor (R <sub>VSENSE</sub> ) is needed for protection. |  |  |

| 37    | PTB3     | Analog Input & General<br>Purpose I/O 3 | This pin shares several functions:<br>Temperature sensor input.<br>Direct voltage sense, used with an external resistor divider<br>General purpose 5.0 V I/O (connection to timer, LIN SCI, and selectable pull-up to VDDX).                                                                                                                       |  |  |

| 38    | PTB2     | Analog Input & General<br>Purpose I/O 2 | This pin shares several functions:<br>Temperature sensor input.<br>Direct voltage sense, used with an external resistor divider<br>General purpose 5.0 V I/O (connection to timer, LIN SCI, and selectable pull-up to VDDX).                                                                                                                       |  |  |

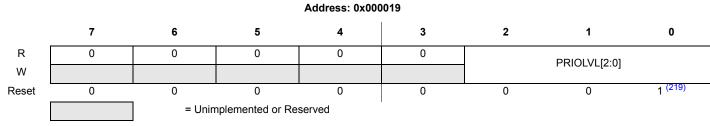

| 39    | PTB1     | Analog Input & General<br>Purpose I/O 1 | This pin shares several functions:<br>Temperature sensor input.<br>Direct voltage sense, used with an external resistor divider<br>General purpose 5.0 V I/O (connection to timer, LIN SCI, and selectable pull-up to VDDX).                                                                                                                       |  |  |

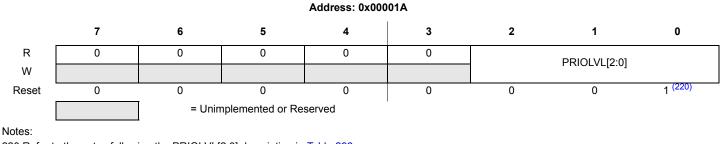

| 40    | PTB0     | Analog Input 0                          | This pin shares several functions:<br>Temperature sensor input.<br>Direct voltage sense, used with an external resistor divider                                                                                                                                                                                                                    |  |  |

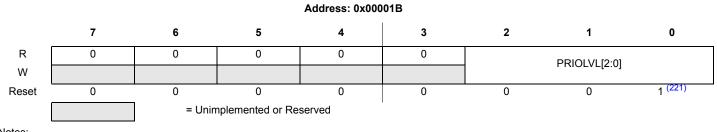

| 41    | GNDSUB   | Substrate Ground                        | Substrate ground connection.                                                                                                                                                                                                                                                                                                                       |  |  |

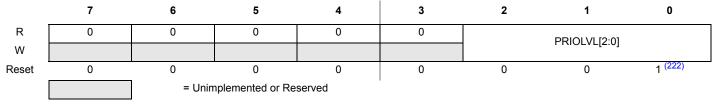

| 42    | LTO      | Logic Test Output                       | Reserved pin for logic test output signal. Typical voltage is 2.5 V. Should be left open during device operation.                                                                                                                                                                                                                                  |  |  |

| 43    | TEST_A   | Test Mode                               | Test mode pin. This pin must be grounded in applications.                                                                                                                                                                                                                                                                                          |  |  |

| 44    | DGND     | Digital Ground                          | This pin is the device digital ground connection.                                                                                                                                                                                                                                                                                                  |  |  |

| 45    | RESET_A  | Reset I/O                               | Reset output pin of the analog die in Normal mode. Bidirectional reset I/O of the analog die in Stop mode. Active low signal with internal pull-up to VDDX. This pin must be connected to RESET.                                                                                                                                                   |  |  |

| 46    | RESET    | MCU Reset                               | Bidirectional reset I/O pin of the MCU die. Active low signal with internal pull-up to VDDRX. This pin must be connected to RESETA.                                                                                                                                                                                                                |  |  |

| 47    | BKGD     | MCU Background Debug<br>and Mode        | The BKGD/MODC pin is used as a pseudo-open-drain pin for the background debug communication. It is used as an MCU operating mode select pin during reset. The state this pin is latched to the MODC bit at the rising edge of RESET. The BKGD pin has a pull-t device. See Background debug controller (BDC).                                      |  |  |

| 48    | PA7      | MCU PA7                                 | General purpose port A input or output pin 7. See Port integration module (S12ZIPIMV1).                                                                                                                                                                                                                                                            |  |  |

# 3.2 Typical applications

Figure 5 and Table 3 show a typical application to illustrate some of the device capabilities.

Both CAN and LIN communications are described.

VSENSE\_2 and VSENSE\_3 inputs are used to show possible redundancy.

External wake-up via PTB4 is used.

Single external voltage sense is used utilizing PTB3.

Single external temperature sense is used utilizing PTB0.

Note: Module GND connected to Battery Minus or Chassis Ground - based on configuration

Figure 5. Typical application example

| Name                 | Description                  | value                 | Comment                                                                              |

|----------------------|------------------------------|-----------------------|--------------------------------------------------------------------------------------|

| D1                   | Reverse Battery Diode        | N/A                   |                                                                                      |

| C <sub>VBAT1</sub>   | Battery Decoupling Capacitor | 4.7 μF                |                                                                                      |

| C <sub>VBAT2</sub>   | Battery Decoupling Capacitor | 100 nF                |                                                                                      |

| R <sub>VS2</sub>     | Vsense Current Limitation    | 2.2 kΩ                |                                                                                      |

| R <sub>VS3</sub>     | Vsense Current Limitation    | 2.2 kΩ                |                                                                                      |

| R <sub>SHUNT</sub>   | Current Measurement          | 50 to 200 $\mu\Omega$ |                                                                                      |

| RISENSEL             | EMC resistor                 | max 500 $\Omega$      |                                                                                      |

| R <sub>ISENSEH</sub> | EMC resistor                 | max 500 Ω             |                                                                                      |

| CISENSEL             | EMC capacitor                | 2.2 nF (typ)          | Selection for best EMC performance                                                   |

| CISENSEH             | EMC capacitor                | 2.2 nF (typ)          |                                                                                      |

| CISENSEHL            | EMC capacitor                | 2.2 nF (typ)          |                                                                                      |

| C <sub>LIN</sub>     | LIN bus filter               | Optional<br>220 pF    | Selection per OEM requirement, for EMC and ESD performance.                          |

| R <sub>P4</sub>      | PTB4 Protection Resistor     | 10 kΩ                 | Minimum value to meet max rating                                                     |

| C <sub>P4</sub>      | PTB4 Protection Capacitor    | 10 nF                 | Minimum value to meet max rating                                                     |

| C <sub>VDDX</sub>    | VDDX Decoupling Capacitor    | 470 nF                |                                                                                      |

| C <sub>VDDH</sub>    | VDDH Decoupling Capacitor    | 470 nF                | An additional 4.7 nF capacitor might be required for specific EMC ter<br>conditions. |

#### Tab

#### **PIN ASSIGNMENT**

#### Table 3. External components (continued)

| Name              | Description                        | value  | Comment                                                                                                                                                                                                         |

|-------------------|------------------------------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| C <sub>VDDA</sub> | VDDA Decoupling Capacitor          | 47 nF  |                                                                                                                                                                                                                 |

| R <sub>TEMP</sub> | Temp Sense Serial Resistor         | 100 kΩ |                                                                                                                                                                                                                 |

| R <sub>S</sub>    | Temperature Sensor                 | N/A    | ex: NTC temperature Sensor                                                                                                                                                                                      |

| R <sub>P0</sub>   | PTB0 Protection Resistor           | 2.2 kΩ |                                                                                                                                                                                                                 |

| R <sub>P5</sub>   | PTB5 Protection Resistor           | 1.0 kΩ | To meet maximum rating. Higher or different value might be required.                                                                                                                                            |

| C <sub>P5</sub>   | PTB5 Protection Capacitor          | 2.2 nF | These components are optional and required to sustain EMC and ESD requirements when the pins go outside of the module.                                                                                          |

| D <sub>P5</sub>   | PTB5 Protection Zener Diode        | 5.1 V  |                                                                                                                                                                                                                 |

| C <sub>P31</sub>  | VSENSE_EXT Protection<br>Capacitor | 2.2 nF |                                                                                                                                                                                                                 |

| C <sub>P32</sub>  | VSENSE_EXT Protection<br>Capacitor | 22 nF  | <ul> <li>To meet maximum rating. Higher or different value might be required. These components are optional and required to sustain EMC and ESD requirements when the pins go outside of the module.</li> </ul> |

| R <sub>P3</sub>   | VSENSE_EXT Protection<br>Resistor  | 10 kΩ  |                                                                                                                                                                                                                 |

# 4 Electrical characteristics

# 4.1 General

This section contains electrical information for the microcontroller and the analog die.

# 4.2 Absolute maximum ratings

Absolute maximum ratings are stress ratings only. A functional operation under or outside these maximums is not guaranteed. Stress beyond these limits may affect the reliability, or cause permanent damage of the device.

This device contains circuitry protecting against damage due to high static voltage or electrical fields. However, it is advised that normal precautions be taken to avoid application of any voltages higher than maximum rated voltages to this high-impedance circuit. Reliability of operation is enhanced if unused inputs are tied to an appropriate voltage level. All voltages are with respect to ground, unless otherwise noted.

#### Table 4. Absolute maximum electrical ratings - analog die

|                                                                                    | Symbol                 | Value                          | Unit |

|------------------------------------------------------------------------------------|------------------------|--------------------------------|------|

| VSUP pin voltage                                                                   | V <sub>VSUP</sub>      | -0.3 to 42                     | V    |

| VSENSE0, VSENSE1, VSENSE2 pin voltage with 2.2 k resistor in serial <sup>(1)</sup> | V <sub>VSENSE012</sub> | -40 to 42                      | V    |

| VSENSE3 pin voltage with 2.2k resistor in serial <sup>(1)</sup>                    | V <sub>VSENSE3</sub>   | -40 to 62                      | V    |

| PTB0, PTB1, PTB2, and PTB3 Voltage                                                 | VPTB0-3                | -0.3 to VDDX+0.3               | V    |

| PTB4 direct voltage<br>PTB4 with external 47 k serial resistor                     | VPTB4                  | -0.3 to 7.0<br>-27 to 42       | V    |

| PTB5 GND Switch current                                                            | IPTB5                  | 1.0                            | mA   |

| ISENSEH and ISENSEL pin voltage                                                    | VISENSE                | -0.5 to V <sub>DDA</sub> +0.25 | V    |

| ISENSEH and ISENSEL pin current                                                    | IISENSE                | -1.0 to 1.0                    | mA   |

| LIN pin voltage                                                                    | V <sub>BUS</sub>       | -27 to 42                      | V    |

| LIN pin current (internally limited)                                               | I <sub>BUSLIM</sub>    | on page 18                     | mA   |

| Voltage at VDDX                                                                    | V <sub>DDX</sub>       | -0.3 to 5.55                   | V    |

| Voltage at VDDH                                                                    | V <sub>DDH</sub>       | -0.3 to 3.0                    | V    |

| VDDH output current                                                                | IVDDH                  | internally limited             | mA   |

| VDDX output current                                                                | I <sub>VDDX</sub>      | internally limited             | mA   |

| RESET_A pin voltage                                                                | V <sub>IN</sub>        | -0.3 to V <sub>DDX</sub> +0.3  | V    |

Notes:

1.It has to be assured by the application circuit that these limits will not be exceeded, e.g. by ISO pulse 1.

#### Table 5. Maximum thermal ratings

| Ratings                                   | Symbol           | Value      | Unit |

|-------------------------------------------|------------------|------------|------|

| Storage temperature                       | T <sub>STG</sub> | -55 to 150 | °C   |

| Package thermal resistance <sup>(2)</sup> | R <sub>θJA</sub> | 32 typ.    | °C/W |

Notes:

$2.R_{\theta JA}$  value is derived using a JEDEC 2s2p test board

# 4.3 Operating conditions

This section describes the operating conditions of the device. Conditions apply to all the following data, unless otherwise noted.

#### Table 6. Operating Conditions <sup>(3)</sup>

| Ratings                                                                                                                              | Symbol                | Value         | Unit |

|--------------------------------------------------------------------------------------------------------------------------------------|-----------------------|---------------|------|

| Functional operating supply voltage - Device is fully functional. All features are operating.                                        | V <sub>SUP</sub>      | 3.5 to 28     | V    |

| Extended range for RAM Content is guaranteed. Other device functionality is limited. With Cranking mode enabled (see Cranking mode). | V <sub>SUPL</sub>     | 2.5 to 3.5    | V    |

| Functional operating VSENSE0 voltage <sup>(4)</sup>                                                                                  | V <sub>SENSE0</sub>   | 0.0 to 10     | V    |

| Functional operating VSENSE1 voltage <sup>(4)</sup>                                                                                  | V <sub>SENSE1</sub>   | 0.0 to 16     | V    |

| Functional operating VSENSE2 voltage <sup>(4)</sup>                                                                                  | V <sub>SENSE2</sub>   | 0.0 to 28     | V    |

| Functional operating VSENSE3 voltage <sup>(4)</sup>                                                                                  | V <sub>SENSE3</sub>   | 0.0 to 52     | V    |

| External voltage and temperature sense input - PTB0-4                                                                                | V <sub>PTB0-4</sub>   | 0.0 to 1.0    | V    |

| ISENSEH, ISENSEL voltage                                                                                                             | VISH/L                | -0.3 to 0.3   | V    |

| LIN output voltage range                                                                                                             | V <sub>VSUP_LIN</sub> | 7.0 to 18     | V    |

| MCU oscillator                                                                                                                       | f <sub>OSC</sub>      | 4.0 to 16.384 | MHz  |

| MCU bus frequency                                                                                                                    | f <sub>BUS</sub>      | 51.2          | MHz  |

| Operating ambient temperature                                                                                                        | Τ <sub>Α</sub>        | -40 to 125    | °C   |

| Operating junction temperature - analog die                                                                                          | T <sub>J_A</sub>      | -40 to 150    | °C   |

| Operating junction temperature - MCU die                                                                                             | T <sub>J_M</sub>      | -40 to 150    | °C   |

Notes:

3. The parametric data are guaranteed while the pins are within Operating Conditions. Other conditions are presented at top of parametric tables or noted into parameters.

4. Values for  $V_{SENSE-x}$  > Max. Specified Value are flagged in the VTH bit.

# 4.4 Supply currents

This section describes the current consumption characteristics of the device, as well as the conditions for the measurements.

# 4.4.1 Measurement conditions

All measurements are without output loads. Unless otherwise noted the currents are measured in special single chip mode and the CPU code is executed from RAM. For Run and Wait current measurements PLL is on and the reference clock is the IRC1M trimmed to 1.024 MHz. The bus frequency is 51.2 MHz and the CPU frequency is 102.4 MHz. Table 7 and Table 8 show the configuration of the CPMU module for Run, Wait and Stop current measurement. Table 9 shows the configuration of the peripherals for run current measurement

|          | Bit settings/conditions                                                                                     |

|----------|-------------------------------------------------------------------------------------------------------------|

| CPMUCLKS | PLLSEL = 0, PSTP = 1, CSAD = 0,<br>PRE = PCE = RTIOSCSEL = COPOSCSEL = 1                                    |

| CPMUOSC  | OSCE = 1, External Square wave on EXTAL $\rm f_{EXTAL}$ = 4.0 MHz, $\rm V_{IH}$ = 1.8 V, $\rm V_{IL}$ = 0 V |

| CPMURTI  | RTDEC = 0, RTR[6:4] = 111, RTR[3:0] = 1111;                                                                 |

| CPMUCOP  | WCOP = 1, CR[2:0] = 111                                                                                     |

| CPMU REGISTER                             | Bit settings/conditions                                                         |  |  |  |  |

|-------------------------------------------|---------------------------------------------------------------------------------|--|--|--|--|

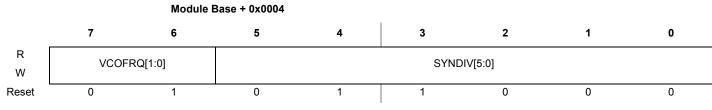

| CPMUSYNR                                  | VCOFRQ[1:0] = 3,SYNDIV[5:0] = 49                                                |  |  |  |  |

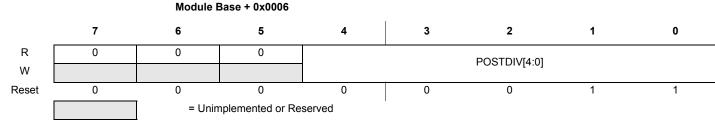

| CPMUPOSTDIV                               | POSTDIV[4:0] = 0,                                                               |  |  |  |  |

| CPMUCLKS                                  | PLLSEL = 1, CSAD = 0                                                            |  |  |  |  |

| CPMUOSC                                   | OSCE = 0, Reference clock for PLL is $f_{REF} = f_{IRC1M}$ trimmed to 1.024 MHz |  |  |  |  |

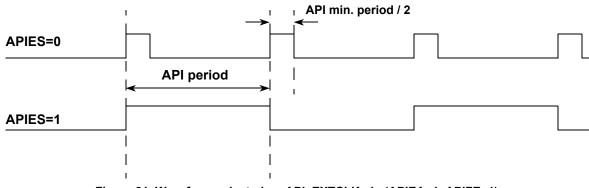

| API settings for stop current measurement |                                                                                 |  |  |  |  |

| CPMUAPICTL                                | APIEA = 0, APIFE = 1, APIE = 0                                                  |  |  |  |  |

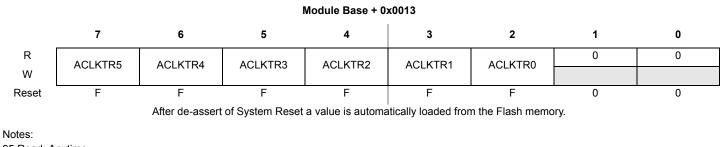

| CPMUACLKTR                                | trimmed to $\geq$ 10 kHz                                                        |  |  |  |  |

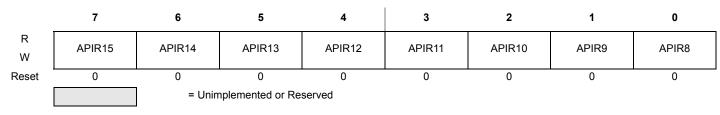

| CPMUAPIRH/RL                              | set to 0xFFFF                                                                   |  |  |  |  |

#### Table 8. CPUM Configuration for Run/Wait and Full Stop Current Measurement

#### Table 9. Peripheral configurations for run supply current measurements

| Peripheral | Configuration                                                                      |

|------------|------------------------------------------------------------------------------------|

| SPI        | configured to master mode, continuously transmit data (0x55 or 0xAA) at 1.0 Mbit/s |

| msCAN      | continuously transmit data (0x55 and 0xAA) at 1.0 MBaud/s                          |

| D2DI       | continuously read data                                                             |

| COP        | COP Watchdog Rate 2 <sup>24</sup>                                                  |

| RTI        | enabled, RTI Control Register (RTICTL) set to \$FF                                 |

| DBG        | the module is disabled                                                             |

#### Table 10. Analog die configurations for normal mode supply current measurements

| Peripheral | Configuration                                                                                                                                                                                                                                                                     |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D2D        | maximum frequency (25.600 MHz)                                                                                                                                                                                                                                                    |

| LIN        | enabled, 50% dominant, 50% recessive                                                                                                                                                                                                                                              |

| TIMER      | enabled, all channels active in output compare mode with minimum timeout                                                                                                                                                                                                          |

| LTC        | enabled, maximum timeout                                                                                                                                                                                                                                                          |

| SCI        | continuously transmitting data (0x55 or 0xAA) with 19.2 kBit/s                                                                                                                                                                                                                    |

| Channels   | Current/voltage: highest sampling rate (8.0 kHz), LPF enabled, chopper ON for Current and Temperature channels, OFF for Voltage channels and compensation enabled, automatic gain adjustment enabled temperature: internal temperature measurement enabled, 1.0 kHz sampling rate |

#### Table 11. Supply currents

| Parameter                                                                                                                                                                                                                                                   | Symbol              | Min.                  | Тур. <sup>(5)</sup>                    | Max.                                   | Unit |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|-----------------------|----------------------------------------|----------------------------------------|------|--|

| MM9Z1_638 combined consumption                                                                                                                                                                                                                              |                     |                       |                                        |                                        |      |  |

| Normal mode current measured at V <sub>SUP</sub> excluding external load current, (3.5 V $\leq$ V <sub>SUP</sub> $\leq$ 28 V; -40 °C $\leq$ T <sub>A</sub> $\leq$ 125 °C) parameter tested up to T <sub>A</sub> = 85 °C                                     | I <sub>RUN</sub>    | -                     | 35                                     | 40                                     | mA   |  |

| Normal mode current measured at V <sub>SUP</sub> - analog die contribution - excluding MCU and external load current, (3.5 V $\leq$ V <sub>SUP</sub> $\leq$ 28 V; -40 °C $\leq$ T <sub>A</sub> $\leq$ 125 °C) parameter tested up to T <sub>A</sub> = 85 °C | I <sub>NORMAL</sub> | -                     | 1.5                                    | 4.0                                    | mA   |  |

| Stop mode current measured at $V_{SUP}$<br>• Continuous base current <sup>(6)</sup><br>T = -40 °C<br>T = 85 °C<br>T = 125 °C <sup>(7)</sup><br>• Stop current during Cranking mode <sup>(6)</sup><br>T = -40 °C<br>T = 85 °C<br>T = 125 °C <sup>(7)</sup>   | I <sub>STOP</sub>   | -<br>-<br>-<br>-<br>- | 105<br>110<br>210<br>110<br>130<br>235 | 125<br>195<br>450<br>135<br>235<br>500 | μΑ   |  |

#### Table 11. Supply currents

| Parameter                                                                                                                               | Symbol             | Min.        | Тур. <sup>(5)</sup> | Max.              | Unit |

|-----------------------------------------------------------------------------------------------------------------------------------------|--------------------|-------------|---------------------|-------------------|------|

| Sleep mode measured at $V_{SUP}$<br>• Continuous base current <sup>(6)</sup><br>T = -40 °C<br>T = 85 °C<br>T = 125 °C <sup>(7)</sup>    | I <sub>SLEEP</sub> | -<br>-<br>- | 65<br>65<br>85      | 85<br>135<br>145  | μA   |

| Pseudo stop current <sup>(6)</sup><br>$T = -40 \degree C$<br>$T = 85 \degree C$<br>$T = 125 \degree C$ <sup>(7)</sup>                   |                    | -<br>-<br>- | 205<br>210<br>310   | 225<br>305<br>550 | μA   |

| Current adder during current trigger event in stop or sleep modes- (typ. 10 ms duration <sup>(8)</sup> , temperature measurement = OFF) |                    | _           | 1500                | 1750              | μA   |

Notes:

5. Typical values noted reflect the approximate parameter mean at T\_A = 25 °C.

6.From  $V_{SUP}$  6.0 to 28 V

7. Guaranteed by design and characterization

8. Duration based on channel configuration. 10 ms typical for Decimation Factor = 512, Chopper = ON.

# 4.5 Analog die electrical characteristics

# 4.5.1 Static electrical characteristics

All characteristics noted under conditions 3.5 V  $\leq$  V<sub>SUP</sub>  $\leq$  28 V, -40 °C  $\leq$  T<sub>A</sub>  $\leq$  125 °C, unless otherwise noted. Parameters tested up to T<sub>A</sub> = 85 °C unless otherwise noted. Typical values noted reflect the approximate parameter mean at T<sub>A</sub> = 25 °C under nominal conditions, unless otherwise noted.

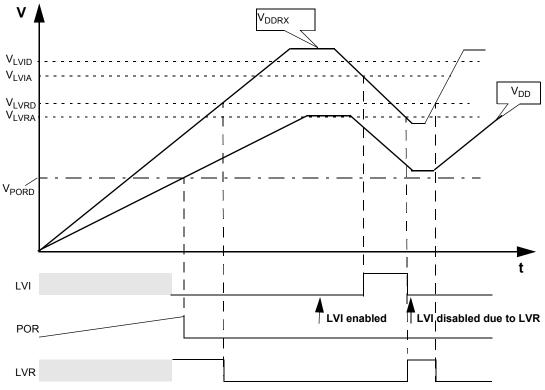

| Parameter                                                                                                  | Symbol             | Min. | Тур.  | Max. | Unit |

|------------------------------------------------------------------------------------------------------------|--------------------|------|-------|------|------|

| Low Voltage Reset L (POR) Assert (measured on LTO) <ul> <li>Cranking Mode Disabled</li> </ul>              | V <sub>PORL</sub>  | 1.75 | 1.9   | 2.12 | V    |

| Low Voltage Reset L (POR) Deassert (measured on LTO) <ul> <li>Cranking Mode Disabled</li> </ul>            | V <sub>PORH</sub>  | 1.85 | 2.1   | 2.35 | V    |

| Low Voltage Reset L (POR) Assert (measured on LTO) <ul> <li>Cranking Mode Enabled<sup>(9)</sup></li> </ul> | V <sub>PORCL</sub> | 1.0  | 1.3   | 1.7  | V    |

| Low Voltage Reset A (LVRA) Assert (measured on VDDA)                                                       | V <sub>LVRAL</sub> | 1.9  | 2.05  | 2.2  | V    |

| Low Voltage Reset A (LVRA) Deassert (measured on VDDA)                                                     | V <sub>LVRAH</sub> | 2.0  | 2.15  | 2.3  | V    |

| Low Voltage Reset X (LVRX) Assert (measured on VDDX)                                                       | V <sub>LVRXL</sub> | 2.5  | 2.75  | 3.0  | V    |

| Low Voltage Reset X (LVRX) Deassert (measured on VDDX)                                                     | V <sub>LVRXH</sub> | 2.7  | 2.95  | 3.25 | V    |

| Low Voltage Reset H (LVRH) Assert (measured on VDDH)                                                       | V <sub>LVRHL</sub> | 1.9  | 2.075 | 2.2  | V    |

| Low Voltage Reset H (LVRH) Deassert (measured on VDDH)                                                     | V <sub>LVRHH</sub> | 2.05 | 2.175 | 2.3  | V    |

| Undervoltage Interrupt (UVI) Assert (measured on VSUP), Cranking Mode Disabled                             | V <sub>UVIL</sub>  | 4.65 | 5.2   | 6.15 | V    |

| Undervoltage Interrupt (UVI) Deassert (measured on VSUP), Cranking Mode Disabled                           | V <sub>UVIH</sub>  | 4.9  | 5.4   | 6.3  | V    |

| Undervoltage Cranking Interrupt (UVI) Assert (measured on VSUP) Cranking Mode<br>Enabled                   | V <sub>UVCIL</sub> | 3.4  | 3.6   | 4.0  | V    |

| Undervoltage Cranking Interrupt (UVI) Deassert (measured on VSUP) Cranking Mode Enabled                    | V <sub>UVCIH</sub> | 3.5  | 3.8   | 4.15 | V    |

| VSENSE2 High Voltage Warning Threshold Assert <sup>(10)</sup>                                              | V <sub>TH</sub>    |      | 28    | •    | V    |

Notes:

9.Deassert with Cranking off =  $V_{PORH}$

10.5.0 V <  $V_{SUP}$  < 28 V, Digital Threshold at the end of channel chain (incl. compensation)

#### Table 13. Static electrical characteristics - resets

| Parameter                                          | Symbol              | Min.                | Тур. | Max.                | Unit |

|----------------------------------------------------|---------------------|---------------------|------|---------------------|------|

| Low-state Output Voltage I <sub>OUT</sub> = 2.0 mA | V <sub>OL</sub>     | -                   | -    | 0.8                 | V    |

| Pull-up Resistor                                   | R <sub>RPU</sub>    | 25                  | _    | 50                  | kΩ   |

| Low-state Input Voltage                            | V <sub>IL</sub>     | _                   | _    | 0.3V <sub>DDX</sub> | V    |

| High-state Input Voltage                           | V <sub>IH</sub>     | 0.7V <sub>DDX</sub> | _    | _                   | V    |

| Reset Release Voltage (VDDX)                       | V <sub>RSTRV</sub>  | 0.0                 | 0.02 | 1.0                 | V    |

| RESET_A pin Current Limitation                     | I <sub>LIMRST</sub> | _                   | _    | 10                  | mA   |

#### Table 14. Static electrical characteristics - voltage regulator outputs

| Parameter                                                                       | Symbol                | Min. | Тур. | Max. | Unit |

|---------------------------------------------------------------------------------|-----------------------|------|------|------|------|

| Analog Voltage Regulator - VDDA <sup>(11)</sup>                                 |                       |      | 1    | 1    | 1    |

| Output Voltage $I_{VDDA} \le 1.0 \text{ mA}$                                    | V <sub>DDA</sub>      | 2.25 | 2.5  | 2.75 | V    |

| Output Current Limitation (Max. value occurs under VDDA short to GND condition) | I <sub>VDDA</sub>     | _    | -    | 30   | mA   |

| Load current available for external sensor supply(i.e Temp sensor)              | I <sub>VDDA EXT</sub> | _    | -    | 1.0  | mA   |

| Line regulation, V <sub>SUP</sub> 3.5 to 28 V, I_Load 1.0 mA                    | LINE REGA             | -30  | -    | 30   | mV   |

#### Table 14. Static electrical characteristics - voltage regulator outputs (continued)

| Parameter                                                                                                                                                             | Symbol                | Min.        | Тур.     | Max.      | Unit |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|-------------|----------|-----------|------|

| Load regulation, I_Load 2.0 μA - 3.0 mA <sup>(12)</sup>                                                                                                               | LOAD REGA             | -50         | _        | 50        | mV   |

| Voltage in Low-power modes (sleep and stop)                                                                                                                           | V <sub>DDA LP</sub>   | _           | 0.0      | 100       | mV   |

| Logic Test Output - LTO <sup>(11)</sup>                                                                                                                               | I I                   |             |          |           |      |

| Output Voltage                                                                                                                                                        | V <sub>LTO</sub>      | 2.25        | 2.5      | 2.75      | V    |

| Output current limitation (for pin FMEA purpose only)                                                                                                                 | I <sub>LTO</sub>      | 1.0         | -        | 30        | mA   |

| High Power Digital Voltage Regulator - VDDH <sup>(13)</sup>                                                                                                           | 1                     |             |          |           |      |

| Output Voltage 1.0 mA ≤ I <sub>VDDH</sub> ≤ 18 mA                                                                                                                     | V <sub>DDH</sub>      | 2.4         | 2.5      | 2.75      | V    |

| Output Current Limitation                                                                                                                                             | I <sub>VDDH</sub>     | -           | -        | 65        | mA   |

| 5.0 V Voltage Regulator - VDDX <sup>(13)</sup>                                                                                                                        | 1                     |             |          |           |      |

| Output Voltage in Normal Mode, 1.0 mA $\leq$ $I_{VDDX}$ $\leq$ 150 mA, $V_{SUP}$ > 5.5 V                                                                              | V <sub>DDX</sub>      | 4.75        | 5.0      | 5.25      | V    |

| Output Current Limitation                                                                                                                                             | I <sub>VDDX</sub>     | 150         | -        | 300       | mA   |

| Load current available for external supply - $V_{SUP}$ > 5.5 V, for all external loads like:<br>CAN transceiver, MCU I/Os, and PTBx for external temperature sensors. | I <sub>VDDX EXT</sub> | -           | -        | 100       | mA   |

| Output Voltage in Low-power Stop mode $I_{VDDX} \leq 2.0$ mA<br>• $V_{SUP} > 5.5$ V<br>• $V_{SUP} > 3.5$ V                                                            | V <sub>DDXSTP</sub>   | 4.75<br>3.2 | 5.0<br>- | 5.25<br>- | V    |

| Line regulation in normal mode, $V_{SUP}$ 6.0 to 18 V, no load and $I_{LOAD}$ = 150 mA                                                                                | Line Reg Vx           | -50         | -        | 50        | mV   |

| Load regulation in normal mode, V <sub>SUP</sub> 6.0 V, I <sub>LOAD</sub> < 150 mA                                                                                    | Load Reg Vx           | _           | _        | 300       | mV   |

| Line regulation in Low-power Stop mode V <sub>SUP</sub> 5.5 to 18 V                                                                                                   | Line Reg<br>VxLP      | -50         | -        | 50        | mV   |

| Load regulation in Low-power Stop mode                                                                                                                                | Load Reg<br>VxLP      | -           | -        | 100       | mV   |

| Output current limitation in Low-power Stop mode                                                                                                                      | IVDDXSTP              | 3.0         | -        | 10        | mA   |

| Drop voltage, I <sub>LOAD</sub> < I <sub>LIM</sub> (I <sub>VDDX</sub> )                                                                                               | VDDX <sub>DRP</sub>   | -           | -        | 300       | mV   |

| External decoupling capacitor                                                                                                                                         | C at V <sub>DDX</sub> | _           | 470      | -         | nF   |

Notes:

11.No additional current must be taken from those outputs.

12. Total VDDA regulator current, including internal device consumption

13. The specified current ranges does include the current for the MCU die. No external loads recommended.

#### Table 15. Static electrical characteristics - LIN physical layer interface - LIN

| Parameter                                                                                                                                                                                              | Symbol                   | Min.  | Тур. | Max.  | Unit             |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|-------|------|-------|------------------|

| Current Limitation for Driver dominant state. $V_{BUS}$ = 18 V                                                                                                                                         | IBUSLIM                  | 40    | 120  | 200   | mA               |

| Input Leakage Current at the Receiver incl. Pullup Resistor R <sub>SLAVE</sub> ; Driver OFF; V <sub>BUS</sub> = 0 V; V <sub>BAT</sub> = 12 V                                                           | IBUS_PAS_DOM             | -1.0  | _    | _     | mA               |

| Input Leakage Current at the Receiver incl. Pullup Resistor R <sub>SLAVE</sub> ; Driver OFF; 8.0 V < V <sub>BAT</sub> < 18 V; 8.0 V < V <sub>BUS</sub> < 18 V; V <sub>BUS</sub> $\ge$ V <sub>BAT</sub> | I <sub>BUS_PAS_REC</sub> | _     | _    | 20    | μA               |

| Input Leakage Current; GND Disconnected; GND_{DEVICE} = V_{SUP}; 0 < V_{BUS} < 18 V; V_{BAT} = 12 V                                                                                                    | I <sub>BUS_NO_GND</sub>  | -1.0  | _    | 1.0   | mA               |

| Input Leakage Current; V_{BAT} disconnected; V_{SUP_DEVICE} = GND; 0 < V_{BUS} < 18 V                                                                                                                  | I <sub>BUS_NO_BAT</sub>  | _     | _    | 10    | μA               |

| Receiver Input Voltage; Receiver Dominant State                                                                                                                                                        | V <sub>BUSDOM</sub>      | -     | -    | 0.4   | V <sub>SUP</sub> |

| Receiver Input Voltage; Receiver Recessive State                                                                                                                                                       | V <sub>BUSREC</sub>      | 0.6   | -    | -     | V <sub>SUP</sub> |

| Receiver Threshold Center (V <sub>TH_DOM</sub> + V <sub>TH_REC</sub> )/2                                                                                                                               | V <sub>BUS_CNT</sub>     | 0.475 | 0.5  | 0.525 | V <sub>SUP</sub> |

| Receiver Threshold Hysteresis (V <sub>TH_REC</sub> - V <sub>TH_DOM</sub> )                                                                                                                             | V <sub>BUS_HYS</sub>     | -     | -    | 0.175 | V <sub>SUP</sub> |

| Voltage Drop at the serial Diode                                                                                                                                                                       | D <sub>SER_INT</sub>     | 0.3   | 0.7  | 1.0   | V                |

| LIN Pull-up Resistor                                                                                                                                                                                   | R <sub>SLAVE</sub>       | 20    | 30   | 60    | kΩ               |

| LIN Internal Capacitor <sup>(14)</sup>                                                                                                                                                                 | C <sub>LIN</sub>         | -     | 5.0  | 30    | pF               |

#### MM9Z1\_638

#### Table 15. Static electrical characteristics - LIN physical layer interface - LIN (continued)

| Parameter                                                                               | Symbol                | Min.   | Тур. | Max. | Unit             |

|-----------------------------------------------------------------------------------------|-----------------------|--------|------|------|------------------|

| Low Level Output Voltage, I <sub>BUS</sub> =40 mA                                       | V <sub>DOM</sub>      | -      | -    | 0.3  | V <sub>SUP</sub> |

| High Level Output Voltage, I <sub>BUS</sub> =-10 $\mu$ A, R <sub>L</sub> =33 k $\Omega$ | V <sub>REC</sub>      | VSUP-1 | -    | -    | V                |

| J2602 Detection Deassert Threshold for VSUP level                                       | V <sub>J2602H</sub>   | 5.9    | 6.3  | 6.7  | V                |

| J2602 Detection Assert Threshold for VSUP level                                         | V <sub>J2602L</sub>   | 5.8    | 6.2  | 6.6  | V                |

| J2602 Detection Hysteresis                                                              | V <sub>J2602HYS</sub> | 70     | 190  | 250  | mV               |

| BUS Wake-up Threshold                                                                   | V <sub>LINWUP</sub>   | 4.0    | 5.25 | 6.0  | V                |

Notes:

14. This parameter is guaranteed by process monitoring but not production tested.

#### Table 16. Static electrical characteristics - high voltage input - PTB4

| Parameter                                     | Symbol                | Min.                 | Тур. | Max.                  | Unit |

|-----------------------------------------------|-----------------------|----------------------|------|-----------------------|------|

| Wake-up Threshold - Rising Edge               | V <sub>WTHR</sub>     | 1.3                  | 2.6  | 3.4                   | V    |

| Input High-voltage (digital Input)            | V <sub>IH</sub>       | 0.7V <sub>DDX</sub>  | -    | V <sub>DDX</sub> +0.3 | V    |

| Input Low-voltage (digital Input)             | V <sub>IL</sub>       | V <sub>SS</sub> -0.3 | _    | 0.35V <sub>DDX</sub>  | V    |

| Input Hysteresis                              | V <sub>HYS</sub>      | -                    | 140  | -                     | mV   |

| Internal Positive Clamp Voltage               | V <sub>PTB4CLMP</sub> | _                    | 9.8  | -                     | V    |

| Input Current PTB4, V <sub>IN</sub> = 8V      | I <sub>IN</sub>       | -10                  | 0    | 10                    | uA   |

| Internal Pull-down Resistance <sup>(15)</sup> | R <sub>PD</sub>       | 50                   | 100  | 200                   | kΩ   |

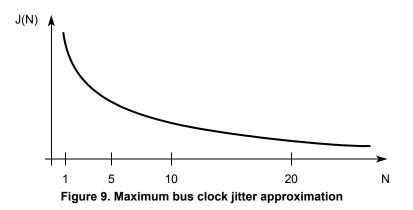

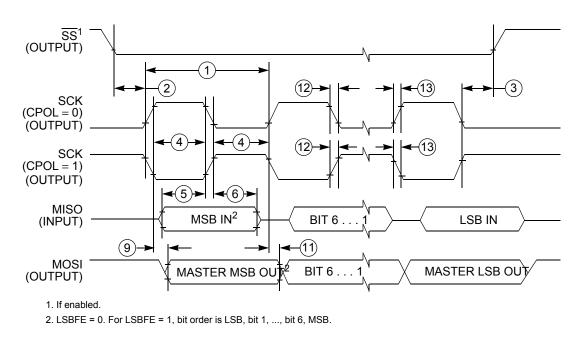

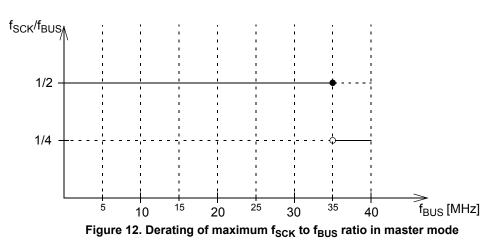

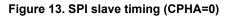

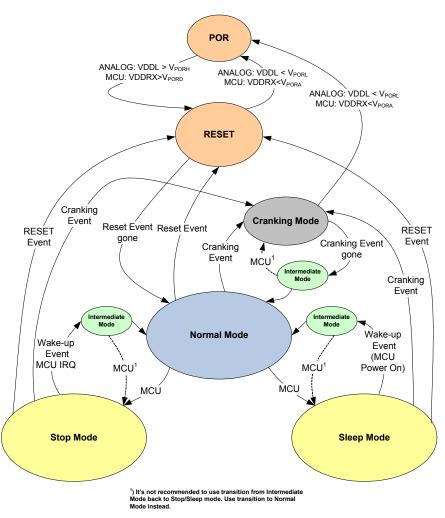

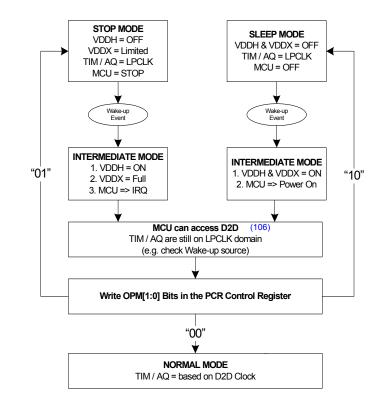

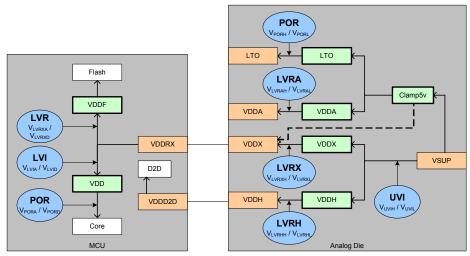

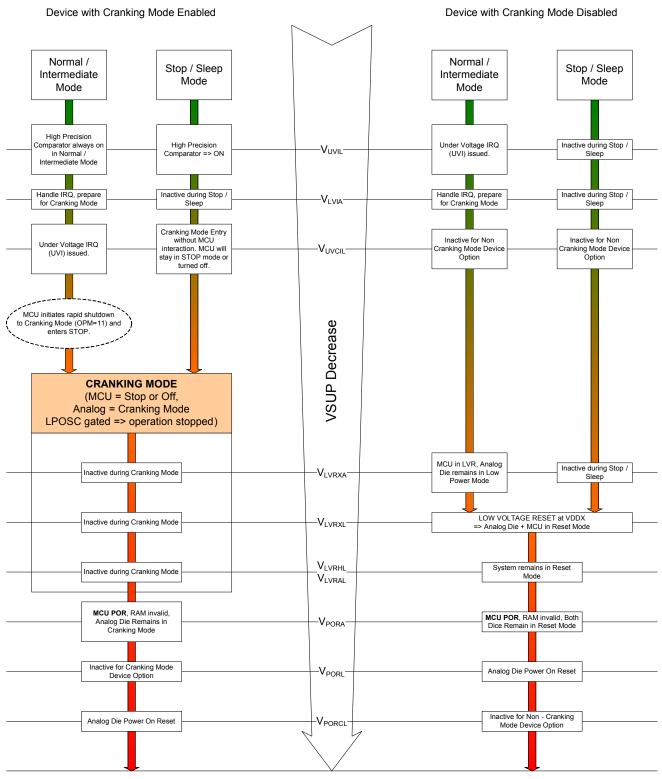

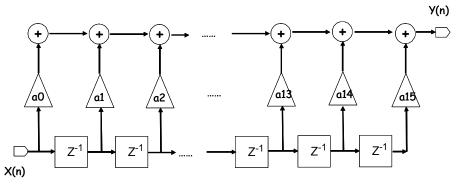

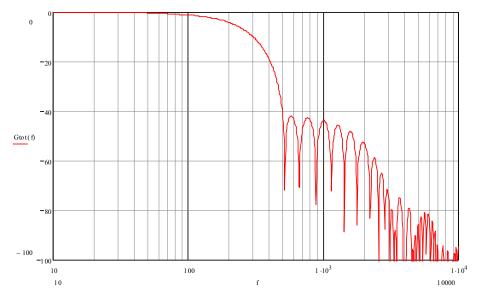

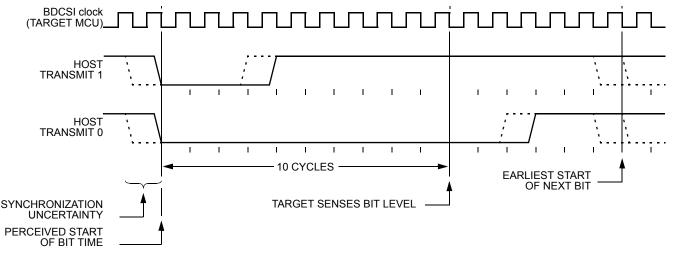

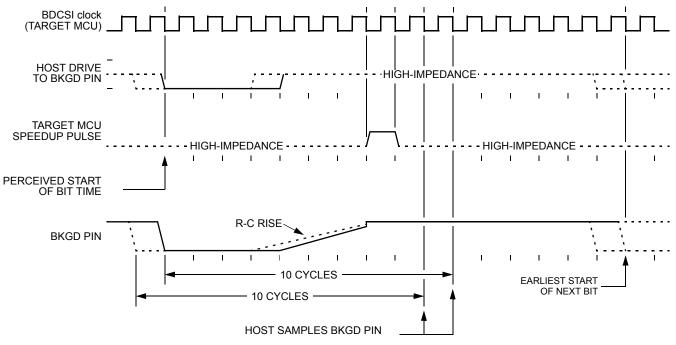

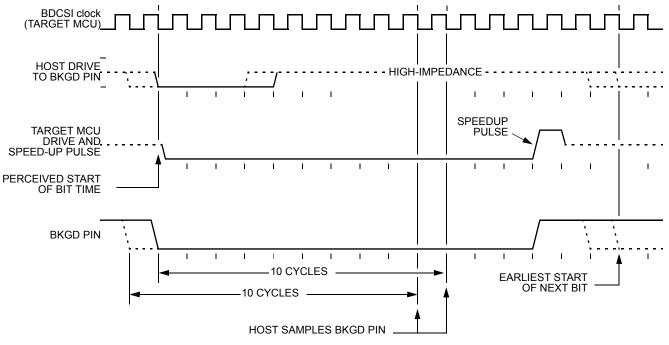

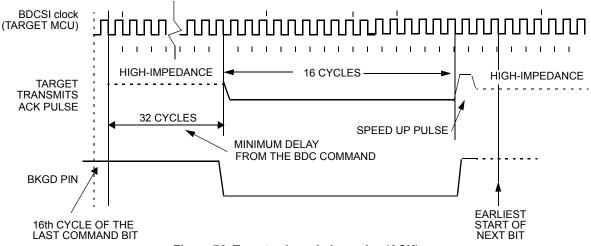

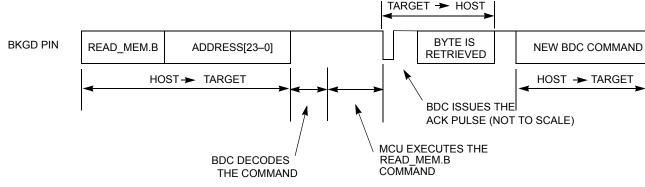

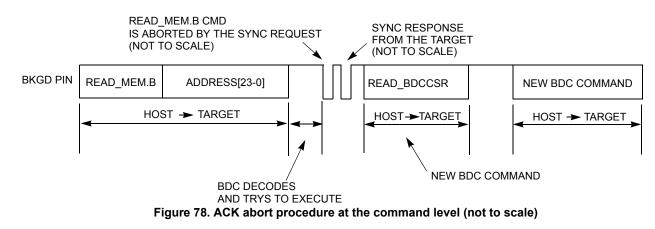

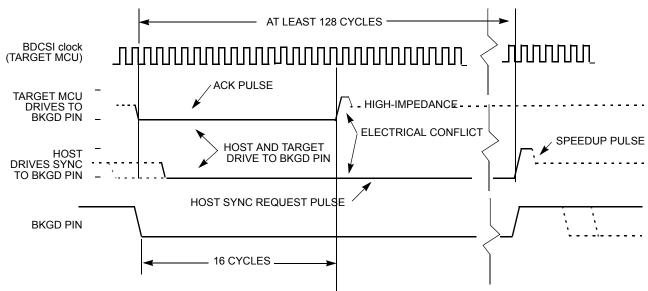

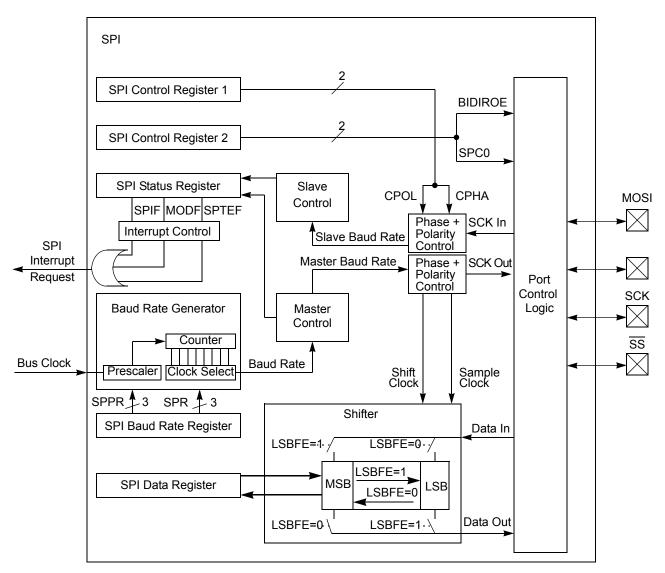

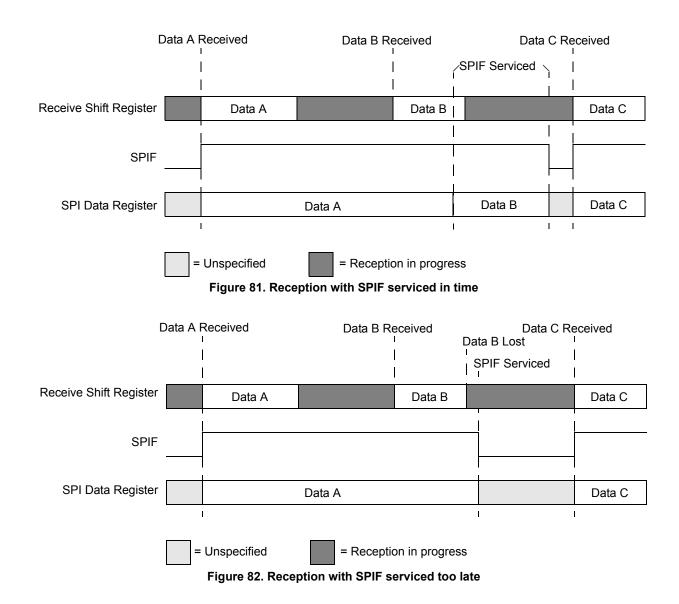

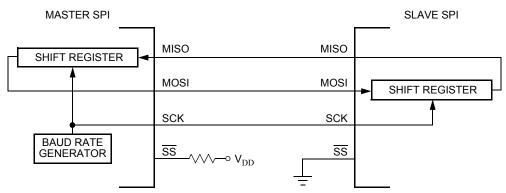

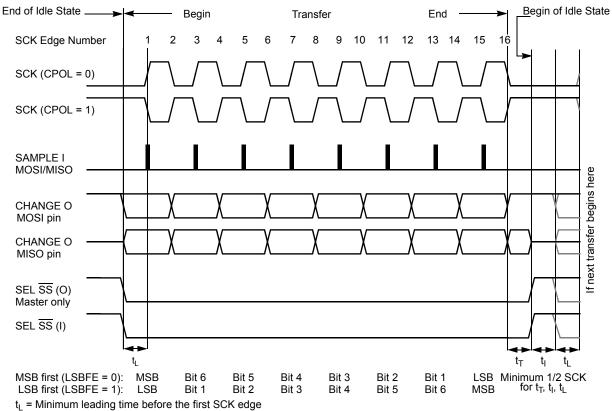

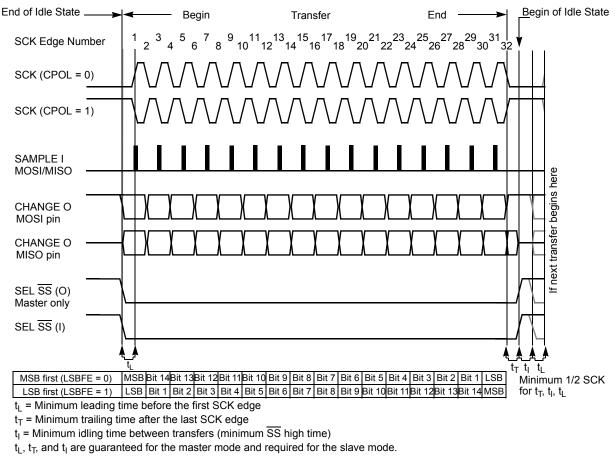

| External Series Resistor                      | R <sub>PTB4</sub>     | 42.3                 | 47   | 51.7                  | kΩ   |