**Product short data sheet**

## 1 General description

The MC33GD3100 is an advanced single channel gate driver for IGBTs and SiC power devices. Integrated Galvanic isolation and low on-resistance drive transistors provide high charging and discharging current, low dynamic saturation voltage and rail-to-rail gate voltage control.

Current and temperature sense minimizes IGBT stress during faults. Accurate and configurable under voltage lockout (UVLO) provides protection while ensuring sufficient gate drive voltage headroom.

The MC33GD3100 autonomously manages severe faults and reports faults and status via INTB pin and an SPI interface. It is capable of directly driving gates of most IGBTs and SiC MOSFETs. Self test, control and protection functions are included for design of high reliability systems (ASIL C/D). It meets the stringent requirements of automotive applications and is fully AEC-Q100 grade 1 qualified.

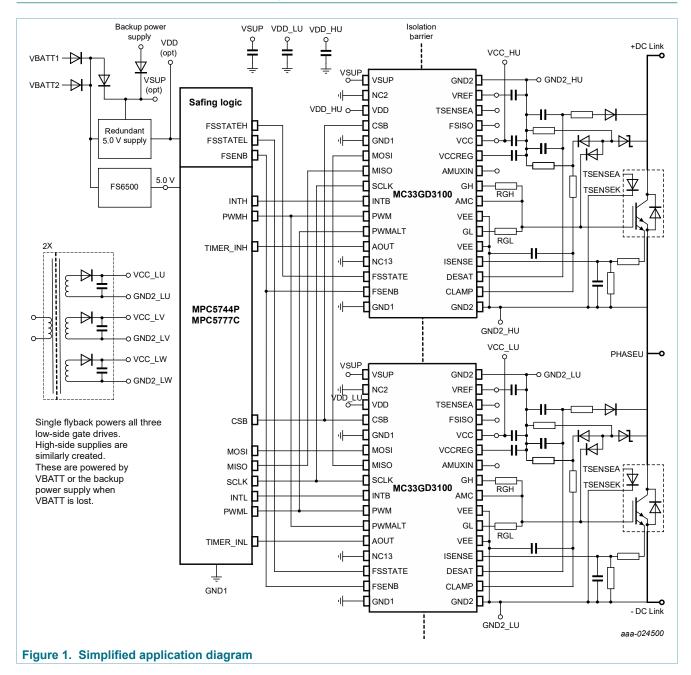

# 2 Simplified application diagram

#### 3 Features and benefits

This section summarizes the key features, safety features, and regulatory approvals.

## 3.1 Key features

- · SPI interface for safety monitoring, programmability and flexibility

- Low propagation delay and minimal PWM distortion

- Integrated Galvanic signal isolation (up to 8 kV)

- Integrated gate drive power stage capable of 15 A peak source and sink

- · Fully programmable Active Miller Clamp

- Compatible with negative gate supply

- Compatible with current sense and temperature sense IGBTs

- Integrated soft shutdown, two-level turn-off, active clamp, and segmented drive for wave shaping

- CMTI > 100 V/ns

- Compatible with 200 V to 1700 V IGBT/SiC, power range > 125 kW

- Operating temperature range -40 °C to 125 °C

- External Creepage distance (CPG): > 7.8 mm

- Operating frequency > 40 kHz

- 5.0 V and 3.3 V tolerant MCU interface available

#### 3.2 Safety features

- Certified to ASIL D ISO26262 functional safety requirements for full diagnostics

- Current, DESAT, and temperature sense inputs and ADC reporting for IGBT/SiC monitoring

- Fast short-circuit protection, overcurrent protection, temperature warning and shutdown

- Interrupt pin for fast response to faults

- · Built-in self-check of all analog and digital circuits

- · Continuous watchdog of die-to-die communications

- · Mandatory deadtime enforcement

- Over and undervoltage supervision of all power supplies on both low and high voltage sides

- · Fail-safe state management pins on both low and high voltage sides

- · VGE real time cycle-by-cycle monitoring

#### 3.3 Safety and regulatory approvals

- Reinforced Isolation per DIN V VDE V 0884-10

- Withstand 2500 V rms (1 minute) isolation per UL 1577

- CSA Component Acceptance Notice 5A

- AEC-Q100 grade 1 automotive qualified

# 4 Ordering information

Table 1. Orderable part variations

| Part number [1] | VDD   | Temperature (T <sub>J</sub> ) | Package                                 |  |

|-----------------|-------|-------------------------------|-----------------------------------------|--|

| MC33GD3100EK    | 5.0 V | −40 °C to 150 °C              | 32-pin wide body<br>SOIC, 0.65 mm pitch |  |

| MC33GD3100A3EK  | 3.3 V | -40 C to 130 C                |                                         |  |

<sup>[1]</sup> To order parts in tape and reel, add the R2 suffix to the part number.

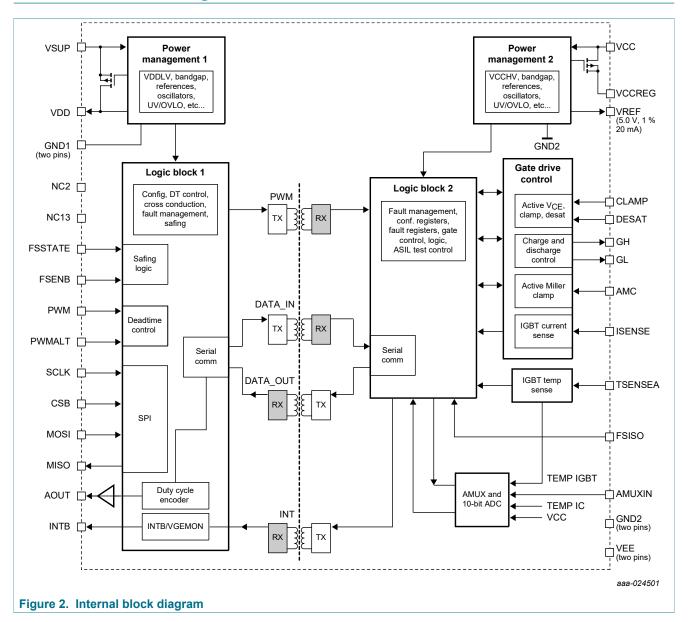

# 5 Internal block diagram

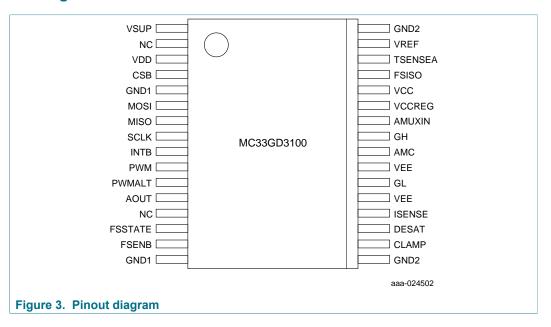

# 6 Pinning information

## 6.1 Pinning

## 6.2 Pin description

Table 2. Pin definitions

| Pin number     | Pin name            | Pin type     |        | Definition                                                                                                                     | Comments                                                                                                                                  |

|----------------|---------------------|--------------|--------|--------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|

| Pins 1 to 16 ( | low-voltage, non-is | olated pins) |        |                                                                                                                                |                                                                                                                                           |

| 1              | VSUP                | power        | input  | Externally supplied voltage source supply; primary supply for non-isolated circuits                                            | Typically supplied by vehicle battery                                                                                                     |

| 2              | NC2                 | _            | _      | No connection                                                                                                                  | NC2 must be connected to GND1                                                                                                             |

| 3              | VDD                 | power        | input  | Internally generated supply to power AOUT, MISO and INTB                                                                       | Not to be used to power other circuitry. External capacitor should be placed at this pin. May be supplied externally (MC33GD3100EK only). |

| 4              | CSB                 | digital      | input  | SPI chip select                                                                                                                | Chip select input. Active low. CSB frames SPI commands and enables SPI port.                                                              |

| 5, 16          | GND1                | ground       | ground | Ground for the non-<br>isolated circuitry: input<br>logic including SPI,<br>PWM, PWMALT, FSENB,<br>FSSTATE, AOUT, VDD,<br>INTB | Isolated from all circuitry referenced to GND2                                                                                            |

| 6              | MOSI                | digital      | input  | SPI master out slave in pin                                                                                                    | Input data for SPI port.<br>MC33GD3100 latches<br>MOSI on rising edge of<br>SCLK, MSB first                                               |

MC33GD3100\_SDS

All information provided in this document is subject to legal disclaimers.

| Pin number    | Pin name                | Pin type |          | Definition                                                                                      | Comments                                                                                                                                                                                     |

|---------------|-------------------------|----------|----------|-------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7             | MISO                    | digital  | output   | SPI master in slave out pin                                                                     | Output data for SPI port,<br>MC33GD3100 outputs<br>MISO on falling edge of<br>SCLK.                                                                                                          |

| 8             | SCLK                    | digital  | input    | SPI clock                                                                                       | Clock for SPI                                                                                                                                                                                |

| 9             | INTB                    | digital  | output   | Interrupt/Fault status output                                                                   | Interrupt pin output, reports faults with active pulldown. Pin is left open if unused.                                                                                                       |

| 10            | PWM                     | digital  | input    | PWM input for the IGBT gate                                                                     | Active high input logic signal turns on the IGBT                                                                                                                                             |

| 11            | PWMALT                  | digital  | input    | PWM input for opposing IGBT gate                                                                | Active high input logic signal turns off IGBT gate (opposing IGBT is turned on). Connected to GND1 if unused.                                                                                |

| 12            | AOUT                    | analog   | output   | Duty cycle encoded analog signals for temperature or voltage                                    | Desired analog signal is selected by SPI. Pin is left open if unused.                                                                                                                        |

| 13            | NC13                    | _        | _        | No Connection                                                                                   | NC13 is unused and<br>should be left open or<br>connected to the MCU<br>to allow compatibility<br>with the GD3160. If<br>GD3160 compatibility is<br>not desired, NC13 can be<br>tied to GND. |

| 14            | FSSTATE                 | digital  | input    | Fail-safe state specifies<br>the desired state of the<br>output during a fail-safe<br>condition | Allows fail-safe logic control. Connected to GND1 if unused.                                                                                                                                 |

| 15            | FSENB                   | digital  | input    | Enables the fail-safe state                                                                     | Allows fail-safe logic control. Connected to VDD if unused.                                                                                                                                  |

| Pins 17 to 32 | (high-voltage, isolated | d pins)  |          |                                                                                                 |                                                                                                                                                                                              |

| 17, 32        | GND2                    | ground 2 | ground 2 | Ground for the isolated (high-voltage) circuitry                                                | Must be connected to IGBT's emitter                                                                                                                                                          |

| 18            | CLAMP                   | analog   | input    | V <sub>CE</sub> sense terminal for actively clamping the collector voltage at turn-off          | Connected to VEE if unused                                                                                                                                                                   |

| 19            | DESAT                   | analog   | output   | V <sub>CE</sub> desaturation<br>monitoring pin                                                  | Connected to GND2 if unused                                                                                                                                                                  |

| 20            | ISENSE                  | analog   | input    | Current sense feedback pin                                                                      | Receives current sense<br>feedback from the IGBT's<br>current sense. Connected<br>to GND2 if unused.                                                                                         |

| 21, 23        | VEE                     | power    | input    | Negative voltage supply for gate of the IGBT                                                    | Typically -5.0 to -8.0 V, referenced to GND2. Connect to GND2 if a negative supply is not used.                                                                                              |

| 22            | GL                      | analog   | output   | Primary discharging pin for IGBT gate                                                           | Pull-down transistor at this pin discharges the IGBT gate                                                                                                                                    |

| Pin number | Pin name | Pin type |        | Definition                                                                      | Comments                                                                                          |

|------------|----------|----------|--------|---------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|

| 24         | AMC      | analog   | input  | Pin connected directly to IGBT gate for gate sensing and Active Miller Clamping | Used for diagnostics and Active Miller Clamping                                                   |

| 25         | GH       | analog   | output | Sole charging pin for IGBT gate                                                 | Pullup transistor at this pin charges the IGBT gate                                               |

| 26         | AMUXIN   | analog   | input  | Analog MUX input                                                                | Connected to GND2 if unused                                                                       |

| 27         | VCCREG   | power    | in/out | Regulated positive supply for the IGBT gate. Requires capacitance.              | 15 V supply derived from VCC. Connected to VCC if regulator unused.                               |

| 28         | VCC      | power    | input  | Positive voltage supply for isolated circuitry and gate of the IGBT             | Typically 15 to 18 V, referenced to GND2                                                          |

| 29         | FSISO    | digital  | input  | Tri-states gate drive transistors to allow external control of IGBT gate        | Used for HV domain<br>management of fail-safe<br>state. Connected to GND2<br>if unused.           |

| 30         | TSENSEA  | analog   | input  | Anode of temp sense diode of IGBT                                               | Sources current and reads voltage of temp sense diode of one IGBT die. Connect to VREF if unused. |

| 31         | VREF     | analog   | output | 5.0 V reference for isolated analog circuitry                                   | Capable of sourcing up to 20 mA                                                                   |

# 7 Absolute maximum ratings

All voltages are referenced to GND1 or GND2. Currents are positive into and negative out of the specified pins. Exceeding these ratings may cause malfunction or permanent device damage.

Table 3. Absolute maximum ratings

All voltages referenced to GND1 (LV domain) or GND2 (HV domain). Currents are positive into and negative out of the specified pins.

| Symbol               | Description (Rating)                                                   |     | Min  | Max                          | Unit |

|----------------------|------------------------------------------------------------------------|-----|------|------------------------------|------|

| POWER SUP            | PLIES AND CURRENT REFERENCES                                           |     |      | '                            | ,    |

| V <sub>VSUP</sub>    | Low voltage domain supply voltage                                      | [1] | -0.3 | 40                           | V    |

| $V_{VDD3p3}$         | Low voltage domain logic supply voltage, 3.3 V version                 | [1] | -0.3 | 6.0                          | V    |

| $V_{VDD5}$           | Low voltage domain logic supply voltage, 5.0 V version                 | [1] | -0.3 | 6.0                          | V    |

| V <sub>VCC</sub>     | High voltage domain positive supply voltage                            | [2] | -0.3 | 25                           | V    |

| $V_{VEE}$            | High voltage domain negative supply voltage                            | [2] | -12  | 0.3                          | V    |

| V <sub>VCC-VEE</sub> | High voltage domain positive/negative supply                           |     | -0.3 | 37                           | V    |

| V <sub>VCCREG</sub>  | High voltage domain post regulated supply voltage                      | [2] | -0.3 | 25                           | V    |

| I <sub>VCCREG</sub>  | VCCREG output current                                                  |     | _    | -100                         | mA   |

| $V_{VREF}$           | VREF voltage                                                           | [2] | -0.3 | 6.0                          | V    |

| I <sub>VREF</sub>    | VREF output current                                                    |     | _    | -20                          | mA   |

| LOGIC PINS           |                                                                        |     |      |                              | ,    |

| V <sub>IN</sub>      | Logic input pin voltage (FSSTATE, FSENB, PWM, PWMALT, SCLK, CSB, MOSI) | [1] | -0.3 | 18                           | V    |

| V <sub>OUT</sub>     | Logic output pin voltage (MISO, INTB, AOUT)                            | [1] | -0.3 | V <sub>VDD_max</sub> + 0.3 V | V    |

| V <sub>FSISO</sub>   | Logic input pin voltage (FSISO)                                        | [2] | -0.3 | 12                           | V    |

MC33GD3100\_SDS

All information provided in this document is subject to legal disclaimers.

| Symbol                 | Description (Rating)                             |     | Min       | Max                             | Unit |

|------------------------|--------------------------------------------------|-----|-----------|---------------------------------|------|

| GATE DRIVE             | OUTPUT STAGE                                     |     | '         |                                 |      |

| V <sub>GH</sub>        | GH voltage                                       | [2] | VEE - 0.3 | V <sub>VCCREG_max</sub> + 0.3 V | V    |

| V <sub>GL</sub>        | GL voltage                                       | [2] | VEE - 0.3 | V <sub>VCCREG_max</sub> + 0.3 V | V    |

| V <sub>AMC</sub>       | AMC voltage                                      | [2] | VEE - 0.3 | V <sub>VCCREG_max</sub> + 0.3 V | V    |

| I <sub>SOURCEMAX</sub> | GH max. source current                           | [3] | _         | -15                             | А    |

| I <sub>SINKMAX</sub>   | GL, AMC max. sink current                        | [3] | _         | 15                              | А    |

| V <sub>CLAMP</sub>     | CLAMP voltage                                    | [2] | VEE - 0.3 | V <sub>VCCREG_max</sub> + 0.3 V | V    |

| V <sub>DESAT</sub>     | DESAT voltage                                    | [2] | -0.3      | V <sub>VCCREG_max</sub> + 0.3 V | V    |

| TEMPERATUR             | RE SENSE PIN                                     |     |           | '                               | ,    |

| V <sub>TSENSEA</sub>   | TSENSEA voltage                                  | [2] | -0.3      | 6.0                             | V    |

| INTB PIN               |                                                  |     |           | 1                               | ,    |

| I <sub>INTB</sub>      | Open drain DC output current                     | [4] | _         | 20                              | mA   |

| ISENSE SENS            | SE PIN                                           |     |           | '                               |      |

| V <sub>ISENSE</sub>    | ISENSE voltage                                   | [2] | -2.0      | V <sub>VCCREG_max</sub> + 0.3 V | V    |

| AMUXIN PIN             |                                                  |     |           | 1                               | ,    |

| V <sub>AMUXIN</sub>    | AMUXIN voltage                                   | [2] | -0.3      | 6.0                             | V    |

| ESD RATINGS            | 5                                                |     |           |                                 |      |

| V <sub>ESDHBM</sub>    | ESD voltage (HBM)                                | [5] |           |                                 | kV   |

|                        | All pins                                         |     | -2.0      | 2.0                             |      |

| V <sub>ESDCDM</sub>    | ESD voltage (CDM) Corner pins                    | [6] | -750      | 750                             | V    |

|                        | Other pins                                       | [7] | -500      | 500                             |      |

| V <sub>ESDModule</sub> | ESD voltage (module level) VSUP, GND1, GND2 pins | 1,1 | -8.0      | 8.0                             | kV   |

| IMMUNITY               |                                                  |     |           |                                 |      |

| dV <sub>ISO</sub> /dt  | Common mode transient immunity                   | [8] | _         | 100                             | V/ns |

| PWM FREQUI             | ENCY                                             |     |           |                                 |      |

| f <sub>PWMMAX</sub>    | Maximum switching frequency                      |     | 0         | 40                              | kHz  |

- [1] Ref = GND1

- [2] Ref = GND2

- [3] 50 %, 100 nF, 10 kHz

- [4] VINTB < 0.8 V

- 5] Human Body Model (HBM) at device level

ANSI/ESDA/JEDEC JS-001: 2010 Model HBM (human body model)

Electrostatic Discharge (ESD) Sensitivity Testing Human Body Model (HBM)

Test points: pin to GND1 and pin to GND2

6] Charged Device Model (CDM)

ANSI/ESD S5.3.1-2009

ESD Association Standard for Electrostatic Discharge Sensitivity Testing - Charged Device Model (CDM) - Component Level

[7] Module Level ESD Tests

ISO 10605:2008/Cor. 1:2010(E)

Road vehicles - Test methods for electrical disturbances from electrostatic discharge

[8] Pulse width = 10 ns

# 8 General functional description

#### 8.1 Introduction

The MC33GD3100 is an advanced single channel gate driver for N-channel power IGBTs and SiC MOSFETs. Integrated galvanic isolation and low on-resistance drive transistors provide high charging and discharging current, low dynamic saturation voltage and rail-

MC33GD3100\_SDS

All information provided in this document is subject to legal disclaimers.

to-rail gate voltage control. Collector current, collector-emitter voltage, and IGBT/SiC temperature sense minimize IGBT/SiC stress during faults.

The MC33GD3100 autonomously manages severe faults and reports faults and status via INTB pin and an SPI interface. It is capable of directly driving gates of most IGBTs and SiC MOSFETs. Self test, control and protection functions are included for design of high reliability systems (ASIL/SIL).

## 8.2 Power supply options

The MC33GD3100 is available in two options: VDD of 3.3 V or 5.0 V. The two options are desired to allow interfacing to MCUs with 3.3 or 5.0 V I/O.

If VDD is 3.3 V, then the user must supply VSUP with a voltage source greater than VSUPUV\_TH, usually battery in a vehicle. In this case, power for VDD is always derived from VSUP; an external VDD supply is not allowed. The MC33GD3100A3EK cannot be powered exclusively by VDD = 3.3 V.

If VDD is 5.0 V, the IC can be powered from a single voltage source at VSUP. In this case, VDD is derived from VSUP.

If VDD is 5.0 V, the IC can be powered from a single, 5.0 V source. In this case, VSUP and VDD must be connected together on the PCB. Since an externally supplied  $V_{VSUP}$  never exceeds VSUPUV\_TH, the internal VDD regulator is never turned on.

#### 8.3 Features

The MC33GD3100 is designed for a wide range of IGBT/SiC voltage ratings. Its logic interface and feedback signals are galvanically isolated from the high voltage circuitry that directly drives the IGBT gate and monitors its temperature sense, DESAT, CLAMP and current sense pins.

The MC33GD3100 is built with two domains and each has its own GND reference. Control and fault signals are transmitted between the non-isolated, "low voltage" domain (LV domain) and the isolated, "high voltage" domain (HV domain) via magnetic coupling. GND1 must be connected to the logic controller's GND. GND2 must be connected to the IGBT's emitter.

Pins 1 through 16 are connected to the low voltage domain. These pins provide interface to all the control, programming, fault monitoring and fail-safe features. A power supply connected to the VSUP pin provides power for low voltage domain.

Pins 17 through 32 are connected to the high voltage domain. These pins provide the interface to the IGBT/SiC gate, its power supplies and its terminals (collector sense, temperature sense and current sense). A power supply connected to the VCC pin provides power for the high voltage domain.

VCC and VEE are the positive and negative power supplies used to charge and discharge the IGBT/SiC gate. VCCREG is the output of a post regulator. This post regulator can be used to minimize positive supply voltage variation when multiple gate voltage supplies are generated from a single source.

The gate drive stage consists of three transistors and a current source. The GH transistor is a high current pullup (gate charging) transistor connected between VCCREG and the GH pin. Pins GL and AMC have separate transistors that provide gate discharge paths. GL is intended to be used as the primary turn-off path with an external resistor used to control discharge current. The AMC pin provides an "Active Miller Clamp", which clamps

MC33GD3100\_SDS

the IGBT's/SiC gate to its emitter when the IGBT/SiC is off. The GH, GL and AMC transistors are capable of currents up to 15 A for 2.0  $\mu$ s. A soft shutdown current source is in parallel with the GL transistor. Its role is to provide a slower gate discharge during a short-circuit condition. Fault conditions can trigger a "two level turn-off" (2LTO). If this feature is enabled, the gate drive temporarily decreases the IGBT's/SiC gate voltage while the possible fault is being validated. Reducing the gate voltage limits the maximum fault current and thereby lessens the safe operating area stress on the IGBT/SiC.

The MC33GD3100 can be used with or without a negative gate drive voltage. Negative gate voltage is often used to ensure an IGBT/SiC is kept off when its opposing IGBT/SiC is turning on. However, using a negative supply increases gate drive losses and complicates the gate drive power supply. Using a low impedance turn off circuit is another way to alleviate or eliminate the problem of dv/dt induced turn on. The AMC transistor provides a very low turn off impedance to hold the IGBT/SiC off when the other half-bridge IGBT/SiC device turns on.

By monitoring the IGBT/SiC collector-emitter voltage, the MC33GD3100 can provide two means of protection. When the IGBT/SiC is commanded on, its  $V_{CE}$  should be only a few volts at most. A short-circuit condition is likely to cause the IGBT's  $V_{CE}$  to exceed its normal on-state voltage. The MC33GD3100's  $V_{CE}$  desaturation detection circuitry monitors  $V_{CE}$  for this condition.

Active clamping of  $V_{CE}$  via a zener placed across the IGBT/SiC collector-gate terminals is another fault management technique. The MC33GD3100 monitors the zener clamp and reduces the turn-off gate drive when excessive  $V_{CE}$  is present. Reducing the gate discharge current improves clamping tolerance and reduces the size of the zeners.

The current sense pin, ISENSE, can be used to monitor the sense cells of a current sense IGBT. Responding directly to an overcurrent or short-circuit condition using current sensing can be a much faster way to respond to a severe overcurrent condition (as compared to desaturation detection).

The MC33GD3100 can also monitor temperature sense diodes or thermistors if the IGBT/SiC has them. An ADC allows reporting the temperature via the SPI as well as using the ADC reading to trigger overtemperature warning or fault conditions. Monitoring the IGBT/SiC temperature via the AOUT pin also allows real time monitoring of the system's performance in the field.

The MC33GD3100's AMUXIN pin provides a means to read other important system voltages, which can be duty cycle encoded and provided at the AOUT pin.

The IC has two ways to report fault and status data. The INTB pin immediately reports latched faults. It is active low when a fault occurs. The SPI can also report fault details as well as status and configuration information.

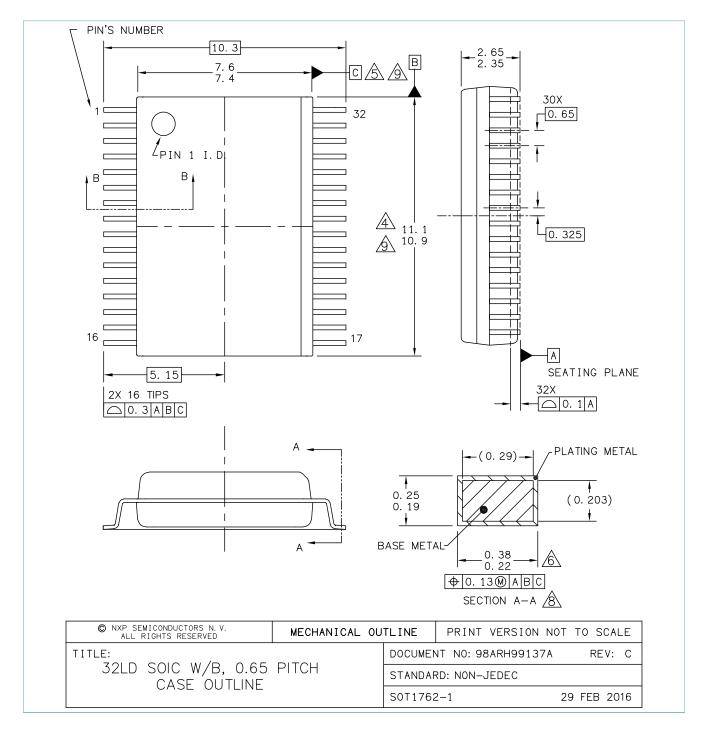

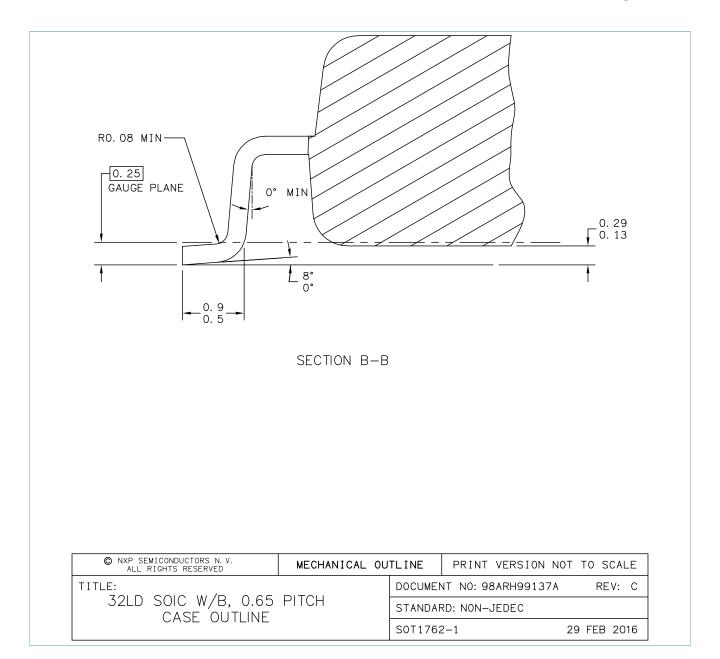

# 9 Packaging

## 9.1 Package mechanical dimensions

Package dimensions are provided in package drawings. To find the most current package outline drawing, go to www.nxp.com and perform a keyword search for the drawing's document number.

Table 4. Package outline

| Package               | Suffix | Package outline drawing number |

|-----------------------|--------|--------------------------------|

| 32-pin wide body SOIC | EK     | 98ARH99137A                    |

#### NOTES:

1. DIMENSIONS ARE IN MILLIMETERS.

0.3 mm FROM THE LEAD TIP.

- 2. DIMENSIONING AND TOLERANCING PER ASME Y14.5M-1994.

- 3. DATUMS B AND C TO BE DETERMINED AT THE PLANE WHERE THE BOTTOM OF THE LEADS EXIT THE PLASTIC BODY.

- THIS DIMENSION DOES NOT INCLUDE MOLD FLASH, PROTRUSION OR GATE BURRS. MOLD FLASH, PROTRUSION OR GATE BURRS SHALL NOT EXCEED 0.15 MM PER SIDE. THIS DIMENSION IS DETERMINED AT THE PLANE WHERE THE BOTTOM OF THE LEADS EXIT THE PLASTIC BODY.

- THIS DIMENSION DOES NOT INCLUDE INTER-LEAD FLASH OR PROTRUSIONS. INTER-LEAD FLASH AND PROTRUSIONS SHALL NOT EXCEED 0.25 MM PER SIDE. THIS DIMENSION IS DETERMINED AT THE PLANE WHERE THE BOTTOM OF THE LEADS EXIT THE PLASTIC BODY.

- THIS DIMENSION DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL NOT CAUSE THE LEAD WIDTH TO EXCEED 0.4 mm. DAMBAR CANNOT BE LOCATED ON THE LOWER RADIUS OR THE FOOT. MINIMUM SPACE BETWEEN PROTRUSION AND ADJACENT LEAD SHALL NOT LESS THAN 0.07 mm.

- EXACT SHAPE OF EACH CORNER IS OPTIONAL.

\*\*A THESE DIMENSIONS APPLY TO THE FLAT SECTION OF THE LEAD BETWEEN 0.10 mm AND

- THE PACKAGE TOP MAY BE SMALLER THAN THE PACKAGE BOTTOM. THIS DIMENSION IS DETERMINED AT THE OUTERMOST EXTREMES OF THE PLASTIC BODY EXCLUSIVE OF MOLD FLASH, TIE BAR BURRS, GATE BURRS AND INTER-LEAD FLASH, BUT INCLUDING ANY MISMATCH BETWEEN THE TOP AND BOTTOM OF THE PLASTIC BODY.

| NXP SEMICONDUCTORS N. V. ALL RIGHTS RESERVED | MECHANICAL OU | TLINE   | PRINT VERSION N    | OT TO SCALE |

|----------------------------------------------|---------------|---------|--------------------|-------------|

| TITLE:                                       | DITOLL        | DOCUMEN | NT NO: 98ARH99137A | REV: C      |

| 32LD SOIC W/B, 0.65<br>CASE OUTLINE          | PIICH,        | STANDAF | RD: NON-JEDEC      |             |

| CASE OUTETNE                                 |               | S0T1762 | 2-1                | 29 FEB 2016 |

# 10 Revision history

#### Table 5. Revision history

| Table 5. Revision history |                                                                         |                                                                                                                                                                                                                                                                                                  |               |                      |  |  |  |

|---------------------------|-------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|----------------------|--|--|--|

| Document ID               | Release date                                                            | Data sheet status                                                                                                                                                                                                                                                                                | Change notice | Supersedes           |  |  |  |

| MC33GD3100_SDS v.9.0      | 20200305                                                                | Product data sheet                                                                                                                                                                                                                                                                               | _             | MC33GD3100_SDS v.8.0 |  |  |  |

| Modifications             | <ul> <li>Made grammar and</li> <li>Updated <u>Table 3</u> to</li> </ul> | Updated Figure 1 to reflect simplified active clamp circuit  Made grammar and style changes to Pin 13 "Comments" and "Definition" cells in Table 2  Updated Table 3 to correct typos and to use a uniform current polarity definition  Changed "Deadtime" to "Mandatory Deadtime" in Section 3.2 |               |                      |  |  |  |

| MC33GD3100_SDS v.8.0      | 20200218                                                                | Product data sheet                                                                                                                                                                                                                                                                               | _             | MC33GD3100_SDS v.7.0 |  |  |  |

| Modifications             | Updated revision nu                                                     | Updated revision number to align with the data sheet                                                                                                                                                                                                                                             |               |                      |  |  |  |

| MC33GD3100_SDS v.7.0      | 20191211                                                                | Product data sheet                                                                                                                                                                                                                                                                               | _             | MC33GD3100_SDS v.6.0 |  |  |  |

| MC33GD3100_SDS v.6.0      | 20190809                                                                | Preliminary data sheet                                                                                                                                                                                                                                                                           | _             | MC33GD3100_SDS v.5.0 |  |  |  |

| MC33GD3100_SDS v.5.0      | 20190716                                                                | Preliminary data sheet                                                                                                                                                                                                                                                                           | _             | MC33GD3100_SDS v.4.0 |  |  |  |

| MC33GD3100_SDS v.4.0      | 20190715                                                                | Preliminary data sheet                                                                                                                                                                                                                                                                           | _             | MC33GD3100_SDS v.3.1 |  |  |  |

| MC33GD3100_SDS v.3.1      | 20181026                                                                | Advance information                                                                                                                                                                                                                                                                              | _             | MC33GD3100_SDS v.3.0 |  |  |  |

| MC33GD3100_SDS v.3.0      | 20181011                                                                | Advance information                                                                                                                                                                                                                                                                              | _             | MC33GD3100_SDS v.2.0 |  |  |  |

| MC33GD3100_SDS v.2.0      | 20180813                                                                | Advance information                                                                                                                                                                                                                                                                              | _             | MC33GD3100_SDS v.1.9 |  |  |  |

| MC33GD3100_SDS v.1.9      | 20180731                                                                | Advance information                                                                                                                                                                                                                                                                              | _             | MC33GD3100_SDS v.1.6 |  |  |  |

| MC33GD3100_SDS v.1.6      | 20180419                                                                | Product preview                                                                                                                                                                                                                                                                                  | _             | _                    |  |  |  |

## 11 Legal information

#### 11.1 Data sheet status

| Document status <sup>[1][2]</sup> | Product status <sup>[3]</sup> | Definition                                                                            |

|-----------------------------------|-------------------------------|---------------------------------------------------------------------------------------|

| Objective [short] data sheet      | Development                   | This document contains data from the objective specification for product development. |

| Preliminary [short] data sheet    | Qualification                 | This document contains data from the preliminary specification.                       |

| Product [short] data sheet        | Production                    | This document contains the product specification.                                     |

- [1] Please consult the most recently issued document before initiating or completing a design.

- [2] The term 'short data sheet' is explained in section "Definitions".

- The product status of device(s) described in this document may have changed since this document was published and may differ in case of multiple devices. The latest product status information is available on the Internet at URL <a href="http://www.nxp.com">http://www.nxp.com</a>.

#### 11.2 Definitions

**Draft** — The document is a draft version only. The content is still under internal review and subject to formal approval, which may result in modifications or additions. NXP Semiconductors does not give any representations or warranties as to the accuracy or completeness of information included herein and shall have no liability for the consequences of use of such information.

Short data sheet — A short data sheet is an extract from a full data sheet with the same product type number(s) and title. A short data sheet is intended for quick reference only and should not be relied upon to contain detailed and full information. For detailed and full information see the relevant full data sheet, which is available on request via the local NXP Semiconductors sales office. In case of any inconsistency or conflict with the short data sheet, the full data sheet shall prevail.

Product specification — The information and data provided in a Product data sheet shall define the specification of the product as agreed between NXP Semiconductors and its customer, unless NXP Semiconductors and customer have explicitly agreed otherwise in writing. In no event however, shall an agreement be valid in which the NXP Semiconductors product is deemed to offer functions and qualities beyond those described in the Product data sheet.

#### 11.3 Disclaimers

Limited warranty and liability — Information in this document is believed to be accurate and reliable. However, NXP Semiconductors does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information. NXP Semiconductors takes no responsibility for the content in this document if provided by an information source outside of NXP Semiconductors. In no event shall NXP Semiconductors be liable for any indirect, incidental, punitive, special or consequential damages (including - without limitation - lost profits, lost savings, business interruption, costs related to the removal or replacement of any products or rework charges) whether or not such damages are based on tort (including negligence), warranty, breach of contract or any other legal theory. Notwithstanding any damages that customer might incur for any reason whatsoever, NXP Semiconductors' aggregate and cumulative liability towards customer for the products described herein shall be limited in accordance with the Terms and conditions of commercial sale of NXP Semiconductors

Right to make changes — NXP Semiconductors reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without

notice. This document supersedes and replaces all information supplied prior to the publication hereof.

$\ensuremath{\mathbf{Applications}}$  — Applications that are described herein for any of these products are for illustrative purposes only. NXP Semiconductors makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification. Customers are responsible for the design and operation of their applications and products using NXP Semiconductors products, and NXP Semiconductors accepts no liability for any assistance with applications or customer product design. It is customer's sole responsibility to determine whether the NXP Semiconductors product is suitable and fit for the customer's applications and products planned, as well as for the planned application and use of customer's third party customer(s). Customers should provide appropriate design and operating safeguards to minimize the risks associated with their applications and products. NXP Semiconductors does not accept any liability related to any default, damage, costs or problem which is based on any weakness or default in the customer's applications or products, or the application or use by customer's third party customer(s). Customer is responsible for doing all necessary testing for the customer's applications and products using NXP Semiconductors products in order to avoid a default of the applications and the products or of the application or use by customer's third party customer(s). NXP does not accept any liability in this

Limiting values — Stress above one or more limiting values (as defined in the Absolute Maximum Ratings System of IEC 60134) will cause permanent damage to the device. Limiting values are stress ratings only and (proper) operation of the device at these or any other conditions above those given in the Recommended operating conditions section (if present) or the Characteristics sections of this document is not warranted. Constant or repeated exposure to limiting values will permanently and irreversibly affect the quality and reliability of the device.

Terms and conditions of commercial sale — NXP Semiconductors products are sold subject to the general terms and conditions of commercial sale, as published at http://www.nxp.com/profile/terms, unless otherwise agreed in a valid written individual agreement. In case an individual agreement is concluded only the terms and conditions of the respective agreement shall apply. NXP Semiconductors hereby expressly objects to applying the customer's general terms and conditions with regard to the purchase of NXP Semiconductors products by customer.

Suitability for use in automotive applications — This NXP Semiconductors product has been qualified for use in automotive applications. Unless otherwise agreed in writing, the product is not designed, authorized or warranted to be suitable for use in life support, life-critical or safety-critical systems or equipment, nor in applications where failure or malfunction of an NXP Semiconductors product can reasonably be expected to result in personal injury, death or severe property or environmental damage. NXP Semiconductors and its suppliers accept no liability for inclusion and/or use of NXP Semiconductors products in such equipment or applications and therefore such inclusion and/or use is at the customer's own risk.

MC33GD3100\_SDS

All information provided in this document is subject to legal disclaimers.

**Export control** — This document as well as the item(s) described herein may be subject to export control regulations. Export might require a prior authorization from competent authorities.

**Translations** — A non-English (translated) version of a document is for reference only. The English version shall prevail in case of any discrepancy between the translated and English versions.

#### 11.4 Trademarks

Notice: All referenced brands, product names, service names and trademarks are the property of their respective owners.

NXP — is a trademark of NXP B.V.

SafeAssure — is a trademark of NXP B.V.

## **NXP Semiconductors**

# MC33GD3100

# Advanced IGBT/SiC gate driver

# **Tables**

|                    | Orderable part variations      |         |                |

|--------------------|--------------------------------|---------|----------------|

| Figur              | es                             |         |                |

| Fig. 1.<br>Fig. 2. | Simplified application diagram | Fig. 3. | Pinout diagram |

## **Contents**

| 1   | General description             | 1  |

|-----|---------------------------------|----|

| 2   | Simplified application diagram  | 2  |

| 3   | Features and benefits           | 3  |

| 3.1 | Key features                    |    |

| 3.2 | Safety features                 |    |

| 3.3 | Safety and regulatory approvals |    |

| 4   | Ordering information            |    |

| 5   | Internal block diagram          |    |

| 6   | Pinning information             |    |

| 6.1 | Pinning                         |    |

| 6.2 | Pin description                 |    |

| 7   | Absolute maximum ratings        | 7  |

| 8   | General functional description  | 8  |

| 8.1 | Introduction                    |    |

| 8.2 | Power supply options            | 9  |

| 8.3 | Features                        |    |

| 9   | Packaging                       |    |

| 9.1 | Package mechanical dimensions   | 10 |

| 10  | Revision history                |    |

| 11  | Legal information               |    |

Please be aware that important notices concerning this document and the product(s) described herein, have been included in section 'Legal information'.

# **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Power Management IC Development Tools category:

Click to view products by NXP manufacturer:

Other Similar products are found below:

EVALZ ADP130-1.2-EVALZ ADP130-1.5-EVALZ ADP130-1.8-EVALZ ADP130-1.8-EVALZ ADP1712-3.3-EVALZ ADP1714-3.3-EVALZ ADP1715-3.3-EVALZ ADP1716-2.5-EVALZ ADP1740-1.5-EVALZ ADP1752-1.5-EVALZ ADP1828LC-EVALZ ADP1870-0.3-EVALZ ADP1871-0.6-EVALZ ADP1873-0.6-EVALZ ADP1874-0.3-EVALZ ADP1882-1.0-EVALZ ADP199CB-EVALZ ADP2102-1.25-EVALZ ADP2102-1.875EVALZ ADP2102-1.8-EVALZ ADP2102-2-EVALZ ADP2102-3-EVALZ ADP2102-4-EVALZ ADP2106-1.8-EVALZ ADP2147CB-110EVALZ AS3606-DB BQ24010EVM BQ24075TEVM BQ24155EVM BQ24157EVM-697 BQ24160EVM-742 BQ24296MEVM-655 BQ25010EVM BQ3055EVM NCV891330PD50GEVB ISLUSBI2CKIT1Z LM2744EVAL LM2854EVAL LM3658SD-AEV/NOPB LM3658SDEV/NOPB LM4510SDEV/NOPB LM5033SD-EVAL LP38512TS-1.8EV