# MC9S12ZVM-Family Reference Manual and Datasheet

S12 MagniV Microcontrollers

Rev. 2.13 29 Apr 2019 MC9S12ZVMRM

nxp.com

The ZVMC256, ZVML31, ZVM32 and ZVM16 devices are targeted for safety relevant systems and have been developed using an ISO26262 compliant development system under the NXP SafeAssure program. For details of device usage in safety relevant systems refer to the MC9S12ZVMB Safety Manual.

The document revision on the Internet is the most current. To verify this is the latest revision, refer to:

nxp.com.

This document contains information for all modules except the CPU. For CPU information please refer to the CPU S12Z Reference Manual. This revision history table summarizes changes to this document. The individual module sections contain revision history tables with more detailed information.

#### NOTE

### This reference manual documents the S12ZVM-Family. It contains a superset of features within the family. Some module versions differ from one part to another within the family. Section 1.2.1 MC9S12ZVM-Family Member Comparison provides support to access the correct information for a particular part within the family.

NXP reserves the right to make changes without further notice to any products herein. NXP makes no warranty, representation, or guarantee regarding the suitability of its products for any particular purpose, nor does NXP assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in NXP data sheets and/or specifications can and do vary in different applications, and actual performance may vary over time. All operating parameters, including "typicals," must be validated for each customer application by customer's technical experts. NXP does not convey any license under its patent rights nor the rights of others. NXP Semiconductors products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the NXP Semiconductors product could create a situation where personal injury or death may occur. Should Buyer purchase or use NXP Semiconductors products for any such unintended or unauthorized application, Buyer shall indemnify and hold NXP Semiconductors and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that NXP Semiconductors was negligent regarding the design or manufacture of the part.

### Table 0-1. Revision History

| Date        | Revision | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 20 MAR 2015 | 2.0      | Added ZVMC256 information<br>Added mask set 2N95G information<br>Added more detailed PTU minimum trigger spacing description<br>Updated CPMU, PIM and GDU chapters for ZVMC256<br>Improved CPMU specification clarity (see CPMU revision history)<br>Removed electrical parameter classification<br>Added reset startup timing parameter<br>Updated BATS parameters<br>Extended BKGD V <sub>IL</sub> condition from 3.15V to 3.13V<br>Extended GDU operating range from 26V to 26.6V<br>Temperature sensor output at 150C changed from 2.25V to 2.33V.<br>Added GDU VBS current parameter<br>Updated package thermal information for ZVM32 and ZVM16 parts<br>Added VBG temperature and voltage dependency parameters<br>Added device stop current at 105C.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 22 APR 2015 | 2.1      | Updated Stop and Wait current parameter values (I <sub>SUPS</sub> , I <sub>SUPW</sub> )<br>Corrected 80LQFP-EP pin name from VSS2 to VSS1<br>Updated ZVMC256 VDDS regulator parameters.<br>Changed PL0 ESD specification<br>Minor corrections to PIM, PMF, SRAM and ADC chapters (see module revision histories)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

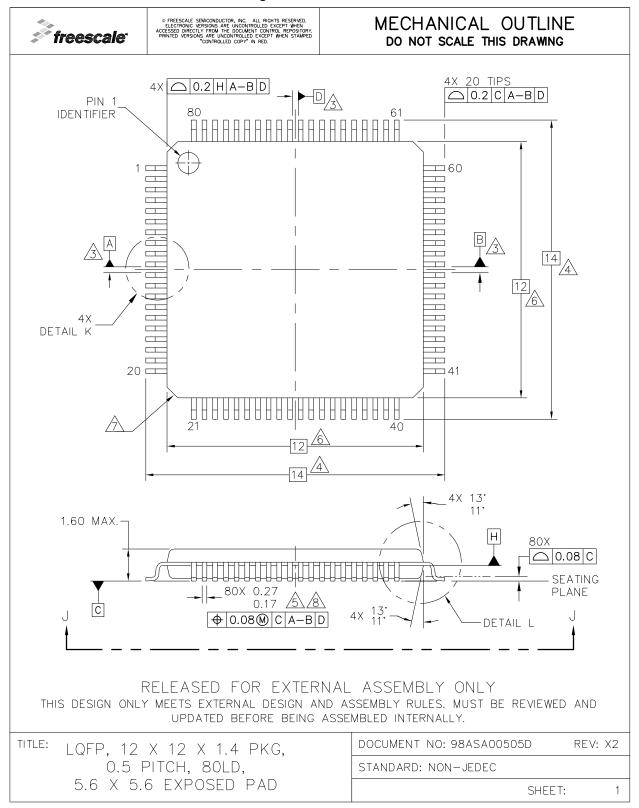

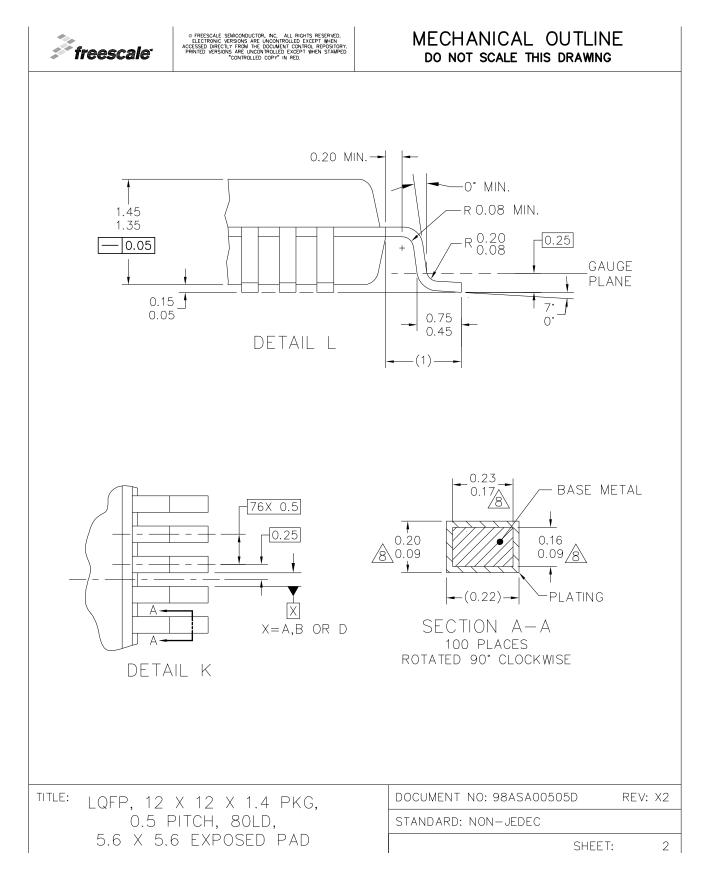

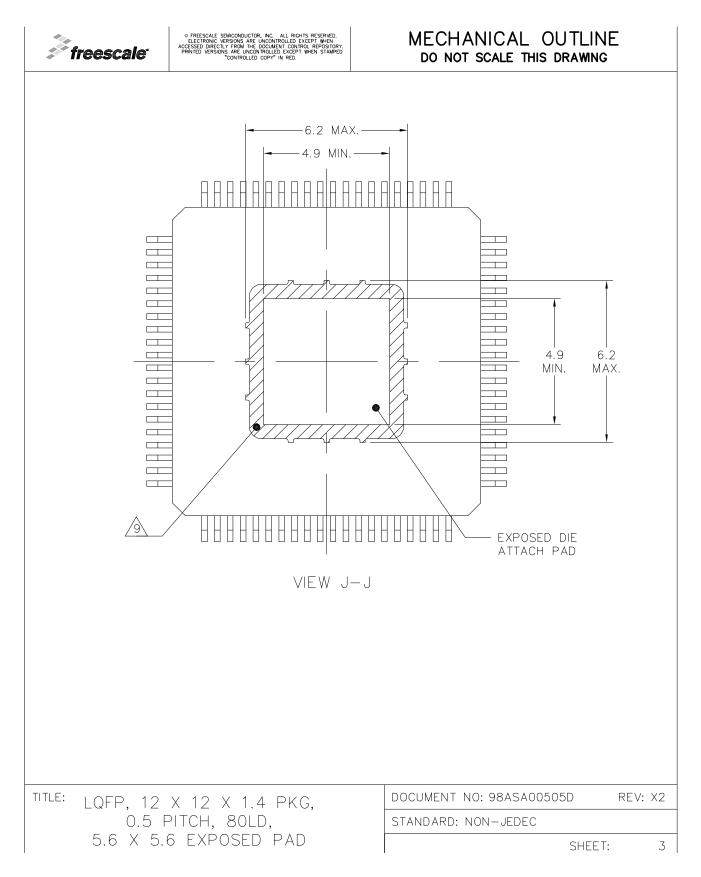

| 27 APR 2015 | 2.2      | Updated Stop current parameter values (I <sub>SUPS</sub> )<br>Updated LINPHY parameter range limit to 5.5V<br>Added more information about VDDS1, VDDS2, SNPS1, SNPS2 to CPMU chapter.<br>Reintroduced EPRES bit for GDU V4<br>Added 80LQFP-EP mechanical package information                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

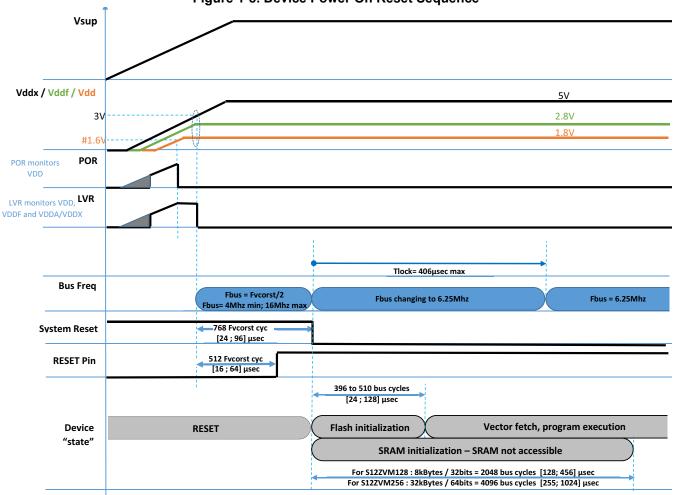

| 20 NOV 2015 | 2.3      | Added devices to Part ID list Table 1-6<br>Added explanation of GSUF dependency on xN14N mask set Table 1-19<br>Minor corrections to reset source and interrupt vector tables Table 1-15<br>Added device level POR information Figure 1-8<br>Minor correction to PIM chapter<br>Added constraints to EXTCON, SCS2 and SCS1 bits in CPMU chapter<br>Added PMF version difference table Table 15-3<br>Corrected footnotes and parameter spelling in GDU register summary<br>Noted GDU sense amplifier dependence on GFDE bit<br>Documented that flash option (FOPT) register can be written in special mode<br>Added pulsed absolute maximum rating for HSx pins Table A-2<br>Extended VDDS1 and VDDS2 maximum ratings Table A-2<br>Added thermal resistance parameter values for 80LQFP-EP package<br>Added VREG configuration to Run/Wait/Stop current measurement configurationTable A-16<br>Removed de-saturation thresholds from electrical spec. tables<br>Added max. and min. values for GDU HD signal division through phase mux.<br>Removed incorrect limit from BATS electrical parameter table headers<br>Extended CANPHY maximum ratings to 175°C<br>Updated SRAM_ECC chapter to cover ZVMC256<br>Minor correction to PMF chapter<br>Updated typical Stop IDD and Pseudo Stop IDD values for ZVMC256 based on validation data<br>Added ZVMC256 parameter for Stop IDD with CANPHY and API enabled Table A-19<br>Renamed bit GSLEWMOD to TDEL (GDU V6). Removed GSLEWMOD bit (GDU V5)<br>Noted temperature sensor slope is subject to further characterization |

#### Table 0-1. Revision History

| Date        | Revision | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 14 DEC 2015 | 2.4      | Added T1IC0RR to PIM MODRR2 register<br>Updated temperature sensor electrical specification, Table B-1<br>Added GDU current sense amp unity bandwidth parameter Table E-1, Table E-2<br>Added GDU current sense input resistance footnote Table E-1, Table E-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

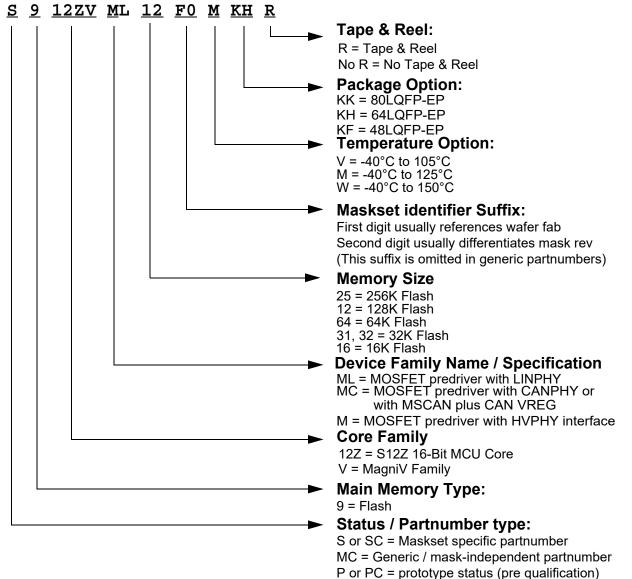

| 14 JAN 2016 | 2.5      | Clarified non production mask sets Table 1-4, Table 1-6<br>Updated ordering information in Appendix L<br>Changed RESET pin input pulse passed parameter minimum specification value.Table A-13<br>Replaced Freescale with NXP in logo and page footers<br>Added maximum value for GDU parameter VBSx current whilst high side inactive Table E-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

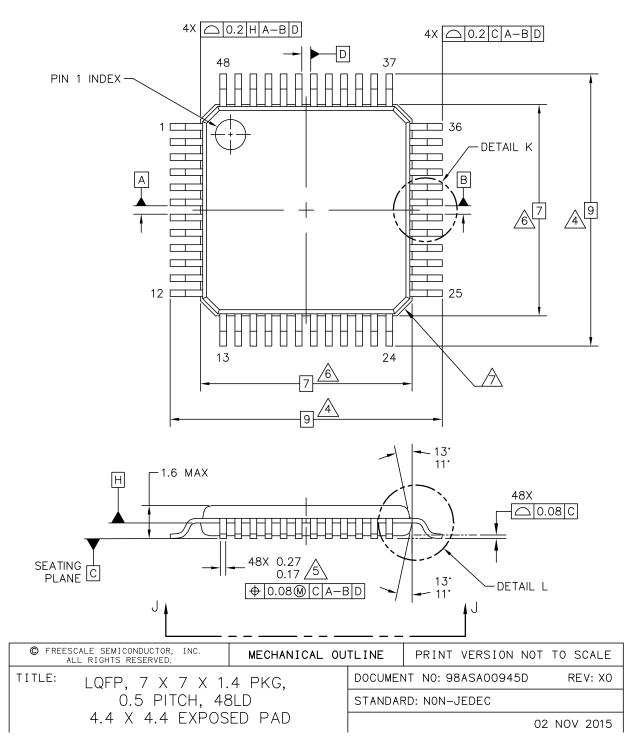

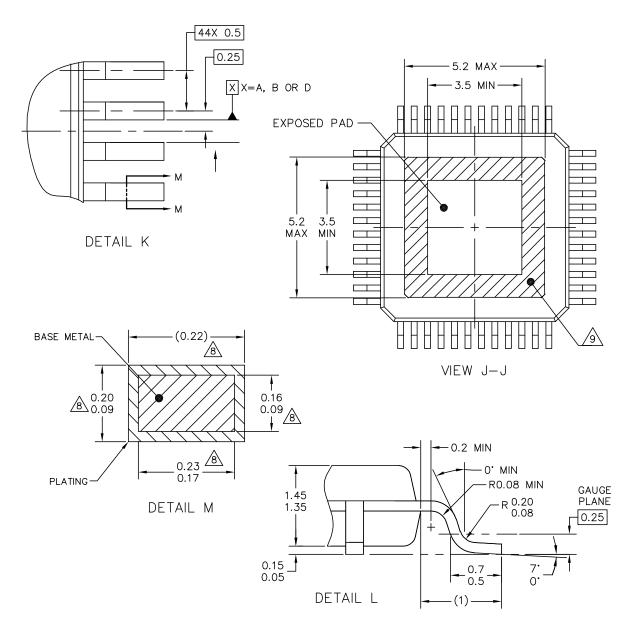

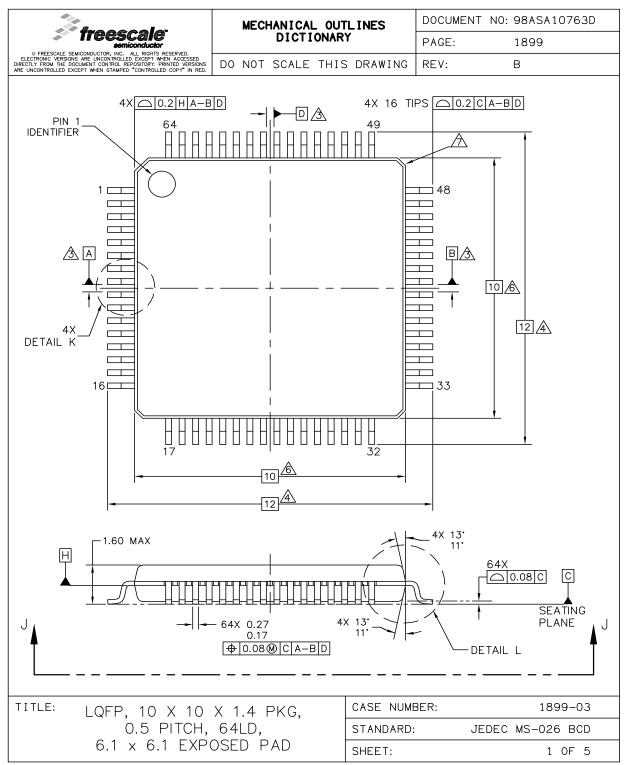

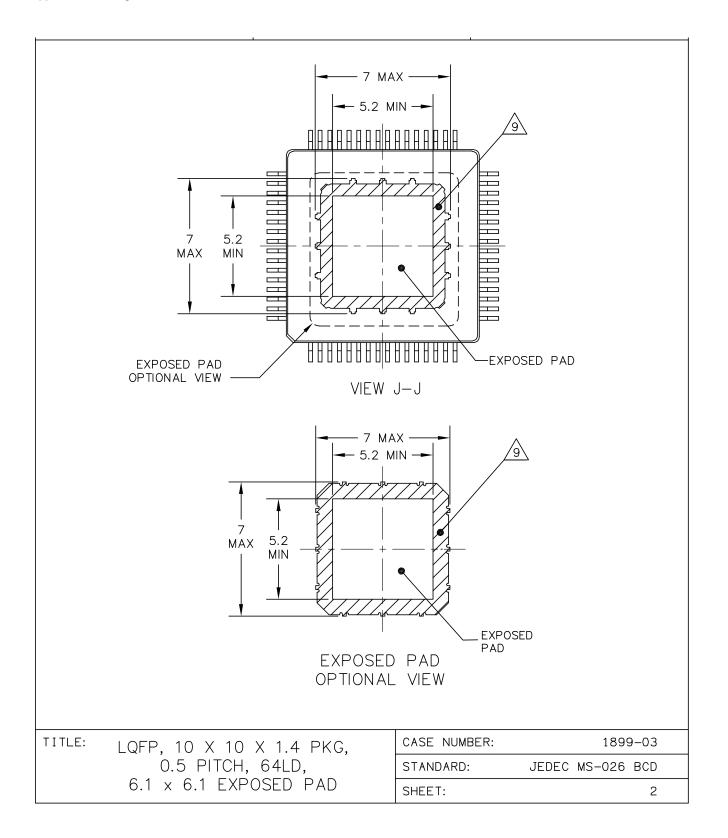

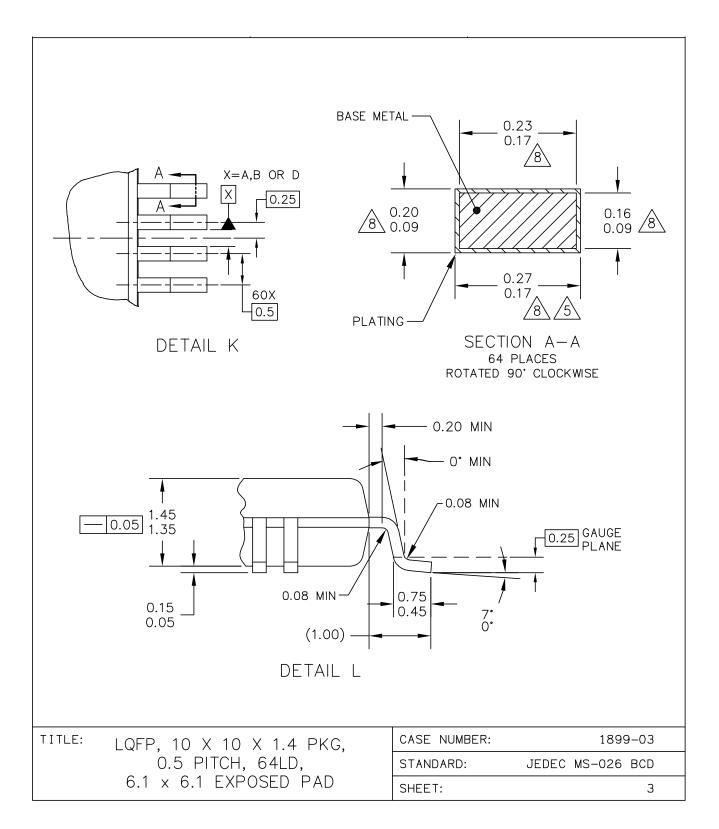

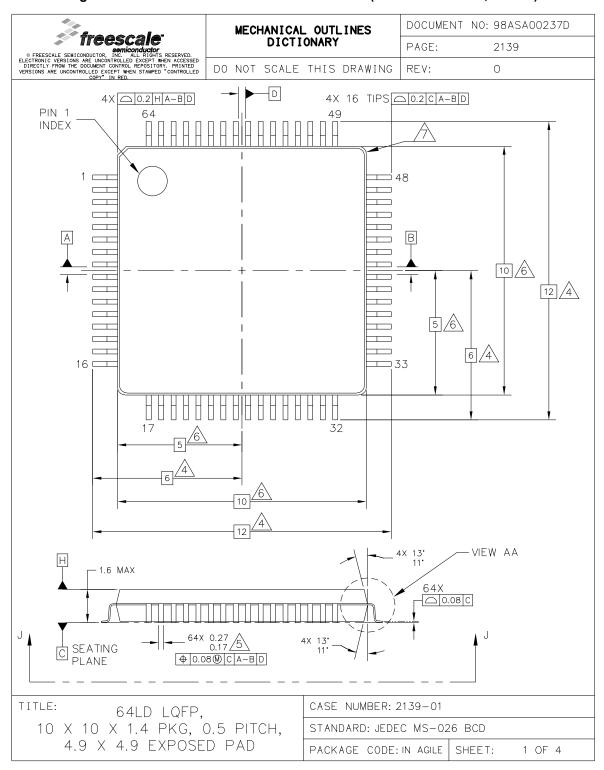

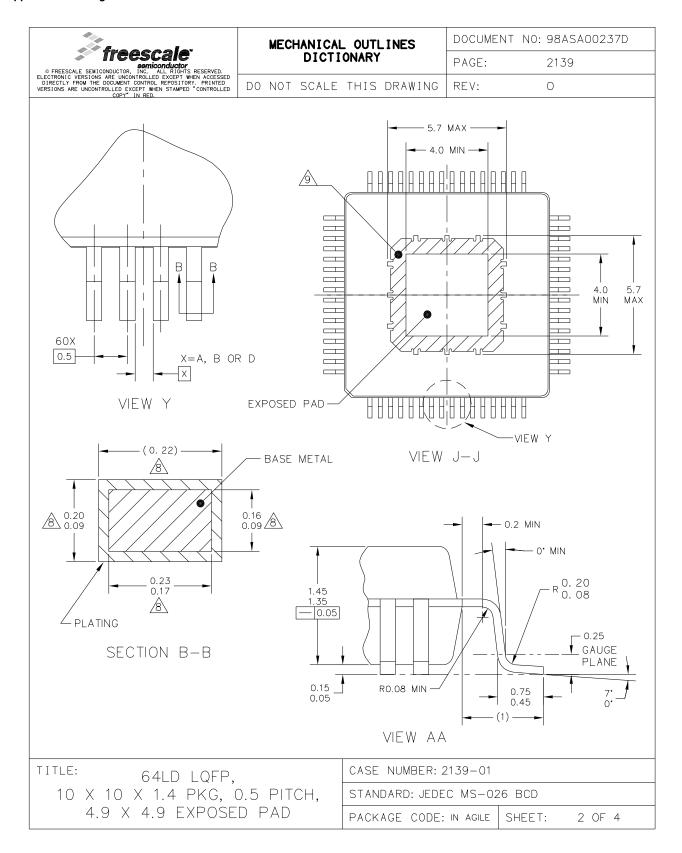

| 07 MAR 2016 | 2.6      | Added 3N95G mask set information Table 1-19, Table 1-4, Table 1-6<br>Added list of ISO26262 compliant devices<br>Moved GDU mask set dependent features to device overview section Table 1-19<br>Added new 64LQFP-EP package diagrams Table K.2<br>Added minimum value for GDU parameter VBSx current whilst high side inactive Table E-2<br>Updated V <sub>CSAoff</sub> parameter limits for GDU V5 and GDU V6 Table E-1, Table E-2<br>Added ADCCMD1[7:6] device dependencies in register listing Section M.13, Section M.14<br>Simplified GDU device dependencies in register listing Section M.15<br>Corrected High Temperature Interrupt spec. (cannot wake up from STOP) Table 1-16<br>Added footnote to Table A-14<br>ZVMC256: added typical Run/Wait IDD values, updated 85°C Stop IDD Table A-18, Table A-19<br>Added bootstrap diode resistance parameter Table E-2<br>Updated GDU boost coil current limit specification Table E-2, Table E-1<br>Reverted to original current sense amp. offset values Table E-2, Table E-1<br>Added package to mask set mapping table Table K-1 |

| 08 MAR 2016 | 2.7      | Changed maximum value of V <sub>BSTOFF</sub> Table E-2, Table E-1<br>Updated 48LQFP-EP Mechanical Information Diagram Section K.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 19 APR 2016 | 2.8      | Added PAD pin leakage specification at 125°C Table A-12<br>Updated t <sub>HGON</sub> , t <sub>HGOFF</sub> parameter values Table E-1<br>Specified VRH drop when using VDDS1 or VDDS2 as VRH on ZVMC256 Section C.1.1.5<br>Added min. and max. desaturation comparator filter times to electrical spec. Table E-1<br>Updated 64LQFP-EP thermal parameters Table A-9, Table A-10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 06 JUN 2016 | 2.9      | Fixed corrupted symbol fonts Table A-3, Table A-5<br>Corrected wrong IFR reference Section 20.3.2.10<br>Clarified PAD8 leakage better Table A-12<br>Added I <sub>SUPR</sub> and I <sub>SUPW</sub> maximum values at T <sub>J</sub> = 175°C for ZVMC256 Table A-18<br>Added Pseudo STOP maximum current for ZVMC256 Table A-20<br>Removed bandgap temperature dependency footnote, Table B-1<br>Changed ZVMC256 SNPS monitor threshold min/max values Table B-2<br>Changed VLS current limit threshold to 112mA Table E-1, Table E-2<br>Removed desaturation comparator filter times from GDU chapter.<br>Added desaturation comparator levels to Table E-1, Table E-2<br>Added low side desaturation comparator functional range as footnote Table E-1, Table E-2                                                                                                                                                                                                                                                                                                                         |

| 29 JUN 2016 | 2.10     | Updated GDU VBS filter Figure 18-20<br>Removed incorrect reference to temperature sensor influencing GDU outputs Section 1.13.3.4<br>Changed Stop IDD (ISUPS) specifications for ZVMC256 Table A-19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

### Table 0-1. Revision History

| Date        | Revision | Description                                                                                                                                                                                                                                                                                                                                                                         |

|-------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

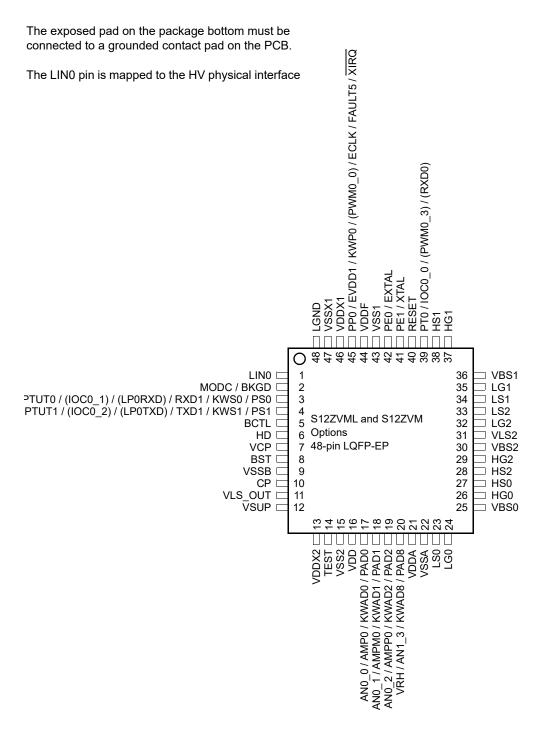

| 28 OCT 2016 | 2.11     | Added IOC0 signal mapping to 48LQFP package Figure 1-6<br>Fixed corrupted symbol fonts in PIM chapter<br>Added diode to VDDC pin Figure 1-18<br>Updated Stop mode current ISUPS maximum values Table A-19<br>Updated tdelon, tdeloff values Table E-1                                                                                                                               |

| 25 Jul 2017 | 2.12     | Updated Section 1.7.2.26.8, "VDDC (Only Available On S12ZVMC Versions)"<br>Updated Chapter 20, "Flash Module (S12ZFTMRZ)<br>Added note on HVI current injection in Table A-14<br>Updated Section C.1.1.4, "Current Injection"<br>Updated footnotes ofTable E-1<br>Updated tdelon, tdeloff values Table E-2                                                                          |

| 28 Apr 2019 | 2.13     | Removed "pulse accumulator" references in Section Chapter 11, "Timer Module (TIM16B4CV3)<br>Block Description" and Section Chapter 12, "Timer Module (TIM16B2CV3) Block Description"<br>Updated footnote 1 in Table A-6<br>Removed obsolete footnotes in Table E-1 and Table E-2<br>Removed term "preliminary" from title of E.2, "GDU specifications for devices featuring GDU V5" |

# Chapter 1 Device Overview MC9S12ZVM-Family

| 1.1 | Introduc | ction                                               | . 25 |

|-----|----------|-----------------------------------------------------|------|

| 1.2 | Features | s                                                   | . 26 |

|     | 1.2.1    | MC9S12ZVM-Family Member Comparison                  | . 26 |

|     | 1.2.2    | Module Version Differences Within The S12ZVM Family | . 27 |

|     | 1.2.3    | Functional Differences Between Masksets             |      |

| 1.3 | Chip-Le  | evel Features                                       | . 28 |

| 1.4 |          | Features                                            |      |

|     | 1.4.1    | S12Z Central Processor Unit (CPU)                   | . 29 |

|     | 1.4.2    | Embedded Memory                                     |      |

|     | 1.4.3    | Clocks, Reset & Power Management Unit (CPMU)        | . 31 |

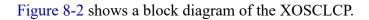

|     | 1.4.4    | Main External Oscillator (XOSCLCP)                  |      |

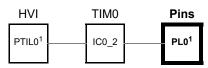

|     | 1.4.5    | Timer (TIM0)                                        |      |

|     | 1.4.6    | Timer (TIM1) (ZVMC256 only)                         |      |

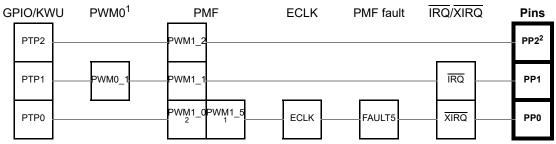

|     | 1.4.7    | Pulse width Modulator with Fault protection (PMF)   |      |

|     | 1.4.8    | Programmable Trigger Unit (PTU)                     |      |

|     | 1.4.9    | LIN physical layer transceiver (ZVML devices only)  |      |

|     | 1.4.10   | Serial Communication Interface Module (SCI)         |      |

|     |          | Multi-Scalable Controller Area Network (MSCAN)      |      |

|     |          | Serial Peripheral Interface Module (SPI)            |      |

|     |          | Analog-to-Digital Converter Module (ADC)            |      |

|     |          | Supply Voltage Sensor (BATS)                        |      |

|     |          | On-Chip Voltage Regulator system (VREG)             |      |

|     |          | Gate Drive Unit (GDU)                               |      |

|     |          | Current Sense                                       |      |

|     | 1.4.18   | High Voltage Physical Interface (ZVM32, ZVM16)      | . 35 |

|     |          | CAN Physical Layer Module (ZVMC256 only)            |      |

|     |          | Pulse Width Modulation Module (PWM) (ZVMC256 only)  |      |

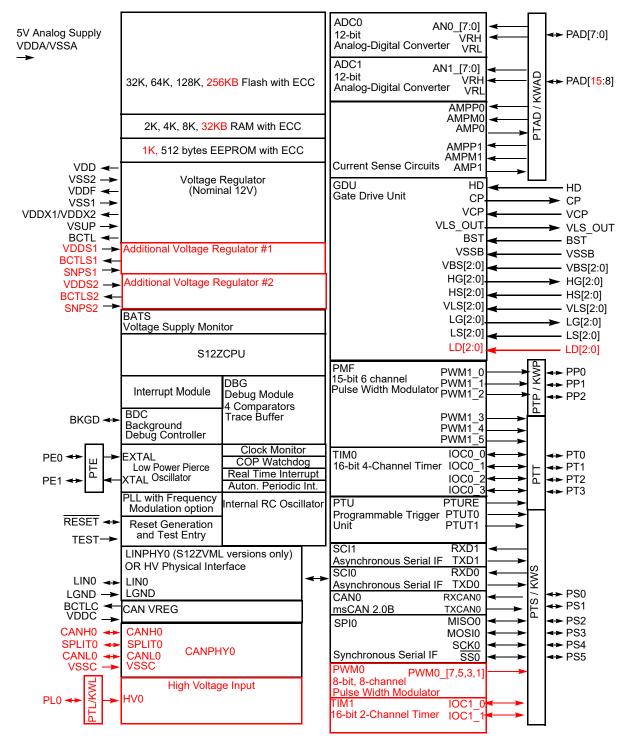

| 1.5 |          | Diagram                                             |      |

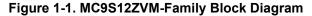

| 1.6 | Device   | Memory Map                                          | . 38 |

|     | 1.6.1    | Flash Module                                        |      |

|     | 1.6.2    | Part ID Assignments                                 | . 41 |

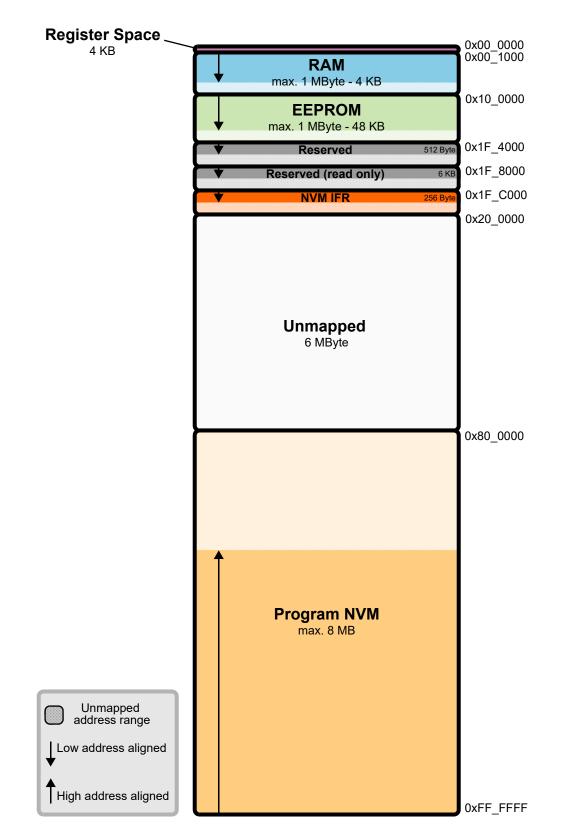

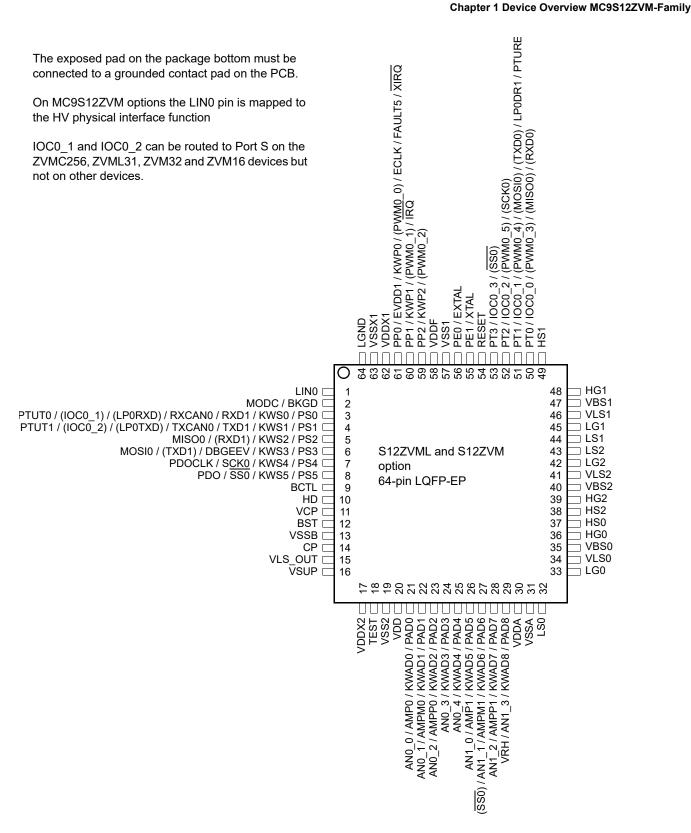

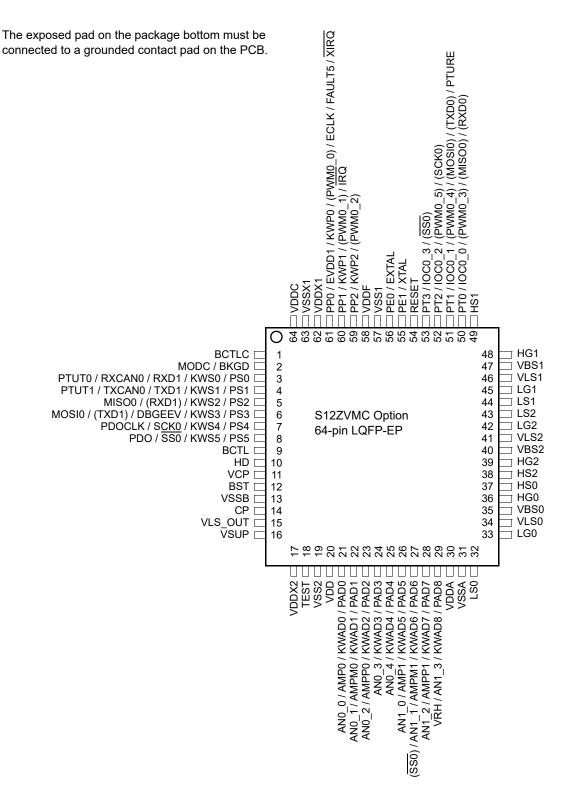

| 1.7 | Signal I | Description and Device Pinouts                      | . 41 |

|     | 1.7.1    | Pin Assignment Overview                             |      |

|     | 1.7.2    | Detailed External Signal Descriptions               | . 42 |

|     | 1.7.3    | Power Supply And Voltage Regulator Related Pins     |      |

|     | 1.7.4    | Package and Pinouts                                 |      |

| 1.8 | Internal | Signal Mapping                                      |      |

|     | 1.8.1    | ADC Connectivity                                    | . 63 |

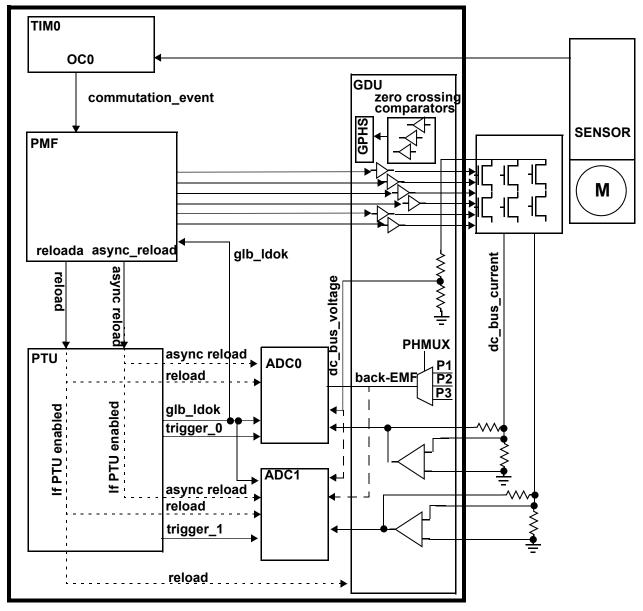

|     | 1.8.2    | Motor Control Loop Signals                          | . 64 |

|     | 1.8.3    | Device Level PMF Connectivity                       |      |

|     | 1.8.4    | BDC Clock Source Connectivity                       |      |

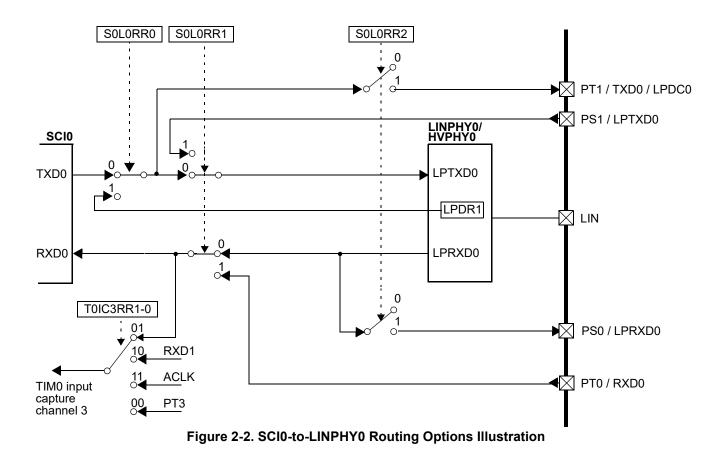

|     | 1.8.5    | LINPHY Connectivity                                 | . 65 |

|     | 1.8.6    | HVPHY Connectivity                                  |      |

|      | 1.8.7    | FTMRZ Connectivity                                 | 66 |

|------|----------|----------------------------------------------------|----|

|      | 1.8.8    | CPMU Connectivity                                  | 66 |

| 1.9  | Modes of | of Operation                                       |    |

|      | 1.9.1    | Chip Configuration Modes                           | 66 |

|      | 1.9.2    | Debugging Modes                                    | 67 |

|      | 1.9.3    | Low Power Modes                                    | 67 |

| 1.10 | Security | 7                                                  | 68 |

|      |          | Features                                           |    |

|      |          | Securing the Microcontroller                       |    |

|      |          | Operation of the Secured Microcontroller           |    |

|      |          | Unsecuring the Microcontroller                     |    |

|      |          | Reprogramming the Security Bits                    |    |

|      | 1.10.6   | Complete Memory Erase                              | 70 |

| 1.11 |          | nd Interrupts                                      |    |

|      |          | Reset                                              |    |

|      |          | Interrupt Vectors                                  |    |

|      |          | Effects of Reset                                   |    |

| 1.12 |          | device level dependencies                          |    |

|      |          | CPMU COP and GDU Configuration                     |    |

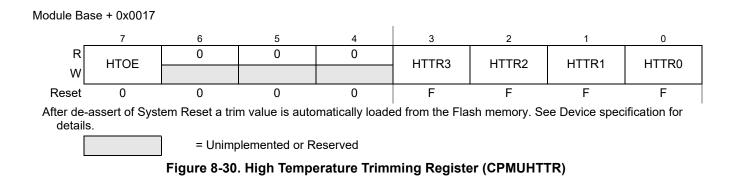

|      |          | CPMU High Temperature Trimming                     |    |

|      | 1.12.3   | CPMU VDDC enable                                   | 77 |

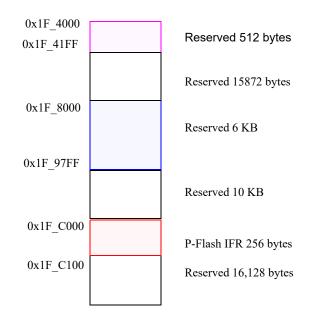

|      |          | Flash IFR Mapping                                  |    |

| 1.13 | 11       | tion Information                                   |    |

|      |          | ADC Calibration                                    |    |

|      |          | SCI Baud Rate Detection                            |    |

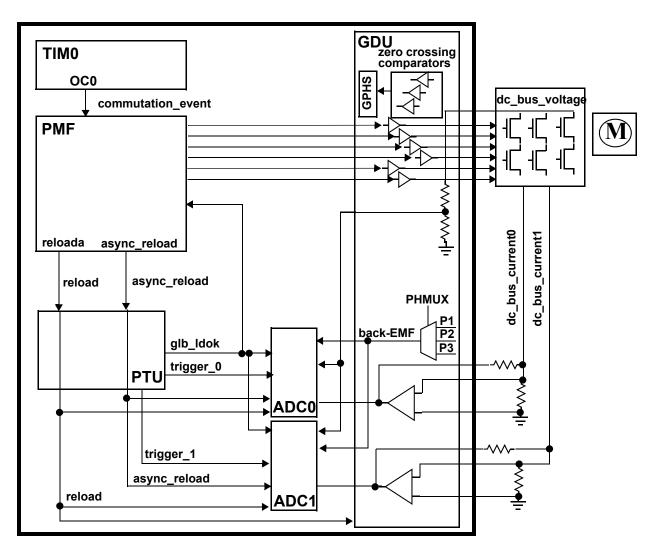

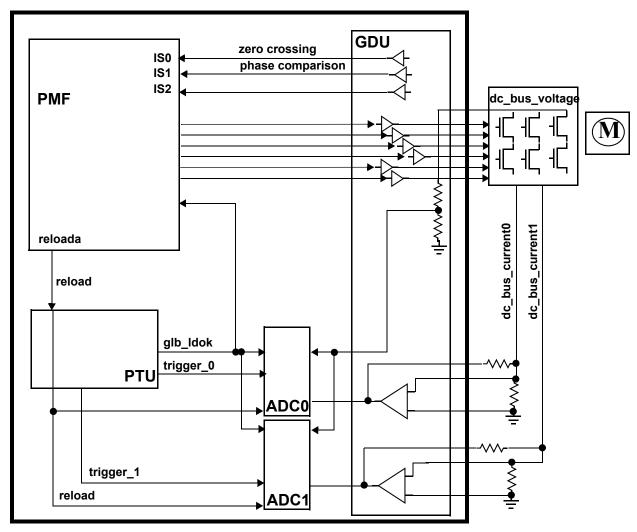

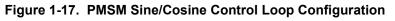

|      |          | Motor Control Application Overview                 |    |

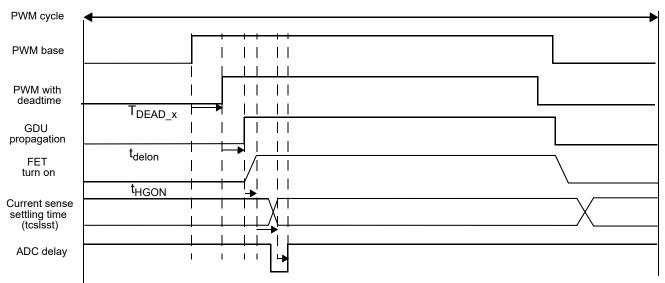

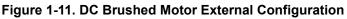

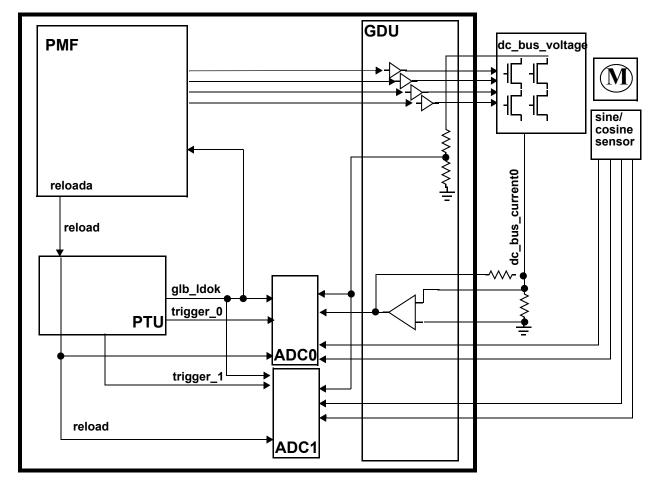

|      |          | BDCM Complementary Mode Operation                  |    |

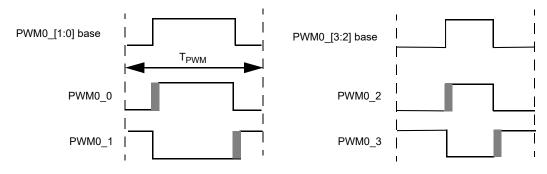

|      |          | BLDC Six-Step Commutation                          |    |

|      |          | PMSM Control                                       |    |

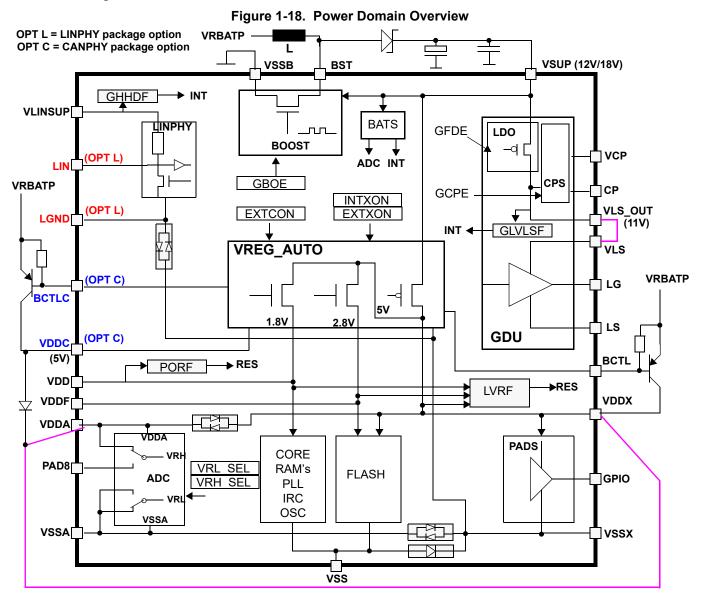

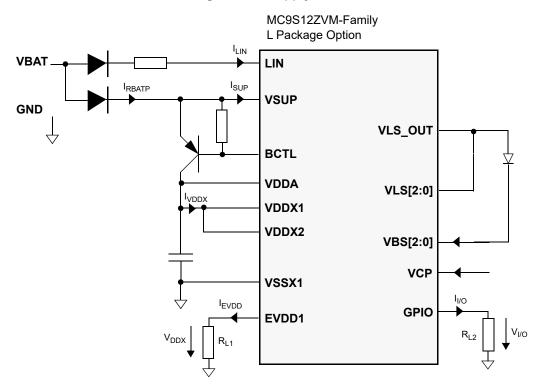

|      |          | Power Domain Overview (All devices except ZVMC256) |    |

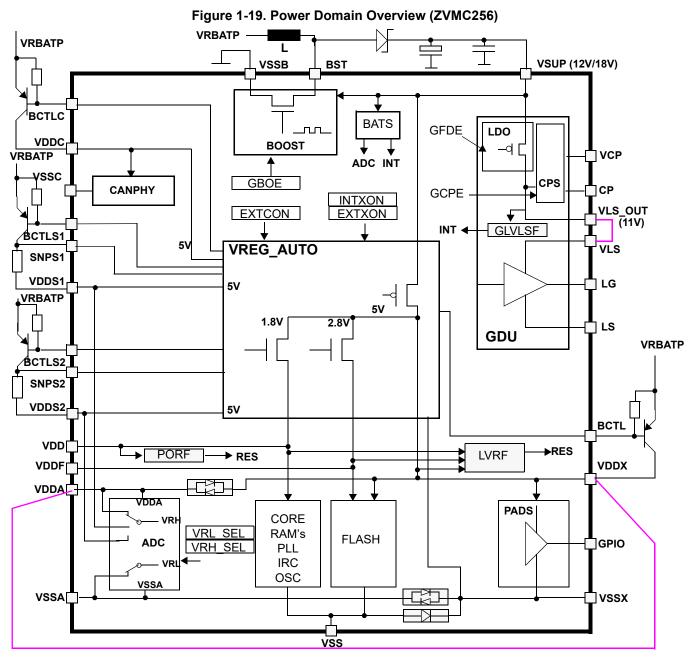

|      | 1.13.8   | Power Domain Overview (ZVMC256)                    | 98 |

|      |          |                                                    |    |

## Chapter 2 Port Integration Module (S12ZVMPIMV3)

| 2.1 | Introduc | tion                            | 104 |

|-----|----------|---------------------------------|-----|

|     | 2.1.1    | Overview                        | 104 |

|     | 2.1.2    | Features                        | 107 |

| 2.2 | External | Signal Description              | 108 |

| 2.3 | Memory   | Map and Register Definition     | 115 |

|     | 2.3.1    | Register Map                    | 116 |

|     | 2.3.2    | PIM Registers 0x0200-0x020F     | 122 |

|     | 2.3.3    | PIM Generic Registers           | 133 |

|     | 2.3.4    | PIM Generic Register Exceptions | 140 |

| 2.4 | Function | nal Description                 | 147 |

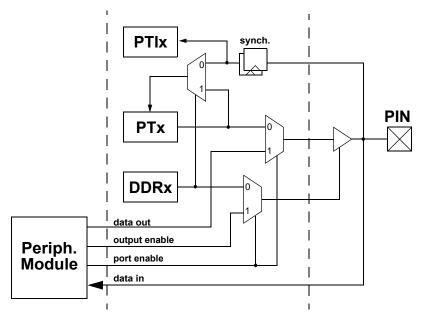

|     | 2.4.1    | General                         | 147 |

|     | 2.4.2     | Registers                                    |

|-----|-----------|----------------------------------------------|

|     | 2.4.3     | Pin I/O Control                              |

|     | 2.4.4     | Interrupts                                   |

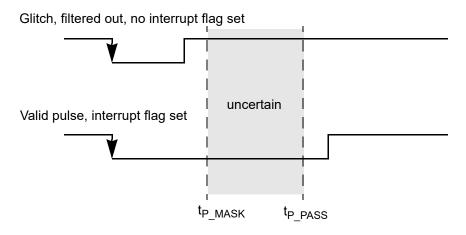

|     | 2.4.5     | Pin interrupts and Key-Wakeup (KWU) 151      |

|     | 2.4.6     | Over-Current Interrupt                       |

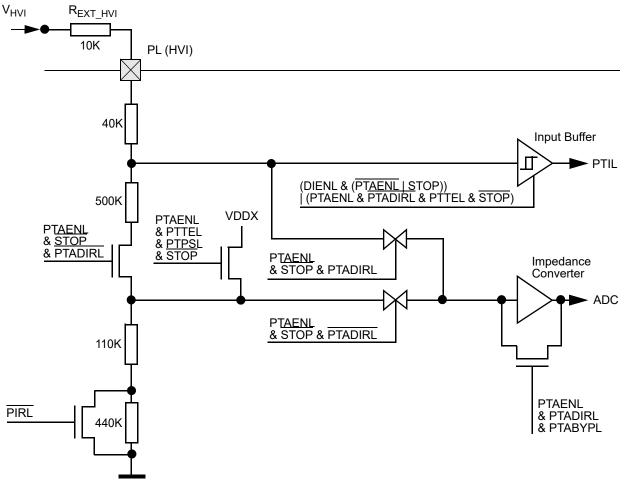

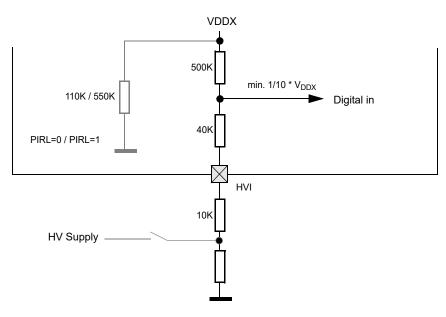

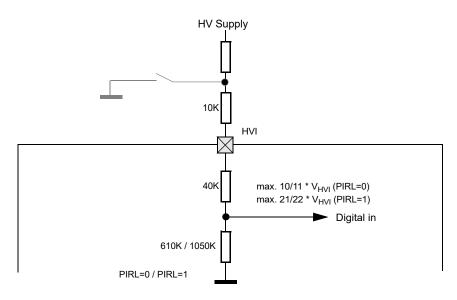

|     | 2.4.7     | High-Voltage Input                           |

| 2.5 | Initializ | ation and Application Information154         |

|     | 2.5.1     | Port Data and Data Direction Register writes |

|     | 2.5.2     | Open Input Detection on HVI                  |

|     | 2.5.3     | Over-Current Protection on EVDD1             |

## Chapter 3 Memory Mapping Control (S12ZMMCV1)

| 3.1 | Introduc | tion                        |

|-----|----------|-----------------------------|

|     | 3.1.1    | Glossary                    |

|     | 3.1.2    | Overview                    |

|     | 3.1.3    | Features                    |

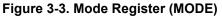

|     | 3.1.4    | Modes of Operation          |

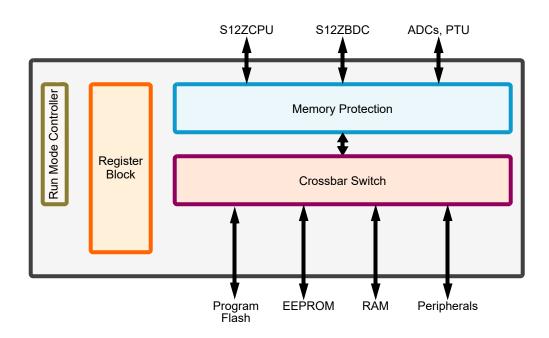

|     | 3.1.5    | Block Diagram               |

| 3.2 | External | Signal Description          |

| 3.3 | Memory   | Map and Register Definition |

|     |          | Memory Map                  |

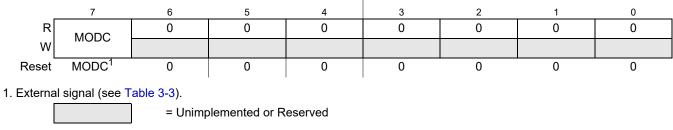

|     | 3.3.2    | Register Descriptions       |

| 3.4 | Function | nal Description             |

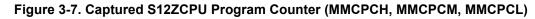

|     |          | Global Memory Map           |

|     | 3.4.2    | Illegal Accesses            |

|     | 3.4.3    | Uncorrectable ECC Faults    |

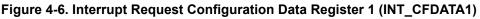

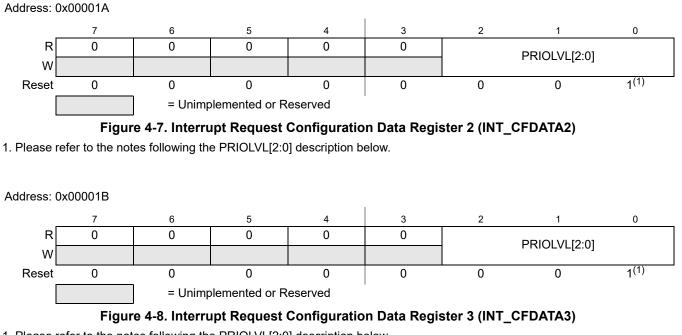

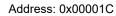

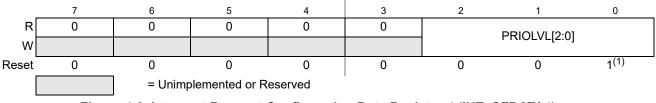

## Chapter 4 Interrupt (S12ZINTV0)

| 4.1 | Introduc | tion                          |

|-----|----------|-------------------------------|

|     | 4.1.1    | Glossary                      |

|     | 4.1.2    | Features                      |

|     | 4.1.3    | Modes of Operation            |

|     | 4.1.4    | Block Diagram                 |

| 4.2 | External | Signal Description            |

| 4.3 | Memory   | Map and Register Definition   |

|     | 4.3.1    | Module Memory Map         172 |

|     |          | Register Descriptions         |

| 4.4 | Function | nal Description               |

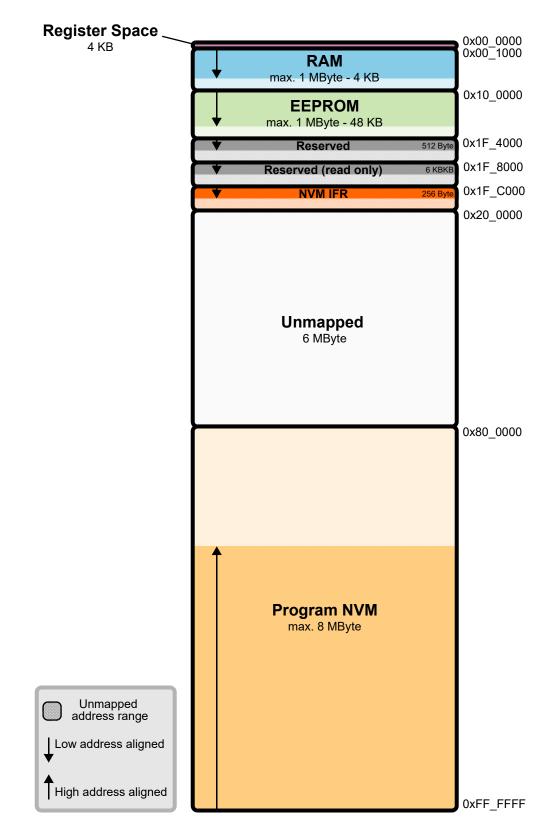

|     | 4.4.1    | S12Z Exception Requests       |

|     |          | Interrupt Prioritization      |

|     | 4.4.3    | Priority Decoder              |

|     | 4.4.4    | Reset Exception Requests      |

|     | 4.4.5      | Exception Priority             | 180 |

|-----|------------|--------------------------------|-----|

|     | 4.4.6      | Interrupt Vector Table Layout  | 180 |

| 4.5 | Initializa | ation/Application Information  | 180 |

|     | 4.5.1      | Initialization                 | 180 |

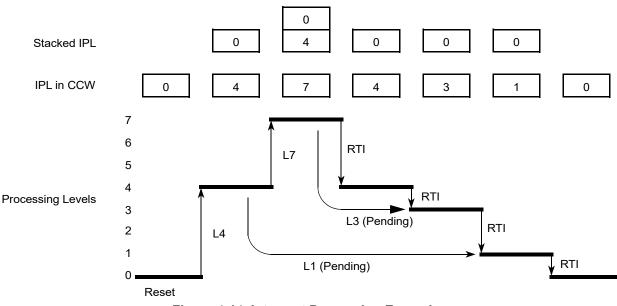

|     | 4.5.2      | Interrupt Nesting              | 181 |

|     | 4.5.3      | Wake Up from Stop or Wait Mode | 182 |

## Chapter 5

# Background Debug Controller (S12ZBDCV2)

| 5.1 | Introduc | tion                                                     |  |

|-----|----------|----------------------------------------------------------|--|

|     | 5.1.1    | Glossary                                                 |  |

|     | 5.1.2    | Features                                                 |  |

|     | 5.1.3    | Modes of Operation                                       |  |

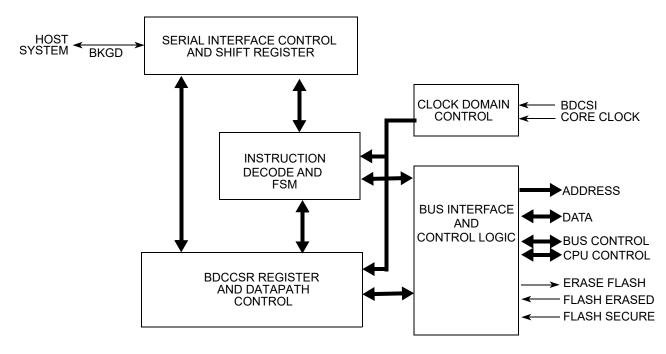

|     | 5.1.4    | Block Diagram                                            |  |

| 5.2 | External | l Signal Description                                     |  |

| 5.3 | Memory   | Map and Register Definition                              |  |

|     | 5.3.1    | Module Memory Map                                        |  |

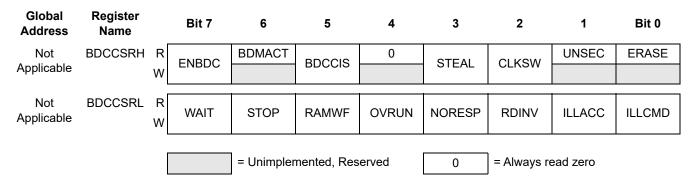

|     | 5.3.2    | Register Descriptions                                    |  |

| 5.4 | Function | nal Description                                          |  |

|     | 5.4.1    | Security                                                 |  |

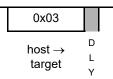

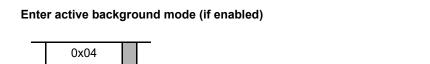

|     | 5.4.2    | Enabling BDC And Entering Active BDM                     |  |

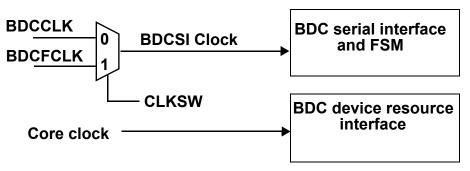

|     | 5.4.3    | Clock Source                                             |  |

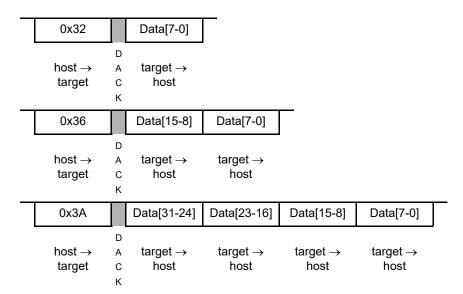

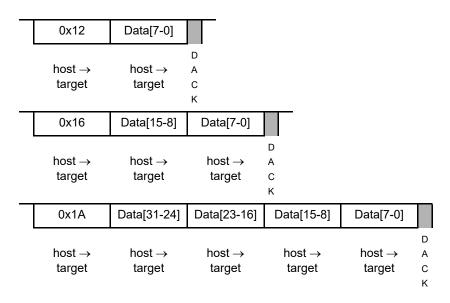

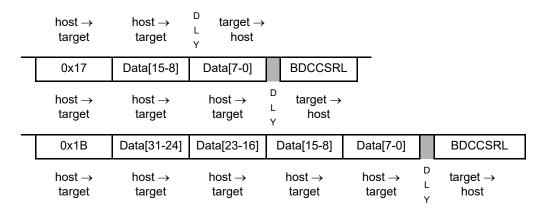

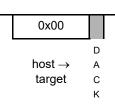

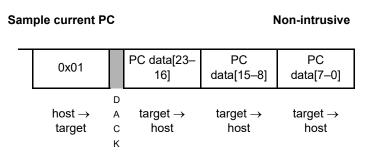

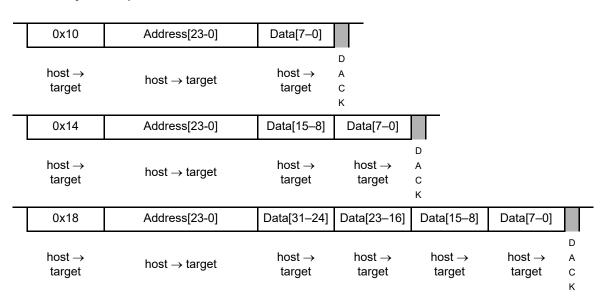

|     | 5.4.4    | BDC Commands                                             |  |

|     | 5.4.5    | BDC Access Of Internal Resources                         |  |

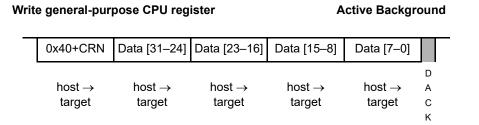

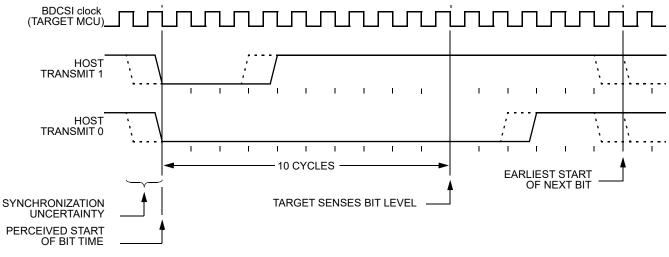

|     | 5.4.6    | BDC Serial Interface                                     |  |

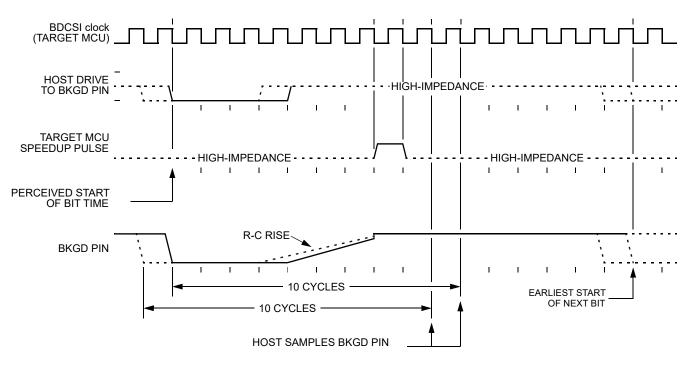

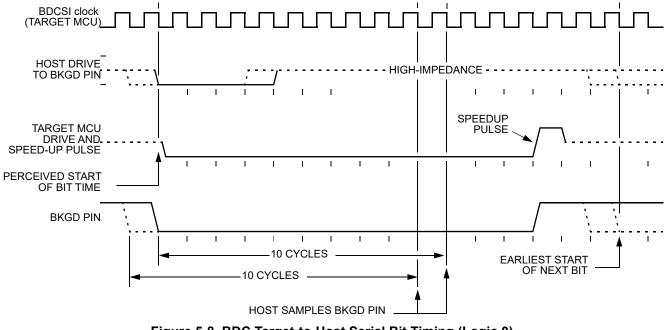

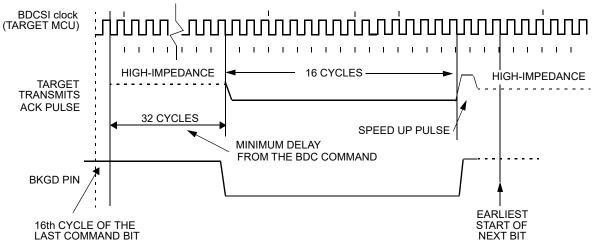

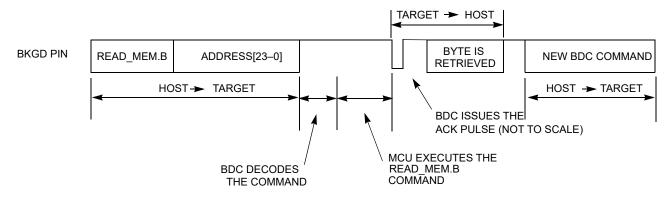

|     | 5.4.7    | Serial Interface Hardware Handshake (ACK Pulse) Protocol |  |

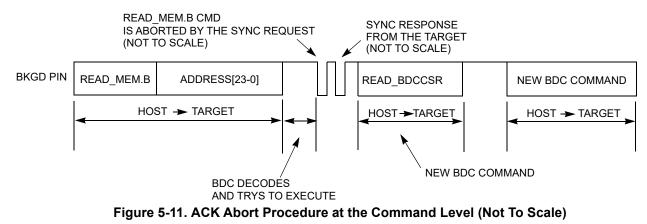

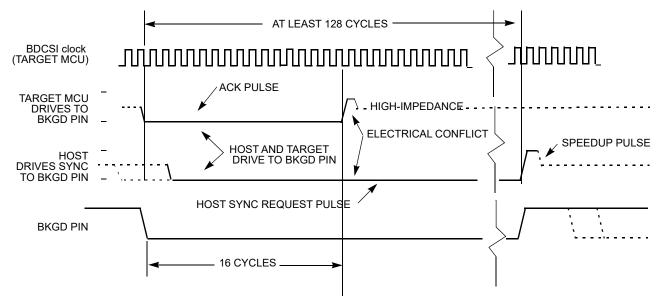

|     | 5.4.8    | Hardware Handshake Abort Procedure                       |  |

|     | 5.4.9    | Hardware Handshake Disabled (ACK Pulse Disabled)         |  |

|     | 5.4.10   | Single Stepping                                          |  |

|     | 5.4.11   | Serial Communication Timeout                             |  |

| 5.5 | Applica  | tion Information                                         |  |

|     | 5.5.1    | Clock Frequency Considerations                           |  |

## Chapter 6 S12Z Debug (S12ZDBG) Module

| Introduc | tion                                                           | 3                                                                                                                                                                                       |

|----------|----------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6.1.1    | Glossary                                                       | 4                                                                                                                                                                                       |

| 6.1.2    | Overview                                                       | 4                                                                                                                                                                                       |

| 6.1.3    | Features                                                       | 4                                                                                                                                                                                       |

| 6.1.4    | Modes of Operation                                             | 5                                                                                                                                                                                       |

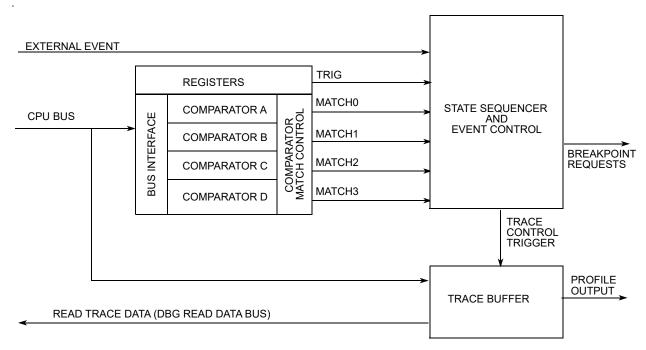

| 6.1.5    | Block Diagram                                                  | 6                                                                                                                                                                                       |

| External | Signal Description                                             | 6                                                                                                                                                                                       |

| 6.2.1    | External Event Input                                           | 6                                                                                                                                                                                       |

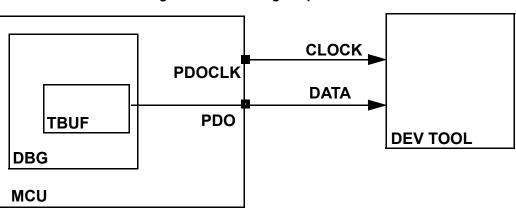

| 6.2.2    | Profiling Output                                               | 7                                                                                                                                                                                       |

|          | 6.1.1<br>6.1.2<br>6.1.3<br>6.1.4<br>6.1.5<br>External<br>6.2.1 | Introduction2226.1.1Glossary2246.1.2Overview2246.1.3Features2246.1.4Modes of Operation2226.1.5Block Diagram2246.1.5Block Diagram2246.2.1External Event Input2246.2.2Profiling Output224 |

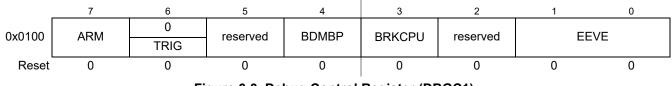

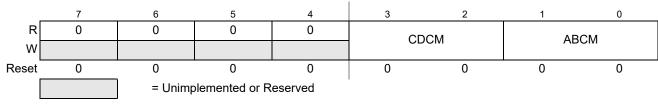

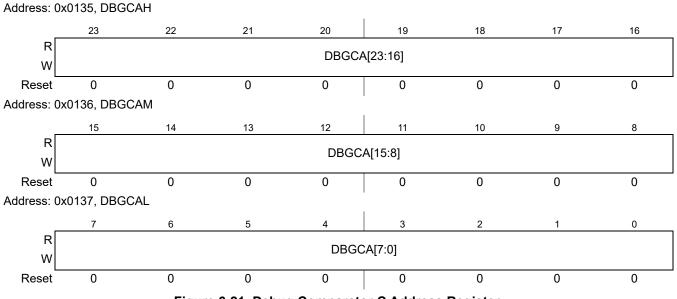

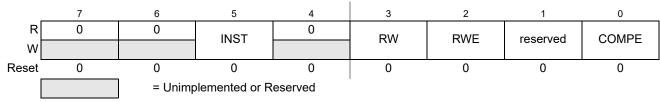

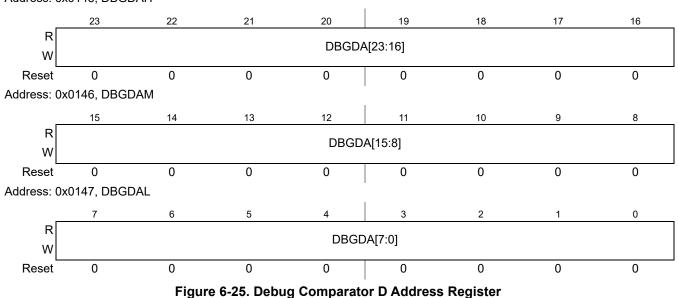

| 6.3 | Memory   | Map and Registers                            | 227 |

|-----|----------|----------------------------------------------|-----|

|     | 6.3.1    | Module Memory Map                            | 227 |

|     | 6.3.2    | Register Descriptions                        | 230 |

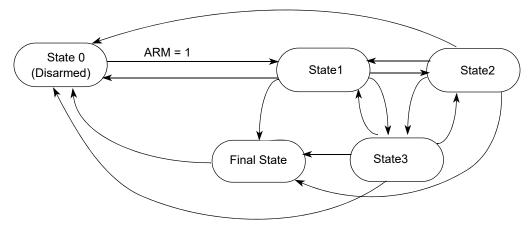

| 6.4 | Function | nal Description                              | 251 |

|     | 6.4.1    | DBG Operation                                | 251 |

|     | 6.4.2    | Comparator Modes                             | 251 |

|     | 6.4.3    | Events                                       | 255 |

|     | 6.4.4    | State Sequence Control                       | 257 |

|     | 6.4.5    | Trace Buffer Operation                       | 258 |

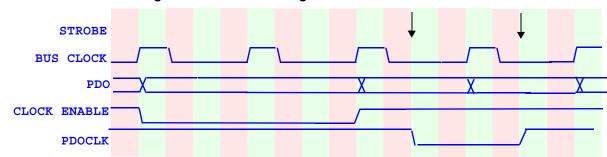

|     | 6.4.6    | Code Profiling                               | 267 |

|     | 6.4.7    | Breakpoints                                  | 271 |

| 6.5 | Applicat | tion Information                             | 272 |

|     | 6.5.1    | Avoiding Unintended Breakpoint Re-triggering | 272 |

|     | 6.5.2    | Debugging Through Reset                      | 272 |

|     | 6.5.3    | Breakpoints from other S12Z sources          | 273 |

|     | 6.5.4    | Code Profiling                               | 273 |

## Chapter 7 ECC Generation Module (SRAM\_ECCV1)

| 7.1.1    | Features                                                                                            | 275                                                                                                        |

|----------|-----------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|

| Memory   | Map and Register Definition                                                                         | . 276                                                                                                      |

| 7.2.1    | Register Summary                                                                                    | . 276                                                                                                      |

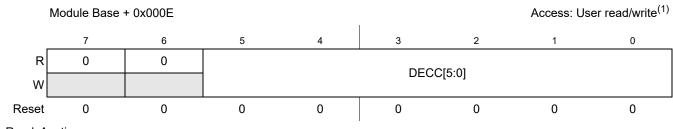

| 7.2.2    | Register Descriptions                                                                               | . 278                                                                                                      |

| Function | nal Description                                                                                     | . 282                                                                                                      |

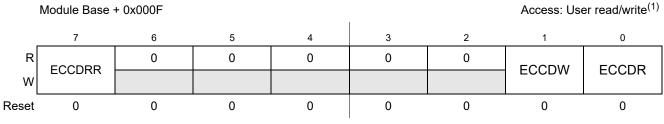

| 7.3.1    | Non-aligned Memory Write Access                                                                     | . 283                                                                                                      |

| 7.3.2    | Aligned 2 and 4 Byte Memory Write Access                                                            | . 284                                                                                                      |

| 7.3.3    | Memory Read Access                                                                                  | . 284                                                                                                      |

| 7.3.4    | Memory Initialization                                                                               | . 284                                                                                                      |

| 7.3.5    | Interrupt Handling                                                                                  | . 285                                                                                                      |

| 7.3.6    | ECC Algorithm                                                                                       | . 285                                                                                                      |

| 7.3.7    | ECC Debug Behavior                                                                                  | . 285                                                                                                      |

|          | 7.1.1<br>Memory<br>7.2.1<br>7.2.2<br>Function<br>7.3.1<br>7.3.2<br>7.3.3<br>7.3.4<br>7.3.5<br>7.3.6 | 7.3.4       Memory Initialization         7.3.5       Interrupt Handling         7.3.6       ECC Algorithm |

## Chapter 8

## S12 Clock, Reset and Power Management Unit (00.17)

| 8.1 | Introduc | etion                                                  | . 288 |

|-----|----------|--------------------------------------------------------|-------|

|     | 8.1.1    | Differences between S12CPMU_UHV_V10 and S12CPMU_UHV_V6 | . 289 |

|     | 8.1.2    | Features                                               | . 290 |

|     | 8.1.3    | Modes of Operation                                     | . 292 |

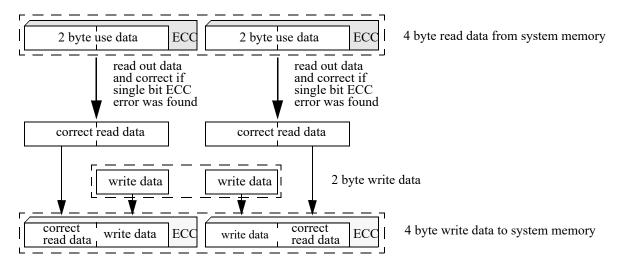

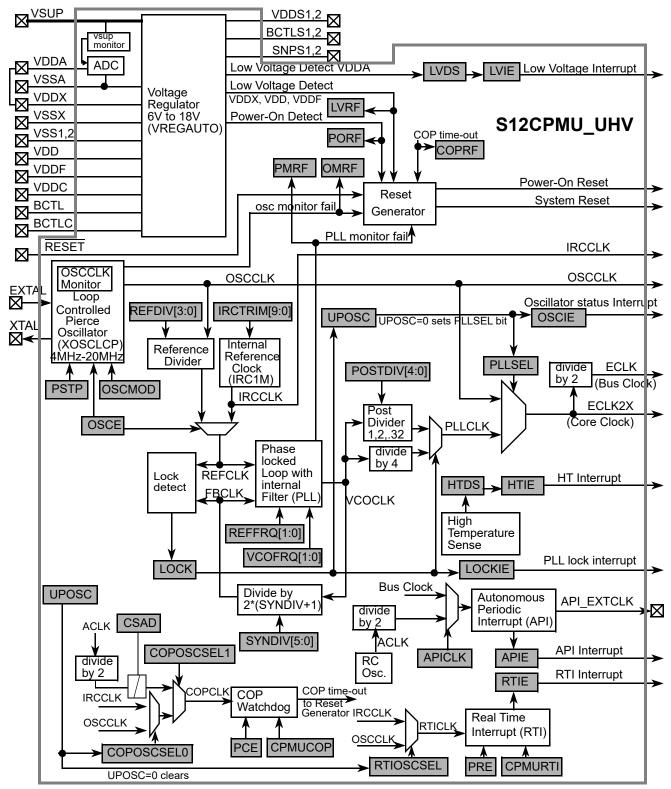

|     | 8.1.4    | S12CPMU_UHV_V10_V6 Block Diagram                       | . 295 |

| 8.2 | Signal I | Description                                            | 297   |

|     | 8.2.1    | RESET                                                  | . 297 |

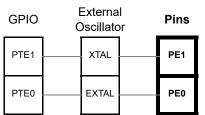

|     | 8.2.2    | EXTAL and XTAL                                         | . 297 |

|     | 8.2.3    | VSUP — Regulator Power Input Pin                       | . 297 |

|     |          |                                                        |       |

|     | 8.2.4      | VDDA, VSSA — Regulator Reference Supply Pins                      | 297 |

|-----|------------|-------------------------------------------------------------------|-----|

|     | 8.2.5      | VDDX, VSSX— Pad Supply Pins                                       | 297 |

|     | 8.2.6      | VDDC— CAN Supply Pin                                              | 298 |

|     | 8.2.7      | VDDS1— Sensor Supply1 Pin                                         |     |

|     | 8.2.8      | VDDS2— Sensor Supply2 Pin                                         | 298 |

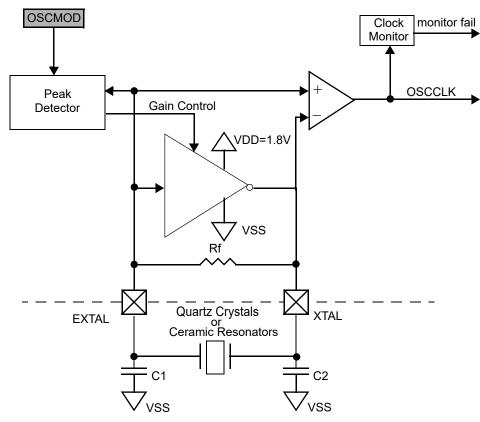

|     | 8.2.9      | BCTL—Base Control Pin for external PNP                            | 298 |

|     | 8.2.10     | BCTLC — Base Control Pin for external PNP for VDDC power domain   | 299 |

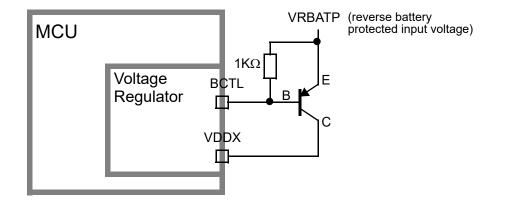

|     | 8.2.11     | BCTLS1 — Base Control Pin for external PNP for VDDS1 power domain | 299 |

|     | 8.2.12     | BCTLS2 — Base Control Pin for external PNP for VDDS2 power domain | 300 |

|     | 8.2.13     | SNPS1 — Sense Pin for VDDS1 power domain                          | 300 |

|     | 8.2.14     | SNPS2 — Sense Pin for VDDS2 power domain                          | 300 |

|     | 8.2.15     | VSS1,2 — Core Ground Pins                                         | 300 |

|     | 8.2.16     | VDD— Core Logic Supply Pin                                        | 301 |

|     | 8.2.17     | VDDF— NVM Logic Supply Pin                                        | 301 |

|     | 8.2.18     | API_EXTCLK — API external clock output pin                        | 301 |

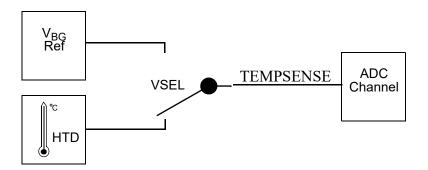

|     | 8.2.19     | TEMPSENSE — Internal Temperature Sensor Output Voltage            | 301 |

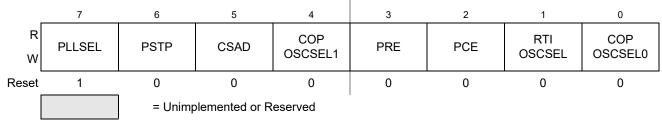

| 8.3 | Memory     | Map and Registers                                                 | 302 |

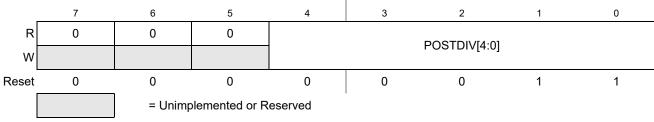

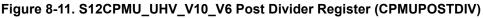

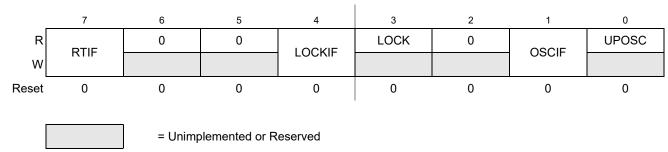

|     | 8.3.1      | Module Memory Map                                                 | 302 |

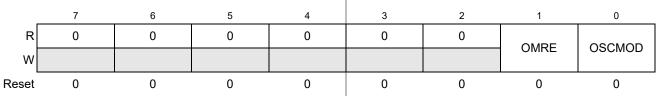

|     | 8.3.2      | Register Descriptions                                             | 304 |

| 8.4 | Function   | nal Description                                                   | 345 |

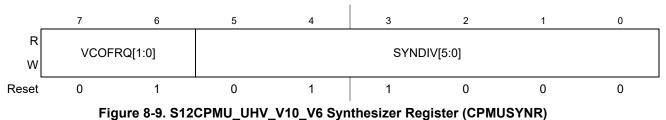

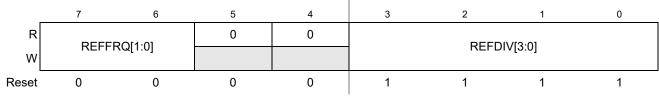

|     | 8.4.1      | Phase Locked Loop with Internal Filter (PLL)                      | 345 |

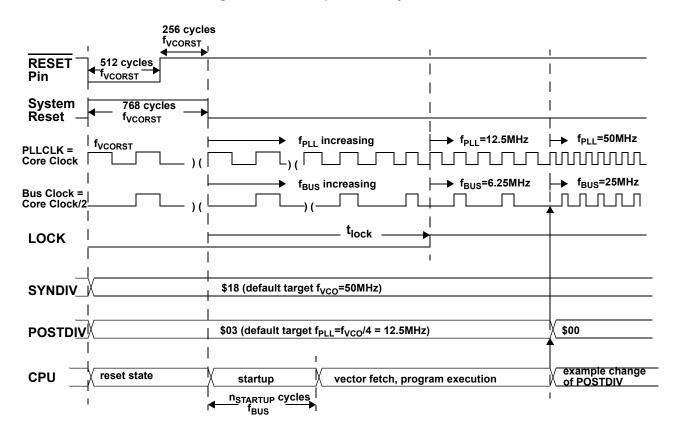

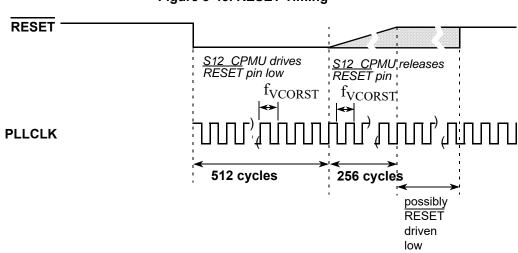

|     | 8.4.2      | Startup from Reset                                                | 347 |

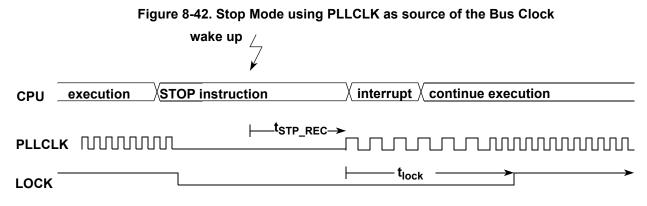

|     | 8.4.3      | Stop Mode using PLLCLK as source of the Bus Clock                 | 348 |

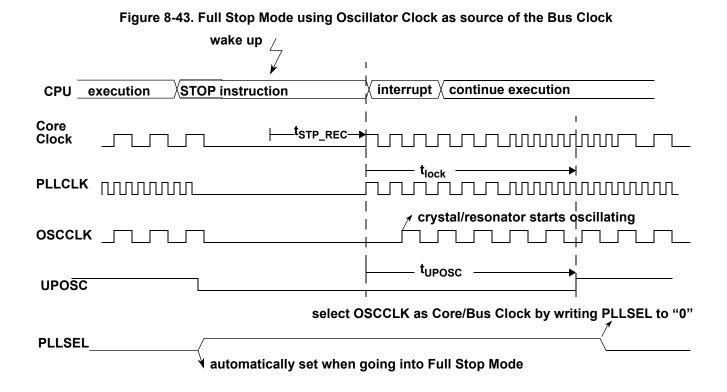

|     | 8.4.4      | Full Stop Mode using Oscillator Clock as source of the Bus Clock  | 348 |

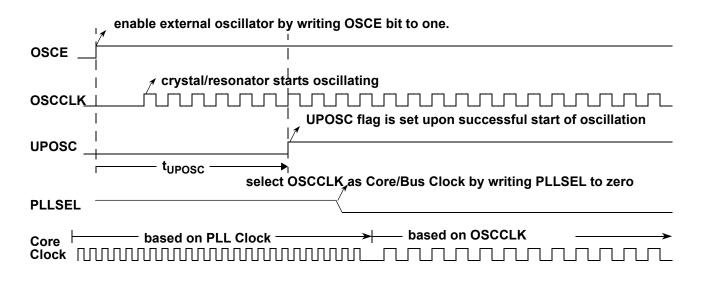

|     | 8.4.5      | External Oscillator                                               | 350 |

|     | 8.4.6      | System Clock Configurations                                       | 351 |

| 8.5 | Resets .   |                                                                   | 352 |

|     | 8.5.1      | General                                                           | 352 |

|     | 8.5.2      | Description of Reset Operation                                    |     |

|     | 8.5.3      | Oscillator Clock Monitor Reset                                    | 353 |

|     | 8.5.4      | PLL Clock Monitor Reset                                           |     |

|     | 8.5.5      | Computer Operating Properly Watchdog (COP) Reset                  | 354 |

|     | 8.5.6      | Power-On Reset (POR)                                              | 355 |

|     | 8.5.7      | Low-Voltage Reset (LVR)                                           | 355 |

| 8.6 | Interrup   |                                                                   | 356 |

|     | 8.6.1      | Description of Interrupt Operation                                | 356 |

| 8.7 | Initializa | ation/Application Information                                     | 358 |

|     | 8.7.1      | General Initialization Information                                |     |

|     | 8.7.2      | Application information for COP and API usage                     | 358 |

|     | 8.7.3      | Application Information for PLL and Oscillator Startup            | 359 |

|     |            |                                                                   |     |

## Chapter 9 Analog-to-Digital Converter (ADC12B\_LBA)

| 9.1 | Differences ADC12B | LBA V1 vs V | /2 vs V3 | <br>361 |

|-----|--------------------|-------------|----------|---------|

|     |                    |             |          |         |

#### MC9S12ZVM Family Reference Manual Rev. 2.13

| 9.2 | Introduc | tion                                                                      |

|-----|----------|---------------------------------------------------------------------------|

| 9.3 | Key Fea  | tures                                                                     |

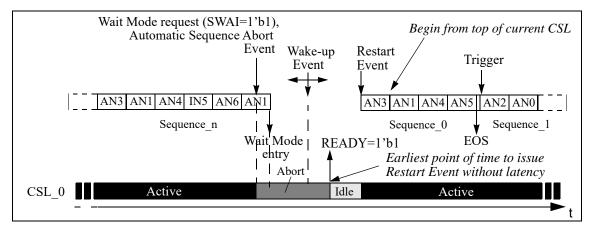

|     | 9.3.1    | Modes of Operation                                                        |

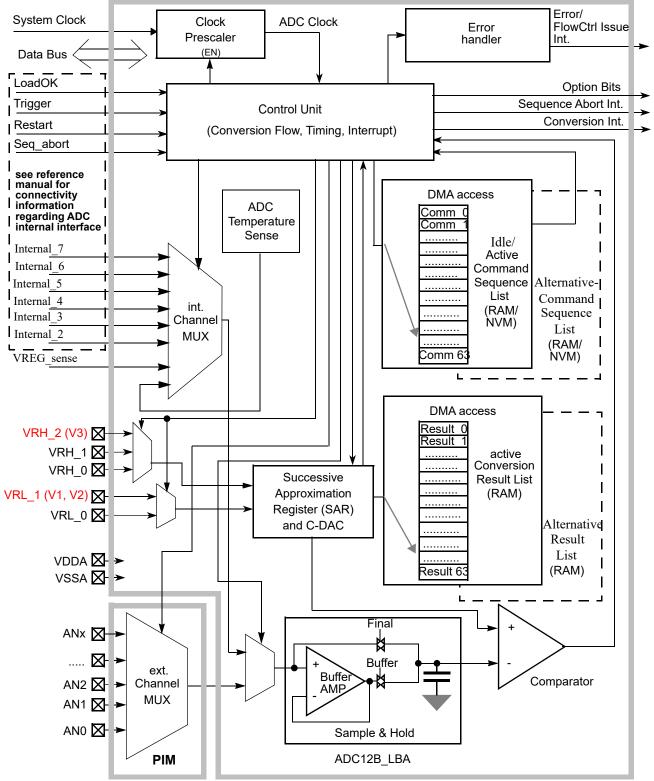

|     | 9.3.2    | Block Diagram                                                             |

| 9.4 | Signal D | Description                                                               |

|     | 9.4.1    | Detailed Signal Descriptions                                              |

| 9.5 | Memory   | Map and Register Definition                                               |

|     | 9.5.1    | Module Memory Map                                                         |

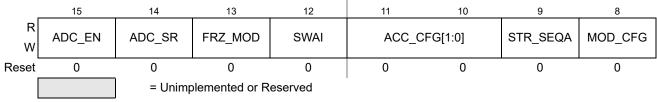

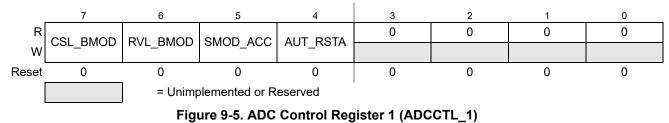

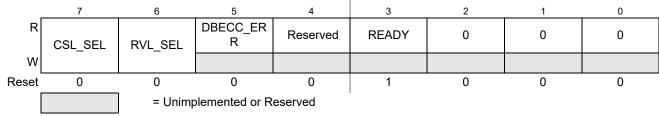

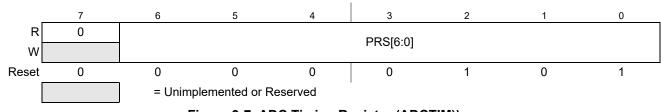

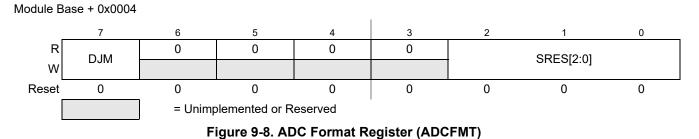

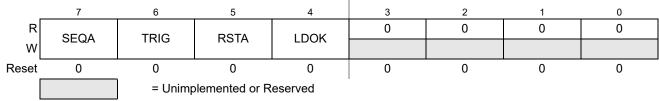

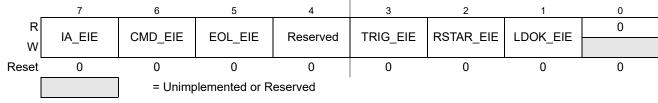

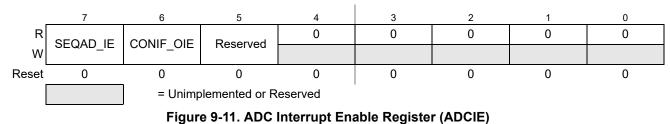

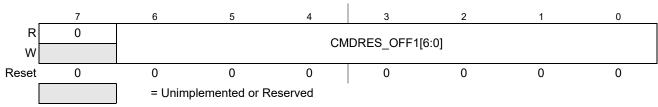

|     | 9.5.2    | Register Descriptions                                                     |

| 9.6 | Function | nal Description                                                           |

|     | 9.6.1    | Overview                                                                  |

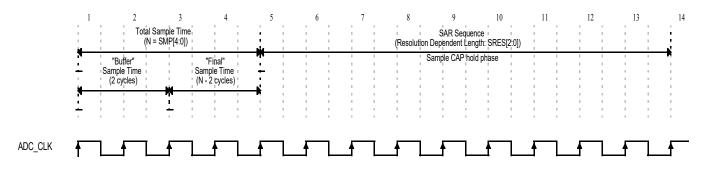

|     | 9.6.2    | Analog Sub-Block                                                          |

|     | 9.6.3    | Digital Sub-Block                                                         |

| 9.7 | Resets . |                                                                           |

| 9.8 | Interrup | ts                                                                        |

|     | 9.8.1    | ADC Conversion Interrupt                                                  |

|     | 9.8.2    | ADC Sequence Abort Done Interrupt                                         |

|     | 9.8.3    | ADC Error and Conversion Flow Control Issue Interrupt                     |

| 9.9 | Use Cas  | es and Application Information                                            |

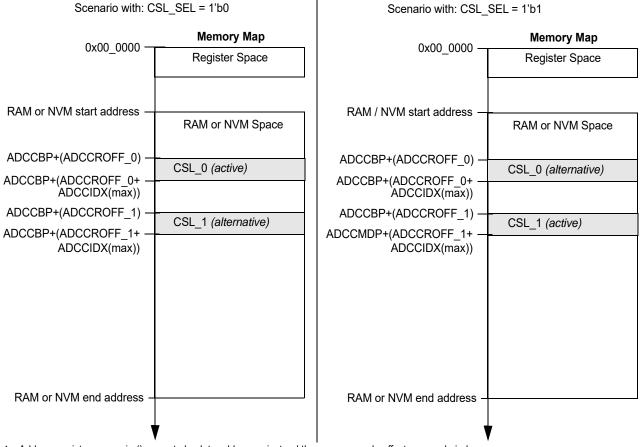

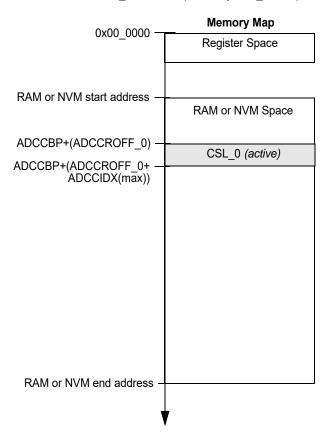

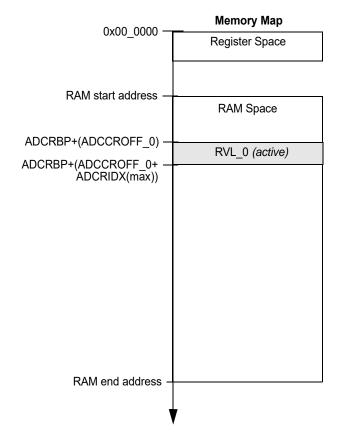

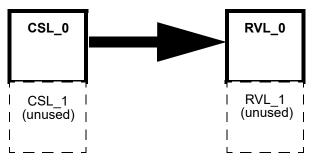

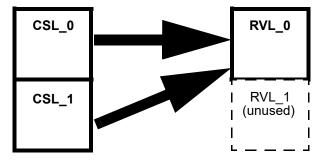

|     | 9.9.1    | List Usage — CSL single buffer mode and RVL single buffer mode            |

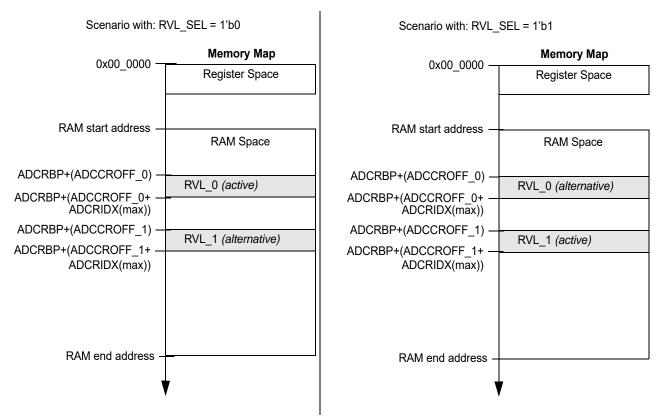

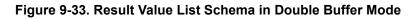

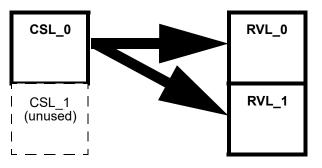

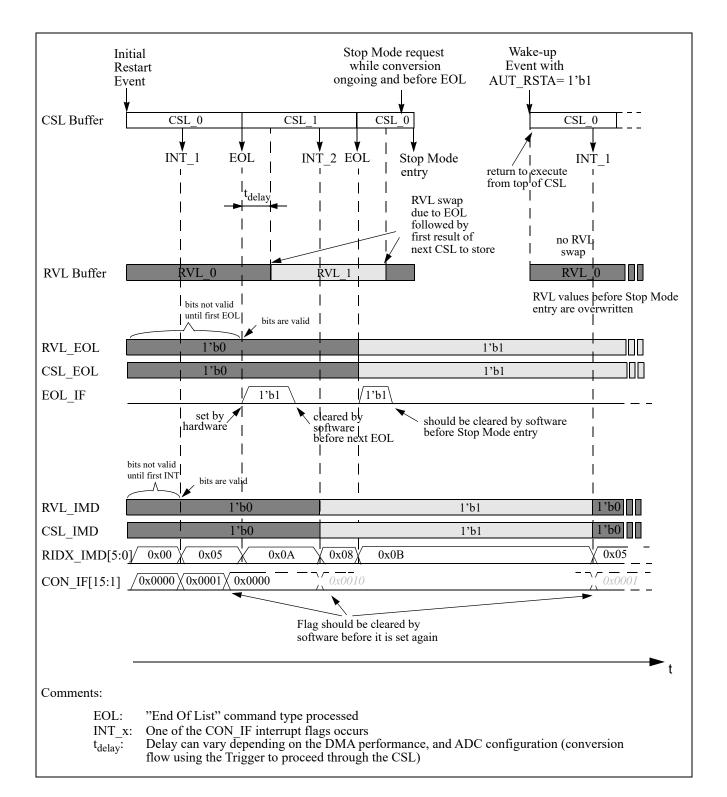

|     | 9.9.2    | List Usage — CSL single buffer mode and RVL double buffer mode            |

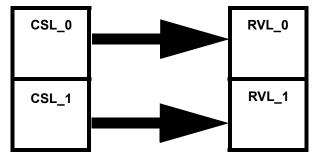

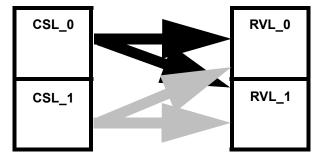

|     | 9.9.3    | List Usage — CSL double buffer mode and RVL double buffer mode            |

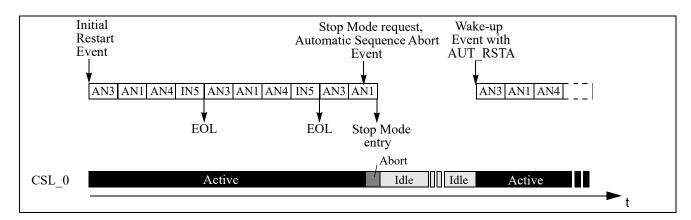

|     | 9.9.4    | List Usage — CSL double buffer mode and RVL single buffer mode            |

|     | 9.9.5    | List Usage — CSL double buffer mode and RVL double buffer mode            |

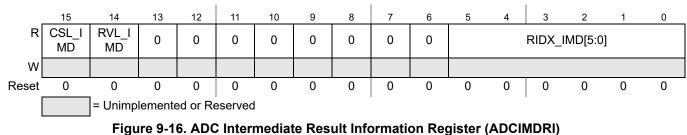

|     | 9.9.6    | RVL swapping in RVL double buffer mode and related registers ADCIMDRI and |

|     |          | ADCEOLRI 424                                                              |

|     | 9.9.7    | Conversion flow control application information                           |

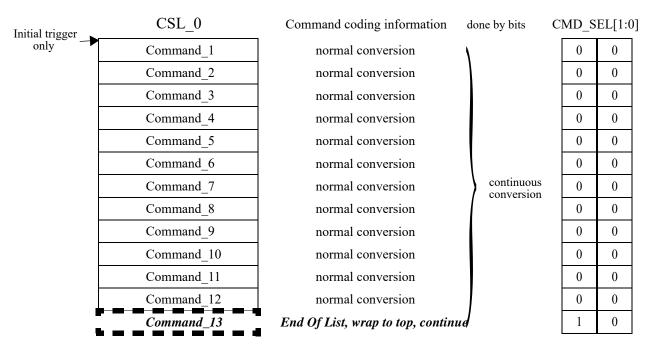

|     | 9.9.8    | Continuous Conversion                                                     |

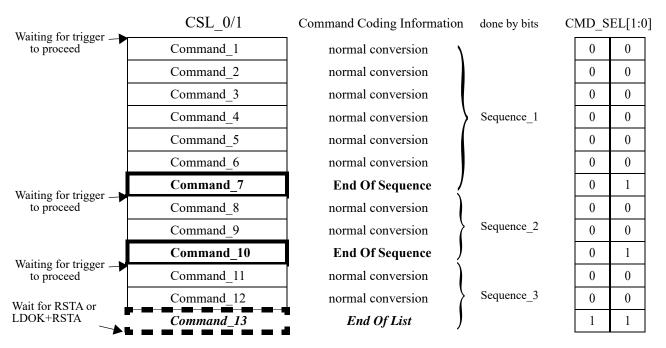

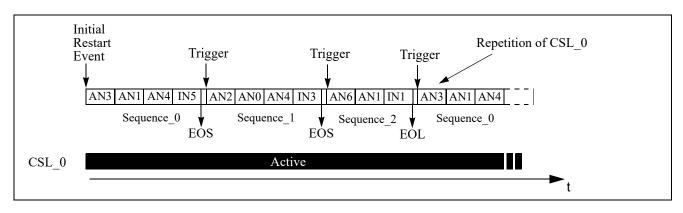

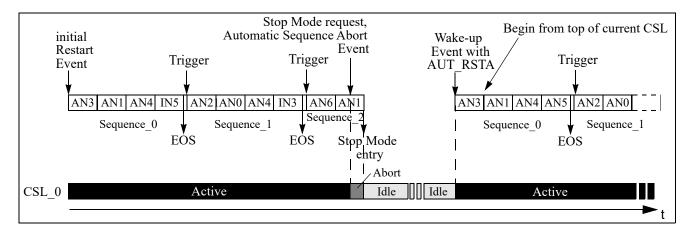

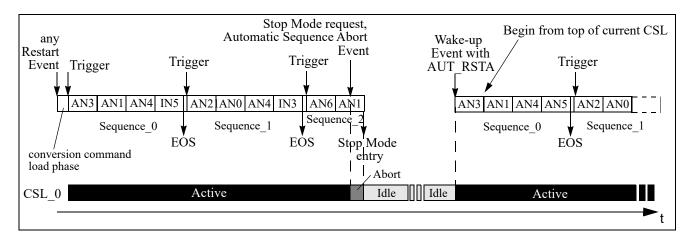

|     | 9.9.9    | Triggered Conversion — Single CSL                                         |

|     | 9.9.10   | Fully Timing Controlled Conversion                                        |

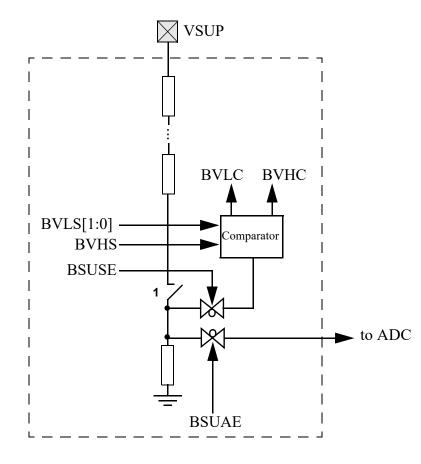

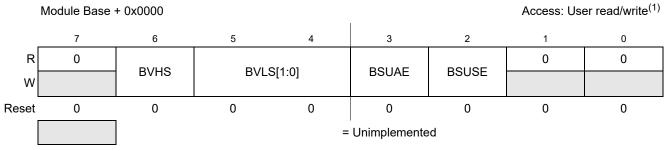

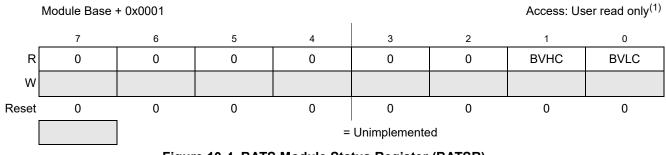

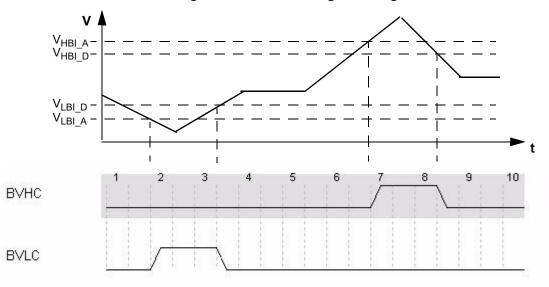

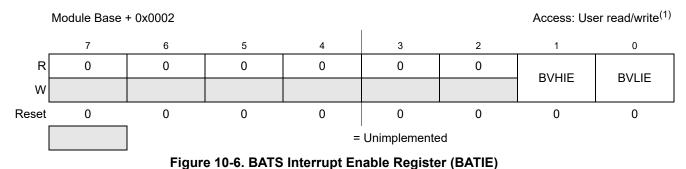

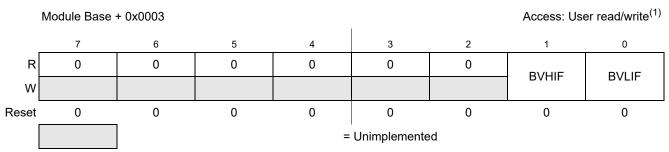

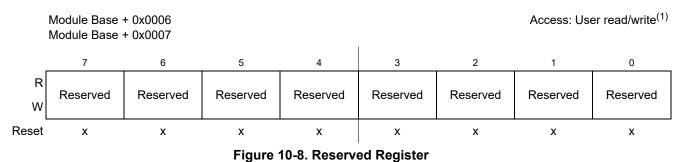

# Chapter 10 Supply Voltage Sensor - (BATSV3)

| 10.1 | Introduction                       |

|------|------------------------------------|

|      | 10.1.1 Features                    |

|      | 10.1.2 Modes of Operation          |

|      | 10.1.3 Block Diagram               |

| 10.2 | External Signal Description        |

|      | 10.2.1 VSUP — Voltage Supply Pin   |

| 10.3 | Memory Map and Register Definition |

|      | 10.3.1 Register Summary            |

|      | 10.3.2 Register Descriptions       |

| 10.4 | Functional Description             |

|      | 10.4.1 General                     |

|      | 10.4.2 Interrupts                  |

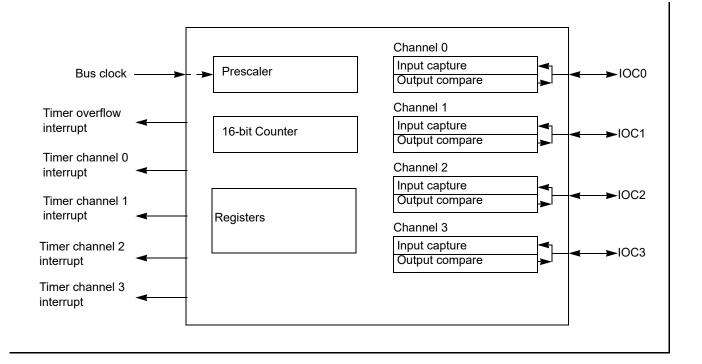

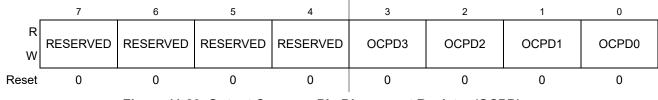

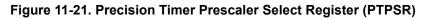

### Chapter 11 Timer Module (TIM16B4CV3) Block Description

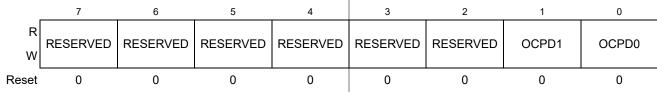

| 11.1 | Introduction                                                      | 441 |

|------|-------------------------------------------------------------------|-----|

|      | 11.1.1 Features                                                   | 441 |

|      | 11.1.2 Modes of Operation                                         | 441 |

|      | 11.1.3 Block Diagrams                                             | 442 |

| 11.2 | External Signal Description                                       |     |

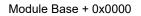

|      | 11.2.1 IOC3 - IOC0 — Input Capture and Output Compare Channel 3-0 | 443 |

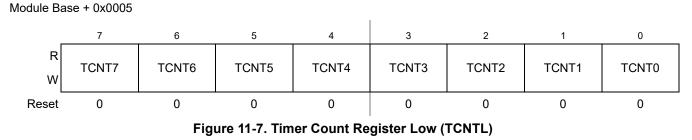

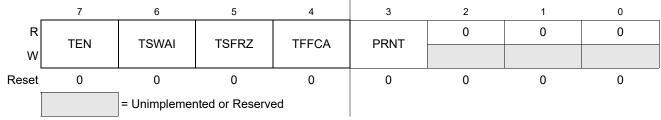

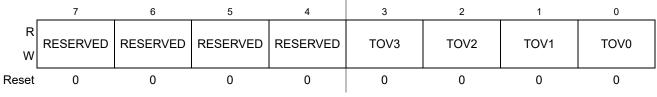

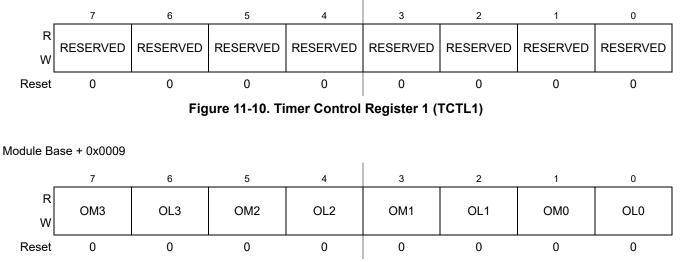

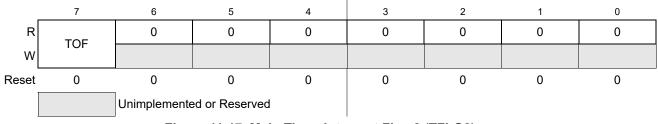

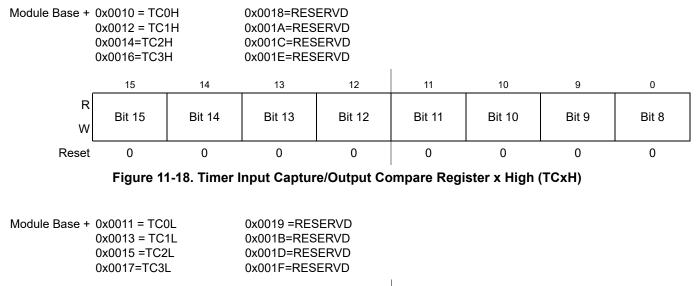

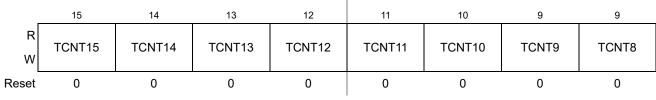

| 11.3 | Memory Map and Register Definition                                | 443 |

|      | 11.3.1 Module Memory Map                                          | 443 |

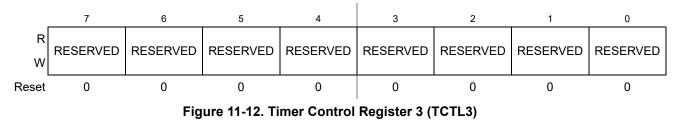

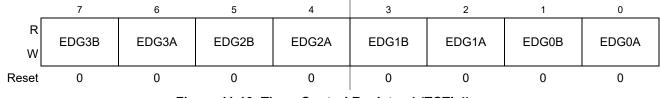

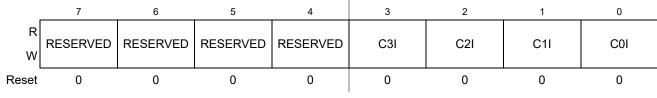

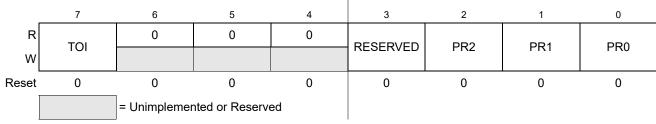

|      | 11.3.2 Register Descriptions                                      | 443 |

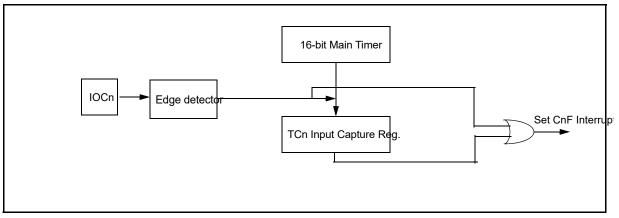

| 11.4 | Functional Description                                            | 455 |

|      | 11.4.1 Prescaler                                                  | 456 |

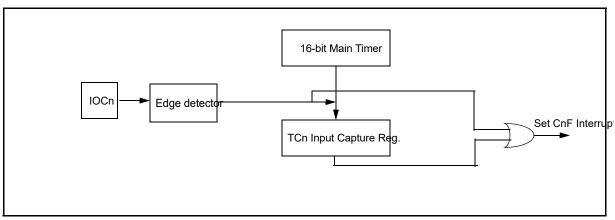

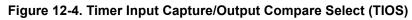

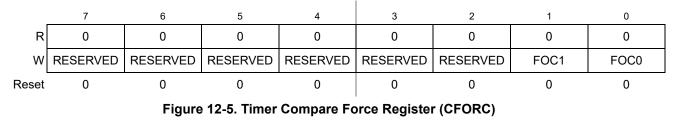

|      | 11.4.2 Input Capture                                              | 457 |

|      | 11.4.3 Output Compare                                             |     |

| 11.5 |                                                                   |     |

| 11.6 | Interrupts                                                        | 458 |

|      | 11.6.1 Channel [3:0] Interrupt (C[3:0]F)                          | 458 |

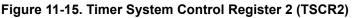

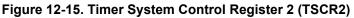

|      | 11.6.2 Timer Overflow Interrupt (TOF)                             | 458 |

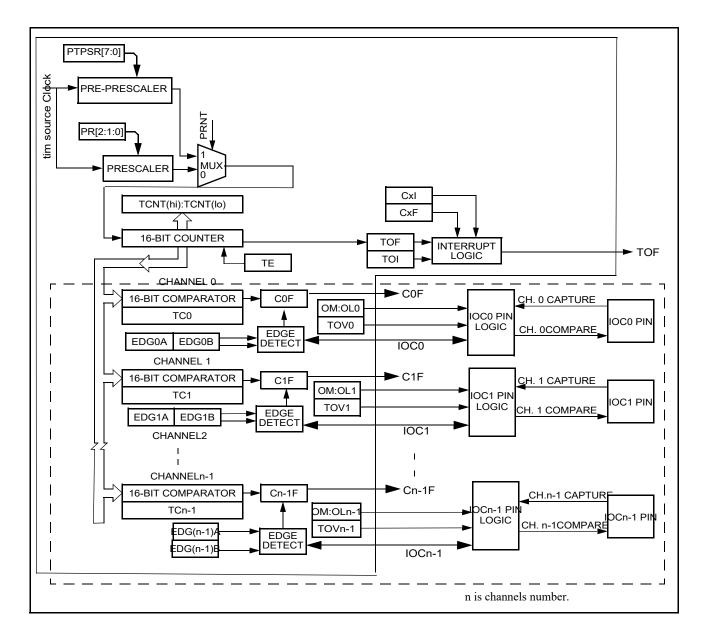

### Chapter 12 Timer Module (TIM16B2CV3) Block Description

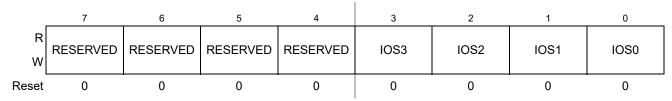

| 12.1 | Introduction                                                      | 459 |

|------|-------------------------------------------------------------------|-----|

|      | 12.1.1 Features                                                   | 459 |

|      | 12.1.2 Modes of Operation                                         | 459 |

|      | 12.1.3 Block Diagrams                                             |     |

| 12.2 | External Signal Description                                       |     |

|      | 12.2.1 IOC1 - IOC0 — Input Capture and Output Compare Channel 1-0 | 461 |

| 12.3 | Memory Map and Register Definition                                |     |

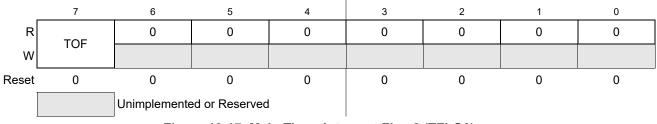

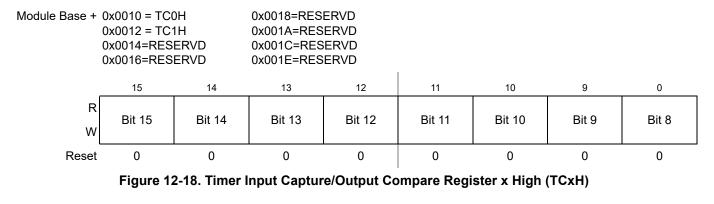

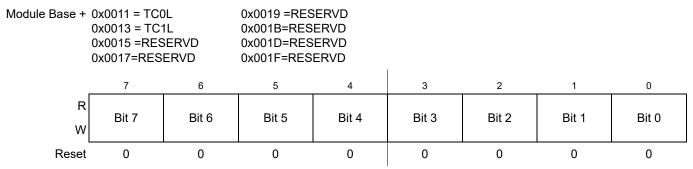

|      | 12.3.1 Module Memory Map                                          | 461 |

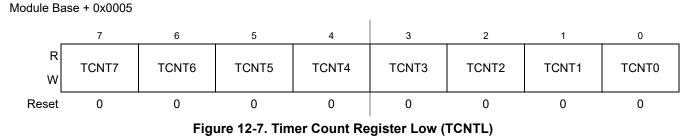

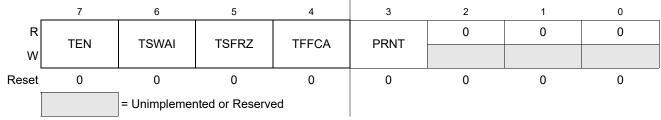

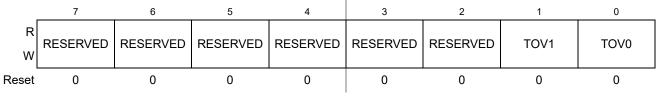

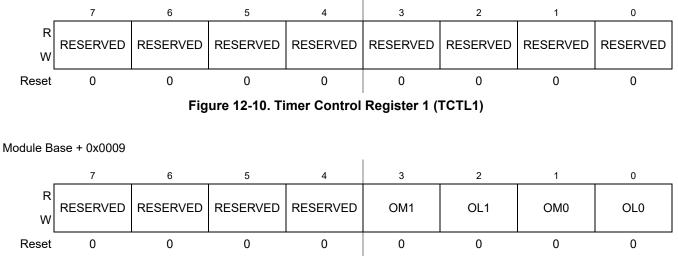

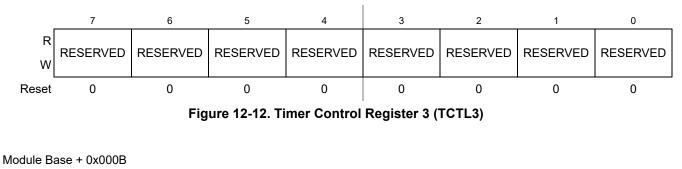

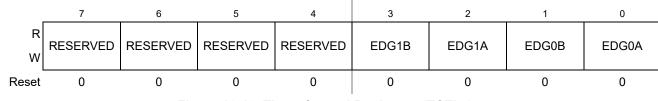

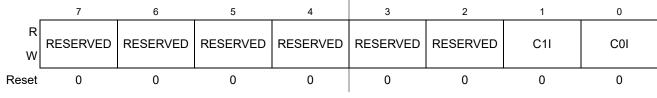

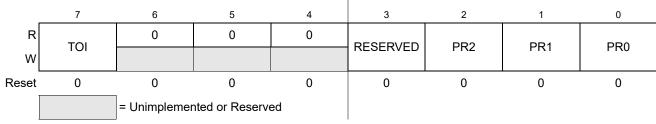

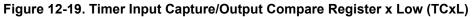

|      | 12.3.2 Register Descriptions                                      | 461 |

| 12.4 | Functional Description                                            |     |

|      | 12.4.1 Prescaler                                                  | 474 |

|      | 12.4.2 Input Capture                                              | 475 |

|      | 12.4.3 Output Compare                                             | 475 |

| 12.5 | Resets                                                            |     |

| 12.6 | Interrupts                                                        |     |

|      | 12.6.1 Channel [1:0] Interrupt (C[1:0]F)                          |     |

|      | 12.6.2 Timer Overflow Interrupt (TOF)                             |     |

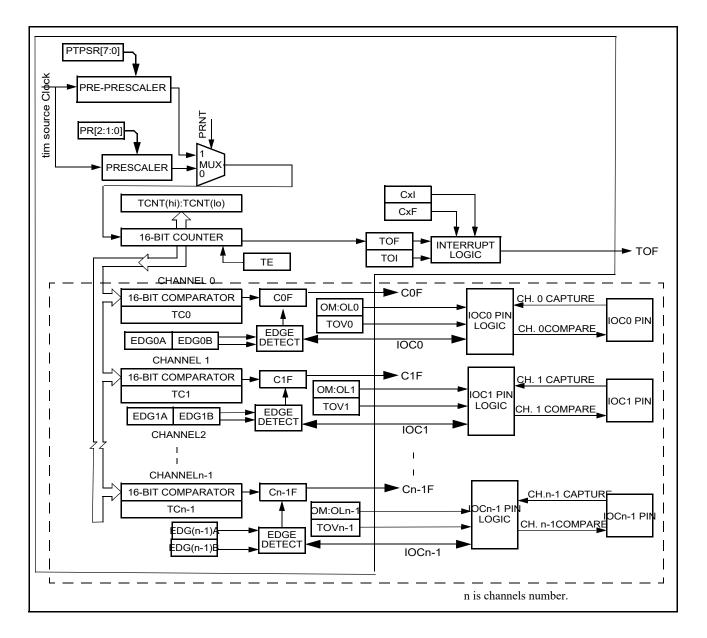

## Chapter 13

## Scalable Controller Area Network (S12MSCANV3)

| 13.1 | Introduction    | 77 |

|------|-----------------|----|

|      | 13.1.1 Glossary | 78 |

#### MC9S12ZVM Family Reference Manual Rev. 2.13

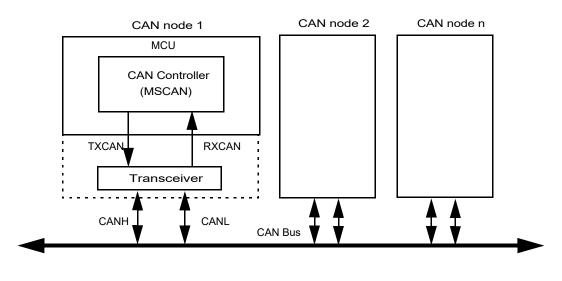

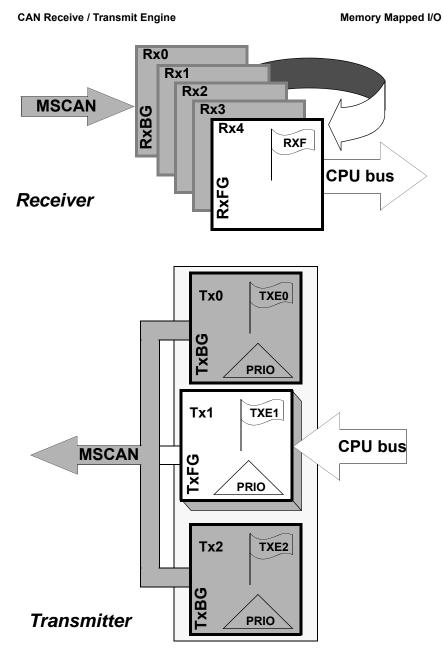

|      | 13.1.2   | Block Diagram                         |

|------|----------|---------------------------------------|

|      | 13.1.3   | Features                              |

|      | 13.1.4   | Modes of Operation                    |

| 13.2 | External | Signal Description                    |

|      |          | RXCAN — CAN Receiver Input Pin        |

|      |          | TXCAN — CAN Transmitter Output Pin    |

|      |          | CAN System                            |

| 13.3 | Memory   | Map and Register Definition           |

|      |          | Module Memory Map    481              |

|      |          | Register Descriptions                 |

|      | 13.3.3   | Programmer's Model of Message Storage |

| 13.4 |          | nal Description                       |

|      | 13.4.1   | General                               |

|      | 13.4.2   | Message Storage                       |

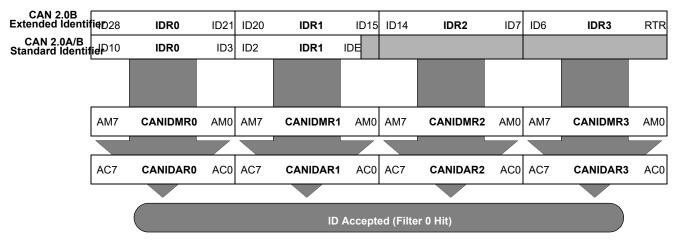

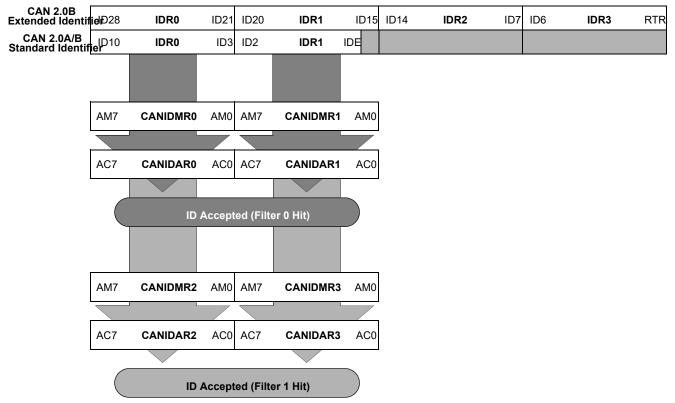

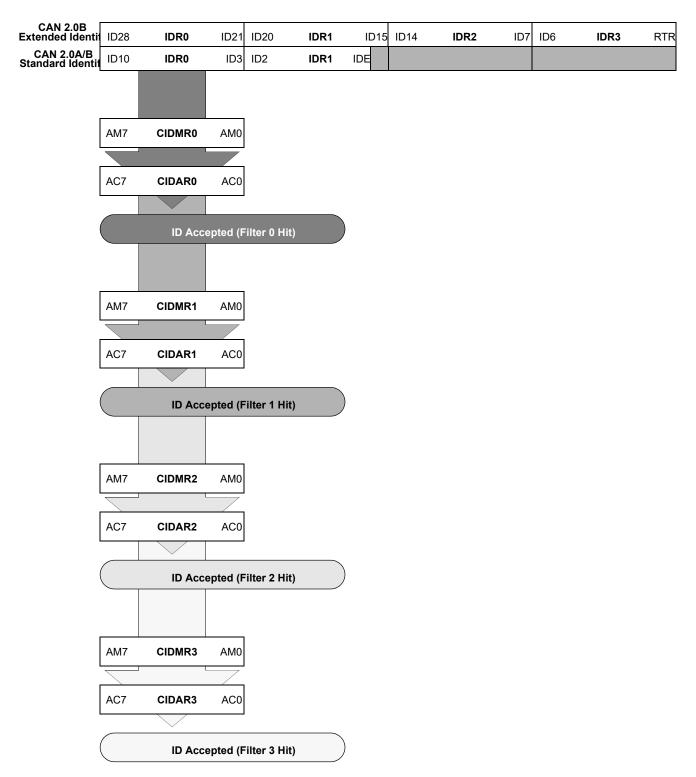

|      | 13.4.3   | Identifier Acceptance Filter          |

|      | 13.4.4   | Modes of Operation                    |

|      | 13.4.5   | Low-Power Options                     |

|      | 13.4.6   | Reset Initialization                  |

|      | 13.4.7   | Interrupts                            |

| 13.5 |          | ation/Application Information         |

|      | 13.5.1   | MSCAN initialization                  |

|      | 13.5.2   | Bus-Off Recovery                      |

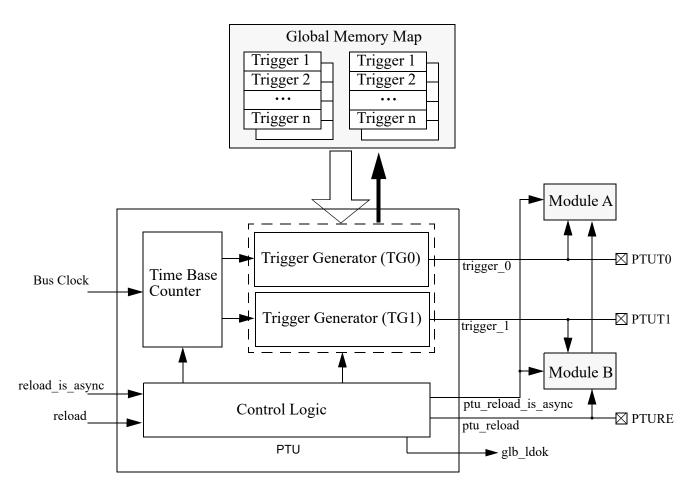

# Chapter 14 Programmable Trigger Unit (PTUV3)

| 14.1 | Introduc | tion                            |

|------|----------|---------------------------------|

|      | 14.1.1   | Features                        |

|      | 14.1.2   | Modes of Operation              |

|      | 14.1.3   | Block Diagram                   |

| 14.2 | External | Signal Description              |

|      | 14.2.1   | PTUT0 — PTU Trigger 0           |

|      | 14.2.2   | PTUT1 — PTU Trigger 1           |

|      | 14.2.3   | PTURE — PTUE Reload Event       |

| 14.3 | Memory   | Map and Register Definition     |

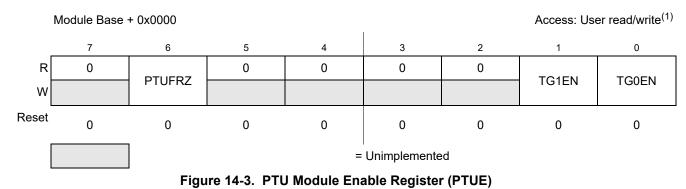

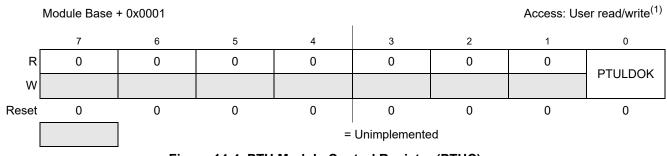

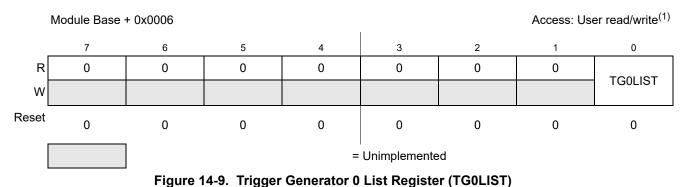

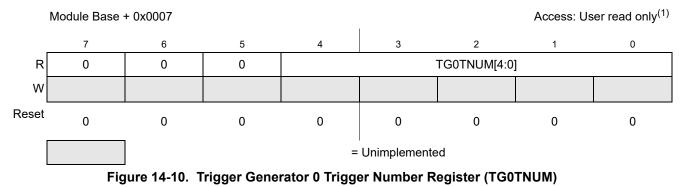

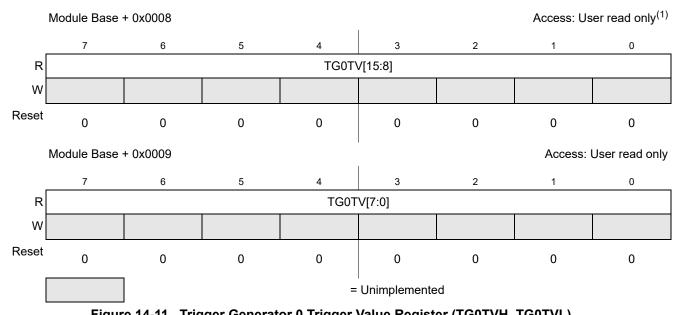

|      | 14.3.1   | Register Summary                |

|      | 14.3.2   | Register Descriptions           |

| 14.4 | Function | al Description                  |

|      | 14.4.1   | General                         |

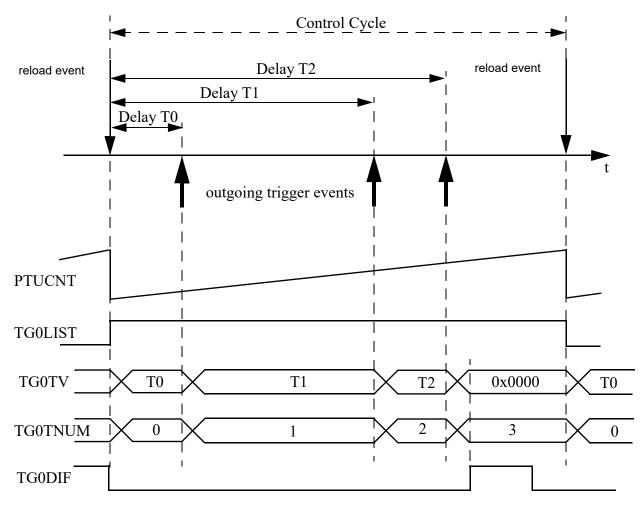

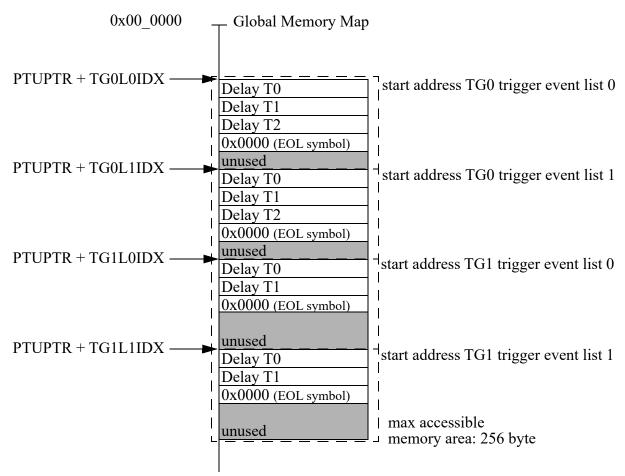

|      | 14.4.2   | Memory based trigger event list |

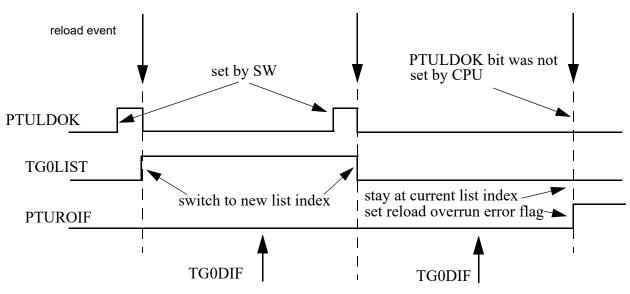

|      | 14.4.3   | Reload mechanism                |

|      | 14.4.4   | Async reload event              |

|      | 14.4.5   | Interrupts and error handling   |

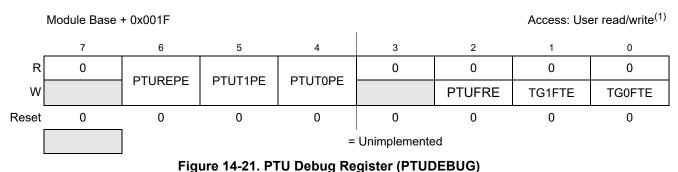

|      | 14.4.6   | Debugging                       |

|      |          |                                 |

|      | Pulse Width Modulator with Fault Protection (PMF15B6C00.17)             |     |

|------|-------------------------------------------------------------------------|-----|

| 15.1 | Introduction                                                            | 560 |

|      | 15.1.1 Features                                                         | 561 |

|      | 15.1.2 Modes of Operation                                               | 561 |

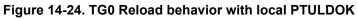

|      | 15.1.3 Block Diagram                                                    | 563 |

| 15.2 | Signal Descriptions                                                     | 564 |

|      | 15.2.1 PWM0–PWM5 Pins                                                   |     |

|      | 15.2.2 FAULT0–FAULT5 Pins                                               |     |

|      | 15.2.3 ISO–IS2 Pins                                                     |     |

|      | 15.2.4 Global Load OK Signal — glb_ldok                                 |     |

|      | 15.2.5 Commutation Event Signal — async_event                           |     |

|      | 15.2.6 Commutation Event Edge Select Signal — async_event_edge_sel[1:0] |     |

|      | 15.2.7 PWM Reload Event Signals — pmf_reloada,b,c                       |     |

|      | 15.2.8 PWM Reload-Is-Asynchronous Signal — pmf_reload_is_async          |     |

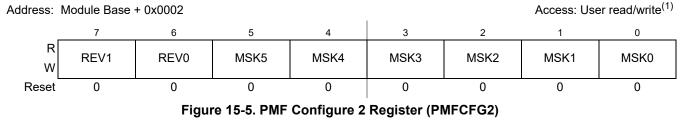

| 15.3 | Memory Map and Registers                                                |     |

|      | 15.3.1 Module Memory Map                                                |     |

|      | 15.3.2 Register Descriptions                                            |     |

| 15.4 | Functional Description                                                  |     |

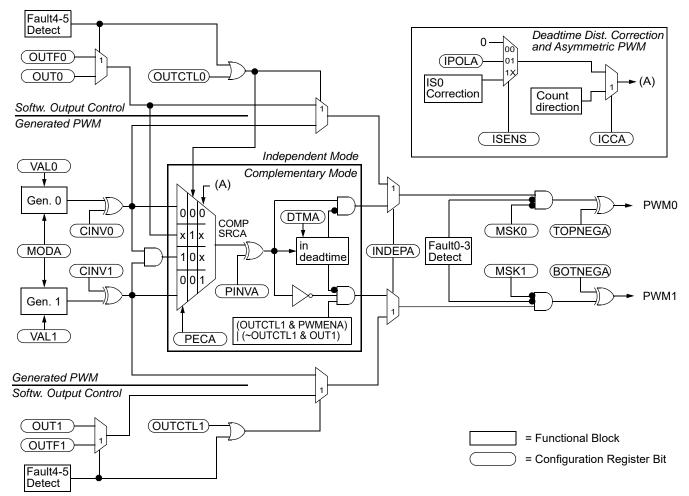

|      | 15.4.1 Block Diagram                                                    |     |

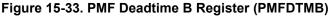

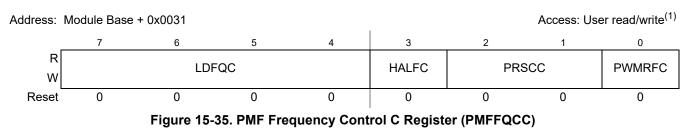

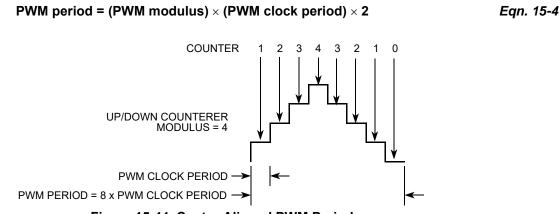

|      | 15.4.2 Prescaler                                                        |     |

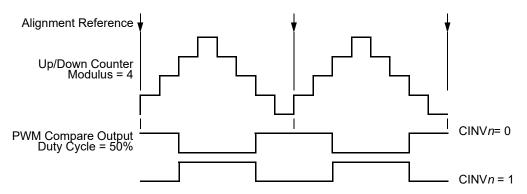

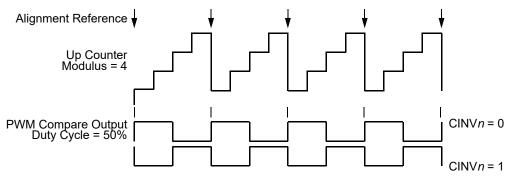

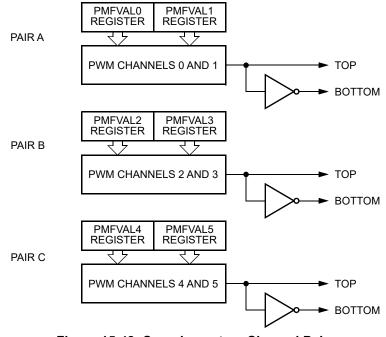

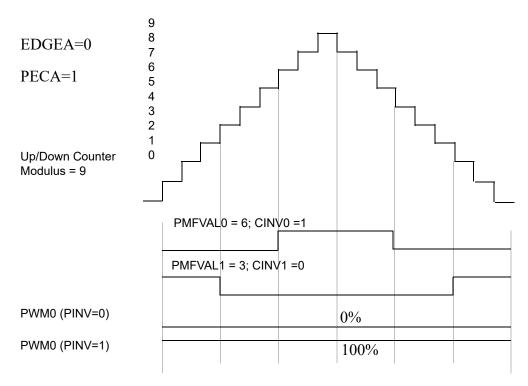

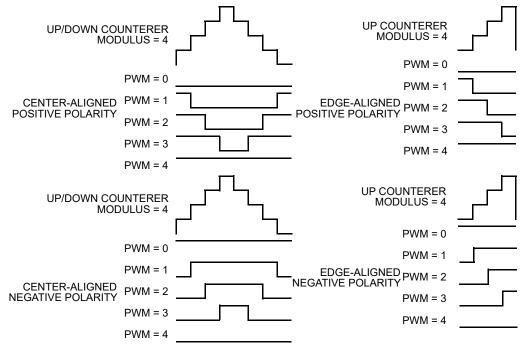

|      | 15.4.3 PWM Generator                                                    |     |

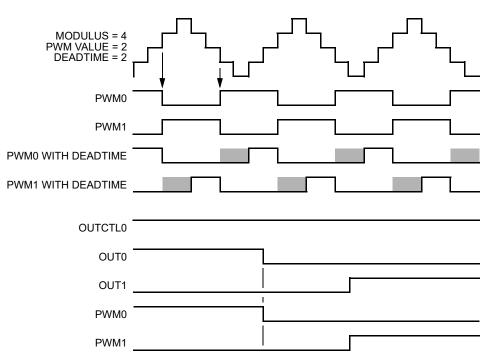

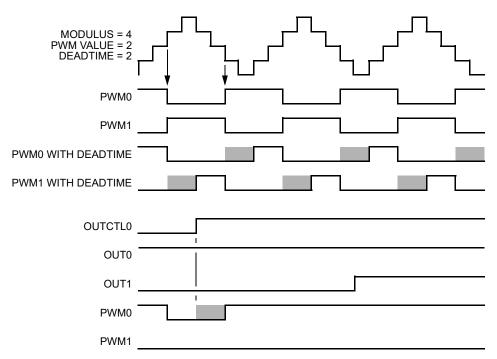

|      | 15.4.4 Independent or Complementary Channel Operation                   |     |

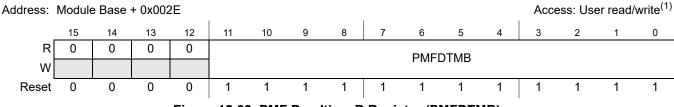

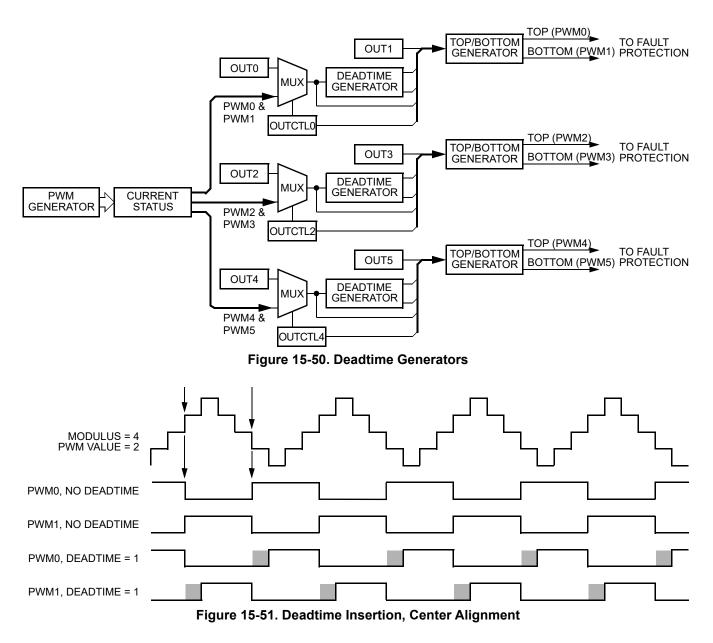

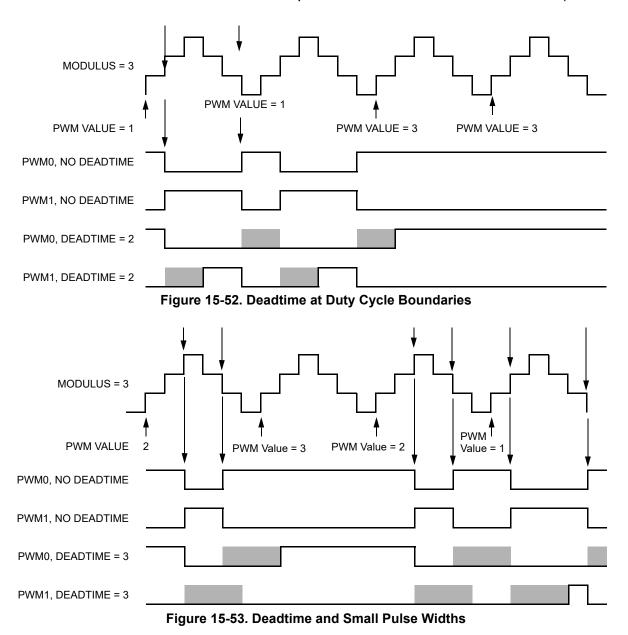

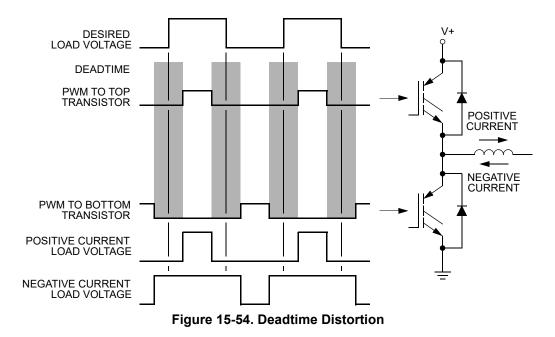

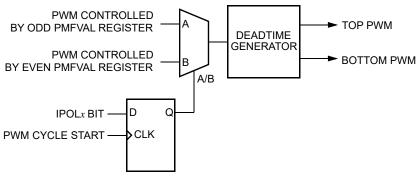

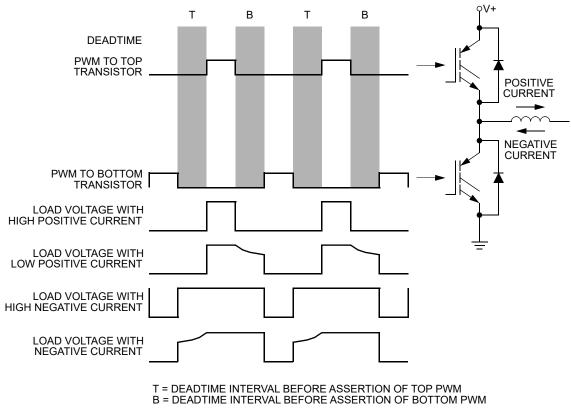

|      | 15.4.5 Deadtime Generators                                              |     |

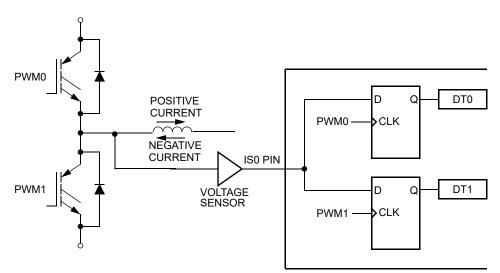

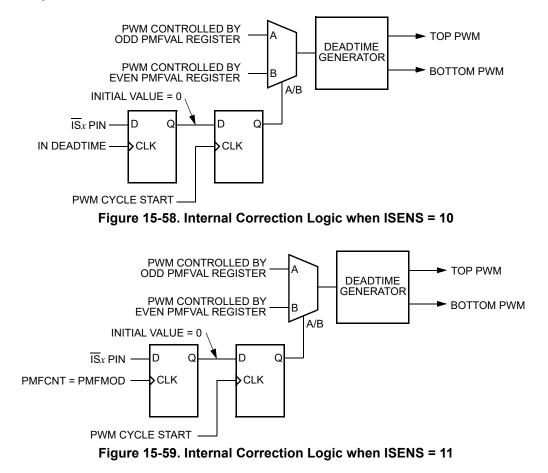

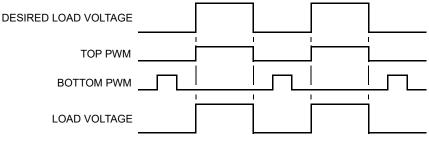

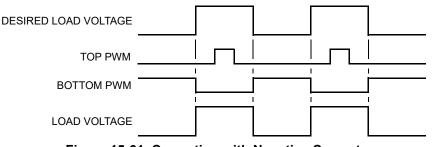

|      | 15.4.6 Top/Bottom Correction                                            |     |

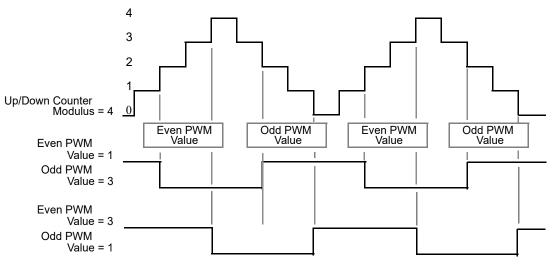

|      | 15.4.7 Asymmetric PWM Output                                            |     |

|      | 15.4.8 Variable Edge Placement PWM Output                               |     |

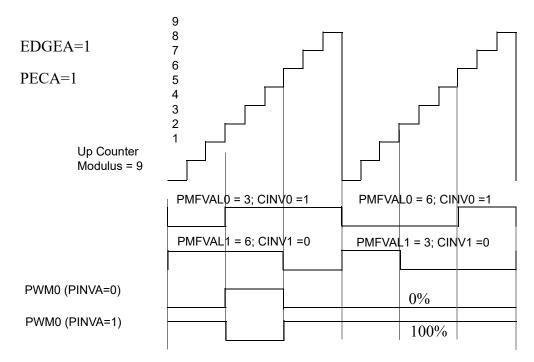

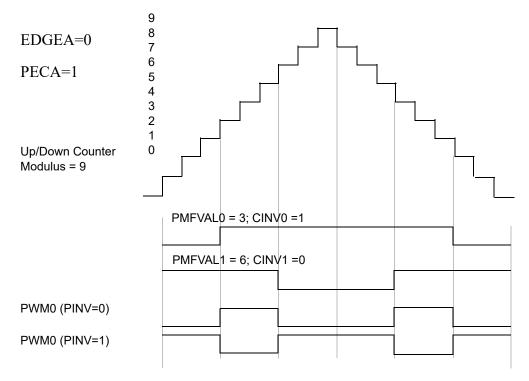

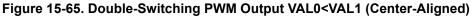

|      | 15.4.9 Double Switching PWM Output                                      |     |

|      | 15.4.10Output Polarity                                                  |     |

|      | 15.4.11Software Output Control                                          |     |

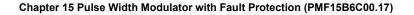

|      | 15.4.12PWM Generator Loading                                            |     |

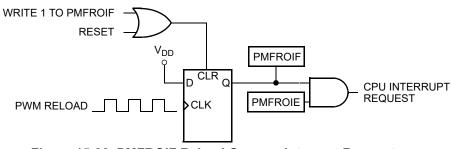

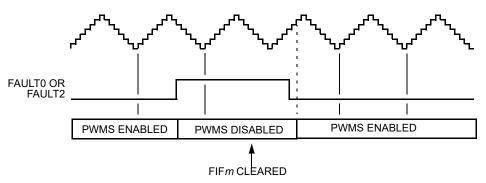

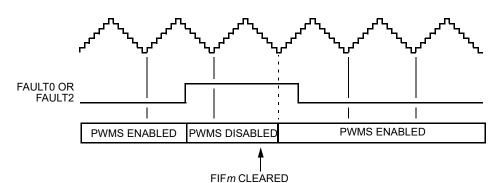

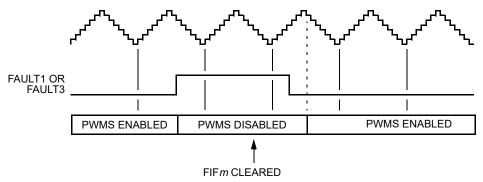

| 155  | 15.4.13Fault Protection                                                 |     |

|      | Resets                                                                  |     |

|      | Clocks                                                                  |     |

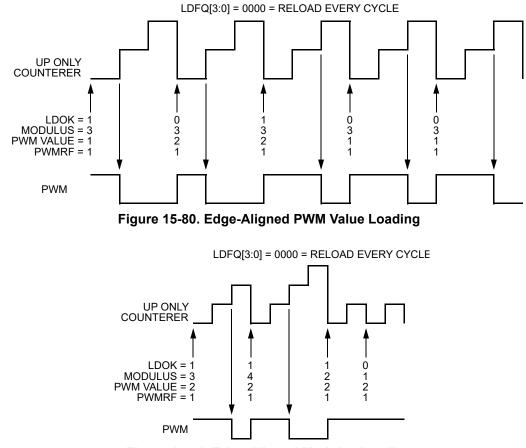

|      | Interrupts                                                              |     |

| 13.8 | Initialization and Application Information                              |     |

|      |                                                                         |     |

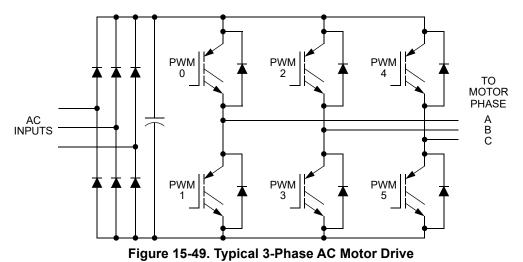

|      | 15.8.2 BLDC 6-Step Commutation                                          | 029 |

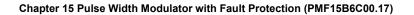

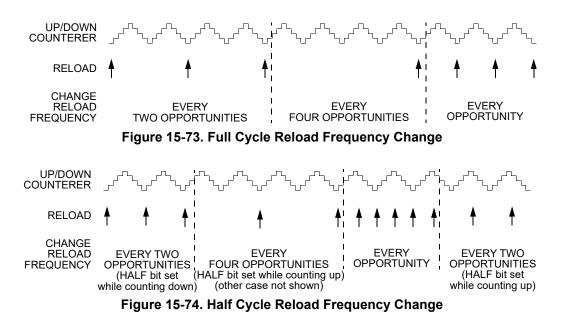

## Chapter 15 Pulse Width Modulator with Fault Protection (PMF15B6C00.17

# Chapter 16

# Serial Communication Interface (S12SCIV6)

| 16.1 | Introduction    | 533 |

|------|-----------------|-----|

|      | 16.1.1 Glossary | 533 |

|      | 16.1.2 Features | 534 |

| MC9S12ZVN | l Family | Reference | Manual | Rev. | 2.13 |

|-----------|----------|-----------|--------|------|------|

|-----------|----------|-----------|--------|------|------|

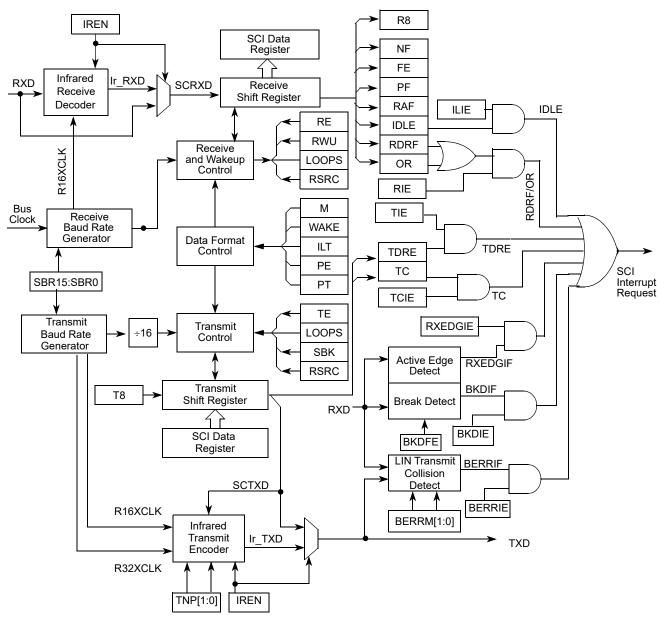

|      | 16.1.3   | Modes of Operation                        | 635 |

|------|----------|-------------------------------------------|-----|

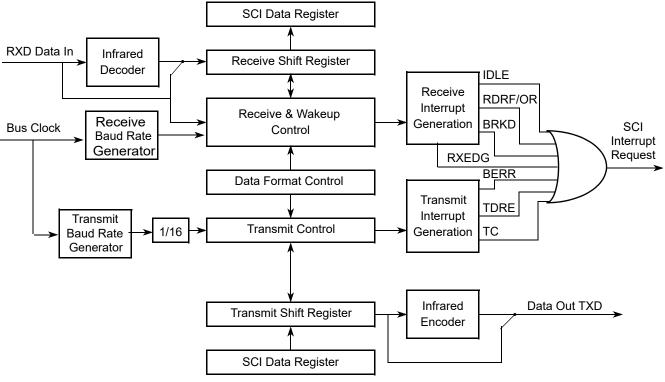

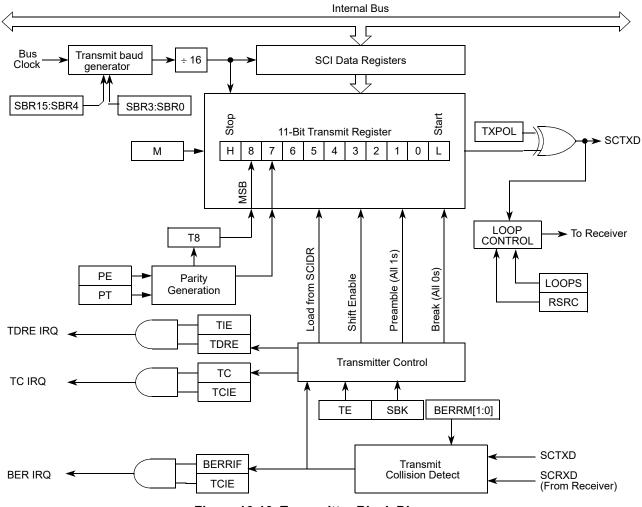

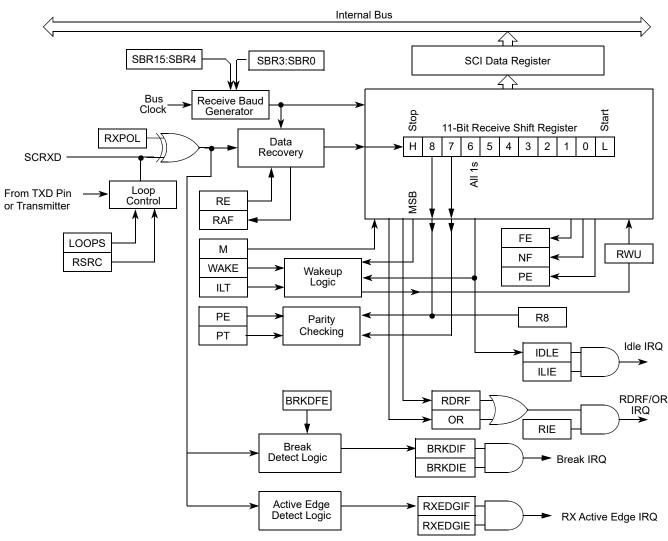

|      | 16.1.4   | Block Diagram                             | 635 |

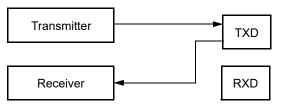

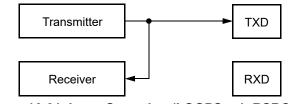

| 16.2 | External | Signal Description                        | 636 |

|      | 16.2.1   | TXD — Transmit Pin                        | 636 |

|      | 16.2.2   | RXD — Receive Pin                         | 636 |

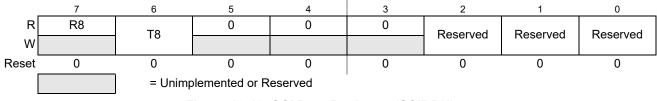

| 16.3 | Memory   | Map and Register Definition               | 636 |

|      | 16.3.1   | Module Memory Map and Register Definition | 636 |

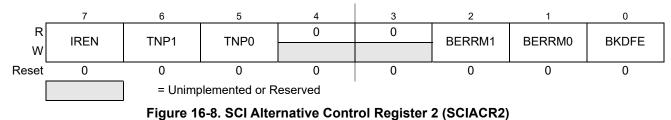

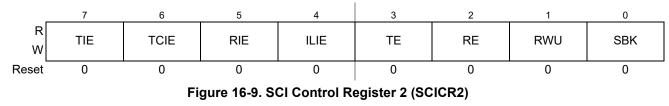

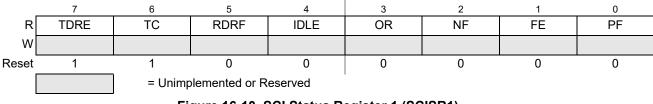

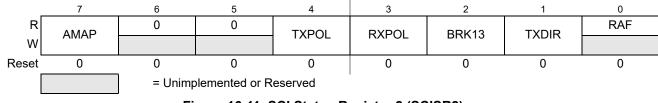

|      | 16.3.2   | Register Descriptions                     | 637 |

| 16.4 | Function | nal Description                           | 650 |

|      | 16.4.1   | Infrared Interface Submodule              | 651 |

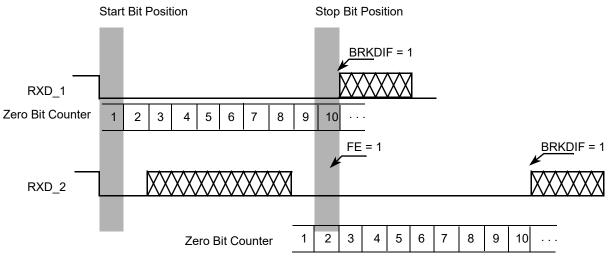

|      | 16.4.2   | LIN Support                               | 651 |

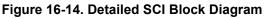

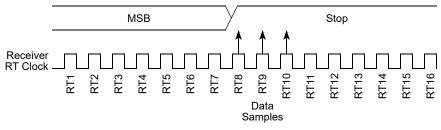

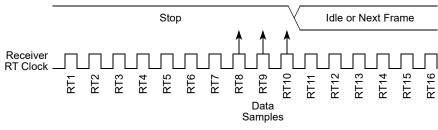

|      | 16.4.3   | Data Format                               | 652 |

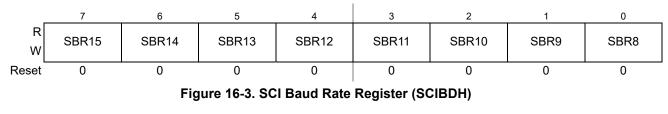

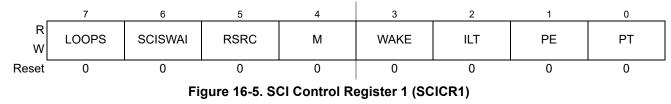

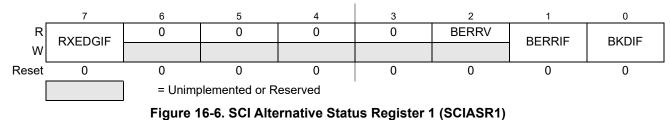

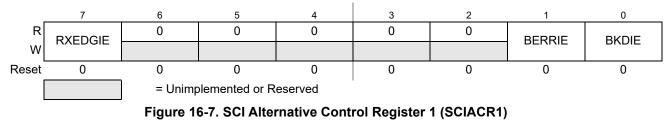

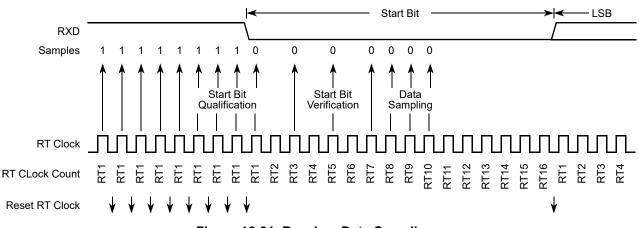

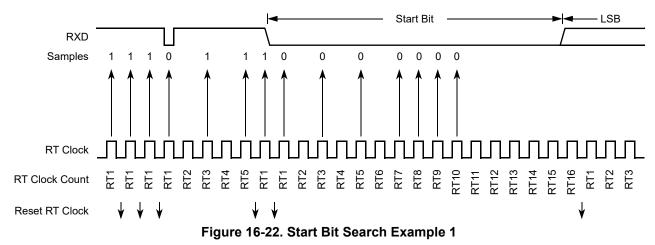

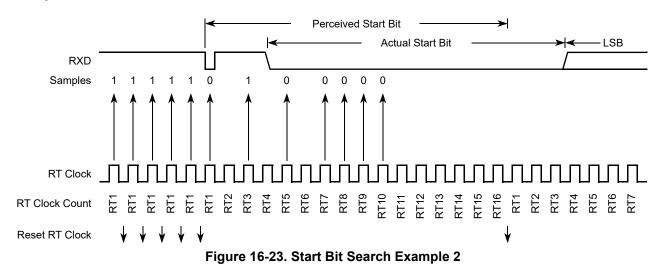

|      | 16.4.4   | Baud Rate Generation                      | 653 |

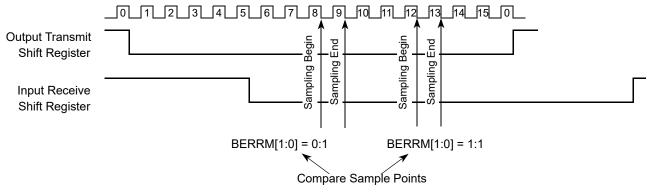

|      | 16.4.5   | Transmitter                               | 654 |

|      |          | Receiver                                  |     |

|      | 16.4.7   | Single-Wire Operation                     | 667 |

|      | 16.4.8   | Loop Operation                            | 668 |

| 16.5 |          | ation/Application Information             |     |

|      | 16.5.1   | Reset Initialization                      | 668 |

|      | 16.5.2   | Modes of Operation                        | 669 |

|      | 16.5.3   | Interrupt Operation                       | 669 |

|      | 16.5.4   | Recovery from Wait Mode                   | 672 |

|      | 16.5.5   | Recovery from Stop Mode                   | 672 |

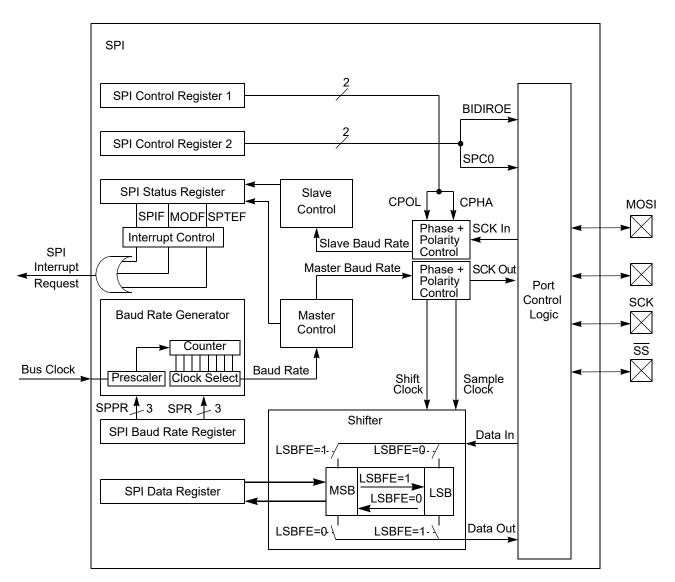

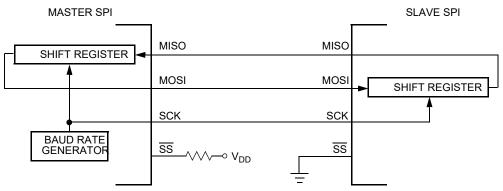

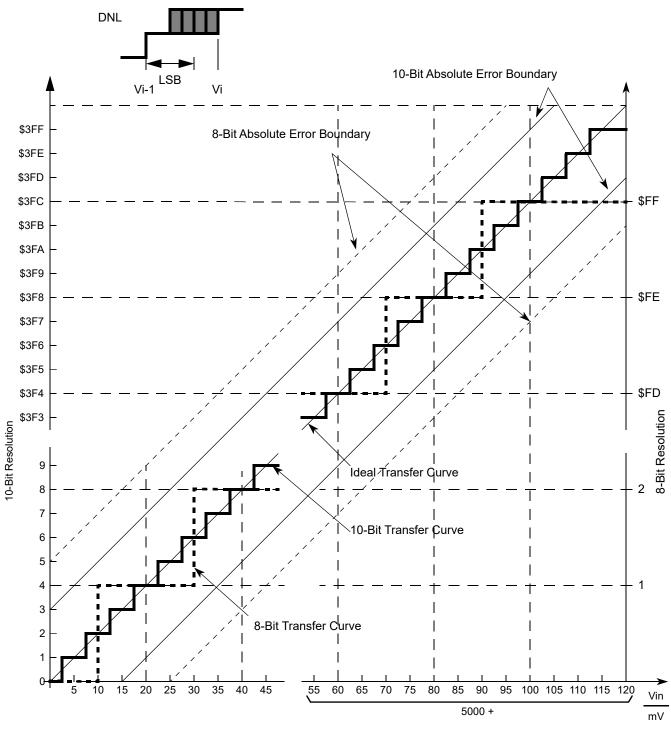

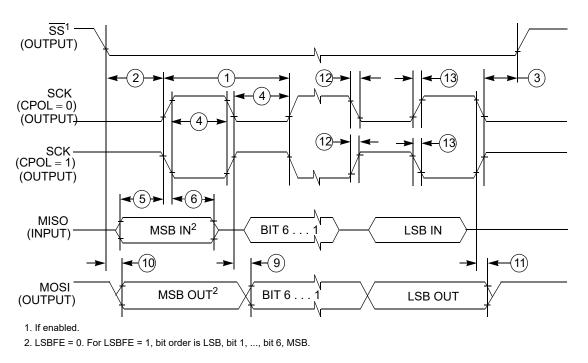

## Chapter 17 Serial Peripheral Interface (S12SPIV5)

| 17.1 | Introduction                              | <br> | 673 |

|------|-------------------------------------------|------|-----|

|      | 17.1.1 Glossary of Terms                  | <br> | 673 |

|      | 17.1.2 Features                           | <br> | 673 |

|      | 17.1.3 Modes of Operation                 | <br> | 673 |

|      | 17.1.4 Block Diagram                      | <br> | 674 |

| 17.2 | External Signal Description               | <br> | 675 |

|      | 17.2.1 MOSI — Master Out/Slave In Pin     | <br> | 675 |

|      | 17.2.2 MISO — Master In/Slave Out Pin     | <br> | 676 |

|      | 17.2.3 $\overline{SS}$ — Slave Select Pin | <br> | 676 |

|      | 17.2.4 SCK — Serial Clock Pin             | <br> | 676 |

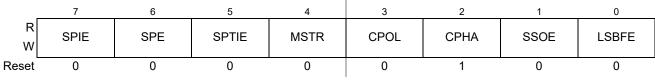

| 17.3 | Memory Map and Register Definition        | <br> | 676 |

|      | 17.3.1 Module Memory Map                  | <br> | 676 |

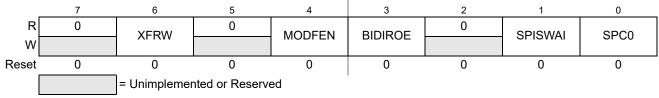

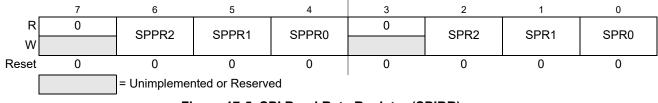

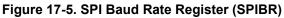

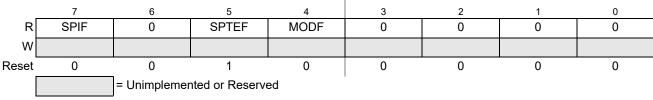

|      | 17.3.2 Register Descriptions              | <br> | 677 |

| 17.4 | Functional Description                    | <br> | 685 |

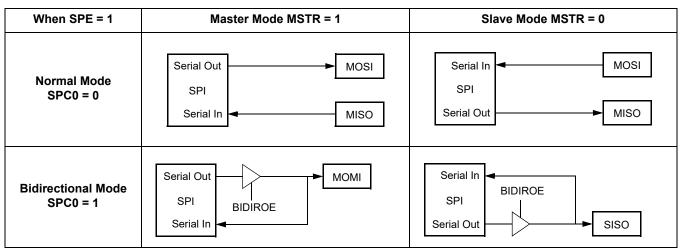

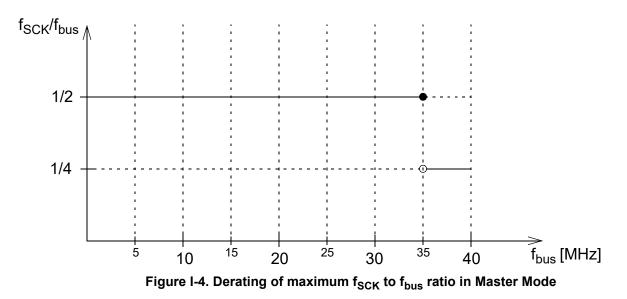

|      | 17.4.1 Master Mode                        | <br> | 686 |

|      | 17.4.2 Slave Mode                         | <br> | 687 |

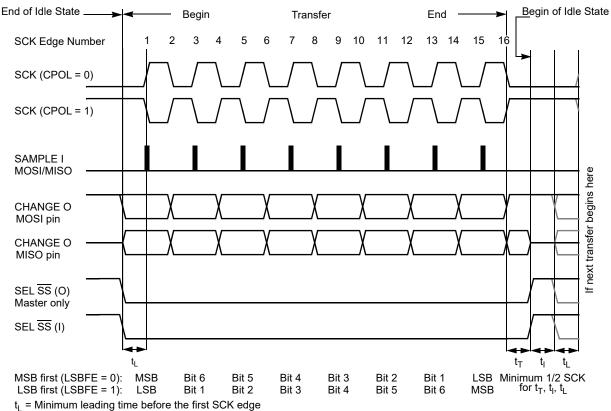

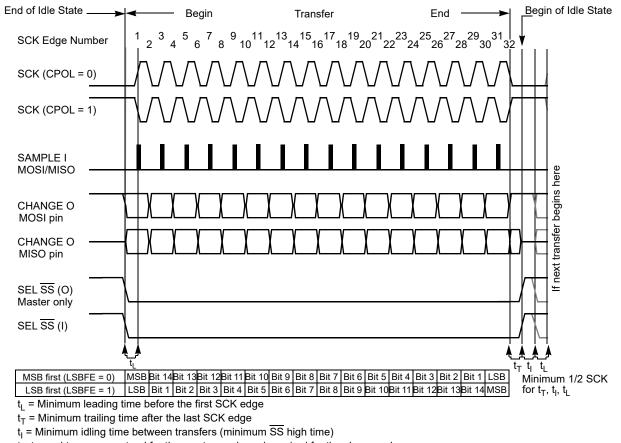

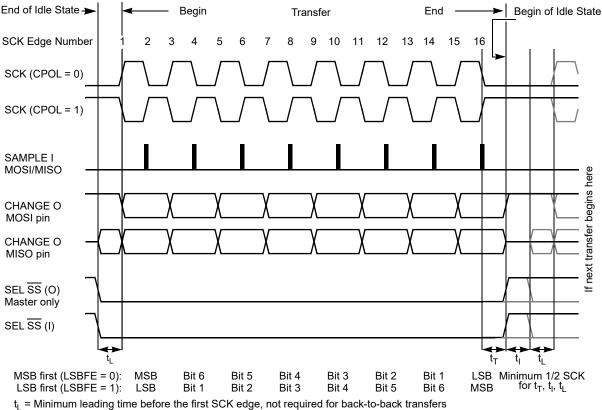

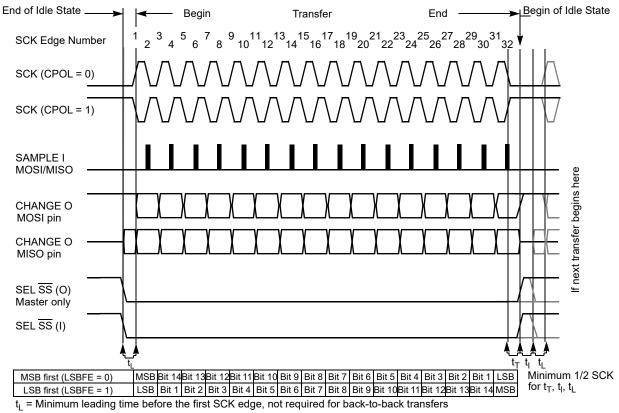

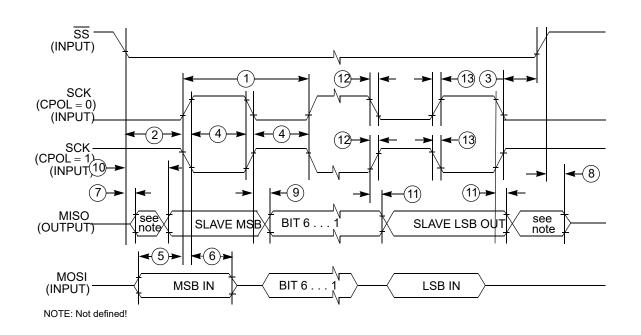

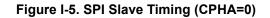

|      | 17.4.3 Transmission Formats               | <br> | 688 |

|      | 17.4.4 SPI Baud Rate Generation           | <br> | 693 |

|      | 17.4.5 Special Features                   | <br> | 694 |

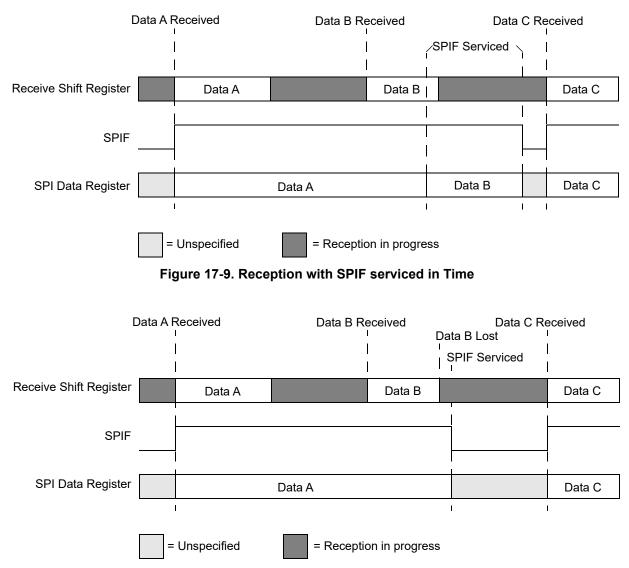

| 17.4.6 Error Conditions       |     |

|-------------------------------|-----|

| 17.4.7 Low Power Mode Options | 696 |

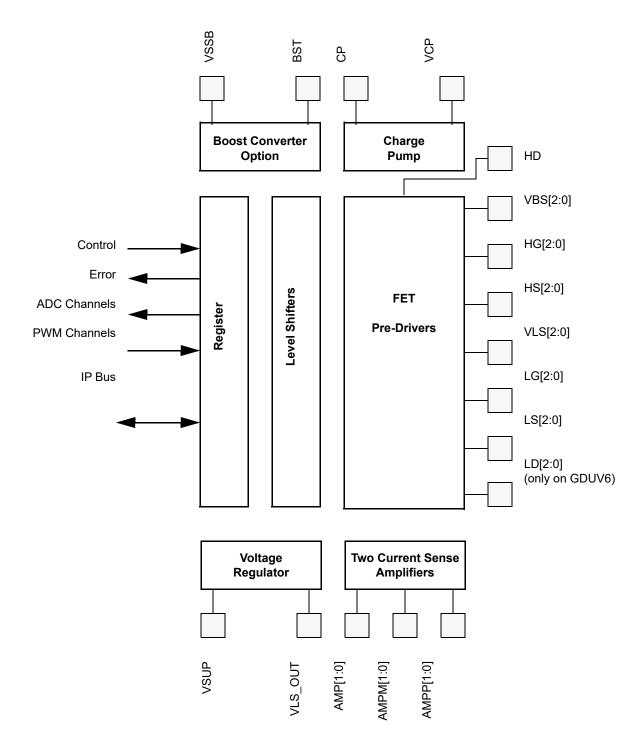

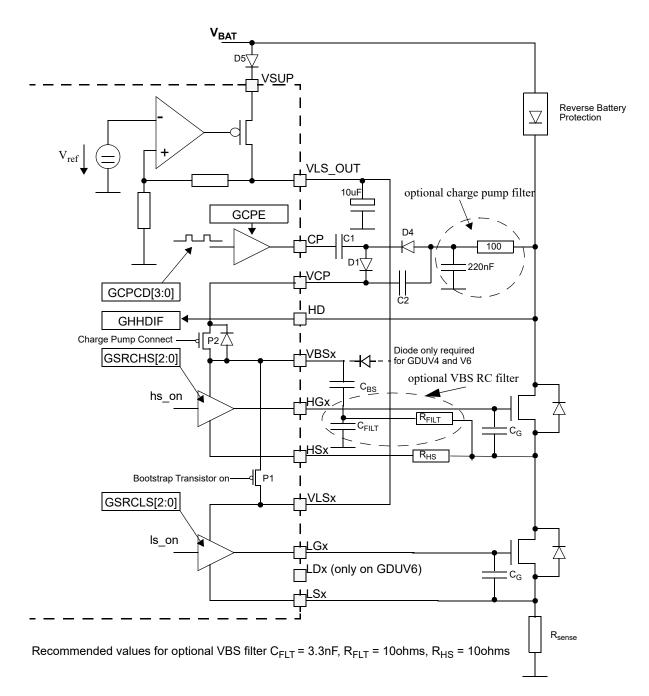

## Chapter 18 Gate Drive Unit (GDU)

| 18.1 | Differences GDUV4 vs GDUV5 vs GDUV6                       | <br> | <br>699 |

|------|-----------------------------------------------------------|------|---------|

|      | 18.1.1 Features                                           | <br> | <br>700 |

|      | 18.1.2 Modes of Operation                                 | <br> | <br>701 |

|      | 18.1.3 Block Diagram                                      |      |         |

| 18.2 | External Signal Description                               | <br> | <br>703 |

|      | 18.2.1 HD — High-Side Drain Connection                    | <br> | <br>703 |

|      | 18.2.2 VBS[2:0] — Bootstrap Capacitor Connection Pins     | <br> | <br>703 |

|      | 18.2.3 HG[2:0] — High-Side Gate Pins                      | <br> | <br>703 |

|      | 18.2.4 HS[2:0] — High-Side Source Pins                    | <br> | <br>703 |

|      | 18.2.5 VLS[2:0] — Voltage Supply for Low-Side Pre-Drivers | <br> | <br>703 |

|      | 18.2.6 LG[2:0] — Low-Side Gate Pins                       | <br> | <br>703 |

|      | 18.2.7 LD[2:0] — Low-Side Gate Pins (only on GDUV6)       | <br> | <br>703 |

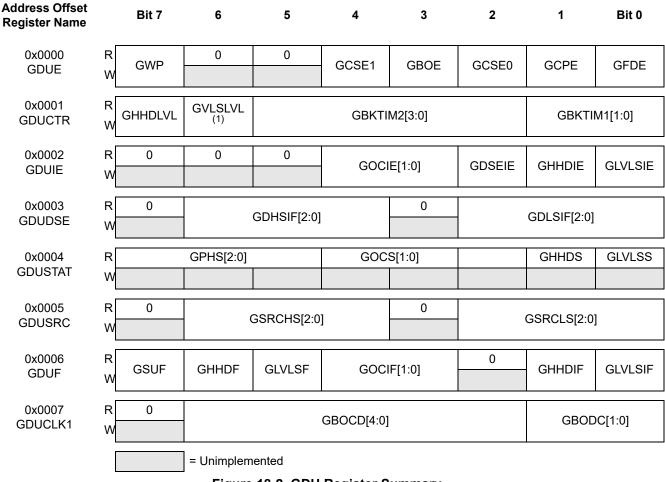

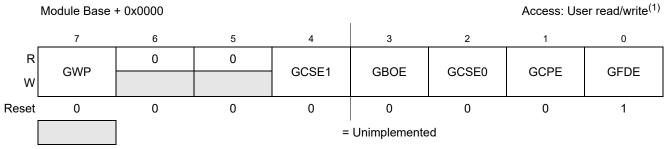

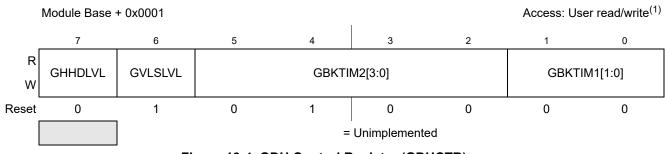

| 18.3 | Memory Map and Register Definition                        | <br> | <br>705 |

|      | 18.3.1 Register Summary                                   | <br> | <br>705 |

|      | 18.3.2 Register Descriptions                              | <br> | <br>706 |

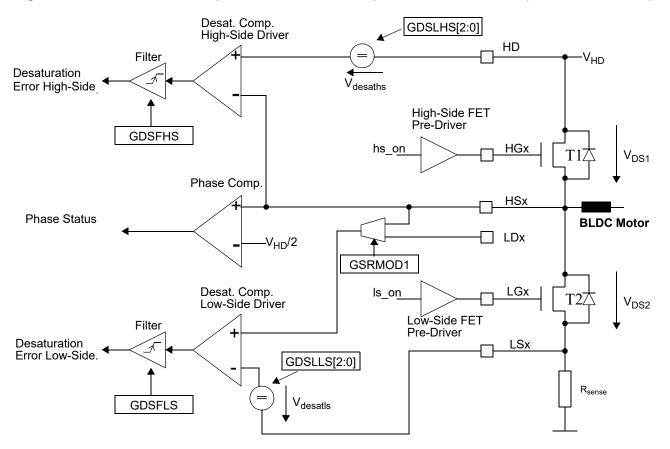

| 18.4 | Functional Description                                    | <br> | <br>726 |

|      | 18.4.1 General                                            | <br> | <br>726 |

|      | 18.4.2 Low-Side FET Pre-Drivers                           | <br> | <br>726 |

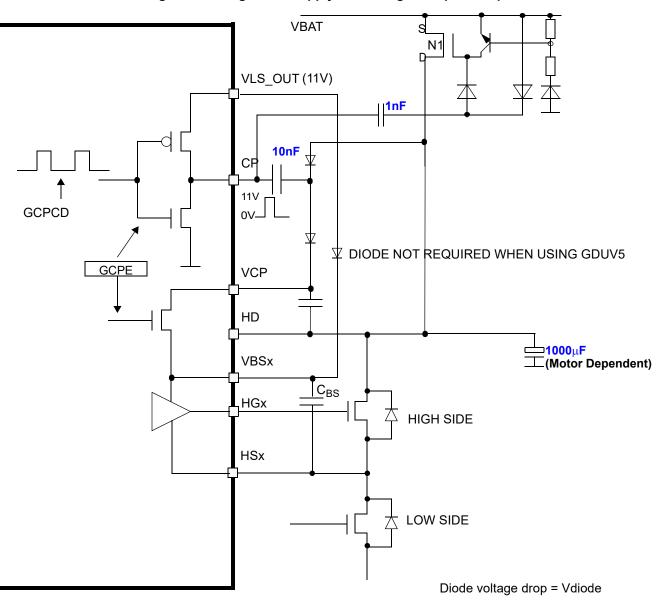

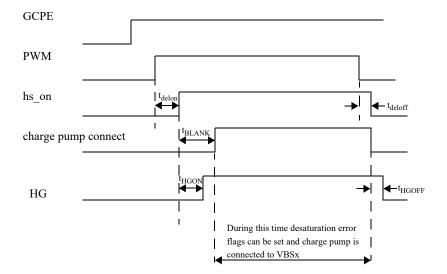

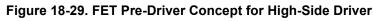

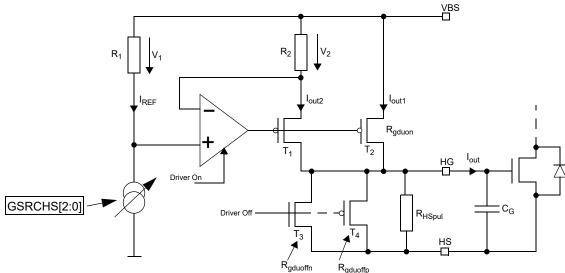

|      | 18.4.3 High-Side FET Pre-Driver                           | <br> | <br>726 |

|      | 18.4.4 Charge Pump                                        | <br> | <br>729 |

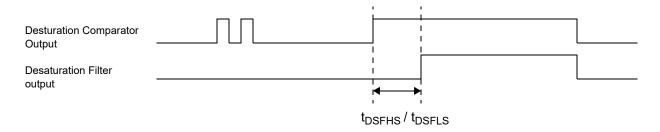

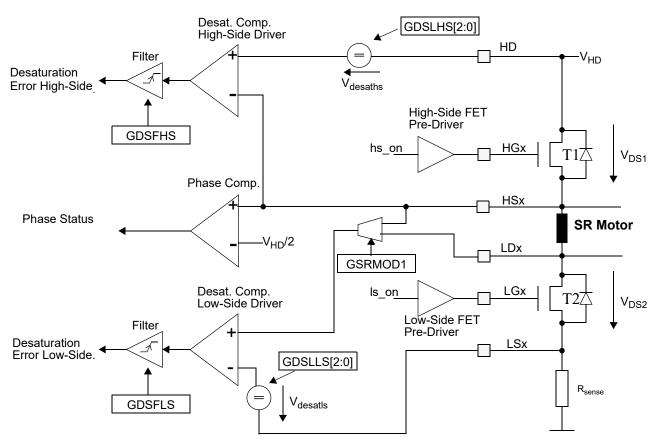

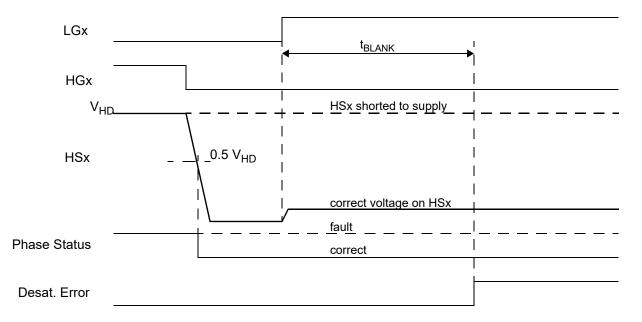

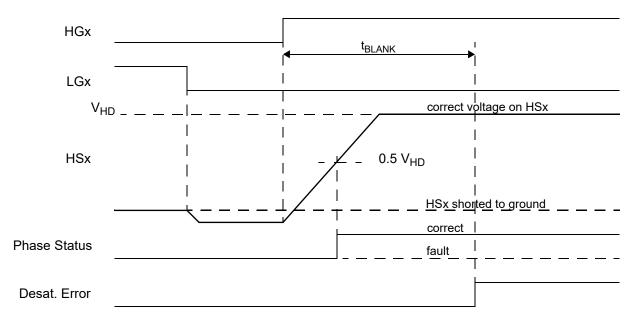

|      | 18.4.5 Desaturation Error                                 | <br> | <br>731 |

|      | 18.4.6 Phase Comparators                                  | <br> | <br>733 |

|      | 18.4.7 Fault Protection Features                          | <br> | <br>734 |

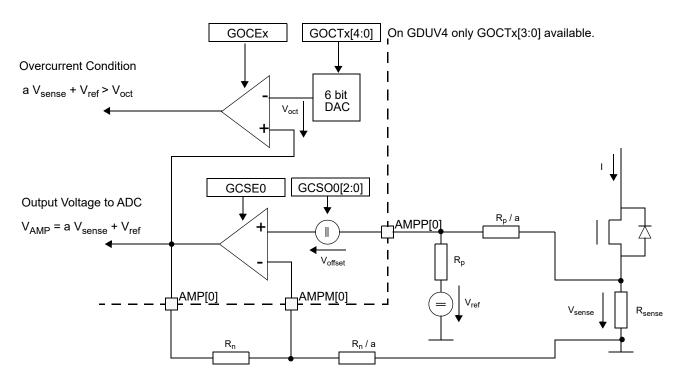

|      | 18.4.8 Current Sense Amplifier and Overcurrent Comparator | <br> | <br>738 |

|      | 18.4.9 GDU DC Link Voltage Monitor                        | <br> | <br>738 |

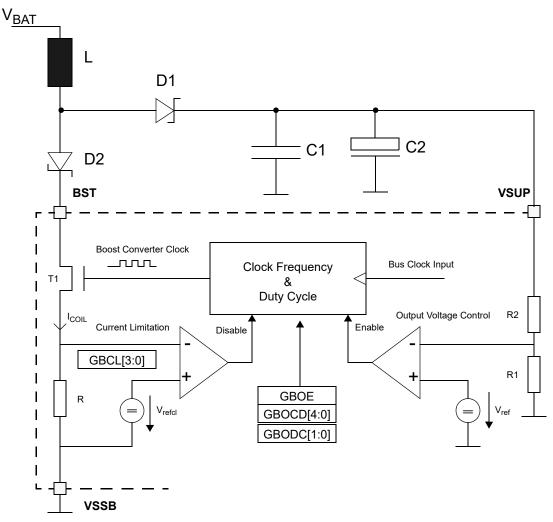

|      | 18.4.10Boost Converter                                    | <br> | <br>739 |

|      | 18.4.11Interrupts                                         | <br> | <br>740 |

| 18.5 | Application Information                                   | <br> | <br>741 |

|      | 18.5.1 FET Pre-Driver Details                             | <br> | <br>741 |

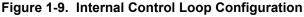

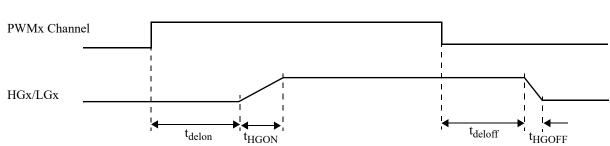

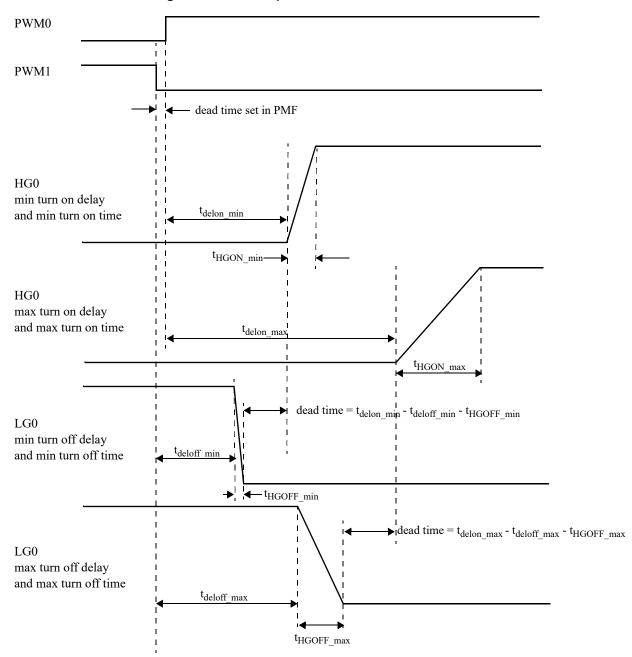

|      | 18.5.2 GDU Intrinsic Dead Time                            | <br> | <br>742 |

|      | 18.5.3 Calculation of Bootstrap Capacitor                 | <br> | <br>744 |

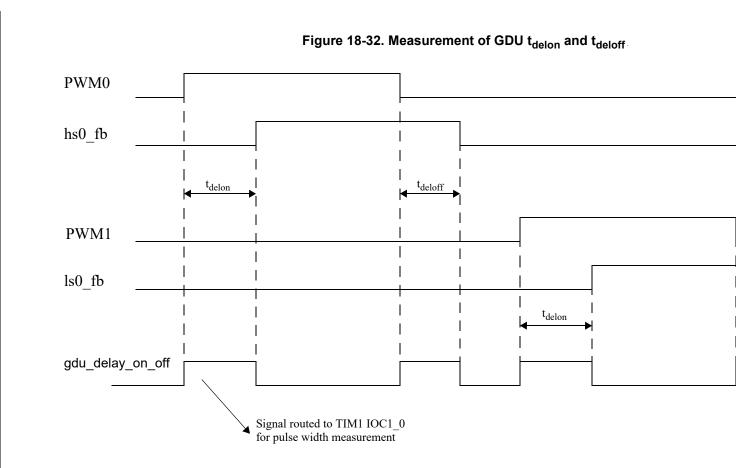

|      | 18.5.4 On Chip GDU tdelon and tdeloff Measurement         | <br> | <br>744 |

# Chapter 19

# LIN/HV Physical Layer (S12LINPHYV3)

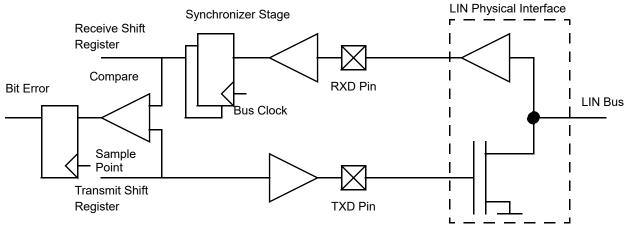

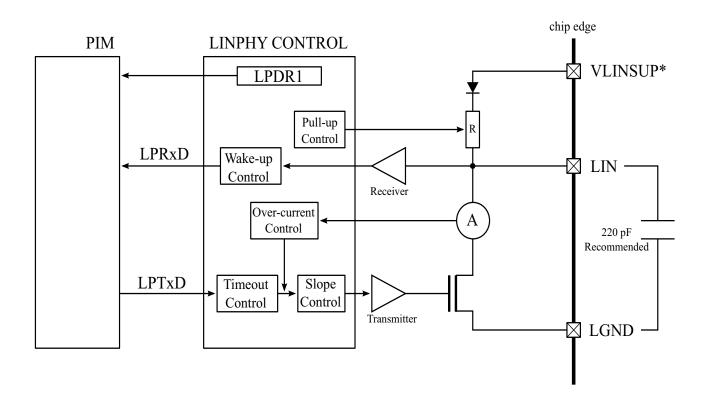

| 19.1 | Introduction              | 753 |

|------|---------------------------|-----|

|      | 19.1.1 Features           | 754 |

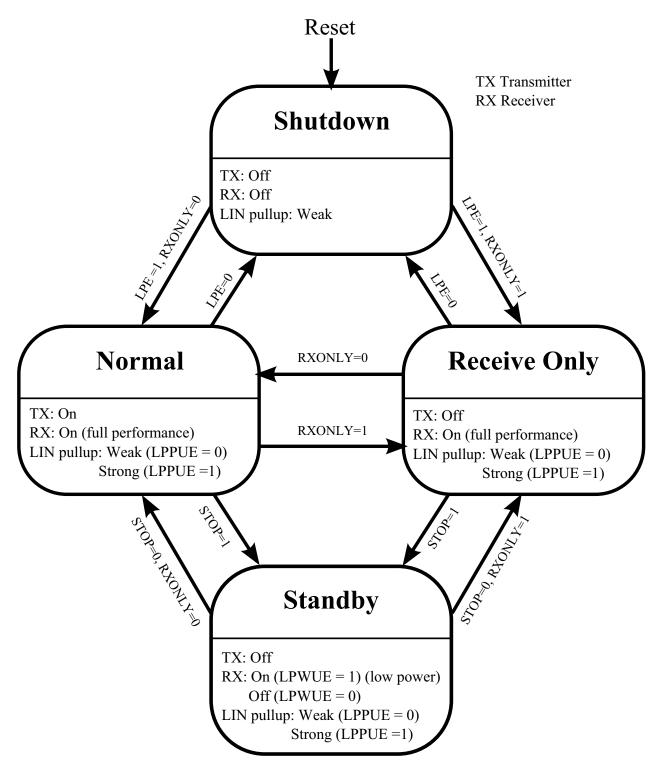

|      | 19.1.2 Modes of Operation | 754 |

|      | 19.1.3 Block Diagram      | 755 |

| 19.2 | External Signal Description                                  |  |

|------|--------------------------------------------------------------|--|

|      | 19.2.1 LIN — LIN Bus Pin                                     |  |

|      | 19.2.2 LGND — LIN Ground Pin                                 |  |

|      | 19.2.3 VLINSUP — Positive Power Supply                       |  |

|      | 19.2.4 LPTxD — LIN Transmit Pin                              |  |

|      | 19.2.5 LPRxD — LIN Receive Pin                               |  |

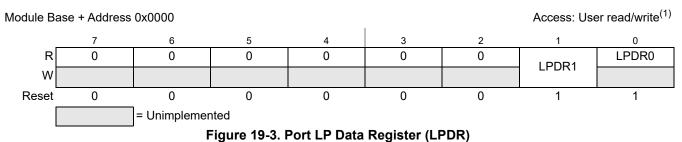

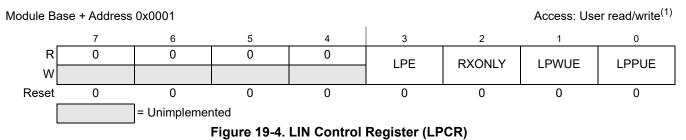

| 19.3 | Memory Map and Register Definition                           |  |

|      | 19.3.1 Module Memory Map                                     |  |

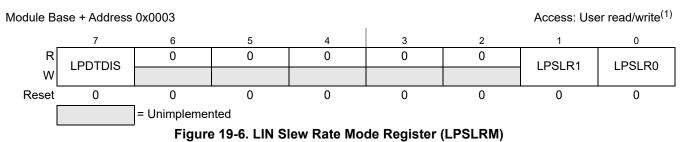

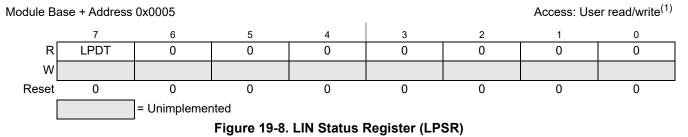

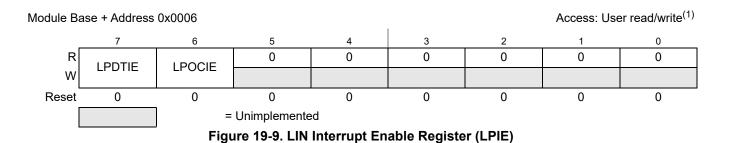

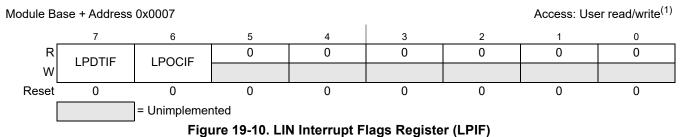

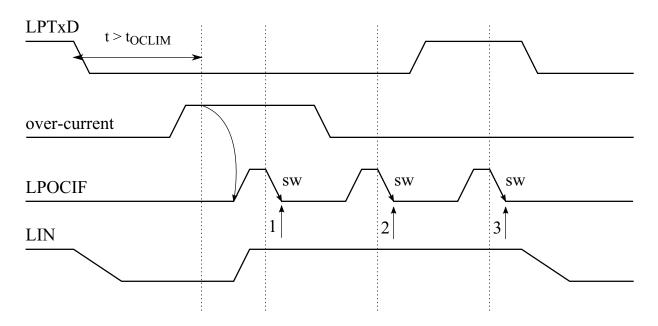

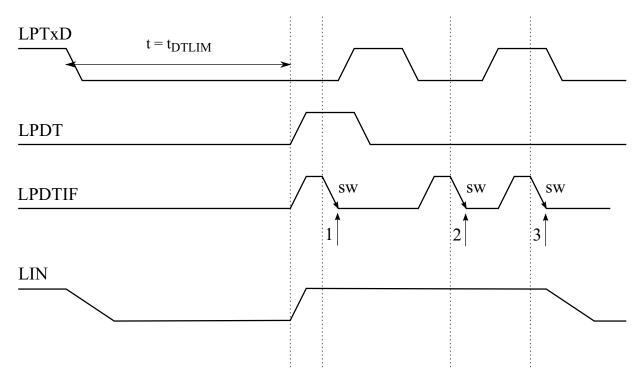

|      | 19.3.2 Register Descriptions                                 |  |

| 19.4 | Functional Description                                       |  |

|      | 19.4.1 General                                               |  |

|      | 19.4.2 Slew Rate and LIN Mode Selection                      |  |

|      | 19.4.3 Modes                                                 |  |

|      | 19.4.4 Interrupts                                            |  |

| 19.5 | Application Information                                      |  |

|      | 19.5.1 Module Initialization                                 |  |

|      | 19.5.2 Interrupt handling in Interrupt Service Routine (ISR) |  |

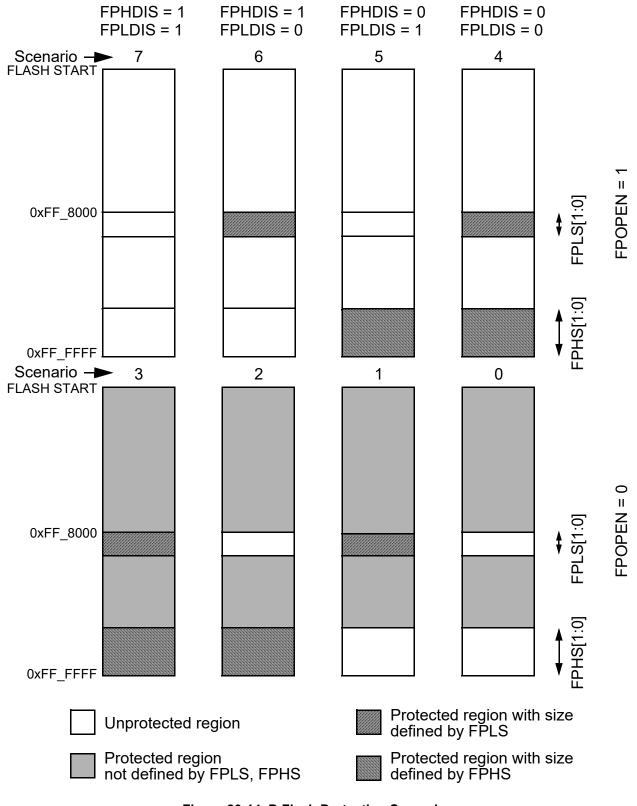

# Chapter 20 Flash Module (S12ZFTMRZ)

| 20.1 | Introduction                                                    | •••   | ••• |       |       | 775 |

|------|-----------------------------------------------------------------|-------|-----|-------|-------|-----|

|      | 20.1.1 Glossary                                                 |       |     |       |       | 776 |

|      | 20.1.2 Features                                                 | •••   |     |       |       | 776 |

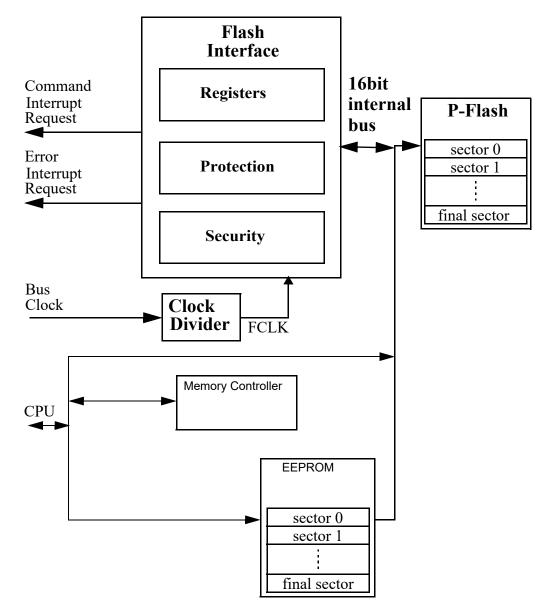

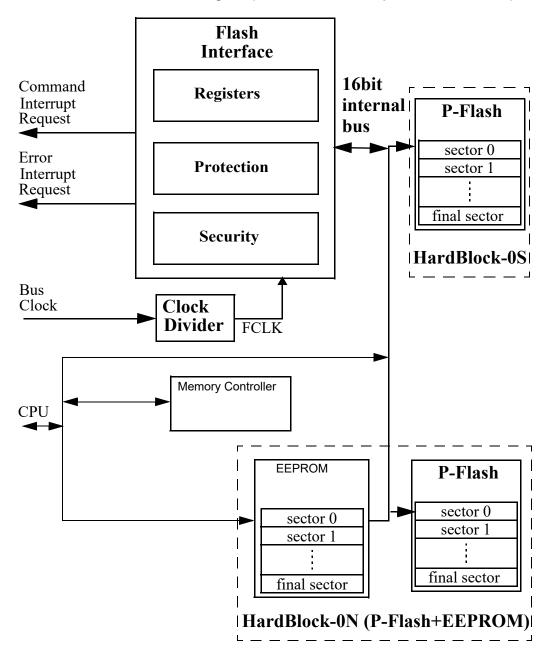

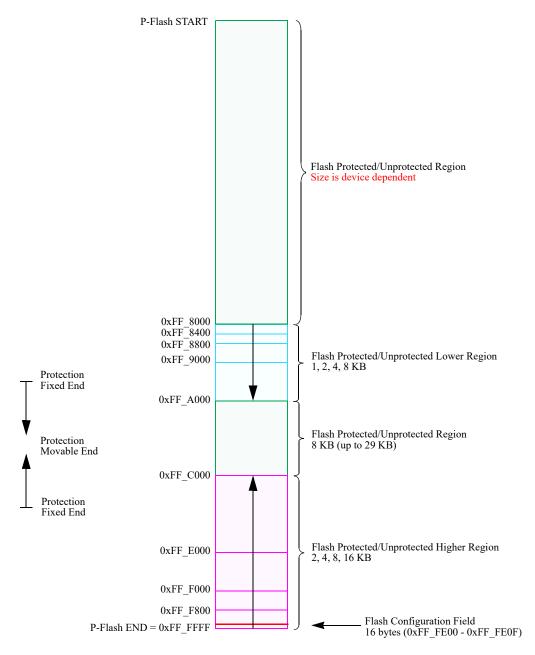

|      | 20.1.3 Block Diagram                                            |       |     |       |       | 777 |

| 20.2 | External Signal Description                                     | • • • |     |       |       | 779 |

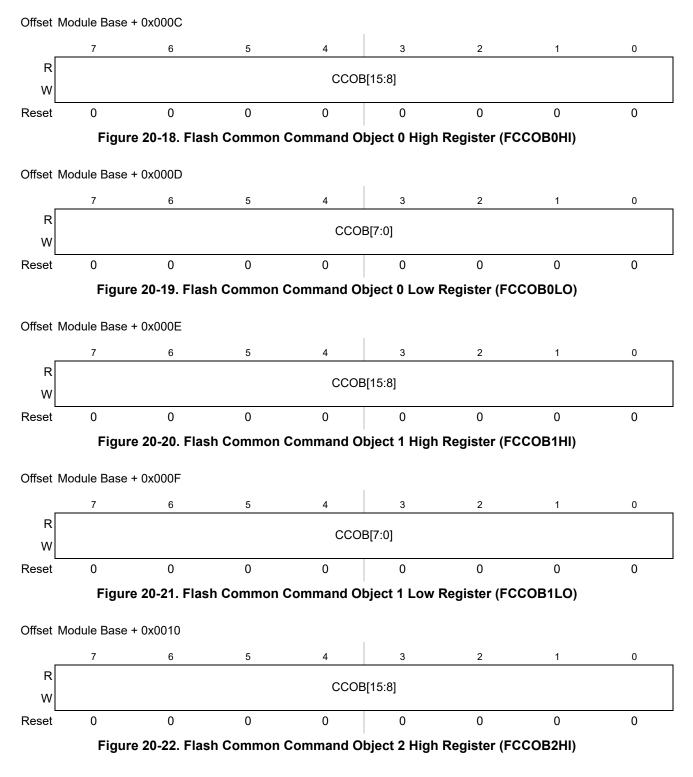

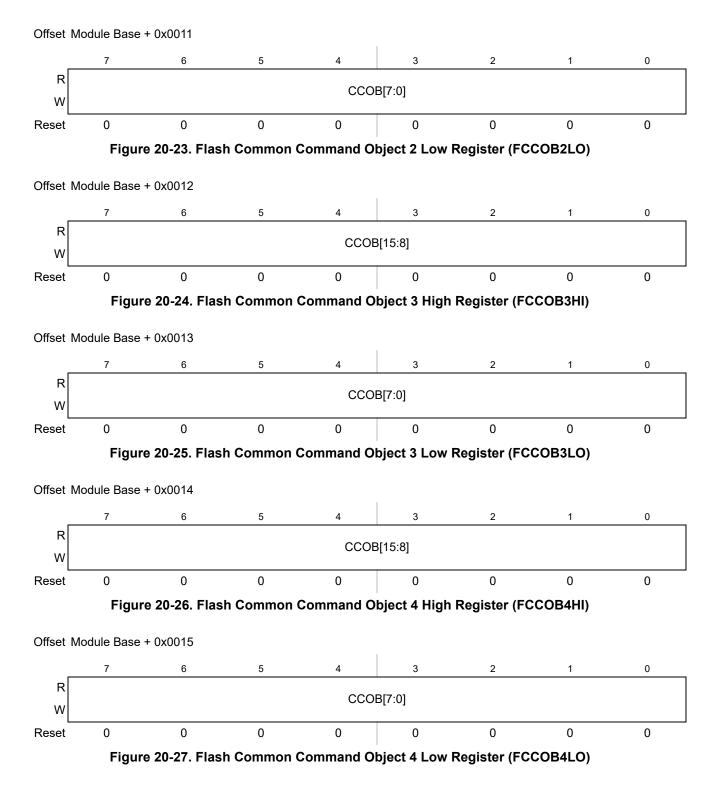

| 20.3 | Memory Map and Registers                                        |       |     |       |       | 780 |

|      | 20.3.1 Module Memory Map                                        |       |     |       |       | 780 |

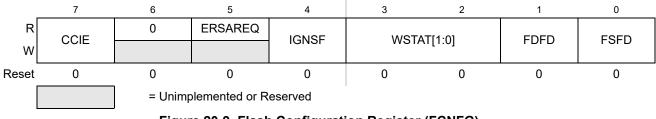

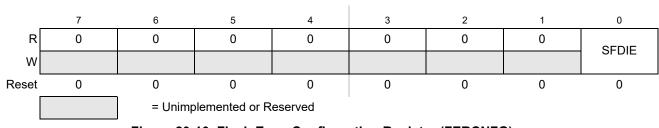

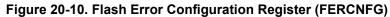

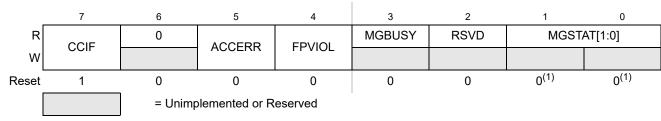

|      | 20.3.2 Register Descriptions                                    |       |     |       |       |     |

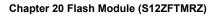

| 20.4 | Functional Description                                          |       |     |       |       | 805 |

|      | 20.4.1 Modes of Operation                                       |       |     |       |       | 805 |

|      | 20.4.2 IFR Version ID Word                                      |       |     |       |       | 805 |

|      | 20.4.3 Flash Block Read Access                                  |       |     |       |       |     |

|      | 20.4.4 Internal NVM resource                                    |       |     |       |       |     |

|      | 20.4.5 Flash Command Operations                                 |       |     |       |       |     |

|      | 20.4.6 Allowed Simultaneous P-Flash and EEPROM Operations       |       |     |       |       |     |

|      | 20.4.7 Flash Command Description                                |       |     |       |       |     |

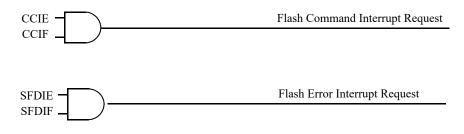

|      | 20.4.8 Interrupts                                               |       |     |       |       |     |

|      | 20.4.9 Wait Mode                                                |       | ••• |       |       | 830 |

|      | 20.4.10Stop Mode                                                | • • • | ••• | • • • | • • • | 830 |

| 20.5 |                                                                 |       |     |       |       |     |

|      | 20.5.1 Unsecuring the MCU using Backdoor Key Access             |       |     |       |       |     |

|      | 20.5.2 Unsecuring the MCU in Special Single Chip Mode using BDM |       |     |       |       |     |

|      | 20.5.3 Mode and Security Effects on Flash Command Availability  |       |     |       |       |     |

| 20.6 | Initialization                                                  | •••   |     |       |       | 832 |

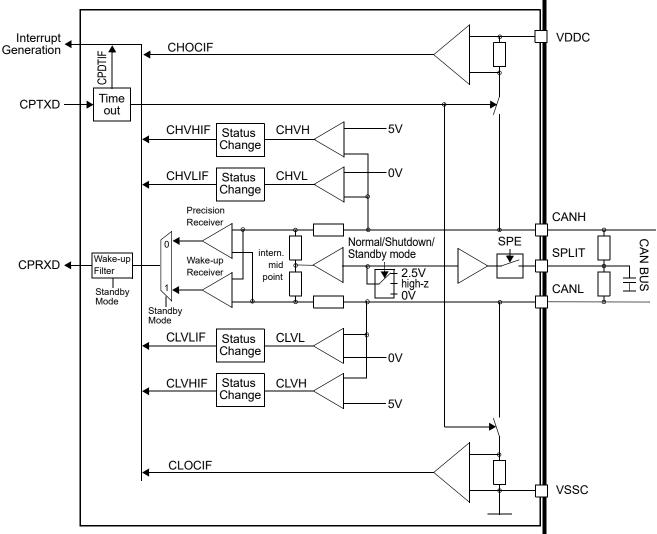

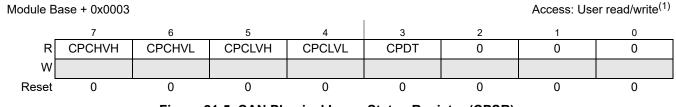

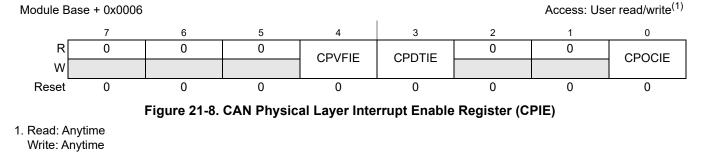

| 21.1 | Introduction                                    | . 833 |

|------|-------------------------------------------------|-------|

|      | 21.1.1 Features                                 | . 833 |

|      | 21.1.2 Modes of Operation                       | . 834 |

|      | 21.1.3 Block Diagram                            | . 834 |

| 21.2 | External Signal Description                     | . 835 |

|      | 21.2.1 CANH — CAN Bus High Pin                  | . 836 |

|      | 21.2.2 CANL — CAN Bus Low Pin                   | . 836 |

|      | 21.2.3 SPLIT — CAN Bus Termination Pin          | . 836 |

|      | 21.2.4 VDDC — Supply Pin for CAN Physical Layer |       |

|      | 21.2.5 VSSC — Ground Pin for CAN Physical Layer | . 836 |

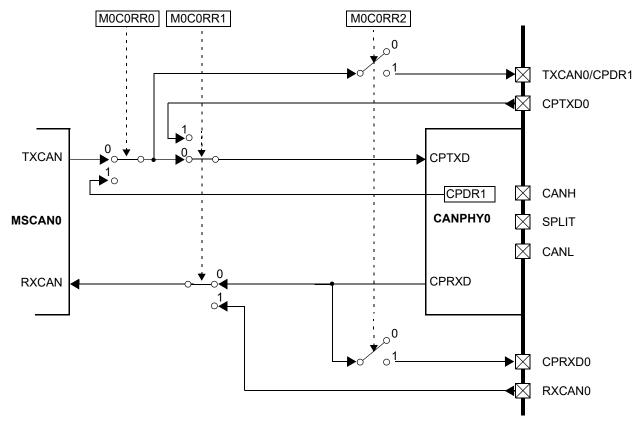

| 21.3 | Internal Signal Description                     |       |

|      | 21.3.1 CPTXD — TXD Input to CAN Physical Layer  |       |

|      | 21.3.2 CPRXD — RXD Output of CAN Physical Layer | . 836 |

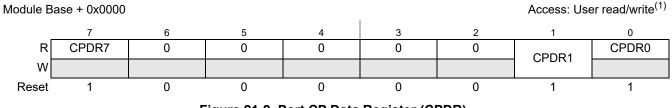

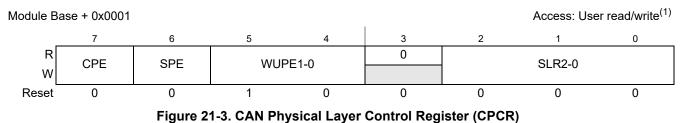

| 21.4 | Memory Map and Register Definition              | . 837 |

|      | 21.4.1 Module Memory Map                        |       |

|      | 21.4.2 Register Descriptions                    | . 838 |

| 21.5 | Functional Description                          | . 845 |

|      | 21.5.1 General                                  |       |

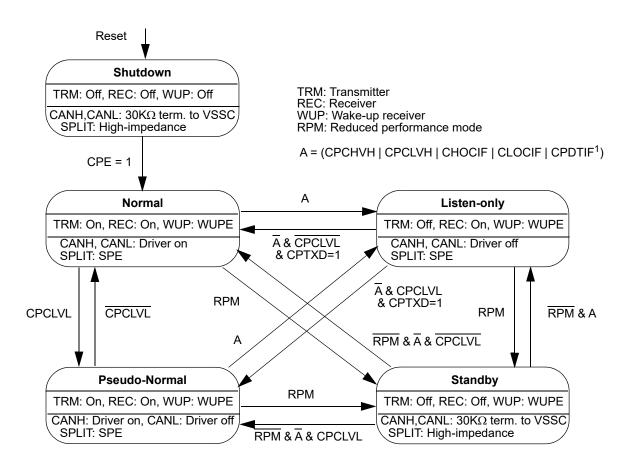

|      | 21.5.2 Modes                                    |       |

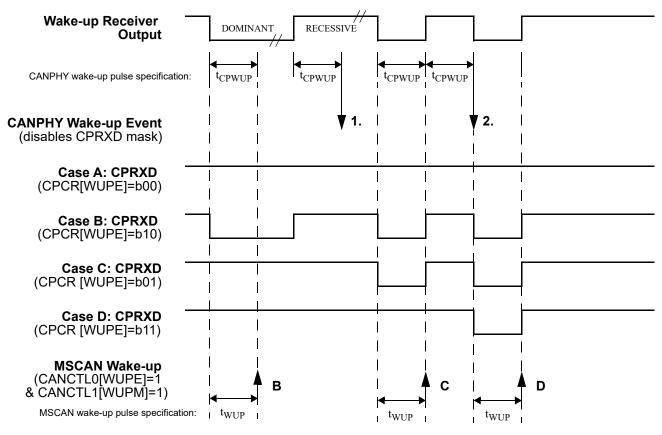

|      | 21.5.3 Configurable Wake-Up                     |       |

|      | 21.5.4 Interrupts                               |       |

| 21.6 | Initialization/Application Information          |       |

|      | 21.6.1 Initialization Sequence                  | . 849 |

|      | 21.6.2 Wake-up Mechanism                        | . 850 |

|      | 21.6.3 Bus Error Handling                       | . 850 |

|      | 21.6.4 CPTXD-Dominant Timeout Recovery          | . 851 |

## Chapter 21 CAN Physical Layer (S12CANPHYV3)

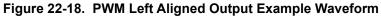

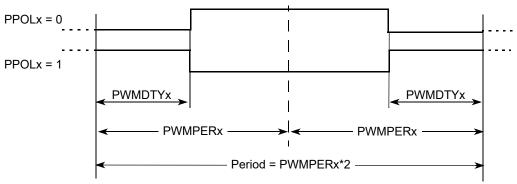

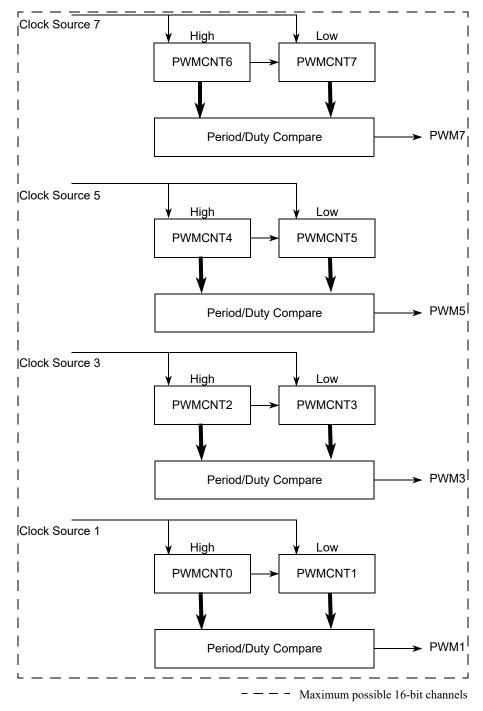

## Chapter 22 Pulse-Width Modulator (S12PWM8B8CV2)

| 22.1 | Introduction                           |     |

|------|----------------------------------------|-----|

|      | 22.1.1 Features                        | 853 |

|      | 22.1.2 Modes of Operation              | 853 |

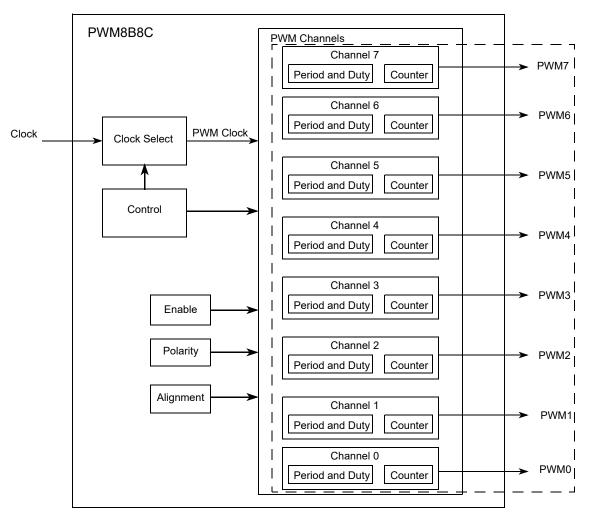

|      | 22.1.3 Block Diagram                   | 854 |

| 22.2 | External Signal Description            | 854 |

|      | 22.2.1 PWM7 - PWM0 — PWM Channel 7 - 0 | 855 |

| 22.3 | Memory Map and Register Definition     | 855 |

|      | 22.3.1 Module Memory Map               | 855 |

|      | 22.3.2 Register Descriptions           | 855 |

| 22.4 | Functional Description                 | 870 |

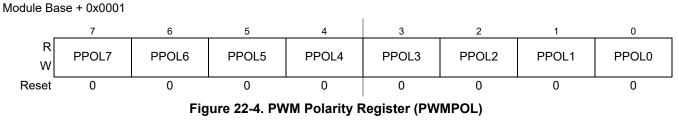

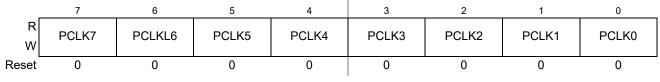

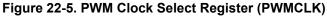

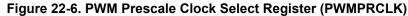

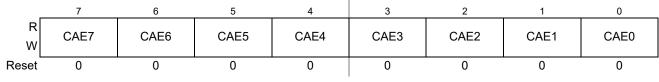

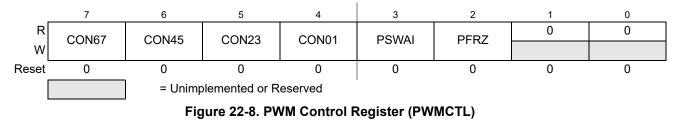

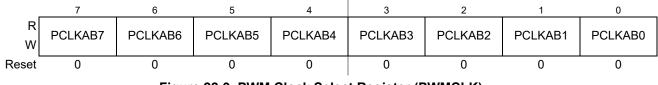

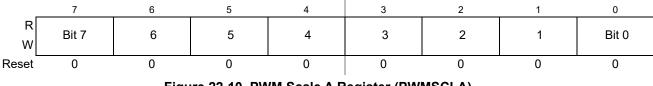

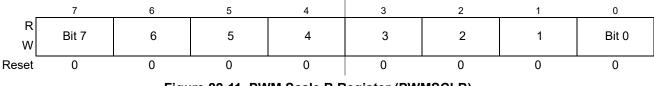

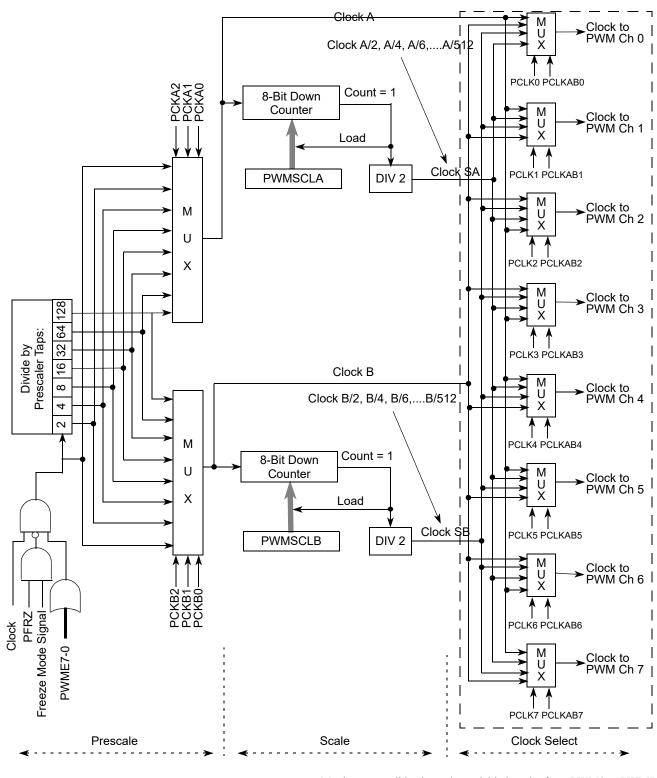

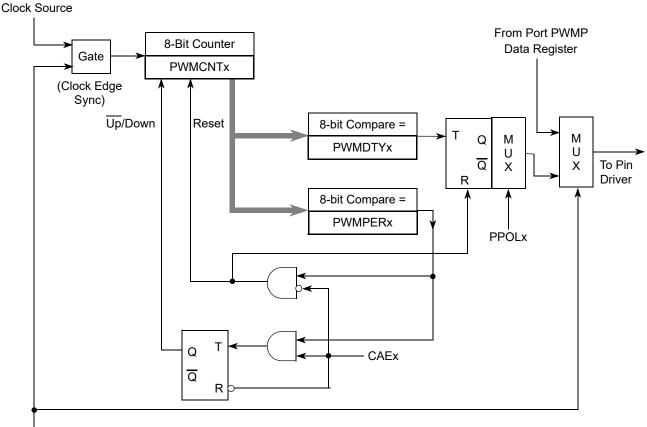

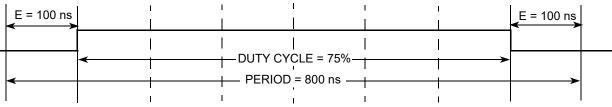

|      | 22.4.1 PWM Clock Select                | 870 |

|      | 22.4.2 PWM Channel Timers              |     |

| 22.5 | Resets                                 | 880 |

| 22.6 | Interrupts |  |  |  |  |  |  |  |  |  | ••• |  |  | ••• | ••• |  | • • |  |  |  |  |  | 88 | 1 |

|------|------------|--|--|--|--|--|--|--|--|--|-----|--|--|-----|-----|--|-----|--|--|--|--|--|----|---|

|------|------------|--|--|--|--|--|--|--|--|--|-----|--|--|-----|-----|--|-----|--|--|--|--|--|----|---|

### Appendix A MCU Electrical Specifications

| A.1 | General                             | 883 |

|-----|-------------------------------------|-----|

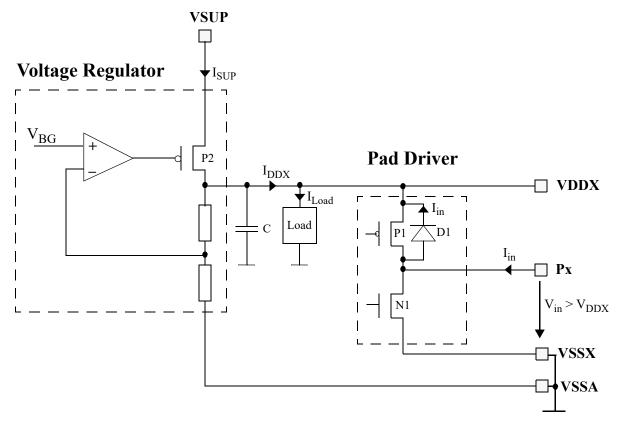

| A.2 | General Purpose I/O Characteristics | 896 |

| A.3 | Supply Currents.                    | 898 |

| A.4 | ADC Calibration Configuration       | 901 |

### Appendix B

## **CPMU Electrical Specifications (VREG, OSC, IRC, PLL)**

| <b>B</b> .1 | VREG Electrical Specifications         | . 903 |

|-------------|----------------------------------------|-------|

| B.2         | Reset and Stop Timing Characteristics  | . 905 |

| B.3         | IRC and OSC Electrical Specifications. | . 906 |

| <b>B.4</b>  | Phase Locked Loop                      | . 906 |

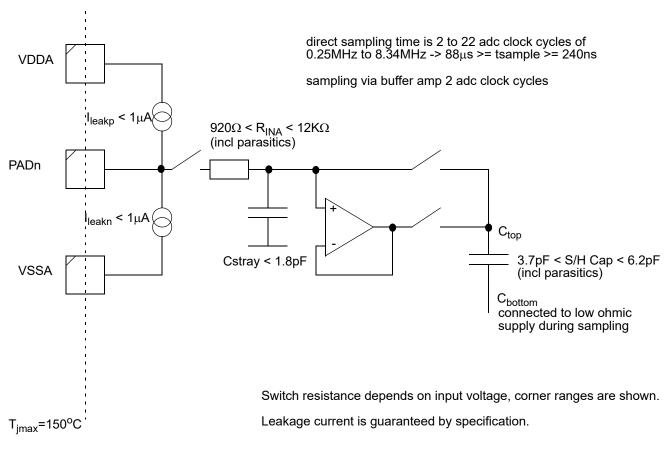

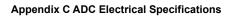

### Appendix C ADC Electrical Specifications

| <b>C</b> .1 | ADC Operating Characteristics |  | 909 |

|-------------|-------------------------------|--|-----|

|-------------|-------------------------------|--|-----|

### Appendix D LIN/HV PHY Electrical Specifications

| D.1 | Static Electrical Characteristics. | 917 | ſ |