# SAF784x One chip CD audio device with integrated MP3/WMA decoder Rev. 02 — 9 May 2008 Product data sheet

### 1. General description

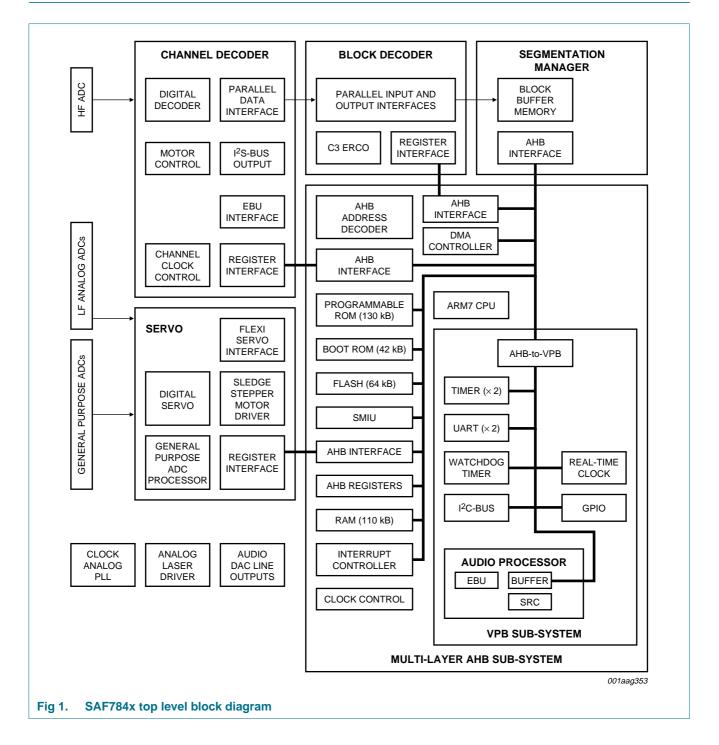

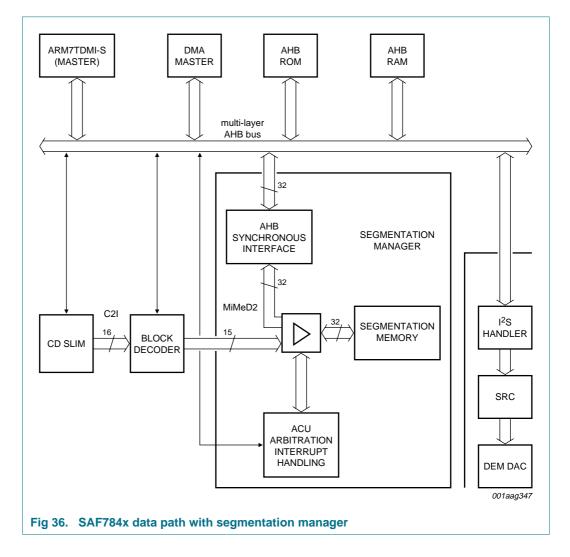

The SAF784x is a single-chip solution CD audio decoder with on-chip MP3 and WMA decoding, digital servo, audio DAC, sample-rate converter, preamplifier, laser driver and integrated ARM7TDMI-S microprocessor. The device contains all of the required ROM and RAM, including an internal re-programmable Flash ROM, and is targeted at low-cost compressed audio CD applications. The design is a one-chip CD audio decoder IC, with additions to allow low-cost system implementation of MP3 and WMA decoding.

### 2. Features

### 2.1 Features

- Channel decoder and digital servo

- 32-bit embedded ARM7 RISC microprocessor supporting both 32-bit and 16-bit ('Thumb') instruction sets

- Maximum ARM operating frequency of 76 MHz, equivalent to 68 MIPS

- Decoding of compressed audio stream (MP3/WMA) on ARM7 core

- All memories required for MP3/WMA decoding embedded on chip: combination of 130 kB mask-programmed internal program ROM (to reduce wait-states on high-speed code, e.g. decompression algorithms), 42 kB boot ROM, 64 kB of internal re-programmable Flash ROM (for simple re-programming of application code) 110 kB internal SRAM

- Programmable clock frequency for ARM microprocessor allowing users to trade-off power consumption and processing power depending on requirements

- Block decoder hardware to perform C3 error correction

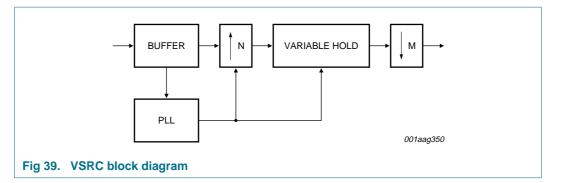

- Sample-rate converter circuit to convert compressed audio sample rates (in the range 8 kHz to 48 kHz) to an output rate of 44.1 kHz

- Microprocessor access to digital representations of the diode input signals from the optical pickup; the microprocessor can also generate the servo output signals RA, FO, SL, allowing the possibility of additional servo algorithms in software

- Programmable PDM outputs (effectively sine and cosine) to allow use of stepper motor for sledge mechanism

- Microprocessor access to audio streams, both from the internal CD decoder and an external stereo auxiliary input (e.g. an analog source from a tuner, converted to digital via on-chip ADCs) to allow audio processing algorithms in the ARM microprocessor, e.g. bass boost, volume control

- Four general-purpose analog inputs (A\_IN1 to A\_IN4) allowing the ARM microprocessor access to other external analog signals, e.g. low-cost keypad, temperature sensor, via on-chip ADCs

- Two additional analog audio inputs (AUX\_L, AUX\_R) to allow the ARM microprocessor access to external audio signals (e.g. tuner); allows audio algorithms (e.g. bass boost) to be performed on external audio signals

- Real-time clock operated from separate 32 kHz crystal; allows low-power Standby mode with real-time clock still operational

- Watchdog timer

- I<sup>2</sup>S-bus, S/PDIF, subcode (V4) and subcode sync outputs

- 32 GPIOs

- Two standard UART channels

- Two external interrupt pins

- I<sup>2</sup>C-bus interface configurable for master or slave modes, supporting 100 kbit/s and 400 kbit/s standards

- Slave I<sup>2</sup>S-bus mode, in which the channel decoder can synchronize the CD playback speed to an I<sup>2</sup>S-bus clock input

- Integrated digital HF/Mirror detector with measurement of minimum and maximum peak values, amplitude and offset

- Integrated CD-text decoder

- Up to 6× decode speed, CLV or CAV modes

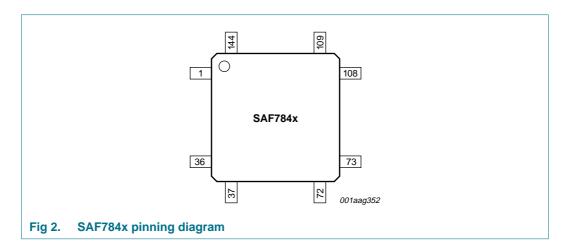

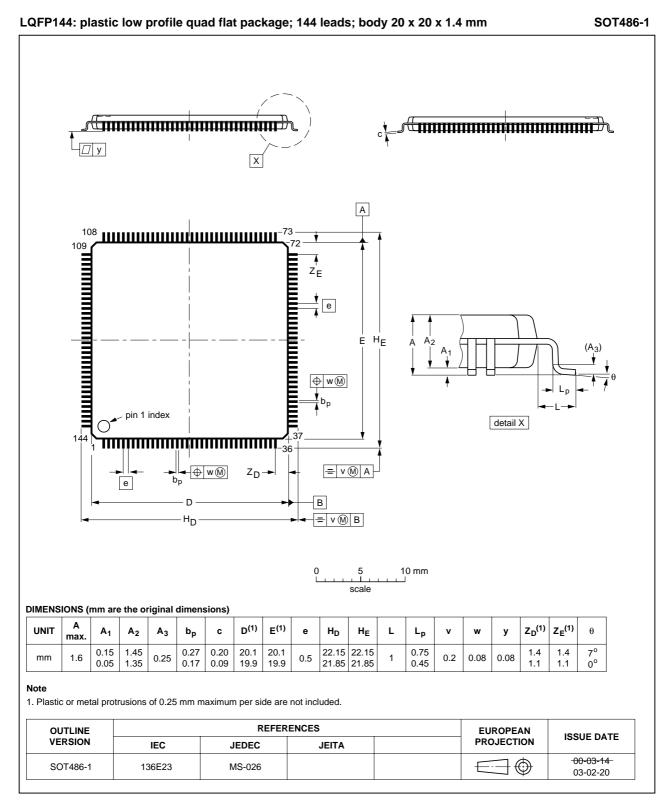

- LQFP144 package with 0.5 mm pin pitch

- Separate left and right channel digital silence detection available on KILL pins

- Digital silence detection available on loopback data from external source as well as internal data

- 'Filterless' pseudo bit stream audio DAC with minimal external components

- Stereo line outputs for audio DAC

- Loopback mode allowing the use of integrated DAC with external I<sup>2</sup>S-bus/EIAJ sources

- Compatible with voltage mode mechanisms

- On-chip buffering and filtering of the diode signals from the mechanism in order to optimize the signals for the decoder and servo parts

- LF (servo) signals converted to digital representations by Sigma-Delta ADCs shared between pairs of channels to minimize DC offset between channels

- HF part summed from signals D1 to D4 and converted to digital signals by HF 6-bit ADC

- Selectable DC offset cancellation of quiescent mechanism voltages and dark currents, digitally controlled; additional fine DC-offset cancellation in digital domain

- Eye pattern monitor system to observe selectable points within the analog pre-amp

- Current and average jitter values available via registers

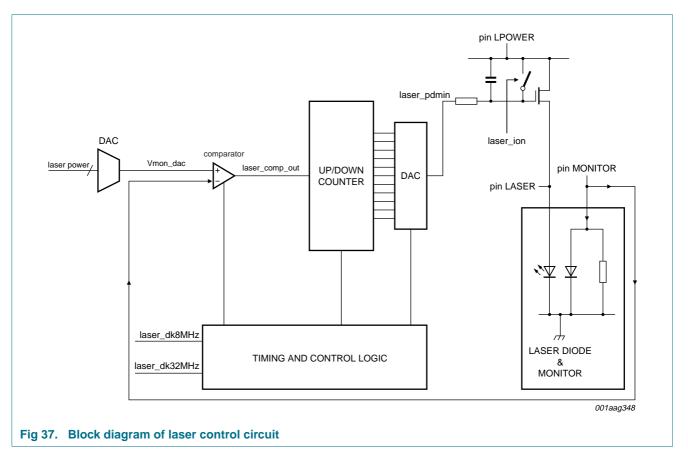

- On-chip laser power control, up to maximum currents of 120 mA

- Laser on-off control, including 'soft'-start control zero-to-nominal output power in 1 ms

- Monitor control and feedback circuit to maintain nominal output power throughout laser life

- Configured for Nsub (N-substrate) monitor diode

- JTAG interface for device access and ARM code development (compatible with ARM multi-ICE)

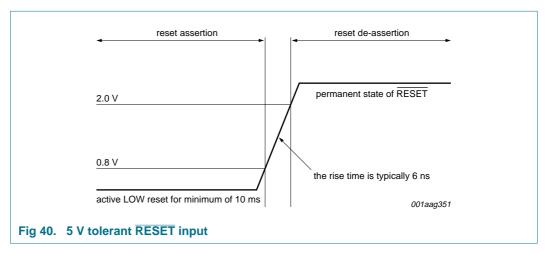

- All digital input pins 5 V tolerant

- Low-latency static memory interface to access a maximum of two 2 MB memory

This product has been qualified in accordance with AEC-Q100

### 2.2 Formats

Reads the following CD-decode formats

- CD-R

- CD-RW

- CD-DA (CD Red Book; IEC 60908)

- CD-ROM (Mode 1 and Mode 2)

- CD-MP3

- CD-WMA

- Video CD

- SACD (CD layer only)

- Support 80 minute to 100 minute CD playback

- Multi-session discs

### 3. Ordering information

### Table 1.Ordering information

| Type number | Package |                                                                                     |          |  |  |

|-------------|---------|-------------------------------------------------------------------------------------|----------|--|--|

|             | Name    | Description                                                                         | Version  |  |  |

| SAF7846HL   | LQFP144 | plastic low profile quad flat package; 144 leads; body $20 \times 20 \times 1.4$ mm | SOT486-1 |  |  |

| SAF7847HL   |         |                                                                                     |          |  |  |

SAF784x

One chip CD audio device with integrated MP3/WMA decoder

## 4. Block diagram

## 5. Pinning information

### 5.1 Pinning

### 5.2 Pin description

#### Table 2. Pin description

All digital inputs and bidirectional pins are 5 V tolerant.

| Symbol      | Pin | Type <sup>[1]</sup> | Description                                              |

|-------------|-----|---------------------|----------------------------------------------------------|

| SL_SIN      | 1   | 0                   | sledge actuator/stepper motor PDM output (sine)          |

| COS/GPIO31  | 2   | В                   | stepper motor PDM output (cosine)/general purpose I/O 31 |

| LPOWER      | 3   | Р                   | laser power supply                                       |

| LASER       | 4   | Р                   | laser diode drive                                        |

| MONITOR     | 5   | AI                  | laser monitor diode input                                |

| VSSA1       | 6   | Р                   | analog ground 1                                          |

| HF_MON      | 7   | AIO                 | HF monitor output signal                                 |

| VDDA1       | 8   | Р                   | analog supply voltage 1                                  |

| D1          | 9   | AI                  | central diode signal voltage input                       |

| D2          | 10  | AI                  | central diode signal voltage input                       |

| D3          | 11  | AI                  | central diode signal voltage input                       |

| D4          | 12  | AI                  | central diode signal voltage input                       |

| R1          | 13  | AI                  | satellite diode signal voltage input                     |

| R2          | 14  | AI                  | satellite diode signal voltage input                     |

| AUX_L       | 15  | AI                  | auxiliary audio left signal input                        |

| AUX_R       | 16  | AI                  | auxiliary audio right signal input                       |

| VDDA2       | 17  | Р                   | analog supply voltage 2                                  |

| OPU_REF_OUT | 18  | AO                  | OPU reference voltage                                    |

| VSSA2       | 19  | Р                   | analog ground 2                                          |

| OSCOUT      | 20  | AO                  | crystal or resonator output                              |

| OSCIN       | 21  | AI                  | crystal or resonator input                               |

| VDDA3       | 22  | Р                   | analog supply voltage 3                                  |

SAF784X\_2 Product data sheet

SAF784x

#### One chip CD audio device with integrated MP3/WMA decoder

#### Table 2. Pin description ...continued

All digital inputs and bidirectional pins are 5 V tolerant.

| Symbol      | Pin | Type <mark>[1]</mark> | Description                                                |

|-------------|-----|-----------------------|------------------------------------------------------------|

| DAC_LP      | 23  | AO                    | audio DAC left channel differential output (positive)      |

| DAC_LN      | 24  | AO                    | audio DAC left channel differential output (negative)      |

| DAC_VREF    | 25  | AIO                   | audio DAC decoupling point (10 $\mu$ F/100 nF to ground)   |

| DAC_RN      | 26  | AO                    | audio DAC right channel differential output (negative)     |

| DAC_RP      | 27  | AO                    | audio DAC right channel differential output (positive)     |

| DAC_FGND    | 28  | Р                     | audio DAC floating ground                                  |

| VSSA3       | 29  | Р                     | analog ground 3                                            |

| OSC_32K_IN  | 30  | AO                    | 32 kHz crystal input                                       |

| OSC_32K_OUT | 31  | AO                    | 32 kHz crystal output                                      |

| VDDD1       | 32  | Р                     | digital core supply voltage 1                              |

| A_IN1/GPIO0 | 33  | AIB                   | analog input 1/general purpose I/O 0                       |

| A_IN2/GPIO1 | 34  | AIB                   | analog input 2/general purpose I/O 1                       |

| A_IN3/GPIO2 | 35  | AIB                   | analog input 3/general purpose I/O 2                       |

| A_IN4/GPIO3 | 36  | AIB                   | analog input 4/general purpose I/O 3                       |

| VSSD1       | 37  | Р                     | digital core ground 1                                      |

| TX/GPIO4    | 38  | В                     | UART transmit/general purpose I/O 4                        |

| RX/GPIO5    | 39  | В                     | UART receive/general purpose I/O 5                         |

| TX2/GPIO6   | 40  | В                     | UART2 transmit/general purpose I/O 6                       |

| DM_ADDR_0   | 41  | 0                     | external memory address bit 0                              |

| RX2/GPIO7   | 42  | В                     | UART2 receive/general purpose I/O 7                        |

| DM_ADDR_1   | 43  | 0                     | external memory address bit 1                              |

| SDA         | 44  | В                     | micro interface data I/O line (open-drain output)          |

| DM_ADDR_2   | 45  | 0                     | external memory address bit 2                              |

| SCL         | 46  | В                     | microprocessor interface clock line                        |

| DM_ADDR_3   | 47  | 0                     | external memory address bit 3                              |

| LKILL       | 48  | 0                     | kill output for left channel (configurable as open-drain)  |

| DM_ADDR_4   | 49  | 0                     | external memory address bit 4                              |

| RKILL       | 50  | 0                     | kill output for right channel (configurable as open-drain) |

| VSSP1       | 51  | Р                     | digital ground 1 to periphery (pads)                       |

| DOBM        | 52  | 0                     | bi-phase mark output (no external buffer required)         |

| VDDP1       | 53  | Р                     | digital supply voltage 1 to periphery (pads)               |

| DM_ADDR_5   | 54  | 0                     | external memory address bit 5                              |

| INT2/GPIO8  | 55  | В                     | external interrupt 2/general purpose I/O 8                 |

| DM_ADDR_6   | 56  | 0                     | external memory address bit 6                              |

| GPIO9       | 57  | В                     | general purpose I/O 9                                      |

| DM_ADDR_7   | 58  | 0                     | external memory address bit 7                              |

| GPIO10      | 59  | В                     | general purpose I/O 10                                     |

| DM_ADDR_8   | 60  | 0                     | external memory address bit 8                              |

| GPIO11      | 61  | В                     | general purpose I/O 11                                     |

|             |     |                       |                                                            |

**SAF784x**

#### One chip CD audio device with integrated MP3/WMA decoder

Table 2.Pin description ...continuedAll digital inputs and bidirectional pins are 5 V tolerant.

| Symbol           | Pin | Type <sup>[1]</sup> | Description                                                                                                |  |

|------------------|-----|---------------------|------------------------------------------------------------------------------------------------------------|--|

| GPIO12           | 63  | В                   | general purpose I/O 12                                                                                     |  |

| DM_ADDR_10       | 64  | 0                   | external memory address bit 10                                                                             |  |

| GPIO13           | 65  | В                   | general purpose I/O 13                                                                                     |  |

| DM_ADDR_11       | 66  | 0                   | external memory address bit 11                                                                             |  |

| GPIO14           | 67  | В                   | general purpose I/O 14                                                                                     |  |

| DM_ADDR_12       | 68  | 0                   | external memory address bit 12                                                                             |  |

| GPIO15           | 69  | В                   | general purpose I/O 15                                                                                     |  |

| DM_ADDR_13       | 70  | 0                   | external memory address bit 13                                                                             |  |

| SDI/GPIO16       | 71  | В                   | serial data input (loopback)/general purpose I/O 16                                                        |  |

| DM_ADDR_14       | 72  | 0                   | external memory address bit 14                                                                             |  |

| WLCI/GPIO17      | 73  | В                   | serial word clock input (loopback)/general purpose I/O 17                                                  |  |

| DM_ADDR_15       | 74  | 0                   | external memory address bit 15                                                                             |  |

| SCLI/GPIO18      | 75  | В                   | serial bit clock input (loopback)/general purpose I/O 18                                                   |  |

| VSSD2            | 76  | Р                   | digital core ground 2                                                                                      |  |

| VDDD2            | 77  | Р                   | digital core supply voltage 2                                                                              |  |

| DM_ADDR_16       | 78  | 0                   | external memory address bit 16                                                                             |  |

| T1/GPIO19        | 79  | В                   | tacho input 1 (for spindle motor sensor)/general purpose I/O 19                                            |  |

| DM_ADDR_17       | 80  | 0                   | external memory address bit 17                                                                             |  |

| T2/GPIO20        | 81  | В                   | tacho input 2 (for spindle motor sensor)/general purpose I/O 20                                            |  |

| DM_ADDR_18       | 82  | 0                   | external memory address bit 18                                                                             |  |

| T3/GPIO21        | 83  | В                   | tacho input 3 (for spindle motor sensor)/general purpose I/O 21                                            |  |

| DM_ADDR_19       | 84  | 0                   | external memory address bit 19                                                                             |  |

| PWM1/CAP1/GPIO22 | 85  | В                   | timer PWM output 1/capture input 1/general purpose I/O 22                                                  |  |

| DM_ADDR_20       | 86  | 0                   | external memory address bit 20                                                                             |  |

| PWM2/CAP2/GPIO23 | 87  | В                   | timer PWM output 2/capture input 2/general purpose I/O 23                                                  |  |

| DM_BLS_0         | 88  | 0                   | external RAM lower-byte lane select (lower 8-bits)                                                         |  |

| PWM3/CAP3/GPIO24 | 89  | В                   | timer PWM output 3/capture input 3/general purpose I/O 24                                                  |  |

| DM_BLS_1         | 90  | 0                   | external RAM upper byte lane select (upper 8-bits)                                                         |  |

| PWM4/CAP4/GPIO25 | 91  | В                   | timer PWM output 4/capture input 4/general purpose I/O 25                                                  |  |

| DM_WE            | 92  | 0                   | external memory right control                                                                              |  |

| MEAS/GPIO26      | 93  | В                   | channel decoder telemetry output/general purpose I/O 26                                                    |  |

| DM_OE            | 94  | 0                   | external memory output enable                                                                              |  |

| CFLG/GPIO27      | 95  | В                   | channel decoder correction statistics/general purpose I/O 27                                               |  |

| DM_CE_0          | 96  | 0                   | external memory chip-select Bank 0                                                                         |  |

| CL1/GPIO28       | 97  | В                   | clock output for sampling channel decoder telemetry outputs/general purpose $\ensuremath{\mathrm{I/O}}$ 28 |  |

| GPIO29           | 98  | В                   | general purpose I/O 29                                                                                     |  |

| VSSP2            | 99  | Р                   | digital ground 2 to periphery (pads)                                                                       |  |

| RESET            | 100 | IUH                 | power-on reset (active LOW)                                                                                |  |

| VDDP2            | 101 | Ρ                   | digital supply voltage 2 to periphery (pads)                                                               |  |

#### One chip CD audio device with integrated MP3/WMA decoder

**SAF784x**

#### Table 2. Pin description ...continued

All digital inputs and bidirectional pins are 5 V tolerant.

| Symbol       | Pin | Type <sup>[1]</sup> | Description                                                |

|--------------|-----|---------------------|------------------------------------------------------------|

| DM_CE_1      | 102 | 0                   | external memory chip-select Bank 1                         |

| INT1         | 103 | IUH                 | external interrupt 1                                       |

| DM_DATA_0    | 104 | В                   | external memory data input/output bit 0                    |

| VSSD3        | 105 | Р                   | digital core ground 3                                      |

| VDDD3        | 106 | Р                   | digital core supply voltage 3                              |

| EF           | 107 | 0                   | C2 error flag                                              |

| DM_DATA_1    | 108 | В                   | external memory data input/output bit 1                    |

| DATA         | 109 | 0                   | serial data output                                         |

| DM_DATA_2    | 110 | В                   | external memory data input/output bit 2                    |

| WCLK         | 111 | 0                   | word clock output                                          |

| DM_DATA_3    | 112 | В                   | external memory data input/output bit 3                    |

| SCLK         | 113 | 0                   | serial clock output                                        |

| DM_DATA_4    | 114 | В                   | external memory data input/output bit 4                    |

| SYNC         | 115 | 0                   | EFM frame synchronization                                  |

| DM_DATA_5    | 116 | В                   | external memory data input/output bit 5                    |

| V4/CL16      | 117 | В                   | versatile pin 4/clock output 16.9344 MHz                   |

| DM_DATA_6    | 118 | В                   | external memory data input/output bit 6                    |

| TDI          | 119 | IU                  | JTAG1/2 test data input                                    |

| DM_DATA_7    | 120 | В                   | external memory data input/output bit 7                    |

| TMS          | 121 | IU                  | JTAG1/2 test mode select                                   |

| DM_DATA_8    | 122 | В                   | external memory data input/output bit 8                    |

| ТСК          | 123 | IDH                 | JTAG1/2 test clock                                         |

| DM_DATA_9    | 124 | В                   | external memory data input/output bit 9                    |

| TRST         | 125 | IU                  | JTAG1/2 asynchronous reset (active LOW)                    |

| DM_DATA_10   | 126 | В                   | external memory data input/output bit 10                   |

| TDO          | 127 | 0                   | JTAG1/2 test data output                                   |

| DM_DATA_11   | 128 | В                   | external memory data input/output bit 11                   |

| ARM_JTAG_SEL | 129 | I                   | select ARM JTAG (active HIGH) or general JTAG (active LOW) |

| DM_DATA_12   | 130 | В                   | external memory data input/output bit 12                   |

| RTCK/GPIO30  | 131 | В                   | JTAG clock output/general purpose I/O 30                   |

| DM_DATA_13   | 132 | В                   | external memory data input/output bit 13                   |

| DEV_ROM      | 133 | ID                  | development ROM select (LOW = internal ROM)                |

| DM_DATA_14   | 134 | В                   | external memory data input/output bit 14                   |

| VSSD4        | 135 | Р                   | digital core ground 4                                      |

| VDDD4        | 136 | Р                   | digital core supply 4                                      |

| DM_DATA_15   | 137 | В                   | external memory data input/output bit 15                   |

| MOTO1        | 138 | 0                   | motor output 1                                             |

| MOTO2        | 139 | 0                   | motor output 2                                             |

| VSSP3        | 140 | Р                   | digital ground 3 to periphery (pads)                       |

| VDDP3        | 141 | Р                   | digital supply voltage 3 to periphery (pads)               |

SAF784X\_2 Product data sheet

#### Table 2. Pin description ... continued

All digital inputs and bidirectional pins are 5 V tolerant.

| in algebra of all a second a second a |     |                       |                   |

|---------------------------------------|-----|-----------------------|-------------------|

| Symbol                                | Pin | Type <mark>[1]</mark> | Description       |

| RA                                    | 142 | 0                     | radial actuator   |

| FO                                    | 143 | 0                     | focus actuator    |

| n.c.                                  | 144 | -                     | not connected pad |

[1] See Table 3 for pin type definition.

| Table 3. | Pin type definition                         |

|----------|---------------------------------------------|

| Туре     | Definition                                  |

| AI       | analog input                                |

| AO       | analog output                               |

| AIO      | analog input/output                         |

| AIB      | analog input or bidirectional               |

| ID       | digital input with pull-down                |

| IDH      | digital input with pull-down and hysteresis |

| IU       | digital input with pull-up                  |

| IUH      | digital input with pull-up and hysteresis   |

| 0        | digital output, slew-rate limited           |

| В        | digital bidirectional, slew-rate limited    |

| Р        | power connection                            |

#### **Functional description 6**.

#### 6.1 Analog data acquisition

The input signals from the OPU photodiodes contain information used in the servo loops and the high frequency data from which the audio samples are reconstructed. The SAF784x contains all the necessary circuitry to process the photodiode signals directly and hence removes the need for a separate external diode signal preamplifier.

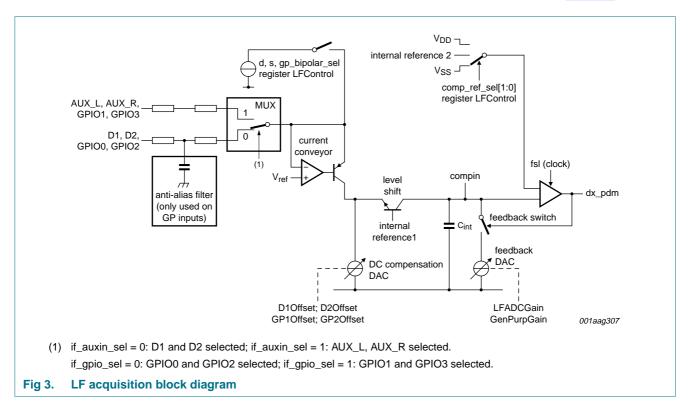

#### 6.1.1 LF acquisition

The LF signal path acquires the photodiode voltage signals and converts them into 4 MHz pulse-density modulated digital data streams. These streams are processed within the digital servo to control the focus, radial and sledge loops.

The servo processing makes use of the difference calculations D1 – D2, D3 – D4 and R1 – R2. Ideally these differences should be zero when the quantities D1 to R2 are equal due to the laser illumination. However in a practical system, errors reduce the accuracy of the signal processing. Two main forms of errors exist - DC offsets and relative gain mismatch between the difference channels.

The DC offsets are minimized in the SAF784x by DC-offset compensation circuitry which allows the DC present in the Pulse Density Modulation (PDM) streams to be measured when the laser is switched off, and then subtracted from the signals in the digital domain when the laser is on.

Relative gain mismatch is minimized by using carefully scaled circuitry in the time-continuous parts of the signal path, and by time-sharing circuitry in the time-discrete parts. A simplified block diagram of the LF acquisition path is shown in Figure 3.

The output of the OPU is converted to a current across the input resistor. The current conveyor provides a low input impedance and a high output impedance and sets a virtual earth at the end of the voltage-to-current converter to the same voltage as  $V_{ref}$  (1.6 V).

The level shifter acts as a summing node for the DC cancellation and produces a current that is referenced to an internal bias voltage which is independent of  $V_{ref}$ .

The output current charges an integration capacitor  $C_{int}$ . When the voltage reaches  $V_{DDA}$  / 2, the comparator switches and sends a feedback current that has opposite polarity to the input current which tries to discharge the capacitor.

The register LFADCGain defines the amount of feedback current and so sets the ADC gain. A PDM waveform appears at the output of the ADC, and is passed through a low-pass filter (in the digital domain). The average value at the output of the filter is in proportion to the voltage between  $V_i$  and  $V_{ref}$ .

Input signals from the OPU, GPIO inputs and the AUX inputs are routed to eight ADCs comprising six LF ADCs and two general purpose ADCs. ADCs LF1, LF2, GP1 and GP2 are shared by some of these inputs which are routed via an internal multiplexer. ADC LF1 is shared by input pairs D1, D2, and AUX\_L, AUX\_R via the multiplexer. ADCs LF3 to LF6 are dedicated to inputs D3, D4, R1 and R2 respectively. ADC GP2 is shared by input pairs GPIO0, GPIO2, and GPIO1, GPIO3 via the multiplexer. The internal multiplexer is controlled by register AuxandGPADCControl.

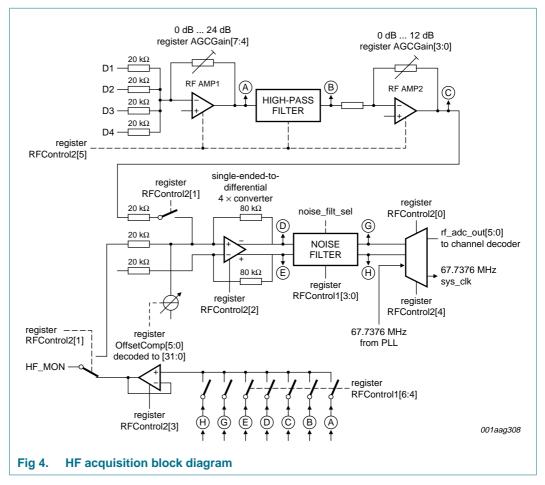

#### 6.1.2 HF acquisition

The HF data (EFM) signal is obtained by summing the signals from the three or four central diodes of the OPU and filtering and converting the signals to a digital representation via a 6-bit HF ADC. Figure 4 shows a simplified block diagram of the HF path.

The four diode signals D1, D2, D3 and D4 are summed in the first RF amplifier. The gain of the first amplifier is controlled by register AGCGain[7:4].

A second gain stage has been added to lessen the gain bandwidth requirements of a single gain stage operational amplifier and also to act as dynamic Automatic Gain Control (AGC). The gain of this amplifier is set by register AGCGain[3:0] and can be changed on-the-fly from the ARM microprocessor. The gain range accommodates 12 dB of gain needed to boost the signal when the laser tracks across a fingerprint defect on the disc.

CD-R, CD-RW, and finger prints, not only reduce the AC signal amplitude compared to a perfectly pressed disc but also reduces the DC pedestal voltage. The high-pass filter will remove all DC present at the input, but offsets will be added by the second and third gain stages. A 5-bit plus-sign DAC controlled by register OffsetComp[5:0] adds a current to compensate for this offset. The current reduces in linear dB steps and follows the AC gain.

To help users set up the correct gain and DC offset for each particular mechanism, an eye pattern monitor facility is included. This consists of a high frequency buffer amplifier whose input can be selected to monitor various important nodes within the analog RF path. The monitor point is controlled by register RFControl1[6:4] field RFMONSEL. The output of the buffer drives HF\_MON pin (pin 7). This register also controls the roll-off frequency of the noise filter which is in front of the 6-bit ADC in the RF path.

Various blocks within the analog RF path can be powered down if required, including the complete path. These power-down bits are controlled by register RFControl2[5:0].

In addition, the 6-bit RF ADC can be stand-alone tested in application mode, or a separate external RF path IC can be connected to SAA7834 by selecting bit 1 of register RFBypassSel. The input for the RF signal is then via pin HF\_MON. In this mode the central diode summing circuit, RF AMP1, high-pass filter and RF AMP2 are all bypassed.

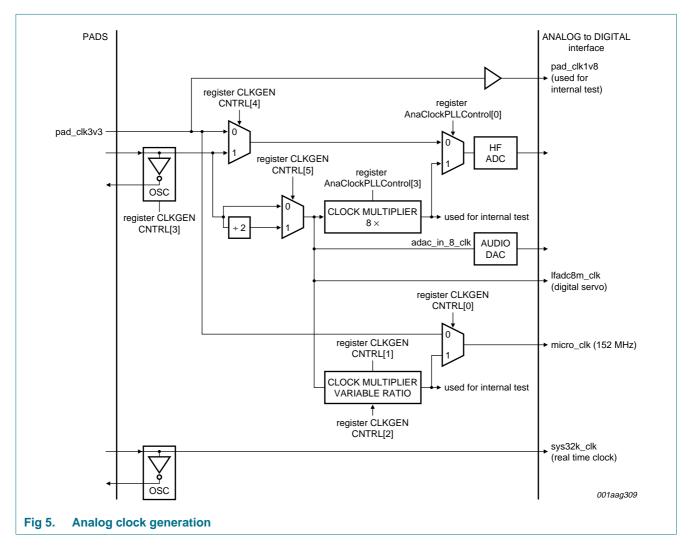

### 6.2 Analog clock generation

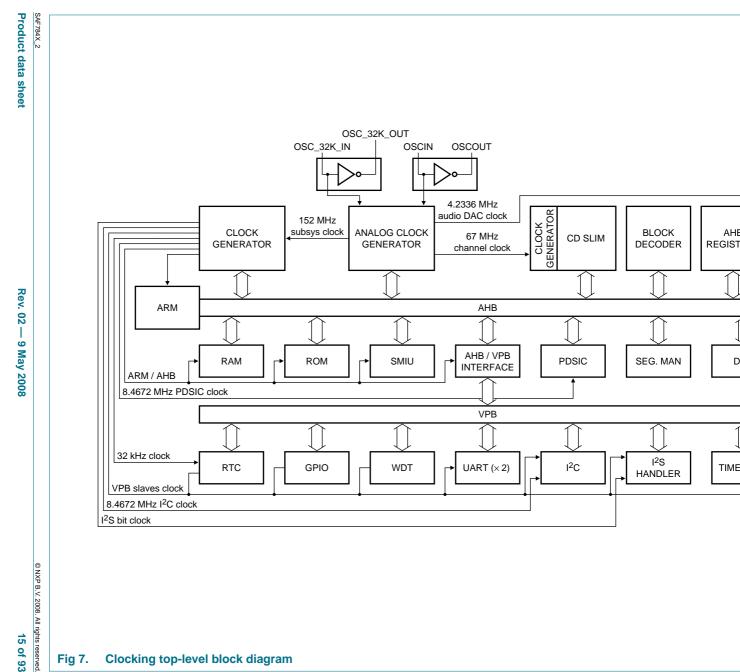

The SAF784x consists of two analog phase-locked loops. The 67 MHz PLL is dedicated to the channel decoder. The 152 MHz PLL is dedicated to the remaining functionality. The clock strategy for the SAF784x is intended to address areas that are prone to noise effects

that can decrease the quality of audio. The clocks related to audio DAC and LF ADC are generated directly from the analog signal, instead of being derived from high frequency PLLs. The clocking strategy for the digital core is shown in Figure 9.

### 6.3 General purpose analog inputs

The four general purpose ADC inputs, GPIO0 (pin 33), GPIO1 (pin 34), GPIO2 (pin 35), and GPIO3 (pin 36), can be used for giving the ARM microprocessor access to external analog sources, such as monitoring temperature and to provide simple resistor-ladder keypad functionality. These inputs use an additional pair of sigma-delta ADCs identical to those used for the LF diode inputs.

The general purpose analog inputs have separate interrupt request lines and use address space in the servo registers for storing the converted digital values. The output of the general purpose ADCs are low-pass filtered and can have fine-offset compensation added before being passed to a decimation filter. The digital values output from the decimation filter are then captured in the servo registers with a resolution of 10 bits per channel.

There are only two ADCs for general purpose application and so each ADC is multiplexed between two inputs: ADC1 between GPIO0 and GPIO2, and ADC2 between GPIO1 and GPIO3. GPIO2 and GPIO3 inputs are selected by signal AuxControlandGPADC.

### 6.4 Auxiliary analog inputs

Analog inputs, AUX\_L and AUX\_R, are available, and have sufficient resolution, for the input of external audio sources, such as allowing ARM access to an external audio source for sound processing algorithms. This allows audio processing of external audio sources via the AUX pins, whilst simultaneously using the general purpose inputs for keyboard and temperature inputs.

Since these two inputs share one pair of the LF sigma-delta ADCs used in the LF path (for inputs D1 and D2) a multiplexer is used to control the data source into the ADCs. Therefore, D1 and D2 cannot be used at the same time as AUX\_L and AUX\_R. This path is designed for a tuner input where the THD specification is ~0.3 % and the S/N is < 60 dB. These performance values are lower than when the normal CD audio path is used i.e. S/N > 80 dB and THD < 0.01 %.

The audio data is converted to a pulse-density modulated digital stream for both input channels. This data is then low-pass filtered and decimated to produce 10-bit representations of the analog inputs.

The auxiliary inputs differ from the general purpose analog inputs because the parallel data is converted to an  $I^2S$  format stream and then sent to the  $I^2S$  handler block to make the data available to the ARM microprocessor. The  $I^2S$  handler contains a 12-deep data FIFO which allows the ARM microprocessor to service the audio data with a lower priority than it would need if it were directly registered; see Figure 6.

# SAF784x

#### One chip CD audio device with integrated MP3/WMA decoder

Fig 7. Clocking top-level block diagram

15 of 93

### 6.5 Channel decoder

#### 6.5.1 Features

The channel decoder in the SAF784x is derived from the design used in the SAA7817HL DVD decoder IC. The design has been optimized for CD decode functionality (EFM and demodulation is removed) and has the following features:

- One-channel interface to the on-chip 6-bit 67 MHz ADC

- Signal conditioning logic with high-pass filter, DC-offset cancellation (AOC) and AGC logic

- HF defect detection circuitry with automatic hold of AGC, AOC, HPF, PLL and slicer on defect detection

- Digital equalizer, noise filter, PLL and slicer

- Run Length 2 (RL2) push back mechanism

- EFM demodulator with sync interpolation

- CD text and subcode Q-channel extraction blocks with software interface via registers

- Decoding, de-interleaving and Reed-Solomon error correction according to CD CIRC standards

- On-chip de-interleaving SRAM memory

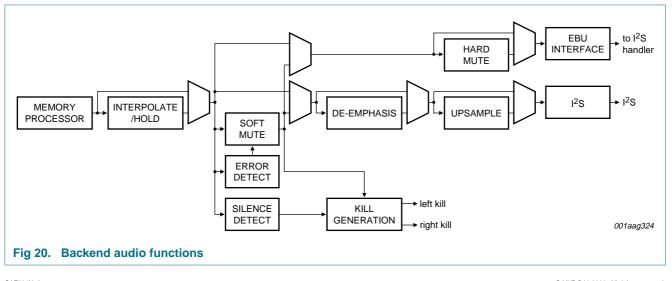

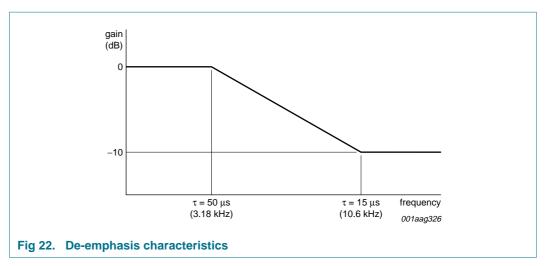

- Audio processing back end with interpolate/hold, mute, kill and silence detect logic, de-emphasis and 4× upsample filter

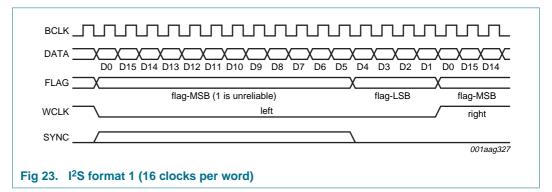

- Two data output interfaces: I<sup>2</sup>S and EBU

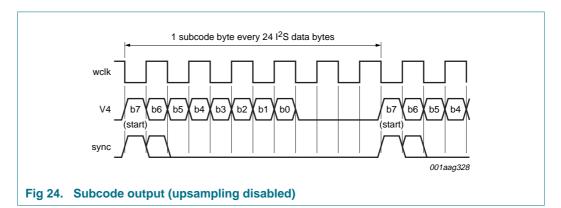

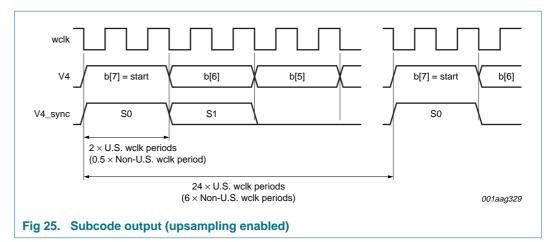

- One serial subcode output interface (V4)

- Motor control for CLV (locked-on EFM) or CAV (locked-on tacho) or open loop or software-controlled regulation with one or two motor pins

- On-board tacho measurement with one or three Hall sensor inputs (T1 to T3), that provides frequency input for motor loop; the sensor inputs are shared with GPIO pins

- 8-bit register map, with AHB slave interface

- An interrupt output with associated interrupt, status and interrupt enable registers for full interrupt-driven operation

- Debug information available via Meas1 (CL1, pin 97) and pin CFLG (pin 95) and parallel debug bus

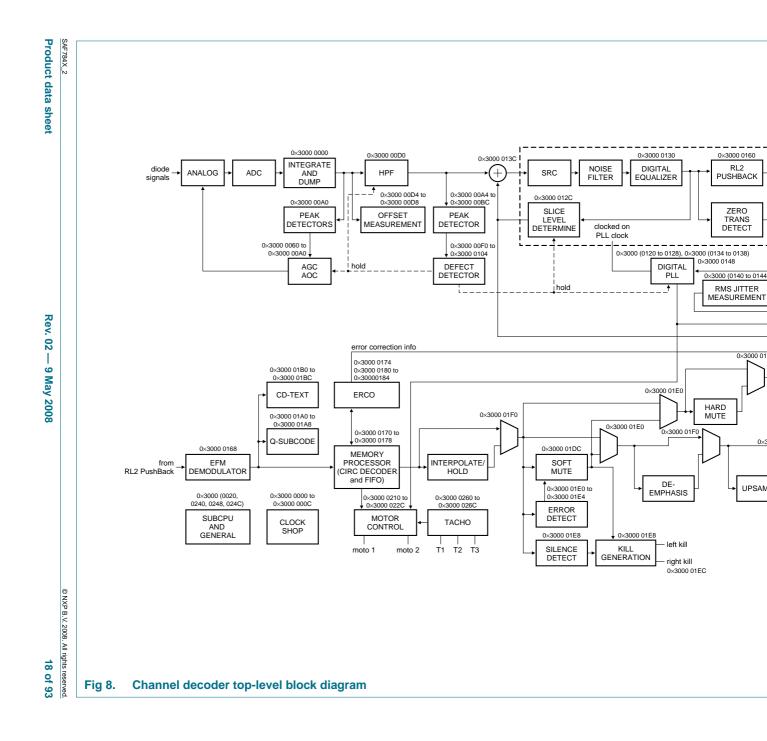

#### 6.5.2 Block diagram

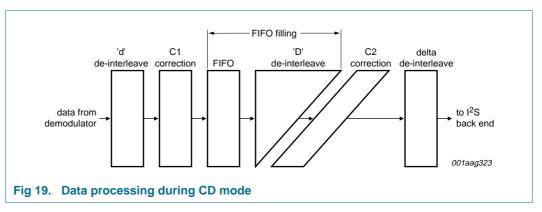

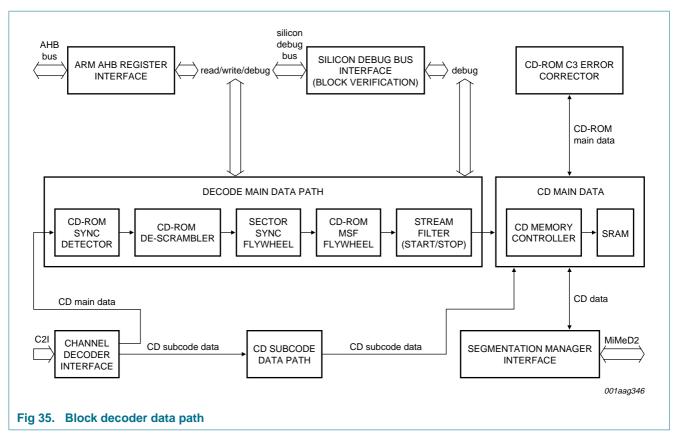

The incoming diode signals are first added and processed in the analog front end to create a normal RF (HF) signal and then converted to digital by the ADC. This signal is then resampled from the ADC clock to the system clock domain via the integrate-and-dump block. Offset and gain on the RF signal is removed via the AGC/AOC loop (via the analog front end). Any remaining offset which is not removed by the analog front end can be removed via the digital HPF. The RF signal is then sliced by the bit detector, clock recovery is done by a full digital PLL with noise filter, equalizer and sample-rate convertor. A defect detector allows AGC, AOC, HPF, slicer and PLL to be held during black or white dots. At this point in the data path, RF samples are converted into a bit stream. The RL2 push back avoids RL3s in the RF being accidently translated into RL1 or RL2 in the bit stream. The channel bit stream is demodulated in to bytes by the EFM demodulator. Q-channel subcode and CD-text information is extracted via the Q-subcode

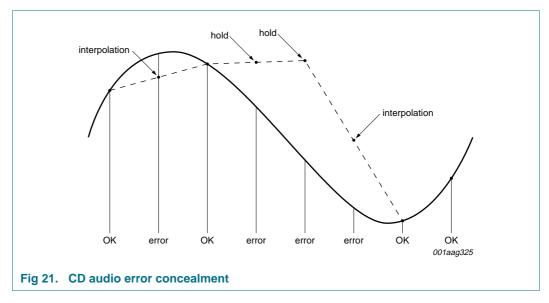

and CD-text decoder, available for readout through the sub-CPU interface. The main data stream is error-corrected by the ERCO, while the memory processor takes care of the CIRC de-interleaving and buffering of data in a FIFO. At the back end of the channel decoder, corrupted audio samples can be interpolated and held, while a burst of errors can trigger the mute block. Detection of digital silence can be used to kill the internal or external audio DAC. Pre-emphasis on the audio disc can be removed via the de-emphasis filter, and the data can be 4× upsampled before it is sent to the audio DAC. CD data is output via the I<sup>2</sup>S and/or the EBU outputs. Motor control can be frequency-regulated to the incoming RF bit rate, with additional phase regulation by FIFO filling, or it can be fully controlled via software. This method guarantees CLV support. A tacho measurement block is also available. The motor can also be regulated by the tacho frequency which allows possible CAV support.

Debug information is available via registers, via the dedicated serial lines Meas1 and Cflg.

The ARM AHB address of registers that control specific logic are shown next to each functional block in Figure 8.

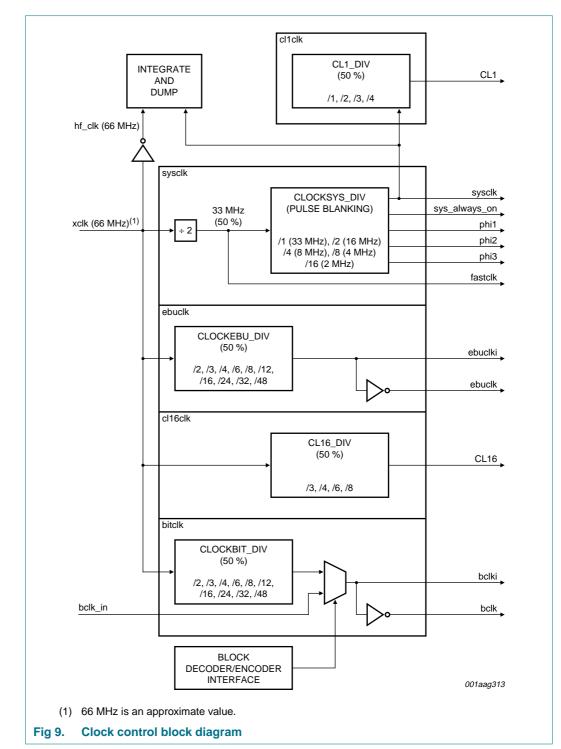

### 6.5.3 Clock control

The clock control block defines the clock frequencies for four clock domains.

- xclk: most internal clocks are derived from the crystal clock. This clock is the output of the clock multiplier in the analog part and has a fixed frequency of 67.7376 MHz

= 8.4672 MHz (f<sub>xtal</sub>) × 8. If a 16 MHz crystal is used, the crystal clock is divided by 2 inside the analog block. Crystal selection is done via AnalPLLControl bit SEL16.

- sysclk domain: the system clock, or its derivatives, runs the main part of the internal channel decoder. The sysclk is derived from xclk divided by 2 (50 % duty cycle) and can be further divided down via register SysclockConfig bit SYSDIV. This register also allows the majority of clocks to be powered down (for Sleep mode). The choice of the sysclk frequency f<sub>clk(sys)</sub> in an application is determined by the expected input bit rate f<sub>bit</sub> of the RF bit stream. The relationship between this incoming bit stream frequency and the system clock frequency f<sub>clk(sys)</sub> is expressed by the ratio f<sub>bit</sub> / f<sub>clk(sys)</sub>. There are two limiting factors:

- The HF-PLL operating range is between  $0.25 \times (f_{bit} / f_{clk(sys)})$  and  $2 \times (f_{bit} / f_{clk(sys)})$

- The decoder and error corrector throughput rate is limited to  $1.7 \times (f_{bit} / f_{clk(sys)})$

- This brings the constraint to  $0.25 < f_{bit} / f_{clk(sys)} < 1.7$ .

- bitclk domain: runs the I<sup>2</sup>S back-end logic. The bit clock (bitclk) is also output as part of the I<sup>2</sup>S interface. In audio slave mode this clock must be programmed to be exactly 44100 Hz × 2 × 16/24/32 (depending on I<sup>2</sup>S mode), to get a 1× data rate to the audio DAC. In master mode with gated bitclk, the bitclk must be programmed to be at a higher rate than the outgoing bit rate required for the disc speed, to avoid FIFO overflow in the decoder. For example, at N = 1, the incoming RF bit rate = 4.3218 MHz, which corresponds to an output bit rate of 1.4112 MHz. This means that the bitclk frequency is above 1.4112 MHz and is high enough when I<sup>2</sup>S-16 is chosen, while I<sup>2</sup>S-32 requires the bitclk to be at least 2.8224 MHz. The bitclk division is selected via register BitClockConfig. Also, bitclk gating can be enabled via the same register.

- ebuclk domain: runs the EBU back end. The EBU (or S/PDIF) interface is only enabled during audio slave mode. The ebuclk needs to be exactly 44100 Hz × 64 = 2.8224 MHz for 1× operation. The ebuclk division is selected via register EBUClockConfig.

The following clocks are also controlled by the clock control block:

- The hf\_clk is fixed at 67.7376 MHz, and is used to clock-in the samples from the ADC, which is clocked by the xclk with the same clock frequency

- The bclk\_in is the incoming I<sup>2</sup>S bit clock, which is used when I<sup>2</sup>S is programmed to receive bclk rather than transmitting it (programmed via register I2SConfig)

- The cl1clk can be used to monitor the Cflg and Meas1 debug lines. The frequency can be programmed via register CLClockConfig

- The cl16clk can be used to clock an external audio DAC or audio filter IC. The frequency can be programmed via register CLClockConfig

#### 6.5.4 Decoder-ARM microprocessor interface

The decoder core is internally connected to the ARM core via the AHB interface for register access to the decoder internal configuration registers.

#### 6.5.4.1 Programming interface

Decoder registers are programmed through the AHB interface. The programming interface is not fully described in this document.

For the application, it should be noted that the interface supports 32-bit registers, while the decoder only contains 8-bit registers. Therefore, the decoder registers are treated as 32-bit registers of which the 24 MSBs are not used.

The register address map occupied by the decoder goes from relative address 0x3000 0000 to address 0x3000 0374, and can be split into two parts:

0x3000 0000 - 0x3000 024C: the decoder's own registers - used to configure the channel decoder, and the functionality they control is described in detail in this section.

0x3000 02A0 - 0x3000 0374: the decoder immigrant registers - used to control parts of the SAF784x that do not have their own AHB interface (they are not used to control the decoder channel decoder).

#### 6.5.4.2 Interrupt strategy

The channel decoder contains two interrupt status registers: InterruptStatus1 contains all interrupts that operate as set/reset latches (set by hardware, reset by reading from the register). InterruptStatus2 contains all interrupts that operate as feed-throughs (set by hardware, reset by hardware or by accessing other registers).

Each interrupt bit can be enabled or disabled separately by writing to its corresponding enable bit in the InterruptEnable1 and InterruptEnable2 registers. If one or several interrupt bits are set and at least one is enabled, the interrupt line of the decoder to the microcontroller will go active (LOW). If an interrupt bit is disabled (enable bit turned off), it is prevented from activating the interrupt line to the microcontroller. However, this mode allows the interrupt to be processed if the status register is polled instead of interrupt handling by the microcontroller.

#### 6.5.5 EFM bit detection and demodulation

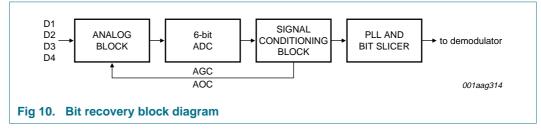

A block diagram of the bit recovery is shown in Figure 10.

The HF signal comprises the four diode inputs inside the analog block. It is pre-processed (LPF, HPF, offset removal and gain adjustment) and then sampled by a 6-bit ADC.

On the sampled HF, bit recovery is done by means of a full digital PLL and slicer.

Before the sampled signal enters the PLL section, it is pre-processed by a signal conditioning block. This consists of an integrate-and-dump block, a high-pass filter and logic available for gain control and offset control on the RF signal in the analog section.

For good playability on defects, a defect detector puts the PLL, the slicer, the AGC, the offset cancellation and the high-pass filter into hold during defects.

The detected bits are then sent to the demodulator for sync extraction and EFM demodulation. For playing on damaged or out-of-specification discs, flywheels are in place to make the sync extraction more robust.

#### 6.5.5.1 Signal conditioning

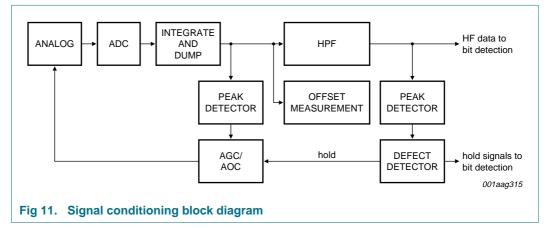

This device has a number of blocks which process the incoming 6-bit HF signal.

- Integrate-and-dump block to adapt the frequency of the ADC to the system clock

- Peak detection logic for amplitude measurement

- Peak detection logic for DC-offset measurement

- Digital high-pass filter with configurable cut-off frequency

- DC and gain control logic for on-board variable gain and offset control (in the analog section)

- A defect detector

All blocks can be configured under microprocessor control.

**Integrate-and-dump block:** the ADC delivers one sample every xclk period (= one sample every hf\_clk period). The sample rate needs to be adapted from this xclk rate to the lower sysclk rate. For more information on sysclk speed, see <u>Section 6.5.3 on</u> page 19. The integrate-and-dump block converts the incoming samples at the hf\_clk frequency into a stream of one sample per sysclk period. It converts an average of a number of samples to achieve this. If the division factor for the system clock is /2, /4, /8, /16, /32, an average of 2, 4, 8, 16 or 32 incoming samples respectively, is taken and passed further. This results in a gain in the number of effective bits of the A-D conversion.

**High-pass filter:** A 1st-order IIR high-pass filter with a variable 3 dB point is implemented to filter out the remaining DC jump-on defects. Most of these defects will have been filtered by the analog HPF. The cut-off frequency of the digital high-pass filter can be changed on-the-fly, by writing to register HighPassFiltCont.

It is possible to reset the state of the high-pass filter via bit 6 of register HighPassFiltCont. The input and the output of the high-pass filter are 8-bits wide.

The high-pass filter is implemented in a '1 minus low pass' structure. It is possible to hold the low-pass filter on defects. For more information, see <u>Section "Defect detector" on page 26</u>.

SAF784x

The high-pass filter works on the system clock. Its bandwidth is also proportional to the sysclk.

A formula for approximating the cut-off frequency (f<sub>c</sub>), of the high-pass filter is:

$$f_{c, HPF} = \frac{HPSet[5:0]}{2\pi \times 2^{II}} \times f_{clk(sys)}$$

(1)

Peak Detectors: The signal conditioning block has two types of peak detector:

- peak detector with decay filter: works on an immediate attack/slow-decay basis, and is used for measuring peaks, amplitude and offset, read by software which sends peak information to the defect detector.

- peak detector based on window: works on the principle of detecting maximum and minimum peaks within a window, and is used for the AGC and AOC control logic.

Both peak detectors monitor the RF after it has passed an optional noise filter. This noise filter is a LPF with a programmable high cut-off frequency. This bandwidth is programmed via register PDBandwidth bit NOISEFILTERBW for the noise filter before the peak detectors of AGC/AOC and measurement read back. The defect detector peak detector has its own noise filter which is programmed via register DefectDetPeakBW bit NOISEFILTERBW.

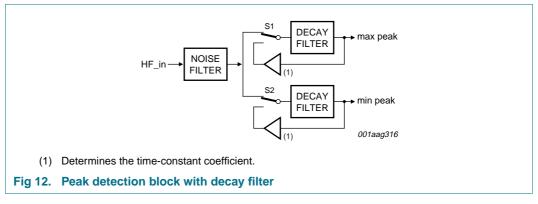

**Peak detector with decay filter:** The functional schematic of this peak detector is shown in Figure 12.

The maximum and minimum peaks of the incoming signal are measured at the inputs of switches S1 and S2 respectively. The maximum and minimum peak signal paths both have a decay filter with a long time-constant and matching bandwidth. The maximum peak decay filter responds to the smallest value possible. The decay filter for the minimum peak responds to the largest value possible.

The decay bandwidth of the measurement readback decay filter is controlled by register PDBandwidth bit DECAYBW, the bandwidth of the defect detector is controlled via register DefectDetPeakBW bit DECAYBW.

The following settings of the decay filters are possible:  $C = 1 - 2^{-m}$ , for m = 6 to 21, where

C = time-constant coefficient, m = DecayBW[3:0] + 6.

The bandwidths and corresponding time-constant (t) of the decay filter are shown in Table 4, when the system clock frequency  $f_{clk(sys)}$  is 10 MHz.

|   | Doody mile. |    |          |    |          |    |          |

|---|-------------|----|----------|----|----------|----|----------|

| m | t           | m  | t        | m  | t        | m  | t        |

| 6 | 6.35 μs     | 10 | 102.4 μs | 14 | 1.64 ms  | 18 | 26.21 ms |

| 7 | 12.75 μs    | 11 | 204.7 μs | 15 | 3.28 ms  | 19 | 52.43 ms |

| 8 | 25.55 μs    | 12 | 409.6 µs | 16 | 6.55 ms  | 20 | 104.8 ms |

| 9 | 51.15 μs    | 13 | 819.2 μs | 17 | 13.11 ms | 21 | 209.7 ms |

| Table 4. | Decay filter time-constants at f <sub>clk(sys)</sub> = 10 MH | z |

|----------|--------------------------------------------------------------|---|

|----------|--------------------------------------------------------------|---|

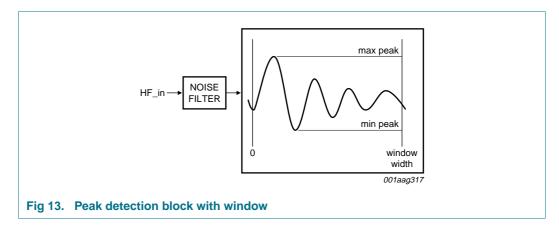

**Peak detector based on window:** The functional schematic of this peak detection is shown in Figure 13.

The minimum and maximum peaks of the incoming signal are measured during a programmable window period. The highest and lowest sample within this window are used to update maximum and minimum peaks.

The window width of the measurement is controlled via register AGCAOCControl bit PDMEASWINDOW.

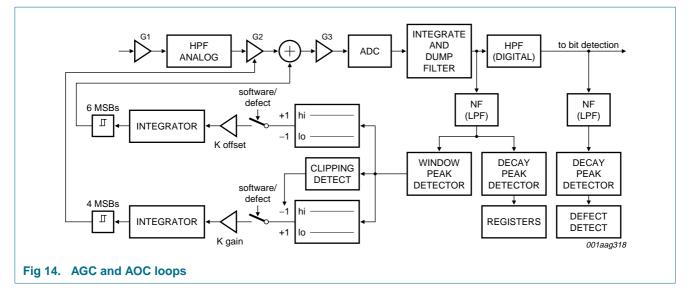

AGC and AOC control block: The AGC control block controls the RF amplitude at the input of the ADC by controlling the gain of an on-chip analog gain amplifier. The AOC control block controls the RF offset at the input of the ADC by adding or subtracting the offset just before the ADC. Both AGC and AOC loops are built up in the same manner and are shown in Figure 14 in their relative position within the signal conditioning block.

# SAF784x

#### One chip CD audio device with integrated MP3/WMA decoder

The maximum and minimum peaks on the envelope of the RF signal after the ADC are first measured via a noise filter and the window peak detector (see <u>Section "Peak</u> <u>Detectors" on page 23</u>. The amplitude is then calculated as maxpeak – minpeak, and the offset as (maxpeak + minpeak) / 2.

For tuning the loops, it is possible to read back the HFMaxPeak, HFMinPeak, HFAmplitude and HFOffset, as measured from their registers by the decay peak detector.

**AGC control:** The RF amplitude at the ADC input can be changed with two gain amplifiers in the analog part: G1 (fixed) and G2 (dynamic). G1 has a gain range from 0 dB to 24 dB in 16 steps of 1.6 dB, while G2 has a range from 0 dB to 12 dB in 16 steps of 0.8 dB. Both gains can be programmed via register AGCGain. G1 will stay fixed, while G2 can be regulated by hardware when the AGC is turned on.

The AGC will regulate the gain such that the measured amplitude stays between a programmed upper threshold (AGCThrHi) and lower threshold (AGCThrLo). If the amplitude is smaller, gain will increase; if the amplitude is too large, gain will decrease. When clipping is detected on either one or both sides, the gain will decrease. These gain changes are not sent to the analog gain amplifier directly but are integrated over time. Only if, on average, a gain increase or decrease is requested, will this result in a real gain increase or decrease of the amplifier. This can also be read back via register AGCGain. The AGC, together with the noise filter on the peak detector, prevents RF noise causing over-sensitive gain regulation. To further reduce sensitive behavior, a hysteresis window with a width of one gain step is added between the integrator and amplifier G2. The bandwidth of the gain loop determines how fast it reacts to fingerprints and scratches; it is programmed via register AGCIntegBW. It is also possible to limit the range of G2 by programming a maximum and minimum boundary by register AGCGainBound.

**AOC control:** Most of the RF offset at the ADC input will be removed by the analog HPF (1st-order HPF with 3 dB point around 3.6 kHz). The remaining offset (mainly introduced by the analog front end), can be removed by adding or subtracting a fixed offset in the analog part. This offset subtraction/addition has a range of 32 steps in each direction, with approximately 1.4 LSBs per step (referenced to the RF ADC). This leads to a full

correction range of  $\pm$  42 LSB steps (more than the whole ADC range). This offset compensation (offset comp) value can be programmed via register OffsetComp, and will be regulated in hardware as soon as the AOC is turned on.

The AOC will regulate the offset comp value such that the measured offset stays within a window programmed by register OffsetBound. The offset comp value decreases if the offset is above this window, and increases if the offset is below the window. If an inversion occurs on the RF signal between analog and digital, the reaction of this loop can be inverted by programming OffsetBound bit OFFSETINV.

The offset changes are not sent to the analog offset subtraction directly, but are integrated over time. Only if, on average, an offset increase or decrease is requested, this will result in a real offset increase or decrease of the analog addition. This can also be read back via register OffsetComp. The AOC, together with the noise filter on the peak detector, prevents RF noise causing over-sensitive offset regulation. To further reduce sensitive behavior, a hysteresis window with a width of one offset step has been added between the integrator and offset comp value. The bandwidth of the offset loop will determine how fast it reacts to fingerprints and other defects; it is programmed via register OffsetIntegBW. It is also possible to limit the range of the offset comp value by programming a maximum and minimum boundary by register OffsetCompBoundHi and OffsetCompBoundLo.

AGC/AOC general and rules-of-thumb: The AGC and AOC hardware regulation loops can be enabled or disabled separately via register AGCAOCControl. This register also allows the use of a 'slow' AGC and/or AOC loop. In this case the programmed loop bandwidth is decreased with an extra factor of 128. In this mode the loops will be too slow to react to defects, but can be used for a slow software-like gain and/or offset regulation to regulate the average gain and offset over the disc comfortably within a specified range.

An important feature is the AGCAOCControl bit DISHOLDNOLOCK, which disables holding of the AGC and AOC loops during defects (triggered by the defect detector, see <u>Section "Defect detector" on page 26</u> while the HF PLL is not in lock. This feature avoids permanent lockups of the loops caused by a small amplitude triggering the defect detector, which in return would hold the AGC loop.

The following things should be taken into account as general 'rules-of-thumb':

- The amplitude thresholds should not be programmed too close to each other: allow at least two gain steps (1.6 dB) from lower to higher boundary and vice versa to avoid an over-sensitive AGC.

- The offset boundary should not be programmed too tight: ± 8 is a good value to avoid an over-sensitive AOC.

The bandwidth of the loops should never be programmed to be too wide ('fast') with respect to the peak detector measurement window, to avoid an unstable loop. If the PDwindow =  $2^n f_{clk(sys)}$  (Hz) wide, the bandwidth of the loops should never be higher than  $2^{-(n+1)}$  (Hz).

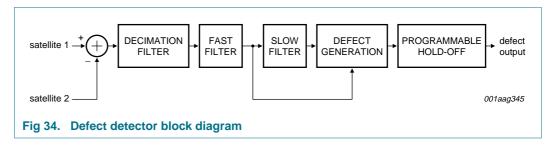

**Defect detector:** The defect detector detects the presence of black or white dots in the RF stream, and freezes some signal conditioning and bit recovery logic during these defects. This prevents the control loops inside this logic drifting away from their optimal point of operation when there is no RF present, so that they can recover very fast when good RF is present again.

The detection of a defect is based on amplitude. The amplitude is measured via a set of peak detectors with decay, as described in <u>Section "Peak Detectors" on page 23</u>. The decay bandwidth and noise filter bandwidth are programmed by register DefectDetPeakBW.

Two thresholds can be programmed. A low threshold will trigger a 'defect-detected' signal as soon as amplitude goes below this threshold. A high threshold will clear this 'defect-detected' signal again as soon as amplitude goes above this threshold. Together, these thresholds apply a hysteresis to the defect detection, avoiding a jittery 'defect-detected' signal (having many on/off parts) when the amplitude is at the threshold edge. Thresholds are programmed in register DefectDetThres.

The 'defect-detected' signal can be used to hold the PLL, slicer, AGC, AOC and HPF during a defect. The feature(s) that will be held can be programmed in register DefectDetEnables. The same register can be used, via software, to force the PLL, slicer and HPF to hold. The AGC and AOC can be held in software by just disabling the loops in register AGCAOCControl.

Two special features exist on the defect detector:

- Optional delay of the enabling and disabling of hold features at the beginning and end of a defect. This can be done by programming a start and/or stop delay (in number of sysclks) via register DefectDetStartStopDelay. Whenever the defect detector detects the start of a defect, it will wait for the start delay before triggering a 'defect-detected processed' signal. When the defect detector detects the end of a defect, it will wait for the programmed stop delay before clearing the defect-detected processed' signal again. This also means that defects which are smaller than the start delay are ignored, and that if the defect contains zones with good RF amplitude but smaller than the stop delay, they are also ignored. In reality, all hold features are triggered by the defect-detected processed' signal; at the decoder output, both delays are zero, so both signals are equal.

- Optional programmable time-window at the end of a defect, during which, higher PLL and/or slicer bandwidths can be used to speed up the recovery of these loops after a defect. This window can be programmed via register DefectDetHighBWDelay. Bandwidth programming is explained in Section 6.5.5.2 on page 28.

The detection of the beginning or end of a defect, with or without start and stop delays, can be used to generate an interrupt. See register InterruptEnable1.

#### 6.5.5.2 Bit detector

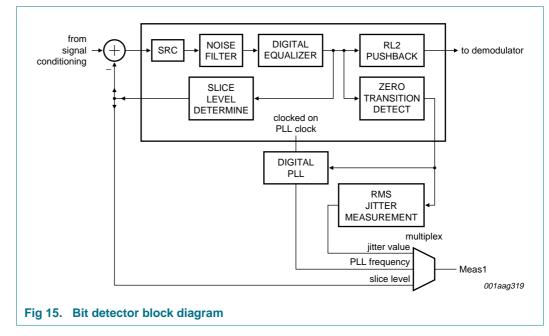

The bit detector block contains the slice-level circuitry, a noise filter to limit HF EFM signal noise contribution, an equalizer, a zero-transition detector, a run-length push-back circuit, a digital PLL and jitter measurement logic.

All processing is performed on the bit clock, and bandwidths are proportional to the channel bit rate. To achieve this, RF data is resampled from the system clock domain to the bitclk domain by making use of a sample-rate convertor. Blocks can be configured under microcontroller control and are described in detail in the next paragraphs.

**Noise filter:** The digital noise filter runs on the channel bit clock frequency  $f_{clk(bit)ch}$ . It limits the bandwidth of the incoming signal to  $\frac{1}{4}$  of the channel bit clock frequency.

Passband:  $0 \times f_{clk(bit)ch}$  to  $0.22 \times f_{clk(bit)ch}$  (Hz)

Stop-band:  $(0.28 \times f_{clk(bit)ch})$  to  $(f_{clk(bit)ch} - 0.28 \times f_{clk(bit)ch})$  (Hz)

Rejection: -28 dB

**Slice-level determination:** The slice-level determination circuit compensates for the incoming signal asymmetry component. Bandwidth of the slice-level determination circuit is programmable via register SlicerBandwidth. Also the higher bandwidths for use after a defect (see <u>Section "Defect detector" on page 26</u>) are programmed in this register. The bandwidth is proportional to the channel bit clock frequency. The slice level, or asymmetry, can be read back via register SlicerAssym.

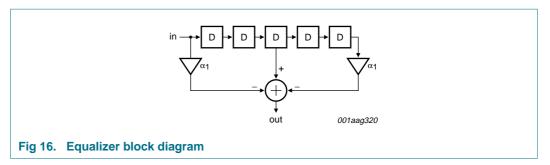

**Equalizer:** In the bit detection circuit, a programmable equalizer is used to boost the high frequency content of the incoming signal.

The equalizer includes an integral five-tap presentable, asymmetrical equalizer. The equalizer block diagram is given in Figure 16.

The first and last tap can be programmed via register PLLEqualiser.

**Usable EFM bit clock range:** The channel bit clock frequency  $f_{clk(bit)ch}$  must obey the following constraints in relation to the system clock frequency  $f_{clk(sys)}$ . The channel bit clock frequency must always be:

- less than  $f_{clk(sys)} \times 2$  (Hz)

- greater than  $f_{clk(sys)} \times 0.25$  (Hz)

Therefore the range is:  $f_{clk(sys)} \times 0.25 < f_{clk(bit)ch} < f_{clk(sys)} \times 2$  (Hz)

A reliable bit detection is only possible within this range. If the input channel bit rate is above  $f_{clk(svs)} \times 2$  then the PLL will saturate to twice the system clock frequency.

Note that while these are theoretical limits, a real-life application should have a safety margin. When the bit clock amplitude is relatively low, the internal filter will filter off more noise, yielding a better performance. If the theoretical upper limit is approached, playability (e.g. black dot performance) will drop significantly. The decoder will only be able to correct the biggest correctable burst error of 16 frames if  $f_{clk(bit)ch} < f_{clk(sys)} \times 1.7$  (Hz).

Taking this restriction on the decoder into account, the new range becomes:

$f_{clk(svs)} \times 0.25 < f_{clk(bit)ch} < f_{clk(svs)} \times 1.7$  (Hz)

**Digital HF PLL:** The digital PLL will recover the channel bit clock. The capture range of the PLL itself is very limited. To overcome this difficulty, two capture aids are present. When using automatic locking, the PLL will switch states based on the difference between expected distance and actual distance between synchronization.

Three different PLL operating modes exist:

- In-lock (normal operation): the PLL frequency matches the frequency of the channel bits with an accuracy error of less than 1 %

- Inner lock aid (capture aid 1): the PLL frequency matches the frequency of the channel bits with an accuracy error of between 1 % and 10 %

- Outer lock aid (capture aid 2): the PLL frequency is more than 10 % away from the channel bit frequency

The operation of PLL in-lock (normal on-track situation) is explained below followed by lock-detection and then the two capture aids.

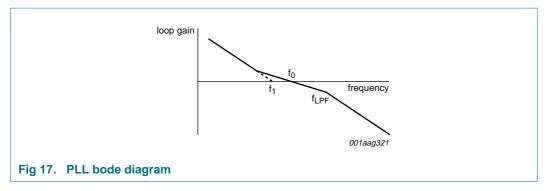

PLL in-lock characteristics: The PLL behavior during in-lock can best be explained in the frequency domain. PLL operation is completely linear during in-lock situations. The open-loop response of the PLL (bode diagram) is given in Figure 17.

f1: Integrator cross-over controlled via KI

f<sub>0</sub>: PLL bandwidth controlled via K<sub>P</sub>

f<sub>2</sub>: LPF bandwidth controlled via K<sub>F</sub>

The three frequencies are programmable using register PLLBandWidth. The higher bandwidths for use after a defect, are programmed in register PLLBandWidthHigh; see <u>Section "Defect detector" on page 26</u>.

When the PLL is in lock, the recovered PLL clock frequency equals the channel bit clock frequency.

**Detection of PLL lock:** The PLL locking state is determined by the distance between detected syncs. This means that the sync detection is actually controlling the automatic PLL locking.

The PLL switches from outer lock to inner lock when successive syncs are detected to be  $588 \pm 25$  channel bits apart. Internally this is also called a 'winsync' (sync falls in a wider window). The number of missed winsyncs is kept in a 3-bit confidence counter, and the PLL will go out of outer lock when seven consecutive out-of-window syncs are found.

The PLL switches from inner lock to in-lock when successive syncs are detected  $588 \pm 1$  channel bits apart. The number of consecutive missed syncs is kept in a bit counter, and saturates on either 16 or 61, depending on the value of bit LOCK[16] or [61] in register DemodControl. When the saturation level is reached, the PLL is set out-of-lock.

The PLL frequency (inner-) and phase (in-) lock status can be read out in register PLLLockStatus.

**PLL outer-lock aid:** The outer lock aid has no limitation on capture range, and will bring the PLL within the range of the inner lock aid. The PLL will first regulate its frequency based on detecting RL3s as the smallest possible RLs (fast-but-rough regulation), and next on detecting RL11s as the largest possible RLs (slow but more accurate).

**PLL inner-lock aid:** The inner-lock aid has a capture range of  $\pm$  4 %, and will bring the PLL frequency to the phase-lock point. It will regulate the PLL frequency such that 588-bits are detected between two EFM-syncs.

**Influencing PLL behavior:** Programmability and observer ability are built into the PLL mainly for debugging purposes, and also to make difficult applications possible. The PLL operation can be influenced in two ways:

- optional manual selection of the PLL state (in-lock, inner-lock, outer-lock, outer-lock with only RL3 regulation).

- optional pre-set of the PLL frequency to a certain value

**Overriding the PLL state:** PLL state can be:

- In-lock

- Inner lock

- Outer lock

- Outer lock with only RL3 regulation

- Hold

Normally, the PLL state is selected automatically by the lock detectors. However, the PLL lock state can be overruled via register PLLLockAidControl. When Lock mode is left at '0', the user can still choose the PLL state, but hardware will overwrite this if the hardware-selected PLL state is closer to locking the PLL.

#### Table 5.PLL lock states

| Lock mode | PLLLockControl | State <sup>[1]</sup>                                      |

|-----------|----------------|-----------------------------------------------------------|

| 0         | 0 0000         | automatic lock behavior                                   |

| 1         | 0 0001         | force HF PLL into in-lock                                 |

| 1         | 0 0110         | force HF PLL into inner-lock aid                          |

| 1         | 0 0100         | force HF PLL into outer-lock aid                          |

| 1         | 0 1000         | force HF PLL into hold mode                               |

| 1         | 1 0100         | force HF PLL into outer-lock aid with RL3 regulation only |

| x         | others         | reserved                                                  |

[1] During PLL hold, the PLL frequency will not change and the frequency preset may be used.

It is possible to pre-set the PLL frequency to a certain value by writing the integrator value of the PLL to register PLLIntegrator. The relationship between the bit frequency, the integrator value, and the sysclk frequency  $f_{clk(sys)}$  is given by:

$$f_{clk(bit)ch} = \frac{PLLFreq[7:0] + 4}{128} \times f_{clk(sys)} (Hz)$$

<sup>(2)</sup>

The real-time value of the PLL frequency can be read at the same address.

#### 6.5.5.3 Limiting the PLL frequency range

The range over which the PLL can capture the input frequency can be limited. The minimum and maximum PLL frequency can be set by bits MININTFREQ, and MAXINTFREQ respectively in register PLLMinMaxBounds.

#### 6.5.5.4 Run length 2 push-back detector

If this circuit is switched on, all run length one and two symbols (invalid run lengths) are pushed back to run length 3. For RL2s, the circuit will determine the transition that was most likely to be in error, and shift transition on that edge. This feature should always be turned on, but can be deselected via register RL2PushBack.

#### 6.5.5.5 Available signals for monitoring

The operation of the bit detector can be monitored by the microcontroller via an external pin. Five signals are available for measurement:

PLL frequency signal: The microcontroller monitors this signal by reading register PLLIntegrator.

Asymmetry signal: This signal is in 2's complement form and can be read from register SlicerAssym.

Jitter signal: A jitter measurement is done internally. The zero-crossing jitter value is available in register PLLJitter.

Internal lock flags.

#### Jitter signal:

Jitter measurement is done in two steps:

- 1. The distance between the EFM zero transition and the bit clock zero transition is measured.

- 2. The calculated jitter for the zero transition is averaged using a 10-bit low-pass filter. The top 8-bits of the filter output can be read back from register PLLJitter. To obtain the jitter in % of the channel bit clock, Equation 3 applies:

$$jitter = \sqrt{\frac{jitter[7:0] - 2.83}{1024}} \times 100 \ (\%)$$

(3)

#### Table 6. Jitter input calculation

| Distance (× f <sub>bit</sub> ) | Average distance (bit clocks) | Jitter filter input (5-bit decimal integer) |

|--------------------------------|-------------------------------|---------------------------------------------|

| < <sup>2</sup> / <sub>16</sub> | 1⁄16                          | 1                                           |

| $^{2}/_{16}$ to $^{4}/_{16}$   | <sup>3</sup> ⁄ <sub>16</sub>  | 9                                           |

| 4/16 to 6/16                   | <sup>5</sup> ⁄ <sub>16</sub>  | 25                                          |

| > <sup>6</sup> / <sub>16</sub> | 7⁄ <sub>16</sub>              | 49                                          |

This jitter measurement is also available via the Meas1 telemetry signal on pin CL1. The full 10-bit output of the filter is available via this pin; see <u>Section 6.5.5.8</u>.

It is also possible to read out an average jitter value via register PLLAverageJitter. This value is an average of the normal jitter value over a period of 8000 bit clock periods. The formula to transform this into a percentage is shown in Equation 4:

average jitter =

$$\sqrt{\frac{averagejitter[7:0] - 2.83}{1024}} \times 100 \ (\%)$$

(4)

#### 6.5.5.6 Use of jitter measurement

The jitter measurement is an absolute-reference jitter measurement. It gives the average square value of the bit detection jitter. Note that bit-to-clock jitter is measured. In this device, the bit-to-clock jitter is measured directly before the bit detection, and contains contributions due to various imperfections of the complete signal path:

• Disc

- Analog preamplifier

- ADC

- Limited bandwidths in this device

- Limited PLL performance

- Influenced by internal noise filter, asymmetry compensation and equalizer

The jitter measurement is absolute reference, because it relates directly to the EFM bit error rate if the disc noise is gaussian.

#### 6.5.5.7 Internal lock flags

The fourth signal that can be monitored are three flags in the PLLLockStatus register: the internally generated inner lock signal FLock, the internally generated lock signal InLock and a LongSym(bol) flag when run length 14 is detected (run length too high).

In automatic mode, the FLock and InLock flags determine what type of PLL capture aid is used.

|            |             | 40             |

|------------|-------------|----------------|

| FLock flag | InLock flag | Capture mode   |

| 0          | 0           | outer-lock aid |

| 1          | 0           | inner-lock aid |

| х          | 1           | in-lock        |

Table 7.

Determining the current PLL capture mode

#### 6.5.5.8 Format of the measurements signal Meas1 on pin CL1

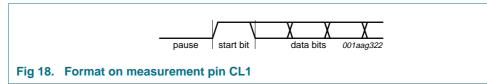

This signal is output via pin CL1 (pin 97) and comprises three measurement signals multiplexed together. The format is shown in <u>Figure 18</u> and <u>Table 8</u>.

The data is sent in a serial format. It consists of a pause, followed by a start bit, followed by data bits.

Bit length: four system clock periods; frame length: 64 bits.

#### Table 8. Data format on measurement pin CL1

| Bit        | Value                    | Description                                |

|------------|--------------------------|--------------------------------------------|

| 0          | '1'                      | start bit <sup>[1]</sup>                   |

| 1 to 10    | jitter(9) to jitter(0)   | first sample of jitter word <sup>[2]</sup> |

| 11         | '0'                      |                                            |

| 12         | '1'                      | intermediate start bit                     |

| 13 to 22   | pllfreq(9) to pllfreq(0) | PLL frequency word                         |

| 23         | '0'                      |                                            |

| 24         | '1'                      | intermediate start bit                     |

| 25 to 32   | asym(7) to asym(0)       | slicer level                               |

| 33, 34, 35 | '0'                      | '000'                                      |

|            |                          |                                            |

Table 8.

Data format on measurement pin CL1 ...continued

| Bit      | Value                  | Description                                 |

|----------|------------------------|---------------------------------------------|

| 36       | '1'                    | intermediate start bit                      |

| 37 to 46 | jitter(9) to jitter(0) | second sample of jitter word <sup>[2]</sup> |

| 47 to 63 | '0'                    | pause                                       |

- [1] The start bit is always preceded by 17 pause bits. The intermediate start bits at bit locations 12, 24 and 36 guarantee that no other '1' value is preceded by 17 '0' bits. This allows a simple start bit detection circuit.

- The jitter word is sampled twice in every frame.

The percentage jitter is calculated using Equation 5:

$$jitter = \sqrt{\frac{jitter[9:0] - 12.81}{4096}} \times 100 \ (\%)$$

(5)

#### 6.5.5.9 Demodulator

The demodulator block performs the following functions:

- EFM demodulation using a logic array

- Sync detection and synchronization

- Sync protection

#### 6.5.5.10 EFM demodulation

Each EFM word of 14 channel bits (which are separated from each other by three merging bits) is demodulated into one data byte making use of the standard logic array demodulation as described in the *CD Red Book (IEC 60908)*.

#### 6.5.5.11 Sync detection and synchronization

The EFM sync pattern is a unique pattern which is not used anywhere else in the EFM data stream. It consists of 24 bits: RL11 + RL11 + RL2. An internal sync pulse is generated when two successive RL11s are detected. A sub-sync pulse is produced when the beginning of a new subcode frame is seen. This is done by analyzing the subcode information: when two successive subcodes are subcode sync-code S0 and S1, sub-sync will be activated.

#### 6.5.5.12 Sync protection

The sub-sync pulse is protected by an interpolation counter, this counter uses the fact that a subcode frame is always 98 subcode symbols long.

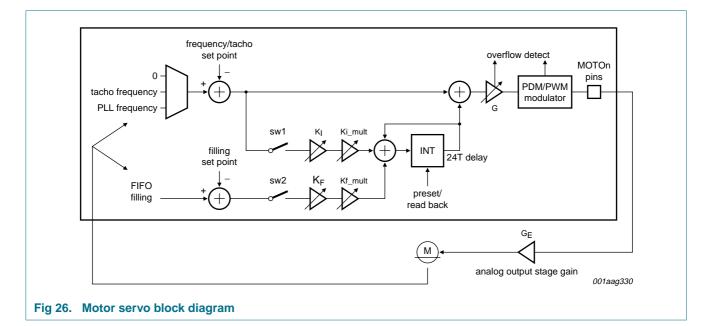

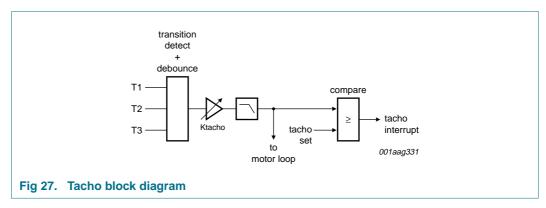

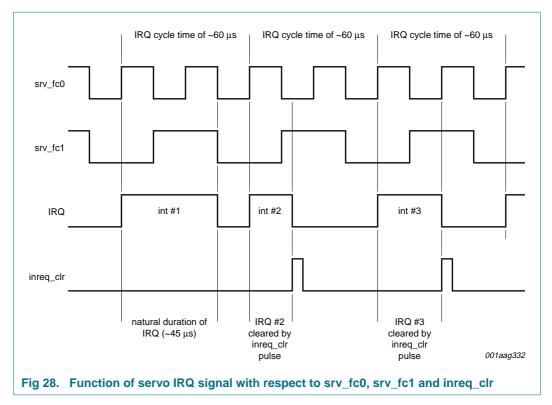

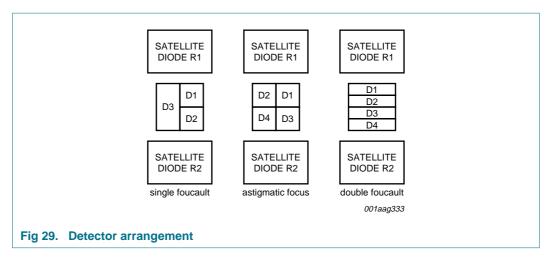

The sync signal itself is also interpolated. If after 33 data bytes (one EFM frame), no new sync is detected, it is assumed that the bit detector has failed to correctly produce it, and the sync signal is given anyway, this is generally called an 'interpolated sync.' Furthermore, if a new sync is detected in the data shortly after a previous sync signal, interpolated or real, no new sync signal will be produced, because this means the frame has 'slipped'. After enough data byte periods, the sync signals are allowed to pass again.