# AN11801

# TEA19161 and TEA19162 controller ICs

Rev. 2.1 — 7 April 2021

**Application note**

### **Document information**

| Information                                                                                                                                | Content                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Keywords TEA19161, TEA19162, PFC, burst mode operation, low-power mod by-cycle control, V <sub>cap</sub> control, resonant power converter |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| Abstract                                                                                                                                   | The TEA19161T and TEA19162T are a set of controller ICs for resonant power supplies that include a PFC.  To reach a high efficiency at all power levels, the TEA19161T(LLC) introduces a new operating mode: low-power mode. This mode operates in the power region between continuous switching (now called high-power mode) and burst mode.  Most LLC resonant converter controllers regulate the output power by adjusting the operating frequency. The TEA19161T regulates the output power by adjusting the voltage across the primary resonant capacitor for accurate state control and a linear power control.  External presets can define operation modes and protections. This feature provides flexibility and ease of design for optimizing controller properties to application-specific requirements. |  |  |  |  |

# TEA19161 and TEA19162 controller ICs

# Table 1. Revision history

| Rev   | Date     | Description      |

|-------|----------|------------------|

| v.2.1 | 20210407 | Updated revision |

| v.2   | 20190107 | second revision  |

| v.1   | 20170505 | Initial revision |

#### TEA19161 and TEA19162 controller ICs

# 1 Introduction

The TEA1916 is a fully digital controller for high-efficiency resonant power supplies. It is a 2-chip combo, which includes the TEA19161 resonant/LLC controller and the TEA19162 PFC controller. Together with the TEA1995T dual SR controller, a complete resonant power supply can be built, which is easy to design and has a very low component count. This power supply meets the efficiency regulations of Energy Star, the Department of Energy (DoE), the Eco-design directive of the European Union, the European Code of Conduct, and other guidelines. So, an additional power supply for standby supply is not required.

This application note describes the TEA19161 and TEA19162 functions for different applications. It covers the functionality of the standard IC versions TEA19161T, TEA19162T, and the safe-restart versions TEA19161CT and TEA19162CT. Because the combination of two controllers provides extensive functionality, many topics are discussed.

This document is set up in such a way, that a chapter or paragraph of a specific topic can be read as a standalone explanation. A minimum number of cross-references to other document parts of the TEA19161T or TEA19162T data sheets is used. This document setup leads to repetition of some information within the application note and to descriptions or figures that are similar to the ones published in the data sheets. To enhance readability, only typical values are given in most cases.

The TEA19161T and TEA19162T can be considered as one PFC + HBC system controller. In this document, the one system controller is called TEA1916. Only in specific cases, the TEA19161T and TEA19162T names are used.

#### 1.1 Related documents

For more information and tools, see the various other TEA1916 documents such as:

- Data sheets TEA19161T (<u>Ref. 1</u>), TEA19161CT (<u>Ref. 3</u>), TEA19162T (<u>Ref. 2</u>), and TEA19162CT (<u>Ref. 4</u>)

- · Excel calculation sheet (available on request)

- Online calculation tool

- · Demo board user manuals

#### TEA19161 and TEA19162 controller ICs

# 1.2 Related products

NXP Semiconductors products that are related to the TEA1916 ones are:

• TEA1716:

This product provides a PFC + LLC controller in an SO24 IC package. It allows low-power consumption burst mode operation.

• TEA1713:

This product provides a PFC + LLC controller in one SO24 IC package. It is more suitable for applications that do not have stringent requirements on burst mode operation.

Other NXP Semiconductors products for resonant power conversion are:

• TEA1795:

Synchronous rectification controller for resonant converters with dual gate drivers in SO8.

• TEA1995:

Synchronous rectification controller for resonant converters with dual gate drivers in an SO8 package. This product is optimized for the TEA1916 operating modes.

TFA1708

X-capacitor discharge IC.

TEA19161 and TEA19162 controller ICs

# 2 TEA1916 highlights and features

#### 2.1 Resonant conversion

The market of today demands high-quality, reliable, small, lightweight, and efficient power supplies.

A resonant DC-to-DC converter produces sinusoidal currents with low switching losses. It provides the possibility of operating at higher frequencies with excellent efficiency at high power levels.

In recent years, LLC resonant converters have become more popular because of the high efficiency at medium and high output load. The latest generation of resonant controllers that support burst-mode operation have enabled good efficiency, even at low output load, a low power consumption in standby, or no-load operation.

The TEA19161 offers a next step in low-load operation. Reducing the converter power losses further and providing programmable operation behavior to make the best fit for each application.

#### 2.2 Power factor correction conversion

Basic switch mode power supplies represent a non-linear impedance (load characteristic) to the mains input. The current taken from the mains supply occurs only at the highest voltage peaks and is stored in a large capacitor. The energy is taken from this capacitor in accordance with the switch-mode power supply operation characteristics.

Government regulations dictate special requirements for the load characteristics of certain applications.

Two main requirements can be distinguished:

- Mains harmonics requirements EN61000-3-2

- Power factor (real power/apparent power)

The requirements impose a more resistive characteristic of the mains load.

To fulfill these requirements, measures must be taken regarding the input circuit of the power supply. To modify the mains load characteristics, passive (typically a series coil) or active (typically a boost converter) circuits can be used.

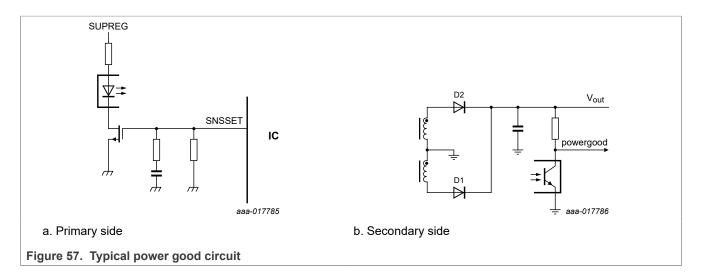

An additional market requirement for the added mains input circuit is that it works with a good efficiency and that the cost is low.

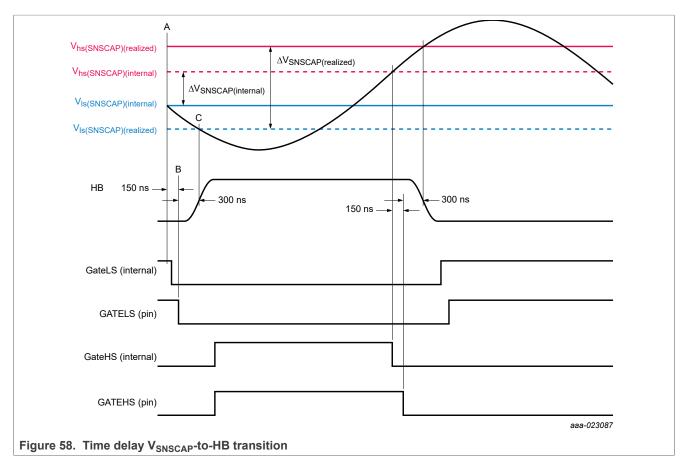

To meet these requirements, using a boost converter in combination with a resonant converter provides the benefit of a fixed DC input voltage. The fixed input voltage ensures an easier design of the resonant converter (especially for wide mains input voltage range applications) and makes reaching a higher efficiency possible.

To implement optimal burst-mode operation and complementary protection functions, the TEA19162 provides a PFC controller that operates in close cooperation with the TEA19161.

#### TEA19161 and TEA19162 controller ICs

### 2.3 TEA19161 and TEA19162 controller combination

The TEA19161T and TEA19162T form a control combo-IC. The combo-IC incorporates a half-bridge controller for a resonant LLC tank and a PFC controller. It provides high efficiency at all power levels. Together with the TEA1995T dual LLC resonant SR controller, a high performance cost-effective resonant power supply can be designed. The design can meet the efficiency requirements of Energy Star, the Department of Energy (DoE), the Eco-design Directive of the European Union, the European Code of Conduct, and other guidelines.

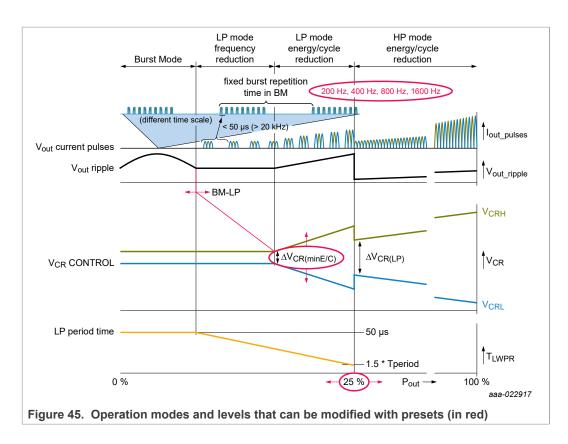

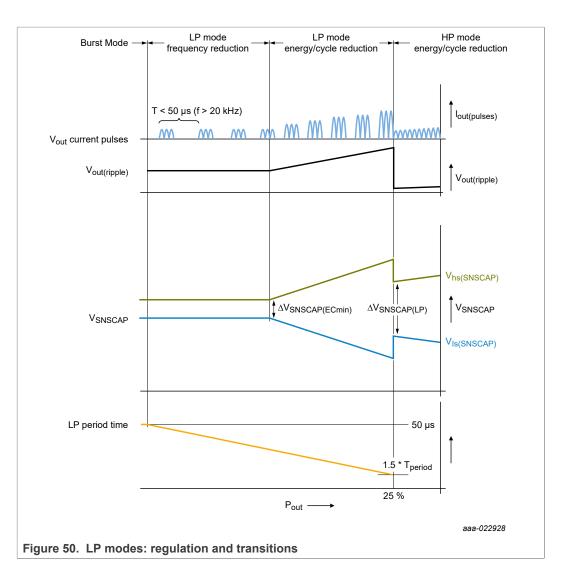

Generally, resonant converters show an excellent efficiency at high power levels, while at lower levels the efficiency reduces because of the relatively high magnetizing current and switching losses. To reach a high efficiency at all power level, the TEA19161T (LLC) introduces a new operating mode, low-power mode. This mode allows operation in the power region between continuous switching (now called high-power mode) and burst mode.

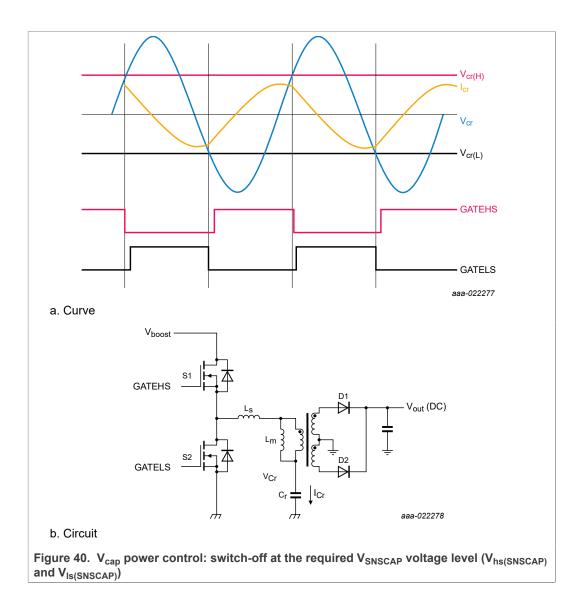

Most LLC resonant converter controllers regulate the output power by adjusting the operating frequency. The TEA19161T regulates the output power by adjusting the voltage across the primary resonant capacitor. The result is accurate state control and a linear power control.

Using a voltage divider, the primary resonant capacitor voltage provides accurate information about the output power to the controller. The voltage divider sets the output power levels. It determines when the system switches from the high-power mode to low-power mode and when it switches from low-power mode to burst mode.

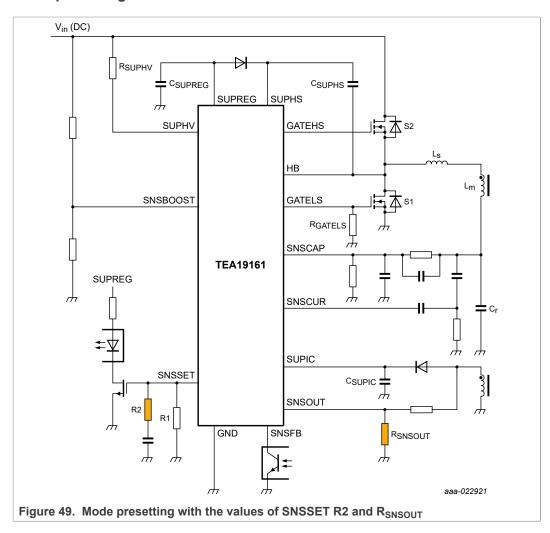

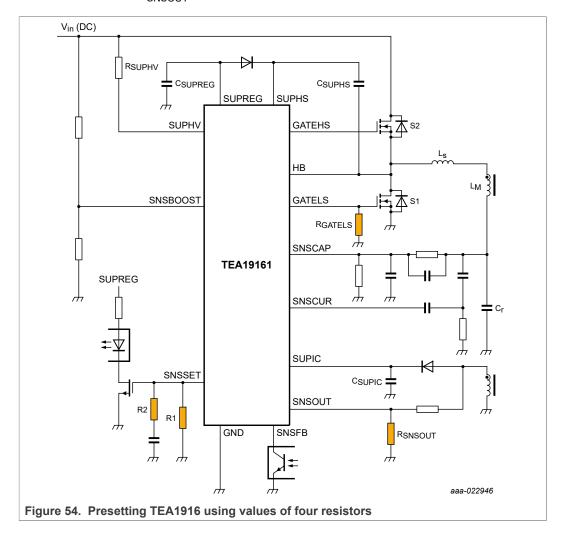

External presets define the operating modes and protections. At start-up, the IC measures the applied resistor value on a pin and sets the mode or protection parameters accordingly. This feature provides flexibility and ease of design to optimize controller properties to application-specific requirements.

The following protections are implemented using the communication between the two controllers:

- Overcurrent protection (OCP)

- Overvoltage protection (OVP)

- Overpower protection (OPP)

- Brownin

- Brownout

- Capacitive mode regulation (CMR)

- Overtemperature protection (OTP)

- Open-loop protection (OLP)

#### TEA19161 and TEA19162 controller ICs

#### 2.4 Features and benefits

#### 2.4.1 Distinctive features

- Complete combo functionality combining TEA19161 and TEA19162

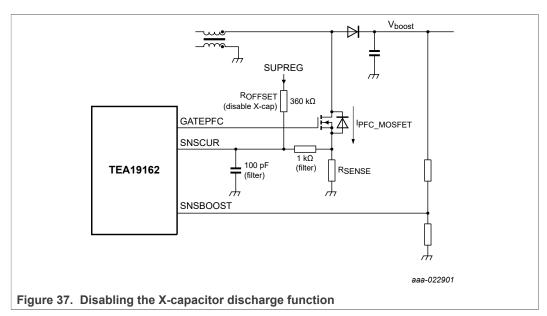

- Integrated X-capacitor discharge without additional external components

- Universal mains supply operation (70 V (AC) to 276 V (AC))

- · Integrated PFC soft start and soft stop

- · Integrated high-voltage start-up

- V<sub>CC</sub> regulation via HV source allowing small VCC capacitor

- Fast system start-up (< 0.5 s)

- Integrated high-voltage level shifter

- · Maximized range of operation on switching frequencies outside the audible area

- · Integrated LLC soft start

- · Power good signal

- Up to 500 kHz half-bridge switching frequency

- Ease of design because control and operation parameters can be preset

# 2.4.2 Green features

- PFC valley/zero voltage switching for minimum switching losses

- PFC frequency limitation for best efficiency at reduced switching losses

- · Very high system efficiency at all load conditions

- Compliant with Energy using Product directive (EuP) lot 6

- Excellent no-load system input power (< 75 mW)

- Regulated low feedback optocoupler current, enabling low no-load power consumption

- · Very low supply current during non-switching state in burst mode

- Transitions between modes and power levels adjustable with external presets

- LLC adaptive non-overlap time

#### TEA19161 and TEA19162 controller ICs

#### 2.4.3 Protection features

- Safe restart mode for system fault conditions

- PFC continuous-mode protection using demagnetization detection

- Accurate overvoltage protection (OVP)

- Open-loop protection (OLP)

- Internal and external IC overtemperature protection (OTP)

- Low and adjustable PFC overcurrent protection (OCP) trip level

- Adjustable brownin/brownout protection

- Supply undervoltage protection (UVP)

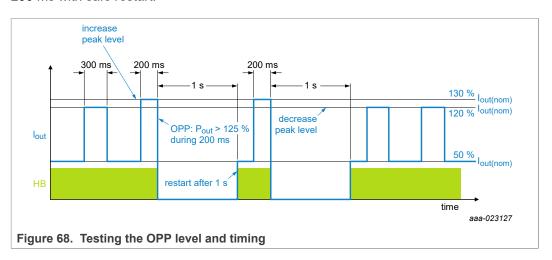

- Overpower protection (OPP)

- Integrated presettable overpower timeout

- Presettable latch or restart function for system fault conditions (CT-versions are safe start versions)

- Capacitive mode protection (CMP)

- Maximum low-side and high-side LLC on-time protection

- Overcurrent protection (OCP)

- Disable input

# 2.5 Typical areas of application

- High-power adapters

- · Low-power adapters

- · Slim notebook adapters

- · Computer power supplies

- LCD television

- · Office equipment

- · Server supplies

- · Professional lighting

TEA19161 and TEA19162 controller ICs

# 3 Pinning

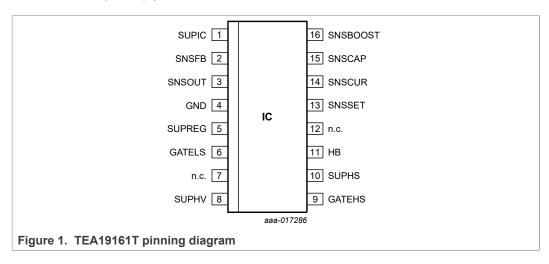

# 3.1 TEA19161T (HBC) pin overview

Table 2. TEA19161T (PFC) pins

| Pin Pin name Functional description summary                                                                                                                                                                                                                                                                                                                                                             |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

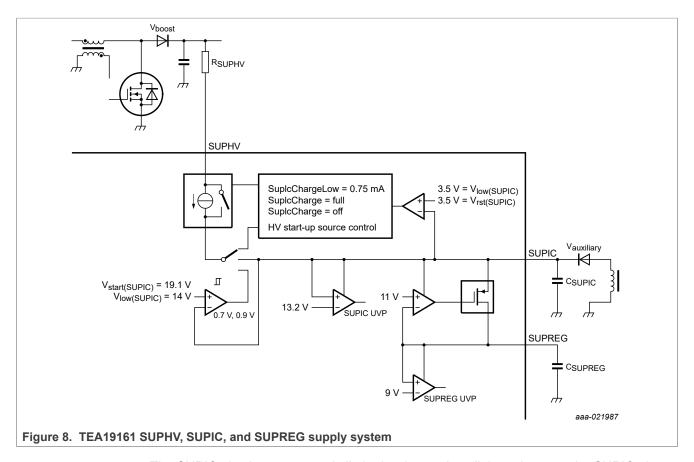

| 1                                                                                                                                                                                                                                                                                                                                                                                                       | SUPIC | IC voltage supply input and output of the HV start-up source.  All internal circuits are directly or indirectly (via SUPREG) supplied from this pin. The exception is high-voltage circuit.  The SUPIC can be connected to the SUPIC function of the TEA19162 PFC controller.  The buffer capacitor on SUPIC can be charged or supplied in several ways:  High-voltage (HV) start-up source  Auxiliary winding from HBC transformer or capacitive supply from switching half-bridge node                                                                                                                                                                                      |  |  |

| W<br>by<br>be<br>Du<br>dri<br>so                                                                                                                                                                                                                                                                                                                                                                        |       | • External DC supply, for example a standby supply  When the SUPIC voltage has reached the start level of 19.1 V, the IC enables operation. If supplied by the HV source, the voltage is regulated with a hysteresis of 0.7 V. When the voltage drops to below 13.2 V, the IC stops operating. A system reset is activated at 3.5 V.  During the non-switching period in burst mode, the HV source is activated when the SUPIC voltage drops to 14 V. To avoid that the system stops during a very long period of non-switching, the HV source regulates the SUPIC voltage with a hysteresis of 0.9 V. In this way, a voltage drop on the SUPIC pin to below 14 V is avoided. |  |  |

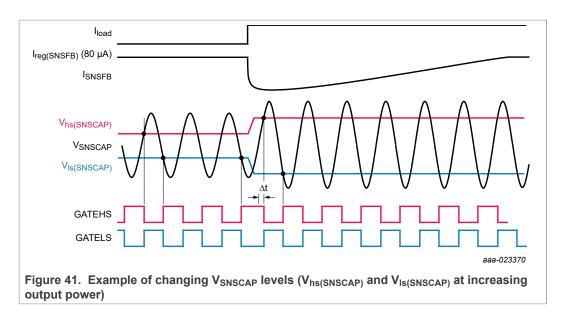

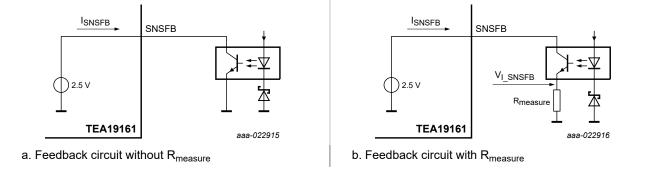

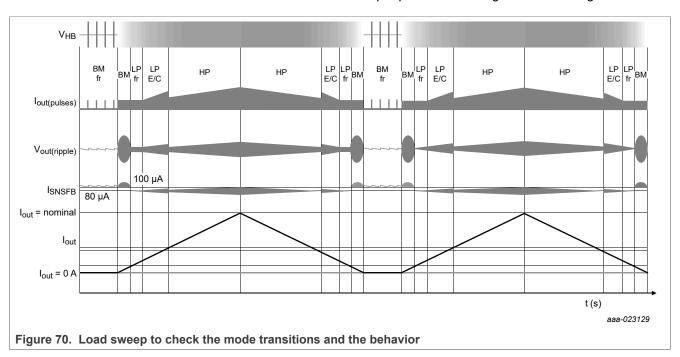

| SNSFB  Sense input for HBC output regulation feedback because Normally, the pin is connected to ground via an optocoupl the feedback.  The IC measures the regulation current. For measuring the additional 100 Ω or 1 kΩ series resistor to GND can be use To minimize power consumption, the internal source slow current level (optobias regulation):  • HP and LP mode: 80 μA  • Burst mode: 100 μA |       | The IC measures the regulation current. For measuring the current during engineering work, an additional 100 $\Omega$ or 1 k $\Omega$ series resistor to GND can be useful. To minimize power consumption, the internal source slowly regulates the SNSFB to an average low current level (optobias regulation):  • HP and LP mode: 80 $\mu$ A  • Burst mode: 100 $\mu$ A  The SNSFB current and voltage levels are now independent of the output power. Changes in the                                                                                                                                                                                                       |  |  |

# TEA19161 and TEA19162 controller ICs

Table 2. TEA19161T (PFC) pins...continued

| Table                                                                                                                                                                                                                                                                                                                                                                                                                           | 2. TEA191611 | (PFC) pinscontinued                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Pin                                                                                                                                                                                                                                                                                                                                                                                                                             | Pin name     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

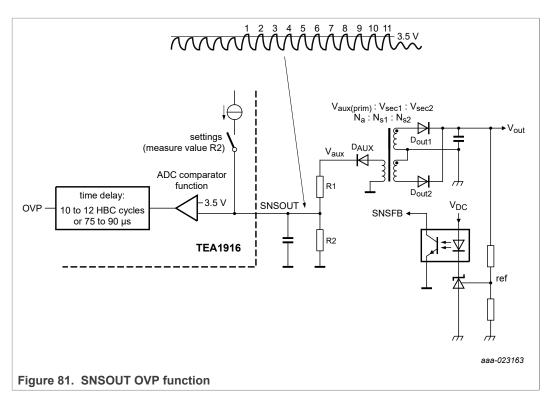

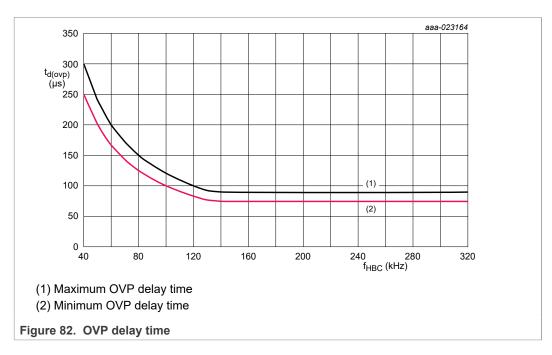

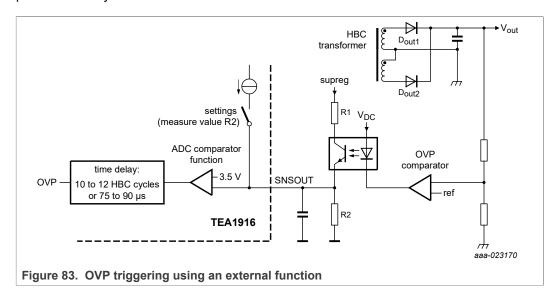

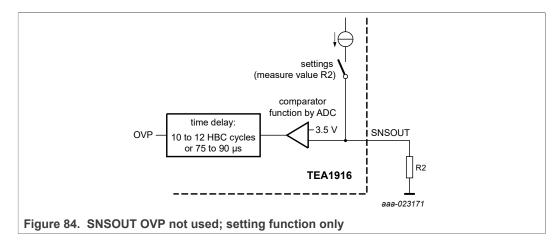

| 3                                                                                                                                                                                                                                                                                                                                                                                                                               | SNSOUT       | Input for indirect sensing the output voltage of the resonant converter cycle-by-cycle. To set the burst repetition frequency, the resistor value to GND ( $R_{SNSOUT}$ ) is measured and stored at start-up. When $R_{SNSOUT}$ < 1.5 k $\Omega$ , start-up is disabled. The peak voltage is measured during each positive half cycle. When SNSOUT exceeds 3.5 V during 11 cycles with a minimum time of 75 $\mu$ s, a latched overvoltage protection is triggered. The CT-versions are safe restart versions. This pin contains a small current source of 50 nA for open-pin detection that pulls the voltage to OVP in this fault condition.                                                                                 |  |  |  |  |  |

| 4                                                                                                                                                                                                                                                                                                                                                                                                                               | GND          | Ground. Reference for GATELS driver and measurement inputs.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |

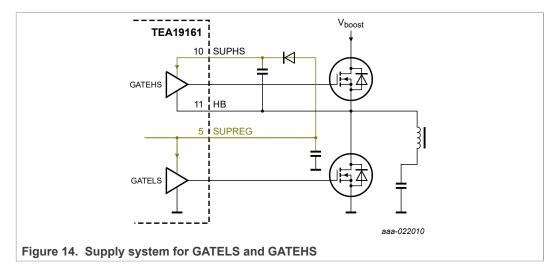

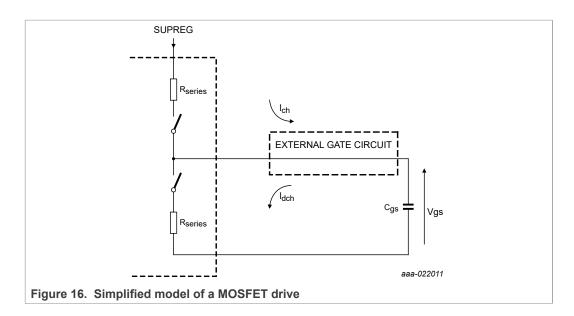

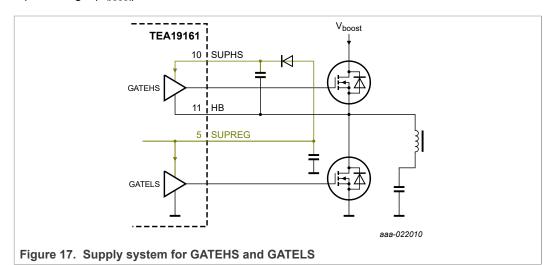

| 5                                                                                                                                                                                                                                                                                                                                                                                                                               | SUPREG       | Output of the internal voltage regulator: 11 V. SUPREG can provide a minimum current of 30 mA. The supply made with this function is used for: GATELS SUPHS with bootstrap Reference voltage for optional external circuit SUPREG is charged along with SUPIC. UVP: If the voltage on the SUPREG pin drops to below 9 V, the IC stops operating.                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |

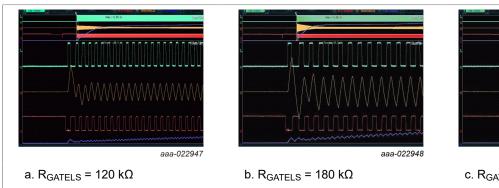

| 6                                                                                                                                                                                                                                                                                                                                                                                                                               | GATELS       | Gate driver output for low-side MOSFET of the HBC.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |

| 7                                                                                                                                                                                                                                                                                                                                                                                                                               | n.c.         | Do not connect. High-voltage spacer.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |

| 8                                                                                                                                                                                                                                                                                                                                                                                                                               | SUPHV        | High-voltage supply input for the HV start-up source. A series resistor (24 k $\Omega$ typical) must be connected as part of the HV source function. The HV source charges the SUPIC pin to the start level of 19.1 V. It regulates the SUPIC pin with a hysteresis of 0.7 V. When the voltage on the SUPIC pin drops to below 3.5 V, the current is limited to 0.75 mA to limit the power if there is a SUPIC short circuit. During the non-switching period in burst mode, the HV source is activated when the SUPIC voltage drops to 14 V. To avoid that the system stops during a very long period of non-switching, the HV source regulates the voltage on the SUPIC pin with a hysteresis of 0.9 V when it exceeds 14 V. |  |  |  |  |  |

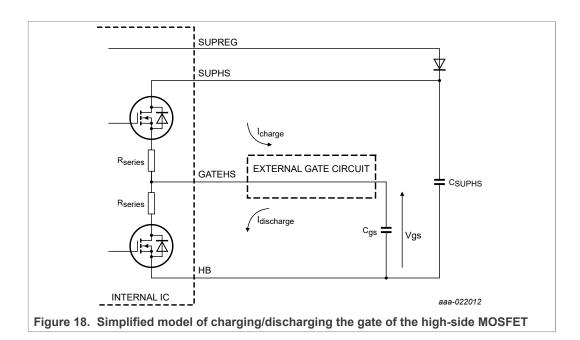

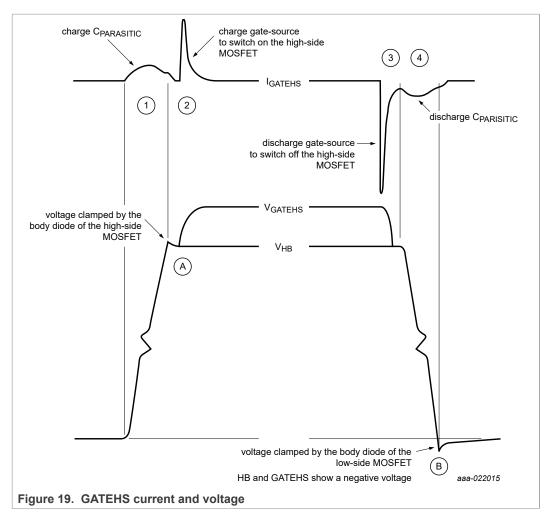

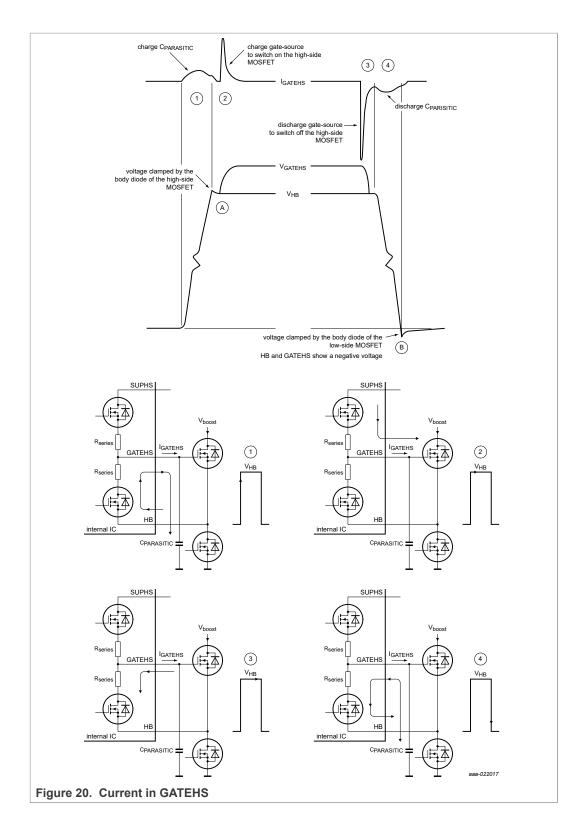

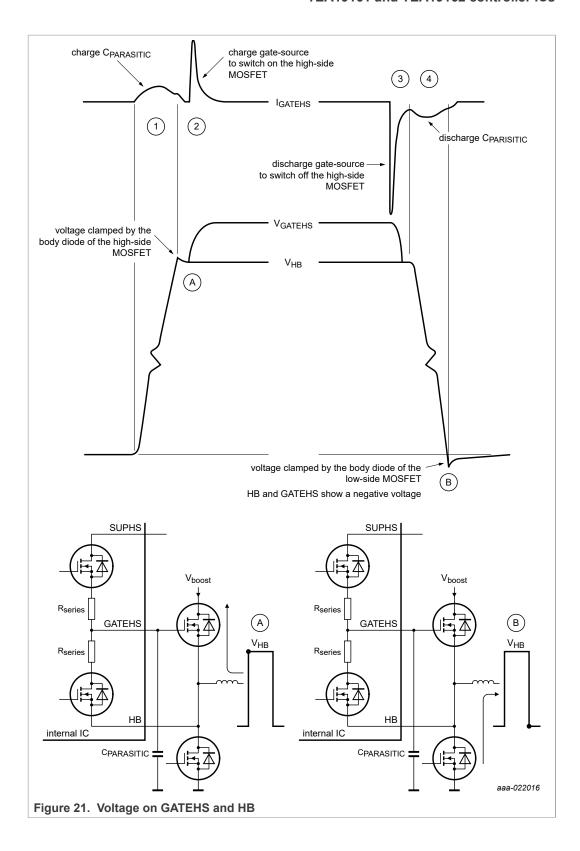

| 9                                                                                                                                                                                                                                                                                                                                                                                                                               | GATEHS       | Gate driver output for high-side MOSFET of HBC.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

| 10                                                                                                                                                                                                                                                                                                                                                                                                                              | SUPHS        | High-side driver supply connected to an external bootstrap capacitor between HB and SUPHS. The supply is obtained using an external diode between the SUPREG and SUPHS pins.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |

| 11                                                                                                                                                                                                                                                                                                                                                                                                                              | НВ           | Reference for the high-side driver GATEHS.  HB is externally connected to a half-bridge node between the MOSFETs of HBC.  It is an input for the internal half-bridge slope dV/dt detection circuit for adaptive non-overlap regulation and top switching in LP mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

| 12                                                                                                                                                                                                                                                                                                                                                                                                                              | n.c.         | Do not connect. High-voltage spacer.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |

| Pin for settings and power good (PG) signal.  Two resistor values are measured and stored at start-up. They provide settings for:  Transition levels HP/LP mode  LP/BM  OPP level  OPP timeout  Restart or latched protection  After measuring the settings, the pin provides an output for a PG signal. This signal shows the of stable operation after start-up. It provides a warning that the supply is about to shut down. |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

# TEA19161 and TEA19162 controller ICs

Table 2. TEA19161T (PFC) pins...continued

| Pin | Pin name | Functional description summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

|-----|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

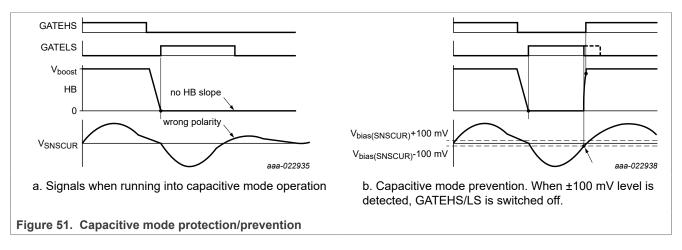

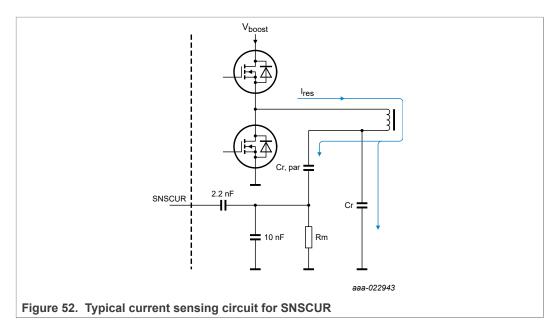

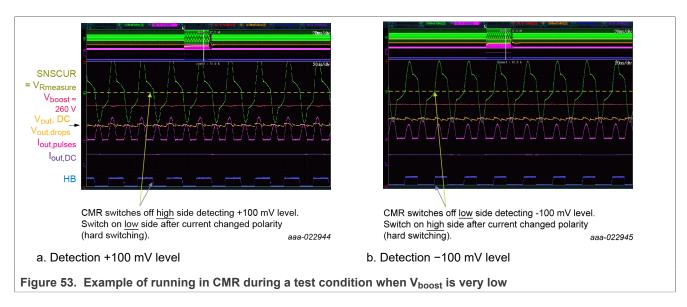

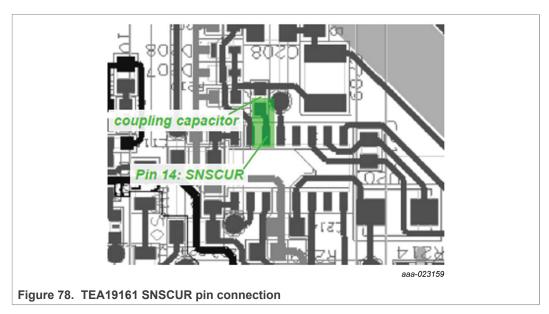

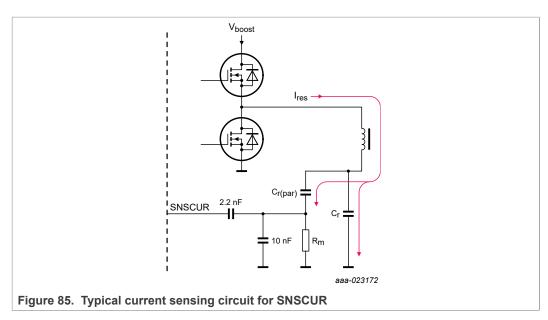

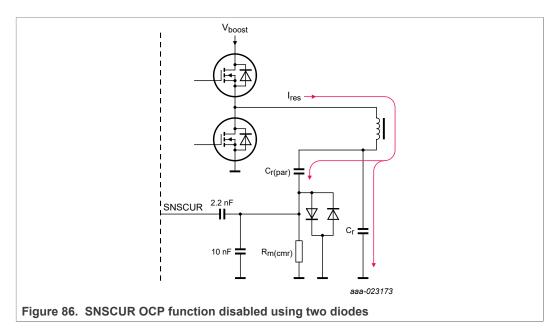

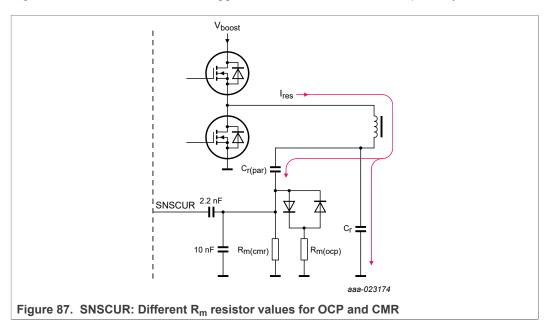

| 14  | SNSCUR   | Sense input for the momentary primary current of the HBC using a voltage across and external measurement resistor. To avoid disturbance, a series capacitor placed very close to the pin applies the voltage signal. The IC biases the DC voltage on the pin to 2.5 V.  Internal voltage levels are:  • If V <sub>SNSCUR</sub> – V <sub>BIAS</sub> > ±1.5 V, the gate driver is switched off to limit the power to the OCP level. After the property of the pin to 2.5 V.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

|     |          | <ul> <li>8 OCP cycles, a latched protection is activated. The CT-version are safe restart versions.</li> <li>V<sub>SNSCUR</sub> - V<sub>BIAS</sub> = ±100 mV level for detecting the (almost) zero current level. To prevent</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

|     |          | <ul> <li>capacitive mode switching, the driver switches off at this level.</li> <li>V<sub>SNSCUR</sub> - V<sub>BIAS</sub> = ±13 mV for detecting the current polarity. Used as parameter in the internal switching logic.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

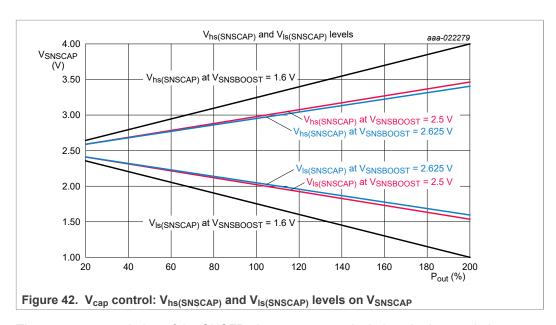

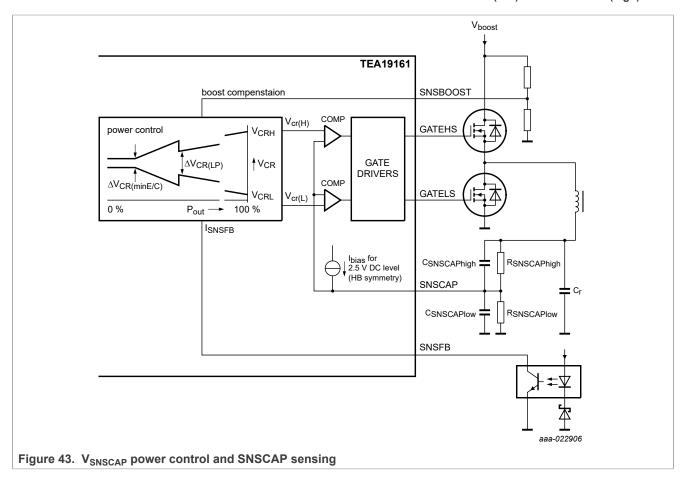

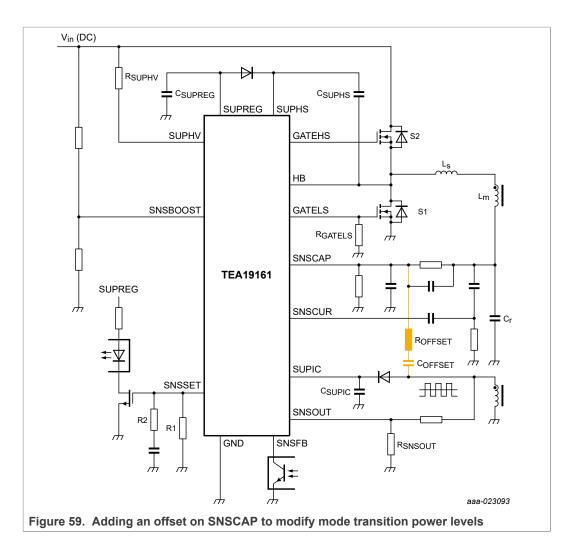

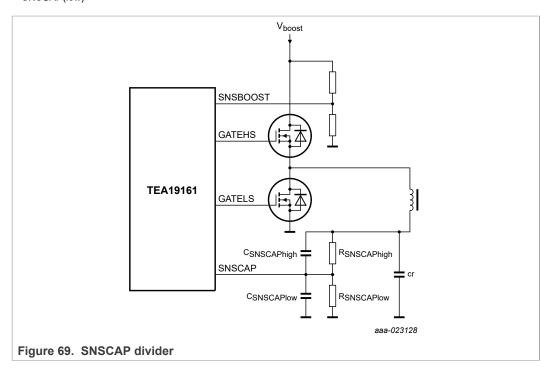

| 15  | SNSCAP   | Senses the voltage on the HBC capacitor for driving the correct output power.  The SNSCAP pin is externally connected to a resistive and a capacitive divider to the voltage on the resonant capacitor.  An internal bias circuit generates a 2.5 V DC level on SNSCAP.  The divider scales the voltage levels on the resonant capacitor for the power level control range from 0 % to 200 % to the maximum SNSCAP voltage range of 1 V to 4 V. The scaling includes input voltage compensation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

|     |          | The scaling sets the correct levels for:  Transition level HP/LP  Minimum energy per cycle (ECmin)  OPP level  200 % power level  For each half cycle, the internal power control sets a new target SNSCAP voltage level for switching off the HBC MOSFET to reach the required power. It is based on:  SNSFB current (feedback regulation)  SNSBOOST voltage (input voltage compensation)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

|     |          | <ul> <li>Mode transition control</li> <li>Slope compensation (power reduction during start-up and protection)</li> <li>HB symmetry regulation</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

| 16  | SNSBOOST | <ul> <li>This pin combines three functions. The boost voltage is sensed for:</li> <li>Brownin and brownout of the HBC</li> <li>HBC input voltage compensation. Adapting the V<sub>cap</sub> levels to keep a constant output power level at varying input voltages.</li> <li>Communication between the TEA19161 and TEA19162 via internal current sources.</li> <li>The SNSBOOST pin is externally connected to a resistive divided boost voltage. The resistor from SNSBOOST to GND must be 95.3 kΩ. To ensure the intended functionality, the parallel capacitor must be ≤ 4.7 nF.</li> <li>The pin uses three voltage levels:</li> <li>Fast latch reset level: 2 V:     For generating a fast latch reset in the TEA19161, the TEA19162 pulls high the pin level using a +200 μA current source.</li> <li>At 2.3 V:     The HBC starts operation because the boost voltage is high enough (brownin).</li> <li>At 1.6 V:     The HBC stops operation, because of the boost voltage is too low (brownout)</li> <li>The voltage levels on SNSBOOST are operated by:</li> <li>External resistive divider of the boost voltage</li> </ul> |  |  |

|     |          | <ul> <li>Current sources in the TEA19162: +200 μA and -100 μA</li> <li>Current sources in the TEA19161: +5 μA, +30 μA, and -100 μA</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

# TEA19161 and TEA19162 controller ICs

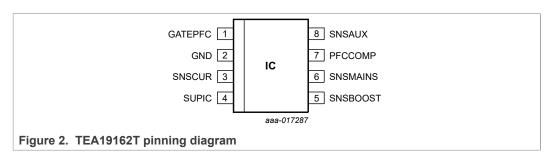

# 3.2 TEA19162T (PFC) pin overview

Table 3. TEA19162T (PFC) pins

| Pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Pin name Functional description summary |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

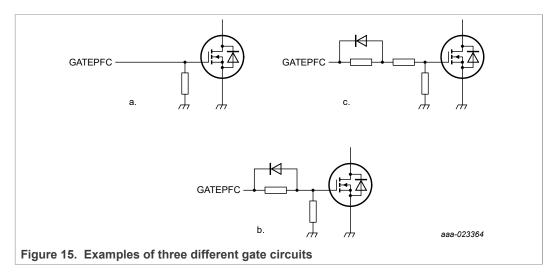

| 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | GATEPFC                                 | Gate driver output for PFC MOSFET.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

| 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | GND                                     | Ground. Reference for PFC driver and measurement points.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

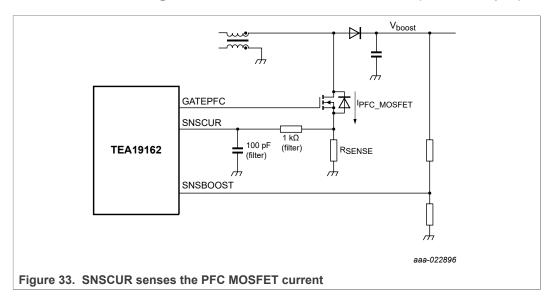

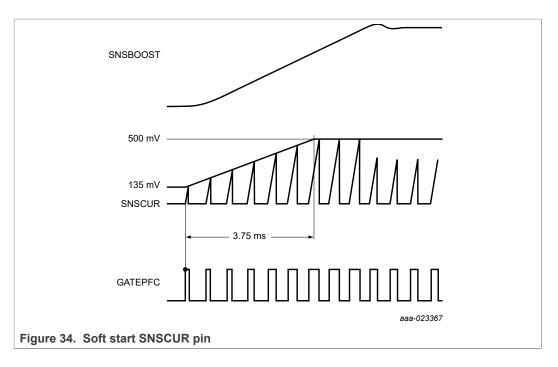

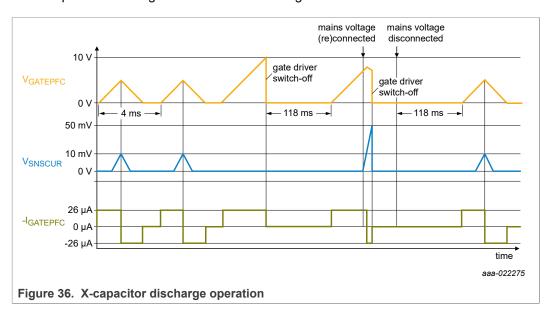

| 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | SNSCUR                                  | Current sense input for PFC This input is used to limit the maximum peak current in the PFC core. The current sense input is a cycle-by-cycle protection. When the SNSCUR level reaches 500 mV, the PFC MOSFET is switched off. The external sense resistor value determines the current value.  Internally, a soft start function limits the peak current to 135 mV at the first cycle. During the soft start time, the peak current limit is gradually increased. It reaches the nominal value of 500 mV after 3.75 ms.  For the X-capacitor discharge function there are two detection levels:  • 10 mV:  Maximum level of the discharge current pulse during X-capacitor discharge.  • 50 mV:  Detection level for ending the X-capacitor discharge function (mains voltage reconnected) |  |  |  |

| 4 SUPIC  IC voltage supply input.  Connected to the SUPIC pin For start-up, the SUPIC pin of the High-voltage (HV) start-up  Auxiliary winding from the High node  External DC supply, for example with the SUPIC voltage readup, the TEA19161 pulls down controllers is synchronized.  When the voltage on the SUFIC voltage on the |                                         | Connected to the SUPIC pin (pin 1) of the TEA19161.  For start-up, the SUPIC pin can be charged or supplied in several ways:  • High-voltage (HV) start-up source in the TEA19161  • Auxiliary winding from the HBC transformer or capacitive supply from the switching half-bridge node  • External DC supply, for example, a standby supply  When the SUPIC voltage reaches the start level of 13 V, the IC is activated. During system start-up, the TEA19161 pulls down the SNSBOOST pin of the TEA19162. In this way, the start of both                                                                                                                                                                                                                                                 |  |  |  |

# TEA19161 and TEA19162 controller ICs

| Table                                       | 3. TEA19162T | (PFC) pinscontinued                                                                                                                                                                                                                                                                                       |  |  |  |  |

|---------------------------------------------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Pin Pin name Functional description summary |              |                                                                                                                                                                                                                                                                                                           |  |  |  |  |

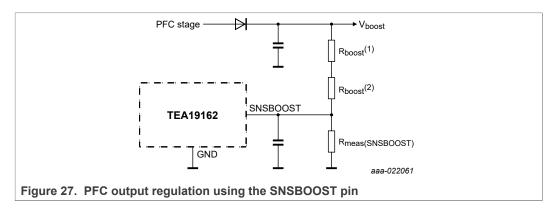

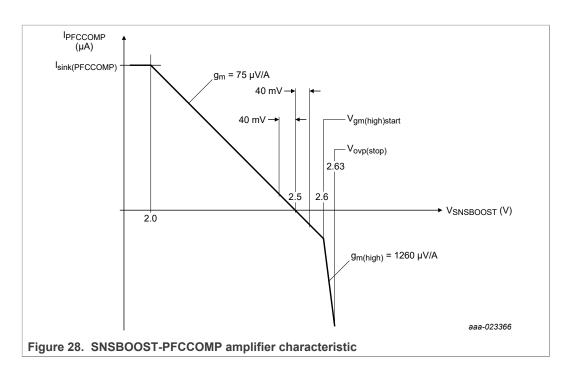

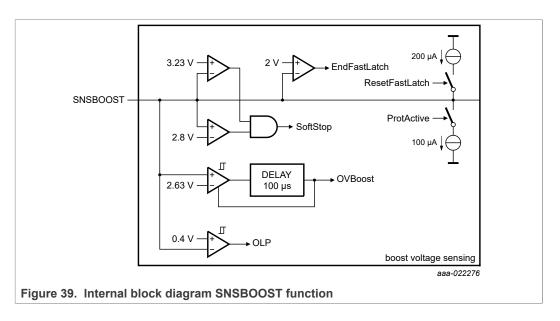

| 5                                           | SNSBOOST     | This pin combines two functions:                                                                                                                                                                                                                                                                          |  |  |  |  |

|                                             |              | It senses the boost voltage for regulation (output voltage of the PFC stage).                                                                                                                                                                                                                             |  |  |  |  |

|                                             |              | • It is used for communication between the TEA19161 and TEA19162 via internal current sources.                                                                                                                                                                                                            |  |  |  |  |

|                                             |              | The SNSBOOST pin is externally connected to a resistive divided boost voltage. The resistor from SNSBOOST to GND must be 100 k $\Omega$ . To ensure the intended functionality, the parallel capacitor must be $\leq 4.7$ nF.                                                                             |  |  |  |  |

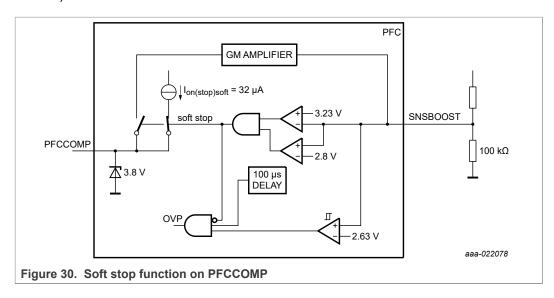

|                                             |              | The SNSBOOST pin uses seven voltage levels:                                                                                                                                                                                                                                                               |  |  |  |  |

|                                             |              | • Short-pin or open-pin detection: $V_{scp(stop)} = 0.4 \text{ V}$ and $V_{scp(start)} = 0.5 \text{ V}$ . This function is also used by the TEA19161 to disable the IC if a protection is triggered or before start-up.                                                                                   |  |  |  |  |

|                                             |              | • Fast latch reset level: 2 V. To generate a fast latch reset in the TEA19161, the pin level is pulled                                                                                                                                                                                                    |  |  |  |  |

|                                             |              | high by a 200 μA internal current source of the TEA19162.                                                                                                                                                                                                                                                 |  |  |  |  |

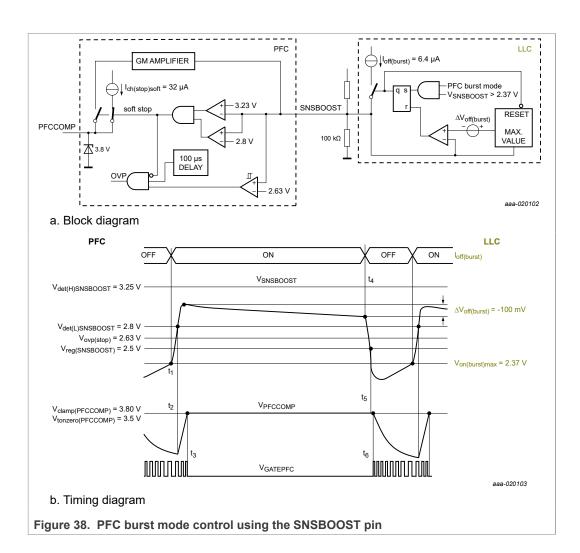

|                                             |              | <ul> <li>Regulation of the PFC output voltage in burst mode by the TEA19161. Soft start at 2.4 V and<br/>soft stop at 2.5 V.</li> </ul>                                                                                                                                                                   |  |  |  |  |

|                                             |              | Control of the burst mode by TEA19161. Soft start at 2.4 V; soft stop at 2.5 V.                                                                                                                                                                                                                           |  |  |  |  |

|                                             |              | • Regulation of the PFC output voltage in normal operation: V <sub>reg(SNSBOOST)</sub> = 2.5 V                                                                                                                                                                                                            |  |  |  |  |

|                                             |              | <ul> <li>The pin voltage varies between 2.8 V and 3.23 V in the burst stop state of the burst mode<br/>operation of the TEA19161.</li> </ul>                                                                                                                                                              |  |  |  |  |

|                                             |              | <ul> <li>PFC OVP (cycle-by-cycle): V<sub>OVP(SNSBOOST)</sub> ≥ 2.63 V (after a delay of 100 μs)</li> </ul>                                                                                                                                                                                                |  |  |  |  |

|                                             |              | The voltage levels on the SNSBOOST pin are influenced by:                                                                                                                                                                                                                                                 |  |  |  |  |

|                                             |              | External resistive divider connected to the boost voltage                                                                                                                                                                                                                                                 |  |  |  |  |

|                                             |              | • Current sources in the TEA19162: -210 μA; +35 nA; +100 μA                                                                                                                                                                                                                                               |  |  |  |  |

|                                             |              | • Current sources in the TEA19161: -6.4 μA; +30 μA; +110 μA                                                                                                                                                                                                                                               |  |  |  |  |

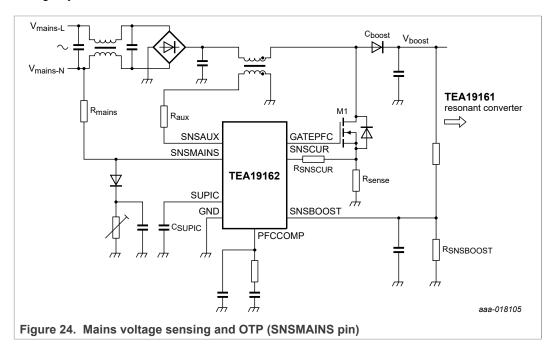

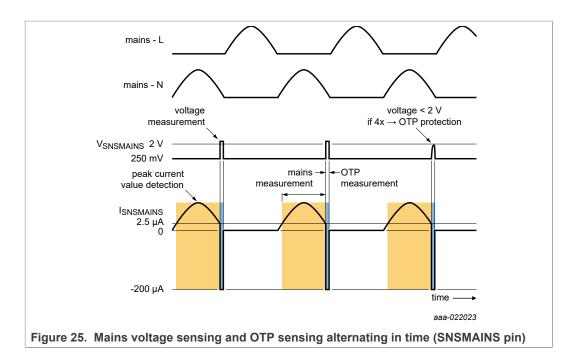

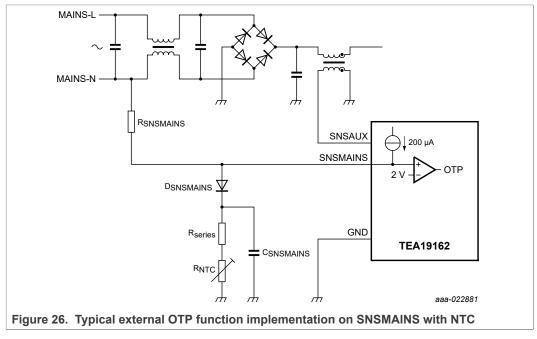

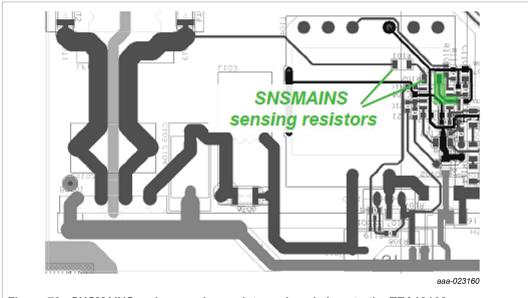

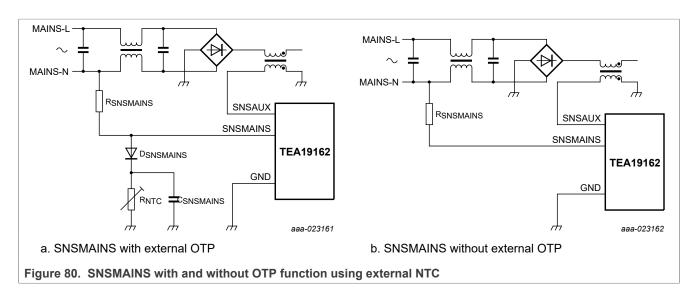

| 6                                           | SNSMAINS     | This pin combines two functions. The functions are alternately active in time during the same half-mains voltage cycle.                                                                                                                                                                                   |  |  |  |  |

|                                             |              | Mains voltage sensing                                                                                                                                                                                                                                                                                     |  |  |  |  |

|                                             |              | During the mains voltage sensing, the SNSMAINS pin is clamped to 0.25 V. The clamping of the SNSMAINS pin prevents that current leaks through the OTP network. There is no interference of the mains voltage measurement.                                                                                 |  |  |  |  |

|                                             |              | For mains sensing, the current flowing in the SNSMAINS pin is measured. The current depends on the external resistor value (typical 20 $M\Omega$ ). The mains voltage determines the amount of current.                                                                                                   |  |  |  |  |

|                                             |              | During a half-mains voltage cycle, the peak current value is determined and stored. The value is used as an input for:                                                                                                                                                                                    |  |  |  |  |

|                                             |              | The mains compensation function of the PFC regulation loop                                                                                                                                                                                                                                                |  |  |  |  |

|                                             |              | The brownin and brownout functions                                                                                                                                                                                                                                                                        |  |  |  |  |

|                                             |              | The SNSMAINS current level is sensed continuously until the current level drops below 2.5 μA.  Then, the external temperature measurement starts.                                                                                                                                                         |  |  |  |  |

|                                             |              | At a current level of 5.75 μA, the brownin level is reached and the IC starts switching. When the current drops again to below 5 μA, the brownout level is reached and the IC switching stops.                                                                                                            |  |  |  |  |

|                                             |              | When, after brownout, the brownin level is reached again, the latched protection state is reset.                                                                                                                                                                                                          |  |  |  |  |

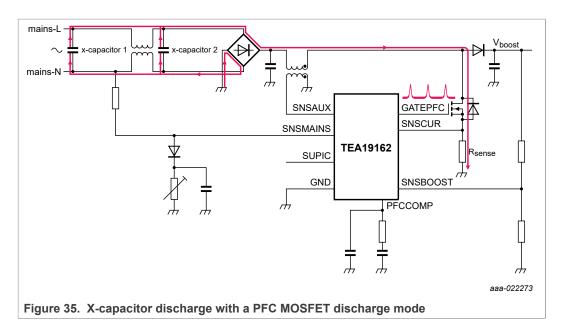

|                                             |              | If during 120 ms no positive dV/dt is detected, the X-capacitor discharge function is triggered. To reconnect the mains, the current on the SNSMAINS pin is monitored during the X-capacitor discharge mode.                                                                                              |  |  |  |  |

|                                             |              | External NTC overtemperature protection (OTP)                                                                                                                                                                                                                                                             |  |  |  |  |

|                                             |              | The OTP measurement lasts maximum 1 ms. During this time, a 200 µA current flows from the pin through the external diode and NTC to ground. The resulting voltage on the pin is measured. When the voltage on the pin < 2 V at four consecutive measurement half-cycles, the OTP protection is activated. |  |  |  |  |

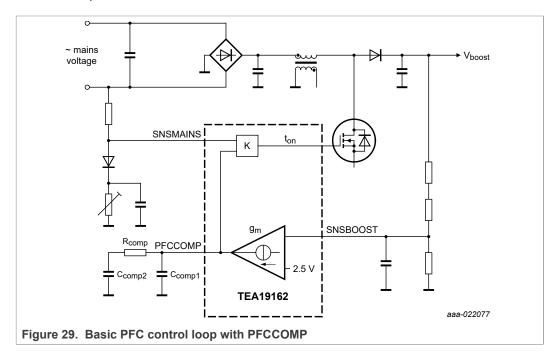

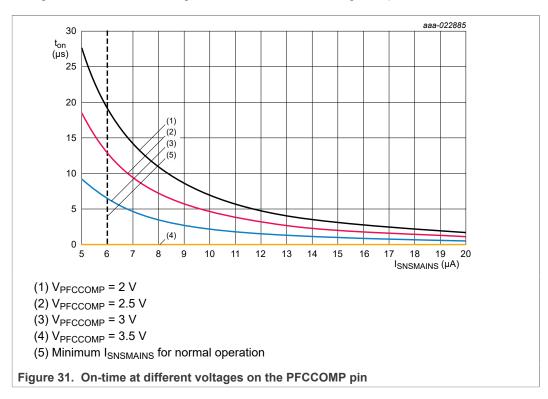

| 7                                           | PFCCOMP      | Frequency compensation for the PFC control-loop. Externally connected filter with typical values: 150 nF // $(33 \text{ k}\Omega + 470 \text{ nF})$ .                                                                                                                                                     |  |  |  |  |

|                                             |              | The voltage on PFCCOMP is used to generate a soft stop behavior.                                                                                                                                                                                                                                          |  |  |  |  |

# TEA19161 and TEA19162 controller ICs

Table 3. TEA19162T (PFC) pins...continued

| Pin | Pin name | Functional description summary                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-----|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

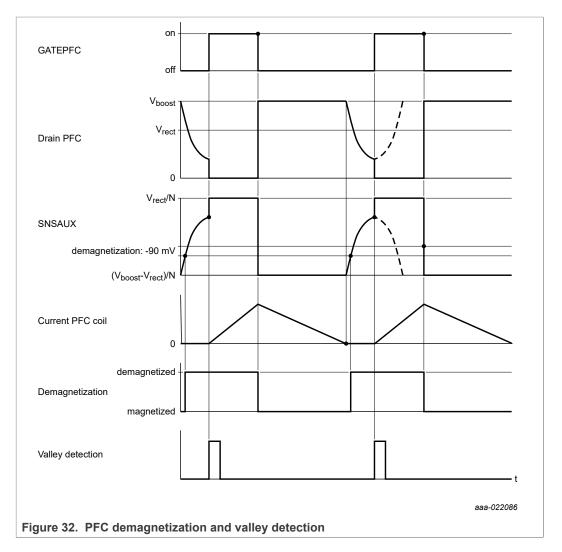

| 8   | SNSAUX   | Sense input from an auxiliary winding of the PFC coil for:  • Demagnetization timing  • Valley detection to control the PFC switching  It is a $-90$ mV level with a timeout of 44.5 $\mu$ s. To prevent damage of the input during surges (for example, lightning), the auxiliary winding must be connected to the pin via an impedance (recommended is a 5.1 k $\Omega$ series resistor).  Open-pin detection is possible using an internal pull-up current source. |

# TEA19161 and TEA19162 controller ICs

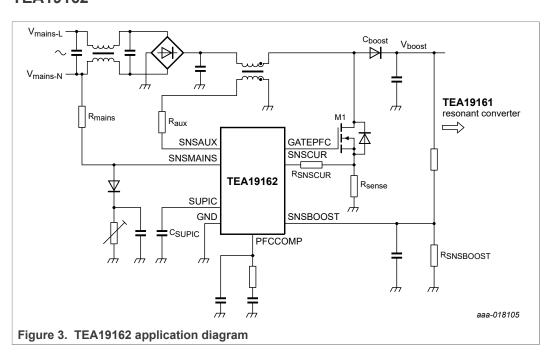

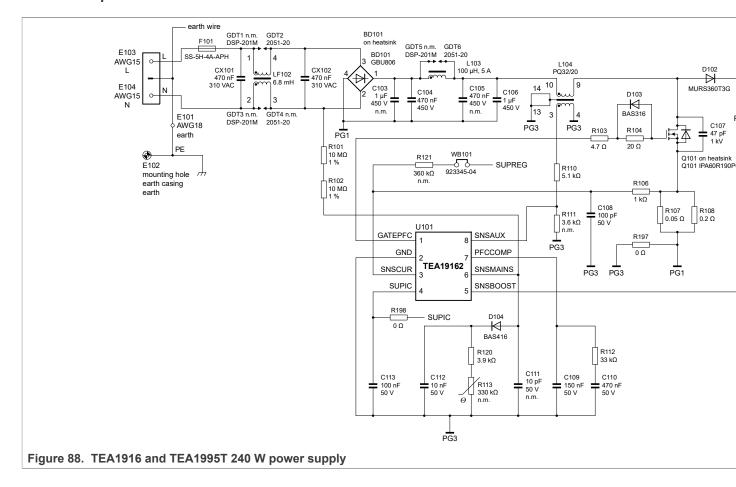

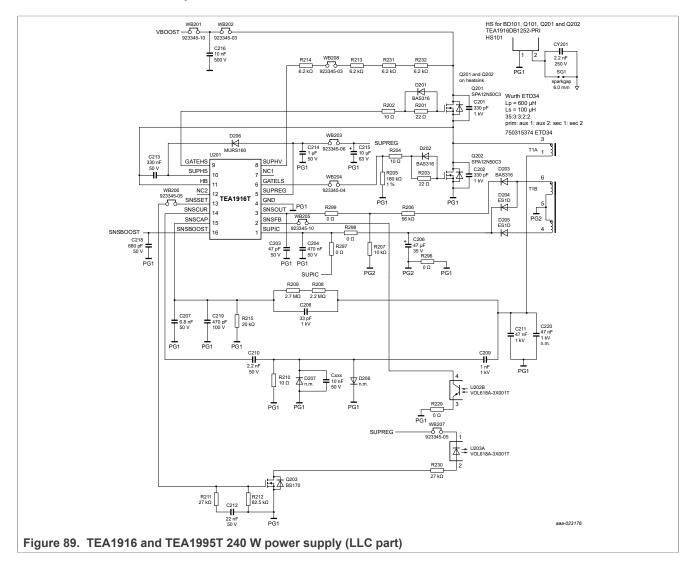

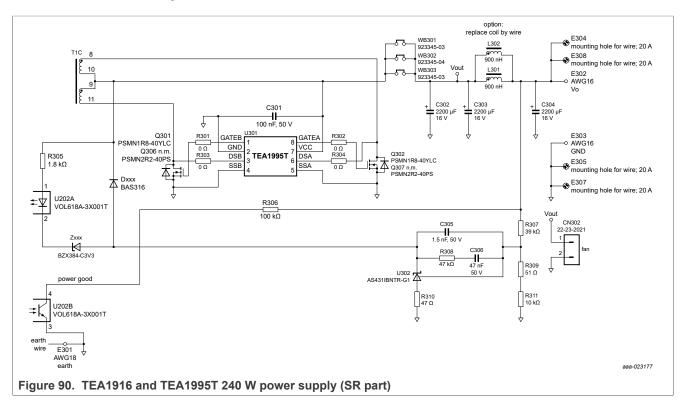

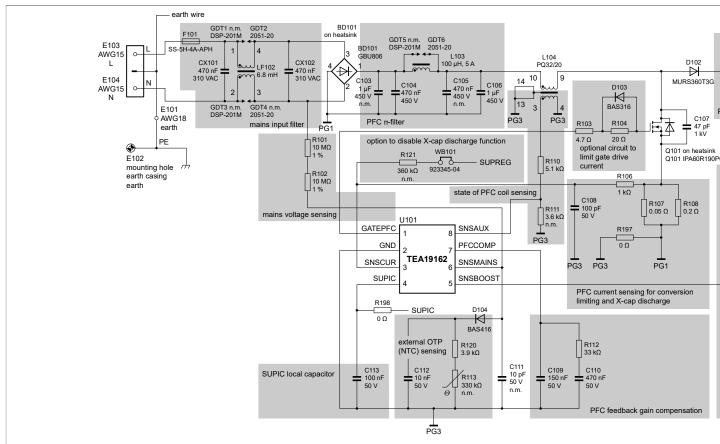

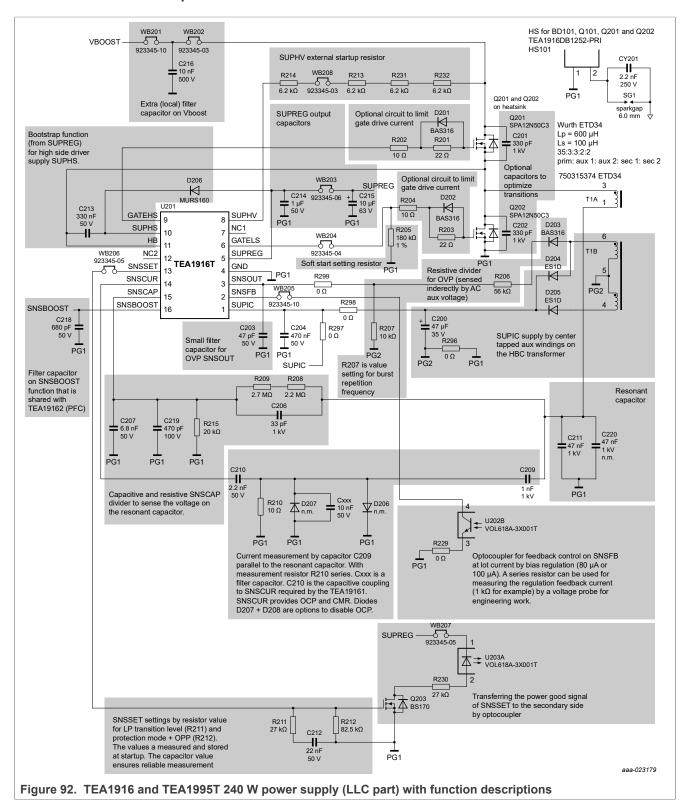

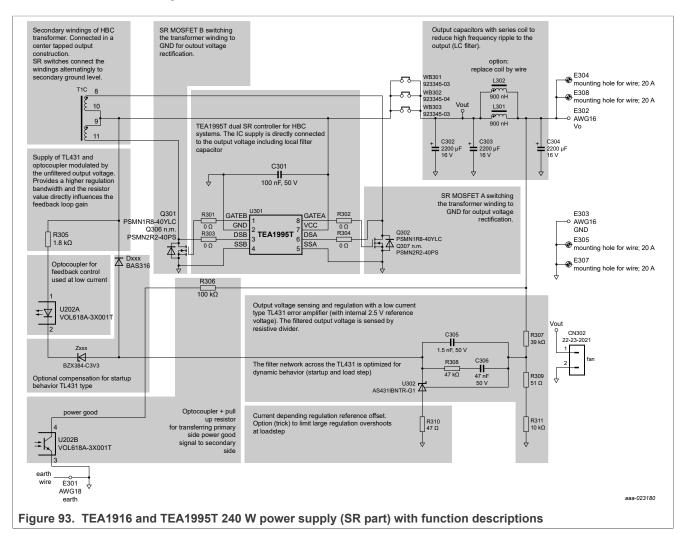

# 4 Application diagram

# 4.1 TEA19162

# TEA19161 and TEA19162 controller ICs

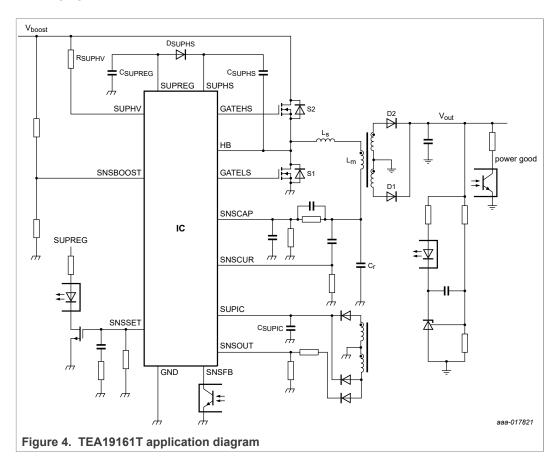

# 4.2 TEA19161T

# 5 Block diagram

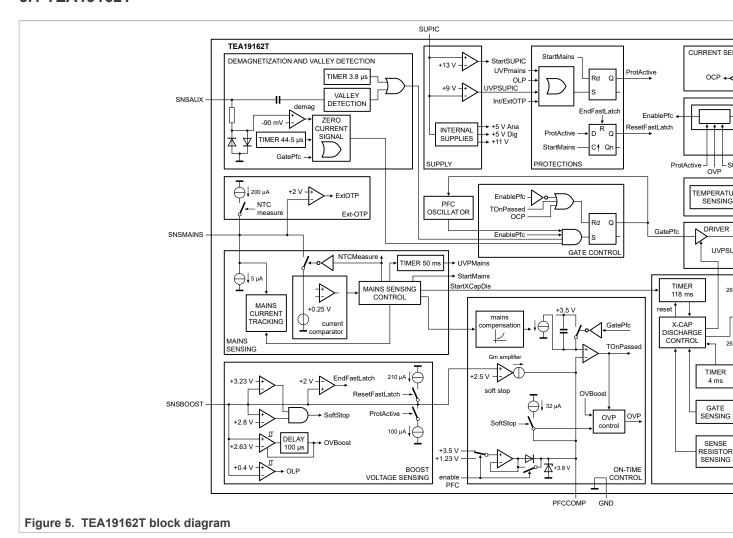

### 5.1 TEA19162T

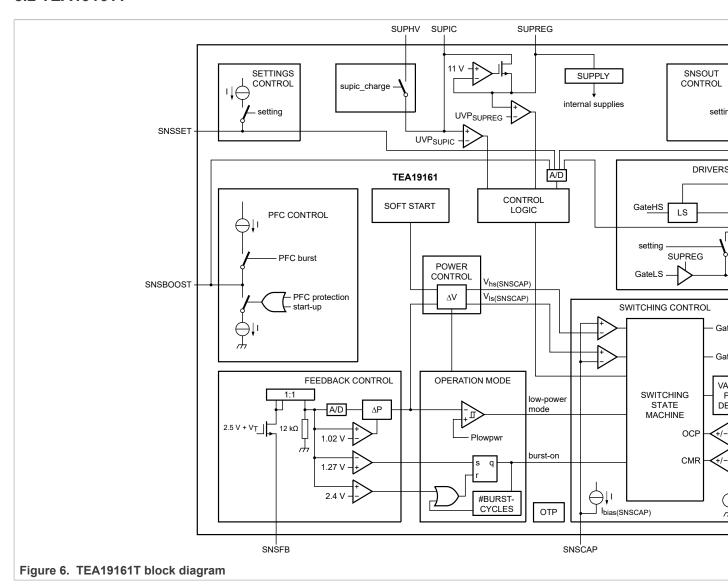

# 5.2 TEA19161T

TEA19161 and TEA19162 controller ICs

# 6 Supply functions and start-up

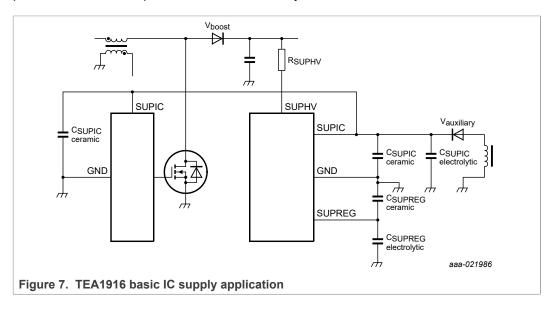

### 6.1 Basic supply system overview

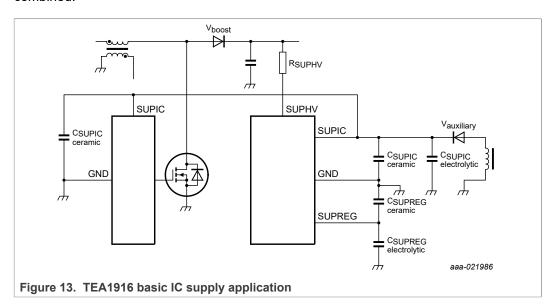

The TEA19161 has a high-voltage supply pin for start-up (SUPHV), a general supply (SUPIC), and an accurate regulated voltage output (SUPREG).

The SUPIC function can be used to supply the TEA19162 PFC controller IC. Start-up and protection levels are optimized to work as one system.

### 6.2 SUPHV high-voltage supply

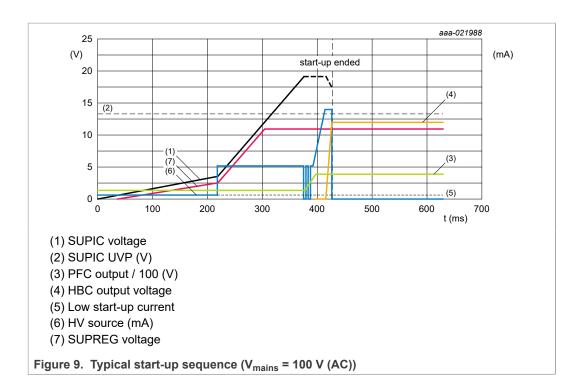

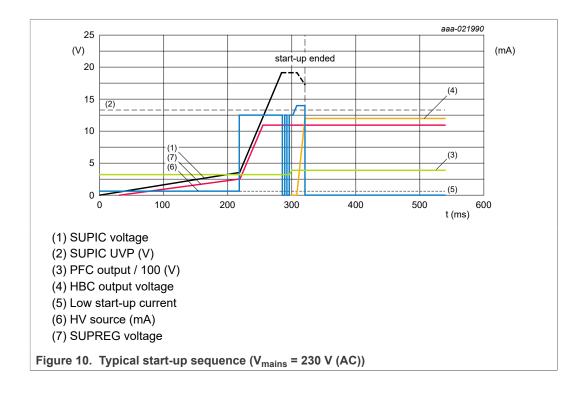

To provide the SUPHV start-up source, the TEA19161 uses an external resistor. In this way, a high start-up current can be provided without too much power dissipation in the IC. It reduces the size of the IC die for low-cost design. Most of the power during start-up is located in the external resistor. To provide a start-up of approximately 0.5 s and generate sufficient MOSFET drive current during start-up,  $R_{\text{SUPHV}}$  is typical 24 k $\Omega$ . The value of the mains voltage influences the behavior.