UBA20260 600 V driver IC for step dimmable CFLs Rev. 2 — 10 October 2011

**Product data sheet**

## 1. General description

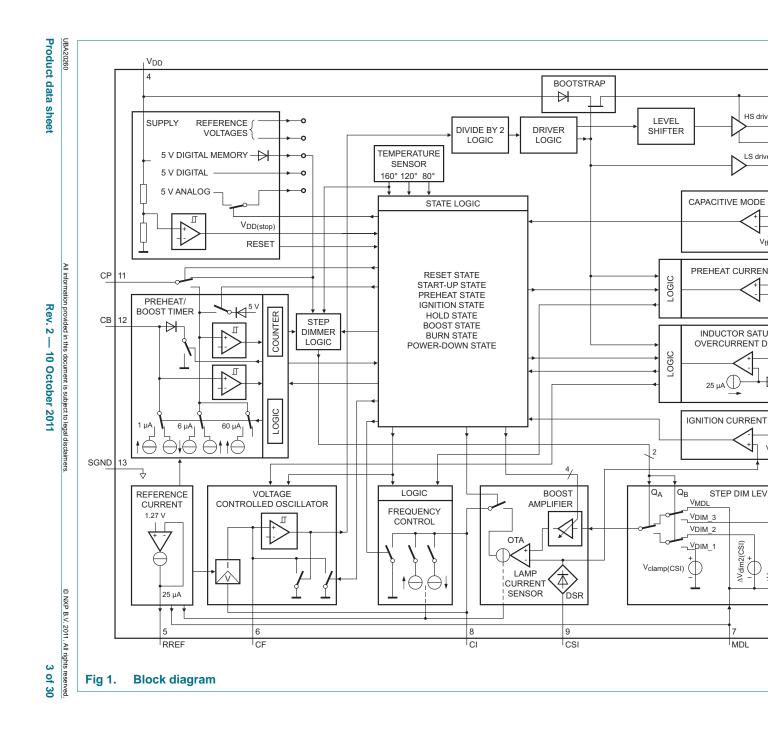

The UBA20260 is a high-voltage integrated circuit designed to control high power self-ballasted Compact Fluorescent Lamp (CFL) lighting applications. The UBA20260 is a controller circuit with advanced features for step dimming and a lamp current controlled boost feature for boosting cold (amalgam) CFLs.

The controller contains a half-bridge drive function for CFLs, a high-voltage level-shift circuit with integrated bootstrap diode, an oscillator function, a current control function for preheat and burn, a timer function and protection circuits. The UBA20260 is supplied using the dV/dt current charge supply circuit from the half-bridge circuit.

Remark: The mains voltages given in this data sheet are AC voltages.

## 2. Features and benefits

## 2.1 Half-bridge features

Integrated high-voltage level-shift function with integrated bootstrap diode

### 2.2 Preheat and ignition features

- Coil saturation protection during ignition

- Adjustable preheat time

- Adjustable preheat current

- Ignition lamp current detection

### 2.3 Lamp boost features

- Adjustable boost timing

- Fixed boost current ratio of 1.5

- Gradually boost to burn transition timing

600 V driver IC for step dimmable CFLs

#### 2.4 Dim features

- 4-level step dimming adjustment using a standard on/off mains switch

- Adjustable memory retention time for step dimming

- Adjustable minimum dimming level

### 2.5 Protection

- OverTemperature Protection (OTP)

- Capacitive Mode Protection (CMP)

- OverPower Protection (OPP)

- OverCurrent Protection (OCP) in both boost and burn states

- Power-down function

## 2.6 Other features

- Current controlled operation in both boost and burn state

- External power-down function

# 3. Applications

Step-dimmable compact fluorescent lamps above 20 W and for universal mains voltages

# 4. Ordering information

#### Table 1. Ordering information

| Type number  | Package |                                                            |          |

|--------------|---------|------------------------------------------------------------|----------|

|              | Name    | Description                                                | Version  |

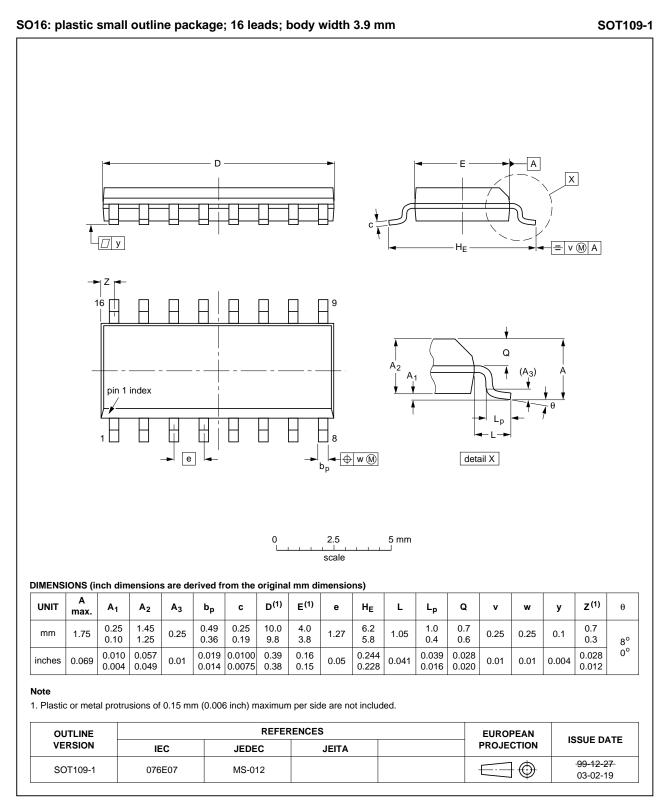

| UBA20260T/N1 | SO16    | Plastic small outline package; 16 leads; body width 3.9 mm | SOT109-1 |

600 V driver IC for step dimmable CFLs

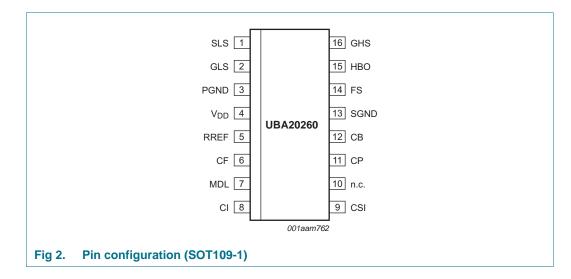

# 6. Pinning information

## 6.1 Pinning

# 6.2 Pin description

| Table 2. | Pin description |                                                           |

|----------|-----------------|-----------------------------------------------------------|

| Symbol   | Pin             | Description                                               |

| SLS      | 1               | source low-side switch input                              |

| GLS      | 2               | low-side gate driver output                               |

| PGND     | 3               | power ground                                              |

| $V_{DD}$ | 4               | low voltage supply                                        |

| RREF     | 5               | internal reference current input                          |

| CF       | 6               | voltage controlled oscillator capacitor                   |

| MDL      | 7               | minimum dimming level input                               |

| CI       | 8               | voltage controlled oscillator input integrating capacitor |

| CSI      | 9               | current feedback sense input                              |

| n.c.     | 10              | not connected                                             |

| CP       | 11              | preheat timing capacitor                                  |

| СВ       | 12              | boost timing capacitor                                    |

| SGND     | 13              | signal ground                                             |

| FS       | 14              | floating supply voltage                                   |

| HBO      | 15              | half-bridge output                                        |

| GHS      | 16              | high-side gate driver output                              |

Product data sheet

600 V driver IC for step dimmable CFLs

# 7. Functional description

## 7.1 Supply voltage

The UBA20260 is an IC for driving external half-bridge MOSFETs in self-ballasted high-power CFLs. The UBA20260 has no dimming control input but instead, four preset fixed dimming levels. Only minor adjustment of the presets is possible.

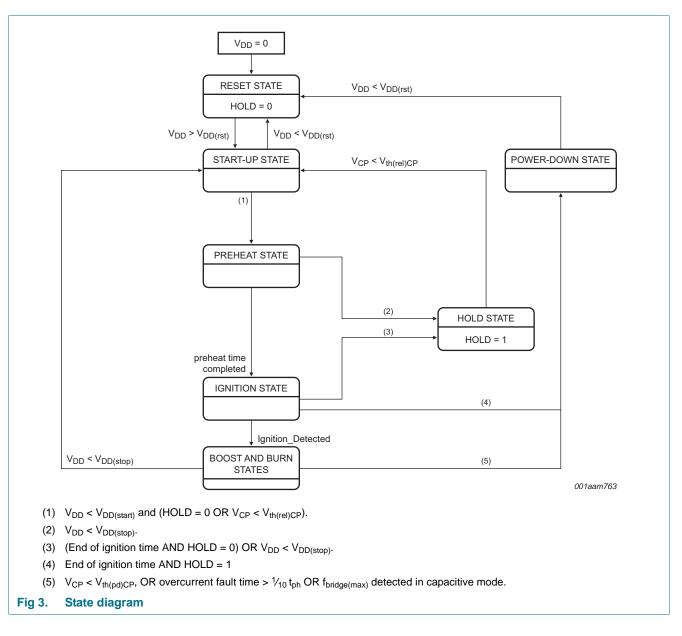

The UBA20260 is rated for a maximum continuous rectified mains voltage of 500 V (with peak 600 V). The UBA20260 includes all functions necessary for preheat, ignition and boost operation of the lamp. In addition, the IC includes the four-step dimming feature and several protective features to safeguard CFL operation. The controller states are shown in Figure 3.

## 7.2 Lamp start-up cycle

#### 7.2.1 Reset state

The UBA20260 is in the reset state when the supply voltage on the  $V_{DD}$  pin is below the  $V_{DD(rst)}$  level. In the reset state, part of the internal supply is turned off and all registers, counters and timers are undefined. The hold state latch is reset and both the external high and low side power transistors (Q1/Q2) are non-conductive.

During power-up, the low voltage supply capacitor on the V<sub>DD</sub> pin is charged through the external start-up resistor. The start-up state is entered when the voltage on the V<sub>DD</sub> pin is above the V<sub>DD(rst)</sub> level. The UBA20260 enters the reset state when the supply voltage on the V<sub>DD</sub> pin drops below V<sub>DD(rst)</sub>.

### 7.2.2 Start-up state

The start-up state is entered by charging the low voltage supply capacitor on the V<sub>DD</sub> pin through the external start-up resistor. At start-up, the High-Side (HS) transistor is non-conductive and the Low-Side (LS) transistor is conductive to enable charging of the bootstrap capacitor. This capacitor supplies the HS driver and Level shifter circuit connected between the FS and HBO pin. A DC reset circuit is integrated into the HS driver. This circuit ensures that below the FS pin lockout voltage, the output voltage  $V_{GHS} - V_{HBO}$  is zero.

When the start-up state is entered, the circuit only starts oscillating at  $f_{bridge(max)}$  when the low voltage supply (V<sub>DD</sub>) reaches the V<sub>DD(start)</sub> value. The circuit always starts oscillating at  $f_{bridge(max)}$ . The circuit enters the preheat state as soon as the capacitor connected to the CP pin is charged above the V<sub>th(CP)max</sub> voltage level. To keep oscillating, V<sub>DD</sub> must be above V<sub>DD(stop)</sub> and below the V<sub>DD(clamp)</sub> upper limit.

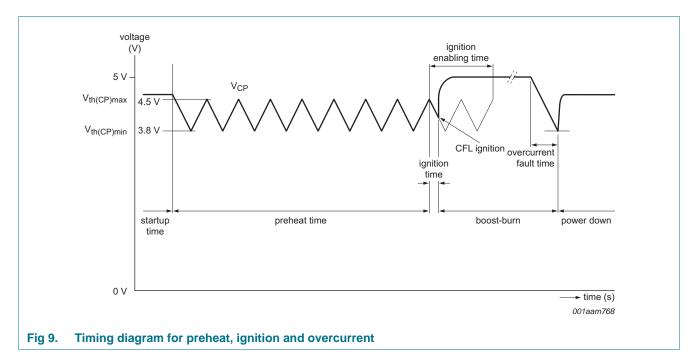

During the start-up state, the voltage on the CF pin is zero and on the CB pin is close to zero. The voltage on the CP pin rises just above  $V_{th(CP)max}$  during the start-up state as shown in Figure 9.

### 7.2.3 Preheat state

After starting at  $f_{bridge(max)}$ , the frequency decreases by charging capacitor  $C_{CI}$  using an output current circuit. The preheat current sensor circuit controls the current output circuit, until the momentary value of the voltage across sense resistor  $R_{SLS}$  reaches the fixed preheat voltage level (SLS pin). At this level, the current of the preheat current sensor reaches the charge and discharge balanced state on capacitor  $C_{CI}$  to set the half-bridge frequency.

The preheat time consists of eight saw-tooth pulses at the CP pin. The preheat time begins as soon as the capacitor on the CP pin is charged above  $V_{th(CP)max}$  value. During the preheat time, the current feedback sensor circuit (input CSI pin) is disabled.

To increase noise immunity, an internal filter of 30 ns is included at the SLS pin.

If the level on the V<sub>DD</sub> pin drops below V<sub>DD(stop)</sub> during preheat, the preheat state is immediately stopped and the circuit enters the hold state. The hold state delays a new preheat cycle by a fixed delay time. A fixed voltage drop on the preheat capacitor C<sub>CP</sub> and the fixed discharge current on the CP pin are used to set the delay time.

#### 600 V driver IC for step dimmable CFLs

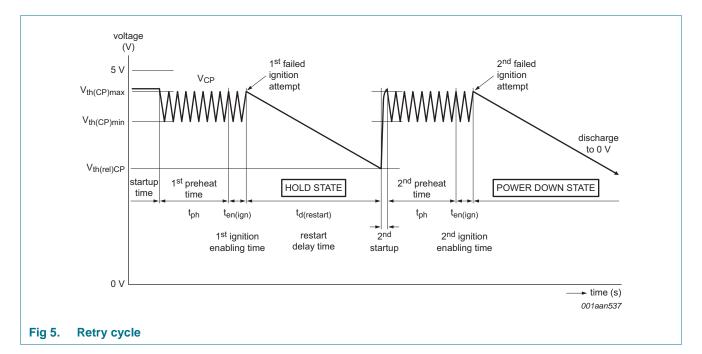

New preheat cycles start after the CP pin level slowly discharges until  $V_{CP} < V_{th(rel)CP}$  and recharges above  $V_{th(CP)max}$  provided  $V_{DD} > V_{DD(start)}$  (see Figure 5).

#### 7.2.4 Ignition state

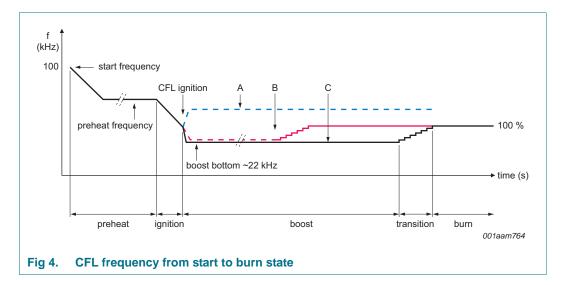

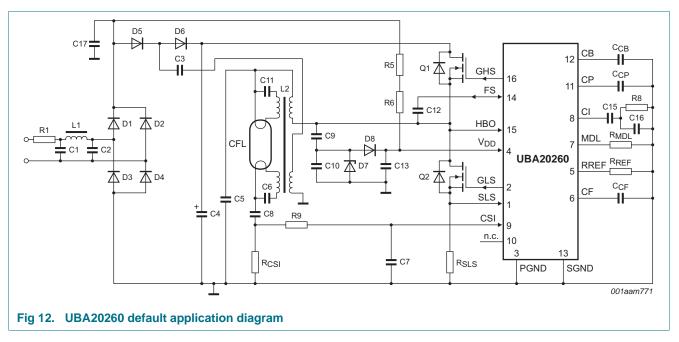

After the preheat state has been completed, the ignition state is entered. In the ignition state, the frequency sweeps down on the CI pin due to capacitor C<sub>CI</sub> charging at a fixed current as shown in Figure 4. During this continuous decrease in frequency, the circuit approaches the resonant frequency of the resonant tank (L2, C5). This action causes a high voltage across the lamp to ignite the lamp. The ignition current sensor circuit which monitors the voltage over resistor R<sub>CSI</sub> (see Figure 12) detects lamp ignition.

If the voltage on pin CSI is above the typical ignition detection threshold voltage level of 0.6 V, lamp ignition is detected. The system changes from ignition state to either the boost or burn state.

If ignition not is detected, the frequency drops further to the minimum half-bridge frequency f<sub>bridge(min)</sub> frequency. To avoid repeated ignition attempts and overheating of the application due to lamp damage, the IC only tries to ignite the lamp twice after power-up. The ignition attempt counter increments at the end of the ignition enabling time when the lamp ignition threshold voltage on the CSI pin is not exceeded. The ignition enabling time is typically  $\frac{1}{4}$  of the preheat time t<sub>ph</sub>. If a second ignition attempt also exceeds the ignition time-out period, the IC enters the power-down state (see Figure 5).

#### 600 V driver IC for step dimmable CFLs

### 7.2.5 Boost state and transition to burn state

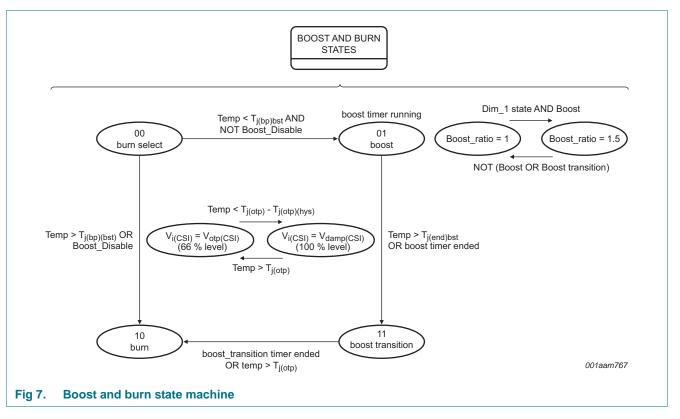

When ignition is detected, by measuring lamp current on the CSI pin, the circuit enters the boost state. Figure 7 shows the boost and burn state in more detail. In the boost state, the nominal burn state lamp current can be increased with a fixed boost ratio of 1.5. This ratio boosts the slow luminescence increase of a cold amalgam CFL lamp, provided the IC is in the DIM\_1 mode. If the IC is at a temperature ( $T_{j(bp)bst}$ ) before entering the boost state, the burn state is bypassed.

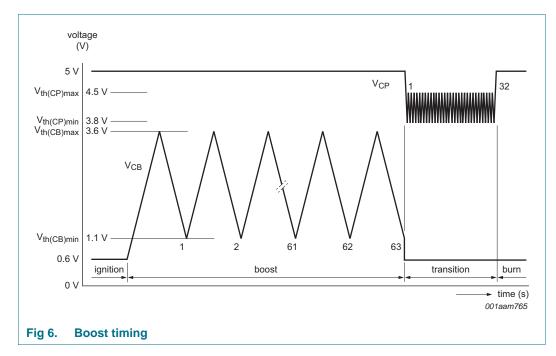

A boost timing circuit is included to determine the boost time and transition to burn time. The circuit consists of a clock generator comprising  $C_{CB}$ ,  $R_{ext(RREF)}$  and a 64-step counter. When the timer is not operating,  $C_{CB}$  is discharged below the  $V_{th(CB)min}$  level of 1.1 V. This voltage, about 0.6 V, is still higher than the level at which the comparator on  $C_{CB}$  detects if the CB pin is shorted to ground.

The boost time consists of 63 saw-tooth pulses on the CB pin, automatically followed by the transition time at the CP pin. The 32 saw-tooth pulses form the transition time from boost to burn and enables a smooth transition between the current controlled boost and burn state. The total transition time is approximately four times the preheat time (see Figure 6).

Product data sheet

#### 600 V driver IC for step dimmable CFLs

In the boost state, a lamp current feedback control is implemented to improve lamp stability (see Section 7.2.6). The lamp current has a fixed ratio of 1.5 compared to the burn state to boost the slow luminescence increase of a cold CFL lamp. In the boost to burn transition time, there is a slow 15-step ratio decrease from 1.5 down to 1. The preheat timer is reused for the transition to burn time and the boost ratio is gradually decreased in 15 steps from 1.5 to 1, within 32 saw-tooth pulses on the CP pin. Using the application values for C<sub>CB</sub> and R<sub>ext(RREF)</sub>, a boost time of more than 300 s is possible. In addition to boost bypass at a temperature of T<sub>j(bp)bst</sub> ( $\approx$  80 °C), a temperature protection function is implemented during boost state of T<sub>j(end)bst</sub> ( $\approx$  120 °C). If the temperature passes this level during boost, the transition timer is immediately started to enter the burn state faster. Effectively this reduces the boost time (see Figure 4 [B]).

The boost state current boost does not start in dim modes DIM\_2, DIM\_3 or MDL; see Figure 4[A].

**Remark:** If the CB pin is short circuited to ground, the boost function is disabled. In such a situation, the bottom frequency  $f_{bridge(min)}$  is 1.8 times higher than the boost bottom frequency  $f_{bridge(bst)min}$ .

#### 7.2.6 Burn state

After the boost state or when it is bypassed, the burn state starts. The lamp current sensor circuit remains enabled (see <u>Figure 4</u>[A]). The CSI (Current Sense Input) pin measures the voltage across sense resistor  $R_{CSI}$ . It is then passed through a Double-Sided Rectifier (DSR) circuit and fed towards an Operational Transconductor Amplifier (OTA).

When the RMS voltage on the CSI pin reaches the actual internal reference level, the lamp current sensor circuit takes over control of the lamp current. The internal current output of the OTA is transferred using an integrator on the CI pin to the input for Voltage Controlled Oscillator (VCO). The VCO regulates the frequency and as a result, the lamp current.

#### 600 V driver IC for step dimmable CFLs

### 7.2.7 Hold state

The hold state is a special state that reduces lamp flicker at deep dim levels, on or near dim and ignition threshold levels. The IC enters the hold state after an ignition failure or when the low supply voltage  $V_{DD}$  drops below  $V_{DD(stop)}$  in the ignition or preheat states (see Figure 3).

A repeated drop in supply voltage below  $V_{DD(stop)}$  in preheat or ignition states, does not increment the ignition attempt counter. The hold state is entered, delaying a new preheat cycle with the same time delay/mechanism by the hold state retention time as shown in Figure 5.

When CP is below  $V_{th(rel)CP}$ , the IC is released from the hold state and moves to the start-up state as shown in Figure 3. Alternatively, the hold state ends when the supply voltage drops below  $V_{DD(rst)}$  and the IC is reset.

With a 470 nF capacitor on the CP pin, the typical hold state retention delay is between 1 s and 1.7 s. This delay is dependent on where the preheat cycle was cut-off on the rising or falling edge of the preheat timing. The retention time for a failed ignition always starts from the top of the rising edge on the CP pin (see Figure 5).

In the hold state, a hold state latch is set (hold state latch = 1) and the oscillator is stopped. In addition, the HS transistor is non-conductive and the LS transistor is conducting.

The voltage on the V<sub>DD</sub> pin alternates between V<sub>DD(start)</sub> and V<sub>DD(stop)</sub> until the voltage on the CP pin reaches V<sub>th(rel)CP</sub> (see Figure 5). The alternating supply voltage is caused by the current drawn by the IC supply pin V<sub>DD</sub>. The supply current is less than 220  $\mu$ A, when

the supply voltage V<sub>DD</sub> rises between V<sub>DD(stop)</sub> and V<sub>DD(start)</sub>. Typically, the supply current is 2 mA when V<sub>DD</sub> falls between V<sub>DD(start)</sub> and V<sub>DD(stop)</sub>. More current is drawn during the fall in V<sub>DD</sub> because the internal analog supply is turned on when V<sub>DD</sub> > V<sub>DD(start)</sub>. This function enables the comparators to monitor the voltage on the CP pin and if the supply voltage V<sub>DD</sub> falls below V<sub>DD(stop)</sub>.

## 7.3 Oscillation and timing

### 7.3.1 Oscillator control

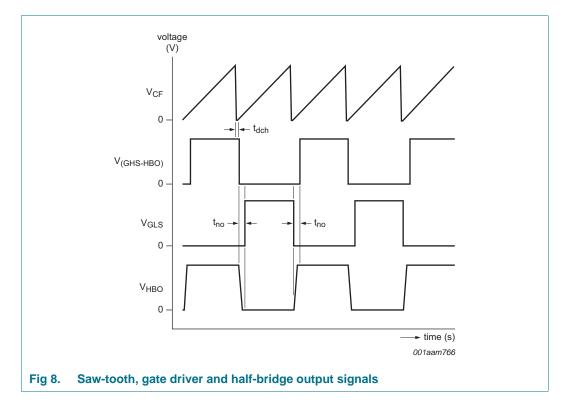

The internal oscillator is a VCO which generates a saw-tooth waveform between the  $V_{th(CF)max}$  level and 0 V. Capacitor  $C_{CF}$ , resistor  $R_{ext(RREF)}$  and the voltage on the CI pin determine the saw-tooth frequency.  $R_{ext(RREF)}$  and  $C_{CF}$  determine the minimum and maximum switching frequencies. Their ratio is internally fixed. Two ratios are available, the ratio between  $f_{bridge(max)}$  and  $f_{bridge(min)}$  is 2.5 and the ratio between  $f_{bridge(max)}$  and  $f_{bridge(bst)min}$  is 4.6. The saw-tooth frequency is twice the half-bridge frequency.

Transistors HS (Q1) and LS (Q2) are switched to conducting at a duty cycle of approximately 50 %. An overview of the oscillator signal and driver signals is shown in Figure 8. The oscillator starts oscillating at  $f_{bridge(max)}$ . The non-overlap time between the gate driver signals V<sub>GLS</sub> and V<sub>GHS</sub> is  $t_{no}$ .

#### 600 V driver IC for step dimmable CFLs

### 7.3.2 Combined timing circuit

A combined timing circuit is used to determine the preheat time, ignition enabling time and overcurrent time (see Figure 9). C<sub>CP</sub>, R<sub>ext(RREF)</sub> and the counter comprise the clock generator circuit. When the timer is not running, C<sub>CP</sub> is charged to 5 V. The timing circuit starts operating after the start-up state when the V<sub>DD</sub> supply voltage has reached V<sub>DD(start)</sub> and the voltage on the CP pin passes V<sub>th(CP)max</sub>. The preheat time consists of eight saw-tooth pulses on the CP pin as shown in Figure 9.

The maximum ignition enabling time after the preheat phase is two complete saw-tooth pulses. During the boost and burn state, part of the timer is used to generate the maximum overcurrent time (more than one half of the saw-tooth pulse). If a continuous overcurrent is detected, the timer starts.

## 7.4 Step dimming

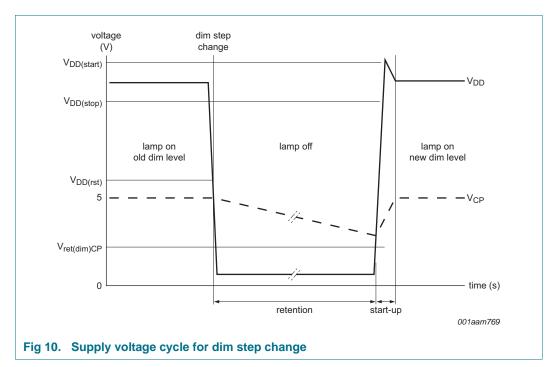

The UBA20260 uses the step dimming method of dimming a lamp load. This method enables the lamp to operate in four different light output level modes including full power. The four different dim level modes can be selected by toggling the supply voltage which is made possible by toggling the mains voltage switch.

To change the dim step, the low supply voltage must be above  $V_{DD(start)}$ . In addition, the voltage must drop below  $V_{DD(rst)}$ , irrespective of whether the IC is in the preheat, ignition, boost or burn states (see Figure 10).

The discharge time of capacitor  $C_{CP}$  (while the  $V_{DD}$  power supply is off) sets step memory retention time. When the voltage on the CP pin drops below  $V_{ret(dim)CP}$  (2 V typical), the step memory is lost. The next time the supply is powered on, the lamp turns on at full brightness. Using the default components, the retention time is  $\pm$  3 s. The retention time calculation can be found in <u>Section 11 on page 22</u>.

#### 600 V driver IC for step dimmable CFLs

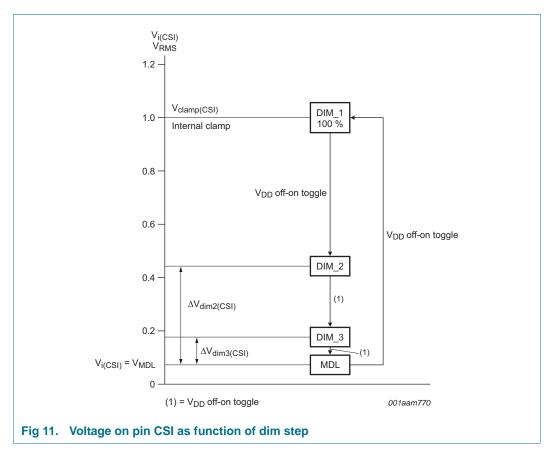

Four internal references determine the actual internal set point levels used for the different step dim levels. Depending on the selected dim level, the current control feedback loop regulates the voltage on the CSI pin. In this way, it ensures that  $V_{i(CSI)}$  is equal to one of the selected internal set point voltages. The sequence of the four dim steps shown in Figure 11 is as follows:

- The lamp is switched off longer than the memory retention time: the IC starts up in the DIM\_1 mode (lamp is 100 % on, no dimming)

- After lamp off/on toggling, the IC twice enters the DIM\_2 mode: the lamp is dimmed to approximately 66 % <sup>(1)</sup> of its initial light output

- The next lamp off/on toggling, the IC enters the DIM\_3 mode: the lamp is dimmed approximately 33 % <sup>(1)</sup> of its initial light output

- Toggling the lamp off/on again: the IC enters the MDL (Minimum Dimming Level) mode. This level equals approximately 10 % <sup>(1)</sup> of the initial light output

- Renewed toggling enters the DIM\_1 mode again.

Where  $^{(1)} = R_{MDL} = 2 k\Omega$

Product data sheet

#### 600 V driver IC for step dimmable CFLs

As the internal step reference voltages are independent from the mains voltage, the lamp current output is kept constant. Making the lamp current output not susceptible to line voltage fluctuations. The MDL level sets the minimum lamp current level and is adjusted using the MDL pin. An accurate minimum dimming voltage level is set using an internal reference current and an external resistor  $R_{MDL}$ . The internal reference current is derived from the internal band gap reference circuit and resistor  $R_{ext(RREF)}$ . The other two step dimming levels are set at a fixed voltage offset referenced to the adjusted MDL level. This means that these levels shift by the same voltage as the MDL shifts. When the MDL level is at the default level, the light output in DIM\_2, DIM\_3 and MDL modes is approximately 66 %, 33 % and 5 % from nominal.

## 7.5 Protection functions and Power-down mode

## 7.5.1 Coil saturation protection

CSP is integrated into the IC to allow the use of small CFL lamps and use of small coils. Saturation of these coils is detected and excessive overcurrent due to saturation is prevented. CSP is only enabled during the ignition state. A cycle-by-cycle control mechanism is used to limit voltages and currents in the resonant circuit when there is no or delayed ignition. It prevents coil saturation, limits high peak currents and the dissipation in the half-bridge power transistors.

Coil saturation is detected by monitoring the voltage across the R<sub>SLS</sub> resistor. A trigger is generated when this voltage exceeds the V<sub>th(sat)SLS</sub> level. When saturation is detected, a fixed current  $\Delta I_{o(sat)CF}$  is injected into the C<sub>CF</sub> capacitor to shorten the half-bridge

switching cycle. The injected current is maintained until the end of the switching cycle. This action immediately increases the half-bridge switching frequency. Additionally, for each successive cycle that coil saturation is detected, capacitor  $C_{CI}$  discharges enabling ignition time-out detection in the ignition state.

CSP is triggered when the voltage on the SLS pin exceeds V<sub>th(sat)SLS</sub> (typically 2.5 V). The voltage V<sub>i(SLS)</sub> on the SLS pin is determined by the external resistor R<sub>SLS</sub> value and also sets the preheat current.

#### 7.5.2 Overcurrent protection

OCP is active in both the burn and boost states but not during boost transition. Overcurrent is detected, when the peak voltage of the absolute value across the current sense resistor connected to the SLS pin exceeds the OCP reference level V<sub>th(ocp)SLS</sub>. A current I<sub>o(CP)</sub> is then sunk from the capacitor connected to the CP pin for the next full cycle.

If overcurrent is not present at the end of this cycle, the current is disabled. A current, equal to  $I_{o(CP)}$  is sourced to the CP pin instead. If overcurrent occurs in more than half the number of cycles, a net discharging of the capacitor connected to the CP pin occurs. When the voltage on the CP pin drops below  $V_{th(CP)min}$ , the IC enters Power-down mode. During a continuous overcurrent condition, the overcurrent fault time of  $t_{fault(oc)}$  takes  $\pm$   $1_{\!/9}$   $t_{ph}$  after which the IC enters Power-down mode. The  $V_{th(ocp)SLS}$  level is the same as the  $V_{th(sat)SLS}$  level during the ignition state.

#### 7.5.3 Overpower protection

OPP is active in the boost and burn state. The lamp current is limited and regulated in all dim step states to the internal dim step reference voltage levels. These reference voltage levels are derived from an internal reference voltage. Consequently, supply voltage fluctuations in the mains supply voltage during overvoltage situations do not affect these reference voltage levels.

When the lamp is in the first dim mode (no dimming), the current is limited and regulated to the nominal lamp current. In addition, in the boost state the first dim mode boosted by a factor of 1.5.

### 7.5.4 Capacitive mode protection

CMP is active in the ignition, burn and boost states and during boost transition. The signal across resistor  $R_{SLS}$  also provides information about the half-bridge switching behavior. When conditions are normal, the current flows from the LS transistor source to the half-bridge when the LS transistor is switched on. This results in a negative voltage on the SLS pin.

As the circuit yields to capacitive mode, the voltage becomes smaller and eventually reverses polarity. CMP prevents this action by checking if the voltage on the SLS pin is above the  $V_{th(capm)SLS}$  level.

If the voltage across resistor  $R_{SLS}$  is above the  $V_{th(capm)SLS}$  threshold when the LS transistor is switched on, the circuit recognizes it as capacitive mode. When capacitive mode is detected, the currents from the OTA, which normally regulate the lamp current, are disabled. Then the capacitive mode sink current  $I_{o(CI)}$  is enabled.

The capacitive mode sink current starts to discharge the capacitor/resistor circuitry on the CI pin and as a result, gradually increases the half-bridge frequency. Discharging continues for the remainder of the current switching cycle ensuring the total current on the CI pin is equal to the sink current. If capacitive mode persists, the action is repeated until capacitive mode is no longer detected. If capacitive mode is no longer detected, the OTA takes over the regulation again.

If the conditions for capacitive mode persist, OTA regulates the system back to capacitive mode and the protection takes over again. The system operates on the edge of capacitive mode.

When in the boost and burn states, the half-bridge load is capacitive at higher frequencies, CMP eventually drives the half-bridge to the maximum frequency  $f_{bridge(max)}$ . This causes the IC to enter Power-down mode.

#### 7.5.5 Overtemperature protection

The OTP circuit is designed to prevent the device from overheating in hazardous environments. The circuit is triggered when the temperature exceeds the maximum temperature value  $T_{j(otp)}$ . OTP changes the lamp current to the level equal to the  $V_{otp(CSI)}$  level. This condition remains until the temperature decreases by  $\pm$  20 °C =  $T_{j(otp)hys}$ . After this decrease in temperature, the lamp current level returns to the nominal level.

### 7.5.6 Power-down mode

Power-down mode is entered when:

- The overcurrent time exceeds the maximum overcurrent fault time t<sub>fault(oc)</sub> or if the overcurrent occurs in more than half the number of cycles when V<sub>th(CP)min</sub> is reached

- If during boost or burn state, f<sub>bridge(max)</sub> is reached due to capacitive mode detection

- Two consecutive failed lamp ignition attempts

In Power-down mode, the oscillator is stopped, the HS transistor is non-conductive and the LS transistor is conductive. The V<sub>DD</sub> supply is internally clamped. The circuit is released from Power-down mode by lowering the low voltage supply below V<sub>DD(rst)</sub> (mains switch reset).

An option is available which enables the IC to enter Power-down mode using external logic. The external power-down option is only available when the IC is in the boost or burn state. The CP pin is used to enable the external power-down option. When the CP pin is connected using a 10 k $\Omega$  resistor to the PGND pin or the SGND pin, V<sub>CP</sub> is pulled below V<sub>th(pd)CP</sub>. The IC then enters Power-down mode.

**Remark:** Do not connect the CP pin directly to pins PGND or SGND. Always connect in series to pins PGND or SGND with a 10 k $\Omega$  resistor. This action avoids the IC being not starting up because of excessive currents flowing during the reset and start-up states.

600 V driver IC for step dimmable CFLs

# 8. Limiting values

#### Table 3. Limiting values

In accordance with the Absolute Maximum Rating System (IEC 60134).[1]

| Symbol                 | Parameter                          | Conditions                          | Min   | Max   | Unit |

|------------------------|------------------------------------|-------------------------------------|-------|-------|------|

| General                |                                    |                                     |       |       |      |

| R <sub>ext(RREF)</sub> | external resistance on<br>pin RREF | Fixed nominal value 33 k $\Omega$   | 30    | 36    | kΩ   |

| SR                     | slew rate                          | on pins HBO with respect to PGND    | -4    | +4    | V/ns |

| Tj                     | junction temperature               |                                     | -40   | +150  | °C   |

| T <sub>amb</sub>       | ambient temperature                | P = 0.8 W                           | -40   | +85   | °C   |

| T <sub>stg</sub>       | storage temperature                |                                     | -55   | +150  | °C   |

| Currents               |                                    |                                     |       |       |      |

| I <sub>i(CF)</sub>     | input current on pin CF            |                                     | 0     | 200   | μΑ   |

| Voltages               |                                    |                                     |       |       |      |

| V <sub>HBO</sub>       | voltage on pin HBO                 | operating                           | -     | 500   | V    |

|                        |                                    | during 1 s                          | -     | 600   | V    |

| V <sub>FS</sub>        | voltage on pin FS                  | with respect to HBO                 | -0.3  | +14   | V    |

| V <sub>DD</sub>        | supply voltage                     |                                     | -0.3  | +14   | V    |

| V <sub>i(CSI)</sub>    | input voltage on pin CSI           |                                     | -5    | +5    | V    |

| V <sub>i(SLS)</sub>    | input voltage on pin<br>SLS        |                                     | -6    | +6    | V    |

| V <sub>CI</sub>        | voltage on pin Cl                  |                                     | 0     | 3.5   | V    |

| V <sub>MDL</sub>       | voltage on pin MDL                 | LPF used as input pin               | 0     | 5     | V    |

| ESD                    |                                    |                                     |       |       |      |

| V <sub>ESD</sub>       | electrostatic discharge            | human body model:                   | -2000 | +2000 | V    |

|                        | voltage                            | all pins, except pins 14, 15 and 16 |       |       |      |

|                        |                                    | pins 14, 15 and 16                  | -1000 | +1000 | V    |

|                        |                                    | charged device model:               |       |       |      |

|                        |                                    | all pins                            | -500  | +500  | V    |

[1] Latch-up in accordance with SNW-FQ-303 on all pins.

# 9. Thermal characteristics

| Table 4.             | Thermal characteristics                     |                           |     |      |

|----------------------|---------------------------------------------|---------------------------|-----|------|

| Symbol               | Parameter                                   | Conditions                | Тур | Unit |

| R <sub>th(j-a)</sub> | thermal resistance from junction to ambient | in free air; SO16 package | 100 | K/W  |

# **10. Characteristics**

#### Table 5. Characteristics

$V_{DD} = 13 \text{ V}; V_{FS} - V_{HBO} = 13 \text{ V}; T_{amb} = 25 \text{ °C};$  settings according to default setting see <u>Table 6 on page 25</u>, all voltages referenced to PGND and SGND, positive currents flow into the UBA20260, unless otherwise specified.

| Symbol                      | Parameter                           | Conditions                                                                                                                                 |            | Min   | Тур   | Max   | Uni |

|-----------------------------|-------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|------------|-------|-------|-------|-----|

| Start-up state              |                                     |                                                                                                                                            |            |       |       |       |     |

| Pin V <sub>DD</sub>         |                                     |                                                                                                                                            |            |       |       |       |     |

| V <sub>DD(rst)</sub>        | reset supply voltage                | HS = off; LS = on                                                                                                                          |            | 5.7   | 6.2   | 6.7   | V   |

| V <sub>DD(stop)</sub>       | stop supply voltage                 |                                                                                                                                            |            | 9.6   | 10    | 10.4  | V   |

| V <sub>DD(start)</sub>      | start supply voltage                |                                                                                                                                            |            | 11.9  | 12.4  | 12.9  | V   |

| V <sub>DD(hys)</sub>        | hysteresis of supply voltage        | start-stop                                                                                                                                 |            | 2.2   | 2.4   | 2.6   | V   |

| V <sub>DD(clamp)</sub>      | clamp supply voltage                | $I_{DD(clamp)} = 5 \text{ mA}$                                                                                                             |            | 13    | 13.4  | 13.8  | V   |

| I <sub>DD(clamp)</sub>      | clamp supply current                | $V_{DD(clamp)} = 14 V$                                                                                                                     |            | 20    | 30    | -     | mΑ  |

| I <sub>DD(startup)</sub>    | start-up supply current             | V <sub>DD</sub> = 9 V                                                                                                                      |            | -     | 190   | 220   | μΑ  |

| I <sub>DD(pd)</sub>         | power-down supply current           | V <sub>DD</sub> = 9 V                                                                                                                      |            | -     | 190   | 220   | μΑ  |

| I <sub>DD</sub>             | supply current                      | default setting; $V_{CI} = V_{CI(clamp)};$<br>$V_{CB} = 0 V$                                                                               | <u>[1]</u> | -     | 1.6   | 2     | mA  |

| High-voltage                | supply                              |                                                                                                                                            |            |       |       |       |     |

| Pins GHS, HB                | O and FS                            |                                                                                                                                            |            |       |       |       |     |

| I <sub>leak</sub>           | leakage current                     | 500 V on high-voltage pins                                                                                                                 |            | -     | -     | 30    | μΑ  |

| Voltage contre              | olled oscillator                    |                                                                                                                                            |            |       |       |       |     |

| Output pin CI               |                                     |                                                                                                                                            |            |       |       |       |     |

| V <sub>CI(max)</sub>        | maximum voltage on pin CI           |                                                                                                                                            |            | 2.7   | 3     | 3.3   | V   |

| V <sub>hr(CI)</sub>         | headroom voltage on pin CI          | $V_{clamp(Cl)} = V_{hr(Cl)} + V_{Cl(max)}$ ; burn and boost state                                                                          |            | -     | 80    | -     | mV  |

| Output pin CF               |                                     |                                                                                                                                            |            |       |       |       |     |

| f <sub>bridge(min)</sub>    | minimum bridge frequency            | $\label{eq:CF} \begin{array}{l} C_{CF} = 100 \; pF; \; V_{CI} = V_{clamp(CI)}; \\ V_{CB} = 0 \; V \end{array}$                             | [2]        | 38    | 40    | 42    | kHz |

| f <sub>bridge(max)</sub>    | maximum bridge frequency            | $C_{CF} = 100 \text{ pF}; V_{CI} = 0 \text{ V}$                                                                                            | [2]        | 88    | 100   | 112   | kHz |

| f <sub>bridge(bst)min</sub> | minimum boost bridge frequency      | $C_{CF} = 100 \text{ pF}; V_{CI} = V_{clamp(CI)}$                                                                                          | [2]        | 21    | 22    | 23    | kHz |

| t <sub>no</sub>             | non-overlap time                    | V <sub>HBO</sub> rising edge                                                                                                               |            | 1.3   | 1.5   | 1.7   | μS  |

|                             |                                     | V <sub>HBO</sub> falling edge                                                                                                              |            | 1.3   | 1.5   | 1.7   | μS  |

| V <sub>th(CF)max</sub>      | maximum threshold voltage on pin CF | $\label{eq:CF} \begin{split} C_{CF} &= 100 \text{ pF};  \text{V}_{CI} = \text{V}_{clamp(CI)}; \\ \text{V}_{CB} &= 0  \text{V} \end{split}$ |            | 2.4   | 2.5   | 2.6   | V   |

| I <sub>o(bst)CF</sub>       | boost output current on pin CF      | $V_{CF}$ = 1.5 V; $V_{CB}$ = $V_{clamp(Cl)}$                                                                                               |            | -12.3 | -11.8 | -11.3 | μΑ  |

| I <sub>o(CF)min</sub>       | minimum output current on pin CF    | $\label{eq:VCF} \begin{array}{l} V_{CF} = 1.5 \ V; \ V_{CB} = 0 \ V; \\ V_{CI} = V_{clamp(CI)} \end{array}$                                |            | -22.8 | -21.8 | -20.8 | V   |

| I <sub>o(CF)max</sub>       | maximum output current on pin CF    | V <sub>CF</sub> = 1.5 V; V <sub>CB</sub> = 0 V                                                                                             |            | -67   | -60   | -53   | μA  |

| Gate driver or              | utput                               |                                                                                                                                            |            |       |       |       |     |

| Output pins GI              | LS, GHS                             |                                                                                                                                            |            |       |       |       |     |

| I <sub>source(drv)</sub>    | driver source current               | $V_G$ = 4 V (GLS or GHS);<br>V <sub>HBO</sub> = 0 V; V <sub>DD</sub> = V <sub>FS</sub> = 12 V                                              |            | -105  | -90   | -75   | mA  |

| R <sub>sink(drv)</sub>      | driver sink resistance              | $V_G = 2 V$ (GLS or GHS);<br>$V_{HBO} = 0 V$ ; $V_{DD} = V_{FS} = 12 V$                                                                    |            | 13    | 15.5  | 18    | Ω   |

### 600 V driver IC for step dimmable CFLs

#### Table 5. Characteristics ...continued

$V_{DD} = 13 \text{ V}; V_{FS} - V_{HBO} = 13 \text{ V}; T_{amb} = 25 \text{ °C};$  settings according to default setting see <u>Table 6 on page 25</u>, all voltages referenced to PGND and SGND, positive currents flow into the UBA20260, unless otherwise specified.

| Boot strap dioo<br>V <sub>F</sub><br>Preheat curren | de<br>forward voltage                  |                                                                                                                                                             |               |      |      |    |

|-----------------------------------------------------|----------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|------|------|----|

| •                                                   | forward voltage                        |                                                                                                                                                             |               |      |      |    |

| Preheat curren                                      |                                        | bootstrap diode; $I_{FS} = 5 \text{ mA}$ ;<br>( $V_F = V_{DD} - V_{FS}$ )                                                                                   | 1.3           | 1.7  | 2.1  | V  |

|                                                     | t sensor                               |                                                                                                                                                             |               |      |      |    |

| Input pin SLS                                       |                                        |                                                                                                                                                             |               |      |      |    |

| I <sub>I(SLS)</sub>                                 | input current on pin SLS               | $V_{i(SLS)} = 0.4 V$                                                                                                                                        | -             | -    | 1    | μΑ |

| V <sub>ph(SLS)</sub>                                | preheat voltage on pin SLS             |                                                                                                                                                             | <u>3</u> 0.57 | 0.60 | 0.63 | V  |

| Output pin CI                                       |                                        |                                                                                                                                                             |               |      |      |    |

| I <sub>o(source)</sub> CI                           | source output current on pin CI        | $V_{CI} = 2 \text{ V}; \text{ V}_{i(SLS)} < 0.6 \text{ V}$                                                                                                  | -10.6         | -9.6 | -8.6 | μA |

| I <sub>o(sink)Cl</sub>                              | sink output current on pin CI          | $V_{CI} = 2 \text{ V}; \text{ V}_{i(SLS)} < 0.6 \text{ V}$                                                                                                  | 26            | 29   | 32   | μA |

| Preheat timer, i                                    | ignition timer, overcurrent timer fu   | nction                                                                                                                                                      |               |      |      |    |

| t <sub>ph</sub>                                     | preheat time                           | $C_{CP}$ = 470 nF; $R_{ext(RREF)}$ = 33 k $\Omega$                                                                                                          | -             | 0.93 | -    | S  |

| t <sub>en(ign)</sub>                                | ignition enable time                   | $C_{CP}$ = 470 nF; $R_{ext(RREF)}$ = 33 k $\Omega$                                                                                                          | -             | 0.22 | -    | s  |

| t <sub>fault(oc)</sub>                              | overcurrent fault time                 | $\label{eq:CP} \begin{array}{l} C_{CP} = 470 \text{ nF}; \ R_{ext(RREF)} = 33 \text{ k}\Omega; \\ \text{initial voltage } V_{CP} = 5 \text{ V} \end{array}$ | -             | 0.1  | -    | S  |

| t <sub>ret(dim)</sub>                               | dimming retention time                 | $C_{CP}$ = 470 nF; $R_{ext(RREF)}$ = 33 kΩ;<br>initial voltage V <sub>CP</sub> = 5 V                                                                        | -             | 2.8  | -    | S  |

| I <sub>o(CP)</sub>                                  | output current on pin CP               | $V_{CP}$ = 4 V; source (–); sink (+)                                                                                                                        | 5.5           | 5.9  | 6.3  | μΑ |

| i ot(aiiii)oi                                       | dimming retention current on<br>pin CP | Current into pin CP; $V_{DD} = 0 V$ ;<br>initial $V_{CP} = 5 V$                                                                                             | -             | 0.5  | -    | μA |

| V <sub>th(CP)</sub> min                             | minimum threshold voltage on pin CP    | $V_{CF} = 0 \text{ V},  V_{CI} = 2 \text{ V}$                                                                                                               | -             | 3.8  | -    | V  |

|                                                     | maximum threshold voltage on pin CP    | $V_{CF} = 0 \text{ V}, \text{ V}_{CI} = 2 \text{ V}$                                                                                                        | -             | 4.5  | -    | V  |

| V <sub>hys(CP)</sub>                                | hysteresis voltage on pin CP           |                                                                                                                                                             | 0.6           | 0.7  | 0.8  | V  |

|                                                     | pull-up current on pin CP              | V <sub>CP</sub> = 3.8 V                                                                                                                                     | -             | -60  | -    | μA |

| V <sub>ret(dim)CP</sub>                             | dimming retention voltage on<br>pin CP | $V_{DD} = 0 V$                                                                                                                                              | -             | 2    | -    | V  |

| · (( · ) ·                                          | power-down threshold voltage on pin CP | burn state; 10 k $\Omega$ connected in series                                                                                                               | -             | 1    | -    | V  |

| V <sub>th(rel)CP</sub>                              | release threshold voltage on pin CP    | hold state                                                                                                                                                  | -             | 2.7  | -    | V  |

| Boost timer                                         |                                        |                                                                                                                                                             |               |      |      |    |

| Pin CB                                              |                                        |                                                                                                                                                             |               |      |      |    |

| t <sub>bst</sub>                                    | boost time                             | C <sub>CB</sub> = 470 nF; T <sub>j</sub> < 80 °C                                                                                                            | -             | 148  | -    | S  |

| I <sub>o(CB)</sub>                                  | output current on pin CB               | V <sub>CB</sub> = 2.35 V; source (-); sink (+)                                                                                                              | 0.8           | 1    | 1.2  | μA |

| V <sub>th(CB)min</sub>                              | minimum threshold voltage on pin<br>CB |                                                                                                                                                             | -             | 1.1  | -    | V  |

| V <sub>th(CB)max</sub>                              | maximum threshold voltage on pin CB    |                                                                                                                                                             | -             | 3.6  | -    | V  |

| V <sub>hys(CB)</sub>                                | hysteresis voltage on pin CB           |                                                                                                                                                             | 2.3           | 2.5  | 2.7  | V  |

|                                                     | boost bypass junction temperature      | T <sub>j</sub> sensed at end of ignition time                                                                                                               | 65            | 80   | 95   | °C |

|                                                     | boost end junction temperature         | T <sub>j</sub> during boost time                                                                                                                            | 105           | 120  | 135  | °C |

### 600 V driver IC for step dimmable CFLs

#### Table 5. Characteristics ...continued

$V_{DD} = 13 \text{ V}; V_{FS} - V_{HBO} = 13 \text{ V}; T_{amb} = 25 \text{ °C};$  settings according to default setting see <u>Table 6 on page 25</u>, all voltages referenced to PGND and SGND, positive currents flow into the UBA20260, unless otherwise specified.

| l <sub>det(dis)bst</sub><br>t <sub>t(bst-burn)</sub><br>Pin CSI | boost disable detection current                     | $V_{CB} = 0 V$                                                                                     | -30            | -25 | -20  | μA |

|-----------------------------------------------------------------|-----------------------------------------------------|----------------------------------------------------------------------------------------------------|----------------|-----|------|----|

|                                                                 | transition time - for an los of the                 |                                                                                                    |                |     |      | μл |

| Pin CSI                                                         | transition time from boost to burn                  | C <sub>CP</sub> = 470 nF; T <sub>j</sub> < 80 °C                                                   | -              | 3.6 | -    | S  |

|                                                                 |                                                     |                                                                                                    |                |     |      |    |

| N <sub>LCBR</sub>                                               | lamp current boost ratio                            | $V_{i(CSI)}$ in boost state versus $V_{i(CSI)}$ in burn state; default start-up state (no dimming) | 1.4            | 1.5 | 1.6  | V  |

| Coil saturation                                                 | n protection and overcurrent detect                 | tion                                                                                               |                |     |      |    |

| nput: pin SLS                                                   |                                                     |                                                                                                    |                |     |      |    |

| V <sub>th(sat)</sub> SLS                                        | saturation threshold voltage on pin SLS             | ignition state                                                                                     | 2.3            | 2.5 | 2.7  | V  |

| V <sub>th(ocp)</sub> SLS                                        | overcurrent protection threshold voltage on pin SLS | boost state and burn state                                                                         | 2.3            | 2.5 | 2.7  | V  |

| leb                                                             | leading edge blanking time                          | detection disabled for first part of GLS time                                                      | -              | 800 | -    | ns |

| Output pin CI                                                   |                                                     |                                                                                                    |                |     |      |    |

| o(sink)Cl                                                       | sink output current on pin CI                       | $V_{CI} = 2 \text{ V}; V_{i(SLS)} > V_{th(sat)SLS}; cycle clocked$                                 | 26             | 29  | 32   | μA |

| Output pin CF                                                   |                                                     |                                                                                                    |                |     |      |    |

| ∆I <sub>o(sat)</sub> CF                                         | saturation output current difference on pin CF      | V <sub>CF</sub> = 1.5 V; ignition state;<br>LS switch = on                                         | -              | 160 | -    | μA |

| gnition currer                                                  | nt detection                                        |                                                                                                    |                |     |      |    |

| nput pin CSI                                                    |                                                     |                                                                                                    |                |     |      |    |

| Vth(det)ign(CSI)                                                | ignition detection threshold voltage on pin CSI     |                                                                                                    | 0.55           | 0.6 | 0.65 | V  |

| tw(det)ign(min)                                                 | minimum ignition detection pulse width              | $V_{th(det)ign(CSI)} = 0.75 \text{ V}$ square pulse                                                | 685            | 885 | 1085 | ns |

| Capacitive mo                                                   | de detection                                        |                                                                                                    |                |     |      |    |

| Input pin SLS                                                   |                                                     |                                                                                                    |                |     |      |    |

| V <sub>th(capm</sub> )SLS                                       | capacitive mode threshold voltage on pin SLS        |                                                                                                    | <u>[4]</u> –15 | -5  | 0    | m\ |

| Output pin CI                                                   |                                                     |                                                                                                    |                |     |      |    |

| o(sink)Cl                                                       | sink output current on pin Cl                       | $V_{i(SLS)} > V_{th(capm)SLS}$ ; $V_{CI} = 2 V$ ;<br>ignition state or boost and burn<br>state     | 26             | 29  | 32   | μA |

| Lamp current                                                    | sensor and dimming control                          |                                                                                                    |                |     |      |    |

| nput pin CSI                                                    |                                                     |                                                                                                    |                |     |      |    |

| R <sub>i(CSI)</sub>                                             | input resistance on pin CSI                         | V <sub>i(CSI)</sub> = 1 V                                                                          | 1              | -   | -    | Mg |

|                                                                 |                                                     | $V_{i(CSI)} = -1 V$                                                                                | 40             | 50  | 60   | kΩ |

| √ <sub>i(CSI)</sub>                                             | input voltage on pin CSI                            | rectification linear for operation                                                                 | -2.5           | -   | +2.5 | V  |

|                                                                 |                                                     | minimum dim level;<br>$R_{ext(RREF)} = 33 \text{ k}\Omega; R_{MDL} = 2 \text{ k}\Omega$            | 44             | 50  | 56   | m\ |

| V <sub>clamp(CSI)</sub>                                         | clamping voltage on pin CSI                         | RMS voltage; clamp active; default start-up burn state; 100 % on                                   | -              | 1   | -    | V  |

#### 600 V driver IC for step dimmable CFLs

#### Table 5. Characteristics ...continued

$V_{DD} = 13 \text{ V}; V_{FS} - V_{HBO} = 13 \text{ V}; T_{amb} = 25 \text{ °C};$  settings according to default setting see <u>Table 6 on page 25</u>, all voltages referenced to PGND and SGND, positive currents flow into the UBA20260, unless otherwise specified.

|                        |                                                               |                                                                                                                                                                                                                       | ,     |     |       |      |

|------------------------|---------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-----|-------|------|

| Symbol                 | Parameter                                                     | Conditions                                                                                                                                                                                                            | Min   | Тур | Max   | Unit |

| $\Delta V_{dim2(CSI)}$ | dimming 2 voltage difference on<br>pin CSI                    | RMS voltage; offset from $V_{i(CSI)}$ at DIM_2 compared to MDL                                                                                                                                                        | 330   | 350 | 370   | mV   |

| $\Delta V_{dim3(CSI)}$ | dimming 3 voltage difference on pin CSI                       | RMS voltage; offset from $V_{i(CSI)}$ at DIM_3 compared to MDL                                                                                                                                                        | 90    | 100 | 110   | mV   |

| Output pin CI          |                                                               |                                                                                                                                                                                                                       |       |     |       |      |

| I <sub>o(CI)</sub>     | output current on pin CI                                      | burn state; V <sub>Cl</sub> = 2 V; source (–)<br>and sink (+)                                                                                                                                                         | 85    | 95  | 105   | μA   |

| Input pin MDL          | (minimum dimming level)                                       |                                                                                                                                                                                                                       |       |     |       |      |

| Isource(MDL)           | source current on pin MDL                                     |                                                                                                                                                                                                                       | -26.3 | -25 | -23.7 | μA   |

| V <sub>MDL</sub>       | voltage on pin MDL                                            | $R_{ext(RREF)} = 33 \text{ k}\Omega; R_{MDL} = 2 \text{ k}\Omega$                                                                                                                                                     | -     | 50  | -     | mV   |

| Temperature p          | protection                                                    |                                                                                                                                                                                                                       |       |     |       |      |

| T <sub>j(otp)</sub>    | overtemperature protection junction temperature               |                                                                                                                                                                                                                       | 145   | 160 | 170   | °C   |

| T <sub>j(otp)hys</sub> | hysteresis overtemperature<br>protection junction temperature |                                                                                                                                                                                                                       | 10    | 20  | 30    | °C   |

| Input pin CSI          |                                                               |                                                                                                                                                                                                                       |       |     |       |      |

| V <sub>otp(CSI)</sub>  | overtemperature protection voltage on pin CSI                 | $ \begin{array}{l} \text{RMS voltage; } R_{\text{ext}(\text{RREF})} = 33 \text{ k}\Omega; \\ R_{\text{MDL}} = 2 \text{ k}\Omega;  T_{j} > T_{j(\text{opt})} - T_{j(\text{hys})(\text{otp})} \end{array} \end{array} $ | 380   | 400 | 420   | mV   |

[1] See <u>Table 6 on page 25</u> for the default settings.

[2] The half-bridge output switching frequency (HBO). The saw-tooth frequency on pin CF is twice as high.

[3] Data sampling of V<sub>ph(SLS)</sub> is performed at the end of the LS power MOSFET conduction period in preheat state.

[4] Data sampling of V<sub>th(capm)SLS</sub> is performed at the start of conduction of the LS power MOSFET, in all states with oscillator active.

#### 600 V driver IC for step dimmable CFLs

# **11. Application information**

### **11.1 Design equations**

All described equations are only valid for  $R_{ext(RREF)} = 33 \text{ k}\Omega$ .

### 11.1.1 C<sub>CP</sub> related timing equations

#### • Preheat time

$$t_{ph} = \frac{C_{CP}}{I_{o(CP)}} \times (16 \times V_{hys(CP)} + 5 - V_{th(CP)max})$$

(1)

### • Ignition enabling time

$$t_{en(ign)} = \frac{C_{CP}}{I_{o(CP)}} \times 4 \times V_{hys(CP)}$$

(2)

#### • Overcurrent fault time

$$t_{fault(oc)} = \frac{C_{CP}}{I_{o(CP)}} \times (5 - V_{th(CP)min})$$

(3)

#### • Transition to burn time

$$t_{t(bst-burn)} = \frac{C_{CP}}{I_{o(CP)}} \times (64 \times V_{hys(CP)} + 5 - V_{th(CP)max})$$

(4)

#### Retain time step dimming

$$t_{ret(dim)} = \frac{C_{CP}}{I_{ret(dim)CP}} \times (5 - V_{ret(dim)CP})$$

(5)

#### • Restart delay time

$$t_{d(restart)} = C_{CP} \times \frac{(V_{th(CP)max} - V_{th(rel)CP})}{I_{restart(CP)}}$$

(6)

Where  $I_{restart(CP)} = 0.5 \ \mu A$  (typical).

### 11.1.2 C<sub>CB</sub> related timing equation

#### Boost time

$$t_{bst} = \frac{C_{CB}}{I_{o(CB)}} \times (126 \times V_{hys(CB)} + V_{th(CB)min} - 0.6)$$

(7)

#### 600 V driver IC for step dimmable CFLs

## 11.1.3 C<sub>CF</sub> related frequency equations

• Maximum bridge frequency

$$f_{bridge(max)} = \frac{0.5}{\frac{C_{CF} + C_{par}}{I_{o(CF)max}} \times V_{th(CF)max} + t_{dch}}$$

(8)

Where  $C_{par}$  = 4.7 pF and  $t_{dch}$  = 0.4  $\mu s.$

#### • Minimum bridge frequency with disabled boost

$$f_{bridge(min)} = \frac{0.5}{\frac{C_{CF} + C_{par}}{I_{o(CF)min}} \times V_{th(CF)max} + t_{dch}}$$

(9)

#### • Minimum bridge frequency with enabled boost

$$f_{bridge(bst)min} = \frac{0.5}{\frac{C_{CF} + C_{par}}{I_{o(bst)CF}} \times V_{th(CF)max} + t_{dch}}$$

(10)

### 11.1.4 R<sub>SLS</sub> related preheat current

$$I_{ph(M)} = \frac{V_{ph(SLS)}}{R_{SLS}}$$

(11)

$$I_{ph(RMS)} \approx \frac{V_{ph(SLS)}}{R_{SLS} \times \sqrt{3}}$$

(12)

### 11.1.5 R<sub>MDL</sub> related minimum dimming level

#### • MDL threshold voltage

$$V_{MDL} = R_{MDL} \times I_{source(MDL)} \tag{13}$$

## 600 V driver IC for step dimmable CFLs

# **11.2 Application Diagram**

Detailed in <u>Table 6</u> is a list of typical application components. See <u>Figure 12</u>.

## **NXP Semiconductors**

## 600 V driver IC for step dimmable CFLs

| Table 6.         Typical application components for a 230 V (AC) mains application |                              |                                                  |

|------------------------------------------------------------------------------------|------------------------------|--------------------------------------------------|

| Reference                                                                          | Component                    | Description                                      |

| R1                                                                                 | 4.7 Ω                        | 2 W fusible resistor                             |

| R5; R6                                                                             | 220 kΩ                       |                                                  |

| R8                                                                                 | 2.2 kΩ                       |                                                  |

| R9                                                                                 | 1 kΩ                         |                                                  |

| R <sub>REF</sub>                                                                   | 33 kΩ; 1 %                   |                                                  |

| R <sub>SLS</sub>                                                                   | 1.2 Ω                        | adjust for preheat current                       |

| R <sub>MDL</sub>                                                                   | 1 kΩ                         | adjust for minimum lamp current                  |

| R <sub>CSI</sub>                                                                   | 8.2 Ω                        | adjust for nominal lamp current                  |

| C1                                                                                 | 47 nF; 630 V                 |                                                  |

| C2                                                                                 | 22 nF; 630 V                 |                                                  |

| C3                                                                                 | 47 nF; 400 V                 |                                                  |

| C4                                                                                 | 10 μF; 400 V                 |                                                  |

| C5                                                                                 | 4.7 nF; 1 kV                 | lamp capacitor                                   |

| C6                                                                                 | 68 nF; 250 V                 |                                                  |

| C7                                                                                 | 100 pF                       |                                                  |

| C8                                                                                 | 47 nF; 400 V                 |                                                  |

| C9                                                                                 | 560 pF; 500 V                | V <sub>DD</sub> charge pump capacitor            |

| C10                                                                                | not mounted                  |                                                  |

| C11                                                                                | 68 nF; 250 V                 |                                                  |

| C12                                                                                | 100 nF                       |                                                  |

| C13                                                                                | 470 nF                       |                                                  |

| C15                                                                                | 220 nF                       |                                                  |

| C16                                                                                | not mounted                  |                                                  |

| C17                                                                                | 22 nF; 400 V                 |                                                  |

| C <sub>CB</sub>                                                                    | 150 nF                       |                                                  |

| C <sub>CP</sub>                                                                    | 330 nF                       |                                                  |

| C <sub>CF</sub>                                                                    | 100 pF; 2 %                  |                                                  |

| Q1; Q2                                                                             | SPS02N60C3                   |                                                  |

| D1 to D4                                                                           | 1N4007                       |                                                  |

| D5; D6                                                                             | 1N4937                       |                                                  |

| D7                                                                                 | BZX84JC12                    |                                                  |

| D8                                                                                 | BAS20                        |                                                  |

| L1                                                                                 | 4.7 mH                       | mains filter inductor; I <sub>SAT</sub> = 300 mA |

| L2                                                                                 | Würth Elektronik: 7608000902 | 2000/21.31.3/22 μH lamp inductor                 |

Table 6.

Typical application components for a 230 V (AC) mains application

## **NXP Semiconductors**

# **UBA20260**

600 V driver IC for step dimmable CFLs

# 12. Package outline

#### Fig 13. Package outline SOT109-1 (SO16)

All information provided in this document is subject to legal disclaimers.

600 V driver IC for step dimmable CFLs

# 13. Abbreviations

| Table 7. A | bbreviations                           |

|------------|----------------------------------------|

| Acronym    | Description                            |

| CFL        | Compact Fluorescent Lamp               |

| CMP        | Capacitive Mode Protection             |

| DSR        | Double-Sided Rectifier                 |

| ESD        | ElectroStatic Discharge                |

| HS         | High-Side                              |

| LS         | Low-Side                               |

| MDL        | Minimum Dimming Level                  |

| OCP        | OverCurrent Protection                 |

| OPP        | OverPower Protection                   |

| ΟΤΑ        | Operational Transconductance Amplifier |

| OTP        | OverTemperature Protection             |

| RMS        | Root Mean Square                       |

| SR         | Slew Rate                              |

| UVLO       | UnderVoltage LockOut                   |

| VCO        | Voltage Controlled Oscillator          |

# 14. Revision history

### Table 8.Revision history

| Document ID   | Release date | Data sheet status    | Change notice | Supersedes    |

|---------------|--------------|----------------------|---------------|---------------|

| UBA20260 v. 2 | 20111010     | Product data sheet   | -             | UBA20260 v. 1 |

| UBA20260 v. 1 | 20110909     | Objective data sheet | -             | -             |

# **15. Legal information**

## 15.1 Data sheet status

| Document status[1][2]          | Product status <sup>[3]</sup> | Definition                                                                            |

|--------------------------------|-------------------------------|---------------------------------------------------------------------------------------|

| Objective [short] data sheet   | Development                   | This document contains data from the objective specification for product development. |

| Preliminary [short] data sheet | Qualification                 | This document contains data from the preliminary specification.                       |

| Product [short] data sheet     | Production                    | This document contains the product specification.                                     |

[1] Please consult the most recently issued document before initiating or completing a design.

[2] The term 'short data sheet' is explained in section "Definitions".

[3] The product status of device(s) described in this document may have changed since this document was published and may differ in case of multiple devices. The latest product status information is available on the Internet at URL <a href="http://www.nxp.com">http://www.nxp.com</a>.

## 15.2 Definitions

**Draft** — The document is a draft version only. The content is still under internal review and subject to formal approval, which may result in modifications or additions. NXP Semiconductors does not give any representations or warranties as to the accuracy or completeness of information included herein and shall have no liability for the consequences of use of such information.

Short data sheet — A short data sheet is an extract from a full data sheet with the same product type number(s) and title. A short data sheet is intended for quick reference only and should not be relied upon to contain detailed and full information. For detailed and full information see the relevant full data sheet, which is available on request via the local NXP Semiconductors sales office. In case of any inconsistency or conflict with the short data sheet, the full data sheet shall prevail.