# **Complete Thermal System Management Controller**

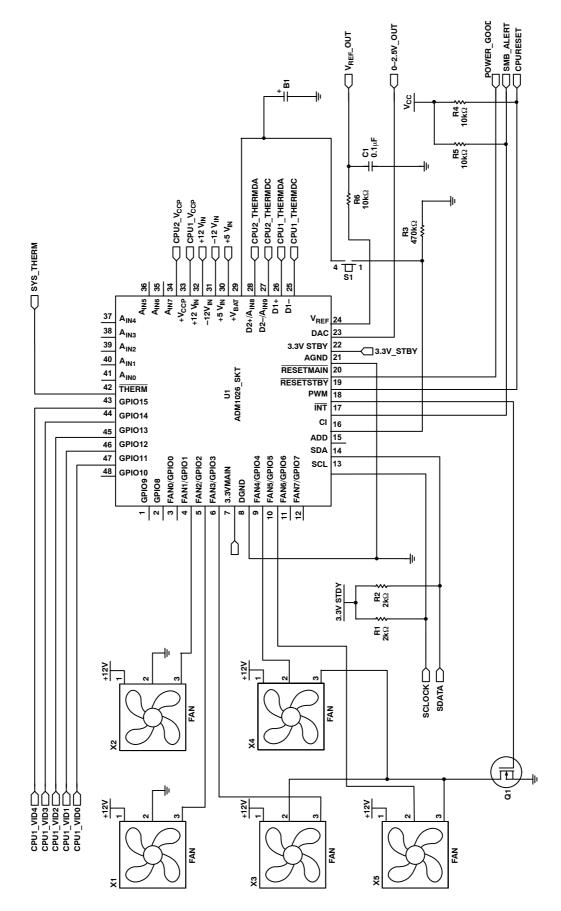

The ADM1026 is a complete system hardware monitor for microprocessor-based systems, providing measurement and limit comparison of various system parameters. The ADM1026 has up to 19 analog measurement channels. Fifteen analog voltage inputs are provided, five of which are dedicated to monitoring +3.3 V, +5.0 V, and  $\pm 12$  V power supplies, and the processor core voltage. The ADM1026 can monitor two other power supply voltages by measuring its own V<sub>CC</sub> and the main system supply. One input (two pins) is dedicated to a remote temperature-sensing diode. Two additional pins can be configured as general-purpose analog inputs to measure 0 V to 2.5 V, or as a second temperature sensing input. The eight remaining inputs are general-purpose analog inputs with a range of 0 V to 2.5 V or 0 V to 3.0 V. The ADM1026 also has an on-chip temperature sensor.

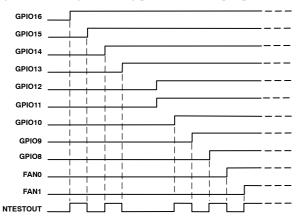

The ADM1026 has eight pins that can be configured for fan speed measurement or as general-purpose logic I/O pins. Another eight pins are dedicated to general-purpose logic I/O. An additional pin can be configured as a general-purpose I/O or as the bidirectional THERM pin.

Measured values can be read out via a 2-wire serial system management bus, and values for limit comparisons can be programmed over the same serial bus. The high speed, successive approximation ADC allows frequent sampling of all analog channels to ensure a fast interrupt response to any out-of-limit measurement.

#### Features

- Up to 19 Analog Measurement Channels (Including Internal Measurements)

- Up to 8 Fan Speed Measurement Channels

- Up to 17 General-Purpose Logic I/O Pins

- Remote Temperature Measurement with Remote Diode (Two Channels)

- On-Chip Temperature Sensor

- Analog and PWM Fan Speed Control Outputs

- 2-Wire Serial System Management Bus (SMBus)

- 8 kB On-Chip EEPROM

- Full SMBus 1.1 Support Includes Packet Error Checking (PEC)

- Chassis Intrusion Detection

- Interrupt Output (SMBAlert)

- Reset Input, Reset Outputs

- Thermal Interrupt (THERM) Output

- Limit Comparison of All Monitored Values

- This is a Pb-Free Device\*

# Applications

- Network Servers and Personal Computers

- Telecommunications Equipment

- Test Equipment and Measuring Instruments

\*For additional information on our Pb-Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

# **ON Semiconductor®**

http://onsemi.com

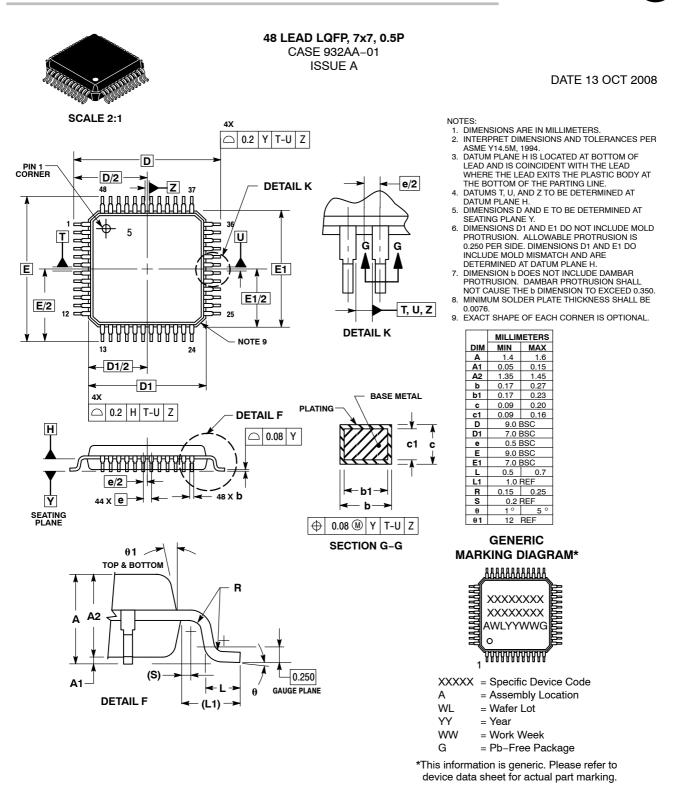

LQFP-48 CASE 932

# MARKING DIAGRAM

| ADM1026JSTZ | = Special Device Code |

|-------------|-----------------------|

| #           | = Pb-Free Package     |

| YYWW        | = Date Code           |

# **ORDERING INFORMATION**

See detailed ordering and shipping information in the package dimensions section on page 54 of this data sheet.

# Table 1. ABSOLUTE MAXIMUM RATINGS

| Parameter                                                                | Rating                          | Unit |

|--------------------------------------------------------------------------|---------------------------------|------|

| Positive Supply Voltage (V <sub>CC</sub> )                               | 6.5                             | V    |

| Voltage on +12 V <sub>IN</sub> Pin                                       | +20                             | V    |

| Voltage on –12 V <sub>IN</sub> Pin                                       | -20                             | V    |

| Voltage on Analog Pins                                                   | -0.3 to (V <sub>CC</sub> + 0.3) | V    |

| Voltage on Open-drain Digital Pins                                       | -0.3 to +6.5                    | V    |

| Input Current at Any Pin                                                 | ±5                              | mA   |

| Package Input Current                                                    | ±20                             | mA   |

| Maximum Junction Temperature (T <sub>JMAX</sub> )                        | 150                             | °C   |

| Storage Temperature Range                                                | –65 to +150                     | °C   |

| Lead Temperature, Soldering<br>Vapor Phase (60 sec)<br>Infrared (15 sec) | 215<br>200                      | °C   |

| ESD Rating<br>-12 V <sub>IN</sub> Pin<br>All Other Pins                  | 1000<br>2000                    | V    |

Stresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.

NOTE: This device is ESD sensitive. Use standard ESD precautions when handling.

#### **Table 2. THERMAL CHARACTERISTICS**

| Package Type | θ <sub>JA</sub> | θ <sub>JC</sub> | Unit |

|--------------|-----------------|-----------------|------|

| 48-lead LQFP | 50              | 10              | °C/W |

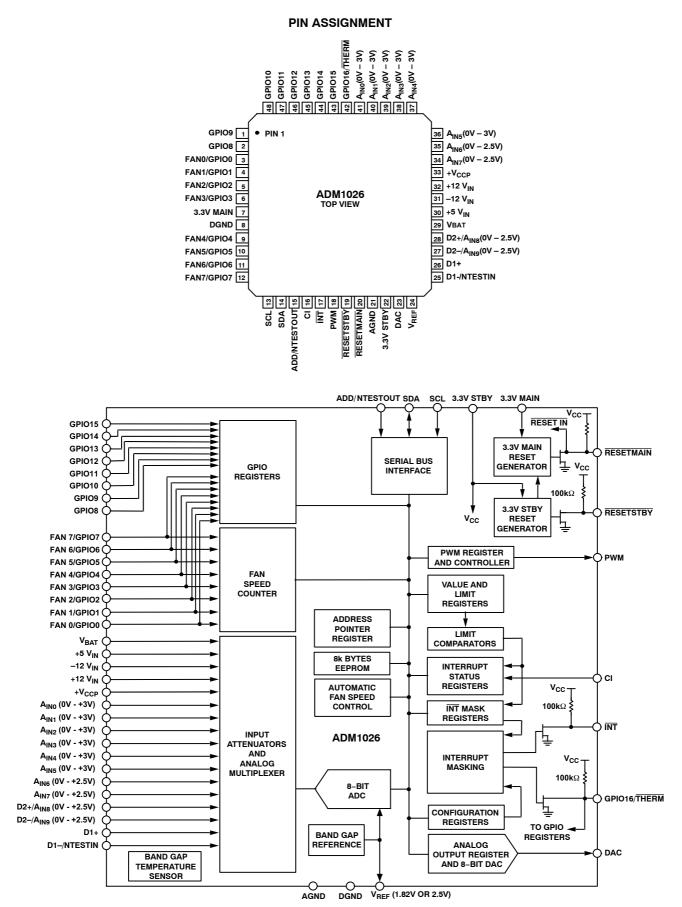

# **Table 3. PIN ASSIGNMENT**

| Pin No. | Mnemonic     | Туре                     | Description                                                                                                                                                                                                                         |

|---------|--------------|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | GPIO9        | Digital I/O <sup>†</sup> | General-purpose I/O pin that can be configured as digital inputs or outputs.                                                                                                                                                        |

| 2       | GPIO8        | Digital I/O <sup>†</sup> | General-purpose I/O pin that can be configured as digital inputs or outputs.                                                                                                                                                        |

| 3       | FAN0/GPIO0   | Digital I/O              | Fan tachometer input with internal 10 k $\Omega$ pullup resistor to 3.3 V STBY. Can be reconfigured as a general-purpose, open drain, digital I/O pin.                                                                              |

| 4       | FAN1/GPIO1   | Digital I/O              | Fan tachometer input with internal 10 k $\Omega$ pullup resistor to 3.3 V STBY. Can be reconfigured as a general-purpose, open drain, digital I/O pin.                                                                              |

| 5       | FAN2/GPIO2   | Digital I/O              | Fan tachometer input with internal 10 k $\Omega$ pullup resistor to 3.3 V STBY. Can be reconfigured as a general-purpose, open drain, digital I/O pin.                                                                              |

| 6       | FAN3/GPIO3   | Digital I/O              | Fan tachometer input with internal 10 k $\Omega$ pullup resistor to 3.3 V STBY. Can be reconfigured as a general-purpose, open drain, digital I/O pin.                                                                              |

| 7       | 3.3 V MAIN   | Analog Input             | Monitors the main 3.3 V system supply. Does not power the device.                                                                                                                                                                   |

| 8       | DGND         | Ground                   | Ground pin for digital circuits.                                                                                                                                                                                                    |

| 9       | FAN4/GPIO4   | Digital I/O              | Fan tachometer input with internal 10 k $\Omega$ pullup resistor to 3.3 V STBY. Can be reconfigured as a general-purpose, open drain, digital I/O pin.                                                                              |

| 10      | FAN5/GPIO5   | Digital I/O              | Fan tachometer input with internal 10 k $\Omega$ pullup resistor to 3.3 V STBY. Can be reconfigured as a general-purpose, open drain, digital I/O pin.                                                                              |

| 11      | FAN6/GPIO6   | Digital I/O              | Fan tachometer input with internal 10 k $\Omega$ pullup resistor to 3.3 V STBY. Can be reconfigured as a general-purpose, open drain, digital I/O pin.                                                                              |

| 12      | FAN7/GPIO7   | Digital I/O              | Fan tachometer input with internal 10 k $\Omega$ pullup resistor to 3.3 V STBY. Can be reconfigured as a general-purpose, open drain, digital I/O pin.                                                                              |

| 13      | SCL          | Digital Input            | Open Drain Serial Bus Clock. Requires a 2.2 k $\Omega$ pullup resistor.                                                                                                                                                             |

| 14      | SDA          | Digital I/O              | Serial Bus Data. Open drain I/O. Requires a 2.2 k $\Omega$ pullup resistor.                                                                                                                                                         |

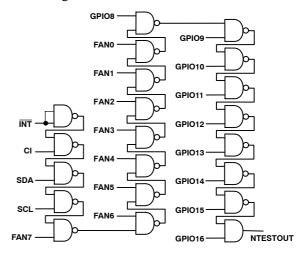

| 15      | ADD/NTESTOUT | Digital Input            | This is a three-state input that controls the two LSBs of the serial bus address. It also functions as the output for NAND tree testing.                                                                                            |

| 16      | CI           | Digital Input            | An active high input that captures a chassis intrusion event in Bit 6 of Status Register 4. This bit remains set until cleared, as long as battery voltage is applied to the $V_{BAT}$ input, even when the ADM1026 is powered off. |

# Table 3. PIN ASSIGNMENT

| Pin No. | Mnemonic             | Туре                     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|---------|----------------------|--------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 17      | ĪNT                  | Digital Output           | Interrupt Request (Open Drain). The output is enabled when Bit 1 of the configuration register is set to 1. The default state is disabled. It has an on-chip 100 k $\Omega$ pullup resistor.                                                                                                                                                                                                                                                                                                         |

| 18      | PWM                  | Digital Output           | Open drain pulse width modulated output for control of the fan speed. This pin defaults to high for the 100% duty cycle for use with NMOS drive circuitry. If a PMOS device is used to drive the fan, the PWM output may be inverted by setting Bit 1 of Test Register 1 = 1.                                                                                                                                                                                                                        |

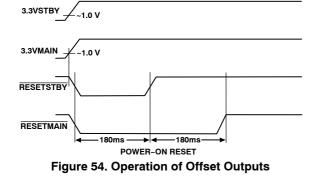

| 19      | RESETSTBY            | Digital Output           | Power-on Reset. 5 mA driver (weak 100 k $\Omega$ pullup), active low output (100 k $\Omega$ pullup) with a 180 ms typical pulse width. RESETSTBY is asserted whenever 3.3 V STBY is below the reset threshold. It remains asserted for approximately 180 ms after 3.3 V STBY rises above the reset threshold.                                                                                                                                                                                        |

| 20      | RESETMAIN            | Digital I/O              | Power-on Reset. 5 mA driver (weak 100 k $\Omega$ pullup), active low output (100 k $\Omega$ pullup) with a 180 ms typical pulse width. RESETMAIN is asserted whenever 3.3 V MAIN is below the reset threshold. It remains asserted for approximately 180 ms after 3.3 V MAIN rises above the reset threshold. If, however, 3.3 V STBY rises with or before 3.3 V MAIN, then RESETMAIN remains asserted for 180 ms after RESETSTBY is deasserted. Pin 20 also functions as an active low RESET input. |

| 21      | AGND                 | Ground                   | Ground pin for analog circuits.                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 22      | 3.3 V STBY           | Power Supply             | Supplies 3.3 V power. Also monitors the 3.3 V standby power rail.                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 23      | DAC                  | Analog Output            | 0 V to 2.5 V output for analog control of the fan speed.                                                                                                                                                                                                                                                                                                                                                                                                                                             |

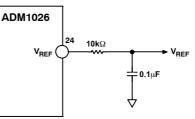

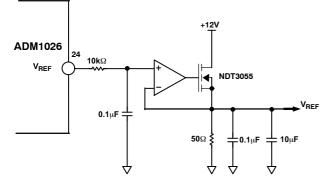

| 24      | V <sub>REF</sub>     | Analog Output            | Reference Voltage Output. Can be selected as 1.8 V (default) or 2.5 V.                                                                                                                                                                                                                                                                                                                                                                                                                               |

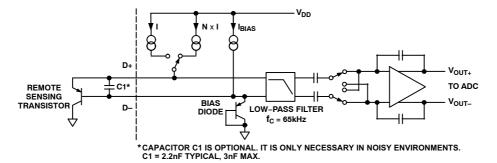

| 25      | D1-/NTESTIN          | Analog Input             | Connected to a cathode of the first remote temperature sensing diode. If it is held high at power-on, it activates the NAND tree test mode.                                                                                                                                                                                                                                                                                                                                                          |

| 26      | D1+                  | Analog Input             | Connected to the anode of the first remote temperature sensing diode.                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 27      | D2-/A <sub>IN9</sub> | Programmable             | Connected to the cathode of the second remote temperature sensing diode or the analog input may be reconfigured as a 0 V $-$ 2.5 V analog input.                                                                                                                                                                                                                                                                                                                                                     |

| 28      | D2+/A <sub>IN8</sub> | Programmable             | Connected to the anode of the second remote temperature sensing diode, or the analog input may be reconfigured as a 0 V $-$ 2.5 V analog input.                                                                                                                                                                                                                                                                                                                                                      |

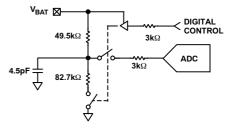

| 29      | V <sub>BAT</sub>     | Analog Input             | Monitors battery voltage, nominally +3.0 V.                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 30      | +5.0 V <sub>IN</sub> | Analog Input             | Monitors the +5.0 V supply.                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 31      | –12 V <sub>IN</sub>  | Analog Input             | Monitors the –12 V supply.                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 32      | +12 V <sub>IN</sub>  | Analog Input             | Monitors the +12 V supply.                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 33      | +V <sub>CCP</sub>    | Analog Input             | Monitors the processor core voltage (0 V to 3.0 V).                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 34      | A <sub>IN7</sub>     | Analog Input             | General-purpose 0 V to 2.5 V analog inputs.                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 35      | A <sub>IN6</sub>     | Analog Input             | General-purpose 0 V to 2.5 V analog inputs.                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 36      | A <sub>IN5</sub>     | Analog Input             | General-purpose 0 V to 3.0 V analog inputs.                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 37      | A <sub>IN4</sub>     | Analog Input             | General-purpose 0 V to 3.0 V analog inputs.                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 38      | A <sub>IN3</sub>     | Analog Input             | General-purpose 0 V to 3.0 V analog inputs.                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 39      | A <sub>IN2</sub>     | Analog Input             | General-purpose 0 V to 3.0 V analog inputs.                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 40      | A <sub>IN1</sub>     | Analog Input             | General-purpose 0 V to 3.0 V analog inputs.                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 41      | A <sub>IN0</sub>     | Analog Input             | General-purpose 0 V to 3.0 V analog inputs.                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 42      | GPIO16/THERM         | Digital I/O <sup>†</sup> | General-purpose I/O pin that can be configured as a digital input or output. Can also be configured as a bidirectional THERM pin (100 k $\Omega$ pullup).                                                                                                                                                                                                                                                                                                                                            |

| 43      | GPIO15               | Digital I/O <sup>†</sup> | General-purpose I/O pin that can be configured as a digital input or output.                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 44      | GPIO14               | Digital I/O <sup>†</sup> | General-purpose I/O pin that can be configured as a digital input or output.                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 45      | GPIO13               | Digital I/O <sup>†</sup> | General-purpose I/O pin that can be configured as a digital input or output.                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 46      | GPIO12               | Digital I/O <sup>†</sup> | General-purpose I/O pin that can be configured as a digital input or output.                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 47      | GPIO11               | Digital I/O <sup>†</sup> | General-purpose I/O pin that can be configured as a digital input or output.                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 48      | GPIO10               | Digital I/O <sup>†</sup> | General-purpose I/O pin that can be configured as a digital input or output.                                                                                                                                                                                                                                                                                                                                                                                                                         |

†GPIO pins are open drain and require external pullup resistors. Fan inputs have integrated 10 kΩ pullups, but these pins become open drain when reconfigured as GPIOs.

| Parameter                                                                                         | <b>Test Conditions/Comments</b>                        | Min         | Тур          | Max          | Unit |

|---------------------------------------------------------------------------------------------------|--------------------------------------------------------|-------------|--------------|--------------|------|

| POWER SUPPLY                                                                                      | -                                                      | •           | •            | •            | •    |

| Supply Voltage, 3.3 V STBY                                                                        |                                                        | 3.0         | 3.3          | 5.5          | V    |

| Supply Current, I <sub>CC</sub>                                                                   | Interface Inactive, ADC Active                         | -           | 2.5          | 4.0          | mA   |

| TEMPERATURE-TO-DIGITAL CONVERTER                                                                  | •                                                      | •           | 1            |              |      |

| Internal Sensor Accuracy                                                                          |                                                        | -           | -            | ±3.0         | °C   |

| Resolution                                                                                        |                                                        | -           | ±1.0         | -            | °C   |

| External Diode Sensor Accuracy                                                                    | 0°C < T <sub>D</sub> < 100°C                           | -           | -            | ±3.0         | °C   |

| Resolution                                                                                        |                                                        | -           | ±1.0         | -            | °C   |

| Remote Sensor Source Current                                                                      | High Level<br>Low Level                                |             | 90<br>5.5    |              | μA   |

| ANALOG-TO-DIGITAL CONVERTER<br>(Including MUX and ATTENUATORS)                                    |                                                        |             |              |              |      |

| Total Unadjusted Error (TUE) (Note 4)                                                             |                                                        | -           | -            | ±2.0         | %    |

| Differential Non-linearity (DNL)                                                                  |                                                        | _           | -            | ±1.0         | LSB  |

| Power Supply Sensitivity                                                                          |                                                        | _           | ±0.1         |              | %/V  |

| Conversion Time<br>(Analog Input or Internal Temperature) (Note 5)                                |                                                        | -           | 11.38        | 12.06        | ms   |

| Conversion Time (External Temperature) (Note 5)                                                   |                                                        | -           | 34.13        | 36.18        | ms   |

| Input Resistance (+5.0 V <sub>IN</sub> , V <sub>CCP</sub> , A <sub>IN0</sub> – A <sub>IN5</sub> ) |                                                        | 80          | 100          | 120          | kΩ   |

| Input Resistance of +12 VIN pin                                                                   |                                                        | 70          | 100          | 115          | kΩ   |

| Input Resistance of -12 V <sub>IN</sub> pin                                                       |                                                        | 8.0         | 10           | 12           | kΩ   |

| Input Resistance (A <sub>IN6</sub> – A <sub>IN9</sub> )                                           |                                                        | 5.0         | -            | -            | MΩ   |

| Input Resistance of V <sub>BAT</sub> pin (Note 4)                                                 |                                                        | 80          | 100          | 120          | kΩ   |

| V <sub>BAT</sub> Current Drain (when measured)                                                    | CR2032 Battery Life >10 Years                          | -           | 80           | 100          | nA   |

| V <sub>BAT</sub> Current Drain (when not measured)                                                |                                                        | -           | 6.0          | -            | nA   |

| ANALOG OUTPUT (DAC)                                                                               |                                                        |             |              |              |      |

| Output Voltage Range                                                                              |                                                        | 0           | -2.5         | -            | V    |

| Total Unadjusted Error (TUE)                                                                      | I <sub>L</sub> = 2 mA                                  | -           | -            | ±5.0         | %    |

| Zero Error                                                                                        | No Load                                                | -           | 1.0          | -            | LSB  |

| Differential Non-linearity (DNL)                                                                  | Monotonic by Design                                    | -           | -            | ±1.0         | LSB  |

| Integral Non-linearity                                                                            |                                                        | -           | ±0.5         | -            | LSB  |

| Output Source Current                                                                             |                                                        | -           | 2.0          | -            | mA   |

| Output Sink Current                                                                               |                                                        | -           | 1.0          | -            | mA   |

| REFERENCE OUTPUT                                                                                  |                                                        |             |              |              |      |

| Output Voltage                                                                                    | Bit 2 of Register 07h = 0<br>Bit 2 of Register 07h = 1 | 1.8<br>2.47 | 1.82<br>2.50 | 1.84<br>2.53 | V    |

| Load Regulation (I <sub>SINK</sub> = 2 mA)                                                        |                                                        | -           | 0.15         | -            | %    |

| Load Regulation (I <sub>SOURCE</sub> = 2 mA)                                                      |                                                        | -           | 0.15         | -            | %    |

| Short Circuit Current                                                                             | V <sub>CC</sub> = 3.3 V                                | -           | 25           | -            | mA   |

| Output Current Source                                                                             |                                                        | -           | 2.0          | -            | mA   |

| Output Current Sink                                                                               |                                                        | -           | 2.0          | -            | mA   |

| Parameter                                          | Test Conditions/Comments                                                                                                     | Min              | Тур                          | Max         | Unit    |

|----------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|------------------|------------------------------|-------------|---------|

| FAN RPM-TO-DIGITAL CONVERTER (Note 6)              |                                                                                                                              |                  | •                            |             |         |

| Accuracy                                           |                                                                                                                              | -                | -                            | ±12         | %       |

| Full-scale Count                                   |                                                                                                                              | -                | _                            | 255         |         |

| FAN0 to FAN7 Nominal Input RPM (Note 5)            | Divisor = 1, fan count = 153<br>Divisor = 2, fan count = 153<br>Divisor = 4, fan count = 153<br>Divisor = 8, fan count = 153 | -<br>-<br>-<br>- | 8800<br>4400<br>2200<br>1100 | -<br>-<br>- | RPM     |

| Internal Clock Frequency                           |                                                                                                                              | 20               | 22.5                         | 25          | kHz     |

| OPEN DRAIN O/Ps, PWM, GPIO0 to 16                  |                                                                                                                              |                  | 1                            | 1           | 1       |

| Output High Voltage, V <sub>OH</sub>               | I <sub>OUT</sub> = 3.0 mA, V <sub>CC</sub> = 3.3 V                                                                           | 2.4              | _                            | _           | V       |

| High Level Output Leakage Current, I <sub>OH</sub> | V <sub>OUT</sub> = V <sub>CC</sub>                                                                                           | _                | 0.1                          | 1.0         | μΑ      |

| Output Low Voltage, V <sub>OL</sub>                | I <sub>OUT</sub> = -3.0 mA, V <sub>CC</sub> = 3.3 V                                                                          | -                | _                            | 0.4         | V       |

| PWM Output Frequency                               |                                                                                                                              | _                | 75                           | _           | Hz      |

| DIGITAL OUTPUTS (INT, RESETMAIN, RESET             | STBY)                                                                                                                        |                  |                              |             |         |

| Output Low Voltage, V <sub>OL</sub>                | I <sub>OUT</sub> = -3.0 mA, V <sub>CC</sub> = 3.3 V                                                                          | -                | _                            | 0.4         | V       |

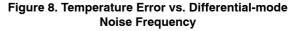

| RESET Pulse Width                                  |                                                                                                                              | 140              | 180                          | 240         | ms      |

| OPEN DRAIN SERIAL DATABUS OUTPUT (SD               | A)                                                                                                                           |                  |                              |             |         |

| Output Low Voltage, V <sub>OL</sub>                | $I_{OUT} = -3.0 \text{ mA}, \text{ V}_{CC} = 3.3 \text{ V}$                                                                  | -                | _                            | 0.4         | V       |

| High Level Output Leakage Current, I <sub>OH</sub> | V <sub>OUT</sub> = V <sub>CC</sub>                                                                                           | _                | 0.1                          | 1.0         | μΑ      |

| SERIAL BUS DIGITAL INPUTS (SCL, SDA)               |                                                                                                                              |                  |                              |             |         |

| Input High Voltage, V <sub>IH</sub>                |                                                                                                                              | 2.2              | -                            | -           | V       |

| Input Low Voltage, V <sub>IL</sub>                 |                                                                                                                              | _                | _                            | 0.8         | V       |

| Hysteresis                                         |                                                                                                                              | _                | 500                          | _           | mV      |

| DIGITAL INPUT LOGIC LEVELS (ADD, CI, FAN           | I 0 to 7, GPIO 0 to 16) (Note 7 and 8)                                                                                       |                  |                              |             |         |

| Input High Voltage, V <sub>IH</sub>                | V <sub>CC</sub> = 3.3 V                                                                                                      | 2.4              | -                            | -           | V       |

| Input Low Voltage, V <sub>IL</sub>                 | V <sub>CC</sub> = 3.3 V                                                                                                      | 0.8              | _                            | _           | V       |

| Hysteresis (Fan 0 to 7)                            | V <sub>CC</sub> = 3.3 V                                                                                                      | _                | 250                          | _           | mV      |

| RESETMAIN, RESETSTBY                               |                                                                                                                              |                  |                              |             |         |

| RESETMAIN Threshold                                | Falling Voltage                                                                                                              | 2.89             | 2.94                         | 2.97        | V       |

| RESETSTBY Threshold                                | Falling Voltage                                                                                                              | 3.01             | 3.05                         | 3.10        | V       |

| RESETMAIN Hysteresis                               |                                                                                                                              | -                | 60                           | -           | mV      |

| RESETSTBY Hysteresis                               |                                                                                                                              | -                | 70                           | -           | mV      |

| DIGITAL INPUT CURRENT                              |                                                                                                                              |                  |                              |             | •       |

| Input High Current, I <sub>IH</sub>                | V <sub>IN</sub> = V <sub>CC</sub>                                                                                            | -1.0             | -                            | -           | μΑ      |

| Input Low Current, I <sub>IL</sub>                 | V <sub>IN</sub> = 0                                                                                                          | -                | -                            | 1.0         | μA      |

| Input Capacitance, C <sub>IN</sub>                 |                                                                                                                              | _                | 20                           | _           | pF      |

| EEPROM RELIABILITY                                 |                                                                                                                              |                  |                              |             |         |

| Endurance (Note 9)                                 |                                                                                                                              | 100              | 700                          | -           | kcycles |

| Data Retention (Note 10)                           |                                                                                                                              | 10               | -                            | -           | Years   |

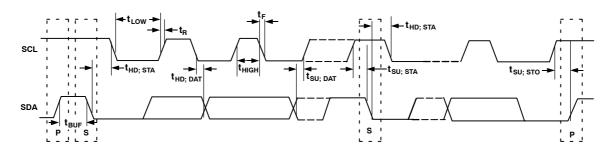

| SERIAL BUS TIMING                                  | · · ·                                                                                                                        |                  |                              |             |         |

| Clock Frequency, f <sub>SCLK</sub>                 | See Figure 2 for All Parameters.                                                                                             | -                | -                            | 400         | kHz     |

| Glitch Immunity, t <sub>SW</sub>                   |                                                                                                                              | -                | -                            | 50          | ns      |

| Bus Free Time, t <sub>BUF</sub>                    |                                                                                                                              | 4.7              | -                            | -           | μs      |

| Start Setup Time, t <sub>SU; STA</sub>             |                                                                                                                              | 4.7              | -                            | _           | μs      |

Table 4. ELECTRICAL CHARACTERISTICS ( $T_A = T_{MIN}$  to  $T_{MAX}$ ,  $V_{CC} = V_{MIN}$  to  $V_{MAX}$ , unless otherwise noted. (Note 1, 2, and 3))

| Parameter                             | Test Conditions/Comments | Min | Тур | Max  | Unit |

|---------------------------------------|--------------------------|-----|-----|------|------|

| SERIAL BUS TIMING                     |                          |     |     |      |      |

| Start Hold Time, t <sub>HD; STA</sub> |                          | 4.0 | -   | -    | μs   |

| SCL Low Time, t <sub>LOW</sub>        |                          | 4.7 | -   | -    | μs   |

| SCL High Time, t <sub>HIGH</sub>      |                          | 4.0 | -   | -    | μs   |

| SCL, SDA Rise Time, t <sub>r</sub>    |                          | -   | -   | 1000 | ns   |

| SCL, SDA Fall Time, t <sub>f</sub>    |                          | -   | -   | 300  | ns   |

| Data Setup Time, t <sub>SU; DAT</sub> |                          | 250 | -   | -    | ns   |

| Data Hold Time, t <sub>HD; DAT</sub>  |                          | 300 | _   | -    | ns   |

All voltages are measured with respect to GND, unless otherwise specified. 1.

2. Typicals are at T<sub>A</sub> = 25°C and represent the most likely parametric norm. Shutdown current typ is measured with V<sub>CC</sub> = 3.3 V.

Timing specifications are tested at logic levels of V<sub>IL</sub> = 0.8 V for a falling edge and V<sub>IH</sub> = 2.1 V for a rising edge.

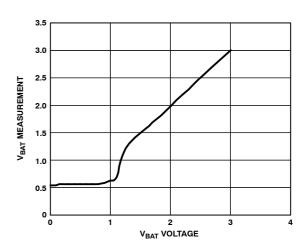

Total unadjusted error (TUE) includes offset, gain, and linearity errors of the ADC, multiplexer, and on-chip input attenuators. V<sub>BAT</sub> is accurate only for V<sub>BAT</sub> voltages greater than 1.5 V (see Figure 14).

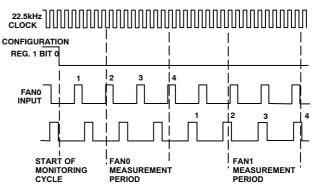

5. Total analog monitoring cycle time is nominally 273 ms, made up of 18 ms × 11.38 ms measurements on analog input and internal temperature channels, and 2 ms × 34.13 ms measurements on external temperature channels.

6. The total fan count is based on two pulses per revolution of the fan tachometer output. The total fan monitoring time depends on the number of fans connected and the fan speed. See the Fan Speed Measurement section for more details.

7. ADD is a three-state input that may be pulled high, low, or left open circuit.

8. Logic inputs accept input high voltages up to 5.0 V even when device is operating at supply voltages below 5.0 V.

9. Endurance is qualified to 100,000 cycles as per JEDEC Std. 22 method A117, and measured at -40°C, +25°C, and +85°C. Typical endurance at +25°C is 700,000 cycles.

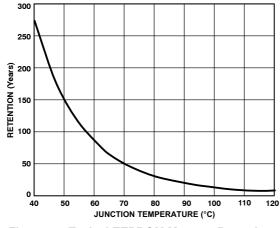

10. Retention lifetime equivalent at junction temperature (T<sub>J</sub>) = 55°C as per JEDEC Std. 22 method A117. Retention lifetime based on activation energy of 0.6 V derates with junction temperature as shown in Figure 15.

Figure 2. Serial Bus Timing Diagram

# **TYPICAL PERFORMANCE CHARACTERISTICS**

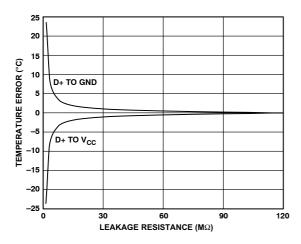

Figure 3. Temperature Error vs. PCB Track Resistance

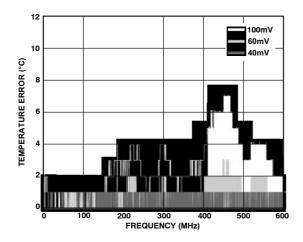

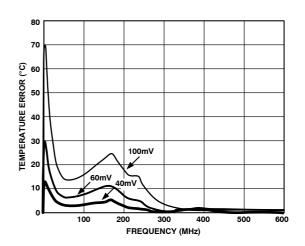

Figure 5. Temperature Error vs. Common-mode Noise Frequency

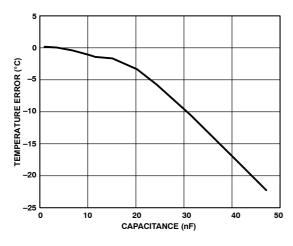

Figure 7. Temperature Error vs. Capacitance Between D+ and D–

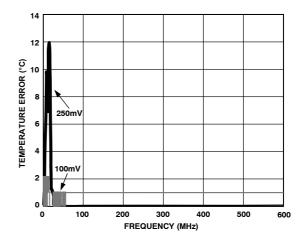

Figure 4. Temperature Error vs. Power Supply Noise Frequency

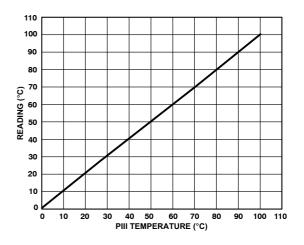

Figure 6. Pentium® III Temperature vs. ADM1026 Reading

# **TYPICAL PERFORMANCE CHARACTERISTICS**

Figure 9. Powerup Reset Timeout vs. Temperature

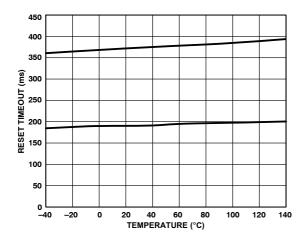

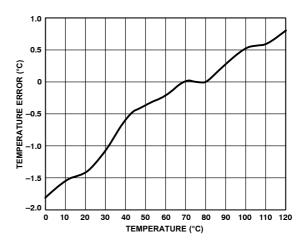

Figure 11. Local Sensor Temperature Error

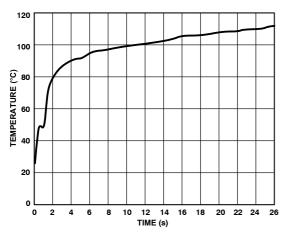

Figure 13. Response to Thermal Shock

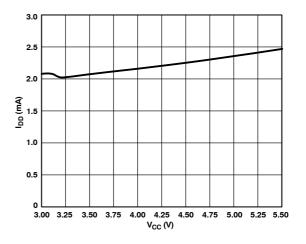

Figure 10. Supply Current vs. Supply Voltage

Figure 12. Remote Sensor Temperature Error

Figure 14. V<sub>BAT</sub> Measurement vs. Voltage

# **Functional Description**

The ADM1026 is a complete system hardware monitor for microprocessor-based systems. The device communicates with the system via a serial system management bus. The serial bus controller has a hardwired address line for device selection (ADD, Pin 15), a serial data line for reading and writing addresses and data (SDA, Pin 14), and an input line for the serial clock (SCL, Pin 13). All control and programming functions of the ADM1026 are performed over the serial bus.

### **Measurement Inputs**

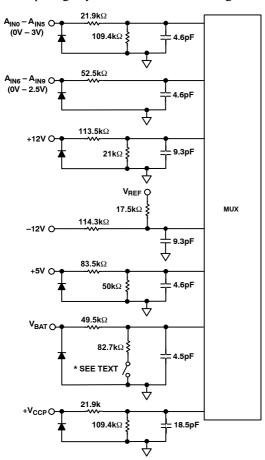

Programmability of the analog and digital measurement inputs makes the ADM1026 extremely flexible and versatile. The device has an 8-bit A/D converter, and 17 analog measurement input pins that can be configured in different ways.

Pins 25 and 26 are dedicated temperature inputs and may be connected to the cathode and anode of a remote temperature sensing diode.

Pins 27 and 28 may be configured as temperature inputs and connected to a second temperature-sensing diode, or may be reconfigured as analog inputs with a range of 0 V to 2.5 V.

Pins 29 to 33 are dedicated analog inputs with on-chip attenuators configured to monitor  $V_{BAT}$ , +5.0 V, -12 V, +12 V, and the processor core voltage  $V_{CCB}$  respectively.

Pins 34 to 41 are general-purpose analog inputs with a range of 0 V to 2.5 V or 0 V to 3.0 V. These are mainly intended for monitoring SCSI termination voltages, but may be used for other purposes.

The ADC also accepts input from an on-chip band gap temperature sensor that monitors system ambient temperature.

In addition, the ADM1026 monitors the supply from which it is powered, 3.3 V STBY, so there is no need for a separate pin to monitor the power supply voltage.

The ADM1026 has eight pins that are general-purpose logic I/O pins (Pins 1, 2, and 43 to 48), a pin that can be configured as GPIO or as a bidirectional thermal interrupt (THERM) pin (Pin 42), and eight pins that can be configured for fan speed measurement or as general-purpose logic pins (Pins 3 to 6 and Pins 9 to 12).

# **Sequential Measurement**

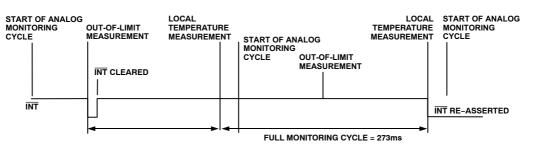

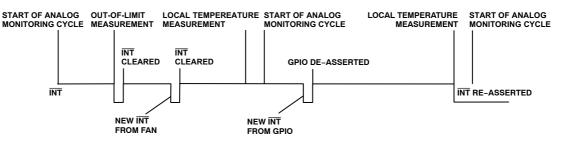

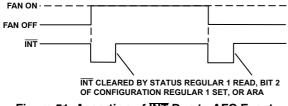

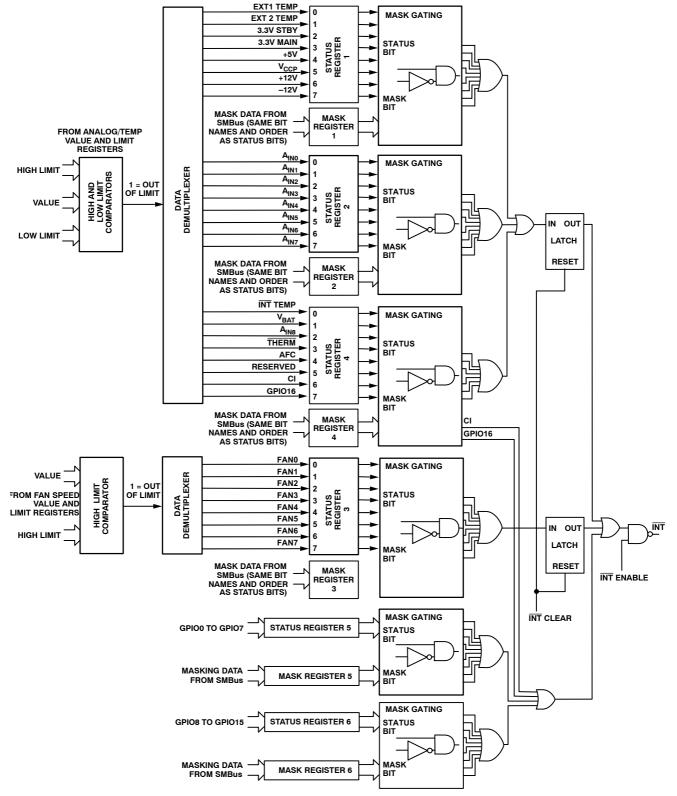

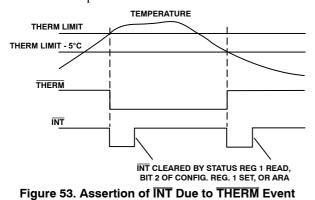

When the ADM1026 monitoring sequence is started, it cycles sequentially through the measurement of analog inputs and the temperature sensor, while at the same time the fan speed inputs are independently monitored. Measured values from these inputs are stored in value registers. These can be read over the serial bus, or can be compared with programmed limits stored in the limit registers. The results of out-of-limit comparisons are stored in the interrupt status registers. An out-of-limit event generates an interrupt on the INT line (Pin 17).

Any or all of the interrupt status bits can be masked by appropriate programming of the interrupt mask registers.

### **Chassis Intrusion**

A chassis intrusion input (Pin 16) is provided to detect unauthorized tampering with the equipment. This event is latched in a battery-backed register bit.

#### Resets

The ADM1026 has two power-on reset outputs, RESETMAIN and RESETSTBY, that are asserted when 3.3 V MAIN or 3.3 V STBY fall below the reset threshold. These give a 180 ms reset pulse at powerup. RESETMAIN also functions as an active-low RESET input.

### Fan Speed Control Outputs

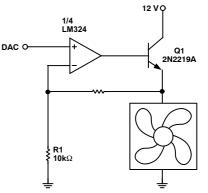

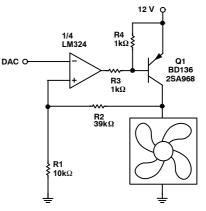

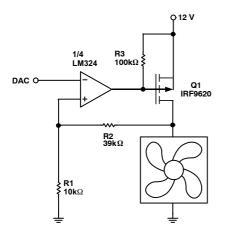

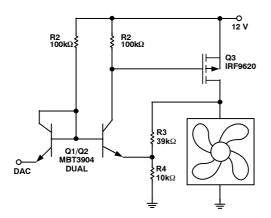

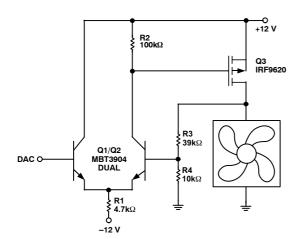

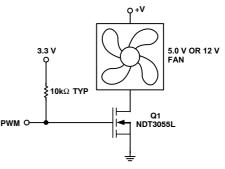

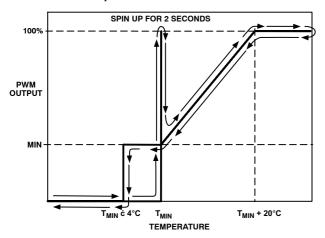

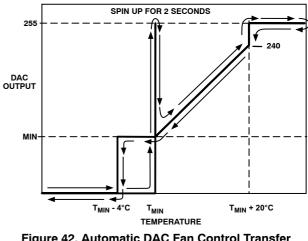

The ADM1026 has two outputs intended to control fan speed, though they can also be used for other purposes. Pin 18 is an open drain, Pulse Width Modulated (PWM) output with a programmable duty cycle and an output frequency of 75 Hz. Pin 23 is connected to the output of an on-chip, 8-bit, digital-to-analog converter with an output range of 0 V to 2.5 V.

Either or both of these outputs may be used to implement a temperature-controlled fan by controlling the speed of a fan using the temperature measured by the on-chip temperature sensor or remote temperature sensors.

### **Internal Registers**

Table 5 describes the principal registers of the ADM1026. For more detailed information, see Table 12 to Table 125.

#### Table 5. PRINCIPLE REGISTERS

| Туре                               | Description                                                                                                                                                                                                          |

|------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Address<br>Pointer                 | Contains the address that selects one of<br>the other internal registers. When writing to<br>the ADM1026, the first byte of data is<br>always a register address, and is written to<br>the address pointer register. |

| Configuration<br>Registers         | Provide control and configuration for<br>various operating parameters.                                                                                                                                               |

| Fan Divisor<br>Registers           | Contain counter prescaler values for fan<br>speed measurement.                                                                                                                                                       |

| DAC/PWM<br>Control<br>Registers    | Contain speed values for PWM and DAC fan drive outputs.                                                                                                                                                              |

| GPIO<br>Configuration<br>Registers | Configure the GPIO pins as input or output and for signal polarity.                                                                                                                                                  |

| Value and<br>Limit<br>Registers    | Store the results of analog voltage inputs,<br>temperature, and fan speed measurements,<br>along with their limit values.                                                                                            |

| Status<br>Registers                | Store events from the various interrupt sources.                                                                                                                                                                     |

| Mask<br>Registers                  | Allow masking of individual interrupt sources.                                                                                                                                                                       |

### EEPROM

The ADM1026 has 8 kB of non-volatile, electrically erasable, programmable read-only memory (EEPROM) from register Addresses 8000h to 9FFFh. This may be used for permanent storage of data that is not lost when the

ADM1026 is powered down, unlike the data in the volatile registers. Although referred to as read-only memory, the EEPROM can be written to (as well as read from) via the serial bus in exactly the same way as the other registers. The main differences between the EEPROM and other registers are:

- An EEPROM location must be blank before it can be written to. If it contains data, it must first be erased.

- Writing to EEPROM is slower than writing to RAM.

- Writing to the EEPROM should be restricted because its typical cycle life is 100,000 write operations, due to the usual EEPROM wear-out mechanisms.

The EEPROM in the ADM1026 has been qualified for two key EEPROM memory characteristics: memory cycling endurance and memory data retention.

Endurance qualifies the ability of the EEPROM to be cycled through many program, read, and erase cycles. In real terms, a single endurance cycle is composed of four independent, sequential events, as follows:

- 1. Initial page erase sequence

- 2. Read/verify sequence

- 3. Program sequence

- 4. Second read/verify sequence

In reliability qualification, every byte is cycled from 00h to FFh until a first fail is recorded, signifying the endurance limit of the EEPROM memory.

Retention quantifies the ability of the memory to retain its programmed data over time. The EEPROM in the ADM1026 has been qualified in accordance with the formal JEDEC Retention Lifetime Specification (A117) at a specific junction temperature ( $T_J = 55^{\circ}$ C) to guarantee a minimum of 10 years retention time. As part of this qualification procedure, the EEPROM memory is cycled to its specified endurance limit described above before data retention is characterized. This means that the EEPROM memory is guaranteed to retain its data for its full specified retention lifetime every time the EEPROM is reprogrammed. Note that retention lifetime based on an activation energy of 0.6 V derates with  $T_J$ , as shown in Figure 15.

Figure 15. Typical EEPROM Memory Retention

#### Serial Bus Interface

Control of the ADM1026 is carried out via the serial system management bus (SMBus). The ADM1026 is connected to this bus as a slave device, under the control of a master device.

The ADM1026 has a 7-bit serial bus slave address. When the device is powered on, it does so with a default serial bus address. The 5 MSBs of the address are set to 01011, and the 2 LSBs are determined by the logical states of Pin 15 ADD/NTESTOUT. This pin is a three-state input that can be grounded, connected to  $V_{CC}$ , or left open-circuit to give three different addresses.

| ADD Pin         | A1 | A0 |

|-----------------|----|----|

| GND             | 0  | 0  |

| No Connect      | 1  | 0  |

| V <sub>CC</sub> | 0  | 1  |

**Table 6. ADDRESS PIN TRUTH TABLE**

If ADD is left open-circuit, the default address is 0101110 (5Ch). ADD is sampled only at powerup on the first valid SMBus transaction, so any changes made while the power is on (and the address is locked) have no effect.

The facility to make hardwired changes to device addresses allows the user to avoid conflicts with other devices sharing the same serial bus, for example if more than one ADM1026 is used in a system.

#### General SMBus Timing

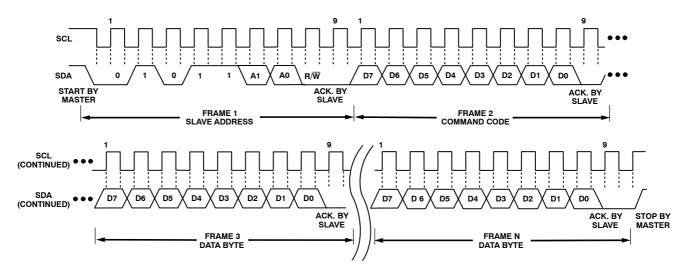

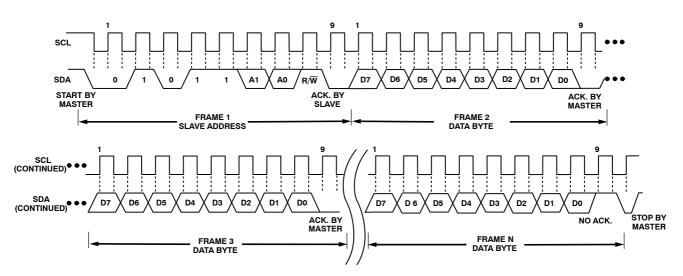

Figure 16 and Figure 17 show timing diagrams for general read and write operations using the SMBus. The SMBus specification defines specific conditions for different types of read and write operations, which are discussed later in this section. The general SMBus protocol\* operates as follows:

1. The master initiates data transfer by establishing a start condition, defined as a high-to-low transition on the serial data line (SDA) while the serial clock line SCL remains high. This indicates that a data stream follows. All slave peripherals connected to the serial bus respond to the start condition and shift in the next 8 bits, consisting of a 7-bit slave address (MSB first) and an  $R/\overline{W}$  bit, which determine the direction of the data transfer, that is, whether data is written to or read from the slave device (0 = write, 1 = read).

The peripheral whose address corresponds to the trans-mitted address responds by pulling the data line low during the low period before the ninth clock pulse, known as the acknowledge bit, and holding it low during the high period of this clock pulse. All other devices on the bus remain idle while the selected device waits for data to be read from or written to it. If the  $R/\overline{W}$  bit is 0, the master writes to the slave device. If the  $R/\overline{W}$  bit is 1, the master reads from the slave device.

2. Data is sent over the serial bus in sequences of nine clock pulses, 8 bits of data followed by an acknowledge bit from the slave device. Data transitions on the data line must occur during the low period of the clock signal and remain stable during the high period, because a low-to-high transition when the clock is high may be interpreted as a stop signal.

If the operation is a write operation, the first data byte after the slave address is a command byte. This tells the slave device what to expect next. It may be an instruction telling the slave device to expect a block write, or it may simply be a register address that tells the slave where subsequent data is to be written.

Because data can flow in only one direction as defined by the  $R/\overline{W}$  bit, it is not possible to send a command to a slave device during a read operation.

Before doing a read operation, it may first be necessary to do a write operation to tell the slave what type of read operation to expect and/or the address from which data is to be read.

3. When all data bytes have been read or written, stop conditions are established. In write mode, the master pulls the data line high during the 10th clock pulse to assert a stop condition. In read mode, the master device releases the SDA line during the low period before the ninth clock pulse, but the slave device does not pull it low (called No Acknowledge). The master takes the data line low during the low period before the 10th clock pulse, then high during the 10th clock pulse to assert a stop condition.

\*If it is required to perform several read or write operations in succession, the master can send a repeat start condition instead of a stop condition to begin a new operation.

Figure 16. General SMBus Write Timing Diagram

Figure 17. General SMBus Read Timing Diagram

### **SMBus Protocols for RAM and EEPROM**

The ADM1026 contains volatile registers (RAM) and non-volatile EEPROM. RAM occupies Addresses 00h to 6Fh, while EEPROM occupies Addresses 8000h to 9FFFh.

Data can be written to and read from both RAM and EEPROM as single data bytes and as block (sequential) read or write operations of 32 data bytes, the maximum block size allowed by the SMBus specification.

Data can only be written to unprogrammed EEPROM locations. To write new data to a programmed location, it is first necessary to erase it. EEPROM erasure cannot be done at the byte level; the EEPROM is arranged as 128 pages of 64 bytes, and an entire page must be erased. Note that of these 128 pages, only 124 pages are available to the user. The last four pages are reserved for manufacturing purposes and cannot be erased/rewritten.

The EEPROM has three RAM registers associated with it, EEPROM Registers 1, 2, and 3 at Addresses 06h, 0Ch, and 13h. EEPROM Registers 1 and 2 are for factory use only. EEPROM Register 3 sets up the EEPROM operating mode. Setting Bit 0 of EEPROM Register 3 puts the EEPROM into read mode. Setting Bit 1 puts it into programming mode. Setting Bit 2 puts it into erase mode.

Only one of these bits must be set before the EEPROM may be accessed. Setting no bits or more than one of them causes the device to respond with No Acknowledge if an EEPROM read, program, or erase operation is attempted.

It is important to distinguish between SMBus write operations, such as sending an address or command, and EEPROM programming operations. It is possible to write an EEPROM address over the SMBus, whatever the state of EEPROM Register 3. However, EEPROM Register 3 must be correctly set before a subsequent EEPROM operation can be performed. For example, when reading from the EEPROM, Bit 0 of EEPROM Register 3 can be set, even though SMBus write operations are required to set up the EEPROM address for reading. Bit 3 of EEPROM Register 3 is used for EEPROM write protection. Setting this bit prevents accidental programming or erasure of the EEPROM. If an EEPROM write or erase operation is attempted when this bit is set, the ADM1026 responds with No Acknowledge. This bit is write-once and can only be cleared by a power-on reset.

EEPROM Register 3 Bit 7 is used for clock extend. Programming an EEPROM byte takes approximately  $250 \ \mu$ s, which would limit the SMBus clock for repeated or block write operations. Because EEPROM block read/write access is slow, it is recommended that this clock extend bit typically be set to 1. This allows the ADM1026 to pull SCL low and extend the clock pulse when it cannot accept any more data.

#### ADM1026 SMBus Operations

The SMBus specifications define several protocols for different types of read and write operations. The ones used in the ADM1026 are discussed below. The following abbreviations are used in the diagrams:

- S START

- W WRITE

- P STOP

- A ACKNOWLEDGE

- R –READ

- A NO ACKNOWLEDGE

# ADM1026 Write Operations

### Send Byte

In this operation, the master device sends a single command byte to a slave device, as follows:

- 1. The master device asserts a start condition on the SDA.

- 2. The master sends the 7-bit slave address followed by the write bit (low).

- 3. The addressed slave device asserts an ACK on the SDA.

- 4. The master sends a command code.

- 5. The slave asserts ACK on the SDA.

- 6. The master asserts a stop condition on the SDA and the transaction ends.

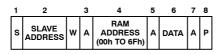

In the ADM1026, the send byte protocol is used to write a register address to RAM for a subsequent single–byte read from the same address or block read or write starting at that address. This is illustrated in Figure 18.

| 1 | 2                |   | 3 | 4                              | 5 | 6 |  |

|---|------------------|---|---|--------------------------------|---|---|--|

| s | SLAVE<br>ADDRESS | w | A | RAM<br>ADDRESS<br>(00h TO 6Fh) | A | Ρ |  |

#### Figure 18. Setting a RAM Address for Subsequent Read

If it is required to read data from the RAM immediately after setting up the address, the master can assert a repeat start condition immediately after the final ACK and carry out a single byte read, block read, or block write operation without asserting an intermediate stop condition.

# Write Byte/Word

In this operation, the master device sends a command byte and one or two data bytes to the slave device as follows:

- 1. The master device asserts a start condition on the SDA.

- 2. The master sends the 7-bit slave address followed by the write bit (low).

- 3. The addressed slave device asserts an ACK on the SDA.

- 4. The master sends a command code.

- 5. The slave asserts an ACK on the SDA.

- 6. The master sends a data byte.

- 7. The slave asserts an ACK on the SDA.

- 8. The master sends a data byte (or may assert stop here.)

- 9. The slave asserts an ACK on the SDA.

- 10. The master asserts a stop condition on the SDA to end the transaction.

In the ADM1026, the write byte/word protocol is used for four purposes. The ADM1026 knows how to respond by the value of the command byte and EEPROM Register 3.

The first purpose is to write a single byte of data to RAM. In this case, the command byte is the RAM address from 00h to 6Fh and the (only) data byte is the actual data. This is illustrated in Figure 19.

Figure 19. Single Byte Write to RAM

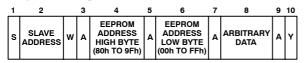

The protocol is also used to set up a 2-byte EEPROM address for a subsequent read or block read. In this case, the command byte is the high byte of the EEPROM address from 80h to 9Fh. The (only) data byte is the low byte of the EEPROM address. This is illustrated in Figure 20.

| 1 | 2                |   | 3 | 4                                              | 5 | 6                                             | 7 | 8 |

|---|------------------|---|---|------------------------------------------------|---|-----------------------------------------------|---|---|

| s | SLAVE<br>ADDRESS | ≥ | 4 | EEPROM<br>ADDRESS<br>HIGH BYTE<br>(80h TO 9Fh) | A | EEPROM<br>ADDRESS<br>LOW BYTE<br>(00h TO FFh) | A | Ρ |

Figure 20. Setting an EEPROM Address

If it is required to read data from the EEPROM immediately after setting up the address, the master can assert a repeat start condition immediately after the final ACK and carry out a single-byte read or block read operation without asserting an intermediate stop condition. In this case, Bit 0 of EEPROM Register 3 should be set.

The third use is to erase a page of EEPROM memory. EEPROM memory can be written to only if it is previously erased. Before writing to one or more EEPROM memory locations that are already programmed, the page or pages containing those locations must first be erased. EEPROM memory is erased by writing an EEPROM page address plus an arbitrary byte of data with Bit 2 of EEPROM Register 3 set to 1.

Because the EEPROM consists of 128 pages of 64 bytes, the EEPROM page address consists of the EEPROM address high byte (from 80h to 9Fh) and the two MSBs of the low byte. The lower six bits of the EEPROM address (low byte only) specify addresses within a page and are ignored during an erase operation.

Figure 21. EEPROM Page Erasure

Page erasure takes approximately 20 ms. If the EEPROM is accessed before erasure is complete, the ADM1026 responds with No Acknowledge.

Last, this protocol is used to write a single byte of data to EEPROM. In this case, the command byte is the high byte of the EEPROM address from 80h to 9Fh. The first data byte is the low byte of the EEPROM address, and the second data

byte is the actual data. Bit 1 of EEPROM Register 3 must be set. This is illustrated in Figure 22.

| 1 | 2                | 3   | 4                                              | 5 | 6                                             | 7 | 8    | 9 | 10 |

|---|------------------|-----|------------------------------------------------|---|-----------------------------------------------|---|------|---|----|

| s | SLAVE<br>ADDRESS | × 4 | EEPROM<br>ADDRESS<br>HIGH BYTE<br>(80h TO 9Fh) | A | EEPROM<br>ADDRESS<br>LOW BYTE<br>(00h TO FFh) | A | DATA | A | Y  |

Figure 22. Single-Byte Write to EEPROM

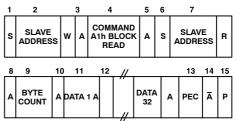

# Block Write

In this operation, the master device writes a block of data to a slave device. The start address for a block write must have been set previously. In the case of the ADM1026, this is done by a Send Byte operation to set a RAM address or by a write byte/word operation to set an EEPROM address.

- 1. The master device asserts a start condition on the SDA.

- 2. The master sends the 7-bit slave address followed by the write bit (low).

- 3. The addressed slave device asserts an ACK on the SDA.

- 4. The master sends a command code that tells the slave device to expect a block write. The ADM1026 command code for a block write is A0h (10100000).

- 5. The slave asserts an ACK on the SDA.

- 6. The master sends a data byte (20h) that tells the slave device that 32 data bytes are being sent to it. The master should always send 32 data bytes to the ADM1026.

- 7. The slave asserts an ACK on the SDA.

- 8. The master sends 32 data bytes.

- 9. The slave asserts an ACK on the SDA after each data byte.

- 10. The master sends a packet error checking (PEC) byte.

- 11. The ADM1026 checks the PEC byte and issues an ACK if correct. If incorrect (NACK), the master resends the data bytes.

- 12. The master asserts a stop condition on the SDA to end the transaction.

| 1 | 2                |   | 3 | 4                             | 5 | 6             | 7 | 8      | 9 |        |   | "                |   | 10  | 11 | 12 |

|---|------------------|---|---|-------------------------------|---|---------------|---|--------|---|--------|---|------------------|---|-----|----|----|

| s | SLAVE<br>ADDRESS | w | A | COMMAND<br>A0h BLOCK<br>WRITE | A | BYTE<br>COUNT | A | DATA 1 | A | DATA 2 | A | //<br>DATA<br>32 | A | PEC | A  | Ρ  |

|   |                  |   |   |                               |   |               |   |        |   |        |   |                  |   |     |    |    |

Figure 23. Block Write to EEPROM or RAM

When performing a block write to EEPROM, Bit 1 of EEPROM Register 3 must be set. Unlike some EEPROM devices that limit block writes to within a page boundary, there is no limitation on the start address when performing a block write to EEPROM, except:

- There must be at least 32 locations from the start address to the highest EEPROM address (9FF) to avoid writing to invalid addresses.

- If the addresses cross a page boundary, both pages must be erased before programming.

# ADM1026 Read Operations

The ADM1026 uses the SMBus read protocols described here.

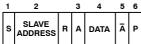

# **Receive Byte**

In this operation, the master device receives a single byte from a slave device as follows:

- 1. The master device asserts a start condition on the SDA.

- 2. The master sends the 7-bit slave address followed by the read bit (high).

- 3. The addressed slave device asserts an ACK on the SDA.

- 4. The master receives a data byte.

- 5. The master asserts a NO ACK on the SDA.

- 6. The master asserts a stop condition on the SDA to end the transaction.

In the ADM1026, the receive byte protocol is used to read a single byte of data from a RAM or EEPROM location whose address has previously been set by a send byte or write byte/word operation. Figure 24 shows this. When reading from EEPROM, Bit 0 of EEPROM Register 3 must be set.

# Figure 24. Single-Byte Read from EEPROM or RAM

# **Block Read**

In this operation, the master device reads a block of data from a slave device. The start address for a block read must have been set previously. In the case of the ADM1026 this is done by a send byte operation to set a RAM address, or by a write byte/word operation to set an EEPROM address. The block read operation consists of a send byte operation that sends a block read command to the slave, immediately followed by a repeated start and a read operation that reads out multiple data bytes as follows:

- 1. The master device asserts a start condition on the SDA.

- 2. The master sends the 7-bit slave address followed by the write bit (low).

- 3. The addressed slave device asserts an ACK on the SDA.

- 4. The master sends a command code that tells the slave device to expect a block read. The ADM1026 command code for a block read is A 1h (10100001).

- 5. The slave asserts an ACK on the SDA.

- 6. The master asserts a repeat start condition on the SDA.

- 7. The master sends the 7-bit slave address followed by the read bit (high).

- 8. The slave asserts an ACK on the SDA.

- 9. The ADM1026 sends a byte count data byte that tells the master how many data bytes to expect. The

ADM1026 always returns 32 data bytes (20h), the maximum allowed by the SMBus 1.1 specification.

- 10. The master asserts an ACK on the SDA.

- 11. The master receives 32 data bytes.

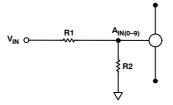

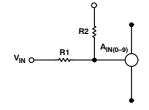

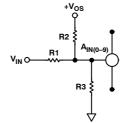

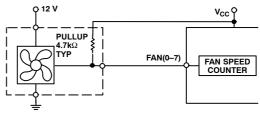

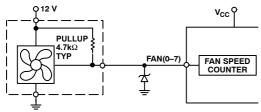

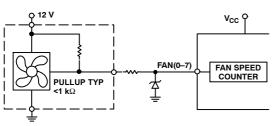

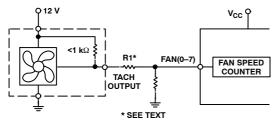

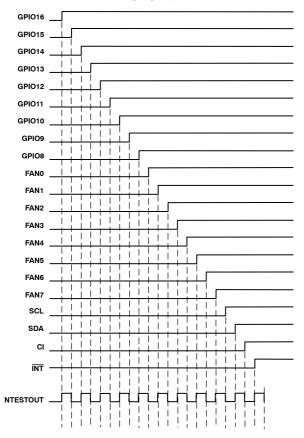

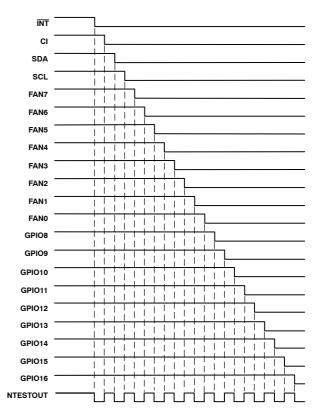

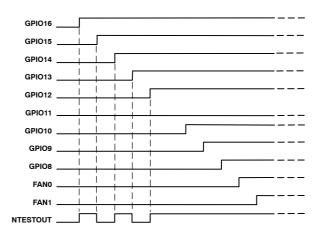

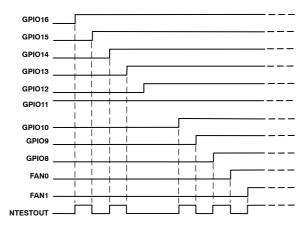

- 12. The master asserts an ACK on the SDA after each data byte.