### Schematic for the AP0101AT2L00XPGAH3-GEVB Evaluation Board

# AP0101 HEADBOARD DEMO3 Card

| Page | Description           |  |  |  |  |  |

|------|-----------------------|--|--|--|--|--|

| 1    | Title Page            |  |  |  |  |  |

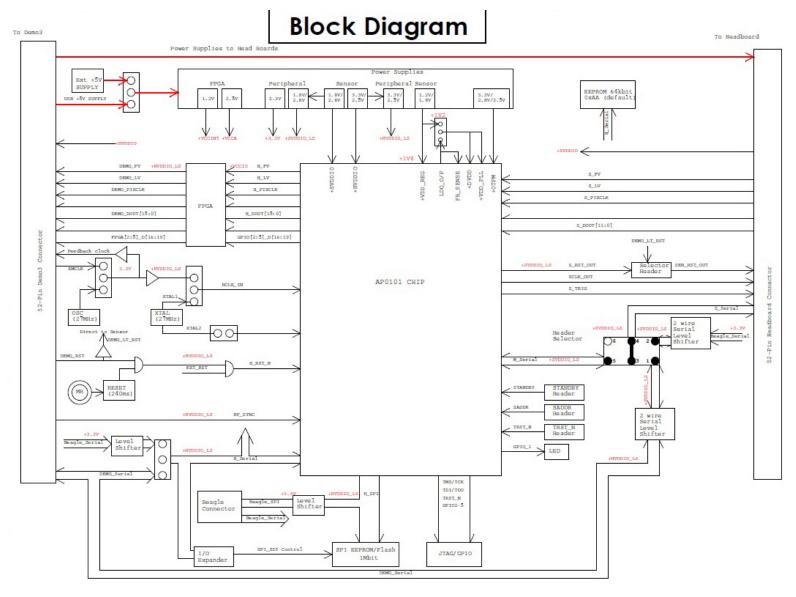

| 2    | Block Diagram         |  |  |  |  |  |

| 3    | Pinout                |  |  |  |  |  |

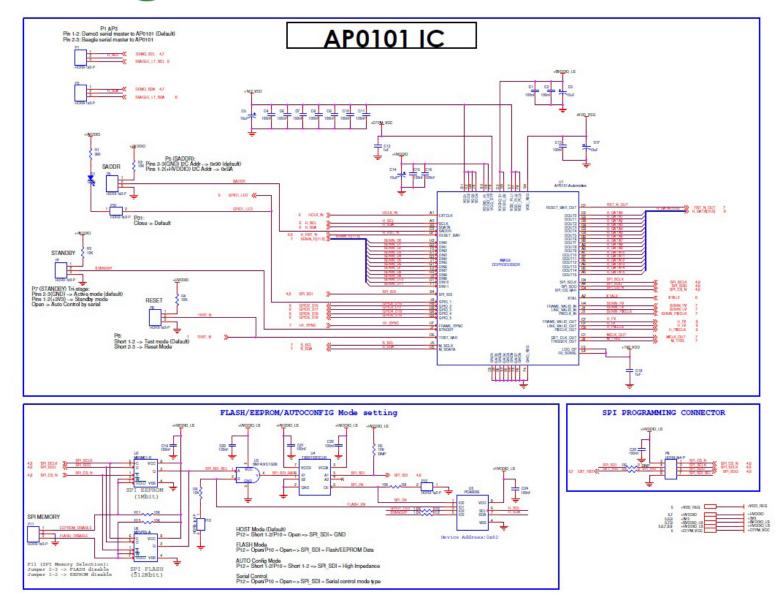

| 4    | AP0101                |  |  |  |  |  |

| 5    | Power                 |  |  |  |  |  |

| 6    | Clock and Reset       |  |  |  |  |  |

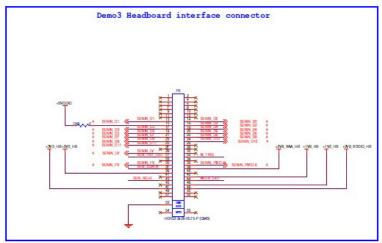

| 7    | External Interfaces   |  |  |  |  |  |

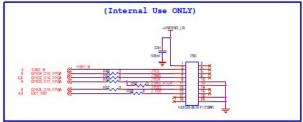

| 8    | BEAGLE/FPGA EXT VF    |  |  |  |  |  |

| 9    | FPGA Interface        |  |  |  |  |  |

| 10   | Configuration Setting |  |  |  |  |  |

| Rev     | Who    | Date     | Description                                                                                                                                     |    |

|---------|--------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Rev 0.0 | skumar | 06/02/15 | Initial.Modified from AP0101_HEADBOARD Demo2                                                                                                    |    |

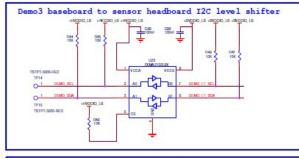

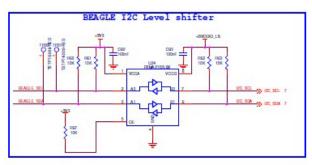

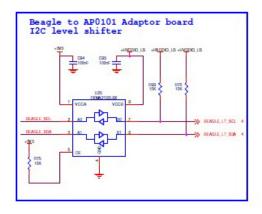

| Rev 0.1 | skumar | 06/25/15 | Added U58 Level shifter between Beagle and AP0101     Removed Header P62&P63 and replaced back with resistor R57&R58     Updated Block diagram  | 5) |

| Rev 0.2 | skumar | 07/15/15 | Deleted P2 and P4 (Removed the provision of external VDD supply for ISP) Text update and feedback clock connected to demo3 base board connector |    |

10/23/2015 - 1 - www.onsemi.com

# **AP0101 IC PINOUT**

|   | 1             | 2       | 3         | 4          | 5        | 6          | 7          | 8           | 9          |

|---|---------------|---------|-----------|------------|----------|------------|------------|-------------|------------|

| A | EXTCLK        | XTAL    | SCLK      | SPI_SDO    | DOUT[15] | DOUT[13]   | DOUT[10]   | DOUT[9]     | DOUT[8]    |

| В | VDD           | VDDIO_H | SDATA     | SPI_SDI    | DOUT[14] | DOUT[12]   | DOUT[11]   | DOUT[7]     | DOUT[6]    |

| C | EXT_CLK_OUT   | VDDIO_S | SADDR     | SPI_CS_BAR | GND      | PIXCLK_OUT | FV_OUT     | DOUT[5]     | DOUT[4]    |

| D | RESET_BAR_OUT | VDD     | GND       | SPI_SCLK   | GND      | TRST_BAR   | LV_OUT     | DOUT[3]     | DOUT[2]    |

| E | DIN[3]        | DIN[7]  | GND       | FB_SENSE   | GND      | GND        | VDD_PLL    | DOUT[1]     | DOUT[0]    |

| F | DIN[11]       | DIN[2]  | LDO_OP    | GND_REG    | GND      | GND        | VDD_PLL    | VDD_PLL     | VDDIO_OTPM |

| G | DIN[6]        | DIN[1]  | DIN[4]    | VDD_REG    | VDDIO_S  | VDD        | RESET_BAR  | GPIO[4]     | GPIO[5]    |

| Н | DIN[10]       | DIN[0]  | DIN[8]    | FV_IN      | M_SDATA  | VDDIO_H    | FRAME_SYNC | GPIO[2]     | GPIO[3]    |

| 1 | DIN[5]        | DIN[9]  | PIXCLK_IN | LV_IN      | M_SCLK   | VDD        | STANDBY    | TRIGGER_OUT | GPIO[1]    |

10/23/2015 - 3 - www.onsemi.com

# ON Semiconductor®

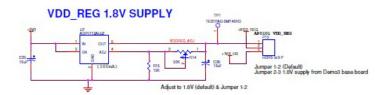

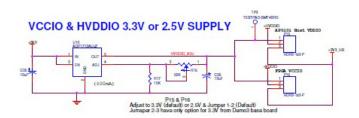

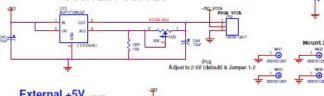

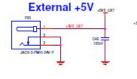

### **Power**

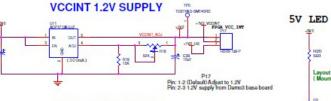

#### VDD\_OTPM 3.3V, 2.8V or 2.5V SUPPLY

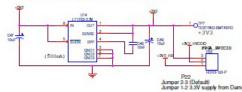

#### PERIPHERAL 3.3V SUPPLY

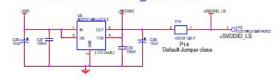

#### PERIPHERAL SVDDIO LS SUPPLY

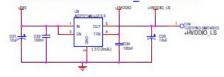

#### PERIPHERAL HVDDIO\_LS SUPPLY

#### VCCA 2.5V SUPPLY

Layout Note ( Mount LED on bottom side of PCB )

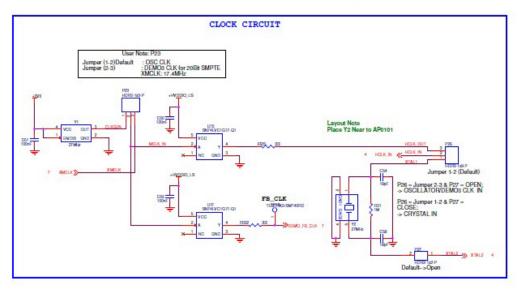

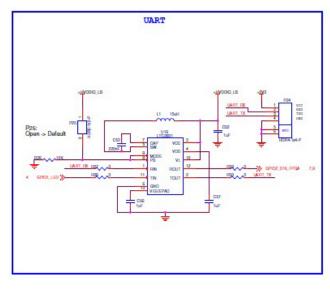

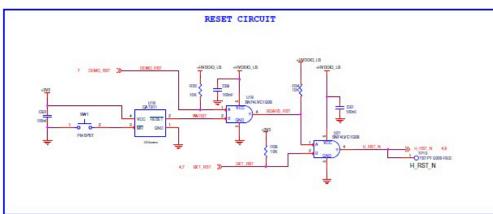

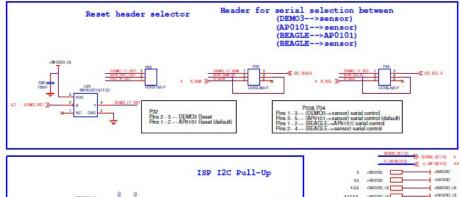

# Clock/Reset/UART

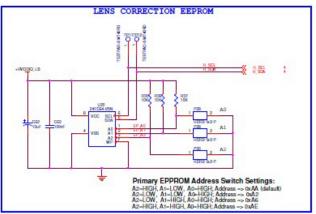

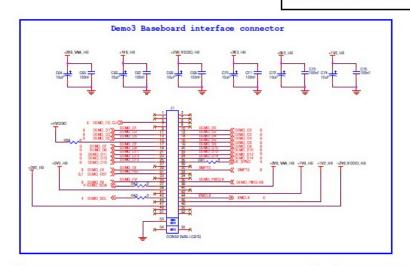

### **External Interface**

+3V2 (A/OCIO

5,8,9 +0V2 HVCCC 5,9 +W2,VDONT

Reset header selector

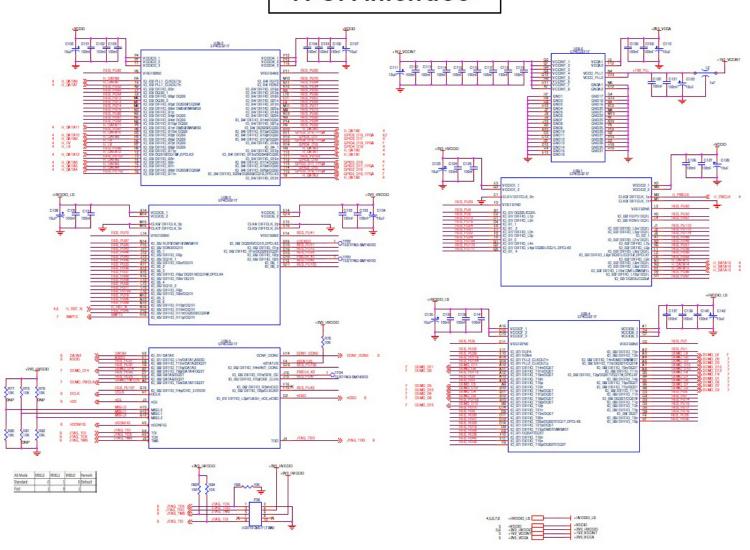

# BEAGLE/FPGA EXT I/F

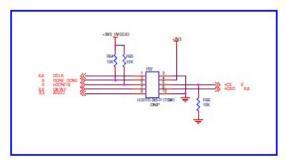

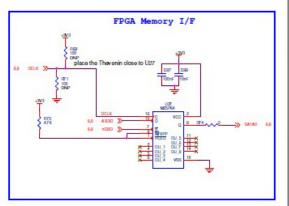

### **FPGA Interface**

# **Configuration Setting**

|                |                             |           |           |           | Beagle Serial configuration                  |                                              |

|----------------|-----------------------------|-----------|-----------|-----------|----------------------------------------------|----------------------------------------------|

| Header         | Pin condition               |           |           |           | Signal condition                             | Remark                                       |

|                | P33                         | P34       | P1        | P3        |                                              | The state of                                 |

| P33/P34 &P1/P3 | Short 1-3                   | Short 1-3 | Short 1-2 | Short 1-2 | DEMO3_Serial => Sensor_Serial/AP0101_Serial  | Demo3 Master control ISP & headboard sensor  |

|                | Short 1-2                   | Short 1-2 | Short 2-3 | Short 2-3 | Beagle_Serial -> Sensor_Serial/AP0101_Serial | Beagle Master control ISP & headboard sensor |

|                | Short 3-5                   | Short 3-5 | N/A       | NA        | AP0101_Serial => Sensor_Serial               | AP0101 Master control headboard sensor       |

|                |                             | 8-2       |           |           | Auto configuration                           |                                              |

| Header         | Pin condition               |           |           |           | Signal condition                             | Remark                                       |

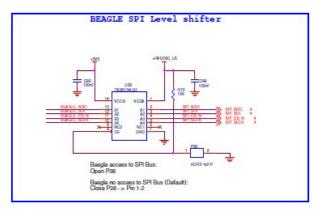

| P38            | Short 1-2                   |           |           |           | Disable U26                                  | Beagle no access to SPI Bus                  |

| P12/P10        | P12=Short 1-2/P10=Open      |           |           |           | HOST Mode(SPI_SDI=>GND)                      |                                              |

|                | P12=Open 1-2/P10=Open       |           |           |           | Flash Mode(SPI_SDI=Flash/EEPROM Data)        |                                              |

|                | P12=Short 1-2/P10=Short 1-2 |           |           |           | Auto-Config(SPI SDI-High Impedance)          |                                              |

10/23/2015 - 10 - www.onsemi.com

### **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Optical Sensor Development Tools category:

Click to view products by ON Semiconductor manufacturer:

Other Similar products are found below:

AR0330CS1C12SPKAH3-GEVB MT9V034C12STCH-GEVB MT9V115EBKSTCH-GEVB 416015300-3 ISL29102IROZ-EVALZ

MT9M02IIA3XTMH-GEVB AR1820HSSC12SHQAH3-GEVB AR1335CSSC11SMKAH3-GEVB MAXCAMOV10640#

MT9M03II12STMH-GEVB TSL2581CS-DB TMD3700-DB NANOUSB2.2 ASX340AT3C00XPEDH3-GEVB AR0144ATSM20XUEAH3-GEVB AR0144CSSC00SUKAH3-GEVB AR0522SRSC09SURAH3-GEVB AR0522SRSM09SURAH3-GEVB AR0521SR2C09SURAH3-GEVB MARS1-MAX9295A-GEVK MARS1-MAX9296B-GEVB ISL29112IROZ-EVALZ AR0233AT2C17XUEAH3-GEVB

AR0431CSSC14SMRAH3-GEVB MARS-DEMO3-MIPI-GEVB TCS3430-DB AR0234CSSC00SUKAH3-GEVB AR0130CSSM00SPCAH-GEVB AR0330CM1C00SHAAH3-GEVB EVALZ-ADPD2212 TMD2772EVM TMG3993EVM MIKROE-2103 TSL2672EVM 1384

MT9M114EBLSTCZDH-GEVB SEN0043 SEN0162 TMD2771EVM TMD3782EVM TSL4531EVM 1918 AS7225 DEMO KIT SEN0097

SEN0228 AR0134CSSC00SUEAH3-GEVB AP0100AT2L00XUGAH3-GEVB AR0144CSSM20SUKAH3-GEVB 725-28915 EVAL-ADPD1081Z-PPG