# **Always-Listening, Voice Trigger Solution**

#### Introduction

BelaSigna<sup>®</sup> R281 is an ultra-low-power voice trigger solution for a wide range of consumer electronic devices. In a typical application BelaSigna R281 is "always listening" and will detect a single, user-trained trigger phrase, asserting a wake-up signal when this trigger phrase is detected.

"Always-listening" key phrase detection with an average power consumption of less than 300  $\mu W$  (not including the power consumption of the microphone) preserves Standby battery life.

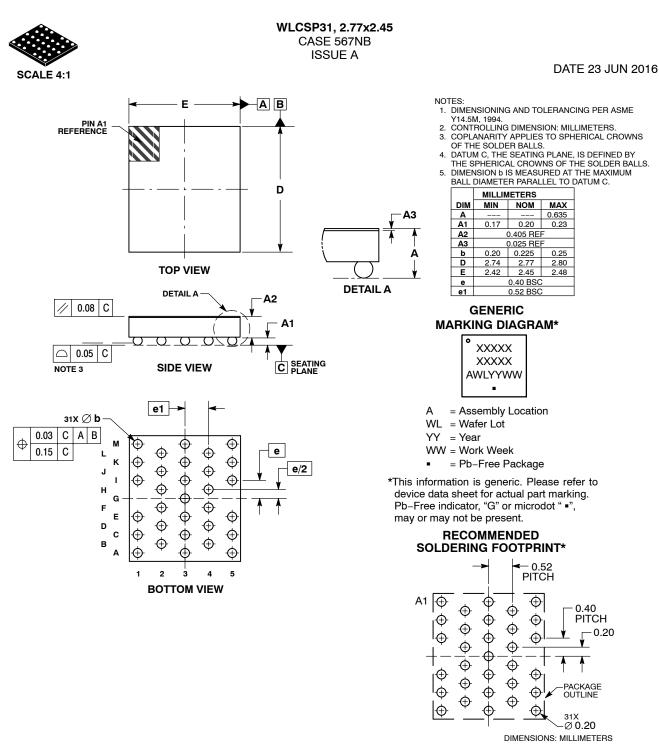

BelaSigna R281 is an ultra-miniature solution that is available in a 2.45 mm x 2.77 mm WLCSP package. It can be designed onto a single layer PCB with 5 mil routing and with a minimal amount of external components.

An external, I<sup>2</sup>C host controller is required to configure the device for operation.

#### **Key Features**

#### Proven Ultra-Low-Power Digital Signal Processing (DSP) Technology

- Audio DSP Technology Originally Developed for Hearing Aids Offers the Required Computational Power at Extremely Low Current Consumption

- $< 300 \,\mu\text{W}$  Average Current Consumption (not including microphone)

#### Mixed-Signal System-on-Chip (SoC)

- Audio-grade, Analog Input with Onboard Pre-amplifier

- Built-in, Regulated Voltages Including Onboard Microphone Bias for Power Efficient Operation

- Supports Analog or Digital Microphone Input

#### **Interfaces and Peripherals**

- I<sup>2</sup>C-based Device Configuration and Control

- GPIO Wake Signal

- Internal Oscillator

#### Applications

- Mobile Phones

- Tablets

- Portable Electronic Devices

- Wearables

- Toys

### **ON Semiconductor®**

www.onsemi.com

| 0W689 | -001 = Specific Device Code |

|-------|-----------------------------|

| А     | = Assembly Location         |

| WL    | = Wafer Lot                 |

| YY    | = Year                      |

|       |                             |

- WW = Work Week

- = Pb-Free Package

#### **ORDERING INFORMATION**

See detailed ordering and shipping information in the package dimensions section on page 10 of this data sheet.

#### **Figures and Data**

#### Table 1. ABSOLUTE MAXIMUM RATINGS

| Parameter                        | Symbol | Min  | Max  | Units |

|----------------------------------|--------|------|------|-------|

| Input Voltage on any Digital Pin |        | -0.3 | 3.8  | V     |

| Input Voltage on any Analog Pin  |        | -0.3 | 3.8  | V     |

| Input Voltage on any Supply Pin  |        | -0.3 | 3.8  | V     |

| Current on any Digital Pin       |        |      | ±5   | mA    |

| Current on any Analog Pin        |        |      | ± 10 | mA    |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

#### Table 2. RECOMMENDED OPERATING CONDITIONS

| Parameter                           | Symbol | Min  | Тур  | Max  | Units |

|-------------------------------------|--------|------|------|------|-------|

| Power Supply Applied to VBAT        | VBAT   | 1.75 | 1.8  | 1.98 | V     |

| Power Supply Applied to VDDO        | VDDO   | 1.62 | 1.8  | 3.63 | V     |

| Internal Oscillator Clock Frequency |        | 1    | 2.56 | 20   | MHz   |

| Ambient Operating Temperature Range | Та     | -40  |      | 85   | °C    |

#### Table 3. ESD AND LATCH-UP CHARACTERISTICS

| Parameter                  | Conditions                  | Max   | Units |

|----------------------------|-----------------------------|-------|-------|

| ESD – Human Body Model     | JEDEC JS-001-2010, all pins | 2000  | V     |

| ESD – Charged Device Model | JESD22-C101-E, all pins     | 750   | V     |

| ESD – Machine Model        | JESE22-A115-C, all pins     | 250   | V     |

| Latch – Up                 | JEDEC STD – 78, all pins    | ± 100 | mA    |

#### **Electrical Performance Specifications**

#### **Typical Values**

Unless otherwise noted, Typ values specify the typical values based on design and characterization data under normal operating conditions. Normal operating conditions include a supply voltage (VBAT) of 1.8 V and an operating temperature of 25°C. For specific blocks, the details of the normal operation conditions are described in their respective sections.

#### **Minimum and Maximum Values**

Unless otherwise noted, Min and Max values specify the designed range or measurement range and are guaranteed by design and/or characterization.

Min and Max values specified may be based on factory production test limits, design, or characterization data.

#### **Normal Operating Conditions**

Unless otherwise noted, normal operating conditions indicate an ambient temperature  $Ta = 25^{\circ}C$  and a supply voltage VBAT = 1.8 V. VDDD and VDDA are calibrated to their preset factory calibration settings and correspond to their respective Typ values. VDDO is powered externally at 1.8 V. No external loads are applied to digital I/O or analog pins.

#### Table 4. SYSTEM DC ELECTRICAL CHARACTERISTICS

Typical operating conditions (Ta = 25°C, VBAT=VDDO=1.8 V, VDDD=1.4 V) unless otherwise noted

| Parameter                | Symbol | Conditions                                                                                                      | Min | Тур | Max | Units |

|--------------------------|--------|-----------------------------------------------------------------------------------------------------------------|-----|-----|-----|-------|

| Average Run Mode Current | IDD    | VBAT=VDDA=1.8 V, charge pump disabled<br>Assumes a ratio of speech present versus<br>quiet environment of 20/80 |     | 170 |     | μΑ    |

# Table 5. DIGITAL I/O PINS (I2C, WAKE\_UP, DMIC) DC ELECTRICAL CHARACTERISTICS Typical operating conditions (Ta = 25°C, VDDO = 1.8 V, Pull – up/Pull – down Enabled) unless otherwise noted

| Parameter                 | Symbol                            | Cor                  | nditions     | Min        | Тур    | Max        | Units |

|---------------------------|-----------------------------------|----------------------|--------------|------------|--------|------------|-------|

| VDDO Supply Voltage Range | VDDO                              |                      |              | 1.25       | 1.8    | 3.63       | V     |

| Output Low Level          | V <sub>ol</sub>                   | l <sub>ol</sub> :    | = 4 mA       |            | 0      | 0.2 x VDDO | V     |

| Output High Level         | V <sub>oh</sub>                   | l <sub>ol</sub> =    | = –4 mA      | 0.8 x VDDO | VDDO   |            | V     |

| Input Low Level           | V <sub>il</sub>                   |                      |              |            | 0      | 0.2 x VDDO | V     |

| Input High Level          | V <sub>ih</sub>                   |                      |              | 0.8 x VDDO | VDDO   |            | V     |

| Pull–Up Resistance        | R <sub>pu</sub>                   | Non–I <sup>2</sup> C | VDDO = 1.8 V | 80         | 122    | 160        | kΩ    |

|                           |                                   |                      | VDDO = 3.3 V | 30         | 48     | 60         |       |

|                           |                                   | l <sup>2</sup> C     | VDDO = 1.8 V | 0.8 / 8    | 1 / 10 | 1.2 / 12   |       |

|                           |                                   | (strong/weak)        | VDDO = 3.3 V | 0.8 / 8    | 1 / 10 | 1.2 / 12   |       |

| Pull–Down Resistance      | R <sub>pd</sub>                   | VDD                  | 0 = 1.8 V    | 120        | 168    | 210        | kΩ    |

|                           |                                   | VDD                  | 0 = 3.3 V    | 30         | 60     | 80         |       |

| Pin Capacitance           | C <sub>pd</sub>                   |                      |              |            | 5      |            | pF    |

| Maximum Output Current    | I <sub>ol</sub> , I <sub>oh</sub> |                      |              |            |        | ± 4        | mA    |

| Input Leakage Current     | l                                 |                      |              |            |        | ± 1        | μΑ    |

### Table 6. VDDA REGULATOR DC & AC ELECTRICAL CHARACTERISTICS

Typical operating conditions (Ta =  $25^{\circ}$ C), charge pump in use, unless otherwise noted

| Parameter       | Symbol | Conditions       | Min | Тур  | Max | Units |

|-----------------|--------|------------------|-----|------|-----|-------|

| Output Voltage  | VDDA   | CL = 1 μF        | 1.8 | 1.98 | 2.0 | V     |

| Load Current    |        |                  |     |      | 4   | mA    |

| Load Regulation |        |                  |     | 5    |     | mV/mA |

| Line Regulation |        |                  |     | 20   |     | mV/V  |

| PSRR            |        | @ 1 kHz unloaded | 20  |      |     | dB    |

#### **Table 7. VREG REGULATOR DC & AC ELECTRICAL CHARACTERISTICS**

Typical operating conditions (Ta = 25°C), unless otherwise noted

| Parameter       | Symbol | Conditions       | Min  | Тур  | Max  | Units |

|-----------------|--------|------------------|------|------|------|-------|

| Output Voltage  | VREG   | CL = 1 μF        | 0.89 | 0.92 | 0.95 | V     |

| Load Current    |        |                  |      |      | 2    | mA    |

| Load Regulation |        |                  |      |      | 20   | mV/mA |

| Line Regulation |        |                  |      |      | 5    | mV/V  |

| PSRR            |        | @ 1 kHz unloaded | 40   |      |      | dB    |

#### Table 8. VDDD REGULATOR DC & AC ELECTRICAL CHARACTERISTICS Typical operating conditions (Ta = $25^{\circ}$ C), unless otherwise noted

| Parameter       | Symbol | Conditions       | Min | Тур | Max | Units |

|-----------------|--------|------------------|-----|-----|-----|-------|

| Output Voltage  | VDDD   | CL = 1 μF        | 1.2 | 1.4 | 1.7 | V     |

| Load Current    |        |                  |     |     | 15  | mA    |

| Load Regulation |        |                  |     |     | 10  | mV/mA |

| Line Regulation |        |                  |     |     | 20  | mV/V  |

| PSRR            |        | @ 1 kHz unloaded | 20  |     |     | dB    |

#### **System Diagrams**

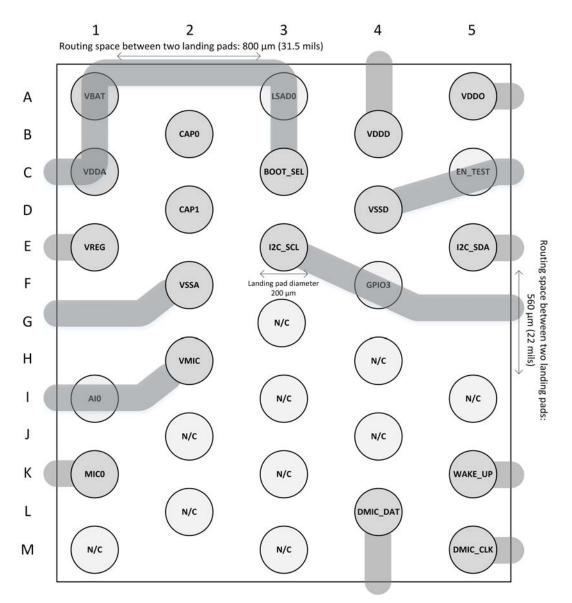

Figure 1. BelaSigna R281 WLCSP Suggested PCB Routing

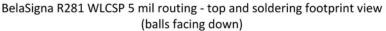

Figure 2. BelaSigna R281 System Diagram (WLCSP Package)

#### **Description of Operation**

Efficient implementation of the trigger phrase recognition algorithm is accomplished through the use of three processing units running concurrently. In addition to the main DSP core performing system configuration and signal processing, an input/output processor continuously collects frames of input speech signals which are analyzed by a highly optimized frequency domain co–processor.

There are two main modes of operation: Recognition Mode and Training Mode.

#### **Recognition Mode**

When in Recognition Mode, the entire system remains in an extremely low-power, "always-on" state continuously listening for speech. When speech is detected, the algorithm proceeds to extract features from the collected audio data, comparing these features to a known set of data computed during the training process. If the features appear to be similar enough to the trained feature data, a match is indicated on the WAKE\_UP pin.

Once the feature extraction and comparison is complete, the system returns to its original low–power state, once again waiting until speech is detected.

#### Training Mode

Before BelaSigna R281 can be placed into Recognition Mode, it must be trained. Training involves recording and analyzing three utterances of a *trigger phrase*. A trigger phrase can be any collection of words or sounds, in any language, up to a maximum length of approximately 1.5 seconds.

When speaking a given phrase, a human will naturally say the same phrase subtly different each time. Having multiple instances of the same phrase, each slightly different, helps to make the matching algorithm more robust. Training must be performed in a quiet environment, or the trigger phrase match results in Recognition Mode will be unpredictable. BelaSigna R281 is placed into Training Mode by issuing an appropriate SetMode command via I<sup>2</sup>C. The algorithm stores relevant feature data from the three separate utterances of the trigger phrase, also known as *training templates*.

Once training is complete, the training templates can be read from memory and stored offline. This template data can then be loaded into memory in the event of a power cycle and the device can be placed directly into Recognition Mode, thus avoiding the need to re-train the device. This same procedure can be used to recognize multiple trigger phrases, provided they have each been individually trained and stored offline. Only one trigger phrase can be active at any one time.

Refer to AND9267/D for more information on the different modes, as well as a description of the  $I^2C$  host control protocol.

#### Initial Power-On State

When BelaSigna R281 is powered on, the device will perform a brief initialization procedure and then wait for a connection to be made from an external host via I<sup>2</sup>C. At this point, the host controller must connect to BelaSigna R281 and load its memory with the algorithm binary image, as well as the training template data. Once this has been completed, the device can be put into Recognition Mode. If no training template data is available (e.g. the training procedure has never been performed), then BelaSigna R281 must be placed into Training Mode and the training procedure performed before entering Recognition Mode.

Whenever power is removed from the device, the contents of memory are lost and must be re–loaded.

For more information refer to AND9267/D.

#### System Performance

#### **Recognition Rate**

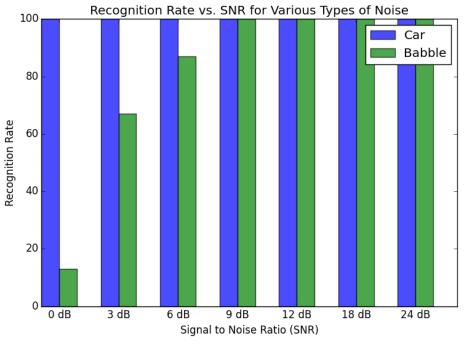

Performance has been measured in various noise conditions and is shown in Figure 3. Tests were performed in a sound isolation booth with a series of pre–recorded trigger and non–trigger phrases playing continuously, mixed

with varying levels of noise. Recognition rate is 100% in a quiet environment (no noise playing). The system was trained in a quiet environment. In all cases, the false trigger rate (the number of times the system triggered on a non-trigger phrase) was 0%.

Figure 3. Recognition Rate Versus SNR

#### **Current Consumption**

Average current consumption was also measured with the device operating in a pure noise environment with no speech present. The results are presented in Table 9.

#### **Table 9. AVERAGE CURRENT CONSUMPTION**

| Condition         | Average Current Consumption (uA), VBAT = 1.8 V |  |  |

|-------------------|------------------------------------------------|--|--|

| Quiet Environment | 160                                            |  |  |

| Babble Noise      | 170                                            |  |  |

\*Not including microphone current consumption

#### **Single User Operation**

Because BelaSigna R281 performs recognition based on a training procedure performed by a specific individual, recognition of the trigger phrase is effectively "single-user". Only the person who trained the system (or an individual with an extremely similar voice print) will be able to reliably trigger the device.

#### **Digital Interfaces**

#### Wake Up Pin

The Wake Up pin is a digital output (referenced to VDDO) which is used to indicate that the trigger phrase was detected. It is intended to be connected to a digital input of an external

host, and its behavior (active high versus active low and duration) is configurable via  $I^2C$ .

For more information refer to AND9267/D.

#### **Boot Select Pin**

This pin is reserved for future purpose and must be connected to VDDA.

#### Inter-IC Communication (I<sup>2</sup>C) Interface

The I<sup>2</sup>C interface is an industry–standard interface that can be used for high–speed transmission of data between BelaSigna R281 and an external device. The interface operates at speeds up to 100 Kbit/sec, and always operates in slave mode at an address of 0x62.

#### **Digital Microphone (DMIC) Interface**

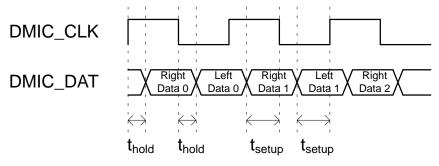

The digital microphone interface provides a means of interfacing a digital microphone to the system instead of an analog microphone. When the device is configured to use a digital microphone input instead of an analog microphone input (the default), an appropriate clock is output on the DMIC\_CLK pin and device accepts PDM signals from a digital microphone on the DMIC\_DAT input pin. A separate algorithm binary image is available supporting a digital microphone input.

Figure 4 shows the timing of the DMIC interface. For more information refer to AND9267/D.

Figure 4. DMIC Timing Diagram

### **Mechanical Information and Circuit Design Guidelines**

| WLCSP<br>Ball Index | Name     | Description                                                                           | Pad Type | Pull          |

|---------------------|----------|---------------------------------------------------------------------------------------|----------|---------------|

| A1                  | VBAT     | Main power supply                                                                     | Р        |               |

| A3                  | LSAD0    | Low-speed Analog to Digital Input                                                     | I        |               |

| A5                  | VDDO     | Digital I/O supply, capacitor to VSSD, typically connected to VBAT                    | Р        |               |

| B2                  | CAP0     | Charge pump capacitor to CAP1                                                         | А        |               |

| B4                  | VDDD     | Digital supply, capacitor to VSSD                                                     | Р        |               |

| C1                  | VDDA     | Analog supply voltage (output), capacitor to VSSA, or connected to VBAT (max. 1.98 V) | Р        |               |

| C3                  | BOOT_SEL | Boot selection (always connect to VDDA)                                               | AI       |               |

| C5                  | EN_TEST  | Test enable                                                                           | DIO      |               |

| D2                  | CAP1     | Charge pump capacitor to CAP0                                                         | А        |               |

| D4                  | VSSD     | Digital core and I/O ground, connect to VSSA on PCB                                   | Р        |               |

| E1                  | VREG     | Analog supply voltage (output), capacitor to VSSA                                     | А        |               |

| E3                  | I2C_SCL  | C_SCL I <sup>2</sup> C clock                                                          |          | PU            |

| E5                  | I2C_SDA  | I <sup>2</sup> C data                                                                 |          | PU<br>(Note   |

| F2                  | VSSA     | Analog ground                                                                         | Р        |               |

| F4                  | GPIO3    | General purpose digital input/output                                                  | DIO      |               |

| G3                  | N/A      | No connection                                                                         | NC       |               |

| H2                  | VMIC     | Analog microphone supply output                                                       | А        |               |

| H4                  | N/A      | No connection                                                                         | NC       |               |

| l1                  | AIO      | Analog input (unused)                                                                 | AI       |               |

| 13                  | N/A      | No connection                                                                         | NC       |               |

| 15                  | N/A      | No connection                                                                         | NC       |               |

| J2                  | N/A      | No connection                                                                         | NC       |               |

| J4                  | N/A      | No connection                                                                         | NC       |               |

| K1                  | MIC0     | Analog microphone input                                                               | AI       |               |

| K3                  | N/A      | No connection                                                                         | NC       |               |

| K5                  | WAKE_UP  | Wake up signal (output)                                                               | DIO      |               |

| L2                  | N/A      | No connection                                                                         | NC       |               |

| L4                  | DMIC_DAT | Digital microphone data input (optional)                                              | DIO      |               |

| M1                  | N/A      | No connection                                                                         | NC       |               |

| M3                  | N/A      | No connection                                                                         | NC       |               |

| M5                  | DMIC_CLK | Digital microphone clock (optional)                                                   | DIO      | PU<br>(Note 2 |

#### Table 10. PIN DESCRIPTION

The value of the I<sup>2</sup>C pull–ups is 10 K

Pull–up is disabled when the DMIC interface is enabled.

#### Legend:

Type: A = analog; D = digital; I = input; O = output; P = power; NC = not connected Pull: PU = pull up; PD = pull down All digital pads have a Schmitt trigger input

#### **Reflow Information**

The reflow profile depends on the equipment that is used for the re–flow and the assembly that is being re–flowed. Information from JEDEC Standard 22–A113D and J–STD–020D.01 can be used as a guideline.

#### Electrostatic Discharge (ESD) Device

CAUTION: ESD sensitive device. Permanent damage may occur on devices subjected to high–energy electrostatic discharges. Proper ESD precautions in handling, packaging and testing are recommended to avoid performance degradation or loss of functionality.

#### **Ordering Information**

To order BelaSigna R281, please contact your account manager.

#### **Chip Identification**

Chip identification information can be retrieved using the GetChipID I<sup>2</sup>C command.

Refer to AND9267/D for more details regarding supported  $I^2C$  commands.

#### **Company or Product Inquiries**

For more information about ON Semiconductor Sales products or services visit our website at <u>http://onsemi.com</u>.

#### **ORDERING INFORMATION**

| Part Number     | Chip ID | Package Option       | Shipping <sup>†</sup> |

|-----------------|---------|----------------------|-----------------------|

| BR281W31A101V1G | 0x5000  | WLCSP31<br>(Pb-Free) | 2500 / Tape & Reel    |

+For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

BELASIGNA is a registered trademark of Semiconductor Components Industries, LLC.

\*For additional information on our Pb–Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

| DOCUMENT NUMBER:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 98AON07006G        | Electronic versions are uncontrolled except when accessed directly from the Document Repository.<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |             |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| DESCRIPTION:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | WLCSP31, 2.77X2.45 |                                                                                                                                                                                     | PAGE 1 OF 1 |

| ON Semiconductor and ()) are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries.<br>ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding<br>the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically<br>disclaims any and all liability, including without limitation special, consequential or incidental damages. ON Semiconductor does not convey any license under its patent rights or the<br>rights of others. |                    |                                                                                                                                                                                     |             |

© Semiconductor Components Industries, LLC, 2019

onsemi, ONSEMI, and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi's product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. onsemi reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product features, availability, functionality, or suitability of its products for any particular purpose, nor does **onsemi** assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using **onsemi** products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by **onsemi**. "Typical" parameters which may be provided in **onsemi** data sheets and/or specifications can and do vary in different applications and calcular performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. **onsemi** does not convey any license under any of its intellectual property rights nor the rights of others. **onsemi** products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use **onsemi** products for any such unintended or unauthorized application, Buyer shall indemnify and hold **onsemi** and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that **onsemi** was negligent regarding the design or manufacture of the part. **onsemi** is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

#### PUBLICATION ORDERING INFORMATION

#### LITERATURE FULFILLMENT:

#### TECHNICAL SUPPORT

onsemi Website: www.onsemi.com

Email Requests to: orderlit@onsemi.com

North American Technical Support: Voice Mail: 1 800-282-9855 Toll Free USA/Canada Phone: 011 421 33 790 2910

Europe, Middle East and Africa Technical Support: Phone: 00421 33 790 2910 For additional information, please contact your local Sales Representative

# **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Audio DSPs category:

Click to view products by ON Semiconductor manufacturer:

Other Similar products are found below :

AT85C51SND3B1-RTTUL BR281W31A101V1G CS47048C-CQZR MAX9892ERT+T SB3231-E1 HMC1022-SX SA3229-E1-T LC75056PE-H IA8201-RDI-01 R3710-CEAA-E1 HMC5622LS7TR TAS3204PAGR LC823450TA-2H LC823450XDTBG ZL38052LDG1 ADAV4601BSTZ AD1954YSTZ ADAU1701JSTZ-RL AD1940YSTZ ADAU1702JSTZ PT2399 XD567 XD1881 TDA7440D013TR LM4863G-N20-R IA8201CQ SPK2611HM7H-1-2 CM108B CM118B HS-100B CM108AH S1V30120F01A100 CMX138AE1 LC786820E-6E03-3H DSPB56720AG LC823455XATBG XFS3031CNP ZL38060LDG1 BD37033FV-ME2 WT588H-16S WT588S-16S MC34118D BD3702FV-E2 TEA1062NG-S16-R TM2313 CD2399 PT2314E PT2259-S TM2312 PT7313E