# **High Performance, Integrated Current Mode PWM Controllers**

The CS5124 is a fixed frequency current mode controller designed specifically for DC-DC converters found in the telecommunications industry. The CS5124 integrates many commonly required current mode power supply features and allows the power supply designer to realize substantial cost and board space savings.

The CS5124 integrates the following features: Internal Oscillator, Slope Compensation, Sleep On/Off, Undervoltage Lock Out, Thermal Shutdown, Soft-Start Timer, Low Voltage Current Sense for Resistive Sensing, Second Current Threshold for Pulse-by-Pulse overcurrent Protection, a Direct Optocoupler Interface and Leading Edge Current Blanking.

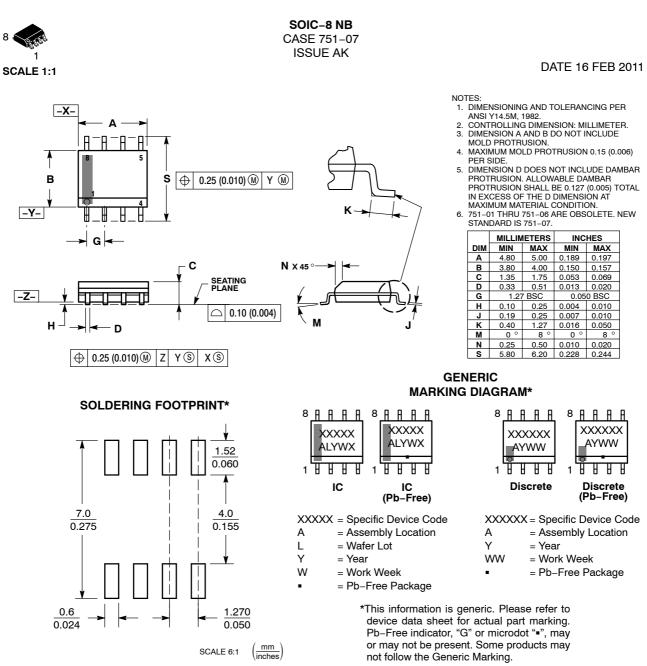

The CS5124 has supply range of 7.7 V to 20 V and is available in 8 pin SOIC narrow package.

#### **Features**

- 400 kHz Oscillating Frequency

- Line UVLO Monitoring

- Low Current Sense Voltage for Resistive Current Sensing

- Bias for Startup Circuitry

- Thermal Shutdown

- Sleep On/Off Pin

- Soft-Start Timer

- Leading Edge Blanking

- Direct Optocoupler Interface

- 90 ns Propagation Delay

- 35 ns Driver Rise and Fall Times

- Sleep Mode

- Pb-Free Packages are Available

### **ON Semiconductor**<sup>®</sup>

http://onsemi.com

## **D SUFFIX CASE 751**

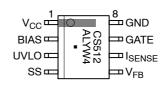

#### **PIN CONNECTIONS AND** MARKING DIAGRAM

| n |

|---|

| , |

- L = Wafer Lot Y

- = Year W

- = Work Week

- = Pb-Free Package

#### **ORDERING INFORMATION**

| Device      | Package             | Shipping <sup>†</sup> |

|-------------|---------------------|-----------------------|

| CS5124XD8   | SOIC-8              | 95 Units/Rail         |

| CS5124XD8G  | SOIC-8<br>(Pb-Free) | 95 Units/Rail         |

| CS5124XDR8  | SOIC-8              | 2500 Tape & Reel      |

| CS5124XDR8G | SOIC-8<br>(Pb-Free) | 2500 Tape & Reel      |

†For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

#### MAXIMUM RATINGS

| Rating                                                | Value             | Unit |

|-------------------------------------------------------|-------------------|------|

| Operating Junction Temperature, T <sub>J</sub>        | -40 to 135        | °C   |

| Storage Temperature Range, T <sub>S</sub>             | -40 to 150        | °C   |

| ESD Susceptibility (Human Body Model)                 | 2.0               | kV   |

| Lead Temperature Soldering: Reflow: (SMD styles only) | (Note 1) 230 peak | °C   |

Maximum ratings are those values beyond which device damage can occur. Maximum ratings applied to the device are individual stress limit values (not normal operating conditions) and are not valid simultaneously. If these limits are exceeded, device functional operation is not implied, damage may occur and reliability may be affected.

1. 60 second maximum above 183°C.

#### MAXIMUM RATINGS

| Pin Name                     | Pin Symbol         | V <sub>MAX</sub> | V <sub>MIN</sub> | ISOURCE                 | I <sub>SINK</sub>       |

|------------------------------|--------------------|------------------|------------------|-------------------------|-------------------------|

| V <sub>CC</sub> Power Input  | V <sub>CC</sub>    | 20 V             | –0.3 V           | 1.0 mA                  | 1.5 A Peak<br>200 mA DC |

| V <sub>CC</sub> Clamp Output | V <sub>BIAS</sub>  | 20 V             | –0.3 V           | 1.0 mA                  | 1.0 mA                  |

| UVLO Shutdown Input          | UVLO               | 6.0 V            | –0.3 V           | 1.0 mA                  | 1.0 mA                  |

| Soft-Start Capacitor Input   | SS                 | 6.0 V            | –0.3 V           | 1.0 mA                  | 2.0 mA                  |

| Voltage Feedback Input       | V <sub>FB</sub>    | 6.0 V            | –0.3 V           | 3.0 mA                  | 20 mA                   |

| Current Sense Input          | I <sub>SENSE</sub> | 6.0 V            | –0.3 V           | 1.0 mA                  | 1.0 mA                  |

| Ground                       | GROUND             | 0 V              | 0 V              | 1.5 A peak<br>200 mA DC | 1.0 mA                  |

| Gate Drive Output            | GATE               | 20 V             | –0.3 V           | 1.5 A peak<br>200 mA DC | 1.5 A peak<br>200 mA DC |

### CS5124

| ELECTRICAL CHARACTERISTICS                              | $(-40^{\circ}C \le T_J \le 125^{\circ}C; -40^{\circ}C \le T_A \le 105^{\circ}C, 7.60 \text{ V} \le V_{CC} \le 20 \text{ V}, \text{UVLO} = 3.0 \text{ V},$ |

|---------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| $I_{SENSE} = 0 V, C_{V(CC)} = 0.33 \mu F, C_{GATE} = 1$ | 0 nF (ESR = 10 $\Omega$ ); C <sub>SS</sub> = 470 pF; C <sub>V(FB)</sub> = 100 pF, unless otherwise specified.)                                            |

| Characteristic                                                                              | Test Conditions                                                                                       | Min                  | Тур  | Max   | Unit      |

|---------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|----------------------|------|-------|-----------|

| General                                                                                     |                                                                                                       |                      |      |       |           |

| I <sub>CC</sub> Operating – V <sub>GATE</sub> not switching                                 | -                                                                                                     | -                    | 10   | 13    | mA        |

| I <sub>CC</sub> at V <sub>CC</sub> Low                                                      | V <sub>CC</sub> = 6.0 V                                                                               | -                    | 500  | 750   | μA        |

| I <sub>CC</sub> Sleep                                                                       | V <sub>UVL</sub> = 1.0 V                                                                              | -                    | 210  | 275   | μA        |

| Low V <sub>CC</sub> Lockout                                                                 |                                                                                                       |                      |      |       |           |

| V <sub>CC</sub> Turn-on Threshold Voltage                                                   | _                                                                                                     | 7.2                  | 7.7  | 8.3   | V         |

| V <sub>CC</sub> Turn-off Threshold Voltage                                                  | _                                                                                                     | 6.8                  | 7.3  | 7.8   | V         |

| V <sub>CC</sub> Hysteresis                                                                  | _                                                                                                     | 350                  | 425  | 500   | mV        |

| UVLO                                                                                        |                                                                                                       |                      |      |       |           |

| Sleep Threshold Voltage                                                                     | UVLO decreasing                                                                                       | 1.5                  | 1.8  | 2.3   | V         |

| Sleep Threshold Voltage                                                                     | UVLO increasing                                                                                       | -                    | 1.88 | 2.45  | V         |

| Sleep Hysteresis                                                                            | _                                                                                                     | 35                   | 85   | 150   | mV        |

| UVLO Turn-off Threshold Voltage                                                             | (Note 2)                                                                                              | 2.3                  | 2.45 | 2.6   | V         |

| UVLO Turn-on Threshold Voltage                                                              | (Note 2)                                                                                              | 2.50                 | 2.63 | 2.76  | V         |

| UVLO Hysteresis                                                                             | Turn–on – Turn–off (–40°C $\leq$ T <sub>J</sub> $\leq$ 100°C) (Note 2)                                | 170                  | 185  | 200   | mV        |

| UVLO Hysteresis                                                                             | Turn–on – Turn–off (100°C $\leq$ T <sub>J</sub> $\leq$ 125°C) (Note 2)                                | 50                   | 185  | 400   | mV        |

| UVLO Input Bias Current                                                                     | -                                                                                                     |                      | _    | 1.0   | μA        |

| UVLO Clamp                                                                                  | With UVLO sinking 1.0 mA                                                                              | 5.0                  | 7.5  | 12    | V         |

| V <sub>CC</sub> Clamp and BIAS Pin                                                          | Connect an NFET as follows: BIAS = G, V <sub>CC</sub> = S,                                            | V <sub>IN</sub> = D. |      |       |           |

| V <sub>CC</sub> Clamp Voltage                                                               | 36 V $\leq$ V $_{IN}$ $\leq$ 60 V, 200 nF $\leq$ C $_{SS}$ $\leq$ 500 nF, R = 500 k                   | 7.275                | 7.9  | 8.625 | V         |

| BIAS Minimum Voltage                                                                        | Measure Voltage on BIAS with: 10 V $\leq$ V_{CC} $\leq$ 20 V & 50 $\mu A \leq$ I_{BIAS} $\leq$ 1.0 mA | 1.6                  | 2.8  | 4.0   | V         |

| BIAS Clamp                                                                                  | With BIAS pin sinking 1.0 mA                                                                          | 12                   | 15   | 20    | V         |

| Difference between Regulated V <sub>CC</sub><br>& V <sub>CC</sub> Turn-on Threshold Voltage | (V <sub>CC</sub> Clamp Voltage) – (V <sub>CC</sub> Turn-on Threshold)                                 | 100                  | -    | -     | mV        |

| 400 kHz Oscillator                                                                          |                                                                                                       |                      |      |       |           |

| Operating Frequency                                                                         | _                                                                                                     | 360                  | 400  | 440   | kHz       |

| Max Duty Cycle Clamp                                                                        | _                                                                                                     | 80.0                 | 82.5 | 85.0  | %         |

| Slope Compensation                                                                          | _                                                                                                     | 15                   | 21   | 26    | mV/į<br>σ |

2. Not tested in production. Specification is guaranteed by design.

### CS5124

| $\textbf{ELECTRICAL CHARACTERISTICS (continued) (-40^{\circ}C \leq T_{J} \leq 125^{\circ}C; -40^{\circ}C \leq T_{A} \leq 105^{\circ}C, 7.60 \text{ V} \leq V_{CC} \leq 20 \text{ V}, \text{UVLO} = 3.0 \text{ V}, 125^{\circ}C; -40^{\circ}C \leq T_{A} \leq 105^{\circ}C, 7.60 \text{ V} \leq V_{CC} \leq 20 \text{ V}, 100^{\circ}C \leq 100^{\circ}C < 100^{\circ}C \leq 100^{\circ}C < 100^{$ |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| $I_{SENSE}$ = 0 V, $C_{V(CC)}$ = 0.33 $\mu$ F, $C_{GATE}$ = 1.0 nF (ESR = 10 $\Omega$ ); $C_{SS}$ = 470 pF; $C_{V(FB)}$ = 100 pF, unless otherwise specified.)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

| Characteristic                                                 | Test Conditions                                                        | Min                   | Тур                   | Max  | Unit |

|----------------------------------------------------------------|------------------------------------------------------------------------|-----------------------|-----------------------|------|------|

| Soft-Start                                                     |                                                                        |                       |                       |      |      |

| Soft-Start Charge Current                                      | -                                                                      | 7.0                   | 10                    | 13   | μA   |

| Soft-Start Discharge Current                                   | _                                                                      | 0.5                   | 10.0                  | -    | mA   |

| V <sub>SS</sub> Voltage when V <sub>FB</sub> Begins to<br>Rise | V <sub>FB</sub> = 300 mV                                               | 1.40                  | 1.62                  | 1.80 | V    |

| Peak Soft-Start Charge Voltage                                 | _                                                                      | 4.7                   | 4.9                   | -    | V    |

| Valley Soft-Start Discharge Voltage                            | _                                                                      | 200                   | 275                   | 400  | mV   |

| Current Sense                                                  |                                                                        |                       |                       |      |      |

| First Current Sense Threshold                                  | At max duty cycle                                                      | 170                   | 195                   | 215  | mV   |

| Second Current Sense Threshold                                 | _                                                                      | 250                   | 275                   | 315  | mV   |

| I <sub>SENSE</sub> to GATE Prop. Delay                         | 0 to 700 mV pulse into I <sub>SENSE</sub> (after blanking time)        | 60                    | 90                    | 130  | ns   |

| Leading Edge Blanking Time                                     | 0 to 400 mV pulse into I <sub>SENSE</sub>                              | 90                    | 130                   | 180  | ns   |

| Internal Offset                                                | Note 3                                                                 | _                     | 60                    | l    | mV   |

| Voltage Feedback                                               |                                                                        |                       |                       |      |      |

| V <sub>FB</sub> Pull–up Res.                                   | _                                                                      | 2.9                   | 4.3                   | 8.1  | kΩ   |

| V <sub>FB</sub> Clamp Voltage                                  | / <sub>FB</sub> Clamp Voltage                                          |                       | 2.90                  | 3.15 | V    |

| V <sub>FB</sub> Fault Voltage Threshold                        | -                                                                      | 460                   | 490                   | 520  | mV   |

| Output Gate Drive                                              |                                                                        |                       |                       |      |      |

| Maximum Sleep Pull-down Voltage                                | V <sub>CC</sub> = 6.0 V, I <sub>OUT</sub> = 1.0 mA                     | _                     | 1.2                   | 2.0  | V    |

| GATE High (AC)                                                 | Series resistance < 1.0 $\Omega$ , (Note 3)                            | V <sub>CC</sub> - 1.0 | V <sub>CC</sub> – 0.5 | -    | V    |

| GATE Low (AC)                                                  | Series resistance < 1.0 $\Omega$ , (Note 3)                            | -                     | 0.0                   | 0.5  | V    |

| GATE High Clamp Voltage                                        | V <sub>CC</sub> = 20 V                                                 | 11.0                  | 13.5                  | 16.0 | V    |

| Rise Time                                                      | Measure GATE rise time,<br>1.0 V < GATE < 9.0 V V <sub>CC</sub> = 12 V | -                     | 45                    | 65   | ns   |

| Fall Time                                                      | Measure GATE fall time,<br>9.0 V > GATE > 1.0 V V <sub>CC</sub> = 12 V | -                     | 25                    | 55   | ns   |

| Thermal Shutdown                                               |                                                                        |                       |                       |      |      |

| Thermal Shutdown Temperature                                   | (Note 3) GATE low                                                      | 135                   | 150                   | 165  | °C   |

| Thermal Enable Temperature                                     | (Note 3) GATE switching                                                | 100                   | 125                   | 150  | °C   |

| Thermal Hysteresis                                             | (Note 3)                                                               | 15                    | 25                    | 35   | °C   |

3. Not tested in production. Specification is guaranteed by design.

### CS5124

### PACKAGE PIN DESCRIPTION

| PIN # | Pin                | Description                                                                                                                                                                                                                                                                                                                                                           |

|-------|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1     | V <sub>CC</sub>    | V <sub>CC</sub> Power Input Pin.                                                                                                                                                                                                                                                                                                                                      |

| 2     | BIAS               | V <sub>CC</sub> Clamp Output Pin. This pin will control the gate of an N-channel MOSFET that in turn regulates Vcc. This pin is internally clamped at 15 V when the IC is in sleep mode.                                                                                                                                                                              |

| 3     | UVLO               | Sleep and under voltage lockout pin. A voltage greater than 1.8 V causes the chip to "wake up" however the GATE remains low. A voltage greater than 2.6 V on this pin allows the output to switch.                                                                                                                                                                    |

| 4     | SS                 | Soft–Start Capacitor Pin. A capacitor placed between SS and GROUND is charged with 10 $\mu$ A and discharged with 10 mA. The Soft–Start capacitor controls both Soft–Start time and hiccup mode frequency.                                                                                                                                                            |

| 5     | V <sub>FB</sub>    | Voltage Feedback Pin. The collector of an optocoupler is typically tied to this pin. This pin is pulled up internally by a 4.3 k $\Omega$ resistor to 5.0 V and is clamped internally at 2.9 V (2.65 V). If V <sub>FB</sub> is pulled > 4.0 V, the oscillator is disabled and GATE will stay high. If the V <sub>FB</sub> pin is pulled < 0.49 V, GATE will stay low. |

| 6     | I <sub>SENSE</sub> | Current Sense Pin. This pin is connected to the current sense resistor on the primary side. If $V_{FB}$ is floating, the GATE will go low if $I_{SENSE}$ = 195 mV (335 mV). If $I_{SENSE}$ > 275 mV (525 mV), Soft–Start will be initiated.                                                                                                                           |

| 7     | GATE               | Gate Drive Output Pin. Capable of driving a 3.0 nF load. GATE is nominally clamped to 13.5 V.                                                                                                                                                                                                                                                                         |

| 8     | GND                | Ground Pin.                                                                                                                                                                                                                                                                                                                                                           |

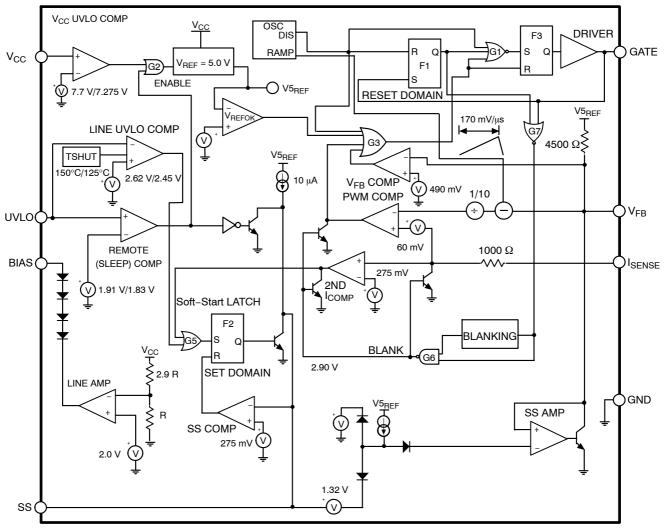

Figure 2. Block Diagram

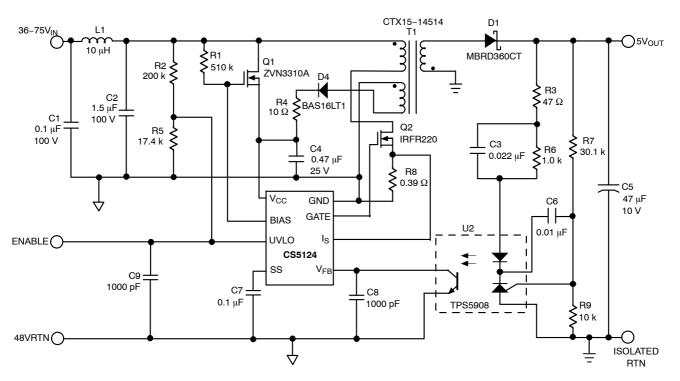

#### Powering the IC

$V_{CC}$  can be powered directly from a regulated supply and requires 500  $\mu$ A of startup current. The CS5124 includes a line bias pin (BIAS) that can be used to control a series pass transistor for operation over a wide input voltage. The BIAS pin will control the gate voltage of an N-channel MOSFET placed between V<sub>IN</sub> and V<sub>CC</sub> to regulate V<sub>CC</sub> at 8.0 V.

#### V<sub>CC</sub> and UVLO Pins

The UVLO pin has three different modes; low power shutdown, Line UVLO, and normal operation. To illustrate how the UVLO pin works; assume that  $V_{IN}$ , as shown in the application schematic, is ramped up starting at 0 V with the UVLO pin open. The SS and I<sub>SENSE</sub> pins also start at 0 V. While the UVLO is below 1.8 V, the IC will remain in a low current sleep mode and the BIAS pin of the CS5124 is internally clamped to a maximum of 15 V. When the voltage on the UVLO pin rises to between 1.8 V and 2.6 V the reference for the V<sub>CC</sub> UVLO is enabled and V<sub>CC</sub> is

regulated to 8.0 V by the BIAS pin, but the IC remains in a UVLO state and the output driver does not switch. When the UVLO pin exceeds 2.6 V and the  $V_{CC}$  pin exceeds 7.7 V, the GATE pin is released from a low state and can begin switching based on the comparison of the I<sub>SENSE</sub> and V<sub>FB</sub> pins. The Soft–Start capacitor begins charging from 0 V at 10  $\mu$ A. As the capacitor charges, a buffered version of the capacitor voltage appears on the V<sub>FB</sub> pin and the V<sub>FB</sub> voltage begins to rise. As V<sub>FB</sub> rises the duty cycle increases until the supply comes into regulation.

#### Soft-Start

Soft–Start is accomplished by clamping the V<sub>FB</sub> pin 1.32 V below the SS pin during normal start up and during restart after a fault condition. When the CS5124 starts, the Soft–Start capacitor is charged from a 10  $\mu$ A source from 0 V to 4.9 V. The V<sub>FB</sub> pin follows the Soft–Start pin offset by –1.32 V until the supply comes into regulation or until

the Soft–Start error amp is clamped at 2.9 V. During fault conditions the Soft–Start capacitor is discharged at 10 mA.

#### **Fault Conditions**

The CS5124 recognizes the following faults: UVLO off, Thermal Shutdown,  $V_{REF(OK)}$ , and Second Current Threshold. Once a fault is recognized, fault latch F2 is set and the IC immediately shuts down the output driver and discharges the Soft–Start capacitor. Soft–Start will begin only after all faults have been removed and the Soft–Start capacitor has been discharged to less than 0.275 V. Each fault will be explained in the following sections.

#### Under Voltage Lockout (UVLO)

The UVLO pin is tied to typically the midpoint of a resistive divider between  $V_{IN}$  and GROUND. During a start up sequence, this pin must be above 2.6 V in order for the IC to begin normal operation. If the IC is running and this pin is pulled below 1.8 V, F2 shuts down the output driver and discharges the Soft–Start capacitor in order to insure proper startup. If the UVLO pin is pulled high again before the Soft–Start discharge and, if no other faults are present, will immediately restart the power supply. If the UVLO pin stays low, then it will enter either the low current sleep mode or the UVLO state depending on the level of the UVLO pin.

#### **Thermal Shutdown**

If the IC junction temperature exceeds approximately  $150^{\circ}$ C the thermal shutdown circuit sets F2, which shuts down the output driver and discharges the Soft–Start capacitor. If no other faults are present the IC will initiate Soft–Start when the IC junction temperature has been reduced by  $25^{\circ}$ C.

### V<sub>REF(OK)</sub>

$V_{REF(OK)}$  is an internal monitor that insures the internal regulator is running before any switching occurs. This function does not trip the fault comparator like the other fault functions. To insure that Soft–Start will occur at low line conditions the UVLO divider should be set up so that the  $V_{CC}$  UVLO comparator turns on before the LINE UVLO comparator.

#### Second Threshold Comparator

Since the maximum dynamic range of the I<sub>SENSE</sub> signal in normal operation is 195 mV, any voltage exceeding this threshold on the I<sub>SENSE</sub> pin is considered a fault and the PWM cycle is terminated. The 2nd I<sub>COMP</sub> compares the I<sub>SENSE</sub> signal with a 275 mV threshold. If the I<sub>SENSE</sub> voltage exceeds the second threshold, F2 is set, the driver turns off, and the Soft–Start capacitor discharges. After the Soft–Start capacitor has discharged to less than 0.275 V Soft–Start will begin. If the fault condition has been removed the supply will operate normally. If the fault remains the supply will operate in hiccup mode until the fault condition is removed.

#### V<sub>FB</sub> Comparator

The  $V_{FB}$  comparator detects when the output voltage is too high. When the regulated output voltage is too high, the feedback loop will drive  $V_{FB}$  low. If  $V_{FB}$  is less than 0.49 V the output of the  $V_{FB}$  comparator will go high and shut the output driver off.

#### Oscillator

The internally trimmed, 400 kHz provides the slope compensation ramp as well as the pulse for enabling the output driver.

#### **PWM Comparator and Slope Compensation**

The CS5124 provides a fixed internal slope compensation ramp that is subtracted from the feedback signal. The PWM comparator compares peak primary current to a portion of the difference of the feedback voltage and slope compensation ramp. The 170 mV/ $\mu$ s slope compensation ramp is subtracted from the voltage feedback signal internally. The difference signal is then divided by ten before the PWM comparator to provide high noise rejection with a low voltage across the current sense network. The effective ramp is 21 mV/ $\mu$ s. A 60 mV nominal offset on the positive input to the PWM comparator allows for operation with the I<sub>SENSE</sub> pin at, or even slightly below GND.

A 4.3 k $\Omega$  pull-up resistor internally connected to a 5.0 V nominal reference provides the bias current to for an optocoupler connection to the V<sub>FB</sub> pin.

#### **APPLICATION INFORMATION**

#### **UVLO and Thermal Shutdown Interaction**

The UVLO pin and thermal shutdown circuit share the same internal comparator. During high temperature operation ( $T_J > 100^{\circ}$ C) the UVLO pin will interact with the thermal shutdown circuit. This interaction increases the turn–on threshold (and hysteresis) of the UVLO circuit. If the UVLO pin shuts down the IC during high temperature operation, higher hysteresis (see hysteresis specification) might be required to enable the IC.

#### **BIAS Pin**

The bias pin can be used to control  $V_{CC}$  as shown in the main application diagram in Figure 1. In order to provide adequate phase margin for the bias control loop, the pole created by the series pass transistor and the  $V_{CC}$  bypass capacitor should be kept above 10 kHz. The frequency of this pole can be calculated by Formula (1).

Pole Frequency =

$$\frac{\text{Transconductance of pass Transistor}}{2 \times \pi \times C_{V(CC)}}$$

(1)

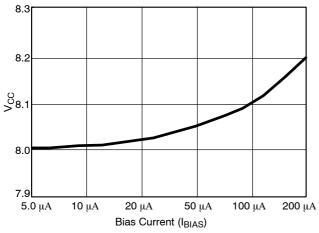

The Line BIAS pin shows a significant change in the regulated  $V_{CC}$  voltage when sinking large currents. This will show up as poor line regulation with a low value pull-up resistor. Typical regulated  $V_{CC}$  vs BIAS pin sink current is shown in Figure 3.

Figure 3. Regulated V<sub>CC</sub> vs. BIAS Sink Current

The BIAS pin and associated components form a high impedance node. Care should be taken during PCB layout to avoid connections that could couple noise into this node. To ensure adequate design margin between the regulated  $V_{CC}$  and the Low  $V_{CC}$  Lockout voltage, a guaranteed minimum differential between the two values is specified (see electrical characteristcs).

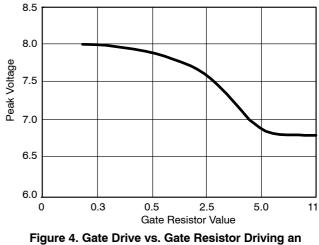

#### Gate Drive

Rail to rail gate driver operation can be obtained (up to 13.5 V) over a range of MOSFET input capacitance if the gate resistor value is kept low. Figure 5 shows the high gate drive level vs. the series gate resistance with  $V_{CC} = 8.0$  V driving an IRF220.

IRF220 (V<sub>CC</sub> = 8.0 V)

A large negative dv/dt on the power MOSFET drain will couple current into the gate driver through the gate to drain capacitance. If this current is kept within absolute maximum ratings for the GATE pin it will not damage the IC. However if a high negative dv/dt coincides with the start of a PWM duty cycle, there will be small variations in oscillator frequency due to current in the controller substrate. If required, this can be avoided by choosing the transformer ratio and reset circuit so that a high dv/dt does not coincide with the start of a PWM cycle, or by clamping the negative voltage on the GATE pin with a Schottky diode

#### First Current Sense Threshold

During normal operation the peak primary current is controlled by the level of the  $V_{FB}$  pin (as determined by the control loop) and the current sense network. Once the signal on the I<sub>SENSE</sub> pin exceeds the level determined by  $V_{FB}$  pin the PWM cycle terminates. During high output currents the  $V_{FB}$  pin will rise until it reaches the  $V_{FB}$  clamp. The first current sense threshold determines the maximum signal allowed on the I<sub>SENSE</sub> pin before the PWM cycle is terminated. Under this condition the maximum peak current is determined by the  $V_{FB}$  Clamp, the slope compensation ramp, the PWM comparator offset voltage and the PWM on time. The nominal first current threshold varies with on time and can be calculated from Formulas (2) and (3) below.

1st Threshold =

$$\frac{2.9 \text{ V} - 170 \text{ mV}/\mu\text{s} \times \text{T}_{ON}}{10} - 60 \text{ mV}$$

(2)

When the output current is high enough for the I<sub>SENSE</sub> pin to exceed the first threshold, the PWM cycle terminates early and the converter begins to function more like a current source. The current sense network must be chosen so that the peak current during normal operation does not exceed the first current sense threshold.

#### Second Current Sense Threshold

The second threshold is intended to protect the converter from overheating by switching to a low duty cycle mode when there are abnormally high fast rise currents in the converter. If the second current sense threshold is tripped, the converter will shut off and restart in Soft–Start mode until the high current condition is removed. The dead time after a second threshold overcurrent condition will primarily be determined by the time required to charge the Soft–Start cap from 0.275 V nominal to 1.32 V.

The second threshold will only be reached when a high dv/dt is present at the current sense pin. The signal must be fast enough to reach the second threshold before the first threshold turns off the driver. This will normally happen if the forward inductor saturates or when there is a shorted load.

Excessive filtering of the current sense signal, a low value current sense resistor, or even an inductor that does not saturate during heavy output currents can prevent the second threshold from being reached. In this case the first current sense threshold will trip during each cycle of high output current conditions. The first threshold will limit output current but some components, especially the output rectifier, can overheat due to higher than normal average output current.

#### **Slope Compensation**

Current mode converters operating at duty cycles in excess of 50% require an artificial ramp to be added to the current waveform or subtracted from the feedback waveform. For the current loop to be stable the artificial ramp must be equivalent to at least 50% of the inductor current down slope and is typically chosen between 75% to 100% of the inductor down current down slope.

To choose an inductor value such that the internal slope compensation ramp will be equal to a certain fraction of the inductor down current slope use the Formula (4).

$$\frac{1}{\text{Internal Ramp}} \times (V_{OUT} + V_{RECTIFIER}) \times \frac{N_{SECONDARY}}{N_{PRIMARY}} \times$$

RSENSE × Slope Value Factor = Inductor Value(H) (4)

Calculating the nominal inductor value for an artificial ramp equivalent to 100% of the current inductor down slope at CS5124 nominal conditions, a 5.0 V output, a 200 m $\Omega$  current sense resistor and a 4:1 transformer ratio yields

$$\frac{1}{20 \text{ mV}/\mu\text{s}} \times (5.0 \text{ V} + 0.3 \text{ V}) \times \frac{1}{4} \times 0.2 \Omega \times 1.0 = 13.2 \,\mu\text{H} \qquad (5)$$

To check that the slope compensation ramp will be greater than 50% of the inductor down under all conditions, substitute the minimum internal slope compensation value and use 0.5 for the slope compensation value. Then check that the actual inductor value will always be greater than the inductor value calculated.

#### Powering the CS5124 from a Transformer Winding

There are numerous ways to power the CS5124 from a transformer winding to enable the converter to be operated at high efficiency over a wide input range.

The CS5124 application circuit in Figure 1 is a flyback converter that uses a second flyback winding to power  $V_{CC}$ . R4 improves  $V_{CC}$  regulation with load changes by snubbing the turn off spike. Once the turn off spike has subsided the voltage of this winding is voltage proportional to the voltage on the main flyback winding. This voltage is regulated because the main winding is clamped by the regulated output voltage.

A flyback winding from a forward transformer can also be used to power V<sub>CC</sub>. Ideally the transformer volt-second product of a forward converter would be constant over the range of line voltages and load currents; and the transformer inductance could be chosen to store the required level of energy during each cycle to power  $V_{CC}$ . Even though the flyback energy is not directly regulated it would remain constant. Unfortunately in a real converter there are many nonideal effects that degrade regulation. Transformer inductance varies, converter frequency varies, energy stored in primary leakage inductance varies with output current, stray transformer capacitances and various parasitics all effect the level of energy available for V<sub>CC</sub>. If too little energy is provided to V<sub>CC</sub>, the bootstrapping circuit must provide power and efficiency will be reduced. If too much energy is provided V<sub>CC</sub> rises and may damage the controller. If this approach is taken the circuit must be carefully designed and component values must be controlled for good regulation.

\*For additional information on our Pb–Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

#### **STYLES ON PAGE 2**

| DOCUMENT NUMBER:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | MENT NUMBER: 98ASB42564B Electronic versions are uncontrolled except when accessed directly from the Document Repositor<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |  |  |  |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| DESCRIPTION: SOIC-8 NB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                            |  |  |  |  |  |  |

| ON Semiconductor and ()) are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries.<br>ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding<br>the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically<br>disclaims any and all liability, including without limitation special, consequential or incidental damages. ON Semiconductor does not convey any license under its patent rights nor the<br>rights of others. |                                                                                                                                                                                                            |  |  |  |  |  |  |

#### SOIC-8 NB CASE 751-07 ISSUE AK

STYLE 1: PIN 1. EMITTER COLLECTOR 2. З. COLLECTOR EMITTER 4 5 FMITTER BASE 6. 7. BASE 8. EMITTER STYLE 5: PIN 1. DRAIN 2. DRAIN З. DRAIN DRAIN 4. GATE 5. 6. GATE SOURCE 7 8. SOURCE STYLE 9: PIN 1. EMITTER, COMMON 2. COLLECTOR, DIE #1 3 COLLECTOR, DIE #2 EMITTER, COMMON 4. 5. EMITTER, COMMON BASE, DIE #2 BASE, DIE #1 6. 7. EMITTER, COMMON 8. STYLE 13: PIN 1. N.C 2. SOURCE З. SOURCE GATE 4. 5. DRAIN 6. DRAIN DRAIN 7. 8. DRAIN STYLE 17: PIN 1. VCC 2. V2OUT З. V10UT TXE 4. 5. RXE 6. VFF GND 7. 8. ACC STYLE 21: CATHODE 1 PIN 1. CATHODE 2 2. 3 CATHODE 3 CATHODE 4 4. 5. CATHODE 5 6. COMMON ANODE COMMON ANODE 7 8. CATHODE 6 STYLE 25: PIN 1. VIN 2 N/C 3. REXT

STYLE 2: PIN 1. COLLECTOR, DIE, #1 COLLECTOR, #1 2. COLLECTOR, #2 З. COLLECTOR, #2 4 5 BASE #2 EMITTER, #2 6. 7. BASE, #1 8. EMITTER, #1 STYLE 6: PIN 1. SOURCE 2. DRAIN З. DRAIN SOURCE 4. SOURCE 5. 6. GATE 7 GATE 8. SOURCE STYLE 10: PIN 1. GROUND 2. BIAS 1 OUTPUT 3 GROUND 4. 5. GROUND 6. BIAS 2 INPUT 7. GROUND 8. STYLE 14 PIN 1. N-SOURCE N-GATE 2. 3 P-SOURCE P-GATE 4. P-DRAIN 5. 6. P-DRAIN N-DRAIN 7. 8. N-DRAIN STYLE 18: PIN 1. ANODE 2. ANODE 3 SOURCE GATE 4. DRAIN 5. 6 DRAIN CATHODE 7. 8. CATHODE STYLE 22 PIN 1. I/O LINE 1 COMMON CATHODE/VCC 2 3 COMMON CATHODE/VCC I/O LINE 3 4. COMMON ANODE/GND 5 6. I/O LINE 4 7 1/0 LINE 5 8. COMMON ANODE/GND STYLE 26: PIN 1. GND 2 dv/dt ENABLE З. 4. ILIMIT 5. SOURCE SOURCE 6. 7. SOURCE 8. VCC STYLE 30: DRAIN 1 PIN 1. DRAIN 1 2 GATE 2 З. 4 SOURCE 2 SOURCE 1/DRAIN 2 SOURCE 1/DRAIN 2 5. 6. 7. SOURCE 1/DRAIN 2

8. GATE 1

STYLE 3: PIN 1. DRAIN, DIE #1 DRAIN, #1 2. DRAIN, #2 З. DRAIN, #2 4 5 GATE #2 SOURCE, #2 6. GATE, #1 8. SOURCE, #1 STYLE 7: PIN 1. INPUT 2. EXTERNAL BYPASS З. THIRD STAGE SOURCE GROUND 4. DRAIN 5. 6. GATE 3 SECOND STAGE Vd 7 8. FIRST STAGE Vd STYLE 11: PIN 1. SOURCE 1 2. GATE 1 SOURCE 2 GATE 2 3 4. 5. DRAIN 2 6. DRAIN 2 DRAIN 1 7. 8. DRAIN 1 STYLE 15: PIN 1. ANODE 1 2. ANODE 1 3 ANODE 1 ANODE 1 4. CATHODE, COMMON 5. CATHODE, COMMON CATHODE, COMMON 6. 7. 8. CATHODE, COMMON STYLE 19 PIN 1. SOURCE 1 2. GATE 1 SOURCE 2 3. GATE 2 4. DRAIN 2 5. 6. MIRROR 2 7. DRAIN 1 8. MIRROR 1 STYLE 23 PIN 1. LINE 1 IN COMMON ANODE/GND 2. З. COMMON ANODE/GND LINE 2 IN 4. LINE 2 OUT 5. 6. COMMON ANODE/GND COMMON ANODE/GND 7 LINE 1 OUT 8. STYLE 27: PIN 1. ILIMIT 2 OVLO UVLO З. INPUT+ 4. 5. SOURCE SOURCE 6. SOURCE 7. 8 DRAIN

#### STYLE 4: PIN 1. ANODE ANODE 2. ANODE З. 4. ANODE 5 ANODE ANODE 6. 7. ANODE 8. COMMON CATHODE STYLE 8: PIN 1. COLLECTOR, DIE #1 2. BASE, #1 З. BASE, #2 COLLECTOR. #2 4. COLLECTOR, #2 5. 6. EMITTER, #2 EMITTER #1 7 8. COLLECTOR, #1 STYLE 12: PIN 1. SOURCE 2. SOURCE SOURCE GATE 3. 4. 5. DRAIN 6. DRAIN DRAIN 7. DRAIN 8. STYLE 16: PIN 1. EMITTER, DIE #1 BASE, DIE #1 2.

EMITTER, DIE #2

COLLECTOR, DIE #2

COLLECTOR, DIE #2

COLLECTOR. DIE #1

COLLECTOR, DIE #1

BASE, DIE #2

SOURCE (P)

GATE (P)

3

4.

5.

6.

7.

8.

2. GATE (N)

3. 4.

STYLE 20: PIN 1. SOURCE (N)

5. DRAIN 6. DRAIN DRAIN 7. 8. DRAIN STYLE 24: PIN 1. BASE 2. EMITTER З. COLLECTOR/ANODE COLLECTOR/ANODE 4. CATHODE 5. 6. CATHODE COLLECTOR/ANODE 7 COLLECTOR/ANODE 8. STYLE 28: PIN 1. SW\_TO\_GND 2. DASIC\_OFF З. DASIC\_SW\_DET 4. GND 5. V MON VBULK 6. 7. VBULK 8. VIN

| DOCUMENT NUMBER:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 98ASB42564B | Electronic versions are uncontrolled except when accessed directly from the Document Repository.<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |             |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--|--|--|

| DESCRIPTION: SOIC-8 NB PAGE 2 C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |             |                                                                                                                                                                                     | PAGE 2 OF 2 |  |  |  |

| ON Semiconductor and are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries.<br>ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding<br>the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or dircuit, and specifically<br>disclaims any and all liability, including without limitation special, consequential or incidental damages. ON Semiconductor does not convey any license under its patent rights nor the |             |                                                                                                                                                                                     |             |  |  |  |

4. GND

5. IOUT

6.

7. IOUT

8. IOUT

2.

З.

4.

5.

6.

7. 8

rights of others.

STYLE 29:

PIN 1.

IOUT

BASE, DIE #1

EMITTER, #1 BASE, #2

EMITTER, #2

COLLECTOR, #2

COLLECTOR, #2

COLLECTOR, #1

COLLECTOR, #1

#### DATE 16 FEB 2011

onsemi, OnSemi, and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. **onsemi** owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of **onsemi**'s product/patent coverage may be accessed at <u>www.onsemi.com/site/pdf/Patent-Marking.pdf</u>. **onsemi** reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided "as-is" and **onsemi** makes no warranty, representation or guarantee regarding the accuracy of the information, product features, availability, functionality, or suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using **onsemi** products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by **onsemi**. "Typical" parameters, including "Typicals" must be provided in **onsemi** data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. **onsemi** does not convey any license under any of its intellectual property rights nor the rights of others. **onsemi** products are not designed, intended, or authorized for use as a critical component in life support systems. or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use onsemi products for any such unintended or unauthorized application, Buyer shall indemnify and hold onsemi and its officers, employees, subsidiaries, affiliates and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death Associated with such unintended or unauthorized use, even if such claim alleges that **onsemi** was negligent regarding the design or manufacture of the part. **onsemi** is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

#### PUBLICATION ORDERING INFORMATION

#### LITERATURE FULFILLMENT:

### Email Requests to: orderlit@onsemi.com

onsemi Website: www.onsemi.com

## **TECHNICAL SUPPORT**

North American Technical Support: Voice Mail: 1 800–282–9855 Toll Free USA/Canada Phone: 011 421 33 790 2910

Europe, Middle East and Africa Technical Support: Phone: 00421 33 790 2910 For additional information, please contact your local Sales Representative

# **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Switching Controllers category:

Click to view products by ON Semiconductor manufacturer:

Other Similar products are found below :

AZ7500EP-E1 NCP1218AD65R2G NCP1234AD100R2G NCP1244BD065R2G NCP1336ADR2G NCP6153MNTWG NCP81101BMNTXG NCP81205MNTXG SJE6600 SMBV1061LT1G SG3845DM NCP4204MNTXG NCP6132AMNR2G NCP81102MNTXG NCP81203MNTXG NCP81206MNTXG NX2155HCUPTR UBA2051C MAX8778ETJ+ NTBV30N20T4G NCP1240AD065R2G NCP1240FD065R2G NCP1361BABAYSNT1G NTC6600NF NCP1230P100G NCP1612BDR2G NX2124CSTR SG2845M NCP81101MNTXG TEA19362T/1J IFX81481ELV NCP81174NMNTXG NCP4308DMTTWG NCP4308DMNTWG NCP4308AMTTWG NCP1251FSN65T1G NCP1246BLD065R2G NTE7154 NTE7242 LTC7852IUFD-1#PBF LTC7852EUFD-1#PBF MB39A136PFT-G-BND-ERE1 NCP1256BSN100T1G LV5768V-A-TLM-E NCP1365BABCYDR2G NCP1365AABCYDR2G MCP1633T-E/MG NCV1397ADR2G NCP1246ALD065R2G AZ494AP-E1