# onsemi

# **110 V 2.5 A Single Channel Floating Gate Drivers with Desaturation Protection and Charge Pump**

# FAD3151MXA, FAD3171MXA

The FAD3151MXA and FAD3171MXA are single channel floating automotive gate drivers suitable for driving high-speed power MOSFETs up to 110 V. Designed in a SOI technology, the drivers are ideal for applications that require noise immunity against severe negative transients and ground offset up to -80 V.

The FAD3151MXA/71 drivers have an integrated desaturation detection to protect the power switches during short-circuit and over-current conditions. The drivers are also equipped with a soft shutdown feature, which initiates a soft shutdown of driver outputs upon desat detection, thus preventing possible overvoltage across power MOSFETs during a heavy-load condition.

The FAD3151MXA/71 drivers are equipped with bidirectional fault reporting pin that can generate a fault output during desat and under-voltage lockout (UVLO) condition. The bidirectional nature of the fault-reporting pin allows the driver to respond to external fault commands, thereby facilitating fault communication across the system. In addition, the FAD3171MXA has an integrated charge pump to support 100% duty cycle operation of high side MOSFETs.

In summary, the FAD3151MXA/71 are versatile drivers with features like desat detection, soft shutdown, fault reporting capability, UVLO protection, and charge pump.

# Features

- Single Channel Gate Driver with 110 V floating Vs capability

- Negative Transient Capability up to -80 V

- 2.5 A Output Source and Sink Current

- MOSFET Drain-Source Desaturation Detection with Soft Shutdown

- Integrated Charge Pump to support 100% Duty Cycle Operation (FAD3171MXA only)

- Under-voltage Lock Out for both Input Logic and Output Stage

- Bi-directional Fault Reporting Pin

- High Speed Driver with Short Propagation Delay

- $dV_s/dt$  Immune to min ±50 V/ns

- 3.3 V and 5 V Input Logic Compatible

- Up to V<sub>DD</sub> Swing on Input Pins

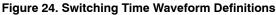

- SOIC-8 package

- Automotive Qualified to AEC Q100

- These Devices are Pb-Free and are RoHS Compliant

# **Typical Applications**

- Gate Driver for 80V and 100V MOSFETs

- 48 V Belt Starter Generator

- 48 V Auxiliary Motor Control (A/C compressor, e-turbo, ...)

- 48 V Battery Switches

- 48 V DC–DC converter

- PTC Heater, Active Discharge Circuit etc.

#### **ORDERING INFORMATION**

| Device     | Package             | Shipping <sup>†</sup> |

|------------|---------------------|-----------------------|

| FAD3151MXA | SOIC-8<br>(Pb-Free) | Tape & Reel           |

| FAD3171MXA | SOIC-8<br>(Pb-Free) | Tape & Reel           |

+For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

#### SAFETY SUPPORT

Support integration into customer's safety application with a set of safety documents including FMEDA and a hardware–software interface document.

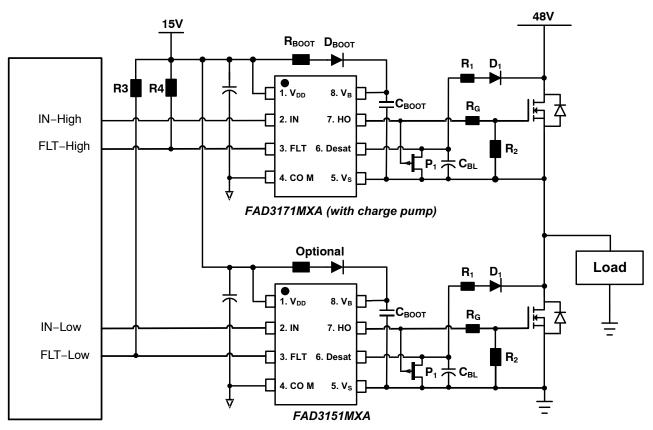

Figure 1. Application Schematic with FAD3171MXA as High Side and FAD3151MXA as Low Side drivers

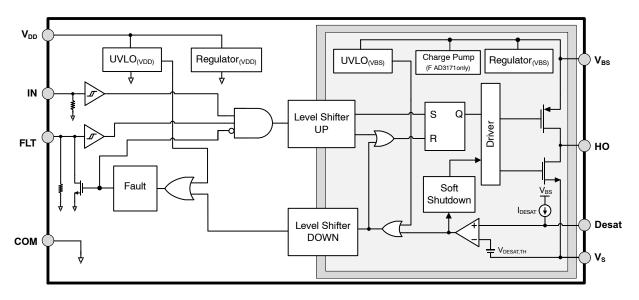

Figure 2. FAD3151MXA and FAD3171MXA (with charge pump) Block Diagram

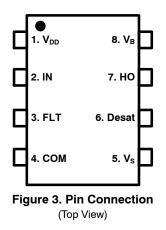

# **PIN FUNCTION DESCRIPTION**

### PIN FUNCTION DESCRIPTION

| Pin # | Pin Name        | Description                                |

|-------|-----------------|--------------------------------------------|

| 1     | V <sub>DD</sub> | Power supply for logic stage               |

| 2     | IN              | Input command                              |

| 3     | FLT             | Bi-directional fault pin                   |

| 4     | СОМ             | Ground for logic stage                     |

| 5     | V <sub>S</sub>  | Floating source connection                 |

| 6     | Desat           | Drain to source desaturation detection pin |

| 7     | НО              | Output                                     |

| 8     | V <sub>B</sub>  | Floating power supply for power stage      |

#### MAXIMUM RATINGS

$T_A = -40^{\circ}C \sim 125^{\circ}C$  unless otherwise noted. Voltage potentials are referenced to COM unless otherwise noted.

| Rating                                                                            | Symbol             | Value                                   | Unit |

|-----------------------------------------------------------------------------------|--------------------|-----------------------------------------|------|

| Logic Power Supply                                                                | V <sub>DD</sub>    | –0.3 to 20                              | V    |

| Logic Input Voltage (IN, FLT)                                                     | V <sub>IN</sub>    | –0.3 to (V <sub>DD</sub> + 0.3)         | V    |

| Floating Source Voltage                                                           | V <sub>S</sub>     | -115 to 115                             | V    |

| Floating Bootstrap Supply Voltage                                                 | V <sub>B</sub>     | $(V_{\rm S}-0.3)$ to $(V_{\rm S}$ + 20) | V    |

| Output Voltage                                                                    | V <sub>HO</sub>    | (Vs – 0.3) to (V <sub>B</sub> + 0.3)    | V    |

| Desaturation Voltage                                                              | V <sub>DESAT</sub> | (Vs – 0.3) to (V <sub>B</sub> + 0.3)    | V    |

| Allowable Offset Voltage Slew Rate                                                | dVs/dt             | +/-50                                   | V/ns |

| Maximum Junction Temperature                                                      | TJ                 | 150                                     | °C   |

| Thermal Resistance, Junction-to-Ambient (Note 1)                                  | Rth <sub>JA</sub>  | 200                                     | °C/W |

| Power Dissipation at T <sub>A</sub> = 25°C                                        | PD                 | 0.625                                   | W    |

| Storage Temperature Range                                                         | T <sub>STG</sub>   | -55 to 150                              | °C   |

| ESD Capability, Human Body Model (Note 2)                                         | ESD <sub>HBM</sub> | 2                                       | kV   |

| ESD Capability, Charged Device Model (Note 2)                                     | ESD <sub>CDM</sub> | 500 for all pins                        | V    |

|                                                                                   |                    | 750 for corner pins                     |      |

| Moisture Sensitivity Level                                                        | MSL                | 1                                       | -    |

| Lead Temperature Soldering<br>Reflow (SMD Styles Only), Pb-Free Versions (Note 3) | T <sub>SLD</sub>   | 260                                     | °C   |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

1. Refer to the following standards:

JESD51-2: Integral circuits thermal test method environmental conditions - natural convection

JESD51-3: Low effective thermal conductivity test board for leaded surface mount packages

2. This device series incorporates ESD protection and is tested by the following methods:

ESD Human Body Model tested per ANSI/ESDA/JEDEC JS-001-2012

ESD Charged Device Model tested per JESD22-C101

3. For information, please refer to our Soldering and Mounting Techniques Reference Manual, SOLDERRM/D

#### **RECOMMENDED OPERATING RANGES**

$T_A = -40^{\circ}C \sim 125^{\circ}C$  unless otherwise noted. Voltage potentials are referenced to COM unless otherwise noted.

| Rating                                      | Symbol          | Min                | Max | Unit |

|---------------------------------------------|-----------------|--------------------|-----|------|

| Power Supply                                | V <sub>DD</sub> | V <sub>DDUV+</sub> | 18  | V    |

| Logic Input Voltage (IN, FLT)               | V <sub>IN</sub> | 0                  | 18  | V    |

| High-Side Vs Floating Supply Offset Voltage | V <sub>S</sub>  | -80                | 110 | V    |

| High-side V <sub>BS</sub> Bootstrap Voltage | V <sub>BS</sub> | V <sub>BSUV+</sub> | 18  | V    |

Functional operation above the stresses listed in the Recommended Operating Ranges is not implied. Extended exposure to stresses beyond the Recommended Operating Ranges limits may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS**

$V_{BIAS}$  ( $V_{DD}$ ,  $V_{BS}$ ) = 15 V,  $V_S$  = 0 V unless otherwise noted,  $T_A$  = -40°C to 125°C. Voltage potentials are referenced to COM unless otherwise noted.

| Parameter                                              | Test Conditions                                                                  | Symbol              | Min | Тур  | Max  | Unit |

|--------------------------------------------------------|----------------------------------------------------------------------------------|---------------------|-----|------|------|------|

| POWER SUPPLY SECTION                                   | •                                                                                |                     |     |      |      |      |

| V <sub>BS</sub> Under-Voltage Positive-going Threshold |                                                                                  | V <sub>BSUV+</sub>  | 6   | 8    | 10.5 | V    |

| V <sub>BS</sub> Under-Voltage Negative-going Threshold |                                                                                  | V <sub>BSUV-</sub>  | 5.5 | 7.5  | 9.7  | 1    |

| V <sub>BS</sub> Slew Rate During Startup (Note 4)      |                                                                                  | V <sub>BS(SR)</sub> | 2.5 |      |      | V/ms |

| V <sub>DD</sub> Under-Voltage Positive-going Threshold |                                                                                  | V <sub>DDUV+</sub>  |     |      | 6    | V    |

| V <sub>DD</sub> Under-Voltage Negative-going Threshold |                                                                                  | V <sub>DDUV-</sub>  | 2.2 | 3.9  |      | 1    |

| Offset Supply Leakage Current                          | V <sub>B</sub> = V <sub>S</sub> = 80 V                                           | I <sub>LK1</sub>    |     |      | 5    | μΑ   |

| Quiescent V <sub>DD</sub> Supply Current               | V <sub>IN</sub> = 0 V or 5 V                                                     | I <sub>QDD</sub>    |     | 270  | 500  | μΑ   |

| Quiescent V <sub>BS</sub> Supply Current               | V <sub>IN</sub> = 0 V or 5 V                                                     | I <sub>QBS</sub>    |     | 525  | 1000 | 1    |

| Operating V <sub>DD</sub> Supply Current               | V <sub>IN</sub> = 0 V or 5 V;<br>f <sub>SW</sub> = 20 kHz; C <sub>L</sub> = 1 nF | I <sub>PDD</sub>    |     | 250  | 600  |      |

| Operating V <sub>BS</sub> Supply Current               | V <sub>IN</sub> = 0 V or 5 V;<br>f <sub>SW</sub> = 20 kHz; C <sub>L</sub> = 1 nF | I <sub>PBS</sub>    |     | 1000 | 2000 | 1    |

4. This limitation applies only to temperatures exceeding 105°C.

### LOGIC INPUT SECTION

| Logic "1" Input threshold for IN, FLT |                       | V <sub>IH</sub>  |     | 2.1 | 2.5 | V  |

|---------------------------------------|-----------------------|------------------|-----|-----|-----|----|

| Logic "0" Input threshold for IN, FLT |                       | V <sub>IL</sub>  | 1.3 | 1.7 |     |    |

| Logic Input High Bias Current         | V <sub>IN</sub> = 5 V | I <sub>IN+</sub> |     | 48  | 70  | μΑ |

| Logic Input Low Bias Current          | V <sub>IN</sub> = 0 V | I <sub>IN-</sub> |     |     | 2   | μΑ |

| Input Pull-down Resistance            |                       | R <sub>IN</sub>  |     | 80  |     | kΩ |

## FAULT SECTION

| Fault Output Internally pulled down voltage level     | 10 k $\Omega$ pull up resistor to<br>V <sub>DD</sub> , V <sub>DESAT</sub> > V <sub>DESAT+</sub> | V <sub>FLT+</sub>     |     |      | 200 | mV |

|-------------------------------------------------------|-------------------------------------------------------------------------------------------------|-----------------------|-----|------|-----|----|

| Fault Output Not Internally pulled down voltage level | 10 kΩ pull up resistor to<br>V <sub>DD</sub> , V <sub>DESAT</sub> < V <sub>DESAT+</sub>         | V <sub>FLT-</sub>     |     | 13.8 |     | V  |

| Fault Pin Pull-down Resistance                        |                                                                                                 | R <sub>FLT</sub>      |     | 110  |     | kΩ |

| Desaturation High detection threshold (Note 5)        |                                                                                                 | V <sub>DESAT,TH</sub> | 2.3 | 3.0  | 4   | V  |

| Desaturation Bias Current                             |                                                                                                 | IDESAT                | 180 | 320  | 430 | μA |

5. The actual desaturation threshold at the Power MOSFET can be adjusted to a value lower than V<sub>DESAT,TH</sub> with an external resistor (see Application Note)

#### GATE DRIVER OUTPUT SECTION

| High-Level Output Voltage (V <sub>B</sub> - V <sub>HO</sub> )                          | V <sub>IN</sub> = 5 V, No Load                                  | V <sub>HOH</sub> |     |     | 50 | mV |

|----------------------------------------------------------------------------------------|-----------------------------------------------------------------|------------------|-----|-----|----|----|

| Low-Level Output Voltage (V <sub>HO</sub> -V <sub>S</sub> )                            | V <sub>IN</sub> = 0 V, No Load                                  | V <sub>HOL</sub> |     |     | 50 | mV |

| Source Peak Pulsed Current (Note 6)                                                    | $V_{IN}$ = 5 V, $V_{HO}$ = 0 V,<br>Pulse Width ≤10 µs           | I <sub>O+</sub>  |     | 2.5 |    | A  |

| Sink Peak Pulsed Current (Note 6)                                                      | V <sub>HO</sub> = V <sub>BS</sub> = 15 V,<br>Pulse Width ≤10 μs | I <sub>O-</sub>  |     | 2.5 |    |    |

| Allowable Negative $V_S$ pin voltage, with signal Propagation Capability from IN to HO |                                                                 | V <sub>S</sub>   | -80 |     |    | V  |

| Driver Output Pull-up Resistance                                                       | I <sub>OUT</sub> = 90 mA (DC)                                   | R <sub>OH</sub>  |     | 3   |    | Ω  |

| Driver Output Pull-down Resistance                                                     | I <sub>OUT</sub> = 90 mA (DC)                                   | R <sub>OL</sub>  |     | 1.2 |    | Ω  |

6. Guaranteed by design

#### **ELECTRICAL CHARACTERISTICS**

$V_{BIAS}$  ( $V_{DD}$ ,  $V_{BS}$ ) = 15 V,  $V_S$  = 0 V unless otherwise noted,  $T_A$  = -40°C to 125°C. Voltage potentials are referenced to COM unless otherwise noted.

| Parameter                                              | Test Conditions                                                                                                               | Symbol                   | Min | Тур  | Max  | Unit |

|--------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|--------------------------|-----|------|------|------|

| CHARGE PUMP SECTION [FAD3171MXA only]                  |                                                                                                                               |                          |     |      |      |      |

| Turn on threshold level, referenced to $V_{BS}$        | $V_{DD} > V_{DDUV+,} R_L = 100 \text{ k}\Omega, \\ V_S = 48 \text{ V}$                                                        | CP <sub>ON</sub>         | 7.9 | 10.8 | 15.2 | V    |

| Turn off threshold level, referenced to $V_{BS}$       |                                                                                                                               | CP <sub>OFF</sub>        | 8.3 | 11.2 | 15   | V    |

| Charge Pump V <sub>BS</sub> hysteresis                 |                                                                                                                               | CP <sub>HYS</sub>        |     | 0.4  |      | V    |

| Delta (CP <sub>ON</sub> – V <sub>BSUV</sub> ) (Note 7) | $\label{eq:VDD} \begin{split} V_{DD} > V_{DDUV+,} \; R_L \text{=} 100 \; \text{k}\Omega, \\ V_S = 48 \; \text{V} \end{split}$ | $\Delta_{\rm CP,VBSUV-}$ | 1   |      |      | V    |

| Charge Pump Supply Voltage                             |                                                                                                                               | V <sub>S,CP</sub>        | 24  |      |      | V    |

| Charge Pump Output Current capability (Note 8)         | $V_{BS} = CP_{ON}, V_S > V_{S,CP}$                                                                                            | I <sub>CP,OUT</sub>      |     |      | 150  | μΑ   |

| Charge Pump Oscillation Frequency (Note 6)             |                                                                                                                               | CP <sub>fs</sub>         |     |      | 5.5  | MHz  |

7. Difference between the charge-pump turn on threshold and  $V_{BS}$  under-voltage negative-going threshold. 8. Net output current, excluding the internal current consumption of the gate driver in steady state.

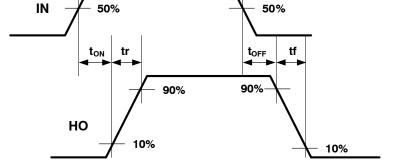

#### DYNAMIC SECTION

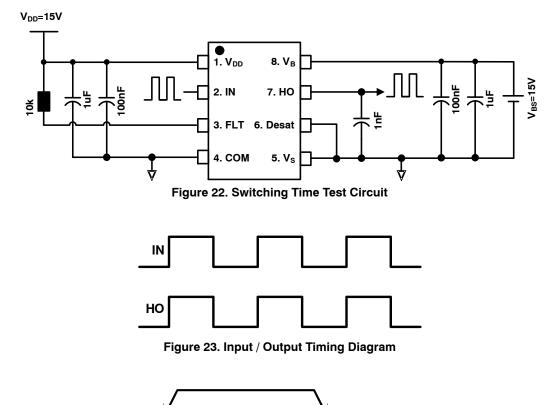

| Input pulse filtering time (Note 9)                         |                                                                                                                                                                                        | T <sub>IN_FILT</sub>                     |     | 40  |     | ns |

|-------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|-----|-----|-----|----|

| Turn-On Propagation Delay                                   | V <sub>S</sub> = 0 V, C <sub>L</sub> = 1000 pF                                                                                                                                         | t <sub>ON</sub>                          |     | 50  | 100 | ns |

| Turn-Off Propagation Delay                                  | V <sub>S</sub> = 0 V, C <sub>L</sub> = 1000 pF                                                                                                                                         | t <sub>OFF</sub>                         |     | 50  | 100 | ns |

| Turn-On Rise Time                                           | Vs = 0 V, C <sub>L</sub> = 1000 pF                                                                                                                                                     | t <sub>R</sub>                           |     | 15  | 25  | ns |

| Turn-Off Fall Time                                          |                                                                                                                                                                                        | t <sub>F</sub>                           |     | 10  | 20  | ns |

| $V_{DD}$ and $V_{BS}$ Under-Voltage filtering time (Note 6) | $V_{DD}$ < $V_{DDUV_{-}}$ or $V_{BS}$ < $V_{BSUV_{-}}$ to $V_{HO}$ falls by 10%                                                                                                        | t <sub>VDDUV</sub><br>t <sub>VBSUV</sub> |     | 10  |     | μs |

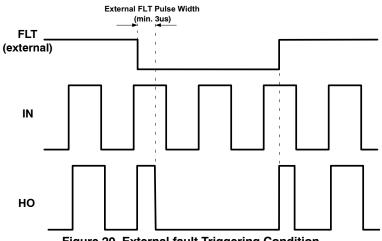

| External FLT Pulse Width (Note 10)                          | V <sub>FLT</sub> < V <sub>IL</sub> to V <sub>HO</sub> falls by<br>10%                                                                                                                  | tFLT_Pulse                               | 3   |     |     | μs |

| Desat detection to HO propagation delay                     | $\label{eq:VDESAT} \begin{array}{l} V_{DESAT} > V_{DESAT+} \mbox{ to } V_{HO} \\ \mbox{falls by 10\% with } R_L \mbox{= } 0 \ \Omega \\ \mbox{ and } C_L \mbox{= } 1 \ nF \end{array}$ | T <sub>DESAT_HO</sub>                    |     | 75  | 110 | ns |

| Desat detection to FLT propagation delay                    | $V_{DESAT} > V_{DESAT,TH}$ to $V_{FLT}$<br>< $V_{FLT-}$                                                                                                                                | T <sub>DESAT_FLT</sub>                   |     | 80  | 110 | ns |

| FLT Locking Duration                                        | Desaturation or UVLO<br>detected                                                                                                                                                       | <sup>t</sup> FLT_LO                      | 150 | 550 |     | μs |

| Soft shutdown resistance                                    |                                                                                                                                                                                        | R <sub>SOFT</sub>                        |     | 170 |     | Ω  |

Shorter input pulses are filtered out and do not cause the output to change state.

The pulse width of the external fault signal at which the driver output turns off.

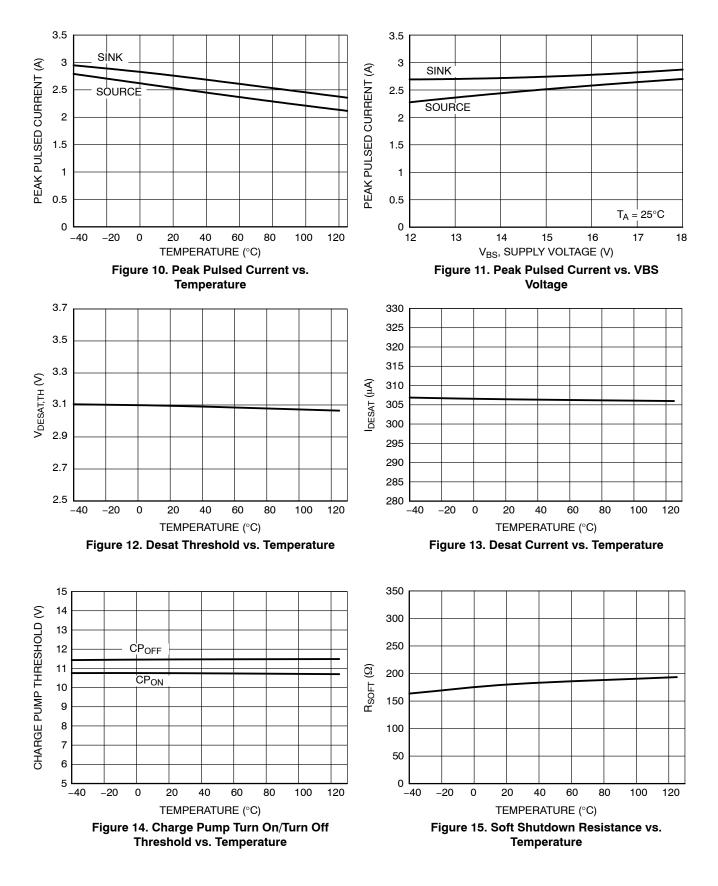

# **TYPICAL CHARACTERISTICS**

# **TYPICAL CHARACTERISTICS**

# GATE DRIVER DESCRIPTION

Figure 2 shows the block diagram of the FAD3151MXA and FAD3171MXA (with charge pump). The section below describes the functional characteristics of 3151/71 gate drivers.

### Input and Fault Signal Buffer

The driver includes input and fault signal buffers to avoid parasitic triggering due to noises at input and fault pins. The input pin has a 40 ns filter, which means the driver output will not change its state for an input pulse shorter than 40 ns. Similarly, the fault pin has a 3  $\mu$ s filter, which means the driver output will not change its state for an external fault pulse shorter than 3  $\mu$ s.

# VDD and VBS Under Voltage Lock Out

The gate driver has UVLO monitoring circuits with a 10  $\mu s$  filter for both  $V_{DD}$  and  $V_{BS}$  power supplies. If the  $V_{DD}$  or  $V_{BS}$  voltages were to drop below their respective UVLO threshold:

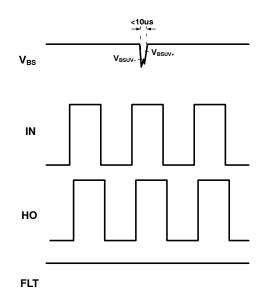

• Within the first 10 µs of an under-voltage condition (see Figure 16):

- The gate driver does not take any action and the output follows the input as expected.

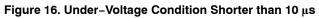

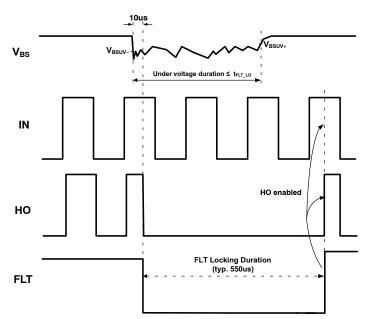

- After 10 µs of under-voltage condition, the UVLO circuit triggers a fault for a period equal to FLT locking duration:

- If the under-voltage condition lasts for a duration shorter than the FLT locking duration, the fault pin is released after the FLT locking duration is over, upon which the driver output will begin to follow the input logic as expected (see Figure 17).

- If the under-voltage condition lasts for a duration longer than the FLT locking duration, the fault pin is released only after the under-voltage condition has disappeared. The driver output will begin to follow the input logic once the fault pin is released (see Figure 18).

The figures below show examples of driver functionality during various under-voltage conditions of the  $V_{BS}$  supply; note that the same description applies for an under-voltage condition of the  $V_{DD}$  supply.

Figure 17. Under-Voltage Condition Shorter than FLT Locking Duration

Figure 18. Under-Voltage Condition Longer than FLT Locking Duration

#### **Desaturation Protection with Soft Shutdown**

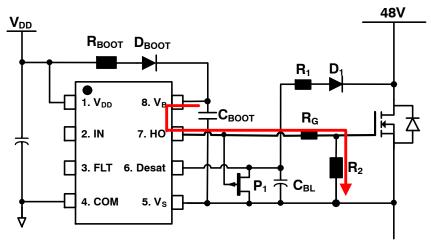

The gate driver has a desaturation detection circuit that monitors the drain to source  $V_{DS}$  voltage of the power MOSFET through the desaturation detection pin. As shown in the simplified block diagram in Figure 2, the desaturation circuit comprises of:

- An internal current source that provides a continuous current toward the power stage to monitor the  $V_{DS}$  voltage. The desat current source ( $I_{DESAT}$ ) is supplied from the  $V_B$  pin and is continuously active as soon as the  $V_{DD}$  is higher than the UVLO<sub>VDD+</sub>, independent of the status of the input logic.

- An internal comparator that compares the voltage at the desat pin (V<sub>DESAT</sub>) with the defined desat threshold (V<sub>DESAT,TH</sub>) of 3 V (typ.). When V<sub>DESAT</sub> exceeds V<sub>DESAT,TH</sub>, the comparator simultaneously turns off the output 'slowly' and triggers a fault condition by pulling down the fault pin internally.

As shown in application schematic in Figure 1, the desat diode  $D_1$ , resistor  $R_1$ , blanking capacitor  $C_{BL}$ , and P-channel JFET  $P_1$  are the minimum external components required to operate the desaturation protection scheme. The driver needs an external pull down transistor  $P_1$  to discharge I<sub>DESAT</sub> and C<sub>BL</sub> as soon as the driver output turns off.

Otherwise, the blanking capacitor will continue to charge up and eventually trigger desat. The presence of a normally on P1 also enhances noise immunity of desat blanking capacitor against false triggering during the turn on event of complementary power switch. The external desat components can be modified to adjust the blanking time and the desat detection threshold for a given application. It is recommended to refer to the Application Note for more details.

If the power switch is turned–off rapidly during a heavy–load condition, the high currents may generate a voltage overshoot across the power switch that could potentially damage it. In order to protect the devices, the driver has a soft shutdown feature, which activates upon desat detection. The output is then driven low through a large turn–off resistance (R<sub>SOFT</sub>) which provides a significantly higher resistive path for the gate capacitance to discharge than during the regular turn–off process. As a result, the possibility of an abrupt overvoltage spike on the power switches is reduced.

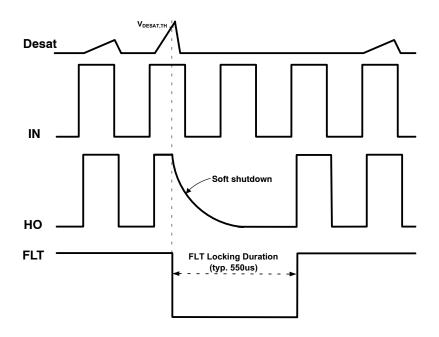

When the voltage at the desaturation pin exceeds the defined desat threshold, following protection sequence is performed:

- The gate driver initiates a soft shutdown. The driver will provide a high resistive path through R<sub>SOFT</sub> for gate capacitance to discharge slowly [see Figure 19]. The fall rate of HO is determined by the time constant of the RC discharge path.

- The driver also triggers an internal fault and pulls down the fault pin for the period equivalent to Fault Locking duration (typ. 550 µs).

- NOTE: If the desat condition persists even after the fault locking duration, and if the input signal is still provided, the driver output will reappear for a period equivalent to the blanking time, after which the desat protection will retrigger the soft shutdown and turn off the output again.

Figure 19. Desaturation Protection and Soft Shutdown

#### **External Fault Triggerring**

The FLT pin is bi-directional in nature and is in a pulled-up state for normal operation. The gate driver pulls down the FLT pin internally during desat and under-voltage lockout condition. As shown in Figure 20, if the FLT pin is externally pulled down to a logic low for a period longer than the external FLT pulse width (min.  $3 \mu$ s), the driver turns off. It is important to note that the FLT locking duration is not valid for external fault trigger condition. As a result, the output is reactivated as soon as the FLT pin is released (set

to logic 1). In this case, the FLT pin performs similar to an enable pin. The external fault triggering capability allows the interconnection of fault pins of multiple gate drivers on both high side and low side driver stages. For example, in a multi-phase inverter system, the fault pins of all high-side drivers (or low-side drivers) could be tied together and controlled with an external controller to achieve Active short-circuit (ASC) protection. It is recommended to refer to the Application Note for more details.

#### Figure 20. External fault Triggering Condition

#### Charge Pump for 100% Duty Cycle Operation

The FAD3171MXA driver contains an internal charge pump that enables 100% duty-cycle operation of high-side power switches. When the high-side switch is kept on for a long duration, the bootstrap capacitor could slowly discharge and may eventually trigger the under-voltage lockout protection and turn off the driver output. Therefore, the purpose of the charge pump is to supply the  $V_{BS}$  quiescent current necessary for the high-side gate driver to operate under 100% duty cycle and to compensate for additional leakage current on the gate path.

It should be ensured that the total leakage current in the gate path does not exceed the maximum output current capability of the charge pump  $I_{CP,OUT}$ . For example, in Figure 21, when the gate is continuously high, the pull-down resistance  $R_2$  will continuously sink a current and for this reason, its value should be high enough to minimize the total leakage current drawn from the charge pump. Considering a maximum output current of 150  $\mu$ A at  $V_{BS} = CP_{ON} = 15$  V, the value of  $R_2$  should be higher than 100 k $\Omega$  to maintain a steady charge pump output.

Figure 21. Leakage Current in the Gate Path

It is important to note that the charge pump is not intended to provide gate charge during switching of power MOSFET; rather its purpose is to only keep the MOSFET turned on. For this, it should be ensured at the system level that the high–side MOSFET is not operated at very high duty cycle or, if a high duty cycle operation is required, the off time should be long enough to allow the bootstrap capacitor on high–side gate driver to completely recharge.

In order to minimize continuous power dissipation, the charge pump turns on only when needed, and remains off at other times. The necessary conditions for the charge pump in FAD3171MXA to activate are:

- The V<sub>DD</sub> voltage is higher than the V<sub>DD</sub> under voltage positive-going threshold (V<sub>DDUV+</sub>)

- The V<sub>S</sub> voltage is higher than V<sub>S,CP</sub> (24 V min.); below this voltage, the efficiency of the charge pump is reduced.

- The V<sub>BS</sub> voltage decreases below the charge pump turn on threshold (CP<sub>ON</sub>).

The charge pump deactivates as soon as:

- The V<sub>BS</sub> voltage rises back to a value higher the charge pump turn off threshold (CP<sub>OFF</sub>).

- The V<sub>DD</sub> is lower than the V<sub>DD</sub> under voltage negative–going threshold (V<sub>DDUV–</sub>).

In order to ensure that the charge pump and the UVLO function do not interfere with each other, the charge pump

#### **Switching Time Definitions**

turn–on threshold (CP<sub>ON</sub>) is designed to be higher than the V<sub>BSUV</sub>– threshold. As a result, the driver output is higher than the V<sub>BSUV</sub>– threshold during charge pump mode. If the load on the charge pump exceeds I<sub>CP,OUT</sub>, the voltage across the V<sub>B</sub>–V<sub>S</sub> pins will slowly decrease and eventually trigger the under–voltage lockout protection and turn off the driver output.

# PACKAGE DIMENSIONS

onsemi, ONSEMI, and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi's product/patent coverage may be accessed at <u>www.onsemi.com/site/pdf/Patent-Marking.pdf</u>. onsemi reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product features, availability, functionality, or suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using onsemi products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by onsemi. "Typical" parameters, including "Typicals" must be validated for each customer applications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. onsemi does not convey any license under any of its intellectual property rights or the rights of others. onsemi products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use onsemi products for any s

#### ADDITIONAL INFORMATION

TECHNICAL PUBLICATIONS: Technical Library: www.onsemi.com/design/resources/technical-documentation onsemi Website: www.onsemi.com ONLINE SUPPORT: www.onsemi.com/support For additional information, please contact your local Sales Representative at www.onsemi.com/suport/sales

# **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Gate Drivers category:

Click to view products by ON Semiconductor manufacturer:

Other Similar products are found below :

56956 57.404.7355.5 LT4936 57.904.0755.0 0131700000 LTP70N06 LVP640 5J0-1000LG-SIL LY2-US-AC240 LY3-UA-DC24 LZNQ2-US-DC12 LZP40N10 60100564 60249-1-CUT-TAPE 0134220000 6035 60713816 61161-90 6131-204-23149P 6131-205-17149P 6131-209-15149P 6131-218-17149P 6131-220-21149P 6131-260-2358P 6131-265-11149P CS1HCPU63 6150-5001 CSB4 CSK-38-60006 CSK-38-60008 621A 622-4053LF 6273 M40N08MA-H M55155/29XH06 64-807 65-1930-6 CV500ISB02 M83723/88Y1407N CWD012-2 CWD03-3 CX3225SB16934D0PPSC2 CX5032GB10000D0PPS02 687-772NF1 70.140.1653 70.200.0653.0 703001B01F060 70-3601 706006D02F0601 706210