## Is Now Part of

# ON Semiconductor®

# To learn more about ON Semiconductor, please visit our website at www.onsemi.com

Please note: As part of the Fairchild Semiconductor integration, some of the Fairchild orderable part numbers will need to change in order to meet ON Semiconductor's system requirements. Since the ON Semiconductor product management systems do not have the ability to manage part nomenclature that utilizes an underscore (\_), the underscore (\_) in the Fairchild part numbers will be changed to a dash (-). This document may contain device numbers with an underscore (\_). Please check the ON Semiconductor website to verify the updated device numbers. The most current and up-to-date ordering information can be found at <a href="www.onsemi.com">www.onsemi.com</a>. Please email any questions regarding the system integration to Fairchild <a href="general-regarding-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-n

ON Semiconductor and the ON Semiconductor logo are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON Semiconductor products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by ON Semiconductor. "Typical" parameters which may be provided in ON Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights nor the rights of others. ON Semiconductor products are not designed, intended, or authorized for use as a critical component in life support systems or any EDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold ON Semiconductor and its officer

# FAN6240 Secondary-Side Synchronous Rectifier Controller for Flyback Converters

### **Features**

- Works in Discontinuous Conduction Mode (DCM).

- Adaptive Turn-off Trigger Blanking Time for easier use

- Turn-on Trigger Blanking Time (Minimum-OFF Time) for Improved Noise Immunity

- Supports High-Frequency Applications up to 200 kHz

- Minimum Turn-on Delay (20 ns)

- Adaptive Turn-off Threshold Control for Minimized SR MOSFET Body Diode Conduction (Dead-Time is independent of SR MOSFET)

- Wide Voltage Range for LDO Input up to 30 V

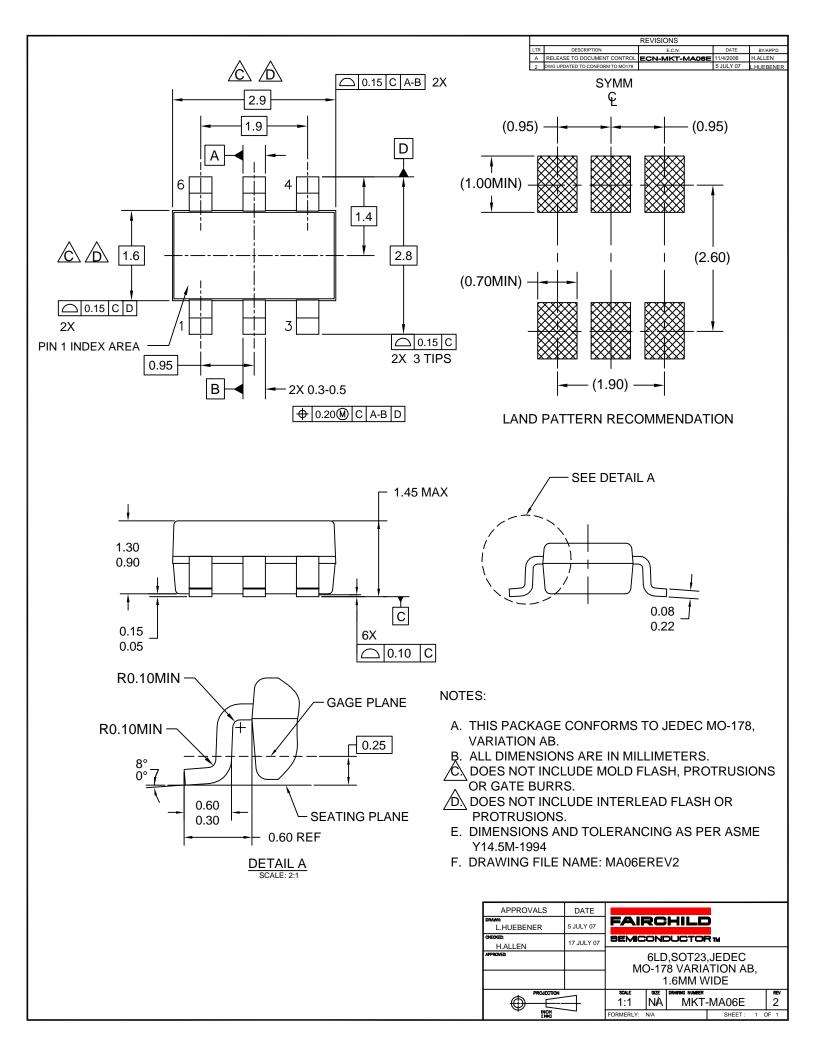

- Small Footprint: SOT-23 6 Pin Package

# **Description**

The FAN6240M6X is a secondary-side synchronous rectifier (SR) controller for an isolated flyback converter operating in Discontinuous Conduction Mode (DCM). The adaptive dead-time control algorithm minimizes the body diode conduction of SR MOSFET while guaranteeing stable and robust SR operation against noise and disturbance caused by the circuit parasitic. 30 V rated input voltage LDO and Low VDD Under-Voltage Lockout (UVLO) voltage allow FAN6240M6X to be used for wide ranges of switched mode power supply output voltage without additional circuit.

# **Applications**

- Battery Chargers for Smart Phones, Feature Phones, and Tablet PCs

- AC-DC Adapters for Portable Devices that Require CV/CC Control

### Ordering Information

| Part Number | Operating<br>Temperature Range | Package                                               | Packing<br>Method |

|-------------|--------------------------------|-------------------------------------------------------|-------------------|

| FAN6240M6X  | -40°C to +125°C                | 6-Lead, SOT23, JEDEC MO-178 Variation AB, 1.6 mm Wide | Tape & Reel       |

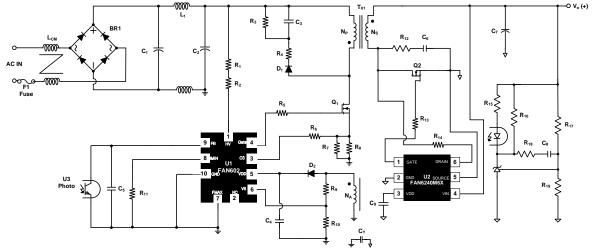

# **Application Diagram**

Figure 1. Typical Application

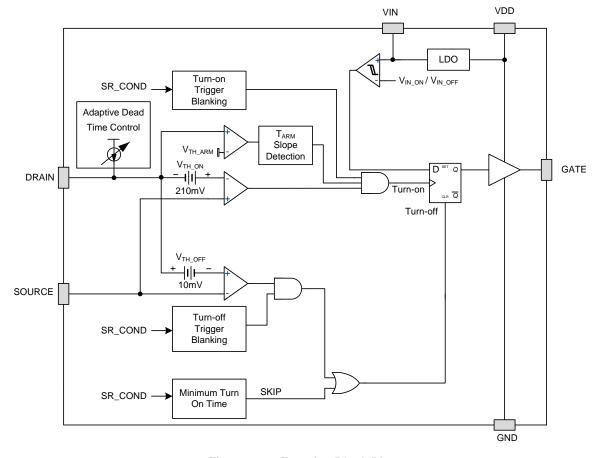

# **Internal Block Diagram**

Figure 2. Function Block Diagram

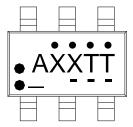

# **Marking Information**

Figure 3. Top Mark

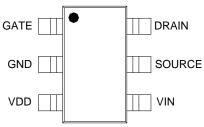

# **Pin Configuration**

Figure 4. Pin Configuration

# **Pin Definitions**

| Pin#                                                                                                                                | Name   | Description                                                                                                                                         |

|-------------------------------------------------------------------------------------------------------------------------------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                                                                                                                                   | GATE   | Gate drive output                                                                                                                                   |

| 2                                                                                                                                   | GND    | Ground                                                                                                                                              |

| 3                                                                                                                                   | VDD    | Internal regulator 5 V output and gate drive power supply rail. Bypass with 1uF capacitor to GND.                                                   |

| 4 VIN LDO input, supports up to 30 V operation. An integrated 5 V LDO gene power supply rail for the low-voltage control circuitry. |        | LDO input, supports up to 30 V operation. An integrated 5 V LDO generates the internal VDD power supply rail for the low-voltage control circuitry. |

| 5                                                                                                                                   | SOURCE | Synchronous rectifier source sense input.                                                                                                           |

| 6                                                                                                                                   | DRAIN  | Synchronous rectifier drain sense input.                                                                                                            |

# **Absolute Maximum Ratings**

Stresses exceeding the absolute maximum ratings may damage the device. The device may not function or be operable above the recommended operating conditions and stressing the parts to these levels is not recommended. In addition, extended exposure to stresses above the recommended operating conditions may affect device reliability. The absolute maximum ratings are stress ratings only.

| Symbol              | Parameter                                        |                                                      | Min. | Max. | Unit |

|---------------------|--------------------------------------------------|------------------------------------------------------|------|------|------|

| V <sub>IN</sub>     | Power Supply Input Pin Voltage                   |                                                      |      | 30   | V    |

| $V_{DD}$            | Internal Regulator Output Pin Voltage            |                                                      |      | 6.5  | V    |

| V <sub>DRAIN</sub>  | Drain Sense Input Pin Voltage                    |                                                      | -1   | 100  | V    |

| V <sub>GATE</sub>   | GATE Gate Drive Output Pin Voltage               |                                                      |      | 6.5  | V    |

| V <sub>SOURCE</sub> | Source Sense Input Pin Voltage                   |                                                      | -1   | 1    | V    |

| P <sub>D</sub>      | Power Dissipation (T <sub>A</sub> =25°C)         |                                                      |      | 23   | mW   |

| ΘJA                 | Thermal Resistance (Junction-to-Ambient Thermal) |                                                      |      | 235  | °C/W |

| TJ                  | Operating Junction Temperature                   |                                                      | -40  | 150  | °C   |

| T <sub>STG</sub>    | Storage Temperature Range                        |                                                      | -60  | 150  | °C   |

| TL                  | Lead Temperature (Soldering) 10 Seconds          |                                                      |      | 260  | °C   |

| ESD                 | SD Electrostatic Discharge Capability            | Human Body Model, ANSI / ESDA /<br>JEDEC JS-001-2012 |      | 2.5  | kV   |

|                     |                                                  | Charged Device Model, JESD22-C101                    |      | 1.5  |      |

#### Notes:

- 1. Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device.

- 2. All voltage values are with respect to the GND pin.

# **Recommended Operating Conditions**

The Recommended Operating Conditions table defines the conditions for actual device operation. Recommended operating conditions are specified to ensure optimal performance. Fairchild does not recommend exceeding them or designing to Absolute Maximum Ratings.

| Symbol              | Parameter                             | Min. | Тур. | Max. | Unit |

|---------------------|---------------------------------------|------|------|------|------|

| V <sub>IN</sub>     | Power Supply Input Pin Voltage        | 2.8  |      | 20   | V    |

| $V_{DD}$            | Internal Regulator Output Pin Voltage | 2.8  |      | 6    | V    |

| $V_{DRAIN}$         | Drain Sense Input Pin Voltage         | -0.3 |      | 100  | V    |

| $V_{GATE}$          | Gate Drive Output Pin Voltage         | -0.3 |      | 6    | V    |

| V <sub>SOURCE</sub> | Source Sense Input Pin Voltage        | -0.3 |      | 1    | V    |

# **Electrical Characteristics**

$V_{IN}$  = 12 V and  $T_J$  = -40°C to 125°C unless otherwise specified.

| Symbol                              | Parameter                                  | Conditions                                                                  | Min. | Тур. | Max. | Unit |

|-------------------------------------|--------------------------------------------|-----------------------------------------------------------------------------|------|------|------|------|

| Input Voltage                       | 9                                          |                                                                             | 1    |      |      |      |

| V <sub>IN_ON</sub>                  | Turn-On Threshold                          | V <sub>IN</sub> Rising                                                      | 3.1  | 3.4  | 3.7  | V    |

| V <sub>IN_OFF</sub>                 | Turn-Off Threshold                         | V <sub>IN</sub> Falling                                                     | 2.8  | 2.9  | 3.0  | V    |

| I <sub>IN_OP</sub>                  | Operating Current                          | $f_{SW}$ = 100 kHz, $C_{GATE}$ = 3.3 nF, $V_{IN}$ = 5 V                     |      | 2    | 3.5  | mA   |

| Power Suppl                         | y Section                                  |                                                                             |      |      |      |      |

| V <sub>DD</sub>                     | Internal LDO Output Voltage                | V <sub>IN</sub> = 20 V                                                      | 5.00 | 5.25 | 5.50 | V    |

| Drain Voltage                       | e Sensing Section                          |                                                                             |      |      |      |      |

| I <sub>OFFSET</sub>                 |                                            | Maximum of adaptive offset current (15 steps, 6 μA resolution)              | 75   | 90   | 105  | μΑ   |

| V <sub>TH_ON</sub>                  | Turn-On Threshold                          | $R_{DRAIN} = 0 \Omega$ (includes comparator input offset voltage)           | -235 | -210 | -185 | mV   |

| T <sub>ON.DLY</sub> <sup>(3)</sup>  | Turn-On Delay                              |                                                                             |      | 20   |      | ns   |

| V <sub>TH_OFF</sub> <sup>(3)</sup>  | Turn-Off Threshold                         |                                                                             |      | 10   |      | mV   |

| T <sub>OFF.DLY</sub> <sup>(3)</sup> | Turn-Off Delay                             |                                                                             |      | 20   |      | ns   |

| V <sub>TH_ARM</sub>                 | Gate Re-arming Threshold                   | V <sub>IN</sub> = 5 V, (Typically 0.7*V <sub>DD</sub> )                     | 3.3  | 3.5  | 3.7  | V    |

| T <sub>ARM</sub> <sup>(3)</sup>     | Gate Re-arming Time for Slope<br>Detection |                                                                             |      | 85   |      | ns   |

| V <sub>TH_HGH</sub> <sup>(3)</sup>  | SR OFF Detection Threshold                 |                                                                             |      | 0.5  |      | V    |

|                                     | -Time and Minimum Off-Time                 |                                                                             |      |      |      |      |

| K <sub>TON</sub> <sup>(3)</sup>     | Adaptive Minimum On-Time Ratio             | Ratio between minimum on time and SR conduction of previous switching cycle |      | 50   |      | %    |

| t <sub>ON_MIN.LL</sub>              | Minimum On-Time Lower Limit                |                                                                             | 300  | 400  | 500  | ns   |

| t <sub>ON_MIN.UL</sub> (3)          | Minimum On-Time Upper Limit                |                                                                             |      | 2    |      | μs   |

| t <sub>OFF_MIN</sub>                | Minimum Off-Time                           | Default Option for Medium<br>Frequency                                      | 1.0  | 1.2  | 1.4  | μs   |

| <b>Output Drive</b>                 | r Section                                  |                                                                             |      |      |      |      |

| V <sub>OL</sub>                     | Output Voltage Low                         | V <sub>IN</sub> = 6 V                                                       |      |      | 0.25 | V    |

| V <sub>OH</sub>                     | Output Voltage High                        | V <sub>IN</sub> = 6 V                                                       | 5.0  |      |      | V    |

| t <sub>R</sub>                      | Rise Time                                  | V <sub>IN</sub> = 6 V, C <sub>L</sub> =3300 pF,<br>GATE = 1 V~4 V           |      |      | 10   | ns   |

| t <sub>F</sub>                      | Fall Time                                  | V <sub>IN</sub> =6 V, C <sub>L</sub> = 3300 pF,<br>GATE = 4 V~1 V           |      |      | 10   | ns   |

| Adaptive Dea                        | ad-Time Control                            |                                                                             |      |      | •    |      |

| t <sub>DEAD</sub> (3)               | Dead-Time Self-Tuning Target               | From GATE OFF to V <sub>DRAIN</sub> rising above V <sub>TH_HGH</sub>        |      | 290  |      | ns   |

### Note:

3. Not tested and guaranteed by design.

# **Functional Description**

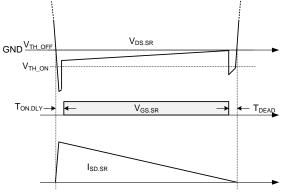

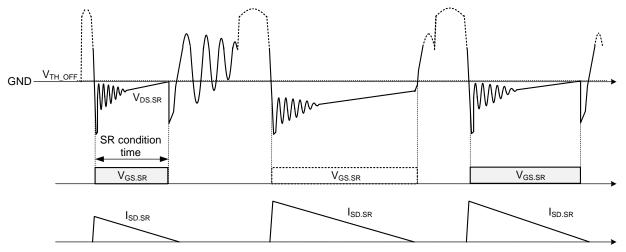

## **Theory of SR Control Operation**

For an ideal circuit operation, the SR control algorithm of FAN6240 is very straightforward. FAN6240 controls the SR MOSFET based on the instantaneous drain-to-source voltage as illustrated in Figure 5. When the body diode starts conducting, the drain-to-source voltage drops below the turn-on threshold (V<sub>TH\_ON</sub>) which triggers the turn-on of the gate. Then the drain-to-source voltage is determined by the product of R<sub>DSON</sub> and instantaneous SR current. When the drain-to-source voltage reaches the turn-off threshold (V<sub>TH\_OFF</sub>) as SR MOSFET current decreases to near zero, FAN6240 turns off the gate. If the turn off threshold (V<sub>TH\_OFF</sub>) is very close to zero, the turn off dead time can be minimized.

Figure 5. SR MOSFET Operation Waveforms (Ideal Case)

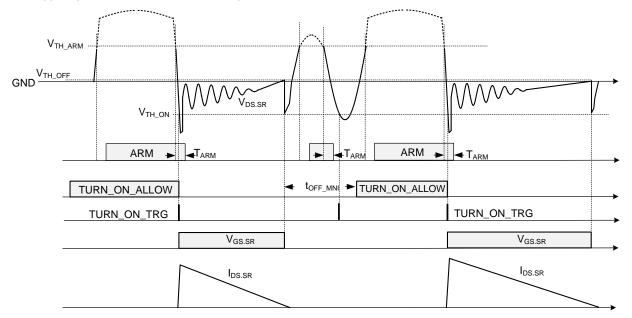

# **SR Turn-On Algorithm**

As the diagram shown in Figure 6, the turn-on of SR GATE is triggered by the three input signals of AND gate. The first input signal is TURN\_ON\_ALLOW signal, which is given after  $t_{OFF\_MIN}$  from the falling edge of  $V_{GS.SR}$  signal. The second input is the TURN\_ON\_TRG signal, which is enabled after DRAIN pin voltage drops below  $V_{TH\_ON}$ . The third signal is  $T_{ARM}$  which allows turn-on trigger only when SR drain voltage drops fast with a large slope, preventing SR from triggering by the drain resonance voltage in DCM operation.

Figure 6. SR Turn-On Algorithm

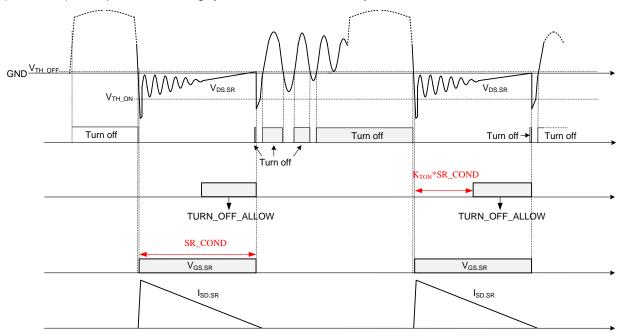

## **SR Turn-Off Algorithm**

As diagram shown in Figure 7, the turn-off of SR GATE is triggered by the two input signals of AND gate. The first input signal is turn off signal, which is enabled when  $V_{DS,SR} > V_{TH_OFF}$ . The second input is TURN\_OFF\_ALLOW signal given from the adaptive turn-off blanking. The blanking time is adaptively determined as half of SR conduction time (SR\_COND) of the previous switching cycle for better noise immunity.

Figure 7. SR Turn-Off Algorithm

### **SR Skipping Mode Algorithm**

As diagram shown in Figure 8, FAN6240 disables SR gate signal (SR skipping) at next cycle when previous cycle SR conduction time  $V_{GS.SR}$  signal is smaller than the minimum ON time  $t_{ON\_MIN.LL}$  in order reduce power consumption. This operation occurs only when the burst mode entry level of the primary side PWM controller is extremely low.

Figure 8. SR Skipping Diagram

ON Semiconductor and in are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at <a href="www.onsemi.com/site/pdt/Patent-Marking.pdf">www.onsemi.com/site/pdt/Patent-Marking.pdf</a>. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON Semiconductor products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by ON Semiconductor. "Typical" parameters which may be provided in ON Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights nor the rights of others. ON Semiconductor products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold ON Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and exp

### **PUBLICATION ORDERING INFORMATION**

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor 19521 E. 32nd Pkwy, Aurora, Colorado 80011 USA Phone: 303-675-2175 or 800-344-3860 Toll Free USA/Canada Fax: 303-675-2176 or 800-344-3867 Toll Free USA/Canada Email: orderlit@onsemi.com N. American Technical Support: 800-282-9855 Toll Free USA/Canada

Europe, Middle East and Africa Technical Support:

Phone: 421 33 790 2910

Japan Customer Focus Center

Phone: 81-3-5817-1050

ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative

# **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Switching Controllers category:

Click to view products by ON Semiconductor manufacturer:

Other Similar products are found below:

AZ7500EP-E1 NCP1218AD65R2G NCP1234AD100R2G NCP1244BD065R2G NCP1336ADR2G NCP6153MNTWG NCP81101BMNTXG

NCP81205MNTXG SJE6600 SMBV1061LT1G SG3845DM NCP4204MNTXG NCP6132AMNR2G NCP81102MNTXG

NCP81203MNTXG NCP81206MNTXG NX2155HCUPTR UBA2051C MAX8778ETJ+ NTBV30N20T4G NCP1240AD065R2G

NCP1240FD065R2G NCP1361BABAYSNT1G NTC6600NF NCP1230P100G NCP1612BDR2G NX2124CSTR SG2845M

NCP81101MNTXG TEA19362T/1J IFX81481ELV NCP81174NMNTXG NCP4308DMTTWG NCP4308DMNTWG NCP4308AMTTWG

NCP1251FSN65T1G NCP1246BLD065R2G NTE7154 NTE7242 LTC7852IUFD-1#PBF LTC7852EUFD-1#PBF MB39A136PFT-G-BND-ERE1 NCP1256BSN100T1G LV5768V-A-TLM-E NCP1365BABCYDR2G NCP1365AABCYDR2G MCP1633T-E/MG NCV1397ADR2G

NCP1246ALD065R2G AZ494AP-E1