# Advanced Synchronous Rectifier Controller for LLC Resonant Converter

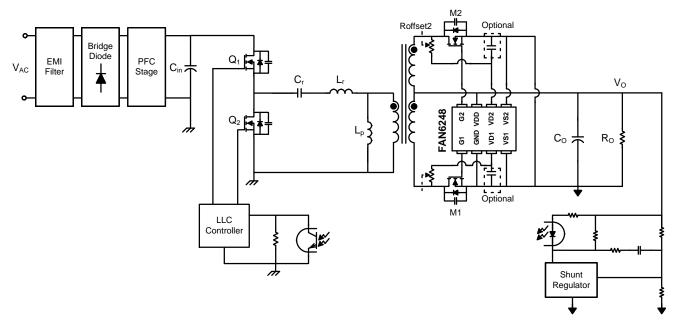

The FAN6248 is an advanced synchronous rectifier (SR) controller that is optimized for LLC resonant converter topology with minimum external components. It has two driver stages for driving the SR MOSFETs which are rectifying the outputs of the secondary transformer windings. The two gate driver stages have their own sensing inputs and operate independently of each other. The adaptive parasitic inductance compensation function minimizes the body diode conduction maximizing the efficiency. The advanced control algorithm allows stable SR operation over entire load range. According to the operating frequency and turn-off threshold voltage, FAN6248 has four different versions – FAN6248HCMX, FAN6248HDMX, FAN6248LCMX, FAN6248LDMX.

### **Features**

- Highly Integrated Self-contained Control of Synchronous Rectifier with a Minimum External Component Count

- Optimized for LLC Resonant Converter

- Anti Shoot-through Control for Reliable SR Operation

- Separate 100 V Rated Sense Inputs for Sensing the Drain and Source Voltage of each SR MOSFET

- Adaptive Parasitic Inductance Compensation to Minimize the Body Diode Conduction

- SR Current Inversion Detection under Light Load Condition

- Light Load Detection to Increase Dead Time Target

- Adaptive Minimum on Time for Noise Immunity

- Operating Voltage Range up to 30 V

- Low Start-up and Stand-by Current Consumption

- Operating Frequency Range from 25 kHz up to 700 kHz

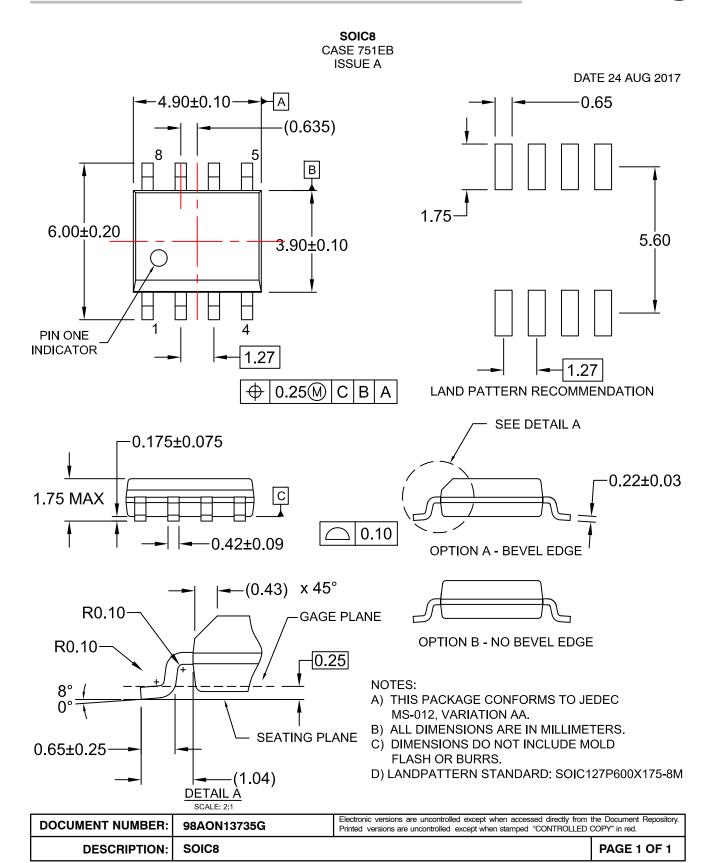

- SOIC-8 Package

- $\bullet\,$  High Driver Output Voltage of 10.5 V to Drive All MOSFET Brands to the Lowest  $R_{DS\_ON}$

- Low Operating Current in Green Mode (typ. 350 µA)

- These Devices are Pb-Free, Halogen Free and are RoHS Compliant

### **Applications**

- High Power Density Laptop Adapter

- High Power Density Adapter

- Large Screen LCD-TV, PDP-TV, RP-TV Power

- High-efficiency Desktop and Server Power Supplies

- Networking and Telecom Power Supplies

- High Power LED Lighting

### ON Semiconductor®

www.onsemi.com

SOIC-8 CASE 751EB

#### MARKING DIAGRAM

U = Frequency, H: High, L: Low

$V = V_{TH OFF}$  Level, C or D

= Assembly Plant Code

X = Year Code

Ζ

= Two Week Code

TT = Die Run Code

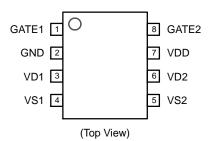

### **PIN CONNECTIONS**

### ORDERING INFORMATION

See detailed ordering and shipping information on page 3 of this data sheet

Figure 1. Typical Application Schematic of FAN6248

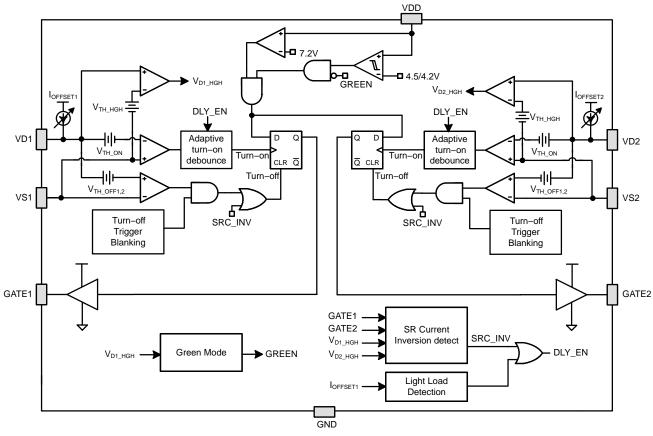

Figure 2. Internal Block Diagram of FAN6248

### **PIN DESCRIPTION**

| Pin Number | Pin Name | Description                                                                                                                                                                                                                                                                                                                                                 |

|------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1          | GATE1    | Gate drive output for SR1                                                                                                                                                                                                                                                                                                                                   |

| 2          | GND      | Ground                                                                                                                                                                                                                                                                                                                                                      |

| 3          | VD1      | Synchronous rectifier drain sense input. A I <sub>OFFSET1</sub> current source flows out of the DRAIN pin such that an external series resistor can be used to adjust the synchronous rectifier turn-off threshold. The I <sub>OFFSET1</sub> current source is turned off when V <sub>DD</sub> is under-voltage or when switching is disabled in green mode |

| 4          | VS1      | Synchronous rectifier source sense input for SR1                                                                                                                                                                                                                                                                                                            |

| 5          | VS2      | Synchronous rectifier source sense input for SR2                                                                                                                                                                                                                                                                                                            |

| 6          | VD2      | Synchronous rectifier drain sense input. A I <sub>OFFSET2</sub> current source flows out of the DRAIN pin such that an external series resistor can be used to adjust the synchronous rectifier turn-off threshold. The I <sub>OFFSET2</sub> current source is turned off when V <sub>DD</sub> is under-voltage or when switching is disabled in green mode |

| 7          | VDD      | Supply Voltage                                                                                                                                                                                                                                                                                                                                              |

| 8          | GATE2    | Gate drive output for SR2                                                                                                                                                                                                                                                                                                                                   |

### **ORDERING AND SHIPPING INFORMATION**

| Ordering Code | Device Marking | V <sub>TH_OFF1</sub> / V <sub>TH_OFF2</sub> | Package | Shipping <sup>†</sup> |

|---------------|----------------|---------------------------------------------|---------|-----------------------|

| FAN6248HCMX   | FAN6248HC      | 25 mV / 50 mV                               | SOIC-8  | 2500 / Tape & Reel    |

| FAN6248HDMX   | FAN6248HD      | 0 mV / 25 mV                                | SOIC-8  | 2500 / Tape & Reel    |

| FAN6248LCMX   | FAN6248LC      | 25 mV / 50 mV                               | SOIC-8  | 2500 / Tape & Reel    |

| FAN6248LDMX   | FAN6248LD      | 0 mV / 25 mV                                | SOIC-8  | 2500 / Tape & Reel    |

<sup>†</sup>For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, <u>BRD8011/D</u>.

#### **MAXIMUM RATINGS**

| Symbol                                     | Parameter                                                                            |                                                  |      | Max  | Unit |

|--------------------------------------------|--------------------------------------------------------------------------------------|--------------------------------------------------|------|------|------|

| V <sub>DD</sub>                            | Power Supply Input Pin Voltage                                                       | ge                                               | -0.3 | 30   | V    |

| $V_{D1}$ , $V_{D2}$                        | Drain Sense Input Pin Voltage                                                        | )                                                | -1   | 100  | V    |

| V <sub>GATE1</sub> ,<br>V <sub>GATE2</sub> | Gate Drive Output Pin Voltage                                                        | 9                                                | -0.3 | 30   | V    |

| V <sub>S1</sub> , V <sub>S2</sub>          | Source Sense Input Pin Volta                                                         | Source Sense Input Pin Voltage                   |      |      | V    |

| P <sub>D</sub>                             | Power Dissipation (T <sub>A</sub> = 25°C                                             | Power Dissipation (T <sub>A</sub> = 25°C)        |      |      | W    |

| $\Theta_{JA}$                              | Thermal Resistance (Junction                                                         | Thermal Resistance (Junction-to-Ambient Thermal) |      |      | °C/W |

| T <sub>J</sub>                             | Operating Junction Temperate                                                         | ure                                              | -40  | 150  | °C   |

| T <sub>STG</sub>                           | Storage Temperature Range                                                            |                                                  | -60  | 150  | °C   |

| TL                                         | Lead Temperature (Soldering)                                                         | Lead Temperature (Soldering) 10 Seconds          |      |      | °C   |

| ESD                                        | Electrostatic Discharge Capability Human Body Model, ANSI / ESDA / JEDEC JS-001-2012 |                                                  |      | 4    | kV   |

|                                            |                                                                                      | Charged Device Model, JESD22-C101                |      | 1.75 |      |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

#### THERMAL CHARACTERISTICS

| Symbol          | Rating                  | Value | Unit |

|-----------------|-------------------------|-------|------|

| $R_{\psiJT}$    | Thermal Characteristics | 22    | °C/W |

| $R_{\theta JA}$ | Thermal Characteristics | 165   | °C/W |

### **RECOMMENDED OPERATING CONDITIONS**

| Symbol                          | Parameter                              | Min  | Max  | Unit |

|---------------------------------|----------------------------------------|------|------|------|

| $V_{DD}$                        | VDD Pin Supply Voltage to GND (Note 2) | 0    | 27   | V    |

| $V_{D1}$ , $V_{D2}$             | Drain Sense Input Pin Voltage          | -0.7 | 100  | V    |

| V <sub>S1</sub> V <sub>S2</sub> | Source Sense Input Pin Voltage         | -0.4 | 0.4  | V    |

| T <sub>A</sub>                  | Operating Ambient Temperature (Note 3) | -40  | +125 | °C   |

Functional operation above the stresses listed in the Recommended Operating Ranges is not implied. Extended exposure to stresses beyond the Recommended Operating Ranges limits may affect device reliability.

- 2. Allowable operating supply voltage V<sub>DD</sub> can be limited by the power dissipation of FAN6248 related to switching frequency, load capacitance and ambient temperature.

- Allowable operating ambient temperature can be limited by the power dissipation of FAN6248 related to switching frequency, load capacitance on GATE pin and V<sub>DD</sub>.

<sup>1.</sup> All voltage values are with respect to the GND pin.

### **ELECTRICAL CHARACTERISTICS** ( $V_{DD} = 12 \text{ V}$ and $T_{J} = -40^{\circ}\text{C}$ to $+125^{\circ}\text{C}$ unless otherwise specified)

| Symbol                    | Parameter                                                                                                                   | Conditions                                                                                                                 | Min      | Тур  | Max   | Unit |

|---------------------------|-----------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|----------|------|-------|------|

| NPUT VOLTAGE              | •                                                                                                                           | •                                                                                                                          |          | •    | •     |      |

| V <sub>DD_ON</sub>        | Turn-On Threshold                                                                                                           | V <sub>DD</sub> rising                                                                                                     | 4.2      | 4.5  | 4.7   | V    |

| V <sub>DD_OFF</sub>       | Turn-Off Threshold                                                                                                          | V <sub>DD</sub> falling                                                                                                    | 4.0      | 4.2  | 4.4   |      |

| V <sub>DD_GATE_ON</sub> * | SR Gate Enable Threshold Voltage                                                                                            | V <sub>DD</sub> rising                                                                                                     |          | 7.2  |       | V    |

| I <sub>DD OP</sub>        | Operating Current                                                                                                           | f <sub>SW</sub> = 100 kHz, C <sub>GATE</sub> = 3.3 nF                                                                      | 7        | 8.5  | 10    | mA   |

| I <sub>DD_SRARTUP</sub>   |                                                                                                                             | V <sub>DD</sub> = V <sub>DD ON</sub> - 0.1 V                                                                               |          |      | 200   | μΑ   |

| I <sub>DD GREEN</sub>     | Operating Current in Green Mode                                                                                             | V <sub>DD</sub> = 12 V (no switching)                                                                                      |          | 350  | 500   | μΑ   |

|                           | SENSING SECTION (V <sub>D1</sub> = V <sub>D2</sub> )                                                                        |                                                                                                                            | <u>I</u> | 1    |       |      |

| V <sub>OSI</sub> *        | Comparator Input Offset Voltage                                                                                             |                                                                                                                            | -1       | 0    | 1     | mV   |

| I <sub>OFFSET</sub> *     | I <sub>OFFSET1</sub> and I <sub>OFFSET2</sub>                                                                               | Maximum of adaptive offset current (15 steps, 9 μA resolution)<br>IOFFSET=IOFFSET_STEP15                                   | 112.5    | 135  | 157.5 | μΑ   |

| $V_{TH\_ON}$              | Turn-On Threshold                                                                                                           | $R_{DRAIN} = 0 \Omega$ (includes comparator input offset voltage)                                                          | -290     | -240 | -190  | mV   |

| t <sub>ON_DLY</sub> *     | Turn on delay for de-bounce time when turn-on delay mode is disabled by detecting normal SR current                         | From $V_{D1}$ falling below $V_{TH\_ON}$ to $V_{GATE}$ rising above $V_{G\_HG}$ (With 50 mV overdrive), $C_{GATE} = 0$ nF  |          | 80   |       | ns   |

| t <sub>ON_DLY2_H</sub> *  | Turn on delay for de-bounce time when turn-on delay mode is enabled by detecting SR current inversion for HC and HD version | From $V_{D1}$ falling below $V_{TH\_ON}$ to $V_{GATE}$ rising above $V_{G\_HG}$ (With 50 mV overdrive), $C_{GATE} = 0$ nF  |          | 850  |       | ns   |

| t <sub>ON_DLY2_L</sub> *  | Turn on delay for de-bounce time when turn-on delay mode is enabled by detecting SR current inversion for LC and LD version | From $V_{D1}$ falling below $V_{TH\_ON}$ to $V_{GATE}$ rising above $V_{G\_HG}$ (With 50 mV overdrive), $C_{GATE} = 0$ nF  |          | 1100 |       | ns   |

| V <sub>TH_OFF1_C</sub> *  | First Level Turn-Off Threshold for HC and LC version                                                                        | $R_{DRAIN} = 0 \Omega$ (includes comparator input offset voltage)                                                          |          | 25   |       | mV   |

| V <sub>TH_OFF2_C</sub> *  | Second Level Turn-Off Threshold for HC and LC version                                                                       | $R_{DRAIN} = 0 \Omega$ (includes comparator input offset voltage)                                                          |          | 50   |       | mV   |

| V <sub>TH_OFF1_D</sub> *  | First Level Turn-Off Threshold for HD and LD version                                                                        | $R_{DRAIN} = 0 \Omega$ (includes comparator input offset voltage)                                                          |          | 0    |       | mV   |

| $V_{TH\_OFF2\_D}^{*}$     | Second Level Turn-Off Threshold for HD and LD version                                                                       | $R_{DRAIN} = 0 \Omega$ (includes comparator input offset voltage)                                                          |          | 25   |       | mV   |

| <sup>t</sup> OFF_DLY*     | Comparator Delay of V <sub>TH_OFF1</sub>                                                                                    | From $V_{D1}$ rising above $V_{TH\_OFF}$ to $V_{GATE}$ falling below $V_{G\_LW}$ (With 10 mV overdrive), $C_{GATE} = 0$ nF |          | 50   |       | ns   |

| V <sub>TH_HGH</sub>       | Drain Voltage High Detect Threshold                                                                                         | V <sub>D1</sub> Rising                                                                                                     | 0.80     | 1    | 1.20  | V    |

| t <sub>DB_HGH_</sub> H*   | V <sub>TH_HGH</sub> Detection Blanking Time for HC and HD version                                                           | From V <sub>D1</sub> falling below V <sub>TH_ON</sub>                                                                      |          | 540  |       | ns   |

| t <sub>DB_HGH_L</sub> *   | V <sub>TH_HGH</sub> Detection Blanking Time for LC and LD version                                                           | From V <sub>D1</sub> falling below V <sub>TH_ON</sub>                                                                      |          | 1    |       | μs   |

| V <sub>OFF_FORCE</sub> *  | Forced Turn-off Threshold                                                                                                   | V <sub>D1</sub> > V <sub>OFF_FORCE</sub> = V <sub>TH_HGH_EN</sub>                                                          |          | 1    |       | V    |

| INIMUM ON-TIM             | E AND MAXIMUM ON-TIME                                                                                                       |                                                                                                                            |          |      | _     |      |

| K <sub>TON</sub> *        | Adaptive Minimum On Time Ratio                                                                                              | Ratio between t <sub>ON_MIN</sub> and SR conduction time of previous switching cycle                                       |          | 25   |       | %    |

| t <sub>ON_MIN_LH</sub> *  | Minimum On-Time Lower Limit for HC and HD version                                                                           | t <sub>ON_MIN_LH</sub> < t <sub>ON_MIN</sub> < t <sub>ON_MIN_UH</sub>                                                      | 200      |      |       | ns   |

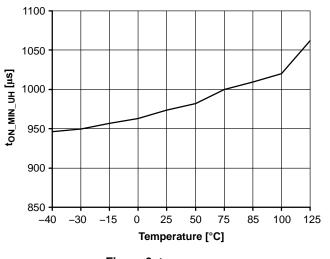

| ton_min_uh                | Minimum On-Time Upper Limit for HC and HD version                                                                           |                                                                                                                            | 0.96 1.2 |      | 1.44  | μs   |

|                           | -                                                                                                                           | •                                                                                                                          |          |      |       |      |

**ELECTRICAL CHARACTERISTICS** (V<sub>DD</sub> = 12 V and T<sub>J</sub> = -40°C to +125°C unless otherwise specified) (continued)

| Symbol                           | Parameter                                                                                                                      | Conditions                                                                                                                                                                                                                 | Min  | Тур  | Max  | Unit  |

|----------------------------------|--------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|-------|

| MINIMUM ON-TIME                  | AND MAXIMUM ON-TIME                                                                                                            |                                                                                                                                                                                                                            |      | •    |      |       |

| t <sub>ON_MIN_LL</sub> *         | Minimum On-Time Lower Limit for LC and LD version                                                                              | t <sub>ON_MIN_LL</sub> < t <sub>ON_MIN</sub> < t <sub>ON_MIN_UL</sub>                                                                                                                                                      |      | 0.4  |      | μs    |

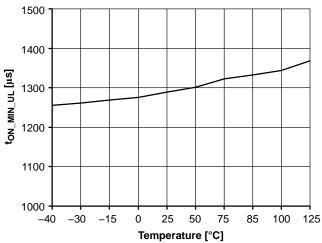

| t <sub>ON_MIN_UL</sub>           | Minimum On-Time Upper Limit for LD and LD version                                                                              |                                                                                                                                                                                                                            | 3.2  | 4    | 4.8  | μS    |

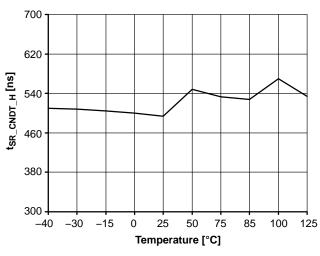

| t <sub>SR_CNDT_H</sub>           | Minimum SR Conduction Time to enable SR for HC and HD version                                                                  | The duration from turn-on trigger to V <sub>DS</sub> rising above V <sub>TH_HGH</sub>                                                                                                                                      | 380  | 600  | 820  | ns    |

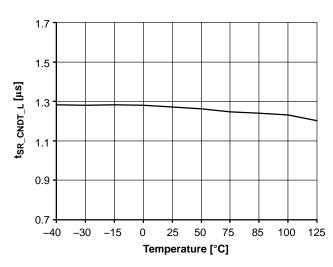

| t <sub>SR_CNDT_L</sub>           | Minimum SR Conduction Time to enable SR for LC and LD version                                                                  | The duration from turn-on trigger to V <sub>DS</sub> rising above V <sub>TH_HGH</sub>                                                                                                                                      | 0.85 | 1.2  | 1.65 | μS    |

| t <sub>SR_MAX_H</sub> *          | Maximum SR Turn-on Time for HC and HD version                                                                                  |                                                                                                                                                                                                                            |      | 15   |      | μS    |

| t <sub>SR_MAX_L</sub> *          | Maximum SR Turn-on Time for LC and LD version                                                                                  |                                                                                                                                                                                                                            |      | 30   |      | μS    |

| REGULATED DEA                    | D TIME                                                                                                                         |                                                                                                                                                                                                                            |      |      |      |       |

| <sup>t</sup> DEAD_H <sup>*</sup> | Dead time regulation target for HC and HD version                                                                              | From $V_{GATE}$ falling below $V_{G\_LW}$ to $V_{DS}$ rising above $V_{TH\_HGH}$                                                                                                                                           |      | 280  |      | ns    |

| t <sub>DEAD_H_LIGHT</sub> *      | Dead time regulation target under light load condition for HC and HD version                                                   | From $V_{GATE}$ falling below $V_{G_LW}$ to $V_{DS}$ rising above $V_{TH\_HGH}$                                                                                                                                            |      | 320  |      | ns    |

| t <sub>DEAD_L</sub> *            | Dead time regulation target for LC and LD version                                                                              | From $V_{GATE}$ falling below $V_{G_LW}$ to $V_{DS}$ rising above $V_{TH_LHGH}$                                                                                                                                            |      | 320  |      | ns    |

| t <sub>DEAD_L_LIGHT</sub> *      | Dead time regulation target under light load condition for LC and LD version                                                   | From $V_{GATE}$ falling below $V_{G_LW}$ to $V_{DS}$ rising above $V_{TH_LHGH}$                                                                                                                                            |      | 360  |      | ns    |

| t <sub>TSDT</sub> *              | Too small dead time threshold to speed up I <sub>OFFSET</sub> change (Speed up 2 times)                                        | From $V_{GATE}$ falling below $V_{G_LW}$ to $V_{DS}$ rising above $V_{TH_LHGH}$                                                                                                                                            |      | 50   |      | ns    |

| K <sub>INV</sub> *               | Adaptive SR current inversion detection time Ratio between T <sub>INV</sub> and SR conduction time of previous switching cycle | $\begin{aligned} & \text{V}_{\text{GATE}} > \text{V}_{\text{G} \text{ HG}} \text{ and V}_{\text{DS}} > \\ & \text{V}_{\text{TH} \text{ OFF}} \\ & \text{K}_{\text{INV}} = 0.25 \times \text{K}_{\text{TON}} \end{aligned}$ |      | 6.25 |      | %     |

| ηιΝV_EXT <sup>*</sup>            | Normal switching cycles without capacitive current spike to exit SR current inversion detection state which has toN_DLY2       |                                                                                                                                                                                                                            |      | 31   |      | cycle |

| GREEN MODE CO                    | NTROL                                                                                                                          |                                                                                                                                                                                                                            |      |      |      |       |

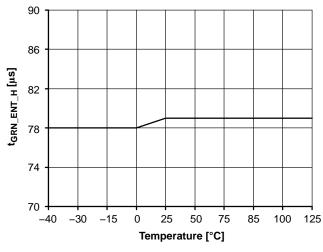

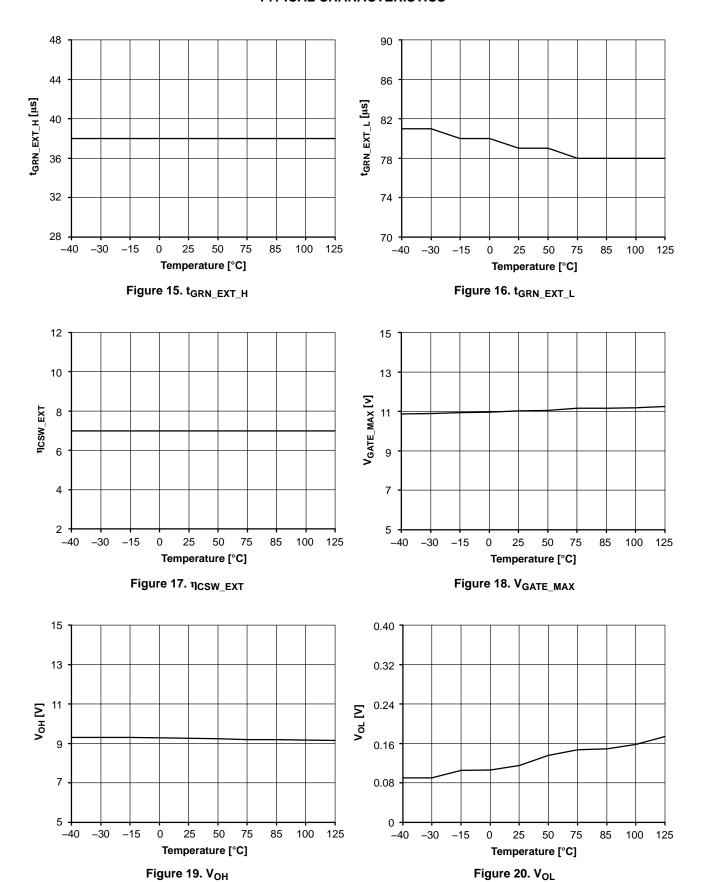

| t <sub>GRN_ENT_H</sub>           | Non-Switching Period to Enter Green<br>Mode for HC and HD version                                                              | Non switching cycles between burst switching bundles                                                                                                                                                                       | 60   | 80   | 100  | μs    |

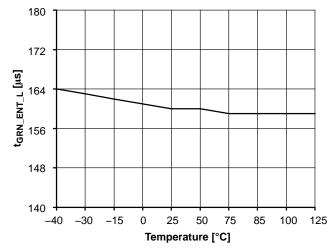

| t <sub>GRN_ENT_L</sub>           | Non-Switching Period to Enter Green<br>Mode for LC and LD version                                                              | Non switching cycles between burst switching bundles                                                                                                                                                                       | 120  | 160  | 200  | μS    |

| tGRN_ENT_DBNC_H                  | De-bounce time to Enter Green Mode for HC and HD version                                                                       | De-bounce time after t <sub>GRN.ENT_H</sub>                                                                                                                                                                                | 130  | 180  | 230  | μs    |

| <sup>t</sup> GRN_ENT_DBNC_L      | De-bounce time to Enter Green Mode for LC and LD version                                                                       | De-bounce time after t <sub>GRN_ENT_L</sub>                                                                                                                                                                                | 240  | 320  | 400  | μs    |

| tGRN_EXT_H                       | Non-Switching Period to Exit Green for HC and HD version                                                                       | Non switching cycles between burst switching bundles                                                                                                                                                                       | 30   | 40   | 50   | μs    |

| t <sub>GRN_EXT_L</sub>           | Non-Switching Period to Exit Green Mode for LC and LD version                                                                  | Non switching cycles between burst switching bundles                                                                                                                                                                       | 60   | 80   | 100  | μs    |

| ηcsw_ext                         | Continuous switching cycles to exit<br>Green Mode for HC, HD, LC and LD<br>version                                             |                                                                                                                                                                                                                            | 4    | 7    | 10   | cycle |

### **ELECTRICAL CHARACTERISTICS** ( $V_{DD}$ = 12 V and $T_J$ = -40°C to +125°C unless otherwise specified) (continued)

| Symbol                  | Parameter                                                                   | Conditions                                                                            | Min | Тур  | Max | Unit |

|-------------------------|-----------------------------------------------------------------------------|---------------------------------------------------------------------------------------|-----|------|-----|------|

| GREEN MODE CO           | ONTROL                                                                      |                                                                                       |     | •    |     |      |

| t <sub>S_NORMAL_H</sub> | Switching period to be recognized as normal switching for HC and HD version |                                                                                       | 13  | 20   | 27  | μs   |

| <sup>t</sup> S_NORMAL_L | Switching period to be recognized as normal switching for LC and LD version |                                                                                       | 27  | 40   | 53  | μs   |

| OUTPUT DRIVER           | SECTION                                                                     |                                                                                       | •   |      |     |      |

| $V_{GATE\_MAX}$         | Gate Clamping Voltage                                                       | 12 V < V <sub>DD</sub> < 25 V                                                         | 9   | 10.5 | 12  | V    |

| V <sub>OL</sub>         | Output Voltage Low                                                          | $V_{DD} = 12 \text{ V}, V_{D1} = V_{D2} = 2 \text{ V},$<br>$I_{GATE} = 50 \text{ mA}$ |     |      | 1.5 | V    |

| V <sub>OH</sub>         | Output Voltage High                                                         | $V_{DD} = 12 \text{ V}, I_{GATE} = -50 \text{ mA}$                                    | 7   |      |     | V    |

| I <sub>SOURCE</sub> *   | Peak Source Current for Turning On                                          | V <sub>DD</sub> = 12 V, V <sub>GATE</sub> = 2 V                                       |     | 0.7  |     | Α    |

| I <sub>SINK</sub> *     | Peak Sink Current for Turning Off                                           | V <sub>DD</sub> = 12 V, V <sub>GATE</sub> = 7 V                                       |     | 1.4  |     | Α    |

| t <sub>R</sub> *        | Rise Time                                                                   | $V_{DD}$ = 12 V, $C_L$ = 3.3 nF,<br>$V_{GATE}$ = 2 V $\rightarrow$ 7 V                |     | 50   |     | ns   |

| t <sub>F</sub> *        | Fall Time                                                                   | $V_{DD}$ = 12 V, $C_L$ = 3.3 nF,<br>$V_{GATE}$ = 7 V $\rightarrow$ 2 V                |     | 30   |     | ns   |

| $V_{G\_LW}^*$           | Gate voltage considered as turned off for adaptive dead time control        | Gate falling                                                                          |     | 4    |     | V    |

| V <sub>G_HG</sub> *     | Gate voltage considered as turned on for adaptive dead time control         | Gate rising                                                                           |     | 6    |     | ٧    |

| SWITCHING FRE           | QUENCY                                                                      |                                                                                       | •   | •    | •   |      |

| f <sub>MAX</sub> *      | Maximum Switching Frequency                                                 |                                                                                       | 700 |      |     | kHz  |

| f <sub>MIN</sub> *      | Minimum Switching Frequency                                                 |                                                                                       |     |      | 25  | kHz  |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

\*Not tested but guaranteed by design

### **KEY DIFFERENT PARAMETERS FOR FAN6248 OPTIONS**

| Item                    | FAN6248HC | FAN6248HD | FAN6248LC | FAN6248LD |

|-------------------------|-----------|-----------|-----------|-----------|

| t <sub>ON_DLY2</sub>    | 850 ns    | 850 ns    | 1100 ns   | 1100 ns   |

| t <sub>DB_HGH</sub>     | 540 ns    | 540 ns    | 1 μs      | 1 μs      |

| ton_min_l               | 200 ns    | 200 ns    | 400 ns    | 400 ns    |

| ton_min_u               | 1.2 μs    | 1.2 μs    | 4 μs      | 4 μs      |

| tsr_cndt                | 0.6 μs    | 0.6 μs    | 1.2 μs    | 1.2 μs    |

| t <sub>SR_MAX</sub>     | 15 μs     | 15 μs     | 30 μs     | 30 μs     |

| t <sub>DEAD</sub>       | 280 ns    | 280 ns    | 320 ns    | 320 ns    |

| t <sub>DEAD_LIGHT</sub> | 320 ns    | 320 ns    | 360 ns    | 360 ns    |

| t <sub>GRN_ENT</sub>    | 80 μs     | 80 μs     | 160 μs    | 160 μs    |

| t <sub>GRN_EXT</sub>    | 40 μs     | 40 μs     | 80 μs     | 80 μs     |

| t <sub>S_NORMAL</sub>   | 20 μs     | 20 μs     | 40 μs     | 40 μs     |

### **TYPICAL CHARACTERISTICS**

### **TYPICAL CHARACTERISTICS**

Figure 9. t<sub>ON\_DLY2\_H</sub>

Figure 10. t<sub>ON\_DLY2\_L</sub>

Figure 11. t<sub>SR\_CNDT\_H</sub>

Figure 12. t<sub>SR\_CNDT\_L</sub>

Figure 13. t<sub>GRN\_ENT\_H</sub>

Figure 14. t<sub>GRN\_ENT\_L</sub>

### **TYPICAL CHARACTERISTICS**

#### APPLICATION INFORMATION

#### **Basic Operation Principle**

FAN6248 controls the SR MOSFET based on the instantaneous drain-to-source voltage sensed across DRAIN and SOURCE pins. Before SR gate is turned on, SR body diode operates as the conventional diode rectifier. Once the body diode starts conducting, the drain-to-source voltage drops below the turn-on threshold voltage  $V_{TH\ ON}$  which triggers the turn-on of the SR gate. Then the drain-to-source voltage is determined by the product of turn-on resistance R<sub>ds</sub> on of SR MOSFET and instantaneous SR current. When the drain-to-source voltage reaches the turn-off threshold voltage V<sub>TH OFF</sub> as SR MOSFET current decreases to near zero, FAN6248 turns off the gate. If a SR dead time is larger or smaller than the dead time regulation target  $t_{DEAD}$ , FAN6248 adaptively changes internal offset voltage to compensate the dead time. In addition, to prevent cross conduction SR operation, FAN6248 has 200 ns of turn-on blocking time just after alternating SR gate is turned off.

#### **SR Turn-off Algorithm**

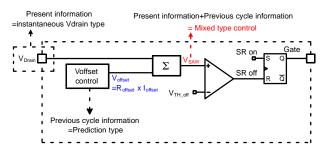

Since a SR turn-off method determines SR conduction time and stable SR operation, the SR turn-off method is one of important feature of SR controllers. The SR turn-off method can be classified into two methods. The first method uses present information by an instantaneous drain voltage. This method is widely used and easy to realize, and can prevent late turn-off. However, it may show premature turn-off by parasitic stray inductances caused by PCB pattern and lead frame of SR MOSFET. The second method predicts SR conduction time by using previous cycle drain voltage information. Since it can prevent the premature turn-off, it is good for the system with constant operating frequency and turn-on time. However, in case of the frequency varying system, it may lead late turn-off so that negative current can flow in the secondary side.

To achieve both advantages, FAN6248 adopts mixed type control method as shown in Figure 21. Basically the instantaneous drain voltage  $V_{Drain}$  is compared with  $V_{TH\_OFF}$  to turn off SR gate. Then, the offset voltage  $V_{Offset}$ , which is determined by the product  $R_{offset}$  and  $I_{offset}$ , is added to  $V_{Drain}$  in order to compensate the stray inductance effect and maintain 280 ns of  $t_{DEAD}$  regardless of parasitic inductances.  $R_{offset}$  is an external resistor in Figure 1 and  $I_{offset}$  is an internal modulation current in Figure 2. Therefore, FAN6248 can show robust operation with minimum dead time.

Figure 21. SR Turn-off Algorithm

### **Adaptive Dead Time Control**

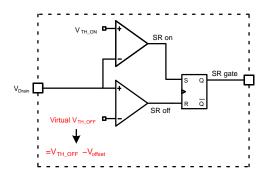

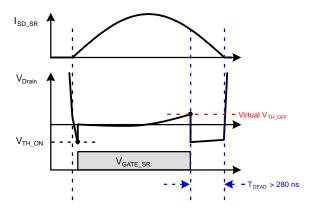

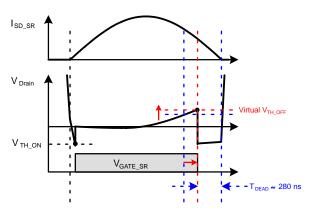

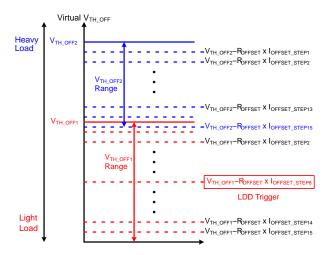

The stray inductances of the lead frame of SR MOSFET and PCB pattern induce positive voltage offset across drain-to-source voltage when SR current decreases. This makes drain-to-source voltage of SR MOSFET larger than the product of  $R_{ds\_on}$  and instantaneous SR current, which results in premature turn-off of SR gate. Since the induced offset voltage changes as load condition changes, the dead time also changes with load variation. To compensate the induced offset voltage, FAN6248 has a adaptive virtual turn-off threshold voltage as shown in Figure 22 with a combination of variable internal turn-off threshold voltages  $V_{TH\_OFF1}$  and  $V_{TH\_OFF2}$  (2 steps) and modulated offset voltage  $V_{offset}$  (16 steps). The virtual turn-off threshold voltage can be expressed as:

Virtual

$$V_{TH OFF} = V_{TH OFF} - V_{offset}$$

(eq. 1)

In FAN6248HC(D) version, if a dead time  $T_{DEAD}$  is larger than 280 ns of  $t_{DEAD\_H}$ , as shown in Figure 23,  $V_{offset}$  is decreased by one step in next switching cycle. As a result, the dead time is decreased by increase of virtual  $V_{TH\_OFF}$ , and becomes close to  $t_{DEAD\_H}$ , as shown in Figure 24. If the dead time is smaller than  $t_{DEAD\_H}$ , the dead time is increased by the virtual  $V_{TH\_OFF}$  decrease. Thus, the dead time is maintained at around  $t_{DEAD\_H}$  regardless of parasitic inductances.

Figure 22. Virtual V<sub>TH\_OFF</sub>

Figure 23. Premature SR Gate Turn-off  $(T_{DEAD} > t_{DEAD H})$

Figure 24. Dead Time Control to Maintain T<sub>DEAD</sub> ≈ t<sub>DEAD</sub> H

#### **Minimum Turn-on Time**

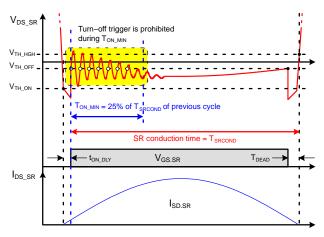

When SR gate is turned on, there may be severe oscillation in drain-to-source voltage of SR MOSFET, which results in several mis-triggering turn-off as shown in Figure 25. To provide stable SR control without mis-trigger, it is desirable to have large turn-off blanking time (= minimum turn-on time) until the drain voltage oscillation attenuates. However, too large blanking time results in problems at light load condition where the SR conduction time is shorter than the minimum turn-on time. To solve this issue, FAN6248 has adaptive minimum turn-on time where the turn-off blanking time changes in accordance with the SR conduction time  $T_{SRCOND}$  measured in previous switching cycle. The SR conduction time is measured by the time from SR gate rising edge to the instant when drain sensing voltage  $V_{DS}$  SR is higher than  $V_{TH\ HGH}$ . From the previous cycle  $T_{SRCOND}$ measurement result, the minimum turn-on time is defined by 25% of  $T_{SRCOND}$ .

### **Capacitive Current Spike Detection**

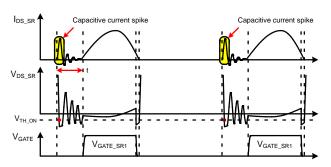

At heavy load condition, the body diode of SR MOSFET in LLC resonant converter starts conducting right after the primary side switching transition takes place. However, when the resonance capacitor voltage amplitude is not large enough at light load condition, the voltage across the

magnetizing inductance of the transformer is smaller than the reflected output voltage. Thus, the secondary side SR body diode conduction is delayed until the magnetizing inductor voltage builds up to the reflected output voltage. However, the primary side switching transition can cause capacitive current spike and turn on the body diode of SR MOSFET for a short time as shown in Figure 26, which induces SR mis-trigger signal. Finally, the SR mis-trigger makes inversion current in the secondary side. If a proper algorithm is not provided to prevent the mis-trigger by the capacitive current spike, severe SR current inversion can happen.

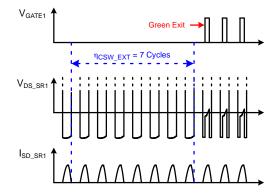

To prevent the SR mis-trigger, FAN6248 has a capacitive current spike detection method. When SR current inversion occurs by the mis-trigger signal, the drain sensing voltage of SR MOSFET becomes positive. In this condition, if  $V_{DS\_SR}$  is higher than  $V_{TH\_OFF}$  for  $(T_{SRCOND} \times K_{INV})$ , SR current inversion is detected. After then, FAN6248 turns off SR immediately and increases turn-on delay to  $t_{ON\_DLY2}$  next cycle.

Figure 25. Minimum Turn-on Time

Figure 26. Capacitive Current Spike at Light Load Condition

As a result, SR mis-trigger is prevented. To exit the SR current inversion detection mode, seven consecutive switching cycles without capacitive current spike are required.

### **Light Load Detection (LLD)**

To guarantee stable operation under light load condition, FAN6248 adopts a light load detection function. The modulation current  $I_{OFFSET}$  is mainly used for the adaptive dead time control. When the output load is heavy, I<sub>OFFSET STEP</sub> declines due to large di/dt in the secondary side current to maintain 280 ns of  $t_{DEAD}$  in FAN6248HC(D). On the contrary, IOFFSET STEP increases at light load condition by small di/dt of SR current. FAN6248 can detect light load condition by using this *I*<sub>OFFSET\_STEP</sub> as shown in Figure 27. When SR turn-off threshold voltage is V<sub>TH OFF1</sub> and the modulation current is higher than IOFFEST\_STEP8, the light load detection is triggered. In this mode, dead time 320 ns becomes to of t<sub>DEAD LIGHT</sub> in FAN6248HC(D) and 360 ns in FAN6248LC(D) version.

#### **Green Mode**

When the power supply system operates at very light load condition, FAN6248 disables SR operation and enters into green mode operation. Once FAN6248 is in the green mode, all the major blocks are disabled to minimize the operating current. When  $V_{DS\_SR}$  has no switching operation longer than  $t_{GRN\_ENT}$  during the burst mode of the primary side LLC controller, the green mode is enabled after  $t_{GRN\_ENT\_DBNC}$  of debounce time. After then, FAN6248 exits the green mode when the non–switching time in the burst mode is less than  $t_{GRN\_EXT\_H}$  or 7 consecutive switching cycles are detected as shown in Figure 28.

Figure 27. Light Load Detection

Figure 28. Green Mode Exit

ON Semiconductor and are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. ON Semiconductor does not convey any license under its patent rights nor the rights of others.

onsemi, ONSEMI, and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi's product/patent coverage may be accessed at <a href="www.onsemi.com/site/pdf/Patent-Marking.pdf">www.onsemi.com/site/pdf/Patent-Marking.pdf</a>. Onsemi reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product features, availability, functionality, or suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using onsemi products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications provided by onsemi. "Typical" parameters which may be provided in onsemi data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. onsemi does not convey any license under any of its intellectual property rights nor the rights of others. onsemi products are not designed, intended, or authorized for use as a critical component in life support systems or any EDA class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer pu

#### **PUBLICATION ORDERING INFORMATION**

LITERATURE FULFILLMENT:

Email Requests to: orderlit@onsemi.com

onsemi Website: www.onsemi.com

TECHNICAL SUPPORT North American Technical Support: Voice Mail: 1 800-282-9855 Toll Free USA/Canada Phone: 011 421 33 790 2910

Europe, Middle East and Africa Technical Support:

Phone: 00421 33 790 2910

For additional information, please contact your local Sales Representative

# **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Switching Controllers category:

Click to view products by ON Semiconductor manufacturer:

Other Similar products are found below:

AZ7500EP-E1 NCP1218AD65R2G NCP1234AD100R2G NCP1244BD065R2G NCP1336ADR2G NCP6153MNTWG NCP81101BMNTXG NCP81205MNTXG SJE6600 SMBV1061LT1G SG3845DM NCP4204MNTXG NCP6132AMNR2G NCP81102MNTXG NCP81203MNTXG NCP81206MNTXG NX2155HCUPTR UBA2051C MAX8778ETJ+ NTBV30N20T4G NCP1240AD065R2G NCP1240FD065R2G NCP1361BABAYSNT1G NTC6600NF NCP1230P100G NCP1612BDR2G NX2124CSTR SG2845M NCP81101MNTXG TEA19362T/1J IFX81481ELV NCP81174NMNTXG NCP4308DMTTWG NCP4308DMNTWG NCP4308DMNTWG NCP4308AMTTWG NCP1251FSN65T1G NCP1246BLD065R2G NTE7154 NTE7242 LTC7852IUFD-1#PBF LTC7852EUFD-1#PBF MB39A136PFT-G-BND-ERE1 NCP1256BSN100T1G LV5768V-A-TLM-E NCP1365BABCYDR2G NCP1365AABCYDR2G MCP1633T-E/MG NCV1397ADR2G NCP1246ALD065R2G AZ494AP-E1