# Highly Integrated Secondary-Side Adaptive USB Type-C Charging Controller with USB-PD with SR Embedded

# FAN6390MPX

The FAN6390MPX is a highly integrated, secondary-side power adaptor controller supporting USB Type-C and USB Power Delivery 2.0/3.0. It includes a fully autonomous USB PD state machine which is fully compliant with the latest USB PD 3.0 specification, minimizing design time and cost. Support for the latest Programmable Power Supply (PPS) rules allows for control of voltages from 3.3 V to 21 V and current limits from 1 A to 3 A to meet a wide range of applications and power levels.

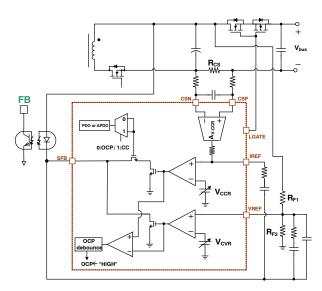

To minimize BOM count, the FAN6390MPX includes internal synchronous rectifier control, an NMOS gate driver for VBUS load switch control, as well as Constant Voltage (CV) and Constant Current (CC) control blocks with adjustable internal references. To ensure proper operation of the adaptor, various protections are integrated into the controller including output over-voltage protection, under-voltage protection, external over-temperature protection via NTC, internal over-temperature protection, CC over voltage protection and Cable Fault Protection.

### Features

- USB Type-C Rev 1.3 Compatible

- Support 60 W Output Profile

- (PDO: 5 V, 9 V, 15 V, 20 V. APDO: 9 V, 15 V, 20 V)

- Constant Voltage (CV) and Constant Current (CC) Regulation with Two Operational Amplifiers of Open–Drain Type for Dual–Loop CV/CC Control

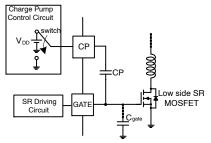

- Charge Pump Circuit to Enhance SR Driving Voltage for High Efficiency

- Small Current Sensing Resistor (5 mΩ) for High Efficiency

- N-Channel Back to Back MOSFET Control as a Load Switch

- Built-in Output Capacitor Bleeding Function for Fast Discharging

- Precise Voltage & Current Control for Minimum Step Size via 10-bit DAC's

- 10-bit ADC for Monitoring Voltage, Current and Temperature

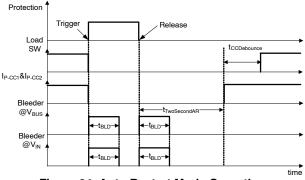

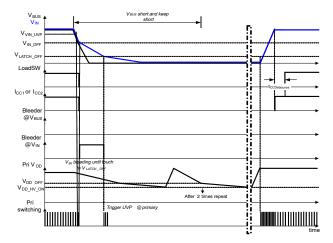

- Auto Re-start Protection Mode Option to Disable Load Switch for 2 seconds

- Support Protections; Output Over-Voltage Protection, Under-Voltage Protection, External Over Temperature Protection via NTC, Internal Over Temperature Protection, Cable Fault Protection, and CC Lines Over Voltage Protection

### **Typical Applications**

- Battery Chargers for Smart Phones, Feature Phones, and Tablet PCs

- AC-DC Adapters for Portable Devices that Require CV/CC Control

www.onsemi.com

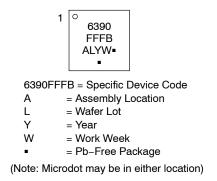

#### MARKING DIAGRAM

### **ORDERING INFORMATION**

See detailed ordering and shipping information in the package dimensions section on page 2 of this data sheet.

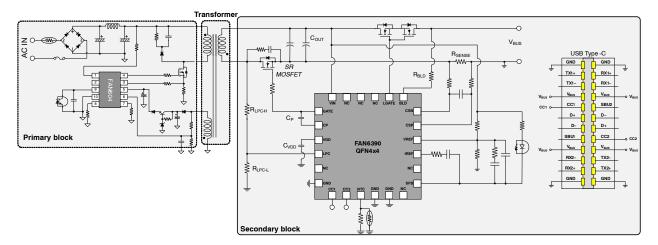

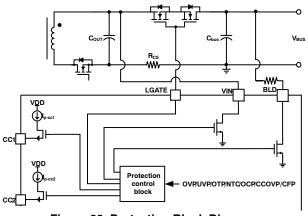

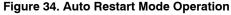

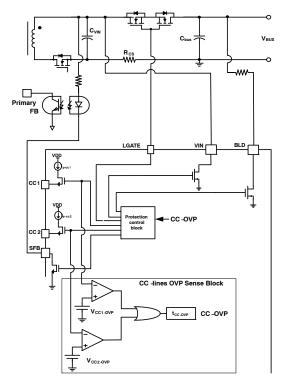

Figure 1. Application Schematic

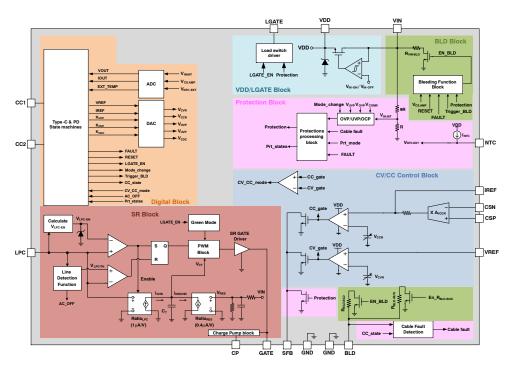

Figure 2. Block Diagram

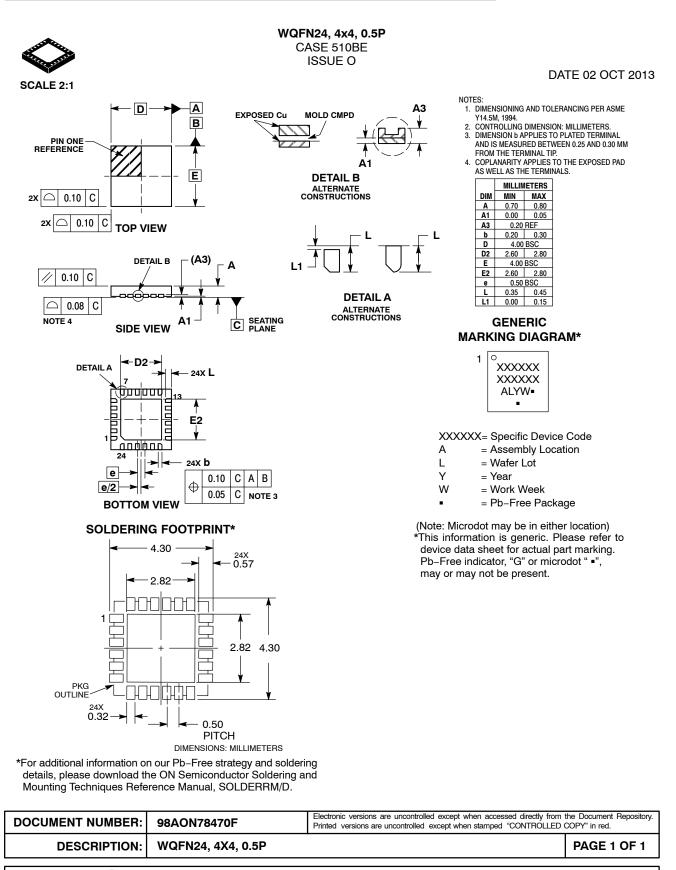

#### **ORDERING INFORMATION**

| Part Number   | Operating Temperature Range | Package                                                                    | Packing Method <sup>†</sup> |

|---------------|-----------------------------|----------------------------------------------------------------------------|-----------------------------|

| FAN6390MPXMPX | –40°C to +125°C             | 24–Lead, MLP, QUAD, JEDEC MO–220,<br>4 mm × 4 mm, 0.5 mm Pitch, Single DAP | Tape & Reel                 |

†For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

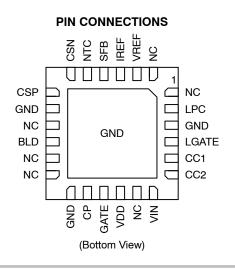

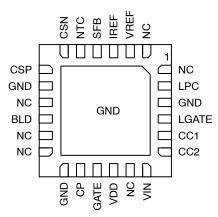

#### Figure 3. Pin Connections (Bottom View)

### Table 1. PIN FUNCTION DESCRIPTION(MLP44)

| Pin # | Pin Name | Description                                                                                                                                                                                                |

|-------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1     | NC       | No connection                                                                                                                                                                                              |

| 2     | LPC      | SR control input signal. This pin is used to detect the voltage on the secondary winding during the on time period of the primary MOSFET                                                                   |

| 3     | GND      | Ground                                                                                                                                                                                                     |

| 4     | LGATE    | Load switch gate drive signal. This pin is tied to the gate of the load switch                                                                                                                             |

| 5     | CC1      | Configuration Channel 1. This pin is used to detect USB Type-C devices and communicate over USB PD when applicable.                                                                                        |

| 6     | CC2      | Configuration Channel 2. This pin is used to detect USB Type-C devices and communicate over USB PD when applicable.                                                                                        |

| 7     | VIN      | Output voltage (Input voltage to the FAN6390MPX). This pin is tied to the output of the adapter to monitor its output voltage and supply internal bias.                                                    |

| 8     | NC       | No connection                                                                                                                                                                                              |

| 9     | VDD      | Internal supply voltage. This pin is connected to an external capacitor.                                                                                                                                   |

| 10    | GATE     | Gate drive output. Totem-pole output to drive the external SR MOSFET.                                                                                                                                      |

| 11    | CP       | SR gate charge pump                                                                                                                                                                                        |

| 12    | GND      | Ground                                                                                                                                                                                                     |

| 13    | NC       | No connection                                                                                                                                                                                              |

| 14    | NC       | No connection                                                                                                                                                                                              |

| 15    | BLD      | Bleeder pin. This pin is tied to VBUS after the load switch to discharge VBUS.                                                                                                                             |

| 16    | NC       | No connection                                                                                                                                                                                              |

| 17    | GND      | Ground                                                                                                                                                                                                     |

| 18    | CSP      | Current sensing amplifier positive terminal. Connect this pin directly to the positive end of the current sense resistor with a short PCB trace.                                                           |

| 19    | CSN      | Current sensing amplifier negative terminal. Connect this pin directly to the negative end of the current sense resistor with a short PCB trace.                                                           |

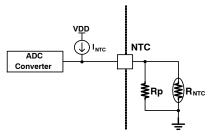

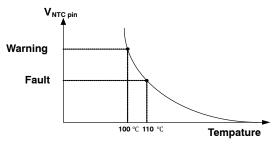

| 20    | NTC      | This pin is used for external temperature detection and protection                                                                                                                                         |

| 21    | SFB      | Secondary Feedback. Common output of the dual OTA open drain operation amplifiers. Typically an opto-<br>coupler is connected to this pin to provide feedback signal to the primary side PWM controller    |

| 22    | IREF     | Constant Current Amplifying Signal. The voltage level on this point is the amplified current sense signal. This pin is tied to the internal CC loop amplifier's non-inverting input terminal               |

| 23    | VREF     | Output Voltage Sensing Voltage. This pin is used for CV regulation, and it is tied to the internal CV loop am-<br>plifier non-inverting input terminal. It is tied to the output voltage resistor divider. |

| 24    | NC       | No connection                                                                                                                                                                                              |

#### Table 2. MAXIMUM RATINGS (Notes 1, 2)

| Rating                                                 | Symbol             | Value       | Unit |

|--------------------------------------------------------|--------------------|-------------|------|

| VIN Pin Input Voltage                                  | V <sub>IN</sub>    | -0.3 to 26  | V    |

| SFB Pin Input Voltage                                  | V <sub>SFB</sub>   | -0.3 to 26  | V    |

| BLD Pin Input Voltage                                  | V <sub>BLD</sub>   | -0.3 to 26  | V    |

| LGATE Pin Input Voltage                                | V <sub>LGATE</sub> | -0.3 to 31  | V    |

| VDD Pin Input Voltage                                  | V <sub>DD</sub>    | –0.3 to 6   | V    |

| IREF Pin Input Voltage                                 | V <sub>IREF</sub>  | –0.3 to 6   | V    |

| VREF Pin Input Voltage                                 | V <sub>VREF</sub>  | –0.3 to 6   | V    |

| CSP Pin Input Voltage                                  | V <sub>CSP</sub>   | –0.3 to 6   | V    |

| CSN Pin Input Voltage                                  | V <sub>CSN</sub>   | –0.3 to 6   | V    |

| LPC pin Input Voltage                                  | V <sub>LPC</sub>   | -0.3 to 6.5 | V    |

| GATE Pin Input Voltage                                 | V <sub>GATE</sub>  | -0.3 to 6.5 | V    |

| NTC Pin Input Voltage                                  | V <sub>NTC</sub>   | –0.3 to 6   | V    |

| CC1 Pin Input Voltage                                  | V <sub>CC1</sub>   | –0.3 to 6   | V    |

| CC2 Pin Input Voltage                                  | V <sub>CC2</sub>   | –0.3 to 6   | V    |

| CP Pin Input Voltage                                   | V <sub>CP</sub>    | -0.3 to 6.5 | V    |

| Power Dissipation ( $T_A = 25^{\circ}C$ )              | PD                 | 0.8644      | W    |

| Operating Junction Temperature                         | TJ                 | -40 to 150  | °C   |

| Storage Temperature Range                              | T <sub>STG</sub>   | -40 to 150  | °C   |

| Lead Temperature, (Soldering, 10 Seconds)              | TL                 | 260         | °C   |

| Human Body Model, ANSI/ESDA/JEDEC JS-001-2012 (Note 3) | ESD <sub>HBM</sub> | 2           | kV   |

| Charged Device Model, JESD22-C101 (Note 3)             | ESD <sub>CDM</sub> | 0.5         | kV   |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

All voltage values, except differential voltages, are given with respect to the GND pin.

Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device.

Meets JEDEC standards JS-001-2012 and JESD 22-C101.

#### Table 3. THERMAL CHARACTERISTICS (Note 4)

| Rating                                                                                                | Symbol                              | Value    | Unit |

|-------------------------------------------------------------------------------------------------------|-------------------------------------|----------|------|

| Thermal Characteristics,<br>Thermal Resistance, Junction-to-Air<br>Thermal Reference, Junction-to-Top | ${f R}_{	heta JA} {f R}_{	heta JT}$ | 122<br>5 | °C/W |

4.  $T_A = 25^{\circ}C$  unless otherwise specified.

#### **Table 4. RECOMMENDED OPERATING RANGES**

| Rating                                              | Symbol           | Min | Max | Unit |

|-----------------------------------------------------|------------------|-----|-----|------|

| Input Voltage                                       | V <sub>in</sub>  |     | 20  | V    |

| Output Current                                      | I <sub>out</sub> |     | 5   | А    |

| Adjustable Output Voltage (Adjustable Version Only) | V <sub>out</sub> |     | 20  | V    |

| Ambient Temperature                                 | T <sub>A</sub>   |     | 80  | °C   |

Functional operation above the stresses listed in the Recommended Operating Ranges is not implied. Extended exposure to stresses beyond the Recommended Operating Ranges limits may affect device reliability.

#### **Table 5. ELECTRICAL CHARACTERISTICS**

$V_{IN}$  = 5 V, LPC = 1.25 V, LPC width = 2  $\mu$ s at T<sub>J</sub> = -40~125°C, F<sub>LPC</sub> = 100 kHz, unless otherwise specified.

| Parameter                                                                          | Test Conditions                                                                   | Symbol                  | Min   | Тур   | Max   | Unit |

|------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|-------------------------|-------|-------|-------|------|

| VDD SECTION                                                                        |                                                                                   |                         |       | •     |       |      |

| Turn-On Valid Threshold Voltage                                                    |                                                                                   | V <sub>DD-valid</sub>   | 2.6   |       |       | V    |

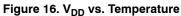

| VIN Operating Voltage at 20V                                                       | V <sub>IN</sub> = 20 V, I <sub>VDD</sub> = 0 mA                                   | V <sub>DD</sub>         | 4.750 | 5.125 | 5.500 | V    |

| VDD Source Current                                                                 | V <sub>IN</sub> = 3.3 V, V <sub>DD</sub> = 2.9 V                                  | I <sub>DD</sub>         | 10    |       |       | mA   |

| VIN SECTION                                                                        |                                                                                   |                         |       |       | •     |      |

| Continuous Operating Voltage<br>(Note 5)                                           |                                                                                   | V <sub>IN-OP</sub>      |       |       | 22.5  | V    |

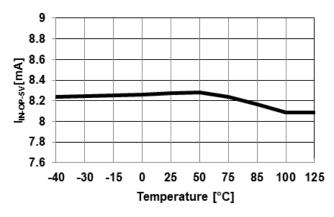

| Operating Supply Current at 5 V                                                    | $V_{\text{IN}}$ = 5 V, $V_{\text{CS}}$ = –25 mV, Rcs = 5 m $\Omega$               | I <sub>IN-OP-5V</sub>   |       |       | 10    | mA   |

| Operating Supply Current at 20 V<br>(Note 5)                                       | $V_{\text{IN}}$ = 20 V, $V_{\text{CS}}$ = –25 mV, Rcs = 5 m\Omega                 | I <sub>IN-OP-20</sub> V |       | 8     |       | mA   |

| Turn-On Threshold Voltage                                                          | V <sub>IN</sub> Increases                                                         | V <sub>IN-ON</sub>      | 2.9   | 3.2   | 3.4   | V    |

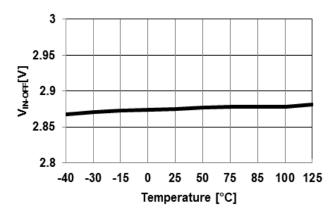

| Turn-Off Threshold Voltage                                                         | $V_{IN}$ Decreases after $V_{IN} = V_{IN-ON}$                                     | V <sub>IN-OFF</sub>     | 2.805 | 2.875 | 3.005 | V    |

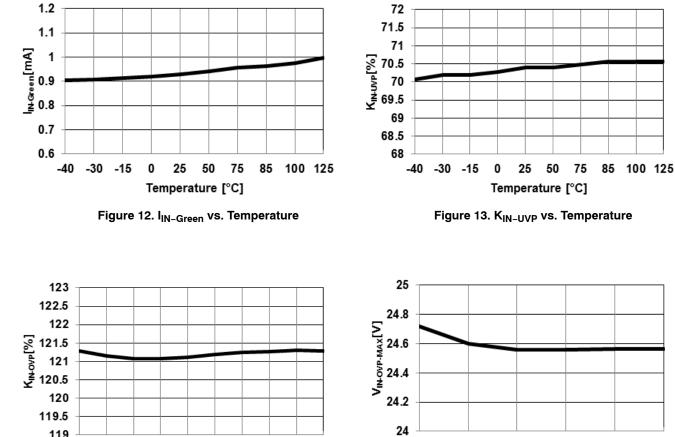

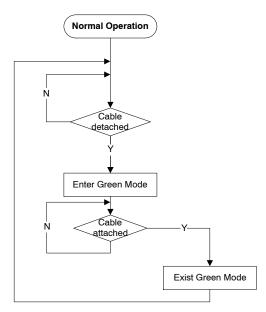

| Green Mode Operating Supply Current                                                | $V_{IN}$ = 5.2 V (default), $V_{CS}$ = 0 mV excluding $I_{P-CC1}$ and $I_{P-CC2}$ | I <sub>IN-Green</sub>   |       |       | 1.3   | mA   |

| VIN-UVP SECTION                                                                    |                                                                                   |                         | -     | -     |       |      |

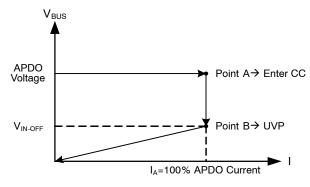

| Ratio V_{IN} Under–Voltage–Protection to $V_{IN}$                                  | Whole output mode, $V_{CS} = 0 \text{ mV}$                                        | K <sub>IN-UVP</sub>     | 65    | 70    | 75    | %    |

| CC Mode UVP Debounce Time                                                          |                                                                                   | t <sub>D-VIN-UVP</sub>  | 45    | 60    | 75    | ms   |

| UVP Blanking Time during Mode<br>Change from Lower Vout to Higher<br>Vout          | Whenever does mode change from<br>lower Vout to higher Vout                       | t <sub>BNK-UVP</sub>    | 160   | 200   | 240   | ms   |

| VIN-OVP SECTION                                                                    |                                                                                   |                         |       |       |       |      |

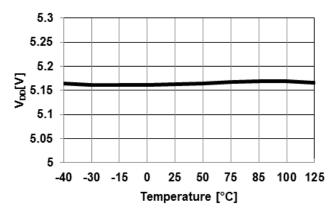

| Ratio V <sub>IN</sub> Over–Voltage–Protection to $V_{IN}$                          | Whole output mode, $V_{CS} = 0 \text{ mV}$                                        | K <sub>IN-OVP</sub>     | 116.0 | 121.5 | 127.0 | %    |

| V <sub>IN</sub> Maximum<br>Over-Voltage-Protection                                 |                                                                                   | V <sub>IN-OVP-MAX</sub> | 23.5  | 24.5  | 25.5  | V    |

| OVP Debounce Time                                                                  |                                                                                   | t <sub>D-OVP</sub>      | 19    | 31    | 43    | μs   |

| OVP Blanking Time during Mode<br>Change from Higher Vout to Lower<br>Vout (Note 5) | Vstep $\leq$ 0.5 V, Vbus $\geq$ 13<br>Disabling OVP & SR Gate.                    | t <sub>BNK-OVP</sub>    |       | 7     |       | ms   |

| OVP Blanking Time during Mode<br>Change from Higher Vout to Lower<br>Vout (Note 5) | Vstep $\leq$ 0.5 V, Vbus < 13<br>Disabling OVP & SR Gate.                         | t <sub>BNK-OVP</sub>    |       | 19    |       | ms   |

| OVP Blanking Time during Mode<br>Change from Higher Vout to Lower<br>Vout (Note 5) | Disabling OVP & SR Gate.<br>Vstep > 0.5 V, Vbus $\ge$ 13                          | t <sub>BNK-OVP</sub>    |       | 56    |       | ms   |

| OVP Blanking Time during Mode<br>Change from Higher Vout to Lower<br>Vout          | Disabling OVP & SR Gate.<br>Vstep > 0.5 V, Vbus < 13                              | t <sub>BNK-OVP</sub>    |       | 200   |       | ms   |

| CONSTANT CURRENT SENSING SEC                                                       | CTION (100% CC)                                                                   |                         |       |       |       |      |

| Current-Sense Amplifier Gain                                                       | $R_{CS} = 5 m\Omega$                                                              | AV-CCB                  |       | 40    |       | V/V  |

| Current-Sense Amplifier Gain<br>(Note 5)                                                   | $R_{CS} = 5 m\Omega$   | A <sub>V-CCR</sub>    |      | 40   |      | V/V |  |

|--------------------------------------------------------------------------------------------|------------------------|-----------------------|------|------|------|-----|--|

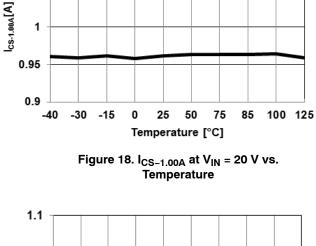

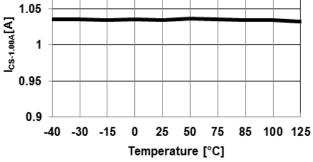

| Current threshold on sensing resistor between CSP and CSN at $I_{OUT.CC} = 1.00 \text{ A}$ | VIN = 3.3 V, 5 V, 20 V | I <sub>CS-1.00A</sub> | 0.86 | 1.00 | 1.14 | A   |  |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions. 5. Guaranteed by Design

#### Table 5. ELECTRICAL CHARACTERISTICS (continued)

$V_{IN}$  = 5 V, LPC = 1.25 V, LPC width = 2 µs at T<sub>J</sub> = -40~125°C, F<sub>LPC</sub> = 100 kHz, unless otherwise specified.

| Parameter                                                                                                | Test Conditions                                                                            | Symbol                     | Min   | Тур   | Max   | Unit |

|----------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|----------------------------|-------|-------|-------|------|

| CONSTANT CURRENT SENSING SEC                                                                             | CTION (100% CC)                                                                            | •                          |       |       |       |      |

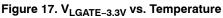

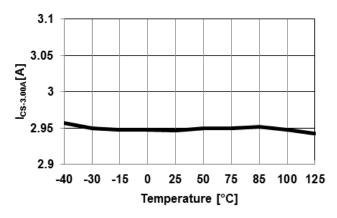

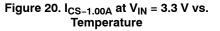

| Current threshold on sensing resistor between CSP and CSN at $I_{OUT.CC} = 3.00 \text{ A}$               | VIN = 3.3 V, 5 V, 20 V                                                                     | I <sub>CS-3.00A</sub>      | 2.88  | 3.00  | 3.12  | A    |

| Current threshold on sensing resistor between CSP and CSN at $\Delta I_{OUT,CC}$ = 50 mA (Note 5)        | $\Delta I_{OTYP} = 50 \text{ mA}$                                                          | I <sub>CS-STEP</sub>       | 48    | 50    | 52    | mA   |

| CONSTANT CURRENT SENSING SEC                                                                             | CTION (107% CC)                                                                            |                            |       |       |       |      |

| Current-Sense Amplifier Gain (Note 5)                                                                    | $R_{CS} = 5 m\Omega$                                                                       | A <sub>V-CCR</sub>         |       | 40    |       | V/V  |

| Current threshold on sensing resistor between CSP and CSN at $I_{OUT.CC} = 3.21 \text{ A}$               | VIN = 5 V                                                                                  | I <sub>CS-3.00A</sub>      | 3.09  | 3.21  | 3.33  | A    |

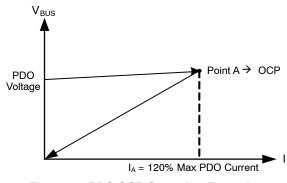

| CONSTANT CURRENT SENSING SEC                                                                             | CTION (120% OCP)                                                                           |                            |       |       |       |      |

| Current-Sense Amplifier Gain (Note 5)                                                                    | $R_{CS} = 5 m\Omega$                                                                       | A <sub>V-CCR</sub>         |       | 40    |       | V/V  |

| Current threshold on sensing resistor between CSP and CSN at $I_{OUT.CC} = 3.60 \text{ A}$               | VIN = 3.3 V, 5 V, 20 V                                                                     | I <sub>CS-3.0A</sub>       | 3.48  | 3.60  | 3.72  | A    |

| OCP Debounce Time                                                                                        |                                                                                            | T <sub>OCP-Debounce</sub>  | 50    | 60    | 70    | ms   |

| OUTPUT CURRENT SENSING SECTION                                                                           | ON                                                                                         |                            |       |       |       |      |

| Current threshold on sensing resistor<br>between CSP and CSN for enabling<br>bleeding during mode change |                                                                                            | I <sub>CS-EN-BLD</sub>     |       |       | 450   | mA   |

| Debounce time for enabling bleeding during mode change                                                   |                                                                                            | T <sub>CS-EN-BLD</sub>     |       |       | 1.0   | ms   |

| CONSTANT VOLTAGE SENSING SEC                                                                             | TION                                                                                       |                            |       |       |       |      |

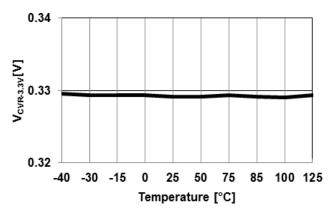

| Reference Voltage at 3.3 V                                                                               | $V_{IN} = 3.3 \text{ V}, V_{CS} = 0 \text{ V}$                                             | V <sub>CVR-3.3V</sub>      | 0.320 | 0.330 | 0.340 | V    |

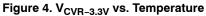

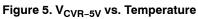

| Reference Voltage at 5.0 V<br>(Power-on reset, default)                                                  | V <sub>IN</sub> = 5.0 V, V <sub>CS</sub> = 0 V                                             | V <sub>CVR-5.0V</sub>      | 0.485 | 0.500 | 0.515 | V    |

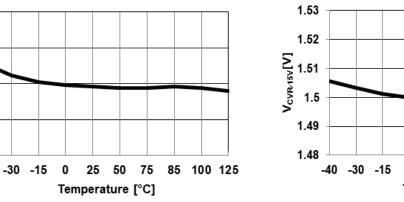

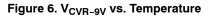

| Reference Voltage at 9 V                                                                                 | $V_{IN}$ = 9 V, $V_{CS}$ = 0 V                                                             | V <sub>CVR-9V</sub>        | 0.873 | 0.900 | 0.927 | V    |

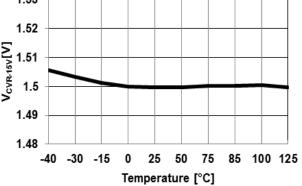

| Reference Voltage at 15 V                                                                                | $V_{IN} = 15 \text{ V}, V_{CS} = 0 \text{ V}$                                              | V <sub>CVR-15V</sub>       | 1.455 | 1.500 | 1.545 | V    |

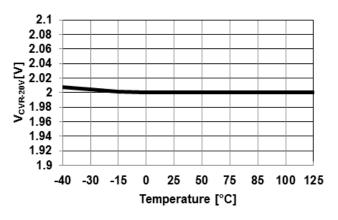

| Reference Voltage at 20 V                                                                                | $V_{IN} = 20 \text{ V}, \text{ V}_{CS} = 0 \text{ V}$                                      | V <sub>CVR-20V</sub>       | 1.940 | 2.000 | 2.060 | V    |

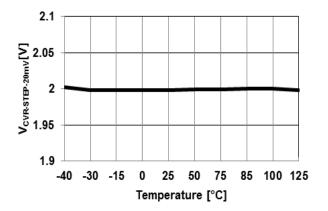

| Reference Voltage of 20 mV step                                                                          | $\Delta V_{\text{IN}}$ = 20 mV, $V_{CS}$ = 0 V                                             | V <sub>CVR-STEP-20mV</sub> | 1.940 | 2.000 | 2.060 | mV   |

| CABLE DROP COMPENSATION SEC                                                                              | ΓΙΟΝ                                                                                       |                            |       |       |       |      |

| Cable Compensation Voltage on V $_{\rm CVR}$ for V $_{\rm OUT}$ = 150 mV/A                               | $R_{CS}$ = 5 m $\Omega$ , $V_{CS}$ = –5 mV or $R_{CS}$ = 10 m $\Omega$ , $V_{CS}$ = –10 mV | V <sub>COMR-CDC</sub>      | 13.5  | 15.0  | 16.5  | mV   |

| FEEDBACK SECTION                                                                                         |                                                                                            |                            |       |       |       |      |

| SFB Pin Maximum Sink Current                                                                             |                                                                                            | I <sub>SFB-Sink-MAX</sub>  | 2     |       |       | mA   |

| BLEEDER SECTION                                                                                          |                                                                                            |                            |       |       |       |      |

| VBUS Leakage Impedance (Note 5)                                                                          |                                                                                            | R <sub>BLD-BUS</sub>       | 100   | 171   | 242   | kΩ   |

| VIN Pin Sink Current when Bleeding<br>(Note 5)                                                           | Bleeding current on VIN at VIN = 20 V                                                      | I <sub>VIN –Sink</sub>     | 300   |       |       | mA   |

| BLD Pin Sink Current when Bleeding (Note 5)                                                              | Bleeding current on BLD at VIN = 20 V                                                      | I <sub>BLD</sub> –Sink     | 250   |       |       | mA   |

| Enable Bleeder Time (Note 5)                                                                             | Disabling OVP & SR Gate.<br>Vstep ≤ 0.5 V, Vbus ≥ 13                                       | t <sub>BLD</sub>           |       | 7     |       | ms   |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions. 5. Guaranteed by Design

#### Table 5. ELECTRICAL CHARACTERISTICS (continued)

$V_{IN}$  = 5 V, LPC = 1.25 V, LPC width = 2 µs at T<sub>J</sub> = -40~125°C, F<sub>LPC</sub> = 100 kHz, unless otherwise specified.

| Parameter                                                                                                    | Test Conditions                                                            | Symbol                     | Min  | Тур  | Мах  | Unit |

|--------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|----------------------------|------|------|------|------|

| BLEEDER SECTION                                                                                              |                                                                            |                            |      |      |      |      |

| Enable Bleeder Time (Note 5)                                                                                 | Disabling OVP & SR Gate.<br>Vstep ≤ 0.5 V, Vbus < 13                       | t <sub>BLD</sub>           |      | 19   |      | ms   |

| Enable Bleeder Time (Note 5)                                                                                 | Disabling OVP & SR Gate.<br>Vstep > 0.5 V, Vbus ≥ 13                       | t <sub>BLD</sub>           |      | 56   |      | ms   |

| Enable Bleeder Time                                                                                          | Disabling OVP & SR Gate.<br>Vstep > 0.5 V, Vbus < 13                       | t <sub>BLD</sub>           | 160  | 200  | 240  | ms   |

| OVER TEMPERATURE PROTECTION                                                                                  | SECTION                                                                    | •                          |      |      | •    |      |

| Current Source on NTC pin                                                                                    | R <sub>par_110</sub> = 3.293 kΩ                                            | I <sub>NTC</sub>           | 55   | 60   | 65   | μA   |

| Debounce Time for Over Temperature<br>Protection (Note 5)                                                    |                                                                            | T <sub>NTC-Debounce</sub>  |      | 77.5 |      | ms   |

| CABLE PROTECTION SECTION                                                                                     |                                                                            |                            |      |      |      |      |

| Delay Time Enabling Pollution<br>Detection after Rd is Detached or after<br>Load Switch is Disabled (Note 5) |                                                                            | <sup>t</sup> POL-EN-Delay  | 9    | 10   | 11   | ms   |

| Debounce Time for Pollution Detection<br>(Note 5)                                                            | $V_{BLD} > V_{POL-TH}$                                                     | t <sub>POL-Debounce</sub>  | 45   | 50   | 55   | ms   |

| Bleeder Enable Time for Pollution<br>Detection (Note 5)                                                      |                                                                            | t <sub>BLD-POL</sub>       | 9    | 10   | 11   | ms   |

| Pollution Detection Current on BLD<br>Pin (Note 5)                                                           |                                                                            | I <sub>POL-DET</sub>       | 350  | 390  | 450  | μΑ   |

| Supply Voltage of Pollution Detection<br>Current (Note 5)                                                    |                                                                            | V <sub>SUP-POL-DET</sub>   | 0.67 | 0.74 | 0.80 | V    |

| Pollution Detection Threshold Level (Note 5)                                                                 | During t <sub>POL-EN</sub> with open-circuited on BLD                      | V <sub>POL-TH</sub>        | 0.50 | 0.60 | 0.65 | V    |

| Guaranteed Pollution Impedance<br>(Note 5)                                                                   |                                                                            | R <sub>POL</sub>           |      |      | 2    | kΩ   |

| PROTECTION OPERATION SPECIFIC                                                                                | ATION SECTION                                                              | •                          |      |      | •    |      |

| Output Voltage Releasing Latch Mode (Note 5)                                                                 | $V_{\text{IN}}$ < $V_{\text{LATCH-OFF}}$ at –5°C and 85°C                  | VLATCH-OFF                 |      |      | 1.55 | V    |

| Time Duration Disabling Load Switch (Note 5)                                                                 |                                                                            | t <sub>TwoSecond</sub> AR. |      | 2    |      | S    |

| TYPE-C SECTION                                                                                               |                                                                            |                            |      |      |      |      |

| 330 $\mu$ A Source Current on CC1 Pin                                                                        | $V_{IN} = 5 V, V_{CC1} = 0 V$                                              | I <sub>P-CC1-330</sub>     | 302  | 330  | 358  | μA   |

| 330 μA Source Current on CC2 Pin                                                                             | $V_{IN} = 5 V, V_{CC2} = 0 V$                                              | I <sub>P-CC2-330</sub>     | 302  | 330  | 358  | μA   |

| Input Impedance on CC1 Pin                                                                                   | $V_{IN}$ = 0 V, Sourcing 330 $\mu A$ on CC1                                | Z <sub>OPEN-CC1</sub>      | 126  |      |      | kΩ   |

| Input Impedance on CC2 Pin                                                                                   | $V_{IN}$ = 0 V, Sourcing 330 $\mu A$ on CC2                                | Z <sub>OPEN-CC2</sub>      | 126  |      |      | kΩ   |

| Rd Impedance Detection Threshold on CC1 Pin                                                                  | $V_{IN}$ = 5 V, $V_{CC2}$ = 0 V, Increasing $V_{CC1}$                      | V <sub>RD-CC1</sub>        | 2.45 | 2.60 | 2.75 | V    |

| Rd Impedance Detection Threshold on CC2 Pin                                                                  | $V_{\text{IN}}$ = 5 V, $V_{\text{CC1}}$ = 0 V, Increasing $V_{\text{CC2}}$ | V <sub>RD-CC2</sub>        | 2.45 | 2.60 | 2.75 | V    |

| UFP Attachment Debounce Time                                                                                 | $V_{IN}$ = 5 V, $V_{CC2}$ = 0 V, Increasing $V_{CC1}$                      | t <sub>CCDebounce</sub>    | 100  | 150  | 200  | ms   |

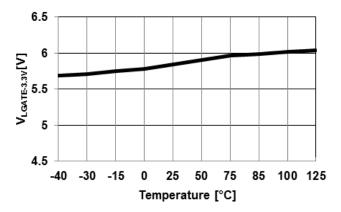

| Gate High Voltage at 3.3 V                                                                                   | V <sub>IN</sub> = 3.3 V                                                    | V <sub>LGATE-3.3V</sub>    | 5.3  |      |      | V    |

| Gate High Voltage at 20 V                                                                                    | V <sub>IN</sub> = 20 V                                                     | V <sub>LGATE-20V</sub>     | 23.5 |      |      | V    |

| Gate High Voltage at V <sub>IN-OVP-Max</sub>                                                                 | V <sub>IN</sub> = V <sub>IN-OVP-Max</sub>                                  | V <sub>LGATE-OVP-Max</sub> |      |      | 31   | V    |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions. 5. Guaranteed by Design

#### Table 5. ELECTRICAL CHARACTERISTICS (continued)

$V_{IN}$  = 5 V, LPC = 1.25 V, LPC width = 2 µs at T<sub>J</sub> = -40~125°C, F<sub>LPC</sub> = 100 kHz, unless otherwise specified.

| Parameter                                                    | Test Conditions                                                                                 | Symbol                       | Min   | Тур   | Мах   | Unit |

|--------------------------------------------------------------|-------------------------------------------------------------------------------------------------|------------------------------|-------|-------|-------|------|

| TYPE-C SECTION                                               | ·                                                                                               |                              |       |       |       |      |

| CC1 Pin Over-Voltage Protection                              |                                                                                                 | V <sub>CC1-OVP</sub>         | 5.5   | 5.75  | 6     | V    |

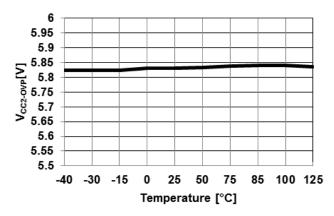

| CC <sub>2</sub> Pin Over–Voltage Protection                  |                                                                                                 | V <sub>CC2-OVP</sub>         | 5.5   | 5.75  | 6     | V    |

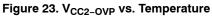

| CC <sub>1</sub> /CC <sub>2</sub> OVP Debounce Time           |                                                                                                 | t <sub>CC-OVP-Debounce</sub> |       |       | 100   | μS   |

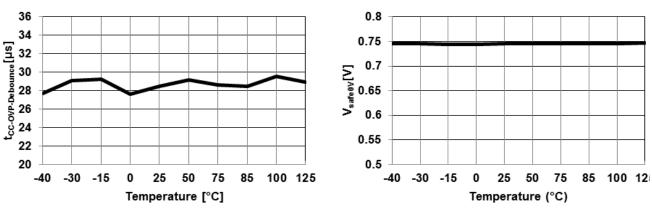

| Safe Operating Voltage at 0 V                                |                                                                                                 | V <sub>safe0V</sub>          | 0.66  | 0.73  | 0.80  | V    |

| OUTPUT DRIVER SECTION                                        | •                                                                                               |                              |       |       |       |      |

| Output Voltage Low                                           | V <sub>IN</sub> = 5 V, I <sub>GATE</sub> = 100 mA                                               | V <sub>OL</sub>              |       |       | 0.25  | V    |

| Output Voltage High                                          | $V_{IN}$ = 3.3 V, $C_{iss}$ = 4.7 nF, $C_p$ = 4.7 nF                                            | V <sub>OH</sub>              | 4.0   |       |       | V    |

| VIN Threshold to Enable Charge<br>Pump (Note 5)              |                                                                                                 | V <sub>CP-EN</sub>           |       | 4.2   |       | V    |

| Rising Time (Note 5)                                         | $V_{\text{IN}}$ = 5 V, $C_{\text{iss}}$ = 4.7 nF, $C_{\text{p}}$ = 4.7 nF GATE = 1 V $\sim$ 4 V | t <sub>R</sub>               |       | 63    |       | ns   |

| Falling Time (Note 5)                                        | $V_{\text{IN}}$ = 5 V, $C_{\text{iss}}$ = 4.7 nF, $C_{p}$ = 4.7 nF GATE = 4 V~ 1 V              | t <sub>F</sub>               |       | 63    |       | ns   |

| Propagation Delay to OUT High<br>(LPC Trigger (Note 5)       | V <sub>IN</sub> =5 V, GATE=1 V                                                                  | t <sub>PD-HIGH-LPC</sub>     |       | 44    |       | ns   |

| Propagation Delay to OUT Low<br>(LPC Trigger (Note 5)        | V <sub>IN</sub> = 5 V, GATE = 4 V                                                               | t <sub>PD-LOW-LPC</sub>      |       | 30    |       | ns   |

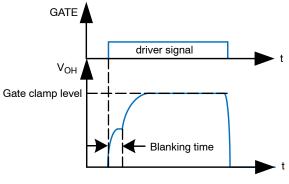

| Gate Inhibit Time (Note 5)                                   |                                                                                                 | t <sub>INHIBIT</sub>         |       | 1.4   |       | μs   |

| INTERNAL RES SECTION                                         | •                                                                                               |                              |       |       |       |      |

| Internal RES Ratio (Note 5)                                  | $V_{IN} = V_{IN-OFF} \sim 20 \text{ V} (N = 6.5 \sim 7.5)$                                      | K <sub>RES</sub>             |       | 0.110 |       | V/V  |

| VIN Dropping Protection Ratio with<br>Two Cycle              | LPC Width = 5 $\mu$ s, V <sub>IN</sub> =5 V to 3.5 V                                            | K <sub>VIN-DROP</sub>        | 60    | 70    | 80    | %    |

| Debounce time for noise immunity on VIN (Note 5)             |                                                                                                 | t <sub>VIN-Debounce</sub>    | 1     | 2     | 3     | μS   |

| Debounce Time for Disable SR when<br>VIN Dropping Protection |                                                                                                 | t <sub>SR_OFF</sub>          | 0     | 6.5   | 13    | ms   |

| LPC SECTION                                                  | ·                                                                                               |                              |       |       |       |      |

| Linear Operation Range of LPC Pin<br>Voltage (Note 5)        | $V_{\text{IN -OFF}} < V_{\text{IN}} \le 5 \text{ V}$                                            | V <sub>LPC</sub>             | 0.4   |       | 3.6   | V    |

| SR Enabled Threshold Voltage<br>@High-Line                   | VLPC-HIGH-H-5V =<br>V <sub>LPC-TH-H-5V</sub> / 0.875                                            | V <sub>LPC-HIGH-H-5</sub> V  | 0.942 | 1.069 | 1.197 | V    |

| SR Enabled Threshold Voltage<br>@High-Line                   | V <sub>LPC-HIGH-H-9</sub> v =<br>V <sub>LPC-TH-H-9</sub> v / 0.875                              | V <sub>LPC-HIGH-H-9</sub> V  | 1.061 | 1.196 | 1.332 | V    |

| SR Enabled Threshold Voltage<br>@High-Line                   | V <sub>LPC-HIGH-H-15V</sub> = V <sub>LPC-TH-</sub><br><sub>H-15V</sub> / 0.875                  | V <sub>LPC-HIGH-H-15</sub> V | 1.245 | 1.433 | 1.541 | V    |

| SR Enabled Threshold Voltage<br>@High-Line                   | V <sub>LPC-HIGH-H-20V</sub> = V <sub>LPC-TH-</sub><br><sub>H-20V</sub> / 0.875                  | V <sub>LPC-HIGH-H-20</sub> V | 1.397 | 1.554 | 1.712 | V    |

| SR Enabled Threshold Voltage @ Low-Line                      | $V_{LPC-HIGH-L-5V} = V_{LPC-TH-L-5V} = 0$                                                       | V <sub>LPC-HIGH-L-5</sub> V  | 0.442 | 0.496 | 0.550 | V    |

| SR Enabled Threshold Voltage @<br>Low-Line                   | $V_{LPC-HIGH-L-9V} = V_{LPC-TH-L-9V} = V_{LPC-TH-L-9V} / 0.875$                                 | V <sub>LPC-HIGH-L-9V</sub>   | 0.561 | 0.584 | 0.685 | V    |

| SR Enabled Threshold Voltage @<br>Low-Line                   | V <sub>LPC-HIGH-L-15V</sub> = V <sub>LPC-TH-</sub><br><sub>L-15V</sub> / 0.875                  | V <sub>LPC-HIGH-L-15V</sub>  | 0.741 | 0.817 | 0.893 | V    |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions. 5. Guaranteed by Design

#### Table 5. ELECTRICAL CHARACTERISTICS (continued)

$V_{IN}$  = 5 V, LPC = 1.25 V, LPC width = 2 µs at T<sub>J</sub> = -40~125°C, F<sub>LPC</sub> = 100 kHz, unless otherwise specified.

| Parameter Test Conditions | Symbol | Min | Тур | Max | Unit |

|---------------------------|--------|-----|-----|-----|------|

|---------------------------|--------|-----|-----|-----|------|

| LPC SECTION                                                 |                                                                                     |                                       |                          |       |       |    |

|-------------------------------------------------------------|-------------------------------------------------------------------------------------|---------------------------------------|--------------------------|-------|-------|----|

| SR Enabled Threshold Voltage @ Low-Line                     | $V_{LPC-HIGH-L-12V} = V_{LPC-TH-L-12V} = 0.875$                                     | V <sub>LPC-HIGH-L-20</sub> V          | 0.897                    | 0.981 | 1.065 | V  |

| Low-to-High Line Threshold Voltage on LPC Pin               | Spec. = (0.70 + 0.02 * V <sub>IN</sub> ) * 2,<br>V <sub>IN</sub> = 5 V              | V <sub>LINE-H-5</sub> V               | 1.46                     | 1.60  | 1.74  | V  |

| High-to-Low Line Threshold Voltage on LPC Pin               | Spec. = (0.65 + 0.02 * V <sub>IN</sub> ) * 2,<br>V <sub>IN</sub> = 5 V              | V <sub>LINE-L-5</sub> V               | 1.37                     | 1.50  | 1.63  | V  |

| Line Change Threshold Hysteresis (Note 5)                   | V <sub>LINE-HYS-5</sub> v =<br>V <sub>LINE-H-5</sub> v - V <sub>LINE-L-5</sub> v    | V <sub>LINE-HYS-5V</sub>              |                          | 0.1   |       | V  |

| Low-to-High Line Threshold Voltage on LPC Pin               | Spec. = (0.70 + 0.02 * V <sub>IN</sub> ) * 2,<br>V <sub>IN</sub> = 9 V              | V <sub>LINE-H-9</sub> V               | 1.62                     | 1.76  | 1.90  | V  |

| High-to-Low Line Threshold Voltage on LPC Pin               | Spec. = (0.65 + 0.02 * V <sub>IN</sub> ) * 2,<br>V <sub>IN</sub> = 9 V              | V <sub>LINE-L-9V</sub>                | 1.53                     | 1.66  | 1.79  | V  |

| Line Change Threshold Hysteresis (Note 5)                   | V <sub>LINE-HYS-9V</sub> =<br>V <sub>LINE-H-9V</sub> - V <sub>LINE-L-9V</sub>       | V <sub>LINE-HYS-9</sub> V             |                          | 0.1   |       | V  |

| Low-to-High Line Threshold Voltage on LPC Pin               | Spec. = (0.70 + 0.02 * V <sub>IN</sub> ) * 2,<br>V <sub>IN</sub> = 15 V             | V <sub>LINE-H-15</sub> V              | 1.85                     | 2.00  | 2.15  | V  |

| High-to-Low Line Threshold Voltage on LPC Pin               | Spec. = (0.65 + 0.02 * V <sub>IN</sub> ) * 2,<br>V <sub>IN</sub> = 15 V             | V <sub>LINE-L-15</sub> V              | 1.76                     | 1.90  | 2.04  | V  |

| Line Change Threshold Hysteresis (Note 5)                   | V <sub>LINE-HYS-15</sub> V =<br>V <sub>LINE-H-15</sub> V - V <sub>LINE-L-15</sub> V | V <sub>LINE-HYS-15</sub> V            |                          | 0.1   |       | V  |

| Low-to-High Line Threshold Voltage on LPC Pin               | Spec. = (0.70 + 0.02 * V <sub>IN</sub> ) * 2,<br>V <sub>IN</sub> = 20 V             | V <sub>LINE-H-20V</sub>               | 2.06                     | 2.20  | 2.34  | V  |

| High-to-Low Line Threshold Voltage on LPC Pin               | Spec. = (0.65 + 0.02 * V <sub>IN</sub> ) * 2,<br>V <sub>IN</sub> = 20 V             | V <sub>LINE-L-20V</sub>               | 1.97                     | 2.10  | 2.23  | V  |

| Line Change Threshold Hysteresis (Note 5)                   | V <sub>LINE-HYS-12V</sub> =<br>V <sub>LINE-H-20V</sub> - V <sub>LINE-L-20V</sub>    | V <sub>LINE-HYS-20V</sub>             |                          | 0.1   |       | V  |

| Higher Clamp Voltage                                        |                                                                                     | V <sub>LPC-CLAMP-H</sub>              | 5.4                      | 6.2   | 7.0   | V  |

| LPC Threshold Voltage to Disable SR Gate Switching          | V <sub>IN</sub> = 5 V. LPC = 3 V↑                                                   | V <sub>LPC-DIS</sub>                  | V <sub>IN</sub> –<br>0.6 |       |       | V  |

| Line Change Debounce Time from<br>Low-Line to High-Line     | Counts for LPC falling < V <sub>LPC-TH-L-5V</sub>                                   | t <sub>LPC-LH-debounce</sub><br>-time | 13                       | 21    | 29    | ms |

| Line Change Debounce from<br>High-Line to Low-Line (Note 5) |                                                                                     | t <sub>LPC-HL-debounce</sub>          |                          | 15    |       | μs |

| INTERNAL TIMING SECTION                                     |                                                                                     |                                       |                          |       |       |    |

| Ratio between V <sub>LPC</sub> & V <sub>RES</sub>  | V <sub>IN</sub> = 5 V, F <sub>LPC</sub> = 50 kHz, K <sub>RES</sub> = 0.11 | Ratio <sub>LPC-RES</sub> | 5.40 | 5.68 | 5.96 |    |

|----------------------------------------------------|---------------------------------------------------------------------------|--------------------------|------|------|------|----|

| Minimum LPC Time to Enable the SR Gate @ High-Line | V <sub>LPC</sub> = 2.5 V                                                  | t <sub>LPC-EN-H</sub>    | 210  | 285  | 360  | ns |

| Minimum LPC Time to Enable the SR Gate @ Low-Line  | V <sub>LPC</sub> = 1.25 V                                                 | t <sub>LPC-EN-L</sub>    | 540  | 705  | 870  | ns |

#### **REVERSE CURRENT MODE SECTION**

| Reverse Current Mode Entry<br>Debounce Time      | $V_{IN} = 5 V, V_{LPC} = 0 V$                 | T <sub>reverse-debounce</sub> | 270 | 400 | 530 | ms |

|--------------------------------------------------|-----------------------------------------------|-------------------------------|-----|-----|-----|----|

| Operating Current during Reverse<br>Current Mode | V <sub>IN</sub> = 5 V, V <sub>LPC</sub> = 0 V | I <sub>OP.reverse</sub>       |     |     | 2.4 | mA |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions. 5. Guaranteed by Design

#### Table 5. ELECTRICAL CHARACTERISTICS (continued)

$V_{IN}$  = 5 V, LPC = 1.25 V, LPC width = 2  $\mu$ s at T<sub>J</sub> = -40~125°C, F<sub>LPC</sub> = 100 kHz, unless otherwise specified.

| Parameter Test Conditions | Symbol | Min | Тур | Мах | Unit |

|---------------------------|--------|-----|-----|-----|------|

|---------------------------|--------|-----|-----|-----|------|

| BMC TRANSMITTER NORMATIVE REQUIREMENTS              |                                                                                                                           |                               |      |      |      |    |  |  |

|-----------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|-------------------------------|------|------|------|----|--|--|

| Unit Internal                                       | 1/fBitRate                                                                                                                | t <sub>UI</sub>               | 3.03 | 3.33 | 3.70 | μs |  |  |

| Rise Time                                           | C <sub>VDD</sub> = 4.7 F                                                                                                  | t <sub>Rise-TX</sub>          | 300  | 500  | 700  | ns |  |  |

| Fall Time                                           | $C_{VDD} = 4.7 \ \mu F$                                                                                                   | t <sub>Fall-TX</sub>          | 300  | 500  | 700  | ns |  |  |

| Transmitter Output Impedance                        | Transmitter output impedance at<br>Niquist frequency of USB2.0 low speed<br>(750 kHz) while Source driving the CC<br>line | zDriver                       | 33   |      | 75   | Ω  |  |  |

| Transitions for Signal Detect                       |                                                                                                                           | n <sub>Transition</sub> Count | 3    |      |      |    |  |  |

| Time Window for Detecting Non-idle                  |                                                                                                                           | t <sub>TransitionWindow</sub> | 12   |      | 20   | μs |  |  |

| Rx bandwidth Limiting Filter<br>(Digital or Analog) |                                                                                                                           | t <sub>RxFilter</sub>         | 100  |      |      | ns |  |  |

| Receiver Input Impedance                            |                                                                                                                           | zBmcRx                        | 1    |      |      | MΩ |  |  |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions. 5. Guaranteed by Design

### **TYPICAL CHARACTERISTICS**

0.91

0.905

0.9

0.895

0.89

-40

V<sub>cvR-9v</sub>[V]

Figure 8. V<sub>CVR-20V</sub> vs. Temperature

Figure 7. V<sub>CVR-15V</sub> vs. Temperature

Figure 9. V<sub>CVR-STEP-20mV</sub> vs. Temperature

#### TYPICAL CHARACTERISTICS (Continued)

-40 -30 -15 0 25 50 75 85 100 125 Temperature [°C]

119

Figure 14. KIN-OVP vs. Temperature

Figure 15. VIN-OVP-MAX vs. Temperature

Temperature [°C]

25

50

75

85

-15

0

#### TYPICAL CHARACTERISTICS (Continued)

1.1

1.05

1

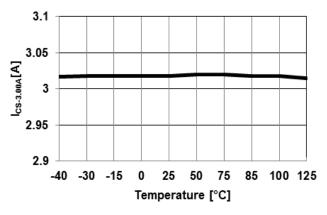

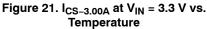

Figure 19.  $I_{CS-3.00A}$  at  $V_{IN}$  = 20 V vs. Temperature

### TYPICAL CHARACTERISTICS (Continued)

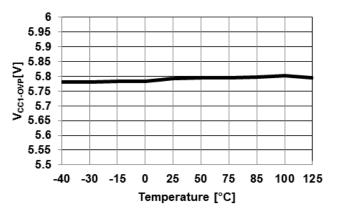

Figure 22. V<sub>CC1-OVP</sub> vs. Temperature

Figure 24. t<sub>CC-OVP</sub>-Debounce vs. Temperature

Figure 25. V<sub>safe0V</sub> vs. Temperature

### **APPLICATIONS INFORMATION**

FAN6390MPX state machine based offers several kinds of trim option to enhance design flexibility as Table 6 shows.

| Function                                       | All Trims                                                                                                                                                                                                                                        | FAN6390MPXMPX Trim                                                                                                                                                                                                                          |

|------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Cable Fault (Note 6)                           | 0: Disabled<br>1: Enabled                                                                                                                                                                                                                        | "1" is selected.<br>"0" is for compliance box test.                                                                                                                                                                                         |

| Internal RES<br>ratio= 1/Ratio <sub>RRES</sub> | 00: 0.14 (for $N_P/N_S = 7.5 \sim 10$ )<br>01: 0.18 (for $N_P/N_S = 9.5 \sim 13$ )<br>10: 0.11 (for $N_P/N_S = 6.5 \sim 7.5$ )<br>11: 0.10 (for $N_P/N_S = 5 \sim 6.5$ )<br>Note: $N_P$ and $N_S$ are primary and<br>secondary transformer turns | "10" is selected.                                                                                                                                                                                                                           |

| Cable Compensation<br>for PDO                  | 00: 150 mV/A<br>01: 50 mV/A<br>10: 100 mV/A<br>11: Disabled                                                                                                                                                                                      | "00" is selected.<br>"11" is used for PD compliance box test that additional cable<br>compensation on DFP is no need.                                                                                                                       |

| Current Sensing                                | 1: 10 mΩ<br>0: 5 mΩ                                                                                                                                                                                                                              | "0" is selected. (Smaller current sensing resistor has better<br>efficiency but could be more expensive. In order to trade off<br>cost and efficiency for flexible design, two kinds of popular<br>current sensing resistors are provided.) |

| Support PD2.0 or 3.0                           | 0: Enable PD2.0<br>1: Enable PD3.0                                                                                                                                                                                                               | "1" is selected. (FAN6390MPX series support only PDO<br>power profile via PD2.0 trim and PDO plus APDO(PPS)<br>power profile via PD3.0 trim.)                                                                                               |

| Default 5 V Adjustment                         | 0: 5.0 V<br>1: 5.2 V                                                                                                                                                                                                                             | "0" is selected. (Two kinds of default 5 V adjustment for flexible design)                                                                                                                                                                  |

| Adjustable Output<br>Profile                   | 8 kinds of output power profile can be se-<br>lectable as list1.                                                                                                                                                                                 | "000" is selected.                                                                                                                                                                                                                          |

| Protection Modes<br>(Note 6)                   | 0: Auto-restart after 2sec<br>1: Latch protection. System re-start up                                                                                                                                                                            | "0" is selected.                                                                                                                                                                                                                            |

| Output OVP                                     | PDO case and PPS case<br>00: 120%<br>01: 125%<br>10: 130%<br>11: 115%                                                                                                                                                                            | "00" is selected.                                                                                                                                                                                                                           |

| Output UVP (Note 7)                            | PDO case:<br>00: 65%<br>01: 60%<br>10: 70%<br>11: Disable<br>PPS case:<br>disable                                                                                                                                                                | "10" is selected.                                                                                                                                                                                                                           |

| PDO Current Mode<br>(Note 8)                   | 00: 5 V (107% CC), 9/15/20 V (120 % CC)<br>01: 5/9/15/20 V (107% CC)<br>10: 5/9/15/20 V (120% CC)                                                                                                                                                | "00" is selected.<br>"10" is used for PD compliance box test.                                                                                                                                                                               |

| Output Power                                   | Output power range from 15 W~60 W<br>000000: 15 W<br>000001: 16 W                                                                                                                                                                                | "111111" is selected.                                                                                                                                                                                                                       |

|                                                | 111111: 60 W                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                             |

Function explanation refers to FAN6390MPX application note.

Based on compliance spec PPS case is current limit. Output voltage could be lower than the requested PPS voltage command during current limit. In order to operate at current limit region, FAN6390MPX series disable UVP and operates until V<sub>IN-OFF</sub>.

Except of PDO, all APDO power profiles are 100% CC.

|                    |                         | Output Profile Trim                    |                              |

|--------------------|-------------------------|----------------------------------------|------------------------------|

| Power Profile Trim | 15 W ≤ P ≤ 27 W         | 27 W < P ≤ 45 W                        | 45 W < P ≤ 60 W              |

| 000                | • 5 V                   | • 5 V                                  | • 5 V                        |

|                    | • 9 V                   | • 9 V                                  | • 9 V                        |

|                    | • 12 V (Note 9)         | • 12 V                                 | • 15 V                       |

|                    | If PD3.0 trim activated | • 15 V                                 | • 20 V                       |

|                    | PPS 5 V                 | If PD3.0 trim activated                | If PD3.0 trim activated      |

|                    | • PPS 9 V               | <ul> <li>PPS 5 V</li> </ul>            | <ul> <li>PPS 9 V</li> </ul>  |

|                    | • FF59V                 |                                        |                              |

|                    |                         | • PPS 9 V                              | • PPS 15 V                   |

|                    |                         | • PPS 15 V                             | • PPS 20 V                   |

| 001                | • 5 V                   | • 5 V                                  | • 5 V                        |

|                    | • 5.5 V                 | • 5.5 V                                | • 5.5 V                      |

|                    | • 6.0 V                 | • 6.0 V                                | • 6.0 V                      |

|                    | • 7.0 V                 | • 7.0 V                                | • 7.0 V                      |

|                    | • 8.0 V                 | • 8.0 V                                | • 9 V                        |

|                    | • 9 V                   | • 9 V                                  | • 15 V                       |

|                    | • 10.0 V                | • 15 V                                 | • 20 V                       |

| 010                |                         |                                        |                              |

| 010                | • 5 V<br>• 6.0 V        | <ul> <li>5 V</li> <li>6.0 V</li> </ul> | • 5 V<br>• 6.0 V             |

|                    | • 7.0 V                 | • 7.0 V                                | • 9 V                        |

|                    |                         |                                        |                              |

|                    | • 8.0 V                 | • 9 V                                  | • 15 V                       |

|                    | • 9 V                   | • 15 V                                 | • 20 V                       |

|                    | If PD3.0 trim activated | If PD3.0 trim activated                | If PD3.0 trim activated      |

|                    | • PPS 5 V               | • PPS 9 V                              | <ul> <li>PPS 15 V</li> </ul> |

|                    | • PPS 9 V               | • PPS 15 V                             | • PPS 20 V                   |

| 011                | • 5 V                   | • 5 V                                  | • 5 V                        |

|                    | • 5.5 V                 | • 5.5 V                                | • 5.5 V                      |

|                    | • 6.0 V                 | • 6.0 V                                | • 6.0 V                      |

|                    | • 6.5 V                 | • 6.5 V                                | • 6.5 V                      |

|                    | • 7.0 V                 | • 7.0 V                                | • 9 V                        |

|                    | • 8.0 V                 | • 9 V                                  | • 15 V                       |

|                    | • 9 V                   | • 15 V                                 | • 20 V                       |

| 100                | • 5V                    | • 5 V                                  | • 5 V                        |

| 100                |                         |                                        | • 5 V<br>• 5.6 V             |

|                    | • 5.6 V                 | • 5.6 V                                |                              |

|                    | • 9 V                   | • 9 V                                  | • 9 V                        |

|                    | • 11 V                  | • 11 V                                 | • 11 V                       |

|                    |                         | • 15 V                                 | • 15 V                       |

|                    |                         |                                        | • 20 V                       |

| 101                | • 5 V                   | • 5 V                                  | • 5 V                        |

|                    | • 9 V                   | • 9 V                                  | • 9 V                        |

|                    | • 14.5 V                | • 14.5 V                               | • 14.5 V                     |

|                    |                         | • 15 V                                 | • 15 V                       |

|                    |                         |                                        | • 20 V                       |

| 110                | • 5 V                   | • 5 V                                  | • 5 V                        |

|                    | • 9 V                   | • 9 V                                  | • 9 V                        |

|                    | • 3 V<br>• 11 V         | • 3 V<br>• 11 V                        | • 3 v<br>• 11 V              |

|                    |                         | • 11 V<br>• 15 V                       | • 15 V                       |

|                    |                         | • 15 V                                 | • 15 V<br>• 20 V             |

| 444                |                         | - 5)/                                  |                              |

| 111                |                         | • 5 V                                  |                              |

|                    |                         | • 9 V                                  |                              |

|                    |                         | • 15 V                                 |                              |

|                    |                         | • 20 V                                 |                              |

### Table 7. UP TO 8 KINDS OF OUTPUT POWER PROFILES SELECTED BY TRIM

9. 12 V can be possible to enable or disable by trim.

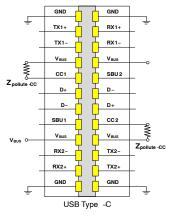

#### USB Type-C Support

The USB Type–C specification defines CC lines (CC1 and CC2) to detect the orientation and roles of a USB Port pair (Source and Sink roles). A source device will provide pull–up currents on the CC lines and the sink will provide a pull–down resistance in order to allow detection of the other when the two are attached. When there is no device attached

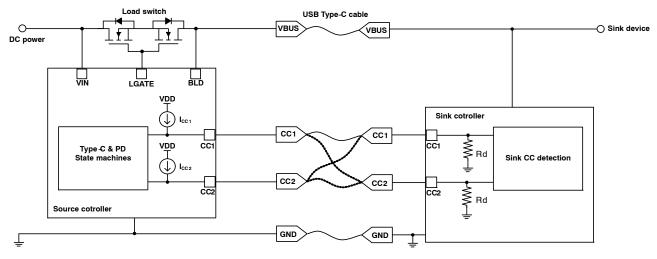

to either the source or sink device, VBUS must not be powered and should be under 0.8 V (Max). The FAN6390MPX operates as a source-only device and provides control of an NMOS load switch to isolate VIN from VBUS to ensure that VBUS can be discharged completely when required.

Figure 26 shows a USB Source connected to a USB Sink with a USB Type–C cable. Since there is only one CC signal in a standard USB Type–C cable, one of pull–ups in the USB Source ( $I_{p-CC1}$  and  $I_{p-CC2}$ ) will be terminated with the Rd to ground in the USB Sink, causing a fixed voltage to be developed across the 5.1 k $\Omega$  pull–down. The FAN6390MPX monitors the CC line voltages to decide if a Sink is attached or not and the orientation of the USB Type–C cable. If the  $V_{Rd}$  voltage is within the attach threshold for t<sub>CCDebounce</sub> according to the thresholds defined in Table 8, the load switch will be enabled to provide vSafe5V on VBUS. The FAN6390MPX advertises support for 3 A current at the vSafe5V output voltage level.

Table 8. CC VOLTAGES ON SOURCE SIDE – 3.0 A @ 5 V

| Detection             | Min Voltage | Max Voltage | Threshold |

|-----------------------|-------------|-------------|-----------|

| Sink (vRd)            | 0.85 V      | 2.45 V      | 2.60 V    |

| No Connect<br>(vOPEN) | 2.75 V      |             |           |

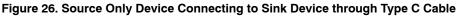

Figure 27 shows the signal levels and timing for a typical USB Type–C attach on CC1. The Source pull–up currents are enabled on both CC1 and CC2 and the USB cable connects the Rd resistor on the CC1 signal in the Sink device which pulls down the CC1 voltage into the vRd range. Once the FAN6390MPX detects the voltage on CC1 within the vRd range for  $t_{CCDebounce}$ , the load switch is enabled and vSafe5V is applied on VBUS.

Figure 27. Attach to Sink Device via USB Type-C Cable

#### **USB PD Support**

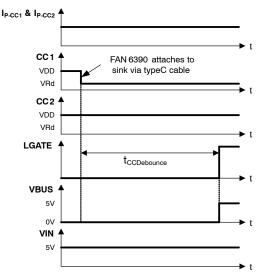

USB Power Delivery (PD) provides a way for a Source and Sink device to negotiate output power settings, allowing for increased power delivery up to 100W. USB PD uses the CC signal that is passed through the USB cable to provide the link between a Source device and a Sink device. In order to communicate properly over the CC signal, all USB PD–capable devices include four major communication components, the Physical Layer, Protocol Layer, Policy Engine and Device Policy Manager as shown in Figure 28.

Figure 28. USB PD Communications Stack

The Physical Layer handles the transmission and reception of the bits on the CC signal. All data is first encoded using a 4b5b line code and then transmitted across the CC signal using Biphase Mark Coding (BMC). A 32-bit CRC is also used to protect the data integrity of the data payload.

The Protocol Layer defines how USB PD messages are constructed and used between a Source device and a Sink device. All USB PD messages must follow a strict packet definition and may also include timing requirements based on the type of message. The Protocol Layer is responsible for verifying the timing parameters and handling any communication errors as they arise.

The Policy Engine is responsible for executing the device Local Policy to control its power delivery behavior. The Policy Engine defines a set of message sequences that must be followed for proper operation. All power negotiations are handled by the Policy Engine.

The Device Policy Manager is responsible for overseeing the power supply and managing changes to the Local Policy, including handling of alert and fault conditions. It is also responsible for the Discover Identity messaging to determine the full capabilities of the cabling.

The FAN6390MPX implements all four components of the Source communication stack in hardware to provide a USB PD 3.0 fully-compliant solution without the need for firmware interaction. Control of the Constant Voltage and Constant Current DAC's is integrated into the Policy Engine to provide seamless power transitions between different contracts.

#### **USB PD Power Profiles**

The USB PD 3.0 specification defines Power Data Objects (PDO) and Augmented Power Data Objects (APDO) as a way for the Source device to advertise its' power capabilities. Power Data Objects are used to describe well-regulated fixed voltage supplies, poorly regulated power supplies and battery supplies that can be directly connected to VBUS. Augmented Power Data Objects are used to describe a power supply whose output voltage can be programmatically adjusted over the advertised voltage range (Programmable Power Supply or PPS). A Source can advertise a combination of PDO's and APDO's, up to a maximum of 7 total Data Objects. In order to provide a consistent experience across Source devices with the same power rating (PDP), a set of Power Rules was introduced into the USB PD 3.0 specification. The Power Rules provide a set of minimum requirements (PDO's and APDO's) that must be met for a Source device based on the advertised PDP.

The FAN6390MPX can be configured to meet a variety of different USB PD Power Profiles, depending on the application requirements. The default power profile option for the FAN6390MPX is the standard 60W option as shown in Table 9.

| Data<br>Object | Output<br>Voltage  | Max<br>Current<br>w/3 A Cable | Current<br>Mode |

|----------------|--------------------|-------------------------------|-----------------|

| PDO1           | 5 V                | 3.21 A                        | OC              |

| PDO2           | 9 V                | 3.6 A                         | OCP             |

| PDO3           | 15 V               | 3.6 A                         | OCP             |

| PDO4           | 20 V               | 3.6 A                         | OCP             |

| APDO1          | 9 V<br>(3.3~11 V)  | 3 A                           | CC              |

| APDO2          | 15 V<br>(3.3~16 V) | 3 A                           | CC              |

| APDO3          | 20 V<br>(3.3~21 V) | 3 A                           | CC              |

Table 9. FAN6390MPX DEFAULT POWER PROFILE

#### **Constant Voltage Control**