# FAN7093 High-Current PN Half-Bridge Driver

#### **Features**

- Path Resistance for a Full-Bridge Configuration: Max. 30.5 mΩ at 150°C

- PWM Capability: > 60 kHz<sup>1</sup> Combined with Active Free Wheeling

- Switched-Mode Current Limitation for Reduced Power Dissipation In Over-Current Condition

- Current Limit Protection: Typ. 43 A

- Independent Current-Sense Output and Diagnostic Flag for High and Low Sides

- Over-Temperature Protection (OTP) with Latch

- Shorted-Load Protection with Latch Behavior

- Over-Voltage Protection (OVP) with Lockout

- Under-Voltage Protection (UVP)

- Logic Level Control Inputs

- Adjustable Slew Rates for Optimized EMI

- Typical Slew Rate of 1 V/µs w ith Open Slew Rate Pin

# **Description**

The FAN7093 is an integrated high-current half-bridge driver for electric motor drive applications. It contains one P-channel high-side MOSFET and one N-channel low-side MOSFET with an integrated control IC in one package. With the P-channel high-side switch, the need for a charge pump is eliminated, which minimizes EMI.

Pins IN and /INH are logic-level inputs and control the half-bridge output. The diagnostic and current sense IS pin outputs a current that is proportional to the current flowing through the half-bridge MOSFETs. The IS pin output represents current for the P-channel or the N-channel, depending on which is active.

The part is protected against a short to battery or ground of the out pin, over-current, over-temperature, over-voltage, and under-voltage conditions. The FAN7093 provides a cost- and space-optimized solution for protected high-current PWM motor drives.

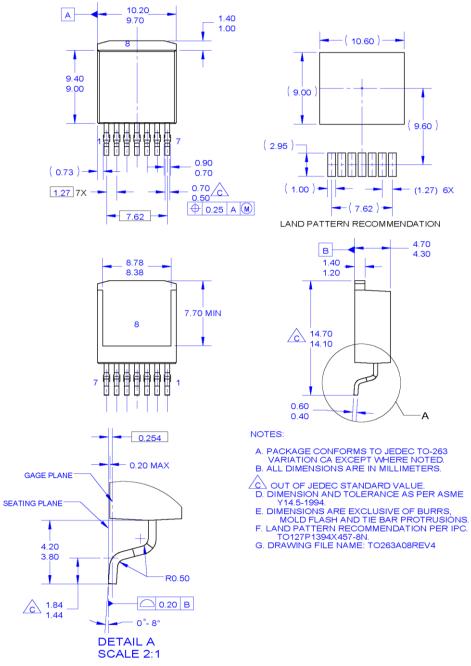

Figure 1. TO263-7L

$<sup>^1</sup>$  The <code>minimum</code> duty cycle is 34% when V  $_{\rm BATT} = 14$  V, R  $_{\rm SR}$  is shorted, and the following parameters are at their typical values: td(ON)Hs, td(ON)Hs, ts(ew(on)Hs, and ts(ew(on)Ls).

## **Ordering Information**

| Part Number  | Operating<br>Temperature Range | Package                                   | Packing<br>Method |

|--------------|--------------------------------|-------------------------------------------|-------------------|

| FAN7093-F085 | -40 to +150°C                  | 8-Lead, TO263, Molded, JEDEC Variation CA | Tape & Reel       |

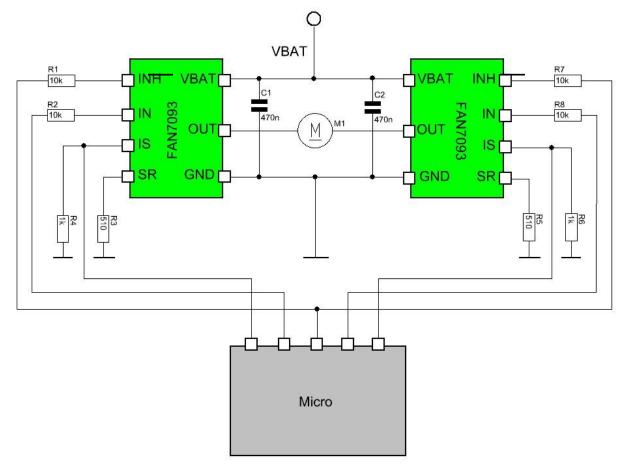

## **Block Diagram**

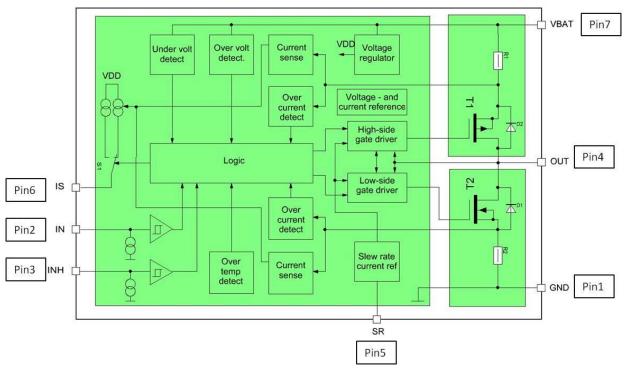

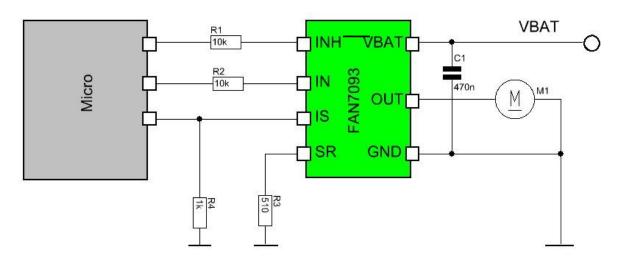

Figure 2. Block Diagram

The FAN7093 is a high-current half-bridge that contains three separate chips in one package: one P-channel high-side MOSFET, one N-channel low-side MOSFET, and with a control IC. All three chips are mounted on one common lead frame, using chip-on-chip and chip-by-chip technologies. The power MOSFETs are vertical MOS transistors to ensure minimum on-state resistance.

Using a P-channel high-side switch eliminates a charge pump and reduces EMI. A microcontroller is able to control the logic level inputs of IN and /INH of the half-bridge. The diagnostic pin IS is a current output stage that delivers a proportional current through the P-channel and N-channel MOSFETS, depending on which is being activated, with the IN or /INH pin forcing

conditions. In case of a short to VBATT or ground, the IS pin acts as an error flag. The error flag can be detected as a logic HIGH level through an attached microcontroller. In an over-current situation, the control IC turns off the MOSFETs and tries to turn them back on after a cool down time of 140 µs (typical). The control IC protects the MOSFETs against over-voltage, under-voltage, and over-temperature conditions. The dead time, to prevent shoot-through between the P- and N-channel MOSFET, is also generated by the control IC. The slew rate of the outputs can be adjusted through an external resistor connected to the SR pin. The FAN7093 can be combined with another FAN7093 to form a full-bridge drive. Multiple FAN7093 can be combined in full-or half-bridge three-phase drive configurations.

# **Pin Configuration**

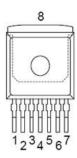

Figure 3. Pin Assignments

## **Pin Definitions**

| Pin  | Symbol                           | I/O | Function                                                                                                                               |

|------|----------------------------------|-----|----------------------------------------------------------------------------------------------------------------------------------------|

| 1    | GND <sup>(1)</sup>               |     | Ground                                                                                                                                 |

| 2    | IN                               | I   | Input. Defines whether the high-side (HS) or low-side (LS) switch is activated.                                                        |

| 3    | 3 /INH I                         |     | Inhibit. When set to LOW, the device enters Sleep Mode and resets Over-<br>Temperature Protection (OTP) and the HS and LS short latch. |

| 4, 8 | OUT <sup>(1)</sup>               | 0   | Pow er output of the bridge                                                                                                            |

| 5    | SR                               | I   | Slew rate. The slew rate of the powerswitches can be adjusted by connecting a resistor between the SR and GND pins.                    |

| 6    | IS                               | 0   | Current sense and diagnostics                                                                                                          |

| 7    | V <sub>BATT</sub> <sup>(1)</sup> |     | Supply                                                                                                                                 |

#### Note:

1. This pin needs power wiring.

Table 1. Truth Table

| Device State                            | /INH | IN   | HS  | LS  | IS   | Mode                                                                                                 |

|-----------------------------------------|------|------|-----|-----|------|------------------------------------------------------------------------------------------------------|

|                                         | LOW  | Х    | OFF | OFF | LOW  | Standby Mode                                                                                         |

| Normal Operation                        | HIGH | LOW  | OFF | ON  | CS   | LS Active                                                                                            |

|                                         | HIGH | HIGH | ON  | OFF | CS   | HS Active                                                                                            |

| Over-Voltage<br>louт ≤ lcp              | Х    | Х    | ON  | OFF | HIGH | Shutdown of LS, HS Activated, Error Detected                                                         |

| Over-Voltage<br>lout > lcp              | Х    | Х    | OFF | OFF | HIGH | Shutdown of LS, HS Error Detected Reset with/INH HIGH to LOW to HIGH when condition no longer exists |

| Under-Voltage                           | Х    | Х    | OFF | OFF | LOW  | UV Lockout                                                                                           |

| Over-Temperature or<br>Shorted LS or HS | LOW  | Х    | OFF | OFF | LOW  | Standby Mode, Reset of Latch                                                                         |

| Over-Temperature or Shorted LS or HS    | HIGH | Х    | OFF | OFF | HIGH | Shutdow n w ith Latch, Error Detected                                                                |

| Current Limit                           | HIGH | HIGH | OFF | ON  | HIGH | Switched Mode, Error Detected <sup>(2)</sup>                                                         |

| Odiront Limit                           | HIGH | LOW  | ON  | OFF | HIGH | Sw itched Mode, Error Detected <sup>(2)</sup>                                                        |

#### Notes:

- 2. Device resumes normal operation after  $t_{\text{CLS}}$ . The error signal is reset after 2 x  $t_{\text{CLS}}$ .

- 3. X=Don't care input and CS=Current Sense Mode status flag.

## **Absolute Maximum Ratings**

Stresses exceeding the absolute maximum ratings may damage the device. The device may not function or be operable above the recommended operating conditions and stressing the parts to these levels is not recommended. In addition, extended exposure to stresses above the recommended operating conditions may affect device reliability. The absolute maximum ratings are stress ratings only.  $T_J = -40^{\circ}\text{C}$  to  $+150^{\circ}\text{C}$ ; all voltages with respect to ground, and positive current flowing into pin (unless otherwise specified).

| Symbol                                     | Parameter                                    | Condition                                 | Min. | Тур.   | Max. | Unit |

|--------------------------------------------|----------------------------------------------|-------------------------------------------|------|--------|------|------|

| V <sub>BATT</sub>                          | Supply Voltage <sup>(4)</sup>                |                                           | -0.3 |        | 45   | V    |

| V <sub>IN</sub> /V <sub>INH</sub>          | Logic Input Voltage <sup>(4)</sup>           |                                           | -0.3 |        | 45   | V    |

| V <sub>SR</sub>                            | Voltage at SR Pin <sup>(4)</sup>             |                                           | -0.3 |        | 1.5  | V    |

| V <sub>IS</sub>                            | Voltage at IS Pin <sup>(4)</sup>             |                                           | -0.3 |        | 7.5  | V    |

| I <sub>D(HS)</sub> ,<br>I <sub>D(LS)</sub> | HS/LS Continuous Drain Current (4,5)         | T <sub>C</sub> < 85°C                     |      | -46/46 |      | Α    |

| I <sub>D(HS),</sub><br>I <sub>D(LS)</sub>  | HS/LS Pulsed Drain Current (4,5)             | $T_C$ < 85°C Single Pulse < 5 $\mu$ s     |      | -90/90 |      | Α    |

| I <sub>D(HS)</sub> ,<br>I <sub>D(LS)</sub> | HS/LS PWM Current <sup>(4,5)</sup>           | T <sub>C</sub> < 125°C f=1 kHz,<br>DC=50% |      | -55/55 |      | А    |

| Tempera                                    | tures                                        |                                           |      |        |      |      |

| TJ                                         | Junction Temperature <sup>(4)</sup>          |                                           | -40  |        | 150  | °C   |

| T <sub>STG</sub>                           | Storage Temperature (4)                      |                                           | -55  |        | 150  | °C   |

| Electrost                                  | atic Discharge Capability (ESD)              |                                           | -    |        |      |      |

| ESD                                        | Human Body Model, JESD22-A114 <sup>(6)</sup> | IN, /INH, SR, IS                          | -2   |        | 2    | kV   |

| LOD                                        | Human Body Wodel, JESD22-A114                | OUT, GND, VBATT                           | -6   |        | 6    | I NV |

#### Notes:

- 4. Not subject to production testing, specified by design.

- 5. Maximum reachable current may be smaller, depending on current-limit level.

- 6. ESD susceptibility, HBM according to AEC-Q100-0042 / JESD22-A114-B (1.5 k $\Omega$ , 100 pF).

# **Recommended Operating Conditions**

The Recommended Operating Conditions table defines the conditions for actual device operation. Recommended operating conditions are specified to ensure optimal performance to the datasheet specifications. On Semiconductor does not recommend exceeding them or designing to Absolute Maximum Ratings.

| Symbol                 | Parameter                                                                                                                                  | Condition                                            | Min. | Тур. | Max. | Unit |

|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|------|------|------|------|

| V <sub>BATT(NOM)</sub> | Supply Voltage Range for Nominal Operation                                                                                                 |                                                      | 7    |      | 18   | V    |

| V <sub>BATT(EXT)</sub> | Supply Voltage Range for Extended Operation                                                                                                | Parameter<br>Deviations<br>Possible                  | 5.5  |      | 28.0 | V    |

| TJ                     | Junction Temperature                                                                                                                       |                                                      | -40  |      | 150  | °C   |

| OJC(LS)                | Thermal Resistance, Junction-Case, Low-Side Sw itch $\Theta_{JC(LS)} = \Delta T_J$ (LS) / $P_V$ (LS) (Error!Reference source not found)    |                                                      |      | 0.8  |      | °C/W |

| Θ <sub>JC(HS)</sub>    | Thermal Resistance, Junction-Case, High-Side Sw itch $\Theta_{JC(HS)}=\Delta T_J$ (HS) $/$ P $_V$ (HS) (Error! Reference source not found) |                                                      |      | 0.45 |      | °C/W |

| Өда                    | Thermal Resistance Junction-Ambient (Error! Reference source not found.)                                                                   | Using Pad Area of<br>One Square Inch<br>of Two-Ounce |      | 40   |      | °C/W |

|           |                  |                   |           | Copper |  |  |

|-----------|------------------|-------------------|-----------|--------|--|--|

| Note:     |                  |                   |           | •      |  |  |

| Not subje | ct to production | n test; specified | by design |        |  |  |

|           |                  |                   |           |        |  |  |

|           |                  |                   |           |        |  |  |

|           |                  |                   |           |        |  |  |

|           |                  |                   |           |        |  |  |

|           |                  |                   |           |        |  |  |

|           |                  |                   |           |        |  |  |

|           |                  |                   |           |        |  |  |

|           |                  |                   |           |        |  |  |

|           |                  |                   |           |        |  |  |

|           |                  |                   |           |        |  |  |

|           |                  |                   |           |        |  |  |

|           |                  |                   |           |        |  |  |

|           |                  |                   |           |        |  |  |

|           |                  |                   |           |        |  |  |

|           |                  |                   |           |        |  |  |

|           |                  |                   |           |        |  |  |

|           |                  |                   |           |        |  |  |

|           |                  |                   |           |        |  |  |

|           |                  |                   |           |        |  |  |

|           |                  |                   |           |        |  |  |

|           |                  |                   |           |        |  |  |

|           |                  |                   |           |        |  |  |

|           |                  |                   |           |        |  |  |

|           |                  |                   |           |        |  |  |

|           |                  |                   |           |        |  |  |

|           |                  |                   |           |        |  |  |

|           |                  |                   |           |        |  |  |

|           |                  |                   |           |        |  |  |

|           |                  |                   |           |        |  |  |

|           |                  |                   |           |        |  |  |

|           |                  |                   |           |        |  |  |

|           |                  |                   |           |        |  |  |

|           |                  |                   |           |        |  |  |

|           |                  |                   |           |        |  |  |

|           |                  |                   |           |        |  |  |

|           |                  |                   |           |        |  |  |

|           |                  |                   |           |        |  |  |

|           |                  |                   |           |        |  |  |

|           |                  |                   |           |        |  |  |

|           |                  |                   |           |        |  |  |

|           |                  |                   |           |        |  |  |

|           |                  |                   |           |        |  |  |

|           |                  |                   |           |        |  |  |

|           |                  |                   |           |        |  |  |

|           |                  |                   |           |        |  |  |

|           |                  |                   |           |        |  |  |

|           |                  |                   |           |        |  |  |

|           |                  |                   |           |        |  |  |

|           |                  |                   |           |        |  |  |

|           |                  |                   |           |        |  |  |

|           |                  |                   |           |        |  |  |

|           |                  |                   |           |        |  |  |

#### Electrical Characteristics

Unless otherwise specified,  $V_{BATT} = 7 \text{ V}$  to 18 V,  $T_{J} = -40 ^{\circ}\text{C}$  to +150  $^{\circ}\text{C}$ ,  $I_{L} = 0 \text{ A}$ , all voltages with respect to ground, and positive current flowing into pin.

| Symbol                 | Parameter         | Condition                                                                                              | Min. | Тур. | Max. | Unit |

|------------------------|-------------------|--------------------------------------------------------------------------------------------------------|------|------|------|------|

| IV <sub>BATT(ON)</sub> | Supply Current    | $V_{\text{INH}}$ =5 V, $V_{\text{IN}}$ =5 V, $R_{\text{SR}}$ =0 $\Omega$ , DC-Mode, No Fault Condition |      |      | 5.0  | mA   |

| V <sub>BATT(OFF)</sub> | Quiescent Current | $V_{INH}=0 V, V_{IN}=0 V$                                                                              |      |      | 450  | μΑ   |

# **Power Stage Characteristics**

The power stages of the FAN7093 consist of a P-channel vertical DMOS transistor for the high-side switch and an N-channel vertical DMOS transistor for the low-side switch. All protection and diagnostic functions are located in the control die. Both switches can be operated up to 60 kHz<sup>2</sup>, allowing active freewheeling and minimizing power dissipation in the forward operation of the integrated diodes.

The on-state resistance, R<sub>DS(ON)</sub>, is dependent on the supply voltage V<sub>BATT</sub> as well as on the junction temperature, T<sub>J</sub>.

## Power Stages — Static Characteristics

Unless otherwise specified,  $V_{BATT}$ =7 V to 18 V,  $T_{J}$ =-40°C to +150°C, all voltages with respect to ground, and positive current flowing into pin.

| Symbol                  | Parameter                                    | Condition                                                       | Min. | Тур. | Max. | Unit |

|-------------------------|----------------------------------------------|-----------------------------------------------------------------|------|------|------|------|

| High-Side S             | Switch                                       |                                                                 | •    |      |      |      |

| R <sub>DS(ON)_</sub> HS | On-State High-Side Resistance                | I <sub>OUT</sub> =-20 A; V <sub>BATT</sub> =14 V <sup>(8)</sup> |      |      | 12.3 | mΩ   |

| ILEAK(HS)               | Leakage Current                              | V <sub>INH</sub> =0 V, V <sub>OUT</sub> =0 V                    |      |      | 50   | μΑ   |

| V <sub>RDF</sub>        | Reverse Diode Forward-Voltage <sup>(9)</sup> | I <sub>OUT</sub> =-9 A                                          |      |      | 1.5  | V    |

| Low-Side S              | witch                                        | •                                                               | •    |      | •    |      |

| R <sub>DS(ON)</sub> _LS | On-State Low-Side Resistance                 | I <sub>OUT</sub> =20 A; V <sub>BATT</sub> =14 V <sup>(8)</sup>  |      |      | 18.2 | mΩ   |

| Leak(LS)                | Leakage Current                              | V <sub>INH</sub> =0 V, V <sub>OUT</sub> =V <sub>BATT</sub>      |      |      | 10   | μΑ   |

|                         | Reverse Diode Forward-Voltage <sup>(9)</sup> | I <sub>OUT</sub> =9 A                                           |      |      | -1.5 | V    |

#### Notes:

notes

- Specified R<sub>DS(ON)</sub> value is related to normal soldering points; R<sub>DS(ON)</sub> values are specified for FAN7093-F085: pin 1,7 to pin 8 (tab, backside).

- Due to active freew heeling, the diode is conducting only for a few µs, depending on the value of the external R<sub>SR</sub> resistor.

$<sup>^2</sup>$  The *minimum* duty cycle is 34% when V<sub>BATT</sub>=14 V, R<sub>SR</sub> is shorted and the following parameters are at their typical values:  $t_{d(ON)HS}$ ,  $t_{Slew(on)HS}$ ,  $t_{Slew(on)HS}$ , and  $t_{Slew(on)LS}$ .

# **Switching Times**

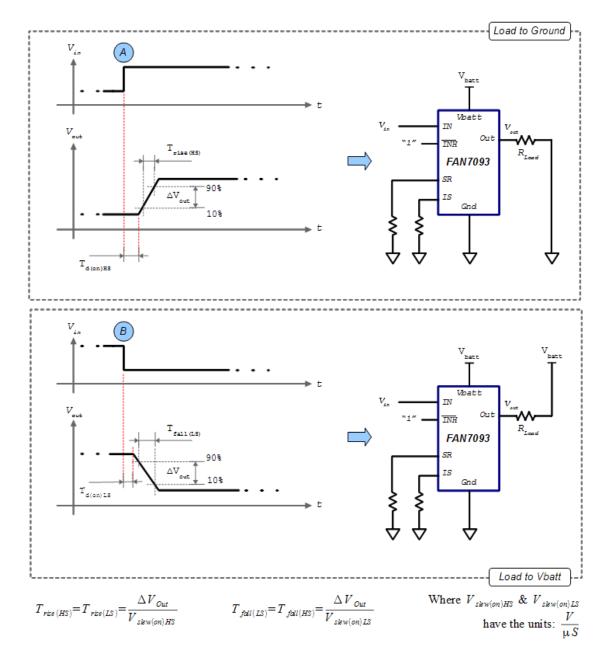

Due to the timing differences for the rising and the falling edges, there is a slight difference between the length of the input pulse and the length of the output pulse, as shown in Figure 4.

Figure 4. Timing Diagrams

# **Power Stages - Dynamic Characteristics**

Unless otherwise specified;  $V_{BATT}$ =7 V - 14 V,  $T_{J}$ =-40°C to +150°C,  $R_{L}$ =2  $\Omega$ , /INH HIGH, all voltages with respect to ground, and positive current flowing into pin.

| Symbol                   | Parameter Condition       |                                                                                         | Min. | Тур. | Max. | Unit  |

|--------------------------|---------------------------|-----------------------------------------------------------------------------------------|------|------|------|-------|

| High-Side Swi            | tch Dynamic Character     | istics                                                                                  |      |      |      |       |

|                          |                           | R <sub>SR</sub> =0Ω                                                                     | 15   | 19   | 24   |       |

| V <sub>Slew(ON)</sub> HS | Slew Rate <sup>(10)</sup> | R <sub>SR</sub> =5.1 kΩ                                                                 | 12   | 15   | 17   | V/µs  |

| v Siew(ON)HS             | Olew Trate                | R <sub>SR</sub> =51 kΩ                                                                  | 5    | 6    | 7    | ν/μ3  |

|                          |                           | R <sub>SR</sub> =Open, R <sub>L</sub> to GND                                            | 0.8  | 1.0  | 1.2  |       |

| t <sub>d(ON)</sub> HS    | Turn-On Delay             | /INH High; IN LOW to HIGH;<br>OUT with RL to GND (see Figure<br>4 top)                  | 0.45 | 2.10 | 4.20 | μs    |

| Low-Side Swi             | tch Dynamic Characteri    | stics                                                                                   |      |      |      |       |

|                          |                           | R <sub>SR</sub> =0Ω                                                                     | 18   | 21   | 24   |       |

| Var. (avv.)              | Slew Rate <sup>(10)</sup> | R <sub>SR</sub> =5.1 kΩ                                                                 | 13   | 17   | 19   | \//uc |

| V <sub>Slew(ON)LS</sub>  | Siew Rate                 | R <sub>SR</sub> =51 kΩ                                                                  | 5    | 7    | 7    | V/µs  |

|                          |                           | R <sub>SR</sub> =Open, R <sub>L</sub> to VBATT                                          | 0.8  | 1.2  | 1.2  |       |

| t <sub>d(ON)</sub> LS    | Turn-On Delay             | /INH HIGH; IN HIGH to LOW;<br>OUT with RL to V <sub>BATT</sub> (see<br>Figure 4 bottom) | 0.45 | 2.10 | 4.20 | μs    |

#### Note:

10. Not production tested.

#### **Protection Functions**

The device provides several integrated protection functions designed to prevent IC damage in fault conditions. Fault conditions are considered as "outside" the normal operating range. Protection functions are not for continuous or repetitive operation, with the exception of current-limit protection. In a fault condition, the FAN7093 applies the highest slew rate possible, independent of the connected slew rate resistor (RsR). Over-voltage, over-temperature, and over-current situations are indicated by a fault current flag  $I_{\rm IS(LIM)}$  at the IS pin. The following describes the protection functions in order of priority. Over-voltage protection overrides all other protections.

## Over-Voltage Protection (OVP)

To ensure a high immunity against over-voltage conditions like load dump, the device turns off the low-side MOSFET and turns on the high-side MOSFET when the supply voltage exceeds the over-voltage protection level  $V_{\rm OV(OFF)}.$  The control IC returns to normal operation  $t_{\rm lock}\!\!=\!\!140~\mu s$  (Typ.) after the supply voltage decreases below the over-voltage lockout level,  $V_{\rm OV(ON)}.$  In H-bridge configurations, this behavior leads to freew heeling in the high side during over-voltage condition. If the load current exceeds  $l_{\rm CP}$  in over-voltage lockout, the IC turns off the high-side driver and latches this state. See Table 1, which shows the condition of the IS pin flag. This state can be reset (if the conditions no longer exist) when /INH goes from HIGH to LOW to HIGH again.

#### **Under-Voltage Protection (UVP)**

To avoid uncontrolled motion; for example, a driven motor at low voltages; the control IC turns off all MOSFETS when the supply voltage drops below the turn-off voltage,  $V_{\rm UV(OFF)}.$  The control IC resumes to normal operation when the supply voltage rises above the turn-on voltage  $V_{\rm UV(ON)}.$  Notice that the IS pin does NOT flag this fault condition.

#### Over-Temperature Protection (OTP)

The FAN7093 is protected against over-temperature by an integrated temperature sensor in the control IC. Over-temperature protection turns off both output stages. This state is latched until the device is reset by a LOW signal with a minimum pulse length of  $t_{\rm reset}$  at the /INH pin, assuming the control IC temperature decreased by at least the thermal hysteresis. Repetitive use of the over-temperature protection decreases product life.

#### **Current Limitation**

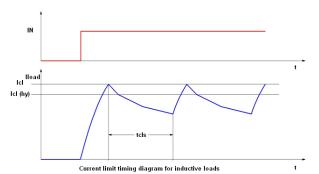

The current is measured in both MOSFETS. As soon as the current reaches the limit  $l_{CL}$ , the low-side or high-side MOSFET is deactivated and the other MOSFET activated for  $t_{CLS}$ . During that time, changes at the IN pin are ignored. The /INH pin can still be used to turn off both MOSFETs. After  $t_{CLS}$ , the MOSFETS return to their initial setting. The error signal at the IS pin is reset after 2 x  $\underline{t}_{CLS}$ . Unintentional triggering of the current-limit circuitry through short current spikes (e.g. inflicted by EMI coming from a motor) is suppressed by an internal filter. Reaction delay of the filter circuitry affects the current limit level  $l_{CL}$ , depending on slew rate of the load current dl/dt.

Figure 5. Current Limitation Timing Diagram (Inductive Load)

In combination with a typical inductive load, such as a motor, this results in a switched-mode current limitation. This method of limiting current has the advantage of greatly reduced power dissipation compared to driving the MOSFET in linear mode. Therefore, it is possible to use the current limitation for a short time without exceeding the maximum allowed junction temperature (e.g. for limiting the inrush current during motor startup). However, regular use of the current limitation is only allowed as long as the specified maximum junction temperature is exceeded. Exceeding not temperature reduces the life of the device.

#### **Short-Circuit Protection (SCP)**

The device is short-circuit protected against:

- Output Shorted to Ground

- Output Shorted to Battery Voltage

- Short-Circuit between the Load Connections

The short-circuit protection is a combination of current limit and over-temperature shutdown of the device.

# **Electrical Characteristics - Protection Functions**

Unless otherwise specified;  $V_{BATT}=7~V$  to 18 V,  $T_{J}=-40^{\circ}C$  to +150°C, all voltages with respect to ground, and positive current flowing into pin.

| Curra la a l           | Down water                                                              | Condition                    | Liı  | l lmi4 |      |      |

|------------------------|-------------------------------------------------------------------------|------------------------------|------|--------|------|------|

| Symbol                 | Parameter                                                               | Condition                    | Min. | Тур.   | Max. | Unit |

| Under-Voltag           | e Shutdown                                                              |                              | l    | 1      |      |      |

| V <sub>UV(ON)</sub>    | Turn-Off Voltage                                                        | V <sub>BATT</sub> Increasing |      |        | 5.6  | V    |

| V <sub>UV(OFF)</sub>   | Turn-On Voltage                                                         | V <sub>BATT</sub> Decreasing | 4.9  |        |      | V    |

| V <sub>UV(HY)</sub>    | Hysteresis                                                              |                              |      | 0.15   |      | V    |

| Over-Voltage           | Lockout                                                                 |                              |      |        |      |      |

| V <sub>OV(ON)</sub>    | Turn-Off Voltage                                                        | V <sub>BATT</sub> Decreasing | 28   |        |      | V    |

| V <sub>OV(OFF)</sub>   | Turn-On Voltage                                                         | V <sub>BATT</sub> Increasing | 27   |        | 35   | V    |

| V <sub>OV(HY)</sub>    | Hysteresis                                                              |                              |      | 1.0    |      | V    |

| t <sub>lock</sub>      | Lockout Time                                                            |                              |      | 140    |      | μs   |

| Current Limit          | ation                                                                   | •                            |      |        |      |      |

| lcL                    | Current Limit Detection Level High and Low Side                         |                              | 35   | 43     | 55   | А    |

| lcp                    | Peak Current Limit Detection Level<br>High and Low Side <sup>(11)</sup> |                              | 72   | 88     | 105  | А    |

| Current Limit          | ation Timing                                                            | •                            | •    | •      | •    | •    |

| t <sub>CLS</sub>       | Shut-Off Time for HS and LS                                             |                              | 100  | 150    | 200  | μs   |

| Thermal Shut           | down                                                                    | •                            | •    | •      | •    | •    |

| T <sub>SD(SENSE)</sub> | Turn-Off Temperature Sense                                              |                              | 170  |        | 190  | °C   |

| T <sub>SD(SENSE)</sub> | Turn-On Temperature Sense                                               |                              | 150  |        | 170  | °C   |

| T <sub>SD(HYS)</sub>   | Thermal Hysteresis                                                      |                              |      | 15     |      | K    |

| t <sub>reset</sub>     | Reset Pulse at /INH Pin (/INH LOW)                                      |                              | 4    |        |      | μs   |

#### Note:

11. Not production tested; specified by design.

## **Control and Diagnostics**

#### **Input Circuit**

The internal gate drivers for the MOSFETS are controlled through inputs IN and /INH and are TTL / CMOS-compatible Schmitt triggers with hysteresis. Setting the /INH pin to HIGH enables the device. In this condition, one of the two power MOSFETS turn on, depending on the input level of the IN pin. To deactivate both switches, the /INH pin must be set LOW. No external driver is needed. The FAN7093 can interface directly with a microcontroller as long as the maximum ratings are not exceeded.

#### **Dead-Time Generation**

The dead time is generated on the control IC to prevent shoot-through between the power MOSFETS. The dead-time is independent of the selected slew rate to reach a high PWM frequency of 60 kHz.

#### Adjustable Slew Rate

To optimize electromagnetic emission (EMI), the switching speed of the MOSFETs is adjustable by an external resistor. The slew rate pin, SR, allows designers to optimize the balance between emission and power dissipation within the application by connecting an external resistor  $R_{SR}$  to GND. If the SR pin is open by design or if intermittent disconnect occurs, the slew rate is set to the value shown in the Power Stages - Dynamic Characteristics table.

# Status Flag Diagnostic with Current-Sense Capability

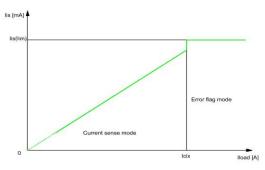

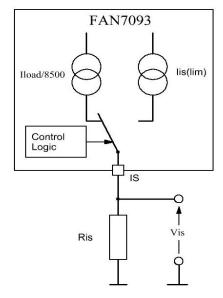

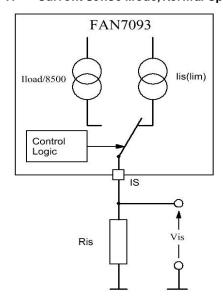

The status pin, IS, is used as a combined current sense and error flag output. In normal operation (Current-Sense Mode), a current source in the control IC is connected to the status pin, which delivers a current proportional to the forward load current flowing through the active high-side or low-side MOSFET. Current flow in the reverse direction cannot be detected except for a marginal leakage current IIS(LK). External resistor RIS determines the voltage per output current. The current-sense ratio value is shown in the Electrical Characteristics - Control and Diagnostics table. In case of a fault condition, the status output is connected to a current source independent of the load current and provides IIS(Iim). The maximum voltage at the IS pin is determined by the choice of the external resistor and the supply voltage. When in a current-limit condition,  $I_{\text{IS(lim)}}$ , is active for a time 2 x  $t_{\text{CLS}}$ ; the flag indicates the error for time t<sub>CL</sub> after the condition no longer exists, but constantly stays active as long as the current-limit condition exists.

Figure 6. Sense Current vs. Load Current and Flag Current

Figure 7. Current Sense Mode, Normal Operation

Figure 8. Error Flag Mode, Fault Condition

# **Electrical Characteristics - Control and Diagnostics**

Unless otherwise specified,  $V_{BATT}$ =7V to 18V,  $T_{J}$ =-40 °C to +150 °C, all voltages with respect to ground, positive current flowing into pin.

| Symbol                 | Parameter                                                                            | Condition                                                                                | Min. | Тур. | Max. | Unit |

|------------------------|--------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|------|------|------|------|

| $V_{INXL}$             | Low Level Voltage, /INH, IN                                                          |                                                                                          | 1.5  |      |      | V    |

| V <sub>INXH</sub>      | High Level Voltage, /INH, IN                                                         |                                                                                          |      |      | 3.5  | V    |

| V <sub>INXH(HYS)</sub> | Input Voltage Hysteresis                                                             |                                                                                          | 500  |      |      | mV   |

| linxh                  | Input Current High Level                                                             | V <sub>INH</sub> =V <sub>IN</sub> =0.4 V to 5.3 V                                        | 20   |      | 80   | μA   |

|                        | Current Sense Ratio in Static on-<br>Condition KILIS=I <sub>L</sub> /I <sub>IS</sub> | R <sub>IS</sub> =800 Ω                                                                   | 4.5  | 8.5  | 13.5 |      |

| KILIS                  |                                                                                      | L=8 A to 50 A                                                                            |      |      |      | 10³  |

|                        |                                                                                      | L=1.1 A to 8 A                                                                           | 3.5  |      |      |      |

| I <sub>IS(LIM)</sub>   | Maximum Analog Sense Current                                                         | R <sub>IS</sub> =800 Ω                                                                   | 4.5  |      | 5.5  | mA   |

| IS(FAULT)              | Sense Current in Fault Condition (12)                                                | R <sub>IS</sub> =800 Ω                                                                   | 5.5  |      | 7.0  | mA   |

| V <sub>IS(FAULT)</sub> | Maximum IS Output Voltage                                                            | R <sub>IS</sub> ≥ 3 kΩ                                                                   |      |      | 7.5  | V    |

| ISLEAK                 | Isense Leakage Current                                                               | /INH HIGH, IN=X, IL=0 A                                                                  |      |      | 300  | μA   |

| t <sub>SET</sub>       | Settling time <sup>(12,13)</sup>                                                     | Resistive Load,<br>V <sub>BATT</sub> =14 V, I <sub>L</sub> =3 A, /INH<br>HIGH, SR to GND |      |      | 4    | μs   |

#### Notes:

- 12. Not subject to production test; specified by design.

- 13. The settling time is from when IN transitions 0 to 1 (the low-side goes OFF and the high-side goes ON) and 1 to 0 (the high-side goes OFF and the low-side goes ON) to when V<sub>(IS)</sub> reaches 90% of its final value.

# **Application Information**

Figure 9. Full-Bridge Motor Application

Figure 10. Half-Bridge Motor Application

# **Physical Dimensions**

Figure 11. 8-Lead, TO263, Molded, JEDEC Variation CA

Package drawings are provided as a service to customers considering ON Semiconductor components. Drawings may change in any manner without notice. Please note the revision and/or date on the drawing and contact a ON Semiconductor representative to verify or obtain the most recent revision. Package specifications do not expand the terms of ON Semiconductor 's worldwide terms and conditions, specifically the warranty therein, which covers ON Semiconductor products.

ON Semiconductor and the ON Semiconductor logo are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON Semiconductor, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by ON Semiconductor. "Typical" parameters which may be provided in ON Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights nor the rights of others. ON Semiconductor products are not designed, intended, or authorized use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold ON Semiconductor and its officers, employees,

#### **PUBLICATION ORDERING INFORMATION**

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor 19521 E. 32nd Pkwy, Aurora, Colorado 80011 USA Phone: 303-675-2175 or 800-344-3860 Toll Free USA/Canada Fax: 303-675-2176 or 800-344-3867 Toll Free USA/Canada Email: orderlit@onsemi.com

N. American Technical Support: 800-282-9855 Toll Free USA/Canada.

Europe, Middle East and Africa Technical Support:

Phone: 421 33 790 2910 **Japan Customer Focus Center** Phone: 81-3-5817-1050 ON Semiconductor Website:  $\underline{www.onsemi.com}$

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative

# **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Gate Drivers category:

Click to view products by ON Semiconductor manufacturer:

Other Similar products are found below:

89076GBEST 00053P0231 56956 57.404.7355.5 LT4936 57.904.0755.0 5882900001 00600P0005 00-9050-LRPP 00-9090-RDPP

5951900000 01-1003W-10/32-15 0131700000 00-2240 LTP70N06 LVP640 5J0-1000LG-SIL LY1D-2-5S-AC120 LY2-US-AC240 LY3UA-DC24 00576P0020 00600P0010 LZN4-UA-DC12 LZNQ2M-US-DC5 LZNQ2-US-DC12 LZP40N10 00-8196-RDPP 00-8274-RDPP

00-8275-RDNP 00-8722-RDPP 00-8728-WHPP 00-8869-RDPP 00-9051-RDPP 00-9091-LRPP 00-9291-RDPP 0207100000 0207400000

01312 0134220000 60713816 M15730061 61161-90 61278-0020 6131-204-23149P 6131-205-17149P 6131-209-15149P 6131-218-17149P

6131-220-21149P 6131-260-2358P 6131-265-11149P