**ON Semiconductor**

Is Now

# Onsemi

To learn more about onsemi<sup>™</sup>, please visit our website at <u>www.onsemi.com</u>

onsemi and ONSEMI. and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. onsemi reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product factures, availability, functionality, or suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using onsemi products, including compliance with all laws, regulations and asfety requirements or standards, regardless of any support or applications information provided by onsemi. "Typical" parameters which may be provided in onsemi data sheets and/or by customer's technical experts. onsemi products and actal performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. onsemi products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use onsemi products for any such unintended or unauthorized application, Buyer shall indemnify and hold onsemi and its officers, employees, subsidiari

# FDMF3039 – Smart Power Stage (SPS) Module

# Features

- Supports PS4 Mode for IMVP-8

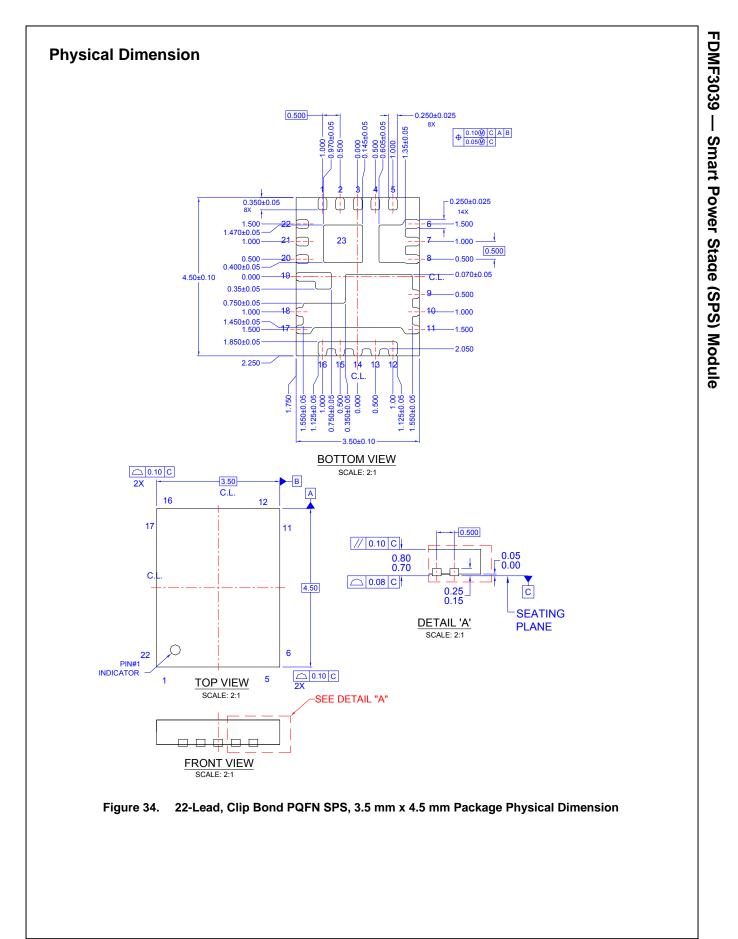

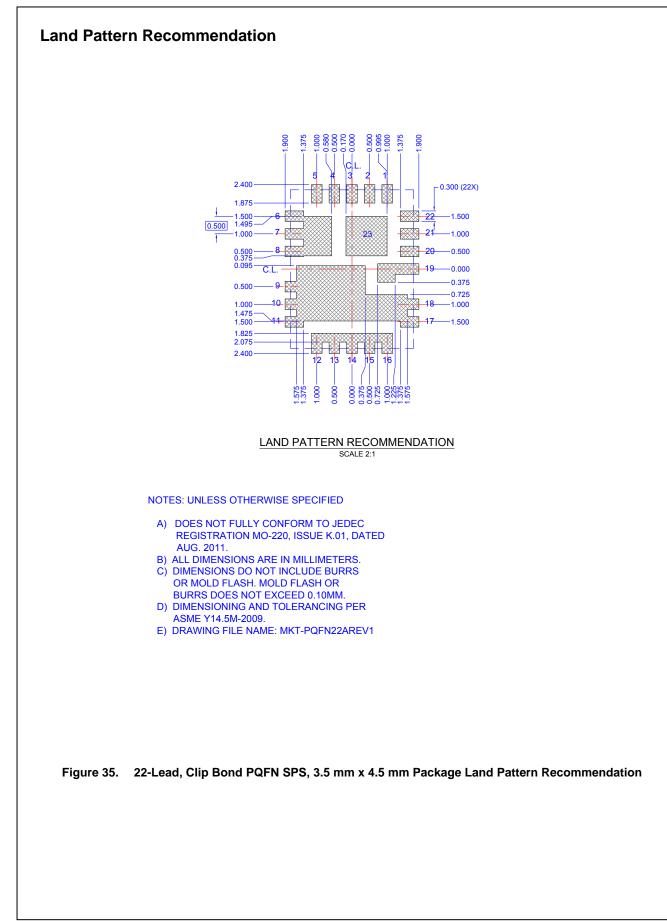

- Ultra-Compact 3.5 mm x 4.5 mm PQFN Copper-Clip Package with Flip Chip Low-Side MOSFET

- High Current Handling: 30 A, 35 A at 10 ms Peak

- 3-State 5 V PWM Input Gate Driver

- Low Shutdown Current: I<sub>VCC</sub> < 6 μA</p>

- Diode Emulation for Enhanced Light-Load Efficiency

- ON Semiconductor PowerTrench<sup>®</sup> MOSFETs for Clean Voltage Waveforms and Reduced Ringing

- ON Semiconductor SyncFET™ Technology (Integrated Schottky Diode) in Low-Side MOSFET

- Integrated Bootstrap Schottky Diode

- Optimized Dead-Times

- Under-Voltage Lockout (UVLO) on VCC

- Optimized for Switching Frequencies up to 1.5 MHz

- Operating Junction Temperature Range: -40°C to +125°C

- ON Semiconductor Green Packaging and RoHS Compliance

# Description

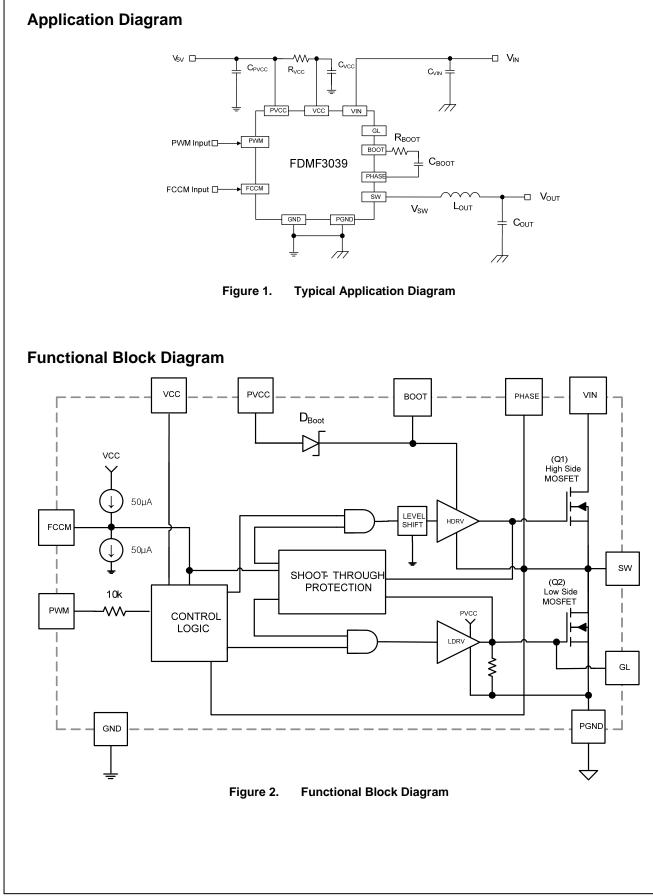

The SPS family is ON Semiconductor's fully optimized, ultra-compact, integrated MOSFET plus driver power stage solution for high-current, high-frequency, synchronous buck, DC-DC applications. The FDMF3039 integrates a driver IC with a bootstrap Schottky diode and two power MOSFETs into a thermally enhanced, ultra-compact 3.5 mm x 4.5 mm package.

With an integrated approach, the SPS switching power stage is optimized for driver and MOSFET dynamic performance, minimized system inductance, and power MOSFET  $R_{DS(ON)}$ . The SPS family uses ON Semiconductor's high-performance PowerTrench<sup>®</sup> MOSFET technology, which reduces switch ringing, eliminating the need for a snubber circuit in most buck converter applications.

A driver IC with reduced dead times and propagation delays further enhances the performance. The FDMF3039 supports diode emulation (using FCCM pin) for improved light-load efficiency. The FDMF3039 also provides a 3-state 5 V PWM input for compatibility with a wide range of PWM controllers.

# Applications

- Notebook, Tablet PC and Ultrabook

- Servers and Workstations, V-Core and Non-V-Core DC-DC Converters

- Desktop and All-in-One Computers, V-Core and Non-V-Core DC-DC Converters

- High-Current DC-DC Point-of-Load Converters

- Small Form-Factor Voltage Regulator Modules

## Ordering Information

| Part Number | <b>Current Rating</b> | Package                                              | Top Mark |

|-------------|-----------------------|------------------------------------------------------|----------|

| FDMF3039    | 30 A                  | 22-Lead, Clip Bond PQFN SPS, 3.5 mm x 4.5 mm Package | FDMF3039 |

August 2017

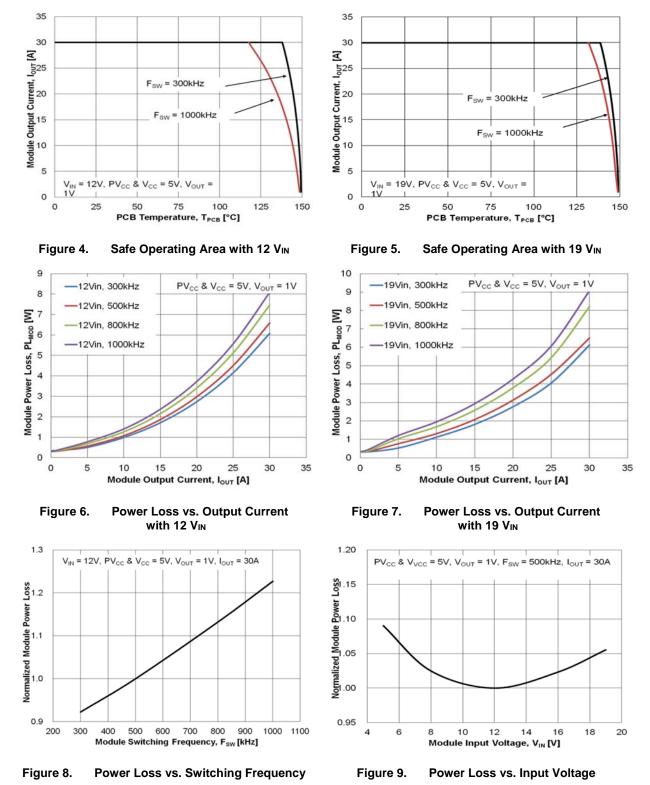

# **Pin Definitions**

| Pin #              | Name  | Description                                                                                                                                                                                                                                                                         |

|--------------------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                  | FCCM  | The FCCM pin enables or disables Diode Emulation. When FCCM is LOW, diode emulation is allowed. When FCCM is HIGH, continuous conduction mode is forced. High impedance on the input of FCCM will shut down the driver IC (and module).                                             |

| 2                  | VCC   | Power supply input for all analog control functions; this is the "quiet" Vcc                                                                                                                                                                                                        |

| 3                  | N.C.  | No connect                                                                                                                                                                                                                                                                          |

| 4                  | BOOT  | Supply for high-side MOSFET gate driver. A capacitor from BOOT to PHASE supplies the charge to turn on the N-channel high-side MOSFET. During the freewheeling interval (LS MOSFET on), the high side capacitor is recharged by an internal diode connected to PVCC. <sup>(1)</sup> |

| 5                  | PHASE | Return connection for the boot capacitor                                                                                                                                                                                                                                            |

| 6~8, 25            | VIN   | Power input for the power stage                                                                                                                                                                                                                                                     |

| 9~11,<br>17,18, 26 | PGND  | Power return for the power stage                                                                                                                                                                                                                                                    |

| 12~16              | SW    | Switching node junction between high and low side MOSFETs; also the input into both the gate driver SW node comparator and the ZCD comparator                                                                                                                                       |

| 19, 24             | GL    | Low-side MOSFET gate monitor                                                                                                                                                                                                                                                        |

| 20, 23             | GND   | Analog ground for analog portions of the IC and for substrate.                                                                                                                                                                                                                      |

| 22                 | PWM   | PWM input to the gate driver IC                                                                                                                                                                                                                                                     |

#### Note:

1. LS = Low Side.

FDMF3039 — Smart Power Stage (SPS) Module

# **Absolute Maximum Ratings**

Stresses exceeding the Absolute Maximum Ratings may damage the device. The device may not function or be operable above the recommended operating conditions and stressing the parts to these levels is not recommended. In addition, extended exposure to stresses above the recommended operating conditions may affect device reliability. The absolute maximum ratings are stress ratings only.  $T_A = T_J = 25^{\circ}C$

| Symbol                 |                                                                               | Parameter                                   |         |                      |      |

|------------------------|-------------------------------------------------------------------------------|---------------------------------------------|---------|----------------------|------|

| Vcc                    | Supply Voltage                                                                | Referenced to GND                           | -0.3    | 7.0                  | V    |

| PVcc                   | Drive Voltage                                                                 | Referenced to GND                           | -0.3    | 7.0                  | V    |

| VPWM                   | PWM Signal Input                                                              | Referenced to GND                           | -0.3    | Vcc+0.3              | V    |

| V <sub>FCCM</sub>      | Skip Mode Input                                                               | Referenced to GND                           | -0.3    | V <sub>CC</sub> +0.3 | V    |

| V <sub>GL</sub>        | Low Gate Manufacturing Test                                                   | Referenced to PGND (DC)                     | GND-0.3 | Vcc+0.3              | V    |

| VGL                    | Pin                                                                           | Referenced to PGND (AC < 20 ns, 10 µJ)      | GND-0.3 | V <sub>CC</sub> +0.3 | V    |

| Vin                    | Dower Input                                                                   | Referenced to PGND                          | -0.3    | 30.0                 | v    |

| VIN                    | Power Input                                                                   | Referenced to PGND (AC < 100 ns)            | -0.3    | 33.0                 |      |

| VPHASE                 |                                                                               | Referenced to PGND (DC)                     | -0.3    | 30.0                 | v    |

| Vsw                    | PHASE and SW                                                                  | Referenced to PGND (AC < 20 ns, 10 $\mu$ J) | -8.0    | 30.0                 |      |

| \/                     | Bootstrap Supply                                                              | Referenced to GND (DC)                      | -0.3    | 33.0                 | V    |

| Vвоот                  |                                                                               | Referenced to GND (AC < 20 ns)              | -0.3    | 36.0                 |      |

| VBOOT-                 |                                                                               | DC                                          | -0.3    | 7.0                  | V    |

| PHASE                  | Boot to PHASE Voltage                                                         | AC < 20 ns, 10 μJ                           | -0.3    | 9.0                  | V    |

| I <sub>O(AV)</sub> (2) | Output Current                                                                | fsw=300 kHz, VIN=12 V, VOUT=1 V             |         | 30                   | Α    |

| IO(AV)'∠'              | Output Current                                                                | fsw=1000 kHz, VIN=12 V, VOUT=1 V            |         | 25                   |      |

| Өл-с                   | Junction-to-Case Thermal Resi                                                 | stance                                      |         | 3                    | °C/W |

| θј-рсв                 | Junction-to-PCB Thermal Resistance (under ON Semiconductor SPS Thermal Board) |                                             |         | 5                    | °C/W |

| TA                     | Ambient Temperature Range                                                     |                                             | -40     | +125                 | °C   |

| TJ                     | Maximum Junction Temperature                                                  |                                             |         | +150                 | °C   |

| T <sub>STG</sub>       | Storage Temperature Range                                                     |                                             | -55     | +150                 | °C   |

| ESD                    | Electrostatic Discharge                                                       | Human Body Model, JESD22-A114               |         | 1.5                  | kV   |

| ESD                    | Protection                                                                    | Charged Device Model, JESD22-C101           |         | 2.5                  | κv   |

Note:

I<sub>O(AV)</sub> is rated with testing ON Semiconductor's SPS evaluation board at T<sub>A</sub> = 25°C with natural convection cooling. This rating is limited by the peak SPS temperature, T<sub>J</sub> = 150°C, and varies depending on operating conditions and PCB layout. This rating may be changed with different application settings.

# **Recommended Operating Conditions**

The Recommended Operating Conditions table defines the conditions for actual device operation. Recommended Operating Conditions are specified to ensure optimal performance to the datasheet specifications. ON Semiconductor does not recommend exceeding them or designing to Absolute Maximum Ratings.

| Symbol | Parameter                         |        | Тур. | Max.    | Unit |

|--------|-----------------------------------|--------|------|---------|------|

| Vcc    | Control Circuit Supply Voltage    |        | 5.0  | 5.5     | V    |

| PVcc   | Gate Drive Circuit Supply Voltage |        | 5.0  | 5.5     | V    |

| VIN    | Output Stage Supply Voltage       | 4.5(3) | 12.0 | 24.0(4) | V    |

Notes:

<sup>3.</sup>  $3.0 \text{ V} \text{ V}_{\text{IN}}$  is possible according to the application condition.

<sup>4.</sup> Operating at high V<sub>IN</sub> can create excessive AC voltage overshoots on the SW-to-GND and BOOT-to-GND nodes during MOSFET switching transient. For reliable SPS operation, SW to GND and BOOT to GND must remain at or below the Absolute Maximum Ratings in the table above.

# **Electrical Characteristics**

Typical value is under V<sub>IN</sub>=12 V, V<sub>CC</sub>=PV<sub>CC</sub>=5 V and T<sub>A</sub>=T<sub>J</sub>=+ 25°C unless otherwise noted. Minimum / Maximum values are under V<sub>IN</sub>=12 V, V<sub>CC</sub>=PV<sub>CC</sub>=5 V  $\pm$  10% and T<sub>J</sub>=T<sub>A</sub>=-40 ~ 125°C unless otherwise noted.

| Symbol             | Parameter                                                         | Condition                                                                                                       | Min.                | Тур.                 | Max. | Unit |

|--------------------|-------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|---------------------|----------------------|------|------|

| Basic Opera        | tion                                                              |                                                                                                                 |                     |                      | 1    |      |

| Icc_sd             | Quiescent Current with PWM<br>and FCCM Pin Floating<br>(PS4 Mode) | Icc=Ivcc + I <sub>PVCC</sub> , PWM=Floating,<br>FCCM=Floating (Non-Switching)                                   |                     | 3                    | 10   | μA   |

| Ісс_нідн           | Quiescent Current with PWM<br>Pin Floating and $V_{FCCM} = 5 V$   | Icc=Ivcc + IPVCC, PWM=Floating,<br>FCCM=5 V                                                                     |                     | 80                   |      | μA   |

| Icc_low            | Quiescent Current with PWM<br>Pin Floating and $V_{FCCM} = 0 V$   | Icc=Ivcc + I <sub>PVCC</sub> , PWM=Floating,<br>FCCM=0 V                                                        |                     | 120                  |      | μA   |

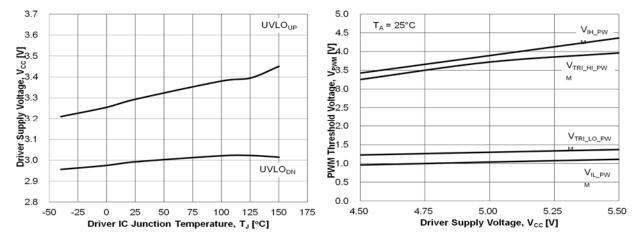

| VUVLO_RISE         | UVLO Rising Threshold                                             | Vcc Rising                                                                                                      |                     | 3.4                  | 3.9  | V    |

| VUVLO_FALL         | UVLO Falling Threshold                                            | Vcc Falling                                                                                                     | 2.5                 | 3.0                  |      | V    |

| t <sub>D_POR</sub> | POR Delay to Enable IC                                            | Vcc UVLO Rising to Internal PWM<br>Enable                                                                       |                     |                      | 15   | μs   |

| FCCM Input         |                                                                   |                                                                                                                 |                     |                      |      |      |

| Ігссм_нідн         | Pull-Up Current                                                   | VFCCM=5 V                                                                                                       |                     | 50                   |      | μA   |

| IFCCM_LOW          | Pull-Down Current                                                 | VFCCM=0 V                                                                                                       |                     | -50                  |      | μA   |

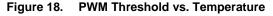

| VIH_FCCM           | FCCM High Level Input<br>Voltage                                  | V <sub>CC</sub> =PV <sub>CC</sub> =5 V                                                                          | 3.8                 |                      |      | V    |

| VTRI_FCCM          | FCCM 3-State Window                                               | Vcc=PVcc=5 V                                                                                                    | 2.2                 |                      | 2.8  | V    |

| VIL_FCCM           | FCCM Low Level Input Voltage                                      | Vcc=PVcc=5 V                                                                                                    |                     |                      | 1.0  | V    |

| tps_exit           | PS4 Exit Latency                                                  | Vcc=PVcc=5 V                                                                                                    |                     |                      | 15   | μs   |

| PWM Input          | •                                                                 |                                                                                                                 |                     |                      |      |      |

| PWM_HIGH           | Pull-Up Current                                                   | V <sub>FCCM</sub> =5 V                                                                                          |                     | 250                  |      | μA   |

| PWM_LOW            | Pull-Down Current                                                 | V <sub>FCCM</sub> =0 V                                                                                          |                     | -250                 |      | μA   |

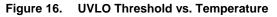

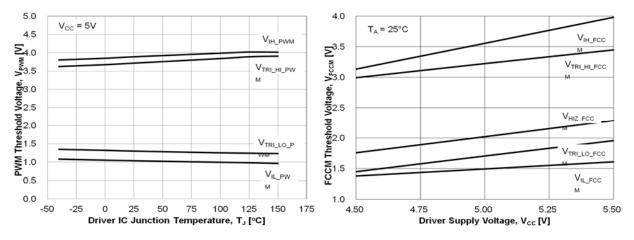

| VIH_PWM            | PWM High Level Input Voltage                                      | Vcc=PVcc=5 V                                                                                                    | 4.1                 |                      |      | V    |

| Vtri_pwm           | PWM 3-State Window                                                | Vcc=PVcc=5 V                                                                                                    | 1.6                 |                      | 3.4  | V    |

| VIL_PWM            | PWM Low Level Input Voltage                                       | V <sub>CC</sub> =PV <sub>CC</sub> =5 V                                                                          |                     |                      | 0.7  | V    |

| td_hold-off        | 3-State Shut-off Time                                             | V <sub>CC</sub> =PV <sub>CC</sub> =5 V, T <sub>J</sub> =25°C                                                    | 100                 | 175                  | 250  | ns   |

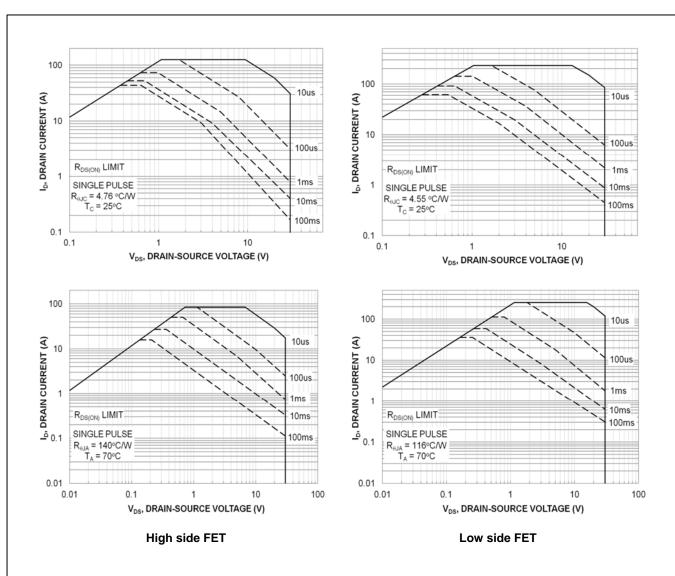

| PWM Propag         | gation Delays & Dead Times (Vແ                                    | N=12 V, Vcc=PVcc=5 V, fsw=1 MHz, lout                                                                           | =10 A, <sup>·</sup> | T <sub>A</sub> =25°C | ;)   |      |

| tpd_phgll          | PWM HIGH Propagation Delay                                        | PWM Going HIGH to GL Going LOW,<br>VIH_PWM to 90% GL                                                            | 14                  | 22                   | 31   | ns   |

| tpd_plghl          | PWM LOW Propagation Delay                                         | $\begin{array}{l} PWM \mbox{ Going LOW to GH Going LOW,} \\ V_{IL\_PWM} \mbox{ to 90\% GH} \end{array}$         | 12                  | 22                   | 32   | ns   |

| tpd_phghh          | PWM HIGH Propagation Delay<br>(FCCM Held LOW)                     | PWM Going HIGH to GH Going HIGH,<br>V <sub>IH_PWM</sub> to 10% GH (FCCM=LOW,<br>I <sub>L</sub> =0, Assumes DCM) | 31                  | 43                   | 54   | ns   |

| <b>t</b> PD_TSGHH  | Exiting 3-State Propagation<br>Delay                              | PWM (from 3-State) Going HIGH to GH Going HIGH, VIH_PWM to 10% GH                                               | 31                  | 41                   | 50   | ns   |

| <b>t</b> PD_TSGLH  | Exiting 3-State Propagation<br>Delay                              | PWM (from 3-State) Going LOW to GL<br>Going HIGH, VIL_PWM to 10% GL                                             | 16                  | 25                   | 33   | ns   |

| td_deadon          | LS Off to HS On Adaptive<br>Dead Time                             | SW <= -0.2 V with GH <=10%, PWM<br>Transition LOW to HIGH                                                       | 9                   | 17                   | 25   | ns   |

| td_deadoff         | HS Off to LS On Adaptive<br>Dead Time                             | SW <= -0.2 V with GL <=10%, PWM<br>Transition HIGH to LOW                                                       | 8.5                 | 19                   | 35   | ns   |

Note:

5. GH = Gate High, internal gate pin of the high-side MOSFET.

Continued on the following page...

# **Electrical Characteristics**

Typical value is under V<sub>IN</sub>=12 V, V<sub>CC</sub>=PV<sub>CC</sub>=5 V and T<sub>A</sub>=T<sub>J</sub>=+ 25°C unless otherwise noted. Minimum / Maximum values are under V<sub>IN</sub>=12 V, V<sub>CC</sub>=PV<sub>CC</sub>=5 V  $\pm$  10% and T<sub>J</sub>=T<sub>A</sub>=-40  $\sim$  125°C unless otherwise noted.

| Symbol                 | Parameter                               | Condition                                | Min. | Тур. | Max. | Unit |

|------------------------|-----------------------------------------|------------------------------------------|------|------|------|------|

| High-Side D            | river (HDRV, $V_{CC} = PV_{CC} = 5 V$ ) | •                                        |      |      | •    |      |

| R <sub>SOURCE_GH</sub> | Output Impedance, Sourcing              | Source Current=100 mA                    |      | 1.0  | 2.5  | Ω    |

| ISOURCE_GH             | Output Sourcing Peak Current            | GH=2.5 V                                 |      | 2    |      | Α    |

| R <sub>SINK_GH</sub>   | Output Impedance, Sinking               | Sink Current=100 mA                      |      | 1.0  | 2.5  | Ω    |

| I <sub>SINK_GH</sub>   | Output Sinking Peak Current             | GH=2.5 V                                 |      | 4    |      | Α    |

| t <sub>R_GH</sub>      | GH Rise Time                            | GH=10% to 90%, C <sub>LOAD</sub> =3.0 nF |      | 10   |      | ns   |

| tF_GH                  | GH Fall Time                            | GH=90% to 10%, C <sub>LOAD</sub> =3.0 nF |      | 6    |      | ns   |

| Low-Side Dr            | iver (LDRV, Vcc = PVcc = 5 V)           | •                                        |      |      |      |      |

| RSOURCE_GL             | Output Impedance, Sourcing              | Source Current=100 mA                    |      | 1.0  | 2.5  | Ω    |

| ISOURCE_GL             | Output Sourcing Peak Current            | GL=2.5 V                                 |      | 2    |      | Α    |

| Rsink_gl               | Output Impedance, Sinking               | Sink Current=100 mA                      |      | 0.5  |      | Ω    |

| ISINK_GL               | Output Sinking Peak Current             | GL=2.5 V                                 |      | 4    |      | Α    |

| t <sub>R_GL</sub>      | GL Rise Time                            | GL=10% to 90%, CLOAD=3.8 nF              |      | 15   |      | ns   |

| t⊧_g∟                  | GL Fall Time                            | GL=90% to 10%, CLOAD=3.8 nF              |      | 7    |      | ns   |

| Boot Diode             | •                                       | ·                                        |      |      |      |      |

| VF                     | Forward-Voltage Drop                    | I <sub>F</sub> =10 mA                    |      | 0.7  |      | V    |

| VR                     | Breakdown Voltage                       | I <sub>R</sub> =1 mA                     | 30   |      |      | V    |

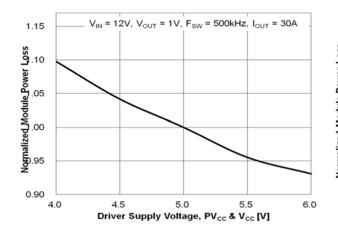

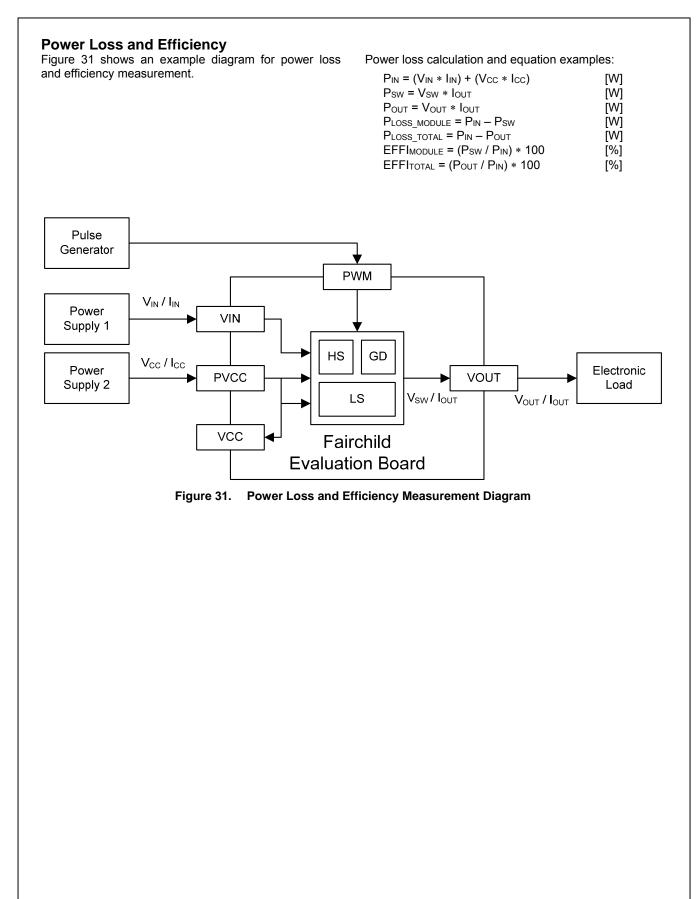

# Typical Performance Characteristics

Test Conditions:  $V_{IN}$ =12 V,  $V_{CC}$ =P $V_{CC}$ =5 V,  $V_{OUT}$ =1 V,  $L_{OUT}$ =250 nH,  $T_A$ =25°C and natural convection cooling, unless otherwise noted.

© 2016 Semiconductor Components Industries, LLC. FDMF3039 • Rev. 2

7

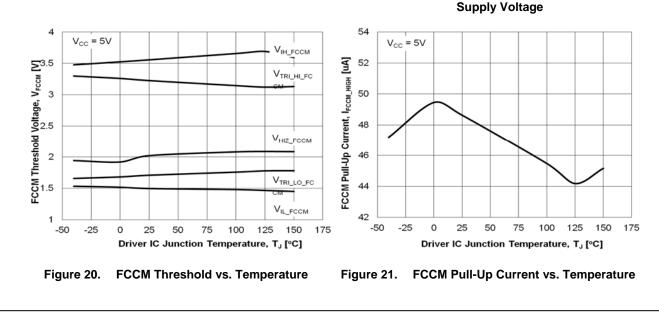

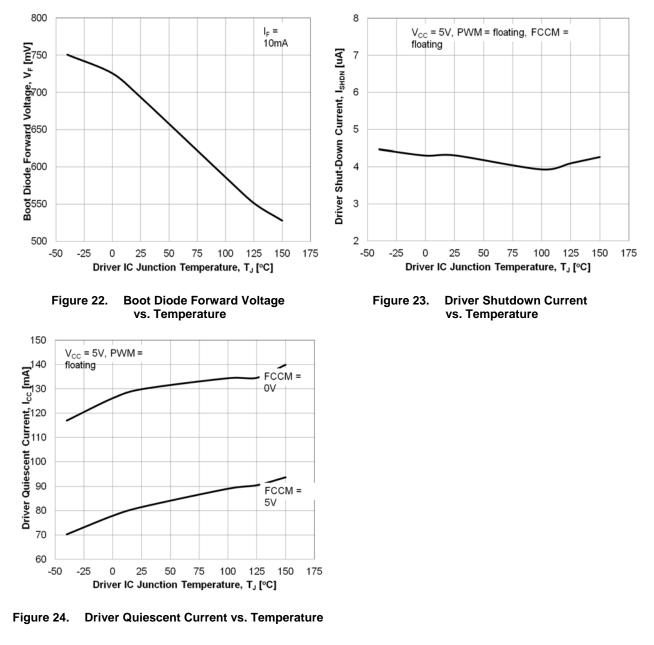

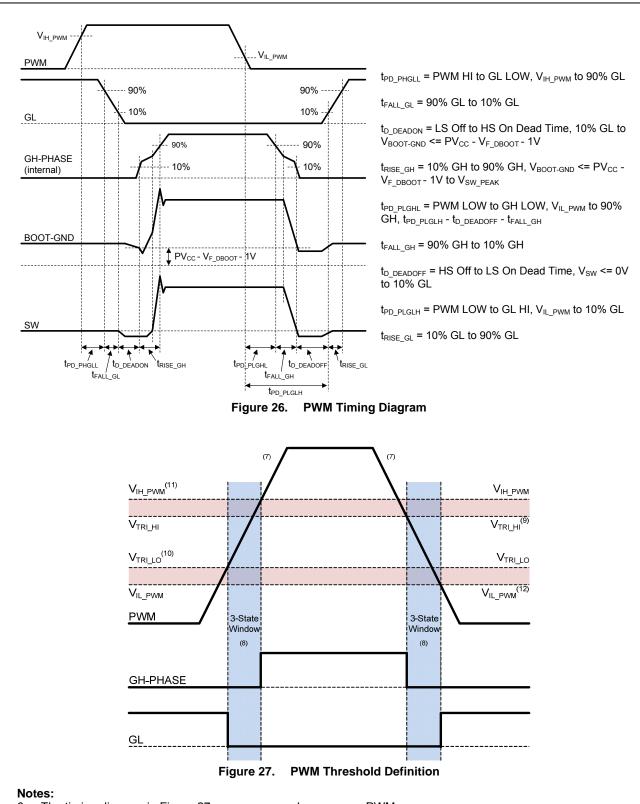

# **Typical Performance Characteristics**

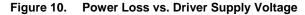

Test Conditions: V<sub>IN</sub>=12 V, V<sub>CC</sub>=PV<sub>CC</sub>=5 V, V<sub>OUT</sub>=1 V, L<sub>OUT</sub>=250 nH, T<sub>A</sub>=25°C and natural convection cooling, unless otherwise noted.

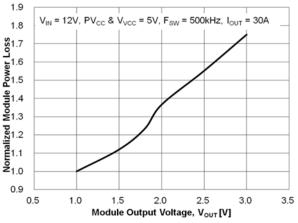

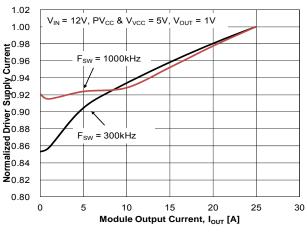

Figure 11. Power Loss vs. Output Voltage

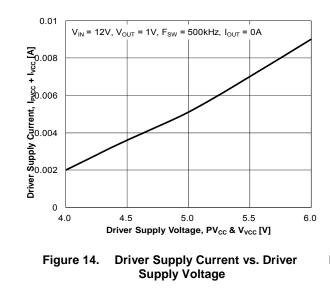

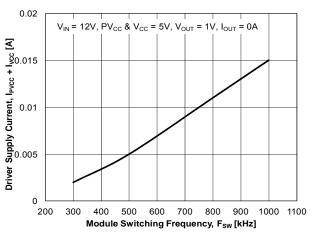

Figure 13. Driver Supply Current vs. Switching Frequency

# **Typical Performance Characteristics**

Test Conditions:  $V_{IN}$ =12 V,  $V_{CC}$ =P $V_{CC}$ =5 V,  $V_{OUT}$ =1 V,  $L_{OUT}$ =250 nH,  $T_A$ =25°C and natural convection cooling, unless otherwise noted.

Figure 17. PWM Threshold vs. Driver Supply Voltage

**FCCM** Threshold vs. Driver

Figure 19.

© 2016 Semiconductor Components Industries, LLC. FDMF3039 • Rev. 2

FDMF3039 — Smart Power Stage (SPS) Module

# **Typical Performance Characteristics**

Test Conditions:  $V_{IN}$ =12 V,  $V_{CC}$ =P $V_{CC}$ =5 V,  $V_{OUT}$ =1 V,  $L_{OUT}$ =250 nH,  $T_A$ =25°C and natural convection cooling, unless otherwise noted.

FDMF3039 — Smart Power Stage (SPS) Module

Figure 25. Forward Bias Safe Operating Area

- 6. The timing diagram in Figure 27 assumes very slow ramp on PWM.

- 7. Slow ramp of PWM implies the PWM signal remains within the 3-state window for a time >>> tD\_HOLD-OFF.

- 8.  $V_{TRI_{HI}}$  = PWM trip level to enter 3-state on PWM falling edge.

- 9.  $V_{\text{TRI_LO}}$  = PWM trip level to enter 3-state on PWM rising edge.

- 10.  $V_{IH_PWM}$  = PWM trip level to exit 3-state on PWM rising edge and enter the PWM HIGH logic state.

- 11. VIL\_PWM = PWM trip level to exit 3-state on PWM falling edge and enter the PWM LOW logic state.

# Description

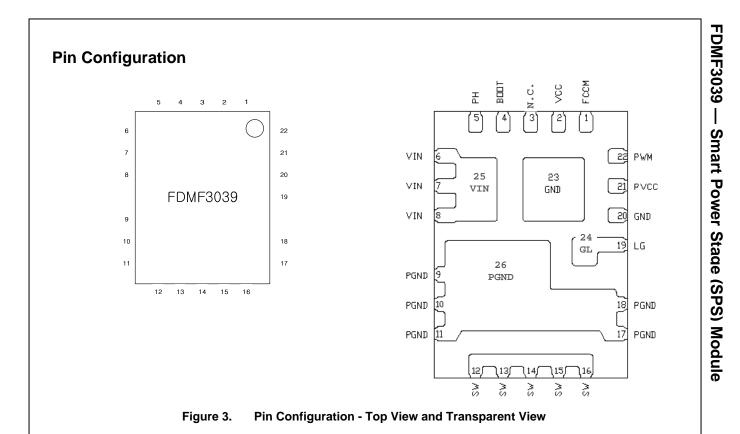

The SPS FDMF3039 is a driver-plus-MOSFET module optimized for the synchronous buck converter topology. A PWM input signal is required to properly drive the high-side and the low-side MOSFETs. The part is capable of driving speed up to 1.5 MHz.

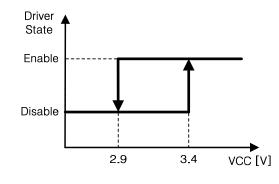

## Power-On Reset (POR & UVLO)

The FDMF3039 incorporates a POR feature that ensures both LDRV and HDRV are forced inactive (LDRV = HDRV = 0) until UVLO > 3.4 V (typical rising threshold). UVLO is performed on VCC (not on PVCC or VIN).

After all gate drive blocks are fully powered on and have finished the startup sequence, the internal driver IC EN\_PWM signal is released HIGH, enabling the driver outputs. Once the driver POR has finished, the driver follows the state of the PWM signal (it is assumed that at startup the controller is either in a high-impedance state or forcing the PWM signal to be within the driver 3-state window).

Figure 28. UVLO

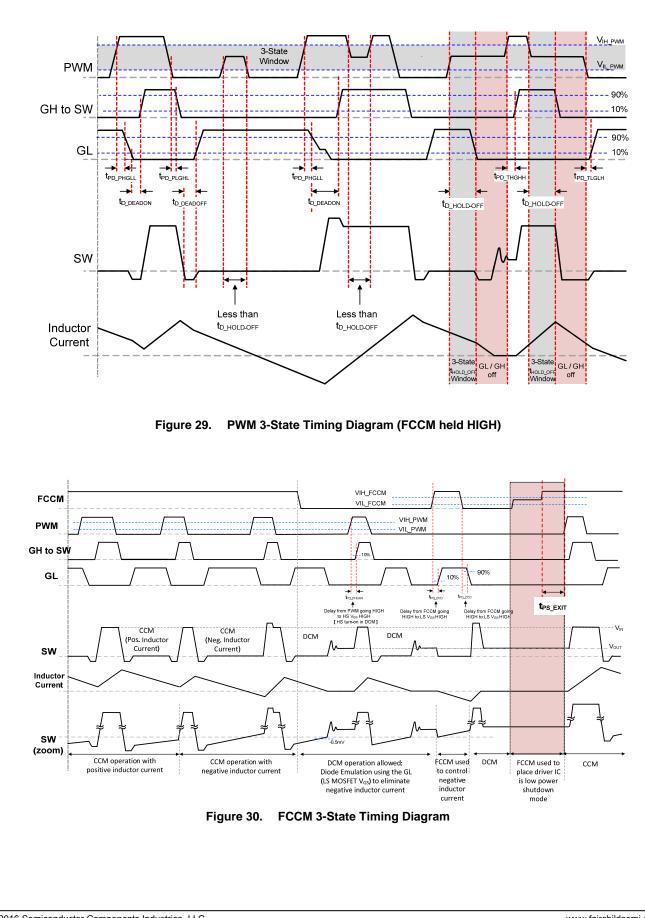

#### 3-State PWM Input

The FDMF3039 incorporates a 3-state 5 V PWM input gate drive design. The 3-state gate drive has both logic HIGH and LOW levels, along with a 3-state shutdown window. When the PWM input signal enters and remains within the 3-state window for a defined hold-off time ( $t_{D_-HOLD-OFF}$ ), both GL and GH are pulled LOW. This feature enables the gate drive to shutdown both the high-side and the low-side MOSFETs to support features such as phase shedding, a common feature on multi-phase voltage regulators.

| Table 1 | I. F | PWM | Logic | Table |

|---------|------|-----|-------|-------|

|         |      |     | LOGIC | Iabic |

| PWM     | FCCM | GH | GL |

|---------|------|----|----|

| 3-State | 1    | 0  | 0  |

| 0       | 1    | 0  | 1  |

| 1       | 1    | 1  | 0  |

# FCCM

The FCCM pin can be used to control Diode Emulation or used to shut down the driver IC (with ICC < 6  $\mu$ A, ICC = current consumed by VCC and PVCC). When FCCM is LOW, diode emulation is allowed. When

FCCM is HIGH, continuous conduction mode is forced. High impedance on the input of FCCM shuts down the driver IC (and module).

#### Table 2. FCCM Logic Table

| PWM     | FCCM    | GH | GL                             | Driver Enable<br>State     |

|---------|---------|----|--------------------------------|----------------------------|

| х       | 3-State | 0  | 0                              | 0 (I <sub>CC</sub> < 6 µA) |

| 3-State | 0       | 0  | 0                              | 1                          |

| 3-State | 1       | 0  | 0                              | 1                          |

| 0       | 0       | 0  | 1 when IL > 0<br>0 when IL < 0 | 1                          |

| 1       | 0       | 1  | 0                              | 1                          |

| 0       | 1       | 0  | 1                              | 1                          |

| 1       | 1       | 1  | 0                              | 1                          |

#### (FCCM = 1 $\rightarrow$ Forced CCM)

Setting the FCCM pin to a HIGH state will allow for forced CCM operation. During forced CCM, the FDMF3039 will always follow the PWM signal and allow for negative inductor current.

#### (FCCM = $0 \rightarrow$ Diode Emulation / DCM)

Setting the FCCM pin to a LOW state will enable diode emulation. Diode emulation allows for higher converter efficiency under light-load situations. With diode emulation is activated, the FDMF3039 will detect the zero current crossing of the output inductor (at lightloads) and will turn off low side MOSFET gate GL to prevent negative inductor current from flowing. Diode emulation ensures Discontinuous Conduction Mode (DCM) operation. Diode emulation is asynchronous to the PWM signal. Therefore, the FDMF3039 will respond to the FCCM input immediately after it changes state.

#### (FCCM = HiZ → Shutdown)

Setting the FCCM pin to a HIGH impedance state (HiZ) will shutdown the driver IC with  $I_{CC}<6 \mu A$ . The FDMF3039 requires a startup latency time of (< 15 µsec) when exiting a HiZ FCCM state. Low  $I_{CC}$  driver shutdown is often needed to support power saving modes in multi-phase voltage regulator designs.

#### **Power Sequence**

The FDMF3039 requires four (4) input signals to perform normal switching operation: VIN, VCC / PVCC, PWM, and FCCM.

The VIN pins are tied to the system main DC power rail.

The PVCC and VCC pins are typically powered from the same 5 V source. These pins can be either tied directly together or tied together through an external RC filter. The filter resistor / capacitor is used to de-couple the switching noise from PVCC to VCC. Refer to Figure 1 for RC filter schematic.

The FCCM pin can be tied to the VCC rail with an external pull-up resistor and it will maintain HIGH once the VCC rail turns on. Or the FCCM pin can be directly tied to the PWM controller for other purposes.

# Synchronous Buck Operating Modes

# Continuous Current Mode with Positive Inductor Current (CCM1)

This condition is typical of a moderate-to-heavily loaded power stage. During this mode, the inductor current is always flowing towards the output capacitor. The highside MOSFET is hard-switching during the turn-on and turn-off events. The low-side MOSFET acts a synchronous rectifier.

# Continuous Current Mode with Negative Inductor Current (CCM2)

This operating mode can occur during two situations:

1.) A converter load transient may force the power stage to pull energy from the output capacitors and deliver the energy back to the input capacitors (Boost Mode). This situation is common in synchronous buck applications that require output voltage load-line positioning.

During this mode, the negative inductor current (current flowing into FDMF3039 SW node) may become large and persist for many cycles. This situation causes the low-side MOSFET to hard switch and the high-side MOSFET acts as a synchronous rectifier. It is highly recommended to check peak SW node voltage stress during any situation that can generate large negative inductor currents.

2.) A power stage that is operating in forced CCM mode with lighter converter loads. Here, the inductor peak-to-peak ripple current is greater than two times the load current and the inductor current is flowing both positive and negative in a switching cycle.

# **Discontinuous Current Mode (DCM)**

This condition is typical of a lightly loaded power stage. During DCM, the high-side MOSFET turns on into an un-energized out filter inductor (i.e. zero inductor current). The inductor current ramps up during the highside MOSFET on-time and is then allowed to ramp back down to aero amps during the low-side on-time (i.e. inductor current returns to zero every switching cycle.

# **High-Side Driver**

The high-side driver (HDRV) is designed to drive a floating N-channel MOSFET (Q1). The bias voltage for the high-side driver is developed by a bootstrap supply circuit, consisting of the internal Schottky diode and external bootstrap capacitor (C<sub>BOOT</sub>). During startup, the SW node should be held at PGND, allowing CBOOT to charge to PVCC through the internal bootstrap diode. When the PWM input goes HIGH, HDRV begins to charge the gate of the high-side MOSFET (internal GH pin). During this transition, the charge is removed from the C<sub>BOOT</sub> and delivered to the gate of Q1. As Q1 turns on, SW rises to  $V_{IN}$ , forcing the BOOT pin to  $V_{IN}$  + VBOOT. which provides sufficient VGs enhancement for Q1. To complete the switching cycle, Q1 is turned off by pulling HDRV to SW. CBOOT is then recharged to PVCC when the SW falls to PGND. HDRV output is in phase with the PWM input. The high-side gate is held LOW when the driver is disabled or the PWM signal is held within the 3-state window for longer than the 3-state hold-off time, to HOLD-OFF.

# Low-Side Driver

The low-side driver (LDRV) is designed to drive the gate-source of a ground-referenced, low- $R_{DS(ON)}$ , N-channel MOSFET (Q2). The bias for LDRV is internally connected between the PVCC and AGND. When the driver is enabled, the driver output is 180° out of phase with the PWM input. When the driver is disabled (FCCM = 0 V), LDRV is held LOW.

# **Application Information**

# **Decoupling Capacitor for PVCC & VCC**

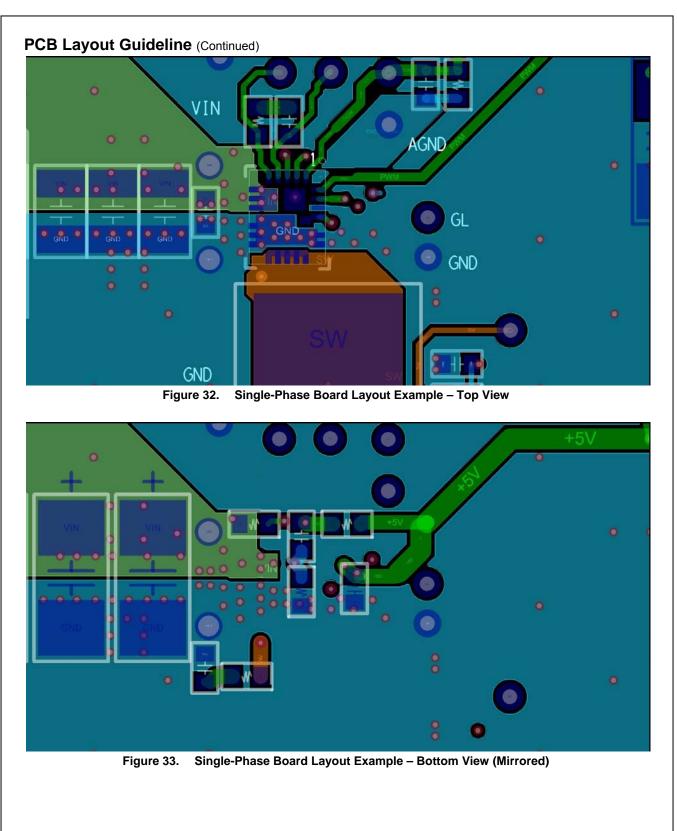

For the supply inputs (PVCC and VCC pins), local decoupling capacitors are required to supply the peak driving current and to reduce noise during switching operation. Use at least  $0.68 \sim 1 \mu F / 0402 \sim 0603 / X5R \sim X7R$  multi-layer ceramic capacitors for both power rails. Keep these capacitors close to the PVCC and VCC pins and PGND and AGND copper planes. If the de-coupling capacitors need to be located on the bottom side of board, place through-hole vias on each pad connecting top side and bottom side PVCC and VCC nodes with low impedance current paths, see Figure 32 and Figure 33 [A1]

The supply voltage range on PVCC and VCC is 4.5 V  $\sim$  5.5 V, and typically 5 V for normal applications.

# **R-C Filter on VCC**

The PVCC pin provides power to the gate drive of the high-side and low-side power MOSFETs. In most cases, PVCC can be connected directly to VCC, which is the pin that provides power to the analog and logic blocks of the driver. To avoid switching noise injection from PVCC into VCC, a filter resistor can be inserted between PVCC and VCC decoupling capacitors.

Recommended filter resistor value range is 0 ~ 4.7  $\Omega$ , typically 0  $\Omega$  for most applications.

# **Bootstrap Circuit**

The bootstrap circuit uses a charge storage capacitor (C<sub>BOOT</sub>). A bootstrap capacitor of 0.1 ~ 0.22  $\mu$ F / 0402 ~ 0603 / X5R ~ X7R is usually appropriate for most switching applications. A series bootstrap resistor may be needed for specific applications to lower high-side MOSFET switching speed. The boot resistor is required when the SPS is switching above 15 V V<sub>IN</sub>; when it is effective at controlling V<sub>SW</sub> overshoot. R<sub>BOOT</sub> value from zero to 4.7  $\Omega$  is typically recommended to reduce excessive voltage spike and ringing on the SW node. A

higher  $R_{BOOT}$  value can cause lower efficiency due to high switching loss of high-side MOSFET.

Do not add a capacitor or resistor between the BOOT pin and GND.

# **PWM (Input)**

The PWM pin recognizes three different logic levels from PWM controller: HIGH, LOW, and 3-state. When the PWM pin receives a HIGH command, the gate driver turns on the high-side MOSFET. When the PWM pin receives a LOW command, the gate driver turns on the low-side MOSFET. When the PWM pin receives a voltage signal inside of the 3-state window ( $V_{TRL_Window}$ ) and exceeds the 3-state hold-off time, the gate driver turns off both high-side and low-side MOSFETs. To recognize the high-impedance 3-state signal from the controller, the PWM pin has an internal resistor divider from VCC to PWM to AGND. The resistor divider sets a voltage level on the PWM pin inside the 3-state window when the PWM signal from the controller is high-impedance.

# FCCM (Input)

When the FCCM pin is set HIGH, the driver IC Zero Cross Detect (ZCD) comparator is disabled, and the high-side and low-side MOSFETs switch in FCCM (Forced CCM) and follow the PWM signal. When the FCCM pin is set LOW, the low-side MOSFET turns off when the SPS driver detects negative inductor current during the low-side MOSFET turn-on period. This operating mode is commonly referred to as diode emulation. The diode emulation feature allows for higher converter efficiency during light-load condition and PFM / DCM operation.

Applications that require diode emulation and/or low shutdown current should actively drive the FCCM pin from a PWM controller. Do not add any noise filter capacitor on the FCCM pin.

# **PCB Layout Guideline**

Figure 32 and Figure 33 provide an example of singlephase layout for the FDMF3039 and critical components. All of the high-current paths; such as VIN, SW, VOUT, and GND coppers; should be short and wide for low parasitic inductance and resistance. This helps achieve a more stable and evenly distributed current flow, along with enhanced heat radiation and system performance.

Input ceramic bypass capacitors must be close to the VIN and PGND pins. This reduces the high-current power loop inductance and the input current ripple induced by the power MOSFET switching operation.

The SW copper trace serves two purposes. In addition to being the high-frequency current path from the SPS package to the output inductor, it serves as a heat sink for the low-side MOSFET. The trace should be short and wide enough to present a low-impedance path for the high-frequency, high-current flow between the SPS and the inductor. The short and wide trace minimizes electrical losses and SPS temperature rise. The SW node is a high-voltage and high-frequency switching node with high noise potential. Care should be taken to minimize coupling to adjacent traces. Since this copper trace acts as a heat sink for the low-side MOSFET, balance using the largest area possible to improve SPS cooling while maintaining acceptable noise emission.

An output inductor should be located close to the FDMF3039 to minimize the power loss due to the SW copper trace. Care should also be taken so the inductor dissipation does not heat the SPS.

PowerTrench<sup>®</sup> MOSFETs are used in the output stage and are effective at minimizing ringing due to fast switching. In most cases, no RC snubber on SW node is required. If a snubber is used, it should be placed close to the SW and PGND pins. The resistor and capacitor of the snubber must be sized properly to not generate excessive heating due to high power dissipation.

Decoupling capacitors on PVCC, VCC, and BOOT capacitors should be placed as close as possible to the PVCC ~ PGND, VCC ~ AGND, and BOOT ~ PHASE pin pairs to ensure clean and stable power supply. Their routing traces should be wide and short to minimize parasitic PCB resistance and inductance.

The board layout should include a placeholder for small-value series boot resistor on BOOT ~ PHASE. The boot-loop size, including series  $R_{BOOT}$  and  $C_{BOOT}$ , should be as small as possible.

A boot resistor may be required when the SPS is operating above 15 V V<sub>IN</sub> and it is effective to control the high-side MOSFET turn-on slew rate and SW voltage overshoot. R<sub>BOOT</sub> can improve noise operating margin in synchronous buck designs that may have noise issues due to ground bounce or high positive and negative V<sub>SW</sub> ringing. Inserting a boot resistance lowers the SPS module efficiency. Efficiency versus switching noise must be considered. R<sub>BOOT</sub> values from 0.5  $\Omega$  to 4.7  $\Omega$  are typically effective in reducing V<sub>SW</sub> overshoot.

The VIN and PGND pins handle large current transients with frequency components greater than 100 MHz. If possible, these pins should be connected directly to the VIN and board GND planes. The use of thermal relief traces in series with these pins is not recommended since this adds extra parasitic inductance to the power path. This added inductance in series with either the VIN or PGND pin degrades system noise immunity by increasing positive and negative V<sub>SW</sub> ringing.

PGND pad and pins should be connected to the GND copper plane with multiple vias for stable grounding. Poor grounding can create a noisy and transient offset voltage level between PGND and AGND. This could lead to faulty operation of gate driver and MOSFETs.

Ringing at the BOOT pin is most effectively controlled by close placement of the boot capacitor. Do not add any additional capacitors between BOOT to PGND. This may lead to excess current flow through the BOOT diode, causing high power dissipation.

The FCCM pin integrates weak internal pull-up and pulldown current sources. The current sources are used to help hold the FCCM in the 3-state window. This pin should not have any noise filter capacitors if actively driven by a PWM controller. Do not float this pin.

Multiple vias should be placed on the VIN and VOUT copper areas to interconnect nodes that are located on multiple layers (top, inner, and bottom layers). The vias will help to evenly distribute current flow and heat conduction.

Care should be taken when routing the copper pour area and via placement on the SW copper. A large SW node copper pour can result in excessive parasitic inductance and capacitance, which can increase switching noise. However, the copper pour area and via placement can affect the efficiency and thermal performance, where a large copper pour can help decrease thermal resistance and parasitic resistance. If possible, place the SW node copper on the top layer with no vias on the SW copper to minimize switch node parasitic noise. If multiple SW node layers are needed, vias should be relatively large and of reasonably low inductance.

Critical high-frequency components; such as  $R_{BOOT}$ ,  $C_{BOOT}$ , RC snubber, and bypass capacitors; should be located as close to the respective SPS module pins as possible on the top layer of the PCB. If this is not feasible, they can be placed on the board bottom side and their pins connected from bottom to top through a network of low-inductance vias.

ON Semiconductor and the ON Semiconductor logo are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON Semiconductor products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by ON Semiconductor. "Typical" parameters which may be provided in ON Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights nor the rights of others. ON Semiconductor products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold ON Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that ON Semiconductor was negligent regarding the design or manufacture of the part. ON Semiconductor is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

#### PUBLICATION ORDERING INFORMATION

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor 19521 E. 32nd Pkwy, Aurora, Colorado 80011 USA Phone: 303-675-2175 or 800-344-3860 Toll Free USA/Canada Fax: 303-675-2176 or 800-344-3867 Toll Free USA/Canada Email: orderlit@onsemi.com N. American Technical Support: 800-282-9855 Toll Free USA/Canada. Europe, Middle East and Africa Technical Support: Dance 101 23 700 2010

Phone: 421 33 790 2910 Japan Customer Focus Center Phone: 81-3-5817-1050 ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative

# **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Gate Drivers category:

Click to view products by ON Semiconductor manufacturer:

Other Similar products are found below :

89076GBEST

00053P0231

56956

57.404.7355.5

LT4936

57.904.0755.0

5882900001

00600P0005

00-9050-LRPP

00-9090-RDPP

5951900000

01-1003W-10/32-15

0131700000

00-2240

LTP70N06

LVP640

5J0-1000LG-SIL

LY1D-2-5S-AC120

LY2-US-AC240

LY3

UA-DC24

00576P0020

00600P0010

LZN4-UA-DC12

LZNQ2M-US-DC5

LZNQ2-US-DC12

LZP40N10

00-8196-RDPP

00-8274-RDPP

00-8275-RDNP

00-8722-RDPP

00-8728-WHPP

00-8869-RDPP

00-9051-RDPP

00-9091-LRPP

00-9291-RDPP

0207100000

0207400000

01312

0134220000

60713816

M15730061

61161-90

61278-0020

6131-204-23149P

6131-205-17149P

6131-209-15149P

6131-218-17149P

6131-220-21149P

6131-260-2358P

6131-265-11149P

6131-205-17149P

6131-209-15149P

6131-218-17149P