# **ON Semiconductor**

# Is Now

To learn more about onsemi™, please visit our website at www.onsemi.com

onsemi and ONSEMI. and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. onsemi reserves the right to make changes at any time to any products or information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product features, availability, functionality, or suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using onsemi products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by onsemi. "Typical" parameters which may be provided in onsemi data sheets and/ or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. onsemi does not convey any license under any of its intellectual property rights nor the rights of others. onsemi products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use onsemi products for any such unintended or unauthorized application,

# FSA831 — USB2.0 High-Speed (480Mbps) Charger Detection with Isolation Switch

#### **Features**

| USB Detection           | USB Battery Charging Rev. 1.2<br>Supports Data Contact Detect (DCD)<br>Dead Battery Provision (DBP)<br>with 30-Minute Timer |

|-------------------------|-----------------------------------------------------------------------------------------------------------------------------|

| Sw itch Type            | Isolation Switch Closes for Charging Downstream Port (CDP) Standard Downstream Port (SDP)                                   |

| V <sub>BUS</sub>        | 28V Over-Voltage Tolerance<br>-2V Under-Voltage Tolerance                                                                   |

| Package                 | 10-Lead MicroPak™<br>1.6 x 2.1mm, 0.5mm Pitch                                                                               |

| Ordering<br>Information | FSA831L10X                                                                                                                  |

# **Applications**

MP3, Mobile Internet Device (MID), Cell Phone, PDA, Digital Camera, Notebook and Netbook

## **Description**

The FSA831 is a charger-detection IC with an integrated isolation switch for use with a micro/mini USB port. The FSA831 detects battery chargers and is compliant with USB Battery Charging Specification, Rev 1.2 (BC1.2). The algorithm incorporates Data Contact Detection (DCD), which ensures that the shorter, inner pins of the USB connector are making contact prior to continuing with battery charger detection. The device determines if a Dedicated Charging Port (DCP), Charging Downstream Port (CDP), or a typical PC host, called a Standard Downstream Port (SDP), is connected. If a charger is detected, the FSA831 determines whether the charger is a DCP or CDP. For SDP and CDP detection, an internal isolation switch is closed to connect the D+/D- lines of the USB cable to the resident USB transceiver within the portable device. The FSA831 conforms to all the constraints for the Dead Battery Provision (DBP) within the BC1.2 specification, including a 30-minute timer that cannot exceed 45 minutes, per BC1.2.

#### **Related Resources**

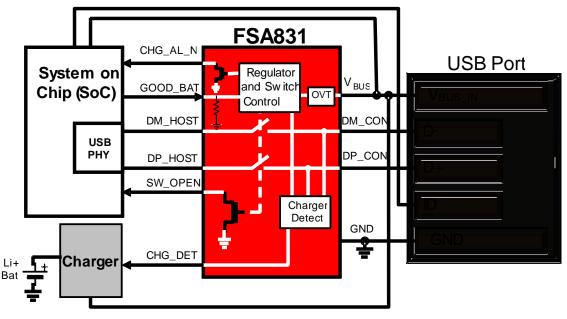

## **Typical Application**

Figure 1. Mobile Phone Example

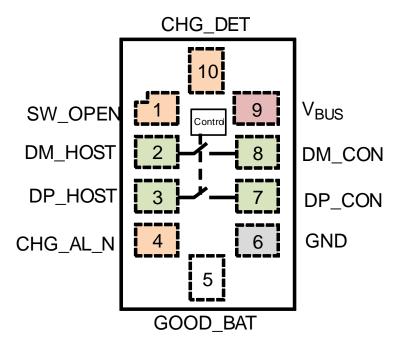

# **Pin Configurations**

Figure 2. Pin Assignments (Top View)

# **Pin Descriptions**

| Name                | Pin# | Description                                                                                                                                                        |

|---------------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| USB Interface       |      |                                                                                                                                                                    |

| DP_HOST             | 3    | D+ signal connected to the resident USB transceiver on the phone                                                                                                   |

| DM_HOST             | 2    | D- signal connected to the resident USB transceiver on the phone                                                                                                   |

| Connector Interface | е    |                                                                                                                                                                    |

| V <sub>BUS</sub>    | 9    | Input voltage supply pin to be connected to the V <sub>BUS</sub> pin of the USB connector                                                                          |

| GND                 | 6    | Ground                                                                                                                                                             |

| DP_CON              | 7    | Connected to the USB connector D+ pin                                                                                                                              |

| DM_CON              | 8    | Connected to the USB connector D- pin                                                                                                                              |

| Status Outputs      |      |                                                                                                                                                                    |

| CHG_DET             | 10   | CMOS push/pull output connected to charger IC for indicating if a charger has been detected (LOW=charger not detected, HIGH=DCP or CDP charger has been detected). |

| SW_OPEN             | 1    | Open-drain output pin; requires pull-up resistor to I/O voltage supply (LOW=switch closed, Hi-Z=switch open).                                                      |

| CHG_AL_N            | 4    | CMOS open-drain output pin (LOW= $V_{BUS}$ is valid and charge is allowed to be drawnfrom $V_{BUS}$ , Hi-Z= $V_{BUS}$ is not at a valid voltage).                  |

| Input Pin           |      |                                                                                                                                                                    |

| GOOD_BAT            | 5    | Input that indicates if the battery is a good battery or a dead battery (LOW=dead battery, HIGH=good battery).                                                     |

Table 1. Functionality

| Device Detected                                                                                                                                                                                                      | GOOD_<br>BAT | SW_<br>OPEN | CHG_<br>AL_N | CHG_<br>DET    | DP_HOST | DM_HOST | DP_CON              | DM_CON              |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|-------------|--------------|----------------|---------|---------|---------------------|---------------------|

| DCP                                                                                                                                                                                                                  | Х            | Hi-Z        | LOW          | HIGH           | Hi-Z    | Hi-Z    | V <sub>DP_SRC</sub> | Hi-Z <sup>(1)</sup> |

| CDP                                                                                                                                                                                                                  | HIGH         | LOW         | LOW          | HIGH           | DP_CON  | DM_CON  | DP_HOST             | DM_HOST             |

| CDP                                                                                                                                                                                                                  | LOW          | Hi-Z        | LOW          | HIGH           | Hi-Z    | Hi-Z    | V <sub>DP_SRC</sub> | Hi-Z                |

| SDP <sup>(2)</sup>                                                                                                                                                                                                   | HIGH         | LOW         | LOW          | LOW            | DP_CON  | DM_CON  | DP_HOST             | DM_HOST             |

| SDP <sup>(2)</sup>                                                                                                                                                                                                   | LOW          | Hi-Z        | LOW          | LOW            | Hi-Z    | Hi-Z    | V <sub>DP_SRC</sub> | Hi-Z                |

| SDP, CDP, or DCP plugged in and after 30-minute timer expires                                                                                                                                                        | LOW          | Hi-Z        | Hi-Z         | LOW            | Hi-Z    | Hi-Z    | Hi-Z                | Hi-Z                |

| V <sub>BUS</sub> < V <sub>BUS</sub> valid to<br>V <sub>BUS</sub> > V <sub>BUS</sub> valid operation prior to<br>completing detection of SDP,<br>CDP, or DCP. Upon detection, all<br>outputs switch as in rows above. | Х            | Hi-Z        | Hi-Z         | Hi-Z to<br>LOW | Hi-Z    | Hi-Z    | Hi-Z                | Hi-Z                |

#### Notes:

- Hi-Z is the internal state of DM\_CON. Since a DCP has been detected, DM\_CON is shorted to DP\_CON externally and DM\_CON is shorted to V<sub>DP SRC</sub>.

- Proprietary chargers that leave DP\_CON and DM\_CON floating are detected as SDP. Proprietary chargers that force DP\_CON=2V and DM\_CON=2.7V (or any other voltages) can be detected as CDP, DCP or SDP depending on the resistances of the resistor dividers on DP\_CON and DM\_CON used to create the voltages on those pins.

## **Functional Description**

## **Data Contact Detect (DCD)**

DCD relies on the D+ and D- lines being present. DCD waits until the internal timeout (450ms typical) has expired in the following cases:

- If a charger does not have a D+ pin on the USB connector

- If the D+ pin is not shorted to D- pin on the connector,

- If D+ is pulled up to a supply

- If D+ does not have a sufficient path to ground to defeat a pull-up IDP\_SRC (10μA typical) current source.

The FSA831 proceeds with charger detection even though it is unlikely a charger is present. If there is no charger, the algorithm reports an SDP and closes the switch. If a device is pulling D+ HIGH, this voltage presents itself to the USB transceiver or Physical Layer Interface (PHY) block within a System on Chip (SoC) after the switch is closed

If the DCD timeout was insufficient and the PHY block is so equipped, DCD and the charging algorithm can be repeated in the PHY block. The stipulation is that the total time from  $V_{BUS}$  valid to USB transceiver connection with a  $1.5k\Omega$  pullup to 3.3V must be one (1) second, per USB 2.0 standards (USB 2.0 connect timing), provided the portable device does not have a dead battery.

A typical PS/2 port (old PC mouse / keyboard port) has a resistive pull-up to  $V_{\text{BUS}}.$  This can cause the DCD to exceed the maximum wait time ( $t_{\text{DCD\_TIMEOUT}})$  and proceed to charger detection. The likely path through charger detection is classifying the PS/2 port as an SDP port. This results in closing the USB switches, which causes the voltage on the

DP\_CON and DM\_CON pins to pass through the switch to DP\_HOST and DM\_HOST, respectively. Since voltages on the PS/2 port can go as high as the  $V_{BUS}$  voltage, the DP\_HOST and DM\_HOST pins can be pulled up to  $V_{BUS}$ . The USB PHY connected to DP\_HOST and DM\_HOST must be equipped to handle these higher voltages.

#### CHG\_AL\_N Output and Output Timing

CHG\_AL\_N output indicates that charge is allowed to be drawn from V\_BUS when CHG\_AL\_N is LOW. When FSA831 first powers up and prior to detection, the CHG\_AL\_N pin can follow V\_BUS up to 28V, which is the absolute maximum V\_BUS voltage allowed. Whenever V\_BUS is at GND, the FSA831 is completely off and the switches and all I/Os are in the Hi-Z state. When V\_BUS climbs above the valid V\_BUS threshold, detection occurs automatically and CHG\_DET, SW\_OPEN, and CHG\_AL\_N all simultaneously switch to the states indicated in Table 1 if GOOD\_BAT is HIGH (see Dead Battery Provision description for GOOD\_BAT = LOW).

#### **Dead Battery Provision**

BC1.2 and USB 2.0 allow a portable device (defined as a device with a battery) with a dead battery to take a maximum of 100mA from the USB  $V_{BUS}$  line for a maximum of 45 minutes as long as the portable device forces the D+ line to  $V_{DP\_SRC}$  (0.6V typical). FSA831 starts detection when  $V_{BUS}$  crosses the  $V_{BUSVLD}$  threshold and, if it detects a CDP or SDP and GOOD\_BAT is HIGH, automatically closes the switch and does not force the DP\_CON pin to  $V_{DP\_SRC}$ .

Once the charger detection is completed, the FSA831 starts a 30-minute timer and forces the DP\_CON pin to  $V_{DP\_SRC}$  until the timer elapses. During the 30 minute period, if

GOOD\_BAT is LOW, VDP\_SRC is applied to DP\_CON and the D+/D- switches are opened, If GOOD\_BAT is HIGH, VDP\_SRC is not applied to DP\_CON and the D+/D- switches are closed, If GOOD\_BAT is LOW when 30 minute timer expires; regardless of whether an SDP, CDP, or DCP was previously detected; the FSA831 removes VDP\_SRC from DP\_CON and forces CHG\_DET LOW and CHG\_AL\_N to Hi-Z (SW\_OPEN remains Hi-Z) To exit this fault condition, remove VBUS, wait for all the VBUS Printed Circuit Board (PCB) capacitance to discharge, and re-apply VBUS. Table 1 provides the functionality of the pins when the timer expires.

When GOOD\_BAT is HIGH and the battery is removed from the portable device while  $V_{BUS}$  is valid, bringing GOOD\_BAT LOW; the FSA831 opens the isolation switches on DP\_CON and DM\_CON and forces the DP\_CON pin to  $V_{DP\_SRC}$ . In this scenario, the timer generally expires because the SoC does not have a supply to bring GOOD\_BAT HIGH unless the battery that was removed is re-inserted within 30 minutes from when the USB plug is inserted.

If an SDP or CDP is inserted with GOOD\_BAT HIGH during the 30-minute timer, then GOOD\_BAT changes to LOW; SW\_OPEN changes to Hi-Z and the counter continues counting until the 30 minutes expires. If GOOD\_BAT then returns to HIGH, SW\_OPEN changes to LOW and finishes out the 30-minute time.

GOOD\_BAT has an internal pull-down resistor to ensure it is LOW when the SoC is powered down. This input is designed to have very low thresholds to interface with low-voltage SoCs driven with 1.2V supplies.

## **Proprietary Chargers**

Only legitimate USB chargers that force VDM\_SRC (0.6V typical) on DM\_CON when VDP\_SRC is applied to DP\_CON are detected by the FSA831 and cause CHG\_DET signal to be asserted. Any charger that forces a HIGH on both DP\_CON and DM\_CON can be detected as CDP, DCP, or

SDP (depending on the resistances of the resistor dividers on DP\_CON and DM\_CON) and used to create the HIGH voltages on those pins. Any charger that lets both DP\_CON and DM\_CON signals float is detected as an SDP and CHG\_DET stays de-asserted. In cases where the proprietary charger is detected as an SDP or CDP, since the switches are closed and access is made from the USB connector D+ and D- lines to the USB PHY block; the chargers can be detected within the PHY if so equipped

## **Ground Drops**

When a DCP is detected,  $V_{DP\_SRC}$  is forced on DP\_CON provided GOOD\_BAT is HIGH or if GOOD\_BAT is LOW and the DBP timer has not expired. For current up to 1.5A flowing into the  $V_{BUS}$  and GND lines of the USB cable, this can translate to substantial ground drops that lift the ground of the portable device. This drop adds to the voltage at the DP\_CON pin as seen from the DCP D+ pin. For the maximum ground drop of 375mV specified in the BC1.2 specification and for the maximum  $V_{DP\_SRC}$  of 0.7V, the voltage as seen by the DCP would be 1.075V. Smart DCPs that rely on this voltage detection to determine attach and detach detection need to take this into account.

### **V<sub>BUS</sub>** Tolerance

When  $V_{\text{BUS}}$  rises, an internal Power On Reset (POR) detects this voltage and prepares the FSA831 for charger detection.

$V_{BUS}$  voltages up to 28V can be tolerated by the  $V_{BUS}$  pin.  $V_{BUS}$  can tolerate voltages up to -2V for cases where a charger is plugged in backwards.

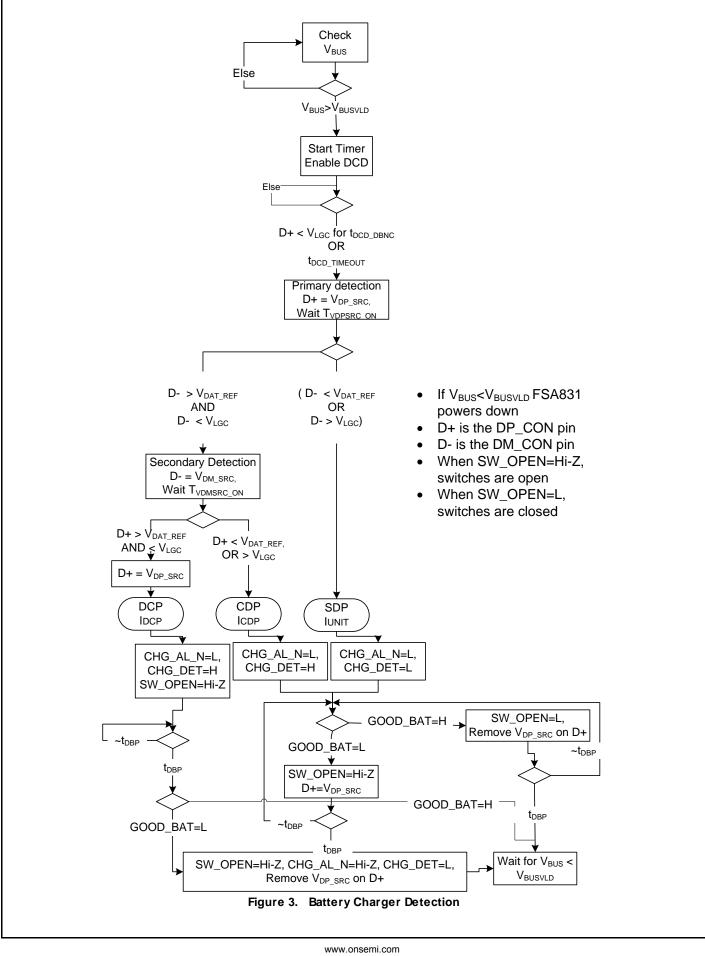

#### **Detection Flow**

The flow diagram in Figure 3 shows how the FSA831 achieves battery charger detection consistent with BC1.2.

# **Absolute Maximum Ratings**

Stresses exceeding the absolute maximum ratings may damage the device. The device may not function or be operable above the recommended operating conditions and stressing the parts to these levels is not recommended. In addition, extended exposure to stresses above the recommended operating conditions may affect device reliability. The absolute maximum ratings are stress ratings only.

| Symbol           | Parameter                                                 |                                                           |          |      | Max. | Unit |

|------------------|-----------------------------------------------------------|-----------------------------------------------------------|----------|------|------|------|

| V <sub>BUS</sub> | Voltage from USB Conne                                    | Voltage from USB Connector                                |          |      |      | V    |

| Vsw              | USB Switch I/O Voltage (                                  | USB Switch I/O Voltage (DP_CON, DM_CON, DP_HOST, DM_HOST) |          |      | 6.0  | V    |

| Isw              | USB Switch Current (DP_                                   | USB Switch Current (DP_CON to DP_HOST, DM_CON to DM_HOST) |          |      |      | mA   |

| V <sub>I/O</sub> | Voltage from GOOD_BAT                                     | , CHG_AL_N, CHG_DET and SW_OPE                            | N VOs    | -0.5 | 6.0  | V    |

| $V_{CA}$         | Voltage from CHG_AL_N Output                              |                                                           |          |      | 28.0 | V    |

| I <sub>I/O</sub> | CHG_AL_N, CHG_DET and SW_OPEN Outputs Sink/Source Current |                                                           |          | -5   | +5   | mA   |

| T <sub>STG</sub> | Storage Temperature Range                                 |                                                           |          | -65  | +150 | °C   |

| TJ               | Maximum Junction Tempo                                    | erature                                                   |          |      | +150 | °C   |

| TL               | Lead Temperature (Solde                                   | ering, 10 Seconds)                                        |          |      | +260 | °C   |

|                  | IEC 61000-4-2 System                                      | USB Pins (DP_CON, DM_CON, VBUS)                           | Air Gap  |      | 15   |      |

| ESD              | , , ,                                                     | OSB FILIS (DE_CON, DIVI_CON, VBOS)                        | Contact  |      | 8    | kV   |

| ESD              | Human Body Model, JED                                     | del, JEDEC JESD22-A114 All                                |          |      | 6    | ΝV   |

|                  | Charged Device Model, C                                   | IEDEC JESD22-C101                                         | All Pins |      | 2    |      |

# **Recommended Operating Conditions**

The Recommended Operating Conditions table defines the conditions for actual device operation. Recommended operating conditions are specified to ensure optimal performance to the datasheet specifications. ON Semiconductor does not recommend exceeding them or designing to Absolute Maximum Ratings.

| Symbol           | Parameter                           | Min. | Max. | Unit |

|------------------|-------------------------------------|------|------|------|

| V <sub>BUS</sub> | V <sub>BUS</sub> Input HIGH Voltage | 4    | 6    | V    |

| Vsw              | Switch I/O Voltage for USB Path     | 0    | 3.6  | V    |

| T <sub>A</sub>   | Operating Temperature               | -40  | +85  | ٥С   |

## **DC Electrical Characteristics**

Unless otherwise indicated, V<sub>BUS</sub>=4V to 6V and T<sub>A</sub>=-40 to +85°C. Typical values are at T<sub>A</sub>=25°C unless otherwise specified.

| Symbol                 | Parameter                                                                                                 | Condition                                                                                                         | Min.     | Тур. | Max. | Unit |

|------------------------|-----------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|----------|------|------|------|

| Status Out             | tputs                                                                                                     |                                                                                                                   |          |      |      |      |

| Vohcd                  | Output HIGH Voltage (CHG_DET)                                                                             | I <sub>OH</sub> =-2mA                                                                                             | 2.0      |      |      | V    |

| V <sub>OL</sub>        | Output LOW Voltage (CHG_DET, CHG_AL_N, SW_OPEN)                                                           | l <sub>OL</sub> =2mA                                                                                              |          |      | 0.4  | V    |

| t <sub>DIFF</sub>      | Skew Betw een Any Output (CHG_DET, CHG_AL_N, SW_OPEN) Sw itching Relative to the Other Outputs Sw itching | I <sub>I/O</sub> = $\pm 2$ mA, CHG_AL_N= $20$ k $\Omega$ to 5V, SW_OPEN= $10$ k $\Omega$ to 1.8V                  |          |      | 100  | ns   |

| V <sub>BUS</sub> Pin   |                                                                                                           |                                                                                                                   |          |      |      |      |

| VBUS <sub>VLD</sub>    | V <sub>BUS</sub> Valid Detection Threshold <sup>(1)</sup>                                                 |                                                                                                                   | 8.0      |      | 4.0  | V    |

| IBUSIN                 | V <sub>BUS</sub> Input Leakage                                                                            | V <sub>BUS</sub> =0V to 0.8V                                                                                      |          |      | 10   | μA   |

| VBUSACT                | V <sub>BUS</sub> Active Mode Average Current                                                              | USB Path Active, USB Switch Closed<br>After Charger Detection                                                     |          |      | 400  | μΑ   |

| tout                   | Time from V <sub>BUS</sub> Valid Asserted to CHG_DET, CHG_AL_N and SW_OPEN Outputs Valid                  | DP_CON pulled down to GND, $15k\Omega$ , all voltages forced on $V_{BUS}$ , DP_CON, DM_CON and GND simultaneously |          |      | 250  | ms   |

| Switch Ch              | aracteristics                                                                                             |                                                                                                                   |          |      |      |      |

| loff                   | Pow er Off Leakage Current                                                                                | USB Path $V_{BUS}$ =0V, $V_{SW}$ =0V or 3.6V, Figure 5                                                            |          |      | 10   | μA   |

| R <sub>ONUSB</sub>     | High-Speed USB Range Switch On Resistance <sup>(1)</sup>                                                  | V <sub>DP_CON</sub> /V <sub>DM_CON</sub> =0V, 0.4V;<br>I <sub>ON</sub> =8mA; Figure 4; V <sub>BUS</sub> =4V to 6V |          | 6.5  | 9.0  | Ω    |

| Control In             | put                                                                                                       |                                                                                                                   | <u>I</u> | 1    | 1    |      |

| V <sub>IH</sub>        | Input HIGH Voltage (GOOD_BAT)                                                                             |                                                                                                                   | 1.1      |      |      | V    |

| V <sub>IL</sub>        | Input LOW Voltage (GOOD_BAT)                                                                              |                                                                                                                   |          |      | 0.5  | V    |

| R <sub>PD</sub>        | Pull Down Resistance (GOOD_BAT)                                                                           |                                                                                                                   | 1        |      |      | ΜΩ   |

| I <sub>IN</sub>        | Input Leakage Current (GOOD_BAT)                                                                          | V <sub>BUS</sub> =5V, GOOD_BAT=0V to 4.4V                                                                         |          |      | 10   | μΑ   |

| loff                   | OFF State Leakage Current (GOOD_BAT)                                                                      | V <sub>BUS</sub> =0V, GOOD_BAT=0V to 4.4V                                                                         |          |      | 10   | μΑ   |

| t <sub>DBP</sub>       | Dead Battery Provision (DBP) Timer                                                                        |                                                                                                                   | 15       | 30   | 45   | min  |

| t <sub>GB</sub>        | Time from GOOD_BAT Asserted to SW_OPEN Meet the R <sub>ONUSB</sub> Specification                          | De-Asserted, Switches Closed and                                                                                  |          |      | 30   | ms   |

| t <sub>DB</sub>        | Time from GOOD_BAT De-asserted to SW_OPEN Asserted, Switches Opened                                       |                                                                                                                   |          |      | 65   | ms   |

| Battery Ch             | narger Detection Parameters from BC1.2 Spe                                                                | cification                                                                                                        |          |      |      |      |

| V <sub>DAT_REF</sub>   | Data Detect Voltage                                                                                       |                                                                                                                   | 0.25     |      | 0.40 | V    |

| V <sub>DM_SRC</sub>    | D- Source Voltage <sup>(2)</sup>                                                                          |                                                                                                                   | 0.5      |      | 0.7  | V    |

| V <sub>DP_SRC</sub>    | D+ Source Voltage <sup>(2)</sup>                                                                          |                                                                                                                   | 0.5      |      | 0.7  | V    |

| $V_{LGC}$              | Logic Threshold                                                                                           |                                                                                                                   | 0.8      |      | 2.0  | V    |

| I <sub>DM_SINK</sub>   | D- Sink Current                                                                                           |                                                                                                                   | 25       |      | 175  | μA   |

| IDP_SINK               | D+ Sink Current                                                                                           |                                                                                                                   | 25       |      | 175  | μA   |

| I <sub>DP_SRC</sub>    | Data Contact Detect Current Source                                                                        |                                                                                                                   |          |      | 13   | μA   |

| t <sub>DCD_DBNC</sub>  | Data Contact Detect Debounce                                                                              |                                                                                                                   |          |      |      | ms   |

| t <sub>DCD_TOUT</sub>  | Time for DCD to Timeout                                                                                   |                                                                                                                   |          | 450  | 900  | ms   |

| tvdpsrc_on             | D+ Voltage Source On Time                                                                                 |                                                                                                                   | 40       |      |      | ms   |

| t <sub>VDMSRC_ON</sub> | D- Voltage Source On Time                                                                                 |                                                                                                                   | 40       |      |      | ms   |

| Notes:                 |                                                                                                           |                                                                                                                   |          |      |      |      |

#### Notes:

- 1. Guaranteed by characterization; not production tested.

- 2. The voltage source,  $V_{DP\_SRC}/V_{DM\_SRC}$ , is able to source at least 250 $\mu$ A when the output voltage is in the specified range. This voltage source should not pull DP\_CON / DM\_CON below 2.2V when DP\_CON / DM\_CON is pulled to a voltage of 3.0V minimum or 3.6V maximum with a resistance of 900 $\Omega$  minimum or 1575 $\Omega$  maximum.

## **AC Electrical Characteristics**

Unless otherwise specified, values are at  $T_A$ =-40 to +85°C; all typical values are for  $V_{CC}$ =3.3V at  $T_A$ =25°C.

| Symbol           | Parameter                                                    | Condition                               | Min. | Тур. | Max. | Unit | Figure   |

|------------------|--------------------------------------------------------------|-----------------------------------------|------|------|------|------|----------|

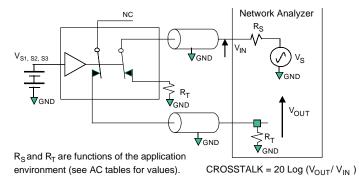

| Xtalk            | Active Channel Crosstalk, DP_CON to                          | $f=1MHz$ , $R_T=50\Omega$ , $C_L=0pF$   |      | -78  |      | dB   | Figure 7 |

| Ataix            | DM_CON <sup>(3)</sup>                                        | $f=240MHz$ , $R_T=50\Omega$ , $C_L=0pF$ |      | -36  |      | QD.  | riguic 7 |

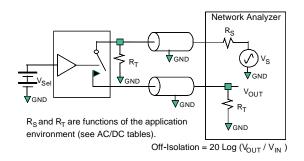

| O <sub>IRR</sub> | Off Isolation Rejection Ratio, DM HOST to DM CON, DP HOST to | $f=1MHz$ , $R_T=50\Omega$ , $C_L=0pF$   |      | -84  |      | dB   | Figure 6 |

| OIKK             | DP_CON <sup>(3)</sup>                                        | $f=240MHz$ , $R_T=50\Omega$ , $C_L=0pF$ |      | -34  |      | 3    | riguic o |

#### Note:

3. Guaranteed by characterization; not production tested.

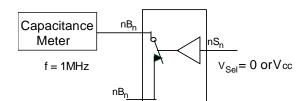

# Capacitance

Unless otherwise specified, values are at  $T_A$ =-40 to +85°C.

| Symbol          | Parameter                                    | Condition                       | Typical | Unit | Figure   |

|-----------------|----------------------------------------------|---------------------------------|---------|------|----------|

| Coff            | DP_CON, DM_CON Off Capacitance (4)           | V <sub>BIAS</sub> =0.2V, f=1MHz | 3.9     | pF   | Figure 8 |

| C <sub>ON</sub> | DP_CON, DM_CON On Capacitance <sup>(4)</sup> | V <sub>BIAS</sub> =0.2V, f=1MHz | 7.2     | pF   | Figure 9 |

#### Note:

4. Guaranteed by characterization; not production tested.

# **Test Diagrams**

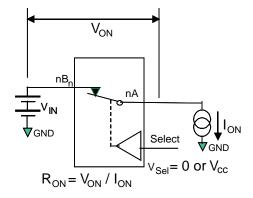

Figure 4. On Resistance

\*\*Each switch port is tested separately.

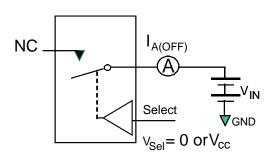

Figure 5. Off Leakage

Figure 6. Channel Off Isolation

Capacitance  $NB_n$   $NB_n$   $NB_n$   $NB_n$   $NB_n$   $NB_n$   $NB_n$   $NB_n$   $NB_n$

Figure 8. Channel Off Capacitance

Figure 7. Active Channel Crosstalk

Figure 9. Channel On Capacitance

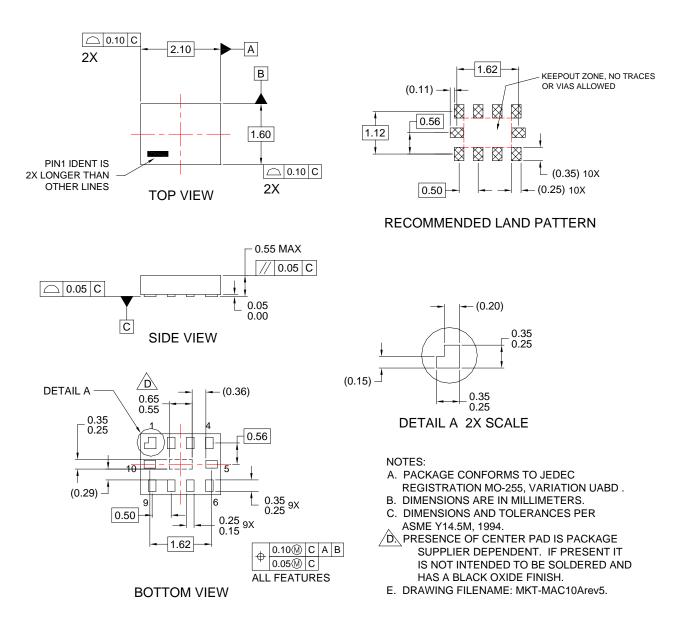

# **Physical Dimensions**

Figure 10. 10-Lead, MicroPak™

| Part Number | Top Mark | Operating Temperature Range |                                                | Packing<br>Method |

|-------------|----------|-----------------------------|------------------------------------------------|-------------------|

| FSA831L10X  | KY       | -40 to 85°C                 | 10-Lead, MicroPak™ 1.6 x 2.1mm,<br>0.5mm Pitch | Tape & Reel       |

Package drawings are provided as a service to customers considering ON Semiconductor components. Drawings may change in any manner without notice. Please note the revision and/or date on the drawing and contact a ON Semiconductor representative to verify or obtain the most recent revision. Package specifications do not expand the terms of Fairchild's worldwide terms and conditions, specifically the warranty therein, which covers ON Semiconductor products.

ON Semiconductor and III) are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at <a href="www.onsemi.com/site/pdf/Patent-Marking.pdf">www.onsemi.com/site/pdf/Patent-Marking.pdf</a>. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages.

Buyer is responsible for its products and applications using ON Semiconductor products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by ON Semiconductor. "Typical" parameters which may be provided in ON Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights nor the rights of others. ON Semiconductor products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold ON Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that ON Semiconductor was negligent regarding the design or manufacture of the part. ON Semiconductor is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

#### **PUBLICATION ORDERING INFORMATION**

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor 19521 E. 32nd Pkwy, Aurora, Colorado 80011 USA Phone: 303-675-2175 or 800-344-3860 Toll Free USA/Canada Fax: 303-675-2176 or 800-344-3867 Toll Free USA/Canada Email: orderlit@onsemi.com

N. American Technical Support: 800-282-9855 Toll Free USA/Canada Europe, Middle East and Africa Technical Support:

Phone: 421 33 790 2910 Japan Customer Focus Center Phone: 81-3-5817-1050

ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative

# **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Battery Management category:

Click to view products by ON Semiconductor manufacturer:

Other Similar products are found below:

MP26121DQ-LF-P NCP1855FCCT1G FAN54063UCX LC05132C01NMTTTG SN2040DSQR ME4075AM5G AP5054HTCER XPD977B

XPD977B18 4056H DW01 DW06 CM1002-UD CM1002-W CM1002-X CM1002-Y CM1006-B CM1006-Q CM1006-WB CM1006-LCD

CM1006-LBD CM1006-WF CM1006-LF CM1006-WG CM1006-WH CM1006-LG CM1003-S02BD CM1003-S09EA CM1003-S10ED

CM1003-S11ED CM1003-S12BC CM1003-S13CC CM1003-S24BC CM1003-S26BC CM1003-WAD CM1003-BBD CM1003-BFD

CM1003-BND CM1003-BLD CM1003-DAD CM1003-BMD CM1003-BPD CM1003-BKD CM1003-BAE CM1003-BHE CM1102B-FF

CM1102B-FD CM1102B-GD CM1112-DAE CM1112-DBE