**ON Semiconductor**

Is Now

# Onsemi

To learn more about onsemi<sup>™</sup>, please visit our website at <u>www.onsemi.com</u>

onsemi and ONSEMI. and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. onsemi reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product factures, availability, functionality, or suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using onsemi products, including compliance with all laws, regulations and asfety requirements or standards, regardless of any support or applications information provided by onsemi. "Typical" parameters which may be provided in onsemi data sheets and/or by customer's technical experts. onsemi products and actal performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. onsemi products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use onsemi products for any such unintended or unauthorized application, Buyer shall indemnify and hold onsemi and its officers, employees, subsidiari

## 1280 (H) x 720 (V) Interline CCD Image Sensor

#### Description

The ON Semiconductor KAI–01150 Image Sensor is a 720p format (1280 x 720 pixel) CCD in a 1/2" optical format. Based on the TRUESENSE 5.5 micron Interline Transfer CCD Platform, the sensor features broad dynamic range, excellent imaging performance, and a flexible readout architecture that enables use of 1, 2, or 4 outputs for full resolution readout of 138 frames per second. A vertical overflow drain structure suppresses image blooming and enables electronic shuttering for precise exposure control.

#### Table 1. GENERAL SPECIFICATIONS

| Parameter                                                                                    | Typical Value                                                     |

|----------------------------------------------------------------------------------------------|-------------------------------------------------------------------|

| Architecture                                                                                 | Interline CCD, Progressive Scan                                   |

| Total Number of Pixels                                                                       | 1364 (H) × 760 (V)                                                |

| Number of Effective Pixels                                                                   | 1320 (H) × 736 (V)                                                |

| Number of Active Pixels                                                                      | 1280 (H) × 720 (V)                                                |

| Pixel Size                                                                                   | 5.5 μm (H) × 5.5 μm (V)                                           |

| Active Image Size                                                                            | 7.04 mm (H) × 3.96 mm (V)<br>8.08 mm (diag.), 1/2" Optical Format |

| Aspect Ratio                                                                                 | 16:9                                                              |

| Number of Outputs                                                                            | 1, 2, or 4                                                        |

| Charge Capacity                                                                              | 20,000 electrons                                                  |

| Output Sensitivity                                                                           | 34 μV/e⁻                                                          |

| Quantum Efficiency<br>Pan (-ABA, -QBA, -PBA)<br>R, G, B (-FBA, -QBA)<br>R, G, B (-CBA, -PBA) | 44%<br>31%, 37%, 38%<br>29%, 37%, 39%                             |

| Base ISO<br>KAI-01150-ABA<br>KAI-01150-FBA<br>KAI-01150-CBA<br>KAI-01150-PBA                 | 330<br>170<br>150<br>330                                          |

| Read Noise (f = 40 MHz)                                                                      | 12 e⁻ rms                                                         |

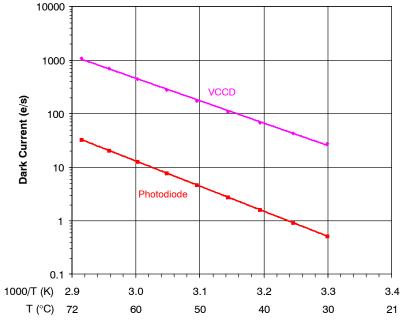

| Dark Current<br>Photodiode / VCCD                                                            | 7 / 140 e⁻/s                                                      |

| Dark Current Doubling Temp<br>Photodiode / VCCD                                              | 7°C / 9°C                                                         |

| Dynamic Range                                                                                | 64 dB                                                             |

| Charge Transfer Efficiency                                                                   | 0.999999                                                          |

| Blooming Suppression                                                                         | > 300 X                                                           |

| Smear                                                                                        | –100 dB                                                           |

| Image Lag                                                                                    | < 10 electrons                                                    |

| Maximum Pixel Clock Speed                                                                    | 40 MHz                                                            |

| Maximum Frame Rate<br>Quad / Dual / Single Output                                            | 138 / 69 / 36 fps                                                 |

| Package Options                                                                              | 68 Pin PGA<br>64 Pin CLCC                                         |

| Cover Glass                                                                                  | AR Coated, 2-Sides or<br>Clear Glass                              |

NOTE: All Parameters are specified at T = 40°C unless otherwise noted.

#### **ON Semiconductor®**

www.onsemi.com

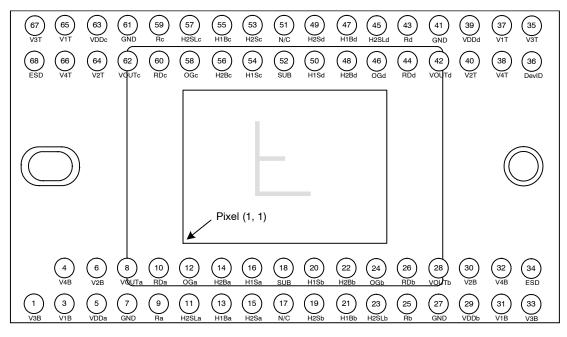

#### Figure 1. KAI-01150 Interline CCD Image Sensor

#### Features

- Bayer Color Pattern, TRUESENSE Sparse Color Filter Pattern, and Monochrome Configurations

- Progressive Scan Readout

- Flexible Readout Architecture

- High Frame Rate

- High Sensitivity

- Low Noise Architecture

- Excellent Smear Performance

- Package Pin Reserved for Device Identification

#### Applications

- Intelligent Traffic Systems

- Security / Surveillance

- Industrial Imaging

#### **ORDERING INFORMATION**

See detailed ordering and shipping information on page 2 of this data sheet.

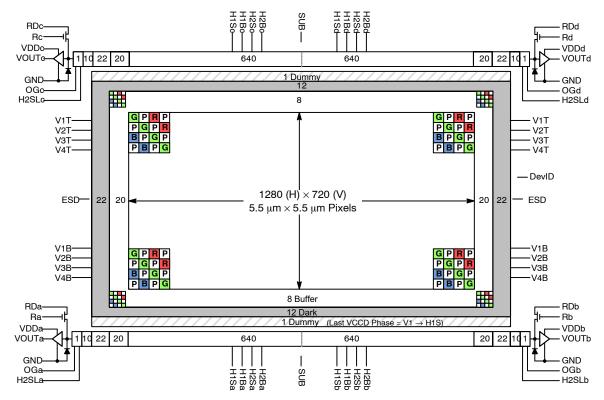

The sensor is available with the TRUESENSE Sparse Color Filter Pattern, a technology which provides a 2x improvement in light sensitivity compared to a standard color Bayer part. The sensor shares common PGA pin-out and electrical configurations with other devices based on the TRUESENSE 5.5 micron Interline Transfer CCD Platform, allowing a single camera design to support multiple members of this sensor family.

#### **ORDERING INFORMATION**

#### Standard Devices

See full datasheet for ordering information associated with devices no longer recommended for new designs.

#### Table 2. ORDERING INFORMATION – STANDARD DEVICES

| Part Number         |                                                                                                                                                     |               |  |  |  |  |

|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|---------------|--|--|--|--|

| KAI-01150-ABA-JD-BA | Monochrome, Telecentric Microlens, PGA Package, Sealed Clear Cover Glass with AR Coating (Both Sides), Standard Grade                               |               |  |  |  |  |

| KAI-01150-ABA-JD-AE | Monochrome, Telecentric Microlens, PGA Package, Sealed Clear Cover Glass with AR Coating (Both Sides), Engineering Grade                            | KAI-01150-ABA |  |  |  |  |

| KAI-01150-ABA-FD-BA | Monochrome, Telecentric Microlens, CLCC Package, Sealed Clear Cover Glass with AR Coating (Both Sides), Standard Grade                              | Serial Number |  |  |  |  |

| KAI-01150-ABA-FD-AE | Monochrome, Telecentric Microlens, CLCC Package, Sealed Clear Cover Glass with AR Coating (Both Sides), Engineering Grade                           |               |  |  |  |  |

| KAI-01150-FBA-JD-BA | Gen2 Color (Bayer RGB), Telecentric Microlens, PGA Package, Sealed Clear Cover Glass with AR Coating (Both Sides), Standard Grade                   |               |  |  |  |  |

| KAI-01150-FBA-JD-AE | Gen2 Color (Bayer RGB), Telecentric Microlens, PGA Package, Sealed Clear Cover Glass with AR Coating (Both Sides), Engineering Grade                |               |  |  |  |  |

| KAI-01150-FBA-FD-BA | Gen2 Color (Bayer RGB), Telecentric Microlens, CLCC Package, Sealed Clear<br>Cover Glass with AR Coating (Both Sides), Standard Grade               | KAI-01150-FBA |  |  |  |  |

| KAI-01150-FBA-FD-AE | Gen2 Color (Bayer RGB), Telecentric Microlens, CLCC Package, Sealed Clear<br>Cover Glass with AR Coating (Both Sides), Engineering Grade            | Serial Number |  |  |  |  |

| KAI-01150-FBA-JB-B2 | Gen2 Color (Bayer RGB), Telecentric Microlens, PGA Package, Sealed Clear<br>Cover Glass (no coatings), Grade 2                                      |               |  |  |  |  |

| KAI-01150-FBA-JB-AE | Gen2 Color (Bayer RGB), Telecentric Microlens, PGA Package, Sealed Clear<br>Cover Glass (no coatings), Engineering Grade                            |               |  |  |  |  |

| KAI-01150-QBA-JD-BA | Gen2 Color (TRUESENSE Sparse CFA), Telecentric Microlens, PGA Package,<br>Sealed Clear Cover Glass with AR Coating (Both Sides), Standard Grade     |               |  |  |  |  |

| KAI-01150-QBA-JD-AE | Gen2 Color (TRUESENSE Sparse CFA), Telecentric Microlens, PGA Package,<br>Sealed Clear Cover Glass with AR Coating (Both Sides), Engineering Grade  | KAI-01150-QBA |  |  |  |  |

| KAI-01150-QBA-FD-BA | Gen2 Color (TRUESENSE Sparse CFA), Telecentric Microlens, CLCC Package,<br>Sealed Clear Cover Glass with AR Coating (Both Sides), Standard Grade    | Serial Number |  |  |  |  |

| KAI-01150-QBA-FD-AE | Gen2 Color (TRUESENSE Sparse CFA), Telecentric Microlens, CLCC Package,<br>Sealed Clear Cover Glass with AR Coating (Both Sides), Engineering Grade |               |  |  |  |  |

See the ON Semiconductor *Device Nomenclature* document (TND310/D) for a full description of the naming convention used for image sensors. For reference documentation, including information on evaluation kits, please visit our web site at <u>www.onsemi.com</u>.

## Not Recommended for New Designs

#### Table 3. ORDERING INFORMATION – NOT RECOMMENDED FOR NEW DESIGNS

| Part Number         | Description                                                                                                                                         | Marking Code  |  |

|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|---------------|--|

| KAI-01150-CBA-JD-BA | Gen1 Color (Bayer RGB), Telecentric Microlens, PGA Package, Sealed Clear<br>Cover Glass with AR Coating (Both Sides), Standard Grade                |               |  |

| KAI-01150-CBA-JD-AE | Gen1 Color (Bayer RGB), Telecentric Microlens, PGA Package, Sealed Clear<br>Cover Glass with AR Coating (Both Sides), Engineering Grade             | -             |  |

| KAI-01150-CBA-FD-BA | Gen1 Color (Bayer RGB), Telecentric Microlens, CLCC Package, Sealed Clear Cover Glass with AR Coating (Both Sides), Standard Grade                  | KAI-01150-CBA |  |

| KAI-01150-CBA-FD-AE | Gen1 Color (Bayer RGB), Telecentric Microlens, CLCC Package, Sealed Clear<br>Cover Glass with AR Coating (Both Sides), Engineering Grade            | Serial Number |  |

| KAI-01150-CBA-JB-B2 | Gen1 Color (Bayer RGB), Telecentric Microlens, PGA Package, Sealed Clear Cover Glass (no coatings), Grade 2                                         | -             |  |

| KAI-01150-CBA-JB-AE | Gen1 Color (Bayer RGB), Telecentric Microlens, PGA Package, Sealed Clear Cover Glass (no coatings), Engineering Grade                               |               |  |

| KAI-01150-PBA-JD-BA | Gen1 Color (TRUESENSE Sparse CFA), Telecentric Microlens, PGA Package,<br>Sealed Clear Cover Glass with AR Coating (Both Sides), Standard Grade     |               |  |

| KAI-01150-PBA-JD-AE | Gen1 Color (TRUESENSE Sparse CFA), Telecentric Microlens, PGA Package,<br>Sealed Clear Cover Glass with AR Coating (Both Sides), Engineering Grade  | KAI-01150-PBA |  |

| KAI-01150-PBA-FD-BA | Gen1 Color (TRUESENSE Sparse CFA), Telecentric Microlens, CLCC Package,<br>Sealed Clear Cover Glass with AR Coating (Both Sides), Standard Grade    | Serial Number |  |

| KAI-01150-PBA-FD-AE | Gen1 Color (TRUESENSE Sparse CFA), Telecentric Microlens, CLCC Package,<br>Sealed Clear Cover Glass with AR Coating (Both Sides), Engineering Grade |               |  |

#### **DEVICE DESCRIPTION**

#### Architecture

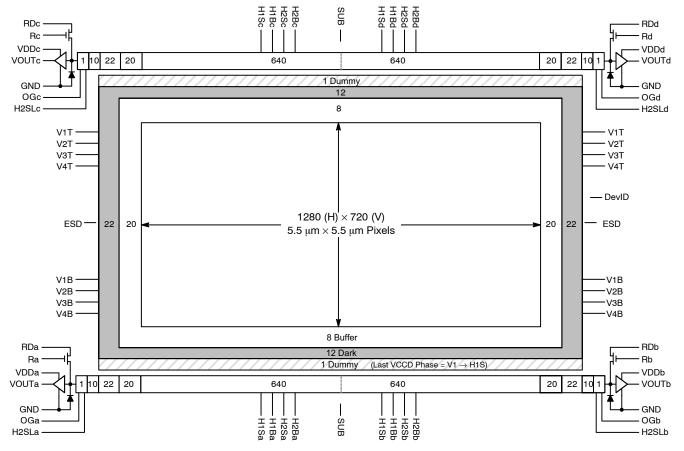

Figure 2. Block Diagram

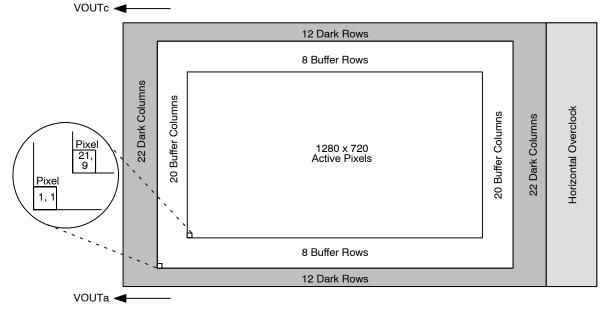

#### **Dark Reference Pixels**

There are 12 dark reference rows at the top and 12 dark rows at the bottom of the image sensor. The dark rows are not entirely dark and so should not be used for a dark reference level. Use the 22 dark columns on the left or right side of the image sensor as a dark reference.

Under normal circumstances use only the center 20 columns of the 22 column dark reference due to potential light leakage.

#### **Dummy Pixels**

Within each horizontal shift register there are 11 leading additional shift phases. These pixels are designated as dummy pixels and should not be used to determine a dark reference level.

In addition, there is one dummy row of pixels at the top and bottom of the image.

#### **Active Buffer Pixels**

20 unshielded pixels adjacent to any leading or trailing dark reference regions are classified as active buffer pixels.

These pixels are light sensitive but are not tested for defects and non-uniformities.

#### Image Acquisition

An electronic representation of an image is formed when incident photons falling on the sensor plane create electron-hole pairs within the individual silicon photodiodes. These photoelectrons are collected locally by the formation of potential wells at each photosite. Below photodiode saturation, the number of photoelectrons collected at each pixel is linearly dependent upon light level and exposure time and non-linearly dependent on wavelength. When the photodiodes charge capacity is reached, excess electrons are discharged into the substrate to prevent blooming.

#### **ESD** Protection

Adherence to the power-up and power-down sequence is critical. Failure to follow the proper power-up and power-down sequences may cause damage to the sensor. See Power-Up and Power-Down Sequence section.

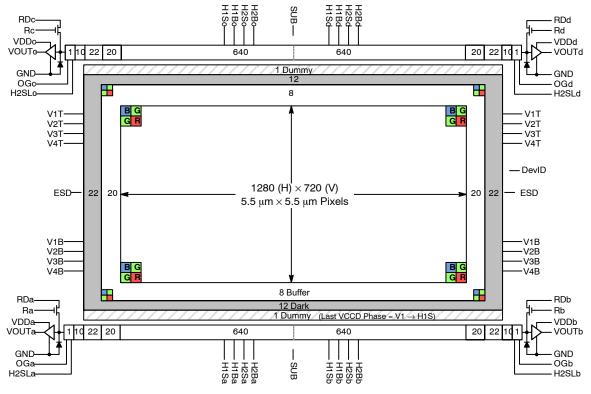

#### **Bayer Color Filter Pattern**

Figure 3. Bayer Color Filter Pattern

#### TRUESENSE Sparse Color Filter Pattern

#### Figure 4. TRUESENSE Sparse Color Filter Pattern

#### **Physical Description**

PGA Pin Description and Device Orientation

Figure 5. PGA Package Pin Designations – Top View

#### Table 4. PGA PACKAGE PIN DESCRIPTION

| Pin | Name  | Description                                                    |

|-----|-------|----------------------------------------------------------------|

| 1   | V3B   | Vertical CCD Clock, Phase 3, Bottom                            |

| 3   | V1B   | Vertical CCD Clock, Phase 1, Bottom                            |

| 4   | V4B   | Vertical CCD Clock, Phase 4, Bottom                            |

| 5   | VDDa  | Output Amplifier Supply, Quadrant a                            |

| 6   | V2B   | Vertical CCD Clock, Phase 2, Bottom                            |

| 7   | GND   | Ground                                                         |

| 8   | VOUTa | Video Output, Quadrant a                                       |

| 9   | Ra    | Reset Gate, Quadrant a                                         |

| 10  | RDa   | Reset Drain, Quadrant a                                        |

| 11  | H2SLa | Horizontal CCD Clock, Phase 2, Storage, Last Phase, Quadrant a |

| 12  | OGa   | Output Gate, Quadrant a                                        |

| 13  | H1Ba  | Horizontal CCD Clock, Phase 1, Barrier, Quadrant a             |

| 14  | H2Ba  | Horizontal CCD Clock, Phase 2, Barrier, Quadrant a             |

| 15  | H2Sa  | Horizontal CCD Clock, Phase 2, Storage, Quadrant a             |

| 16  | H1Sa  | Horizontal CCD Clock, Phase 1, Storage, Quadrant a             |

| 17  | N/C   | No Connect                                                     |

| 18  | SUB   | Substrate                                                      |

| 19  | H2Sb  | Horizontal CCD Clock, Phase 2, Storage, Quadrant b             |

| 20  | H1Sb  | Horizontal CCD Clock, Phase 1, Storage, Quadrant b             |

| 21  | H1Bb  | Horizontal CCD Clock, Phase 1, Barrier, Quadrant b             |

| 22  | H2Bb  | Horizontal CCD Clock, Phase 2, Barrier, Quadrant b             |

| 23  | H2SLb | Horizontal CCD Clock, Phase 1, Storage, Last Phase, Quadrant b |

| 24  | OGb   | Output Gate, Quadrant b                                        |

#### Pin Name Description 25 Rb Reset Gate, Quadrant b RDb Reset Drain, Quadrant b 26 27 GND Ground VOUTb Video Output, Quadrant b 28 29 VDDb Output Amplifier Supply, Quadrant b 30 V2B Vertical CCD Clock, Phase 2, Bottom 31 V1B Vertical CCD Clock, Phase 1, Bottom V4B Vertical CCD Clock, Phase 4, Bottom 32 V3B Vertical CCD Clock, Phase 3, Bottom 33 34 ESD ESD Protection Disable 35 V3T Vertical CCD Clock, Phase 3, Top 36 DevID **Device Identification** V1T Vertical CCD Clock, Phase 1, Top 37 38 V4T Vertical CCD Clock, Phase 4, Top VDDd Output Amplifier Supply, Quadrant d 39 40 V2T Vertical CCD Clock, Phase 2, Top GND Ground 41 VOUTd 42 Video Output, Quadrant d 43 Rd Reset Gate, Quadrant d RDd Reset Drain, Quadrant d 44 H2SLd Horizontal CCD Clock, Phase 2, Storage, Last Phase, Quadrant d 45 46 OGd Output Gate, Quadrant d H1Bd Horizontal CCD Clock, Phase 1, Barrier, Quadrant d 47 H2Bd Horizontal CCD Clock, Phase 2, Barrier, Quadrant d 48 H2Sd Horizontal CCD Clock, Phase 2, Storage, Quadrant d 49 Horizontal CCD Clock, Phase 1, Storage, Quadrant d 50 H1Sd 51 N/C No Connect SUB 52 Substrate 53 H2Sc Horizontal CCD Clock, Phase 2, Storage, Quadrant c 54 H1Sc Horizontal CCD Clock, Phase 1, Storage, Quadrant c 55 H1Bc Horizontal CCD Clock, Phase 1, Barrier, Quadrant c 56 H2Bc Horizontal CCD Clock, Phase 2, Barrier, Quadrant c H2SLc Horizontal CCD Clock, Phase 2, Storage, Last Phase, Quadrant c 57 OGc 58 Output Gate, Quadrant c Rc Reset Gate, Quadrant c 59 60 RDc Reset Drain, Quadrant c GND 61 Ground 62 VOUTc Video Output, Quadrant c 63 VDDc Output Amplifier Supply, Quadrant c 64 V2T Vertical CCD Clock, Phase 2, Top V1T Vertical CCD Clock, Phase 1, Top 65 V4T 66 Vertical CCD Clock, Phase 4, Top 67 V3T Vertical CCD Clock, Phase 3, Top ESD EDS Protection Disable 68

#### Table 4. PGA PACKAGE PIN DESCRIPTION (continued)

1. Liked named pins are internally connected and should have a common drive signal.

2. N/C pins (17, 51) should be left floating.

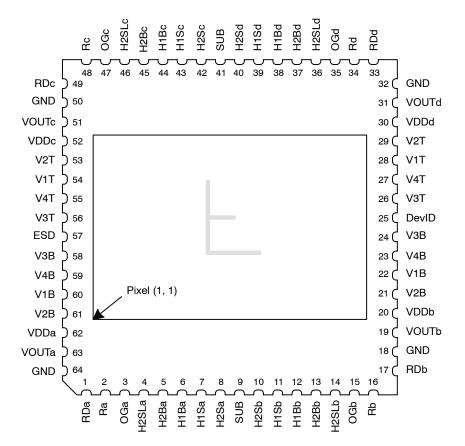

Ceramic Leadless Chip Carrier Pin Description

| Pin | Name  | Description                                                    |  |

|-----|-------|----------------------------------------------------------------|--|

| 1   | RDa   | Reset Drain, Quadrant a                                        |  |

| 2   | Ra    | Reset Gate, Quadrant a                                         |  |

| 3   | OGa   | Output Gate, Quadrant a                                        |  |

| 4   | H2SLa | Horizontal CCD Clock, Phase 2, Storage, Last Phase, Quadrant a |  |

| 5   | H2Ba  | Horizontal CCD Clock, Phase 2, Barrier, Quadrant a             |  |

| 6   | H1Ba  | Horizontal CCD Clock, Phase 1, Barrier, Quadrant a             |  |

| 7   | H1Sa  | Horizontal CCD Clock, Phase 1, Storage, Quadrant a             |  |

| 8   | H2Sa  | Horizontal CCD Clock, Phase 2, Storage, Quadrant a             |  |

| 9   | SUB   | Substrate                                                      |  |

| 10  | H2Sb  | Horizontal CCD Clock, Phase 2, Storage, Quadrant b             |  |

| 11  | H1Sb  | Horizontal CCD Clock, Phase 1, Storage, Quadrant b             |  |

| 12  | H1Bb  | Horizontal CCD Clock, Phase 1, Barrier, Quadrant b             |  |

| 13  | H2Bb  | Horizontal CCD Clock, Phase 2, Barrier, Quadrant b             |  |

| 14  | H2SLb | Horizontal CCD Clock, Phase 2, Storage, Last Phase, Quadrant b |  |

| 15  | OGb   | Output Gate, Quadrant b                                        |  |

| 16  | Rb    | Reset Gate, Quadrant b                                         |  |

| 17  | RDb   | Reset Drain, Quadrant b                                        |  |

| 18  | GND   | Ground                                                         |  |

| 19  | VOUTb | Video Output, Quadrant b                                       |  |

#### Table 5. CLCC PACKAGE PIN DESCRIPTION

#### Pin Name Description VDDb 20 Output Amplifier Supply, Quadrant b V2B Vertical CCD Clock, Phase 2, Bottom 21 22 V1B Vertical CCD Clock, Phase 1, Bottom V4B Vertical CCD Clock, Phase 4, Bottom 23 V3B Vertical CCD Clock, Phase 3, Bottom 24 25 DevID **Device Identification** 26 V3T Vertical CCD Clock, Phase 3, Top V4T Vertical CCD Clock, Phase 4, Top 27 V1T Vertical CCD Clock, Phase 1, Top 28 V2T 29 Vertical CCD Clock, Phase 2, Top 30 VDDd Output Amplifier Supply, Quadrant d 31 VOUTd Video Output, Quadrant d GND Ground 32 RDd 33 Reset Drain, Quadrant d Rd Reset Gate, Quadrant d 34 Output Gate, Quadrant d 35 OGd H2SLd Horizontal CCD Clock, Phase 2, Storage, Last Phase, Quadrant d 36 Horizontal CCD Clock, Phase 2, Barrier, Quadrant d 37 H2Bd 38 H1Bd Horizontal CCD Clock, Phase 1, Barrier, Quadrant d 39 H1Sd Horizontal CCD Clock, Phase 1, Storage, Quadrant d H2Sd Horizontal CCD Clock, Phase 2, Storage, Quadrant d 40 41 SUB Substrate H2Sc Horizontal CCD Clock, Phase 2, Storage, Quadrant c 42 43 H1Sc Horizontal CCD Clock, Phase 1, Storage, Quadrant c H1Bc Horizontal CCD Clock, Phase 1, Barrier, Quadrant c 44 45 H2Bc Horizontal CCD Clock, Phase 2, Barrier, Quadrant c 46 H2SLc Horizontal CCD Clock, Phase 2, Storage, Last Phase, Quadrant c OGc 47 Output Gate, Quadrant c Rc Reset Gate, Quadrant c 48 49 RDc Reset Drain, Quadrant c 50 GND Ground 51 VOUTc Video Output, Quadrant c VDDc Output Amplifier Supply, Quadrant c 52 V2T 53 Vertical CCD Clock, Phase 2, Top V1T Vertical CCD Clock, Phase 1, Top 54 55 V4T Vertical CCD Clock, Phase 4, Top V3T Vertical CCD Clock, Phase 3, Top 56 57 ESD ESD Protection Disable 58 V3B Vertical CCD Clock, Phase 3, Bottom 59 V4B Vertical CCD Clock, Phase 4, Bottom V1B Vertical CCD Clock, Phase 1, Bottom 60 61 V2B Vertical CCD Clock, Phase 2, Bottom 62 VDDa Output Amplifier Supply, Quadrant a VOUTa 63 Video Output, Quadrant a 64 GND Ground

#### Table 5. CLCC PACKAGE PIN DESCRIPTION (continued)

1. Liked named pins are internally connected and should have a common drive signal.

#### **IMAGING PERFORMANCE**

#### **Table 6. TYPICAL OPERATION CONDITIONS**

Unless otherwise noted, the Imaging Performance Specifications are measured using the following conditions.

| Description  | Condition                                       | Notes                                       |

|--------------|-------------------------------------------------|---------------------------------------------|

| Light Source | Continuous red, green and blue LED illumination | For monochrome sensor, only green LED used. |

| Operation    | Nominal operating voltages and timing           |                                             |

#### **Table 7. SPECIFICATIONS**

| Description                                             | Symbol                | Min.     | Nom.     | Max. | Units             | Sampling<br>Plan | Temperature<br>Tested At<br>(°C) | Notes |

|---------------------------------------------------------|-----------------------|----------|----------|------|-------------------|------------------|----------------------------------|-------|

| Dark Field Global Non-Uniformity                        | DSNU                  | -        | -        | 2.0  | mVpp              | Die              | 27, 40                           |       |

| Bright Field Global Non-Uniformity                      |                       | -        | 2.0      | 5.0  | %rms              | Die              | 27, 40                           | 1     |

| Bright Field Global Peak to Peak<br>Non–Uniformity      | PRNU                  | -        | 5.0      | 15.0 | %pp               | Die              | 27, 40                           | 1     |

| Bright Field Center Non–Uniformity                      |                       | -        | 1.0      | 2.0  | %rms              | Die              | 27, 40                           | 1     |

| Maximum Photoresponse<br>Nonlinearity                   | NL                    | -        | 2        | _    | %                 | Design           |                                  | 2     |

| Maximum Gain Difference Between<br>Outputs              | ΔG                    | -        | 10       | -    | %                 | Design           |                                  | 2     |

| Maximum Signal Error due to<br>Nonlinearity Differences | ΔNL                   | -        | 1        | -    | %                 | Design           |                                  | 2     |

| Horizontal CCD Charge Capacity                          | HNe                   | -        | 55       | -    | ke-               | Design           |                                  |       |

| Vertical CCD Charge Capacity                            | VNe                   | -        | 45       | -    | ke-               | Design           |                                  |       |

| Photodiode Charge Capacity                              | PNe                   | -        | 20       | -    | ke-               | Die              | 27, 40                           | 3     |

| Horizontal CCD Charge Transfer<br>Efficiency            | HCTE                  | 0.999995 | 0.999999 | -    |                   | Die              |                                  |       |

| Vertical CCD Charge Transfer<br>Efficiency              | VCTE                  | 0.999995 | 0.999999 | -    |                   | Die              |                                  |       |

| Photodiode Dark Current                                 | lpd                   | -        | 7        | 70   | e/p/s             | Die              | 40                               |       |

| Vertical CCD Dark Current                               | lvd                   | -        | 140      | 400  | e/p/s             | Die              | 40                               |       |

| Image Lag                                               | Lag                   | -        | -        | 10   | e-                | Design           |                                  |       |

| Antiblooming Factor                                     | Xab                   | 300      | -        | -    |                   | Design           |                                  |       |

| Vertical Smear                                          | Smr                   | -        | -100     | -    | dB                | Design           |                                  |       |

| Read Noise                                              | n <sub>e-T</sub>      | -        | 12       | -    | e⁻rms             | Design           |                                  | 4     |

| Dynamic Range                                           | DR                    | -        | 64       | -    | dB                | Design           |                                  | 4, 5  |

| Output Amplifier DC Offset                              | V <sub>odc</sub>      | -        | 9.4      | -    | V                 | Die              | 27, 40                           |       |

| Output Amplifier Bandwidth                              | f <sub>-3db</sub>     | -        | 250      | -    | MHz               | Die              |                                  | 6     |

| Output Amplifier Impedance                              | R <sub>OUT</sub>      | -        | 127      | -    | Ω                 | Die              | 27, 40                           |       |

| Output Amplifier Sensitivity                            | $\Delta V / \Delta N$ | -        | 34       | _    | μV/e <sup>-</sup> | Design           |                                  |       |

1. Per color

2. Value is over the range of 10% to 90% of photodiode saturation.

The operating value of the substrate voltage, VAB, will be marked on the shipping container for each device. The value of VAB is set such that the photodiode charge capacity is 680 mV.

At 40 MHz

Uses 20LOG (PNe/ n<sub>e-T</sub>)

Assumes 5 pF load.

#### Table 8. KAI-01150-ABA AND KAI-01150-PBA CONFIGURATIONS

| Description                           | Symbol            | Min. | Nom. | Max. | Units | Sampling<br>Plan | Temperature<br>Tested At (°C) | Notes |

|---------------------------------------|-------------------|------|------|------|-------|------------------|-------------------------------|-------|

| Peak Quantum Efficiency               | QE <sub>max</sub> | -    | 44   | -    | %     | Design           |                               |       |

| Peak Quantum Efficiency<br>Wavelength | λQE               | I    | 480  | -    | nm    | Design           |                               |       |

#### Table 9. KAI-01150-FBA AND KAI-01150-QBA GEN2 COLOR CONFIGURATIONS WITH MAR GLASS

| Description                           |                      | Symbol            | Min. | Nom.              | Max. | Units | Sampling<br>Plan | Temperature<br>Tested At (°C) | Notes |

|---------------------------------------|----------------------|-------------------|------|-------------------|------|-------|------------------|-------------------------------|-------|

| Peak Quantum Efficiency               | Blue<br>Green<br>Red | QE <sub>max</sub> | -    | 38<br>37<br>31    | _    | %     | Design           |                               |       |

| Peak Quantum Efficiency<br>Wavelength | Blue<br>Green<br>Red | λQE               | -    | 460<br>530<br>605 | _    | nm    | Design           |                               |       |

#### Table 10. KAI-01150-CBA AND KAI-01150-PBA GEN1 COLOR CONFIGURATIONS WITH MAR GLASS

| Description                           |                      | Symbol            | Min. | Nom.              | Max. | Units | Sampling<br>Plan | Temperature<br>Tested At (°C) | Notes |

|---------------------------------------|----------------------|-------------------|------|-------------------|------|-------|------------------|-------------------------------|-------|

| Peak Quantum Efficiency               | Blue<br>Green<br>Red | QE <sub>max</sub> | -    | 39<br>37<br>29    | -    | %     | Design           |                               | 1     |

| Peak Quantum Efficiency<br>Wavelength | Blue<br>Green<br>Red | λQE               | _    | 470<br>540<br>620 | _    | nm    | Design           |                               | 1     |

1. This color filter set configuration (Gen1) is not recommended for new designs.

#### Table 11. KAI-01150-FBA GEN2 COLOR CONFIGURATIONS WITH CLEAR GLASS

| Description                           |                      | Symbol            | Min. | Nom.              | Max. | Units | Sampling<br>Plan | Temperature<br>Tested At (°C) | Notes |

|---------------------------------------|----------------------|-------------------|------|-------------------|------|-------|------------------|-------------------------------|-------|

| Peak Quantum Efficiency               | Blue<br>Green<br>Red | QE <sub>max</sub> | -    | 35<br>34<br>29    | -    | %     | Design           |                               |       |

| Peak Quantum Efficiency<br>Wavelength | Blue<br>Green<br>Red | λQE               | -    | 460<br>530<br>605 | -    | nm    | Design           |                               |       |

#### Table 12. KAI-01150-CBA GEN1 COLOR CONFIGURATIONS WITH CLEAR GLASS

| Description                           |                      | Symbol            | Min. | Nom.              | Max. | Units | Sampling<br>Plan | Temperature<br>Tested At (°C) | Notes |

|---------------------------------------|----------------------|-------------------|------|-------------------|------|-------|------------------|-------------------------------|-------|

| Peak Quantum Efficiency               | Blue<br>Green<br>Red | QE <sub>max</sub> | -    | 36<br>34<br>27    | _    | %     | Design           |                               | 1     |

| Peak Quantum Efficiency<br>Wavelength | Blue<br>Green<br>Red | λQE               | _    | 470<br>540<br>620 | _    | nm    | Design           |                               | 1     |

1. This color filter set configuration (Gen1) is not recommended for new designs.

#### **TYPICAL PERFORMANCE CURVES**

#### **Quantum Efficiency**

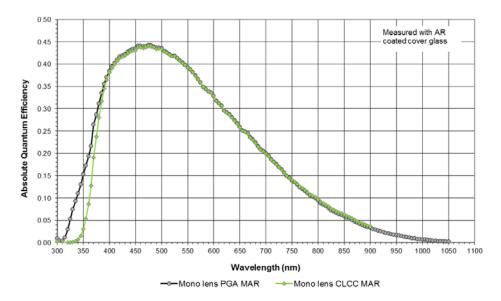

Monochrome with Microlens

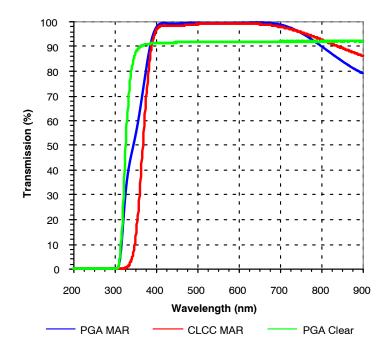

NOTE: The PGA and CLCC versions have different quantum efficiencies due to differences in the cover glass transmission. See Figure 34: Cover Glass Transmission for more details.

Figure 7. Monochrome with Microlens Quantum Efficiency

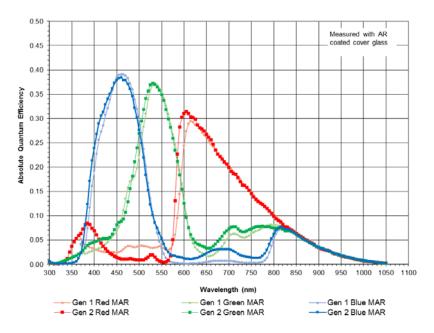

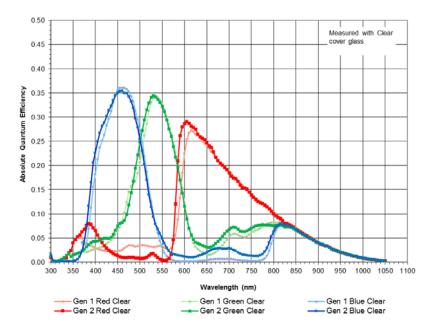

Color (Bayer RGB) with Microlens and MAR Cover Glass (Gen2 and Gen1 CFA)

Figure 8. MAR Glass Color (Bayer) with Microlens Quantum Efficiency

Color (Bayer RGB) with Microlens and Clear Cover Glass (Gen2 and Gen1 CFA)

Figure 9. Clear Glass Color (Bayer) with Microlens Quantum Efficiency

#### Color (TRUESENSE Sparse CFA) with Microlens (Gen2 and Gen1 CFA)

Figure 10. Color (TRUESENSE Sparse CFA) with Microlens Quantum Efficiency

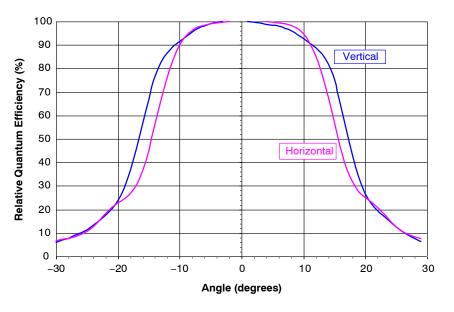

#### Angular Quantum Efficiency

For the curves marked "Horizontal", the incident light angle is varied in a plane parallel to the HCCD. For the curves marked "Vertical", the incident light angle is varied in a plane parallel to the VCCD.

#### Monochrome with Microlens

Figure 11. Monochrome with Microlens Angular Quantum Efficiency

Dark Current vs. Temperature

Figure 12. Dark Current vs. Temperature

#### **Power-Estimated**

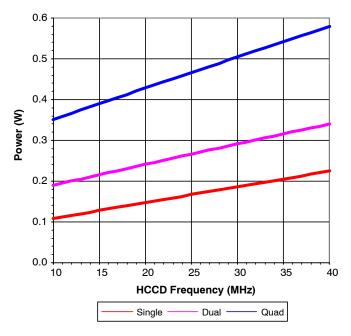

Figure 13. Power

**Frame Rates**

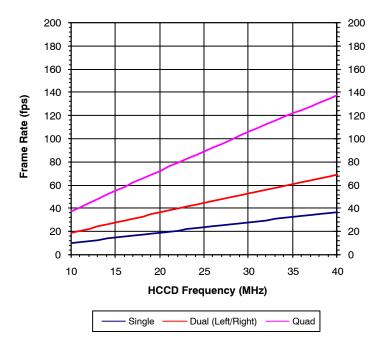

Figure 14. Frame Rates

#### **DEFECT DEFINITIONS**

#### Table 13. OPERATION CONDITIONS FOR DEFECT TESTING AT 40°C

| Description                 | Condition                                                                                                              | Notes |

|-----------------------------|------------------------------------------------------------------------------------------------------------------------|-------|

| Operational Mode            | Two Outputs, Using VOUTa and VOUTc, Continuous Readout                                                                 |       |

| HCCD Clock Frequency        | 10 MHz                                                                                                                 |       |

| Pixels per Line             | 1520                                                                                                                   | 1     |

| Lines per Frame             | 480                                                                                                                    | 2     |

| Line Time                   | 154.9 μs                                                                                                               |       |

| Frame Time                  | 74.4 ms                                                                                                                |       |

| Photodiode Integration Time | Mode A: PD_Tint = Frame Time = 74.4 ms, No Electronic Shutter Used<br>Mode B: PD_Tint = 33 ms, Electronic Shutter Used |       |

| VCCD Integration Time       | 58.9 ms                                                                                                                | 3     |

| Temperature                 | 40°C                                                                                                                   |       |

| Light Source                | Continuous Red, Green and Blue LED Illumination                                                                        | 4     |

| Operation                   | Nominal Operating Voltages and Timing                                                                                  |       |

Horizontal overclocking used.

Vertical overclocking used.

VCCD Integration Time = 380 lines × Line Time, which is the total time a pixel will spend in the VCCD registers.

4. For monochrome sensor, only the green LED is used.

#### Table 14. DEFECT DEFINITIONS FOR TESTING AT 40°C

| Description                             | Definition                                                                                                                                      | Standard<br>Grade | Grade 2 | Notes |

|-----------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|---------|-------|

| Major Dark Field Defective Bright Pixel | $\begin{array}{l} PD\_Tint = Mode \ A \rightarrow Defect \geq 25 \ mV \\ or \\ PD\_Tint = Mode \ B \rightarrow Defect \geq 12 \ mV \end{array}$ | 10                | 10      | 1     |

| Major Bright Field Defective Dark Pixel | Defect ≥ 12%                                                                                                                                    | 10                | 10      | 1     |

| Minor Dark Field Defective Bright Pixel | $\begin{array}{l} PD\_Tint = Mode \ A \rightarrow Defect \geq 13 \ mV \\ or \\ PD\_Tint = Mode \ B \rightarrow Defect \geq 6 \ mV \end{array}$  | 100               | 100     |       |

| Cluster Defect (Standard Grade)         | A group of 2 to 10 contiguous major defective pixels,<br>but no more than 2 adjacent defects horizontally.                                      | 0                 | N/A     | 2     |

| Cluster Defect (Grade 2)                | A group of 2 to 10 contiguous major defective pixels.                                                                                           | N/A               | 5       | 2     |

| Column Defect                           | A group of more than 10 contiguous major defective pixels along a single column.                                                                | 0                 | 0       | 2     |

1. For the color device (KAI-01150-CBA or KAI-01150-PBA), a bright field defective pixel deviates by 12% with respect to pixels of the same color.2. Column and cluster defects are separated by no less than two (2) good pixels in any direction (excluding single pixel defects).

#### Table 15. OPERATION CONDITIONS FOR DEFECT TESTING AT 27°C

| Description                           | Condition                                                                                                              | Notes |

|---------------------------------------|------------------------------------------------------------------------------------------------------------------------|-------|

| Operational Mode                      | Two Outputs, Using VOUTa and VOUTc, Continuous Readout                                                                 |       |

| HCCD Clock Frequency                  | 20 MHz                                                                                                                 |       |

| Pixels per Line                       | 1520                                                                                                                   | 1     |

| Lines per Frame                       | 480                                                                                                                    | 2     |

| Line Time                             | 77.8 μs                                                                                                                |       |

| Frame Time                            | 37.3 ms                                                                                                                |       |

| Photodiode Integration Time (PD_Tint) | Mode A: PD_Tint = Frame Time = 37.3 ms, No Electronic Shutter Used<br>Mode B: PD_Tint = 33 ms, Electronic Shutter Used |       |

| VCCD Integration Time                 | 29.5 ms                                                                                                                | 3     |

| Temperature                           | 27°C                                                                                                                   |       |

| Light Source                          | Continuous Red, Green and Blue LED Illumination                                                                        | 4     |

| Operation                             | Nominal Operating Voltages and Timing                                                                                  |       |

1. Horizontal overclocking used.

Vertical overclocking used.

Vertical overclocking used.

VCCD Integration Time = 380 lines × Line Time, which is the total time a pixel will spend in the VCCD registers.

For monochrome sensor, only the green LED is used.

#### Table 16. DEFECT DEFINITIONS FOR TESTING AT 27°C

| Description                             | Definition                                                                                                                    | Standard<br>Grade | Grade 2 | Notes |

|-----------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|-------------------|---------|-------|

| Major Dark Field Defective Bright Pixel | $\begin{array}{l} PD\_Tint = Mode \ A \to Defect \geq 8 \ mV \\ or \\ PD\_Tint = Mode \ B \to Defect \geq 4 \ mV \end{array}$ | 10                | 10      | 1     |

| Major Bright Field Defective Dark Pixel | Defect ≥ 12%                                                                                                                  | 10                | 10      | 1     |

| Cluster Defect (Standard Grade)         | A group of 2 to 10 contiguous major defective pixels,<br>but no more than 2 adjacent defects horizontally.                    | 0                 | N/A     | 2     |

| Cluster Defect (Grade 2)                | A group of 2 to 10 contiguous major defective pixels.                                                                         | N/A               | 5       | 2     |

| Column Defect                           | A group of more than 10 contiguous major defective pixels along a single column.                                              | 0                 | 0       | 2     |

1. For the color device (KAI-01150-CBA or KAI-01150-PBA), a bright field defective pixel deviates by 12% with respect to pixels of the same color.

2. Column and cluster defects are separated by no less than two (2) good pixels in any direction (excluding single pixel defects).

#### **Defect Map**

The defect map supplied with each sensor is based upon testing at an ambient (27°C) temperature. Minor point defects are not included in the defect map. All defective pixels are reference to pixel 1, 1 in the defect maps. See Figure 15: Regions of Interest for the location of pixel 1, 1.

#### **TEST DEFINITIONS**

#### **Test Regions of Interest**

| Image Area ROI:  | Pixel (1, 1) to Pixel (1320, 736)    |

|------------------|--------------------------------------|

| Active Area ROI: | Pixel (21, 9) to Pixel (1300, 728)   |

| Center ROI:      | Pixel (611, 319) to Pixel (710, 418) |

Only the Active Area ROI pixels are used for performance and defect tests.

#### Overclocking

The test system timing is configured such that the sensor is overclocked in both the vertical and horizontal directions. See Figure 15 for a pictorial representation of the regions of interest.

Figure 15. Regions of Interest

#### Tests

#### Dark Field Global Non-Uniformity

This test is performed under dark field conditions. The sensor is partitioned into 60 sub regions of interest, each of which is 128 by 120 pixels in size. See Figure 16: Test Sub Regions of Interest. The average signal level of each of the 60 sub regions of interest is calculated. The signal level of each of the sub regions of interest is calculated using the following formula:

Signal of ROI[i] = (ROI Average in Counts -

- Horizontal Overclock Average in Counts) ·

- · mV per Count

```

Units : mVpp (millivolts Peak to Peak)

```

Where i = 1 to 144. During this calculation on the 60 sub regions of interest, the maximum and minimum signal levels are found. The dark field global uniformity is then calculated as the maximum signal found minus the minimum signal level found.

#### Global Non-Uniformity

This test is performed with the imager illuminated to a level such that the output is at 70% of saturation (approximately 476 mV). Prior to this test being performed the substrate

voltage has been set such that the charge capacity of the sensor is 680 mV. Global non-uniformity is defined as

Active Area Signal = Active Area Average – Dark Column Average

#### Global Peak to Peak Non-Uniformity

This test is performed with the imager illuminated to a level such that the output is at 70% of saturation (approximately 476 mV). Prior to this test being performed the substrate voltage has been set such that the charge capacity of the sensor is 680 mV. The sensor is partitioned into 60 sub regions of interest, each of which is 128 by 120 pixels in size. See Figure 16: Test Sub Regions of Interest. The average signal level of each of the 60 sub regions of interest (ROI) is calculated. The signal level of each of the sub regions of interest is calculated using the following formula:

Signal of ROI[i] = (ROI Average in Counts -

- Horizontal Overclock Average in Counts) ·

- · mV per Count

Where i = 1 to 60. During this calculation on the 60 sub regions of interest, the maximum and minimum signal levels are found. The global peak to peak uniformity is then calculated as:

Global Uniformity =

$$100 \cdot \left(\frac{\text{Max. Signal} - \text{Min. Signal}}{\text{Active Area Signal}}\right)$$

Units : % pp

#### Center Non-Uniformity

This test is performed with the imager illuminated to a level such that the output is at 70% of saturation (approximately 476 mV). Prior to this test being performed the substrate voltage has been set such that the charge capacity of the sensor is 680 mV. Defects are excluded for the calculation of this test. This test is performed on the center 100 by 100 pixels of the sensor. Center uniformity is defined as:

Center ROI Uniformity =  $100 \cdot \left(\frac{\text{Center ROI Standard Deviation}}{\text{Center ROI Signal}}\right)$

Units : % rms

Center ROI Signal = Center ROI Average - Dark Colum Average

#### Dark Field Defect Test

This test is performed under dark field conditions. The sensor is partitioned into 60 sub regions of interest, each of which is 128 by 120 pixels in size. In each region of interest, the median value of all pixels is found. For each region of interest, a pixel is marked defective if it is greater than or equal to the median value of that region of interest plus the defect threshold specified in the "Defect Definitions" section.

#### Bright Field Defect Test

This test is performed with the imager illuminated to a level such that the output is at approximately 476 mV. Prior to this test being performed the substrate voltage has been set such that the charge capacity of the sensor is 680 mV. The average signal level of all active pixels is found. The bright and dark thresholds are set as:

Dark Defect Threshold = Active Area Signal · Threshold

#### Bright Defect Threshold = Active Area Signal $\cdot$ Threshold

The sensor is then partitioned into 60 sub regions of interest, each of which is 128 by 120 pixels in size. In each region of interest, the average value of all pixels is found. For each region of interest, a pixel is marked defective if it is greater than or equal to the median value of that region of interest plus the bright threshold specified or if it is less than or equal to the median value of that region of interest minus the dark threshold specified.

Example for major bright field defective pixels:

- Average value of all active pixels is found to be 476 mV.

- Dark defect threshold:  $476 \text{ mV} \cdot 12 \% = 57 \text{ mV}.$

- Bright defect threshold:  $476 \text{ mV} \cdot 12 \% = 57 \text{ mV}.$

- Region of interest #1 selected. This region of interest is pixels 21, 9 to pixels 148, 128.

- Median of this region of interest is found to be 470 mV.

- Any pixel in this region of interest that is ≥ (470 + 57 mV) 527 mV in intensity will be marked defective.

- Any pixel in this region of interest that is ≤ (470 - 57 mV) 413 mV in intensity will be marked defective.

- All remaining 60 sub regions of interest are analyzed for defective pixels in the same manner.

#### Test Sub Regions of Interest

|        |    |    |    |    |    |    |    |    |    | (1 | Pixel<br>300,728) |

|--------|----|----|----|----|----|----|----|----|----|----|-------------------|

|        | 51 | 52 | 53 | 54 | 55 | 56 | 57 | 58 | 59 | 60 |                   |

|        | 41 | 42 | 43 | 44 | 45 | 46 | 47 | 48 | 49 | 50 |                   |

|        | 31 | 32 | 33 | 34 | 35 | 36 | 37 | 38 | 39 | 40 |                   |

|        | 21 | 22 | 23 | 24 | 25 | 26 | 27 | 28 | 29 | 30 |                   |

|        | 11 | 12 | 13 | 14 | 15 | 16 | 17 | 18 | 19 | 20 |                   |

| Pixel  | 1  | 2  | 3  | 4  | 5  | 6  | 7  | 8  | 9  | 10 |                   |

| (21,9) |    |    |    |    |    |    |    |    |    |    | ,                 |

VOUTa ┥

Figure 16. Test Sub Regions of Interest

#### OPERATION

#### **Absolute Maximum Ratings**

Absolute maximum rating is defined as a level or condition that should not be exceeded at any time per the

description. If the level or the condition is exceeded, the device will be degraded and may be damaged. Operation at these values will reduce MTTF.

#### Table 17. ABSOLUTE MAXIMUM RATINGS

| Description           | Symbol           | Minimum | Maximum | Unit | Notes |

|-----------------------|------------------|---------|---------|------|-------|

| Operating Temperature | T <sub>OP</sub>  | -50     | 70      | °C   | 1     |

| Humidity              | RH               | 5       | 90      | %    | 2     |

| Output Bias Current   | I <sub>OUT</sub> | -       | 60      | mA   | 3     |

| Off-Chip Load         | CL               | -       | 10      | pF   |       |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

1. Noise performance will degrade at higher temperatures.

2.  $T = 25^{\circ}C$ . Excessive humidity will degrade MTTF.

3. Total for all outputs. Maximum current is -15 mA for each output. Avoid shorting output pins to ground or any low impedance source during operation. Amplifier bandwidth increases at higher current and lower load capacitance at the expense of reduced gain (sensitivity).

#### Table 18. ABSOLUTE MAXIMUM VOLTAGE RATINGS BETWEEN PINS AND GROUND

| Description                            | Minimum   | Maximum    | Unit | Notes |

|----------------------------------------|-----------|------------|------|-------|

| VDDα, VOUTα                            | -0.4      | 17.5       | V    | 1     |

| RDα                                    | -0.4      | 15.5       | V    | 1     |

| V1B, V1T                               | ESD – 0.4 | ESD + 24.0 | V    |       |

| V2B, V2T, V3B, V3T, V4B, V4T           | ESD – 0.4 | ESD + 14.0 | V    |       |

| H1Sa, H1Ba, H2Sa, H2Ba, H2SLa, Ra, OGa | ESD – 0.4 | ESD + 14.0 | V    | 1     |

| ESD                                    | -10.0     | 0.0        | V    |       |

| SUB                                    | -0.4      | 40.0       | V    | 2     |

1.  $\alpha$  denotes a, b, c or d.

2. Refer to Application Note Using Interline CCD Image Sensors in High Intensity Visible Lighting Conditions

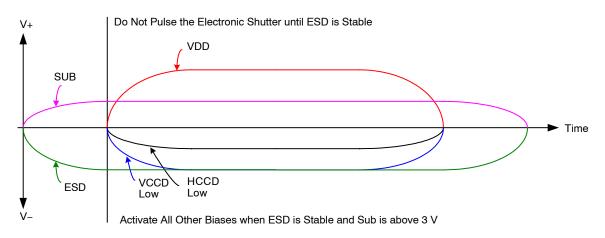

#### Power-Up and Power-Down Sequence

Adherence to the power-up and power-down sequence is critical. Failure to follow the proper power-up and power-down sequences may cause damage to the sensor.

#### Notes:

- 1. Activate all other biases when ESD is stable and SUB is above 3 V.

- 2. Do not pulse the electronic shutter until ESD is stable.

- 3. VDD cannot be +15 V when SUB is 0 V.

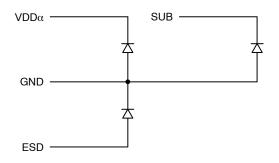

- 4. The image sensor can be protected from an accidental improper ESD voltage by current limiting the SUB current to less than 10 mA. SUB and VDD must always be greater than GND. ESD must always be less than GND. Placing diodes between SUB, VDD, ESD and ground will protect the sensor from accidental overshoots of SUB, VDD and ESD during power on and power off. See the figure below.

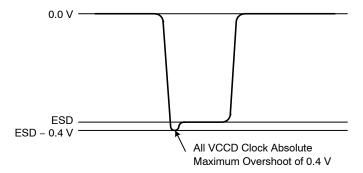

The VCCD clock waveform must not have a negative overshoot more than 0.4 V below the ESD voltage.

Figure 18. VCCD Clock Waveform

Example of external diode protection for SUB, VDD and ESD. $\alpha$  denotes a, b, c or d.

#### **DC Bias Operating Conditions**

| Description             | Pins  | Symbol           | Min. | Nom.            | Max.            | Unit | Max. DC<br>Current | Notes   |

|-------------------------|-------|------------------|------|-----------------|-----------------|------|--------------------|---------|

| Reset Drain             | RDα   | RD               | 11.8 | 12.0            | 12.2            | V    | 10 μA              | 1       |

| Output Gate             | OGα   | OG               | -2.2 | -2.0            | -1.8            | V    | 10 μA              | 1       |

| Output Amplifier Supply | VDDα  | V <sub>DD</sub>  | 14.5 | 15.0            | 15.5            | V    | 11.0 mA            | 1, 2    |

| Ground                  | GND   | GND              | 0.0  | 0.0             | 0.0             | V    | –1.0 mA            |         |

| Substrate               | SUB   | V <sub>SUB</sub> | 5.0  | V <sub>AB</sub> | V <sub>DD</sub> | V    | 50 μA              | 3, 8    |

| ESD Protection Disable  | ESD   | ESD              | -9.5 | -9.0            | Vx_L            | V    | 50 μA              | 6, 7, 9 |

| Output Bias Current     | VOUTα | I <sub>OUT</sub> | -3.0 | -7.0            | -10.0           | mA   | -                  | 1, 4, 5 |

1.  $\alpha$  denotes a, b, c or d.

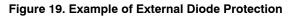

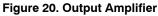

2. The maximum DC current is for one output.  $I_{DD} = I_{OUT} + I_{SS}$ . See Figure 20. 3. The operating value of the substrate voltage, V<sub>AB</sub>, will be marked on the shipping container for each device. The value of V<sub>AB</sub> is set such that the photodiode charge capacity is the nominal P<sub>Ne</sub> (see Specifications).

An output load sink must be applied to each VOUT pin to activate each output amplifier.

5. Nominal value required for 40 MHz operation per output. May be reduced for slower data rates and lower noise.

6. Adherence to the power-up and power-down sequence is critical. See Power Up and Power Down Sequence section. 7. ESD maximum value must be less than or equal to  $V1_L + 0.4 V$  and  $V2_L + 0.4 V$ .

Refer to Application Note Using Interline CCD Image Sensors in High Intensity Visible Lighting Conditions.

Where Vx\_L is the level set for V1\_L, V2\_L, V3\_L, or V4\_L in the application.

#### **AC Operating Conditions**

#### Table 20. CLOCK LEVELS

| Description                              | Pins<br>(Note 1) | Symbol          | Level     | Min.             | Nom. | Max.            | Unit | Capacitance<br>(Note 2) |

|------------------------------------------|------------------|-----------------|-----------|------------------|------|-----------------|------|-------------------------|

| Vertical CCD Clock, Phase 1              | V1B, V1T         | V1_L            | Low       | -8.2             | -8.0 | -7.8            | V    | 6 nF                    |

|                                          |                  | V1_M            | Mid       | -0.2             | 0.0  | 0.2             |      | (Note 6)                |

|                                          |                  | V1_H            | High      | 11.5             | 12.0 | 12.5            |      |                         |

| Vertical CCD Clock, Phase 2              | V2B, V2T         | V2_L            | Low       | -8.2             | -8.0 | -7.8            | V    | 6 nF                    |

|                                          |                  | V2_H            | High      | -0.2             | 0.0  | 0.2             |      | (Note 6)                |

| Vertical CCD Clock, Phase 3              | V3B, V3T         | V3_L            | Low       | -8.2             | -8.0 | -7.8            | V    | 6 nF                    |

|                                          |                  | V3_H            | High      | -0.2             | 0.0  | 0.2             |      | (Note 6)                |

| Vertical CCD Clock, Phase 4              | V4B, V4T         | V4_L            | Low       | -8.2             | -8.0 | -7.8            | V    | 6 nF                    |

|                                          |                  | V4_H            | High      | -0.2             | 0.0  | 0.2             |      | (Note 6)                |

| Horizontal CCD Clock,<br>Phase 1 Storage | H1Sα             | H1S_L           | Low       | –5.2<br>(Note 7) | -4.0 | -3.8            | V    | 90 pF<br>(Note 6)       |

|                                          |                  | H1S_A           | Amplitude | 3.8              | 4.0  | 5.2<br>(Note 7) |      |                         |

| Horizontal CCD Clock,<br>Phase 1 Barrier | Η1Βα             | H1B_L           | Low       | –5.2<br>(Note 7) | -4.0 | -3.8            | V    | 60 pF<br>(Note 6)       |

|                                          |                  | H1B_A           | Amplitude | 3.8              | 4.0  | 5.2<br>(Note 7) |      |                         |

| Horizontal CCD Clock,<br>Phase 2 Storage | H2Sa             | H2S_L           | Low       | –5.2<br>(Note 7) | -4.0 | -3.8            | V    | 90 pF<br>(Note 6)       |

|                                          |                  | H2S_A           | Amplitude | 3.8              | 4.0  | 5.2<br>(Note 7) |      |                         |

| Horizontal CCD Clock,<br>Phase 2 Barrier | Η2Βα             | H2B_L           | Low       | –5.2<br>(Note 7) | -4.0 | -3.8            | V    | 60 pF<br>(Note 6)       |

|                                          |                  | H2B_A           | Amplitude | 3.8              | 4.0  | 5.2<br>(Note 7) |      |                         |

| Horizontal CCD Clock,                    | H2SLa            | H2SL_L          | Low       | -5.2             | -5.0 | -4.8            | V    | 20 pF                   |

| Last Phase (Note 3)                      |                  | H2SL_A          | Amplitude | 4.8              | 5.0  | 5.2             | 1    | (Note 6)                |

| Reset Gate                               | Rα               | R_L<br>(Note 4) | Low       | -3.5             | -2.0 | -1.5            | V    | 16 pF<br>(Note 6)       |

|                                          |                  | R_H             | High      | 2.5              | 3.0  | 4.0             |      |                         |

| Electronic Shutter (Note 5)              | SUB              | VES             | High      | 29.0             | 30.0 | 40.0            | V    | 400 pF<br>(Note 6)      |

1.  $\alpha$  denotes a, b, c or d.

2. Capacitance is total for all like named pins.

Use separate clock driver for improved speed performance.

Reset low should be set to -3 V for signal levels greater than 40,000 electrons.

Refer to Application Note Using Interline CCD Image Sensors in High Intensity Visible Lighting Conditions.

Capacitance values are estimated.

If the minimum horizontal clock low level is used (-5.2 V), then the maximum horizontal clock amplitude should be used (5.2 V amplitude) to create a -5.2 V to 0.0 V clock. If a 5 V clock driver is used, the horizontal low level should be set to -5.0 V and the high level should be a set to 0.0 V.

The figure below shows the DC bias (VSUB) and AC clock (VES) applied to the SUB pin. Both the DC bias and AC clock are referenced to ground.

Figure 21. DC Bias and AC Clock Applied to the SUB Pin

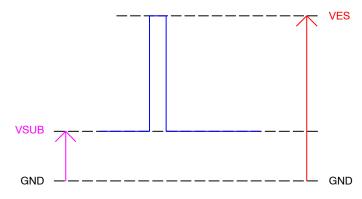

#### **Device Identification**

The device identification pin (DevID) may be used to determine which ON Semiconductor 5.5 micron pixel interline CCD sensor is being used.

#### Table 21.

| Description           | Pins  | Symbol | Min.  | Nom.  | Max.  | Unit | Max. DC<br>Current | Notes   |

|-----------------------|-------|--------|-------|-------|-------|------|--------------------|---------|

| Device Identification | DevID | DevID  | 4,000 | 5,000 | 6,000 | Ω    | 50 μA              | 1, 2, 3 |

Nominal value subject to verification and/or change during release of preliminary specifications.

If the Device Identification is not used, it may be left disconnected.

After Device Identification resistance has been read during camera initialization, it is recommended that the circuit be disabled to prevent З. localized heating of the sensor due to current flow through the R\_DeviceID resistor.

#### **Recommended Circuit**

Note that V1 must be a different value than V2.

## TIMING

#### Table 22. REQUIREMENTS AND CHARACTERISTICS

| Description            | Symbol                            | Min. | Nom. | Max. | Unit | Notes               |

|------------------------|-----------------------------------|------|------|------|------|---------------------|

| Photodiode Transfer    | t <sub>PD</sub>                   | 1.0  | -    | -    | μs   |                     |

| VCCD Leading Pedestal  | t <sub>3P</sub>                   | 4.0  | -    | -    | μs   |                     |

| VCCD Trailing Pedestal | t <sub>3D</sub>                   | 4.0  | -    | -    | μs   |                     |

| VCCD Transfer Delay    | t <sub>D</sub>                    | 1.0  | -    | -    | μs   |                     |

| VCCD Transfer          | t <sub>V</sub>                    | 1.0  | -    | -    | μs   |                     |

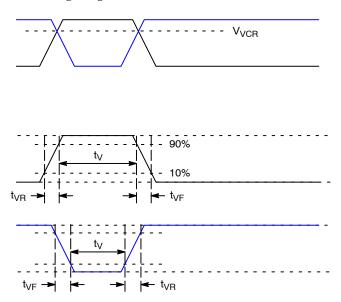

| VCCD Clock Cross-Over  | V <sub>VCR</sub>                  | 75   | -    | 100  | %    | 2                   |

| VCCD Rise, Fall Times  | t <sub>VR</sub> , t <sub>VF</sub> | 5    | -    | 10   | %    | 2, 3                |

| HCCD Delay             | t <sub>HS</sub>                   | 0.2  | -    | -    | μs   |                     |

| HCCD Transfer          | t <sub>e</sub>                    | 25.0 | -    | -    | ns   |                     |

| Shutter Transfer       | t <sub>SUB</sub>                  | 1.0  | -    | -    | μs   |                     |

| Shutter Delay          | t <sub>HD</sub>                   | 1.0  | -    | -    | μs   |                     |

| Reset Pulse            | t <sub>R</sub>                    | 2.5  | -    | -    | ns   |                     |

| Reset - Video Delay    | t <sub>RV</sub>                   | -    | 2.2  | -    | ns   |                     |

| H2SL – Video Delay     | t <sub>HV</sub>                   | -    | 3.1  | -    | ns   |                     |

| Line Time              | t <sub>LINE</sub>                 | 19.0 | -    | -    | μs   | Dual HCCD Readout   |

|                        |                                   | 36.1 | -    | -    |      | Single HCCD Readout |

| Frame Time             | t <sub>FRAME</sub>                | 7.2  | -    | -    | ms   | Quad HCCD Readout   |

|                        |                                   | 14.5 | -    | -    |      | Dual HCCD Readout   |

|                        |                                   | 26.8 | -    | -    |      | Single HCCD Readout |

Refer to timing diagrams as shown in Figure 23, Figure 24, Figure 25, Figure 26 and Figure 27.

Refer to Figure 27: VCCD Clock Rise Time, Fall Time and Edge Alignment

Relative to the pulse width.

#### **Timing Diagrams**

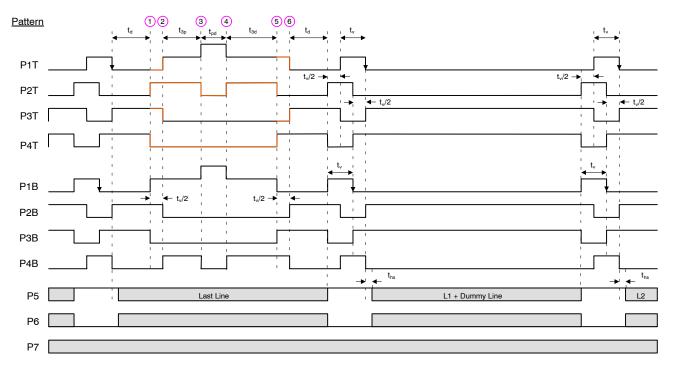

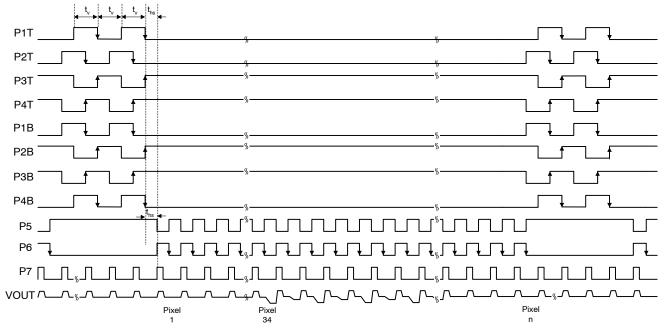

The timing sequence for the clocked device pins may be represented as one of seven patterns (P1–P7) as shown in the table below. The patterns are defined in Figure 23 and

Figure 24. Contact ON Semiconductor Application Engineering for other readout modes.

#### Table 23. TIMING DIAGRAMS

| Device Pin    | Quad Readout | Dual ReadoutDual ReadoutVOUTa, VOUTbVOUTa, VOUTc |                             | Single Readout<br>VOUTa     |  |  |

|---------------|--------------|--------------------------------------------------|-----------------------------|-----------------------------|--|--|

| V1T           | P1T          | P1B                                              | P1T                         | P1B                         |  |  |

| V2T           | P2T          | P4B                                              | P2T                         | P4B                         |  |  |

| V3T           | P3T          | P3B                                              | P3T                         | P3B                         |  |  |

| V4T           | P4T          | P2B                                              | P4T                         | P2B                         |  |  |

| V1B           | P1B          |                                                  |                             |                             |  |  |

| V2B           | P2B          |                                                  |                             |                             |  |  |

| V3B           | РЗВ          |                                                  |                             |                             |  |  |

| V4B           | P4B          |                                                  |                             |                             |  |  |

| H1Sa          | P5           |                                                  |                             |                             |  |  |

| H1Ba          | P5           |                                                  |                             |                             |  |  |

| H2Sa (Note 2) | P6           |                                                  |                             |                             |  |  |

| H2Ba          | P6           |                                                  |                             |                             |  |  |

| Ra            | Ρ7           |                                                  |                             |                             |  |  |

| H1Sb          | P5 P5        |                                                  |                             |                             |  |  |

| H1Bb          |              | P5                                               | P6                          |                             |  |  |

| H2Sb (Note 2) |              | P6                                               | P6                          |                             |  |  |

| H2Bb          |              | P6                                               | P5                          |                             |  |  |

| Rb            | P7           |                                                  | P7 (Note 1) or Off (Note 3) | P7 (Note 1) or Off (Note 3) |  |  |

| H1Sc          | P5           | P5 (Note 1) or Off (Note 3)                      | P5                          | P5 (Note 1) or Off (Note 3) |  |  |

| H1Bc          | P5           | P5 (Note 1) or Off (Note 3)                      | P5                          | P5 (Note 1) or Off (Note 3) |  |  |

| H2Sc (Note 2) | P6           | P6 (Note 1) or Off (Note 3)                      | P6                          | P6 (Note 1) or Off (Note 3) |  |  |

| H2Bc          | P6           | P6 (Note 1) or Off (Note 3)                      | P6                          | P6 (Note 1) or Off (Note 3) |  |  |

| Rc            | P7           | P7 (Note 1) or Off (Note 3)                      | P7                          | P7 (Note 1) or Off (Note 3) |  |  |

| H1Sd          | P5           | P5 (Note 1) or Off (Note 3)                      | P5                          | P5 (Note 1) or Off (Note 3) |  |  |

| H1Bd          | P5           | P5 (Note 1) or Off (Note 3)                      | P6                          | P5 (Note 1) or Off (Note 3) |  |  |

| H2Sd (Note 2) | P6           | P6 (Note 1) or Off (Note 3)                      | P6                          | P6 (Note 1) or Off (Note 3) |  |  |

| H2Bd          | P6           | P6 (Note 1) or Off (Note 3)                      | P5                          | P6 (Note 1) or Off (Note 3) |  |  |

| Rd            | P7           | P7 (Note 1) or Off (Note 3)                      | P7 (Note 1) or Off (Note 3) | P7 (Note 1) or Off (Note 3) |  |  |

| #Lines/Frame<br>(Minimum) | 380 | 760 | 380  | 760 |  |

|---------------------------|-----|-----|------|-----|--|

| #Pixels/Line<br>(Minimum) | 693 |     | 1386 |     |  |

1. For optimal performance of the sensor. May be clocked at a lower frequency. If clocked at a lower frequency, the frequency selected should be a multiple of the frequency used on the a and b register.

2. H2SLx follows the same pattern as H2Sx For optimal speed performance, use a separate clock driver.

3. Off = +5 V. Note that there may be operating conditions (high temperature and/or very bright light sources) that will cause blooming from the unused c/d register into the image area.

#### Photodiode Transfer Timing

A row of charge is transferred to the HCCD on the falling edge of V1 as indicated in the P1 pattern below. Using this timing sequence, the leading dummy row or line is combined with the first dark row in the HCCD. The "Last Line" is dependent on readout mode – either 380 or 760 minimum counts required. It is important to note that, in general, the rising edge of a vertical clock (patterns P1–P4) should be coincident or slightly leading a falling edge at the same time interval. This is particularly true at the point where P1 returns from the high (3<sup>rd</sup> level) state to the mid-state when P4 transitions from the low state to the high state.

Figure 23. Photodiode Transfer Timing

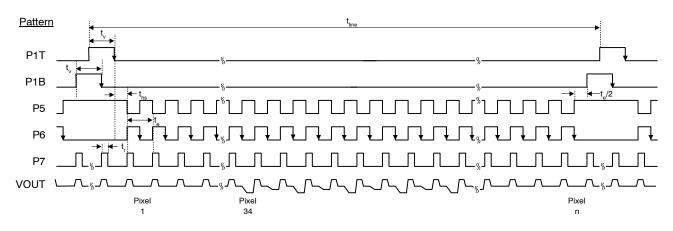

#### Line and Pixel Timing

Each row of charge is transferred to the output, as illustrated below, on the falling edge of H2SL (indicated as

P6 pattern). The number of pixels in a row is dependent on readout mode – either 693 or 1386 minimum counts required.

Figure 24. Line and Pixel Timing

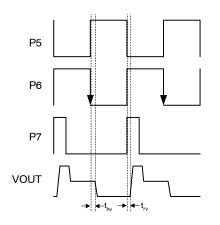

Pixel Timing Detail

Figure 25. Pixel Timing Detail

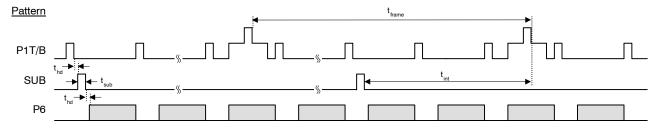

#### Frame/Electronic Shutter Timing

The SUB pin may be optionally clocked to provide electronic shuttering capability as shown below. The

resulting photodiode integration time is defined from the falling edge of SUB to the falling edge of V1 (P1 pattern).

Figure 26. Frame/Electronic Shutter Timing

VCCD Clock Rise Time, Fall Time and Edge Alignment

Figure 27. VCCD Clock Rise Time, Fall Time and Edge Alignment

Line and Pixel Timing – Vertical Binning by 2

#### STORAGE AND HANDLING

#### Table 24. STORAGE CONDITIONS

| Description         | Symbol          | Minimum | Maximum | Units | Notes |

|---------------------|-----------------|---------|---------|-------|-------|

| Storage Temperature | T <sub>ST</sub> | -55     | 80      | °C    | 1     |

| Humidity            | RH              | 5       | 90      | %     | 2     |

1. Long-term storage toward the maximum temperature will accelerate color filter degradation.

2. T = 25°C. Excessive humidity will degrade MTTF.

For information on ESD and cover glass care and cleanliness, please download the *Image Sensor Handling and Best Practices* Application Note (AN52561/D) from www.onsemi.com.

For information on environmental exposure, please download the Using Interline CCD Image Sensors in High Intensity Lighting Conditions Application Note (AND9183/D) from www.onsemi.com.

For information on soldering recommendations, please download the Soldering and Mounting Techniques Reference Manual (SOLDERRM/D) from www.onsemi.com. For quality and reliability information, please download the *Quality & Reliability* Handbook (HBD851/D) from www.onsemi.com.

For information on device numbering and ordering codes, please download the *Device Nomenclature* technical note (TND310/D) from <u>www.onsemi.com</u>.

For information on Standard terms and Conditions of Sale, please download <u>Terms and Conditions</u> from <u>www.onsemi.com</u>.

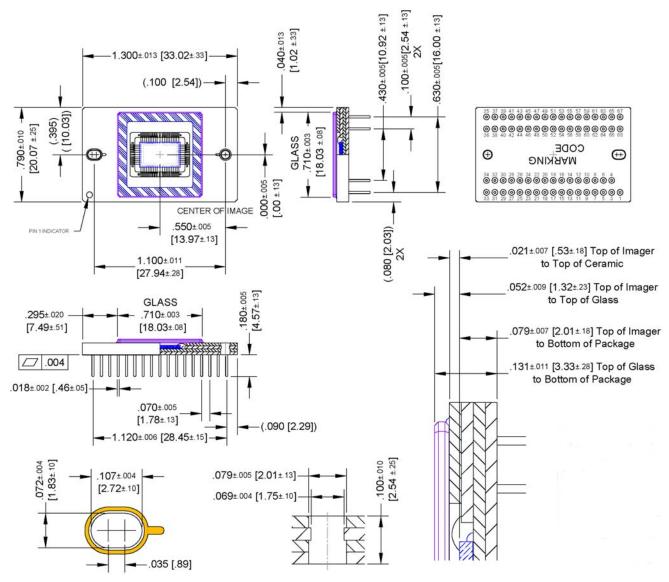

#### **MECHANICAL INFORMATION**

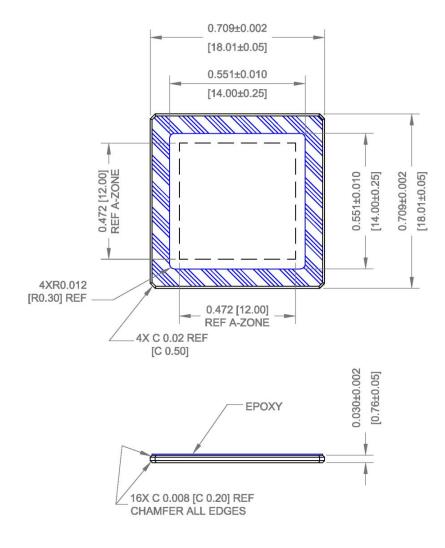

#### PGA Completed Assembly

- 1. See Ordering Information for marking code.

- 2. No materials to interfere with clearance through guide holes.

- 3. The center of the active image is nominally at the center of the package.

- 4. Die rotation < 0.5 degrees.

- 5. Glass rotation < 1.5 degrees

- 6. Internal traces may be exposed on sides of package. Do not allow metal to contact sides of ceramic package.

- 7. Recommended mounting screws:

- a.)  $1.6 \times 0.35$  mm (ISO Standard)

- b.) 0-80 (Unified Fine Thread Standard).

- 8. Units: IN [MM]

Figure 29. PGA Completed Assembly

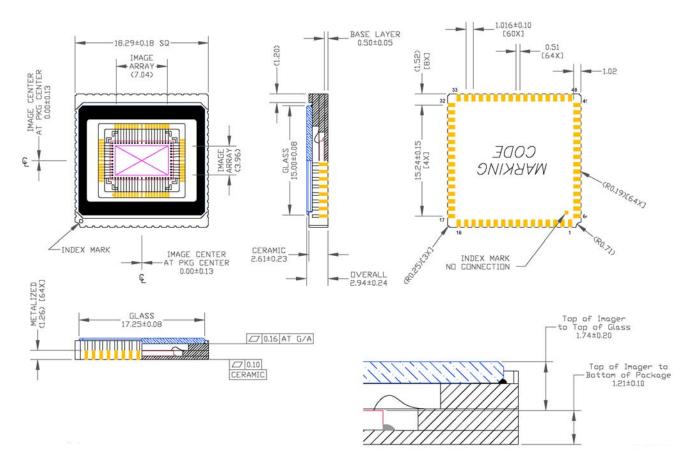

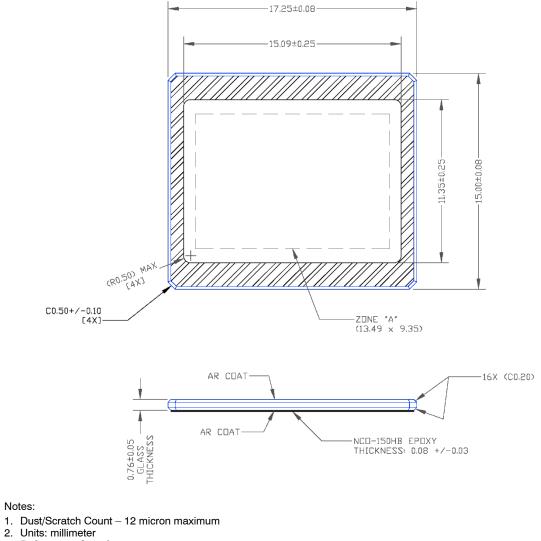

#### **CLCC Completed Assembly**

- 1. See Ordering Information for marking code.

- 2. Die rotation < 0.5 degrees.

- 3. Units: millimeters.

- Dust/Scratch Count 12 micron maximum

Units: IN [MM]

Reflectance Specification

a. 420 nm to 435 nm < 2.0%</li>

b. 435 nm to 630 nm < 0.8%</li>

context

- - c. 630 nm to 680 nm < 2.0%

- Beflectance Specification

a. 420 nm to 435 nm < 2.0%</li>

b. 435 nm to 630 nm < 0.8%</li>

- c. 630 nm to 680 nm < 2.0%

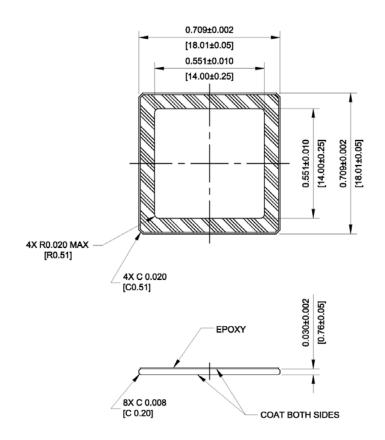

#### **PGA Clear Cover Glass**

- 1. Dust/Scratch Count 12 micron maximum

- 2. Units: IN

#### **Cover Glass Transmission**

NOTE: PGA and CLCC MAR transmission data differ due to in-spec differences from glass vendor.

Figure 34. Cover Glass Transmission

ON Semiconductor and the intervent and the intervent of the patient patient of the patient of the patient patient patient of the patient patient patient patient of the patient patient patient patient of the patient patient

#### PUBLICATION ORDERING INFORMATION

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor 19521 E. 32nd Pkwy, Aurora, Colorado 80011 USA Phone: 303-675-2175 or 800-344-3860 Toll Free USA/Canada Fax: 303-675-2176 or 800-344-3867 Toll Free USA/Canada Email: orderlit@onsemi.com N. American Technical Support: 800–282–9855 Toll Free USA/Canada Europe, Middle East and Africa Technical Support:

Phone: 421 33 790 2910 Japan Customer Focus Center Phone: 81-3-5817-1050 ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative

## **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Image Sensors category:

Click to view products by ON Semiconductor manufacturer:

Other Similar products are found below :