# LA6571

## Monolithic Linear IC 5CH Driver for Mini Disk and Compact Disk

#### Overview

The LA6571 is 5-channel driver for mini disk and compact disk applications (BTL-AMP: 5CH).

#### Features

- Power amplifier 5-channel built-in.

- IO max 1A

- Level shift circuit built-in.

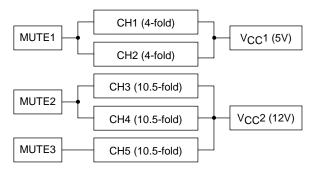

- Mute circuit (output ON/OFF) with three built-in channels (2-2-1). (Operates independently for each of MUTE1: CH1 and 2, MUTE2: CH3 and 4, and MUTE3: CH5. Not operating for the regulator (REG))

- Regulator (REG) built-in (external PNP transistor). Voltage setting (typ: 1.5V or more) with an external resistor

- Overheat protection circuit (thermal shutdown) built-in.

### **Specifications**

#### **Maximum Ratings** at $Ta = 25^{\circ}C$

| Parameter              | Symbol              | Conditions                      | Ratings     | Unit |

|------------------------|---------------------|---------------------------------|-------------|------|

| Supply voltage         | V <sub>CC</sub> max |                                 | 14          | V    |

| Maximum output current | I <sub>O</sub> max  | Each output for channel 1 to 5. | 1           | А    |

| Maximum input voltage  | V <sub>IN</sub> B   |                                 | 13          | V    |

| MUTE pin voltage       | VMUTE               |                                 | 13          | V    |

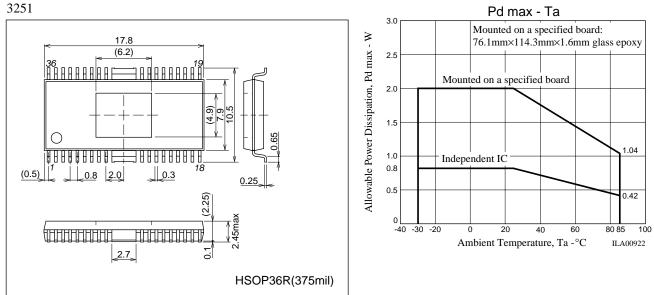

| Allowable loss         | Pd max              | Independent IC                  | 0.8         | W    |

|                        |                     | Mounted on a specified board*   | 2           | W    |

| Operating temperature  | Topr                |                                 | -30 to +85  | °C   |

| Storage temperature    | Tstg                |                                 | -55 to +150 | °C   |

\* Mounted on a specified board: 76.1mm×114.3mm×1.6mm glass epoxy

Stresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.

#### **Recommended Operating Conditions** at $Ta = 25^{\circ}C$

| Parameter        | Symbol            | Conditions | Ratings                  | Unit |

|------------------|-------------------|------------|--------------------------|------|

| Supply voltage 1 | V <sub>CC</sub> 1 |            | 4.5 to V <sub>CC</sub> 2 | V    |

| Supply voltage 2 | V <sub>CC</sub> 2 |            | 6 to 13                  | V    |

| Parameter                           | Symbol                | Quantitiana                                                       | Ratings |      |                       |      |

|-------------------------------------|-----------------------|-------------------------------------------------------------------|---------|------|-----------------------|------|

|                                     |                       | Conditions                                                        | min     | typ  | max                   | Unit |

| [ALL Blocks]                        |                       |                                                                   |         |      |                       |      |

| No-load current drain ON            | I <sub>CC</sub> ON    | All outputs ON *1                                                 |         | 30   | 50                    | mA   |

| No-load current drain OFF           | I <sub>CC</sub> OFF   | All outputs OFF *1                                                |         | 10   | 20                    | mA   |

| VREF input voltage range            | VREF-IN               |                                                                   | 1       |      | V <sub>CC</sub> 2-1   | V    |

| Thermal shutdown temperature        | TSD                   | *7                                                                | 150     | 175  | 200                   | °C   |

| [BTL AMP Block] (CH1 to CH5)        |                       |                                                                   |         |      |                       |      |

| Output offset voltage               | VOFF                  | Voltage difference in output between<br>BTL AMP and each channel. | -50     |      | 50                    | mV   |

| Output offset voltage               | V <sub>OFF</sub> 1    | Voltage difference in output between<br>BTL AMP and each channel. | -80     |      | 80                    | mV   |

| Output voltage                      | VO                    | CH1,CH2 *3                                                        | 3.2     | 4.0  |                       | V    |

| Output voltage                      | V <sub>O</sub> 1      | CH3,CH4,CH5 *4                                                    | 9.7     | 10.5 |                       | V    |

| Closed-circuit voltage gain         | V <sub>G</sub> 1      | Gain between input and output for CH1, CH2, and CH5 *2            | 4.2     | 5.0  | 6.0                   | time |

| Closed-circuit voltage gain         | V <sub>G</sub> 3      | Gain between input and output for CH3 and CH4 *2                  | 8.2     | 9.0  | 11.0                  | time |

| Slew rate                           | SR                    | AMP Independent.<br>Multiply 2 between outputs. *7                |         | 0.5  |                       | V/µs |

| MUTE ON voltage                     | V <sub>MUTE</sub> ON  | Each MUTE *6                                                      | 2       |      |                       | V    |

| MUTE OFF voltage                    | V <sub>MUTE</sub> OFF | Each MUTE *6                                                      |         |      | 0.5                   | V    |

| [Input AMP Block]                   |                       |                                                                   |         |      |                       |      |

| Input voltage range                 | V <sub>IN</sub> op    |                                                                   | 0       |      | V <sub>CC</sub> 2-1.5 | V    |

| Output offset voltage               | VOFF op               |                                                                   | -10     |      | 10                    | mV   |

| Output current (SINK)               | SINK op               |                                                                   | 2       |      |                       | mA   |

| Output current (SOURCE)             | SOURCE op             | *5                                                                | 300     | 500  |                       | μA   |

| [Power Supply Block] (PNP transisto | or: 2SB632K)          |                                                                   |         |      |                       |      |

| Regulator output                    | Vout                  | For error Amp, $R_L = 10k\Omega$ at buffer                        | 1.2     | 1.3  | 1.4                   | V    |

| REG-IN SINK current                 | REG-IN-SINK           | Base current to external PNP                                      | 5       | 10   |                       | mA   |

| Line regulation                     | ΔV <sub>O</sub> LN    | $6V \le V_{CC} \le 12V$ , $I_O = 200mA$                           |         | 20   | 150                   | mV   |

| Load regulation                     | ΔV <sub>O</sub> LD    | $5mA \le I_O \le 200mA$                                           |         | 50   | 200                   | mV   |

\*1. Current dissipation that is a sum of  $V_{CC}$ 1 and  $V_{CC}$ 2 at no load.

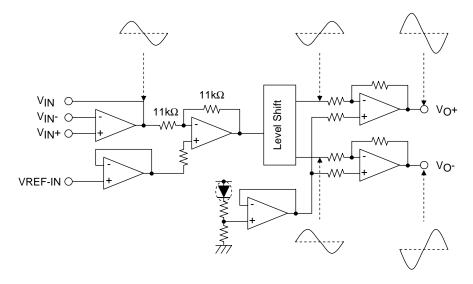

\*2. Input AMP is a BUFFER AMP.

\*3. Voltage difference between both ends of load (8 $\Omega$ ). Output saturated.

\*4. Voltage difference between both ends of load (12 $\Omega$ ). Output saturated.

\*5. The source of input OP-AMP is a constant current. (See the specified block diagram.)

As the  $11k\Omega$  resistance to the next stage is a load, pay due attention when setting the input OP-AMP gain.

\*6. Output ON with MUTE: [H] and OFF with MUTE: [L] (HI impedance).

\*7. Design guarantee value

## Package Dimensions

unit : mm

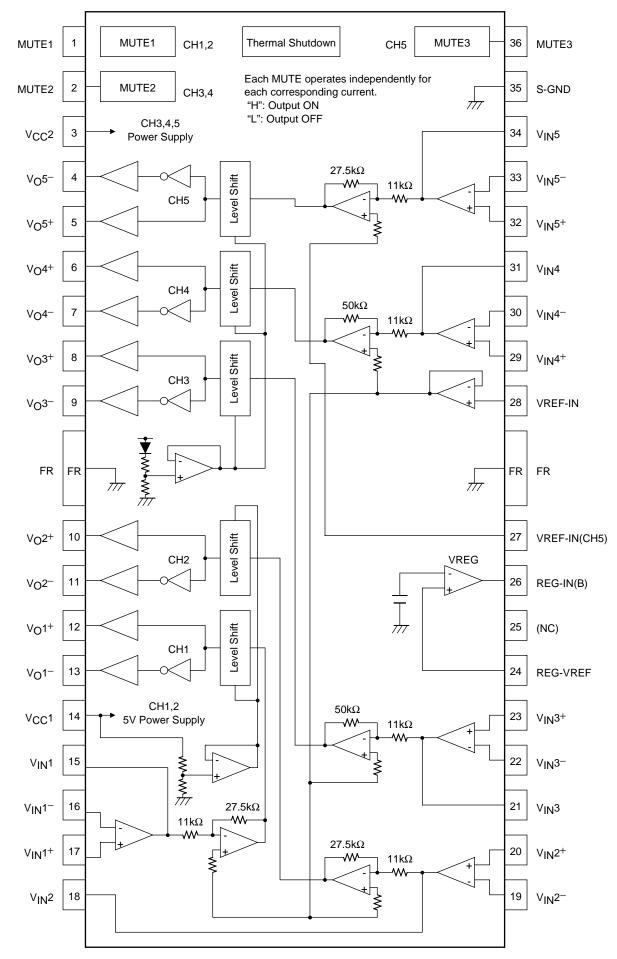

## **Pin Description**

| Pin<br>Name | Pin<br>Name                    | Pin No. | Equivalent Circuit Diagram        | Description                                              |

|-------------|--------------------------------|---------|-----------------------------------|----------------------------------------------------------|

| Input       | VIN <sup>1+</sup>              | 17      |                                   | Each input pin                                           |

|             | V <sub>IN</sub> 1 <sup>-</sup> | 16      |                                   |                                                          |

|             | V <sub>IN</sub> 1              | 15      | $V_{IN} \bigcirc V_{IN} \bigcirc$ |                                                          |

|             | V <sub>IN</sub> 2 <sup>+</sup> | 20      |                                   |                                                          |

|             | V <sub>IN</sub> 2 <sup>-</sup> | 19      |                                   |                                                          |

|             | V <sub>IN</sub> 2              | 18      |                                   |                                                          |

|             | V <sub>IN</sub> 3+             | 23      |                                   |                                                          |

|             | V <sub>IN</sub> 3-             | 22      |                                   |                                                          |

|             | V <sub>IN</sub> 3              | 21      |                                   |                                                          |

|             | VIN4 <sup>-</sup>              | 30      |                                   |                                                          |

|             | $V_{IN}4^+$                    | 29      |                                   |                                                          |

|             | V <sub>IN</sub> 4              | 31      |                                   |                                                          |

|             | $V_{IN}5^+$                    | 32      |                                   |                                                          |

|             | V <sub>IN</sub> 5 <sup>-</sup> | 33      | S-GND () + + + + + +              |                                                          |

|             | V <sub>IN</sub> 5              | 34      |                                   |                                                          |

| Output      | V <sub>O</sub> 1 <sup>+</sup>  | 12      |                                   | Each output                                              |

|             | V <sub>O</sub> 1 <sup>-</sup>  | 13      |                                   |                                                          |

|             | V <sub>O</sub> 2 <sup>+</sup>  | 10      |                                   |                                                          |

|             | V <sub>O</sub> 2 <sup>-</sup>  | 11      |                                   |                                                          |

|             | V <sub>O</sub> 3+              | 8       |                                   |                                                          |

|             | V <sub>O</sub> 3-              | 9       |                                   |                                                          |

|             | V04+                           | 6       |                                   |                                                          |

|             | V04-                           | 7       |                                   |                                                          |

|             | $V_{O}^{5^{+}}$                | 5       |                                   |                                                          |

|             | V <sub>O</sub> 5 <sup>-</sup>  | 4       |                                   |                                                          |

| MUTE        | MUTE1                          | 1       |                                   | Turns ON/OFF the output for                              |

|             | MUTE2                          | 2       |                                   | MUTE1: CH1, 2                                            |

|             | MUTE3                          | 36      |                                   | MUTE2: CH3, 4, and                                       |

|             |                                |         |                                   | MUTE3: CH5.                                              |

|             |                                |         |                                   | Each MUTE operates                                       |

|             |                                |         |                                   | independently.                                           |

|             |                                |         |                                   | MUTE: H output ON                                        |

|             |                                |         |                                   | MUTE: L output OFF                                       |

|             |                                |         |                                   | With the output OFF, the<br>output has a high impedance. |

|             |                                |         | S-GND () <sup></sup>              | output has a high impedance.                             |

\* MUTE operates independently for each corresponding channel.

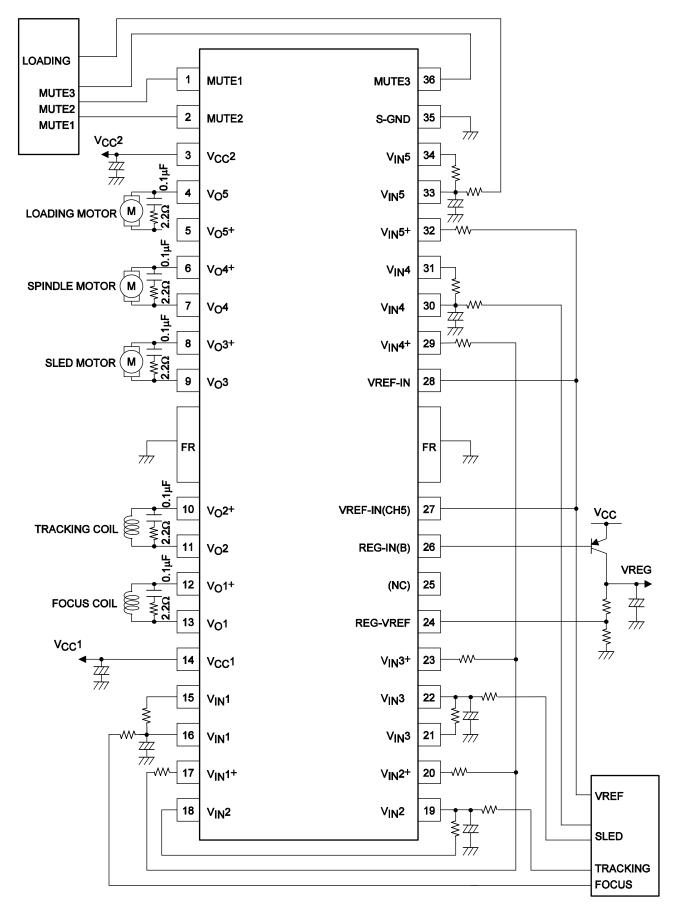

### Schematic Diagram of I/O Related Components

#### **Block Diagram**

## Sample Application Circuit

ON Semiconductor and the ON logo are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of SCILLC's product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typical" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affimative Action Employeer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

# **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Motor/Motion/Ignition Controllers & Drivers category:

Click to view products by ON Semiconductor manufacturer:

Other Similar products are found below :

FSB50550TB2FSBF15CH60BTHMSVCPM2-63-12MSVGW45-14-2MSVGW54-14-3MSVGW54-14-5NTE7043LA6565VR-TLM-ELB11650-ELB1837M-TLM-ELB1845DAZ-XELC898300XA-MHSS30-TE-L-E26700LV8281VR-TLM-HBA5839FP-E2IRAM236-1067ALA6584JA-AHLB11847L-ENCV70501DW002R2GAH293-PL-BSTK672-630CN-ETND315S-TL-2HFNA23060FSB50250ABFNA41060MSVB54MSVBTC50EMSVCPM3-54-12MSVCPM3-63-12MSVCPM4-63-12MSVTA120FSB50550ABNCV70501DW002GLC898301XA-MHLV8413GP-TE-L-EMSVGW45-14-3MSVGW45-14-4MSVGW45-14-5MSVGW54-14-4STK984-091A-EMP6519GQ-ZLB11651-EIRSM515-025DA4LV8127T-TLM-HMC33812EKR2NCP81382MNTXGTDA21801LB11851FA-BHNCV70627DQ001R2GKKKKKKKKKK