# Variable Speed Single-phase Full-wave Pre-driver for Fan Motor

## **Monolithic Digital IC**

#### Overview

LB11868V is a single-phase bipolar driving motor pre-driver with the variable speed function compatible with external PWM signal. With a few external parts, a highly-efficient and highly-silent variable drive fan motor with low power consumption can be achieved. This product is best suited for driving of the server requiring large air flow and large current and the fan motor of consumer appliances.

#### **Functions and Features**

- Single-phase Full-wave Driving Pre-driver

- Variable Speed Control Possible with External PWM Input

- Current Limiting Circuit Incorporated

- Reactive Current Cut Circuit Incorporated

- Minimum Speed Setting Pin

- Soft Start Setting Pin

- Start Setting Pin of On Time

- Pch-FET Kickback Absorption Setting Pin

- Lock Protection and Automatic Reset Circuits Incorporated

- FG (Rotational Speed Detection) Output, RD (Lock Detection) Output

- Thermal Shutdown Circuit Incorporated

### ON Semiconductor®

www.onsemi.com

SSOP24 CASE 565AR

#### **MARKING DIAGRAM**

XXXXX = Specific Device Code

Y = Year M = Month

DDD = Additional Traceability Data

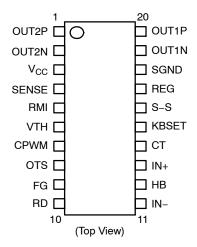

#### PIN ASSIGNMENT

#### **ORDERING INFORMATION**

See detailed ordering and shipping information on page 11 of this data sheet.

#### **SPECIFICATIONS**

## ABSOLUTE MAXIMUM RATINGS $(T_A = 25^{\circ}C)$

| Symbol                     | Parameter                                  | Conditions                        | Ratings     | Unit |

|----------------------------|--------------------------------------------|-----------------------------------|-------------|------|

| V <sub>CC</sub> max        | V <sub>CC</sub> Pin Maximum Supply Voltage |                                   | 18          | V    |

| I <sub>OUT</sub> N max     | OUTN Pin Maximum Current                   |                                   | 30          | mA   |

| V <sub>OUT</sub> N max     | OUTN Pin Output Withstand Voltage          |                                   | 18          | V    |

| I <sub>OUT</sub> P max     | OUTP Pin Maximum Sink Current              |                                   | 30          | mA   |

| I <sub>OUT</sub> P off max | Maximum Inflow Current at OUTP<br>Pin OFF  | DUTY 8% under                     | 10          | mA   |

| V <sub>OUT</sub> P max     | OUTP Pin Output Withstand Voltage          | (Note 1)                          | 19          | V    |

| VVTH/<br>VRMI max          | VTH/RMI Pins Withstand Voltage             |                                   | 7           | V    |

| V <sub>S-S</sub> max       | S-S Pin Withstand Voltage                  |                                   | 7           | V    |

| V <sub>OTS</sub> max       | OTS Pin Withstand Voltage                  |                                   | 7           | V    |

| V <sub>KBSET</sub> max     | KBSET Pin Withstand Voltage                |                                   | 7           | V    |

| V <sub>FG/RD</sub> max     | FG/RD Pin Withstand Voltage                |                                   | 19          | V    |

| I <sub>FG/RD</sub> max     | FG/RD Pin Maximum Sink Current             |                                   | 10          | mA   |

| I <sub>REG</sub> max       | REG Pin Maximum Output Current             |                                   | 10          | mA   |

| I <sub>HB</sub> max        | HB Pin Maximum Output Current              |                                   | 10          | mA   |

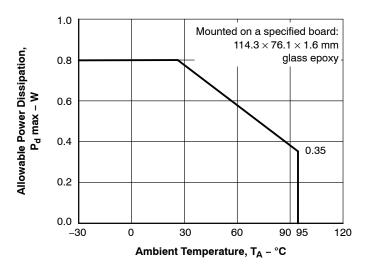

| P <sub>d</sub> max         | Allowable Power Dissipation                | With specified substrate (Note 2) | 800         | mW   |

| T <sub>opr</sub>           | Operating Temperature                      | (Note 3)                          | -30 to +95  | °C   |

| T <sub>stg</sub>           | Storage Temperature                        |                                   | -55 to +150 | °C   |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

- 1. The direct input from the power supply is improper. There must be resistance between OUTP and the power side power supply.

- 2. Specified substrate: 114.3 mm  $\times$  76.1 mm  $\times$  1.6 mm, glass epoxy board.

- 3.  $T_i$  max = 150°C must not be exceeded.

### **RECOMMENDED OPERATING CONDITIONS** (T<sub>A</sub> = 25°C)

| Symbol              | Parameter                      | Conditions | Ratings    | Unit |

|---------------------|--------------------------------|------------|------------|------|

| V <sub>CC</sub>     | V <sub>CC</sub> Supply Voltage |            | 4.0 to 16  | V    |

| V <sub>TH/RMI</sub> | VTH/RMI Input Voltage Range    |            | 0 to 4.0   | V    |

| V <sub>ICM</sub>    | Hall Input Voltage Range       |            | 0.2 to 1.8 | V    |

Functional operation above the stresses listed in the Recommended Operating Ranges is not implied. Extended exposure to stresses beyond the Recommended Operating Ranges limits may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS** (T<sub>A</sub> = 25°C, V<sub>CC</sub> = 12 V)

| Symbol              | Parameter                  | Conditions                | Min  | Тур  | Max  | Unit |

|---------------------|----------------------------|---------------------------|------|------|------|------|

| I <sub>CC</sub> 1   | CircuitCcurrent            | During drive              | 7.5  | 9.0  | 10.5 | mA   |

| I <sub>CC</sub> 2   |                            | During lock protection    | 6.0  | 7.6  | 9.0  | mA   |

| $V_{REG}$           | REG Voltage                | I <sub>REG</sub> = 5 mA   | 3.65 | 3.80 | 3.95 | V    |

| $V_{HB}$            | HB Voltage                 | I <sub>HB</sub> = 5 mA    | 1.14 | 1.24 | 1.34 | V    |

| $V_{LIM}$           | Current Limiting Voltage   |                           | 195  | 215  | 235  | mV   |

| $V_{CPWM}H$         | CPWM Pin "H" Level Voltage |                           | 2.35 | 2.50 | 2.65 | V    |

| $V_{CPWM}L$         | CPWM Pin "L" Level Voltage |                           | 0.65 | 0.80 | 0.95 | V    |

| I <sub>CPWM</sub> 1 | CPWM Pin Charge Current    | V <sub>CPWM</sub> = 0.5 V | 19   | 24   | 29   | μΑ   |

## **ELECTRICAL CHARACTERISTICS** ( $T_A = 25^{\circ}C$ , $V_{CC} = 12 \text{ V}$ ) (continued)

| Symbol                             | Parameter                     | Conditions                                                      | Min  | Тур                  | Max                  | Unit  |

|------------------------------------|-------------------------------|-----------------------------------------------------------------|------|----------------------|----------------------|-------|

| I <sub>CPWM</sub> 2                | CPWM Pin Discharge Current    | V <sub>CPWM</sub> = 2.8 V                                       | 19.5 | 24.5                 | 29.5                 | μΑ    |

| FPWM                               | CPWM Oscillation Frequency    | C = 220 pF                                                      | _    | 32                   | -                    | kHz   |

| V <sub>CT</sub> H                  | CT Pin "H" Level Voltage      |                                                                 | 2.35 | 2.50                 | 2.65                 | V     |

| V <sub>CT</sub> L                  | CT Pin "L" Level Voltage      |                                                                 | 0.65 | 0.80                 | 0.95                 | V     |

| I <sub>CT</sub> 1                  | CT Pin Charge Current         | V <sub>CT</sub> = 0.5 V                                         | 1.6  | 2.0                  | 2.4                  | μΑ    |

| I <sub>CT</sub> 2                  | CT Pin Discharge Current      | V <sub>CT</sub> = 2.8 V                                         | 0.16 | 0.20                 | 0.24                 | μΑ    |

| R <sub>CT</sub>                    | CT Pin Charge/Discharge Ratio | I <sub>CT</sub> 1/I <sub>CT</sub> 2                             | 8    | 10                   | 12                   | times |

| $I_{S-S}$                          | S-S Pin Discharge Current     | V <sub>S-S</sub> = 1 V                                          | 0.35 | 0.45                 | 0.55                 | μΑ    |

| I <sub>OTS</sub> 1                 | OTS Pin Charge Current        | V <sub>OTS</sub> = 0.5 V                                        | 0.65 | 0.85                 | 1.05                 | μΑ    |

| I <sub>OTS</sub> 2                 | OTS Pin Discharge Current     | V <sub>OTS</sub> = 0.5 V                                        | 50   | 58                   | 66                   | μΑ    |

| V <sub>OTS</sub>                   | OTS Pin Threshold Voltage     |                                                                 | 1.2  | 1.3                  | 1.4                  | V     |

| V <sub>O</sub> NH                  | OUTN Output H-level Voltage   | I <sub>O</sub> = 1 mA                                           | -    | V <sub>CC</sub> -0.9 | V <sub>CC</sub> -1.0 | V     |

|                                    |                               | I <sub>O</sub> = 10 mA                                          | -    | V <sub>CC</sub> -1.9 | V <sub>CC</sub> -2.1 | V     |

| V <sub>O</sub> NL                  | OUTN Output L-level Voltage   | IO = 10 mA                                                      | -    | 0.9                  | 1.05                 | V     |

| V <sub>O</sub> PL                  | OUTP Output L-level Voltage   | IO = 10 mA                                                      | _    | 0.4                  | 0.55                 | V     |

| V <sub>HN</sub>                    | Hall Input Sensitivity        | IN+, IN- differential voltage (including offset and hysteresis) | -    | ±10                  | ±20                  | mV    |

| V <sub>FG</sub> L/ <sub>RD</sub> L | FG/RD Output L-level Voltage  | I <sub>FG/RD</sub> = 5 mA                                       | -    | 0.2                  | 0.3                  | V     |

| I <sub>FG</sub> L/ <sub>RD</sub> L | FG/RD Pin Leakage Current     | V <sub>FG/RD</sub> = 19 V                                       | -    | -                    | 10                   | μΑ    |

| I <sub>VTH</sub> /I <sub>RMI</sub> | VTH/RMI Pin Bias Current      | CPWM = 2 V, V <sub>TH/RMI</sub> = 1 V                           | -    | -                    | 0.3                  | μΑ    |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

## TRUTH TABLE - DRIVE LOCK CPWM = H VTH, RMI, S-S = L

| IN- | IN+ | СТ | OUT1P | OUT1N | OUT2P | OUT2N | FG  | RD  | Mode                                     |

|-----|-----|----|-------|-------|-------|-------|-----|-----|------------------------------------------|

| Н   | L   | L  | L     | L     | OFF   | Н     | L   | L   | $OUT1 \to 2 \; drive$                    |

| L   | Н   |    | OFF   | Н     | L     | L     | OFF | L   | $\text{OUT2} \rightarrow \text{1 drive}$ |

| Н   | L   | Н  | OFF   | L     | OFF   | Н     | L   | OFF | Lock protection                          |

| L   | Н   |    | OFF   | Н     | OFF   | L     | OFF | OFF |                                          |

#### TRUTH TABLE - SPEED CONTROL CT, S-S = L

| VTH, RMI | CPWM | OTS | IN- | IN+ | OUT1P | OUT1N | OUT2P | OUT2N | Mode                         |

|----------|------|-----|-----|-----|-------|-------|-------|-------|------------------------------|

| L        | Н    | L   | Н   | L   | L     | L     | OFF   | Н     | OUT1 $\rightarrow$ 2 drive   |

|          |      |     | L   | Н   | OFF   | Н     | L     | L     | $OUT2 \rightarrow 1 \ drive$ |

| Н        | L    |     | H   | L   | OFF   | L     | OFF   | Н     | Regeneration mode            |

|          |      |     | L   | Н   | OFF   | Н     | OFF   | L     |                              |

| Н        | L    | Н   | Н   | L   | OFF   | L     | OFF   | L     | Standby mode                 |

|          |      |     | L   | Н   | OFF   | L     | OFF   | L     |                              |

NOTE: For VTH, RMI, and S-S pins, refer to the timing chart.

Figure 1. P<sub>d</sub> max – T<sub>A</sub>

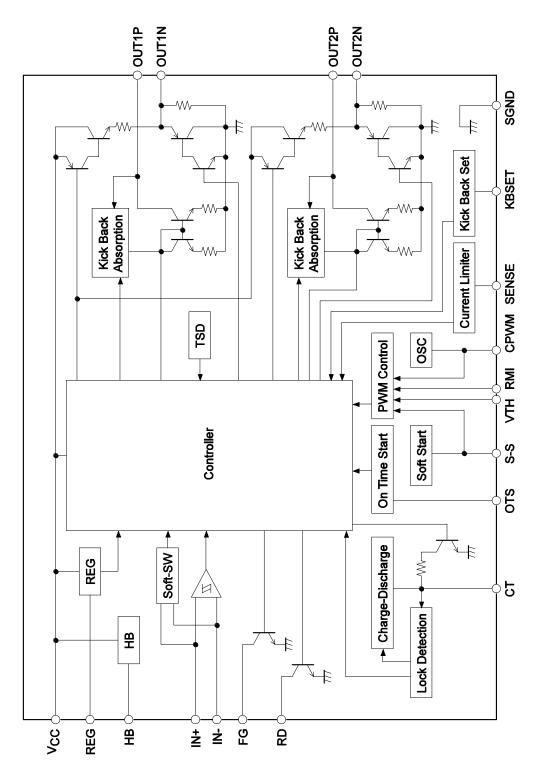

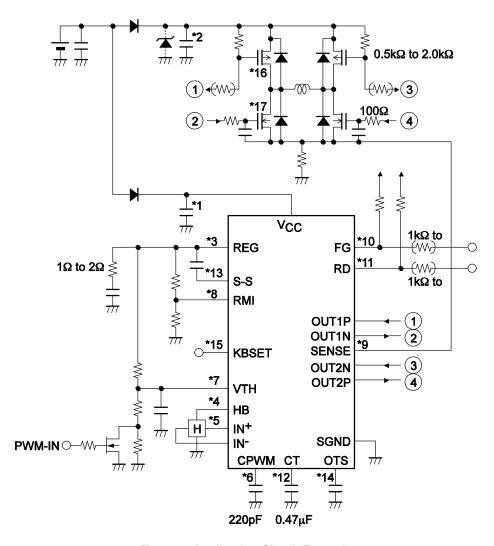

## **BLOCK DIAGRAM**

Figure 2. Block Diagram

#### **APPLICATION CIRCUIT**

Figure 3. Application Circuit Example

- \*1: Power Stabilization Capacitor:

- For the power stabilization capacitor on the signal side, use the capacitance of 1  $\mu F$  or more.

- Connect  $V_{CC}$  and SGND with a thick and shortest pattern.

- \*2: Power Stabilization Capacitor on the Power Side: For the power stabilization capacitor on the power side, use the capacitance of 1 μF or more. Connect the power supply on the power side and

GND with a thick and shortest pattern.

When the IC is used for a fan with a high current level, insert a zener diode between the power supply on the power side and GND.

\*3: REG Pin:

3.8 V constant-voltage output pin. For the REG oscillation prevention and stabilization, use a capacitor with capacitance of 1  $\mu F$  or more. Connect the REG pin and SGND with a thick and shortest pattern.

\*4: HB Pin:

Used for Hall device bias purposes.

\*5: IN+, IN- Pins:

Hall signal input pin.

Wiring should be short to prevent carrying of noise.

If noise is carried, insert the capacitor between IN+ and IN- pins.

The Hall input circuit functions as a comparator with hysteresis (15 mV).

This also has a soft switch section with  $\pm 30 \text{ mV}$  (input signal differential voltage).

It is also recommended that the Hall input level is minimum 100mV (p-p).

\*6: CPWM Pin:

Pin to connect the capacitor for generation of the PWM basic frequency.

The use of CP = 220 pF causes oscillation at f = 30 kHz (typical), which is the basic frequency

of PWM.

As this is used also for the current limiting canceling signal, ON-time start function and Soft start function, be sure to connect the capacitor even when the speed control is not made.

#### \*7: RMI Pin:

Minimum speed setting pin.

Perform pull-up with REG when this pin is not to be used.

If the IC power supply is likely to be turned OFF first when the pin is used with external power supply, be sure to insert the current limiting resistor to prevent inflow of large current. (The same applies to the VTH pin.)

#### \*8: VTH Pin:

Speed control pin.

Connect this pin to GND when it is not used (at full speed).

For the control method, refer to the timing chart. For control with pulse input, insert the current limiting resistor and use the pin with the frequency of 20 kHz to 100 kHz (20 kHz to 50 kHz recommended).

#### \*9: SENSE Pin:

Current limiting detection pin.

When the pin voltage exceeds VLIM, the current is limited and the operation enters the lower regeneration mode.

Connect this pin to GND when it is not to be used.

#### \*10: FG Pin:

Rotational speed detection pin.

Open collector output that can detect rotational speeds by the FG output in response to the phase switching signal.

Keep this pin open when it is not to be used. It is recommended that a current-limiting resistor with a resistance of 1  $k\Omega$  or more be inserted in order to protect the pin during unplugging and plugging the connector or when mistakes are made in connection.

#### \*11: RD Pin:

Lock detection pin.

In open collector output, L upon rotation and H when locked (using pull-up resistance).

Keep this pin open when it is not to be used.

## \*12: CT Pin:

Pin to connect the lock detection capacitor. The constant-current charge and discharge circuits incorporated cause locking when the pin voltage becomes VCTH and unlocking when it is VCTL. Connect the pin to GND when it is not to be used (locking not necessary).

#### \*13: S-S Pin:

Pin to connect the soft-start setting capacitor. Connect the capacitor between REG and S-S pin. This pin enables setting of the soft start time according to the capacity of the capacitor. See the timing char.

Connect the pin to GND when it is not to be used.

#### \*14: OTS Pin:

Pin to connect the ON-time start setting capacitor. A constant-current charging circuit and a discharging circuit based on the control duty ratio are incorporated, and when the pin voltage exceeds VOTS, the CT pin is discharged and the S–S pin is charged.

Connect the pin to GND when it is not to be used (when the lowest speed setting is used).

#### \*15: KBSET Pin:

Pch kickback absorption circuit setting pin.

Open: The kickback absorption circuit is activated at a VCC voltage of 7.4 V (typ) or above.

Pull-down to GND: Always OFF

Pull-up to REG: Always ON (but when the IC power is OFF, the kickback absorption circuit is OFF)

If the Pch load is to be reduced due to the large fan current, short the KBSET pin to GND, and use a zener diode between the power supply on the power side and GND.

Kickback absorption circuit ON: At OUTPOFF, the OUTP voltage is clamped at VCC + 0.85 V (at room temperature and inflow current 5 mA (typ)). Kickback absorption circuit OFF: At OUTPOFF, the OUTP voltage is clamped at 18 V or so (at room temperature and inflow current 5 mA (typ)) in order to protect the pin.

At OUTPOFF, the maximum inflow current must not be exceeded.

#### \*16: Pch FET:

If the Pch kickback absorption circuit is activated and a zener diode between the power supply and GND is not used, the kickback during phase switching is absorbed by Pch.

Since the circuit is activated with a high voltage difference between the drain and source, select a FET with sufficiently high capability.

#### \*17: Nch FET:

If the Nch gate voltage fluctuates significantly due to the effects of switching, insert a capacitor between the gate and GND.

Since an Nch diode is used during coil current regeneration, select a FET with sufficiently high capability.

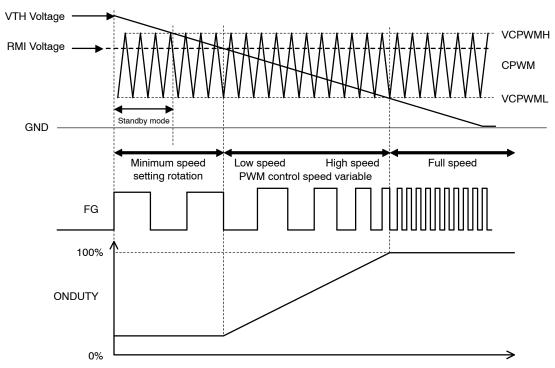

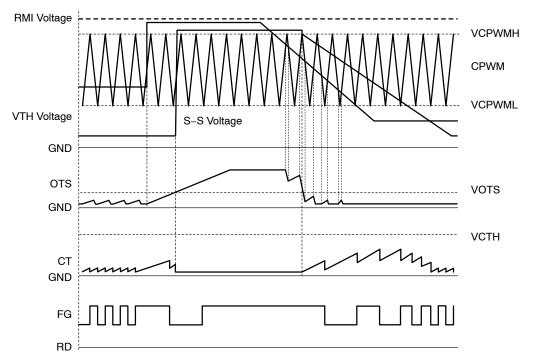

# CONTROL TIMING CHART (SPEED CONTROL)

Figure 4. Control Timing Chart - Speed Control

- 1. Minimum Speed Setting (Standby) Mode:

The low-speed fan rotation occurs at the minimum speed set with the RMI pin.

When the minimum speed is not set (RMI pin pulled up to REG), the motor stops.

If the VHT voltage rises when the lowest speed is not set (RMI pin is pulled up to REG), the fan stops running, and if the OTS pin capacitor is used, the standby mode is established.

Details of the standby mode are given in the section "Control timing chart (ON-time start, Lock protection).

- 2. Low Speed ⇔ High Speed:

PMW control is made by comparing the CPWM oscillation voltage (VCPWMLVCPEMH) and VTH voltage.

The drive mode is established when the VTH voltage is low.

Both upper and lower output FET are turned ON

when the VTH voltage is low.

When the VTH voltage is high, Pch is turned off, and the coil current is regenerated inside the lower FET. Therefore, as the VTH voltage decreases, the output ON-DUTY increases, causing an increase in the coil current and raising the motor rotation speed.

The upper output Pch is turned OFF when the VTH voltage is high, regenerating the coil current in the lower TR. Therefore, as the VTH voltage decreases, the output ON-DUTY increases, causing increase in the coil current, raising the motor rotation speed.

The rotational speed can be monitored using the FG output.

3. Full Speed Mode:

The full speed mode becomes effective when the VTH voltage is VCPWML or less. (Set VTH = GND when the speed control is not to be made.)

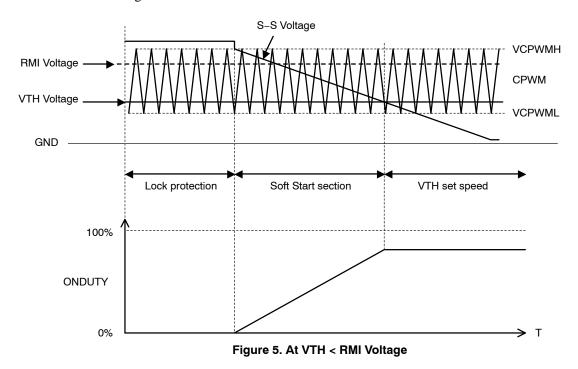

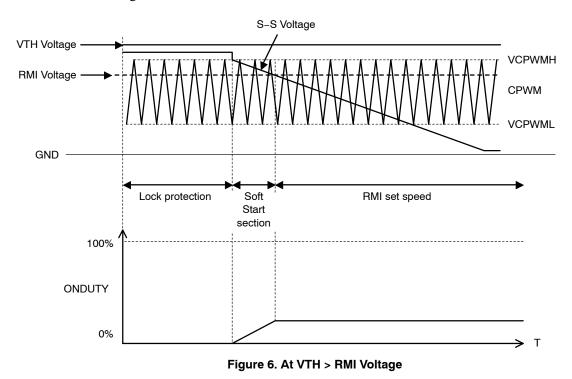

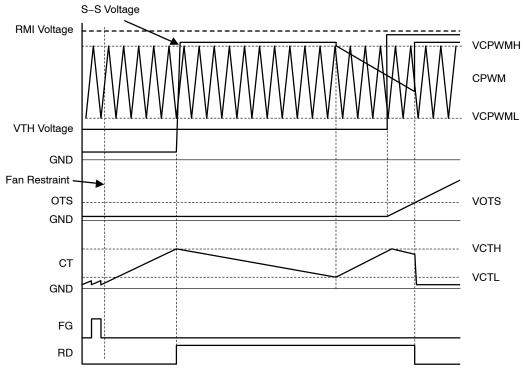

# CONTROL TIMING CHART (SOFT START)

### 1. At VTH < RMI Voltage

#### 2. At VTH > RMI Voltage

Adjust the S-S pin voltage gradient by means of the capacitance of the capacitor between the S-S pin and REG.

Recommended capacitor:  $0.1~\mu$  to  $1~\mu F$

# CONTROL TIMING CHART (ON-TIME START, LOCK PROTECTION)

1. When a stop signal based on the VTH voltage has been input during normal rotation.

Figure 7.

When the output duty ratio based on the VTH/RMI input drops to below 1% or so, the OTS voltage rises, and when it reaches VOTS, the standby mode is established, the CT pin discharges, and the S-S pin is charged. In the standby mode, if the drive mode has been established again by the

VTH/RMI input, the rotation is started immediately with soft start.

The CT pin discharges at the same time as the switching of FG. For details on lock protection, refer to 2.

2. When a stop signal based on the VTH voltage has been input while the fan is constrained

Figure 8.

When the fan is constrained, the CT pin voltage rises, and when it reaches VCTH, the lock protection mode is established, and OUTP is set to OFF and RD is set to OFF.

When the lock protection mode is established, the CT pin discharges, and when VCTL is reached, restart (soft start) is

initiated. When rotation is started and the FG signal is switched, RD is set to low.

NOTE: RD is also set to low when the standby mode is established when locked.

#### **ORDERING INFORMATION**

| Device         | Package                                      | Wire Bond | Shipping <sup>†</sup> (Qty / Packing) |

|----------------|----------------------------------------------|-----------|---------------------------------------|

| LB11868V-TLM-H | SSOP20J (225mil)<br>(Pb–Free / Halogen Free) | Au-wire   | 2,000 / Tape & Reel                   |

| LB11868V-W-AH  | SSOP20J (225mil)<br>(Pb–Free / Halogen Free) | Cu-wire   | 2,000 / Tape & Reel                   |

<sup>†</sup>For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, <a href="https://example.com/BRD8011/D">BRD8011/D</a>.

20

**DATE 23 OCT 2013**

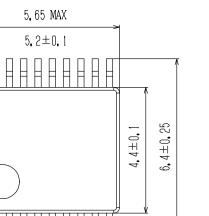

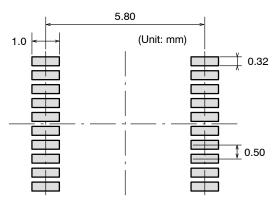

# SSOP20J (225mil)

CASE 565AP ISSUE A

[⊕|0**.** 12 (M)

0. 10 S 01. 0 S MAX

#### **SOLDERING FOOTPRINT\***

0.5

(0.35)

NOTE: The measurements are not to guarantee but for reference only.

\*For additional information on our Pb-Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

# GENERIC MARKING DIAGRAM\*

XXXXX = Specific Device Code

Y = Year

M = Month

DDD = Additional Traceability Data

\*This information is generic. Please refer to device data sheet for actual part marking. Pb–Free indicator, "G" or microdot " ■", may or may not be present.

| DOCUMENT NUMBER: | 98AON66067E      | Electronic versions are uncontrolled except when accessed directly from the Document Repos<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |             |  |  |

|------------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--|--|

| DESCRIPTION:     | SSOP20J (225MIL) |                                                                                                                                                                               | PAGE 1 OF 1 |  |  |

ON Semiconductor and are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. ON Semiconductor does not convey any license under its patent rights nor the rights of others.

onsemi, ONSEMI, and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi's product/patent coverage may be accessed at <a href="www.onsemi.com/site/pdf/Patent-Marking.pdf">www.onsemi.com/site/pdf/Patent-Marking.pdf</a>. onsemi reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product features, availability, functionality, or suitability of its products for any particular purpose, nor does **onsemi** assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using **onsemi** products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by **onsemi**. "Typical" parameters which may be provided in **onsemi** data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. **onsemi** does not convey any license under any of its intellectual property rights nor the rights of others. **onsemi** products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use **onsemi** products for any such unintended or unauthorized application, Buyer shall indemnify and hold **onsemi** and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that **onsemi** was negligent regarding the design or manufacture of the part. **onsemi** is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

#### PUBLICATION ORDERING INFORMATION

LITERATURE FULFILLMENT: Email Requests to: orderlit@onsemi.com

onsemi Website: www.onsemi.com

**TECHNICAL SUPPORT** North American Technical Support: Voice Mail: 1 800–282–9855 Toll Free USA/Canada

Phone: 011 421 33 790 2910

Europe, Middle East and Africa Technical Support:

Phone: 00421 33 790 2910

For additional information, please contact your local Sales Representative

## **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Motor/Motion/Ignition Controllers & Drivers category:

Click to view products by ON Semiconductor manufacturer:

Other Similar products are found below:

FSB50550TB2 FSBF15CH60BTH MSVCPM2-63-12 MSVGW45-14-2 MSVGW54-14-3 MSVGW54-14-5 NTE7043 LA6565VR-TLM-E LB11650-E LB1837M-TLM-E LB1845DAZ-XE LC898300XA-MH SS30-TE-L-E 26700 LV8281VR-TLM-H BA5839FP-E2 IRAM236-1067A LA6584JA-AH LB11847L-E NCV70501DW002R2G AH293-PL-B STK672-630CN-E TND315S-TL-2H FNA23060 FSB50250AB FNA41060 MSVB54 MSVBTC50E MSVCPM3-54-12 MSVCPM3-63-12 MSVCPM4-63-12 MSVTA120 FSB50550AB NCV70501DW002G LC898301XA-MH LV8413GP-TE-L-E MSVGW45-14-3 MSVGW45-14-4 MSVGW45-14-5 MSVGW54-14-4 STK984-091A-E MP6519GQ-Z LB11651-E IRSM515-025DA4 LV8127T-TLM-H MC33812EKR2 NCP81382MNTXG TDA21801 LB11851FA-BH NCV70627DQ001R2G